# **REDUCED SWITCH COUNT MULTILEVEL INVERTERS: TOPOLOGIES, PWM SCHEMES AND FAULT TOLERANT OPERATION**

*Submitted in partial fulfilment of the

requirements for the award of the

degree of*

**DOCTOR OF PHILOSOPHY**

*By*

**Hari Priya Vemuganti

(Roll No. 714118)**

**Dr. D. Sreenivasarao**

Assistant Professor

**Dr. G. Siva Kumar**

Assistant Professor

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506 004, TELANGANA, INDIA**

**NOVEMBER 2018**

## **APPROVAL SHEET**

This Thesis entitled "**Reduced switch count multilevel inverters: Topologies, PWM schemes and Fault tolerant operation**" by Hari Priya Vemuganti (Roll No. 714118) is approved for the degree of Doctor of Philosophy.

### **Examiners**

---

---

---

### **Supervisors**

**Dr. D. Sreenivasarao**

Assistant Professor

EED, NIT Warangal

**Dr. G. Siva Kumar**

Assistant Professor

EED, NIT Warangal

### **Chairman**

**Dr. S. Srinivasa Rao**

Professor & Head

EED, NIT Warangal

Date: \_\_\_\_\_

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506 004**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**CERTIFICATE**

This is to certify that the thesis entitled "**Reduced switch count multilevel inverters: Topologies, PWM schemes and Fault tolerant operation,**" which is being submitted by **Hari Priya Vemuganti (Roll No. 714118)**, is a bona fide work submitted to National Institute of Technology, Warangal in partial fulfilment of the requirement for the award of the degree of **Doctor of Philosophy** in Department of Electrical Engineering. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Supervisors**

**Dr. D. Sreenivasarao**

Assistant Professor

EED, NIT Warangal

**Dr. G. Siva Kumar**

Assistant Professor

EED, NIT Warangal

Date:

Place: NIT Warangal

## **DECLARATION**

This is to certify that the work presented in the thesis entitled “Reduced switch count multilevel inverters: Topologies, PWM schemes and Fault tolerant operation” is a bona fide work done by me under the supervision of Dr. D. Sreenivasarao and Dr. G. Siva Kumar, Department of Electrical Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Hari Priya Vemuganti**

**(Roll No. 714118)**

Date:

Place: NIT Warangal

## ACKNOWLEDGEMENT

---

Apart from personal efforts and steadfastness to work, constant inspiration and encouragement given by a number of individuals acted as the driving force in attaining this day in my life. To quote them all may be an onerous task but direct and indirect assistance and guidance received is gratefully acknowledged. I would like to express my feelings of gratefulness and submit my acknowledgement for them further in the following lines.

I take this opportunity to express my sincere gratitude towards my supervisors **Dr. D. Sreenivasarao** and **Dr. G. Siva Kumar**, Assistant Professors, Electrical Engineering Department (EED), National Institute of Technology Warangal (NITW), for their proficient and enthusiastic guidance, valuable suggestions, discussions, continued encouragement and constant inspiration throughout the course and critically examining thesis write-up. I extend my gratitude to their families for their patience and perseverance for smooth completion of my course.

I also express my sincere gratitude towards my doctoral scrutiny committee (DSC) Chairman **Prof. S. Srinivasa Rao**, and members namely, **Prof. M. Sydulu** (EED), **Prof. Sonawane Shirish Hari** (Chemical Department), **Dr. T. Vinay Kumar** (EED), and **Dr. P. C Sekhar** (Asst. Prof., EED, IIT Bhubaneshwar) for their valuable suggestions and cooperation.

I wish to express my sincere thanks to **Prof. N.V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

I am very much thankful to **Prof. S. Srinivasa Rao**, Head, EED and **Prof. V. T. Somasekhar**, Former Head, EED for their constant encouragement, support and cooperation.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal. They have always been encouraging and supportive.

I also acknowledge my sincere gratitude to the Ministry of Human Resources Development (MHRD), Government of India for their financial support to carry out this research.

I also acknowledge the warm support of my well-wishers and co-scholars for their instant help, cooperation, advice, suggestion, and moral support during my stay. The list may go long but I would like to mention some of them: Ms. Sai Spandana, Mr. Hareesh, Mr. G. Eshwar Gowd, Mr. Pranay Kumar, Mr. Ram Kumar, Mr. Chinna, Ms. Shara Sowmya, Mr. Satish, Ms. Srilatha, Ms. Sagarika, Ms. Sunitha, Mr. Pradeep, Ms. Navya and Mr. Naresh.

I am express my in-depth gratitude to Dr. N. Sambasiva Rao (Alumni of NITW), Mr. Ch. Ramesh (IES) for being a passionate driving force to get into Ph. D. I also thank Mrs. Nikkath, Ms. Lasya and Ms. Deepthi for boosting confidence in me to reach NITW.

Finally, I wish to express my deepest gratitude to my father **Late Sreenivasa Rao**, mother **Padma**, Sister Vamsi Priya, brother-in-law Sandeep, and niece Sri Aadhyा, for their patience, endless support, trust and encouragement.

May all praises be to the Almighty, the most beneficent, and the most merciful.

*(Hari Priya Vemuganti)*

# ABSTRACT

---

The fast growing energy needs and drastic globalization have increased the requirement of reliable, high efficient and uninterrupted power for various industrial, transport, telecommunication, aerospace, traction, energy storage, residential and domestic applications. Hence, an efficient and controllable power converter is a pre-requisite for meeting the desired specifications at the load end. Conventional controllers such as thyratrons, mercury-arc rectifiers, magnetic amplifiers and rheostat controllers possess various limitations in terms of size, cost, complexity, maintenance, reliability, efficiency, safety and robustness. The advent of self-commutating devices, the era of power converters have changed enormously. Among, ac-dc (rectifiers) and dc-ac (inverters) converters plays a significant role in most of the applications.

AC-DC power conversion can be broadly categorised into voltage source (VSI) and current source inverters (CSI). However, one may prefer CSI due to its robustness or the VSI due to its high efficiency, low initial cost, and smaller physical size. Among these, VSI based power converters has been considered in the present work as they have higher market penetration and noticeable development in last two decades. The poor harmonic performance, high device ratings and requirement of input and output filters makes the two-level VSI impractical for direct use in high-power, medium-voltage applications. Thus, to realize VSI for high-power applications, multipulse and multilevel inverters (MLI) are the two popular solutions reported in literature. The first one requires phase-shifting transformers which increases the converter size, cost and complexity. However, the later one does not involve any phase-shifting transformers and can be directly incorporated for high-power medium-voltage applications with matured medium power electronic devices. Owing to this, MLIs have gathered much attention in industry and academia as one of the preferred choice for high-power applications and successfully made their way into the industry.

MLIs are proven as a matured technology for various commercialized and customized products for a wide power range of applications such as traction, compressors, extruders, pumps, fans, grinding mills, rolling mills, conveyors, crushers, blast furnace blowers, gas turbine starters, mixers, mine hoists, electric vehicles, reactive power compensators, renewable energy generation, custom power devices, marine propulsion, high-voltage direct-current (HVDC) transmission. Among the topologies of MLIs, diode clamped (DCMLI), flying capacitor (FCMLI), and cascade H-bridge (CHB) are widely popular and termed as classical MLIs. These topologies gathered a great attention both from academia and industry. Their practical implementation is heavily influenced by the application, control complexity and cost.

The requirement of large number of power components and voltage unbalance problem at higher levels limits the DCMLI for low power rating applications. The requirement of large number of capacitors and their pre-charge requirement limits FCMLI to high bandwidth applications such as traction drives.

The modular structure and high fault tolerance ability makes CHB best suited for high-voltage medium-power applications (13.8 kV, 30 MVA). However, CHB requires isolated dc sources for active power transfer applications. As similar to DCMLI and FCMLI, switch count of CHB increases with number of levels in phase-voltage. In addition, topologies of classical MLIs present great deal of challenge in implementation to higher levels. This is due to its increased device count at higher levels, which complicates its circuit configuration and imparts size, cost and maintenance limitations. Hence, researchers continued to explore and evolve newer topologies by making more or less changes on the classical MLIs. CHB with unequal dc link voltages or hybrid combination with DCMLI can increase the number of levels with significant reduction in switch count. However, unequal blocking voltages of switching devices and limited switching redundancies of these topologies cause uneven utilization of dc sources.

The increased component count of power semiconductor devices and capacitor/dc sources of classical MLI topologies has provoked the researchers to contribute further to evolve newer topologies with reduction in size and cost. Thus, MLI with reduced device count originated and this domain of MLIs are called as reduced switch count (RSC) MLIs. From the past decade, various enthusiasts carried out extreme research on RSC-MLIs and developed numerous topologies with significant reduction in component count, total blocking voltage, cost and ease of control. Several RSC-MLI topologies such as multilevel dc link (MLDCL), packed U-cell (PUC), cascaded bi-polar switched cells (CBSC), reverse voltage (RV), switched dc sources (SDS), basic unit MLI, envelope-type (E-type), T-type, hybrid T-type, series-connected switched sources (SCSS), switched series parallel sources (SSPS), nested MLI, switched capacitor unit, reduced cascaded and various other three-phase and cascaded topologies are reported in literature.

In this connection, qualitative and quantitative features of RSC-MLI topologies have discussed in this thesis and, a comparison has made to facilitate a well-informed selection of topology for a given application. For this, a comprehensive comparison between various RSC-MLI topologies is presented in terms of performance parameters such as device count, device ratings, blocking voltages, requirement of bi-directional switches, nature of dc link, modularity, fault tolerant ability, switching and conduction losses, power distribution and utilization of dc link voltages. Considering the above factors, RSC-MLIs are categorized into symmetrical and asymmetrical configurations, topologies with separate level and polarity generator, generalized

and unit-based configurations, H-bridge and hexagonal switch cell (HSC) structures, topologies with uni-directional and bi-directional switches, topologies with isolated/floating dc sources and topologies with series/parallel operation of dc sources.

The reduction in switch count, even power sharing among dc voltage sources and adequate switching redundancies are the paramount criteria for the selection of inverter topology. Among these, MLDCL possess simplified and modular structure with appreciable reduction in switch count, multiple switching redundancies, symmetric and simplified switching operation, fault tolerant ability, even power distribution, equal device blocking voltages and dc link voltage balancing ability. Owing to these key and worthy benefits, this topology had gathered more attention and further served as a viable alternative for CHB in applications such as grid-connected photo-voltaic system, uninterrupted power supplies (UPS), custom power devices (CPD), adjustable speed drives (ASD), battery energy storage systems (BESS), active front-end (AFE) applications and electric vehicles (EV).

The significant reduction in switch count of RSC-MLI topologies has simplified their circuit configuration such that, each switch may involve in attaining more than one voltage level. Asymmetrical RSC-MLIs further reduced the switch count and made the topologies much simpler. However, significant reduction in switch count have reduced the redundancies and modified the switching combination such that, devices conducting for obtaining lower voltage level may not remain in conduction at higher levels as well. This acted as a limitation of conventional carrier based pulse width modulation (PWM) schemes such as level-shifted (LSPWM) and phase-shifted (PSPWM) to control these RSC-MLIs.

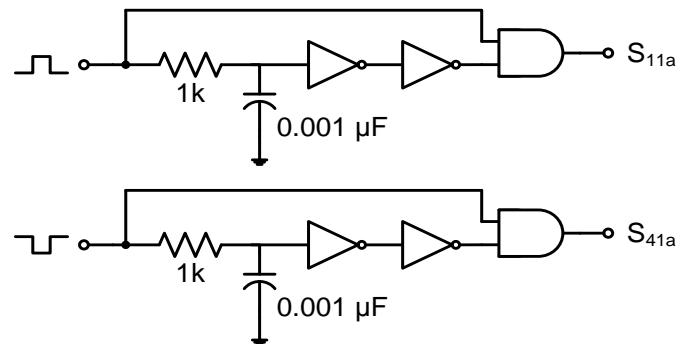

To control any RSC-MLI, selective harmonic elimination (SHE) and space vector (SV) PWM are often preferred. However, these schemes require elusive calculations and complexity increases at higher number of levels. Hybrid PWM is another popular scheme reported for implementing asymmetrical cascaded configurations such as CHB and SSPS (with an addition of H-Bridge). However, requires estimation of output voltage of the higher voltage bridge/units, to derive the reference signal for lower voltage bridge/units. Switching schemes using low frequency carrier reported for MLDCL, CBSC, basic unit RSC-MLI, T-type and Hybrid T-type topologies are easy to realize but, produces lower order harmonics. On the other hand, among the carrier based PWM schemes, multi reference, reduced carrier and hybrid switching function are widely popular. Multi reference modulation results high THD in line-voltage and requires multiple dc off shifted references which increases the complexity in closed loop-applications. Hybrid switching function PWM results in satisfactory THD but requires numerous comparators at higher levels, which increases computational burden. Reduced carrier PWM

scheme with logical expressions are the simplest. However, these logical expressions are not generalized and vary with topology and number of levels.

Therefore, to overcome the limitations of conventional PWM schemes of RSC-MLI, modified carrier and modulating signal arrangements are proposed in this thesis. The performance of the modified PWM schemes with the proposed carrier arrangement is evaluated on five-level inverter topologies and its superior THD performance over the conventional schemes is validated. Further, a simple carrier based PWM scheme with unified logical expressions is proposed. The proposed logical expression remains valid to control any RSC-MLI, irrespective to the voltage ratios and topological arrangement and produces good THD performance with less computation burden.

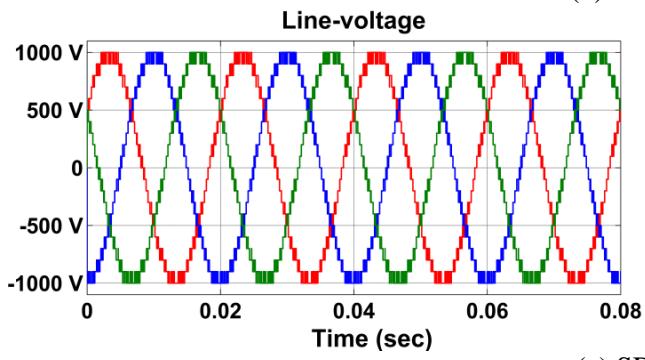

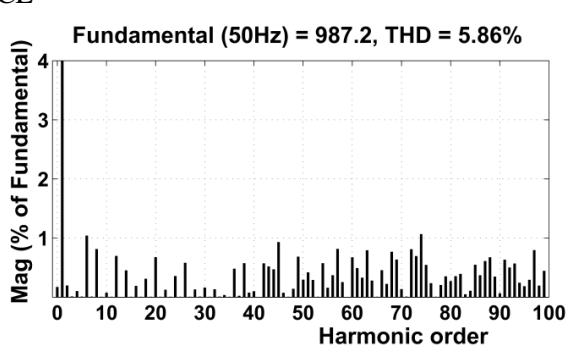

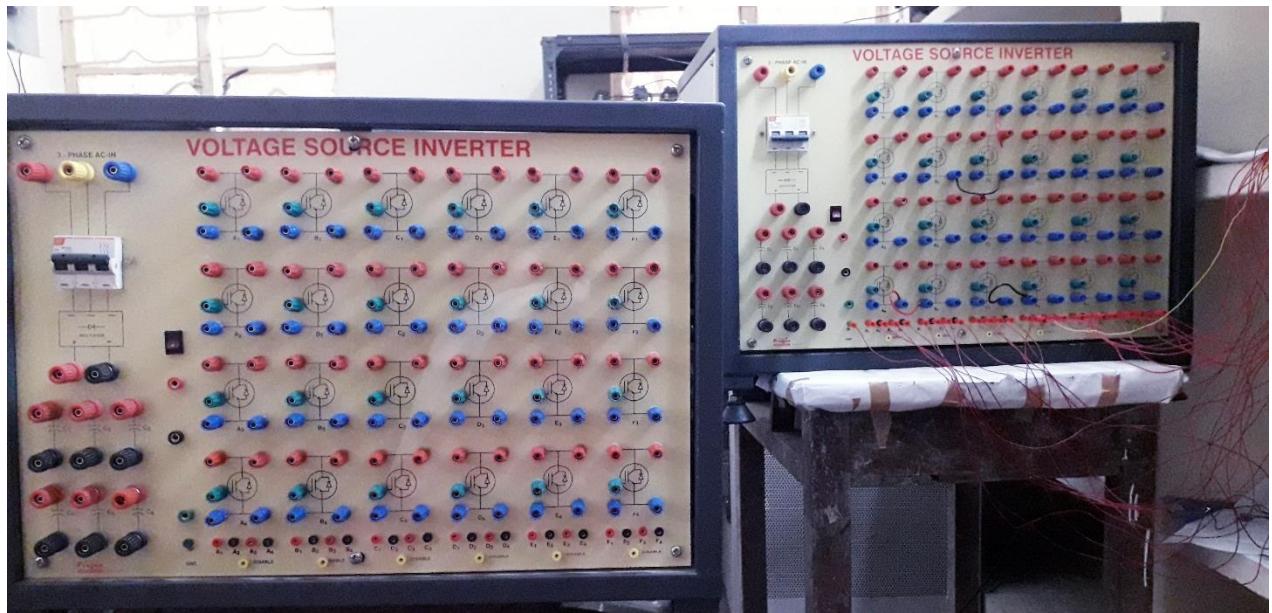

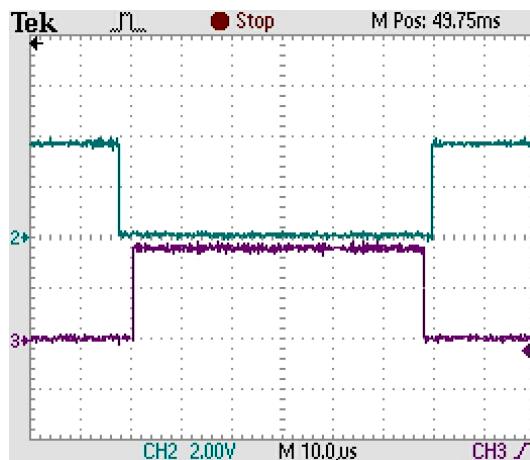

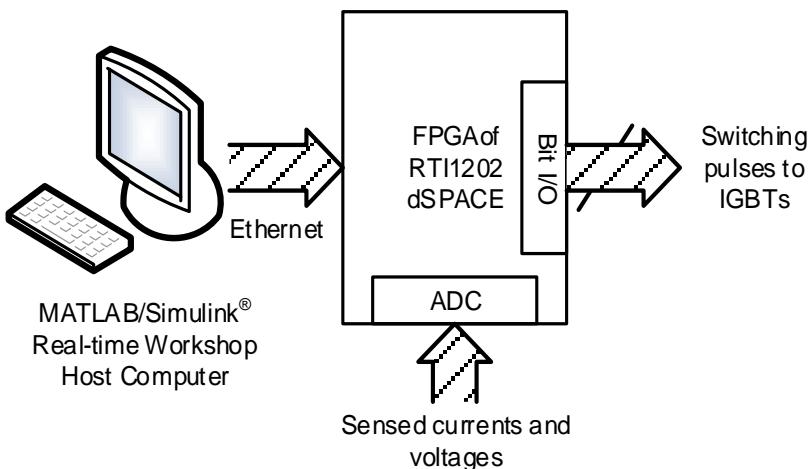

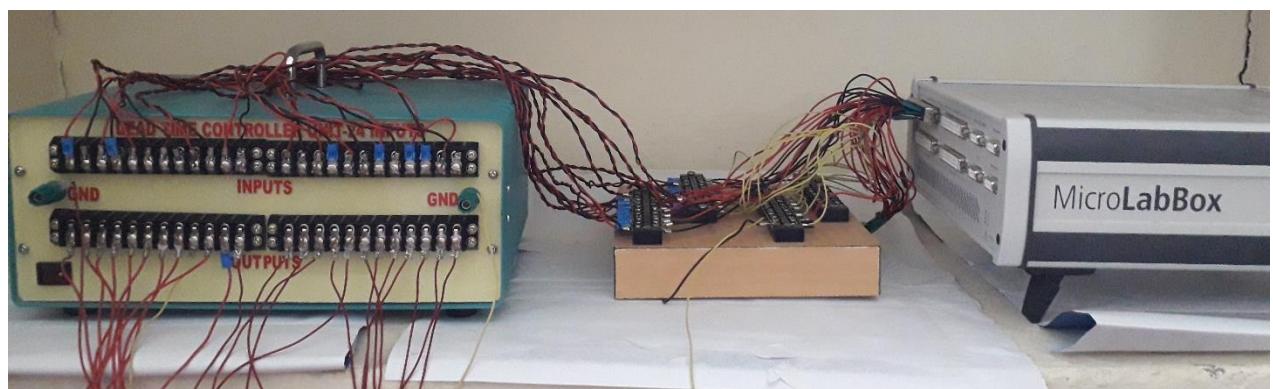

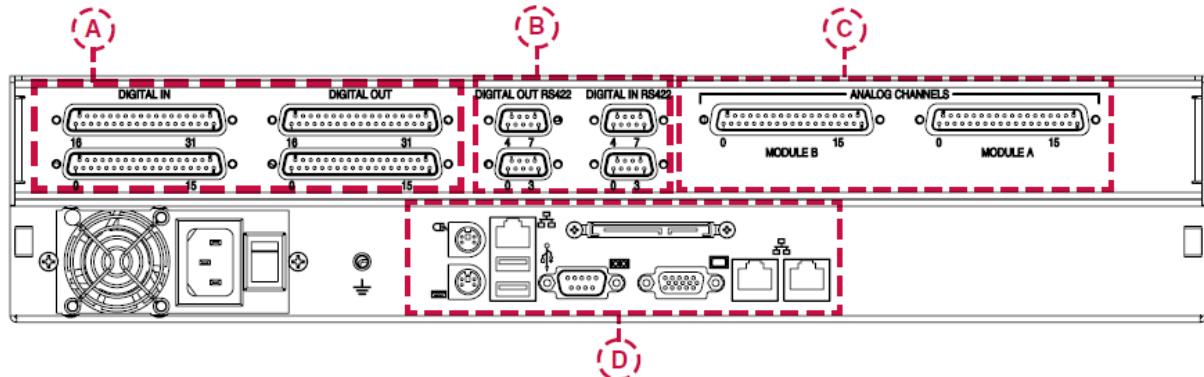

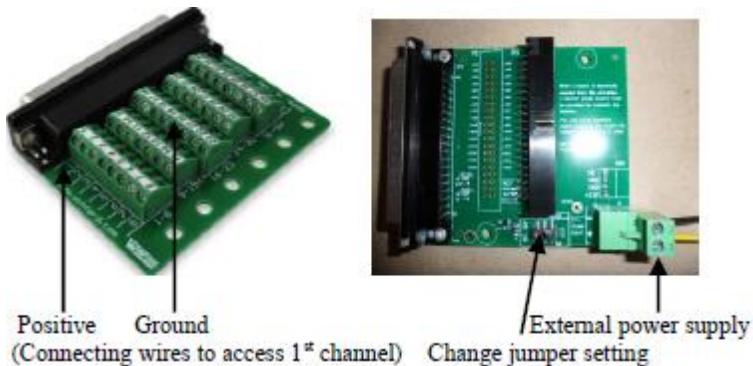

To validate the ability of the proposed switching logic, the PWM scheme is implemented in MATLAB/Simulink environment for thirteen-level asymmetrical RSC-MLI configurations such as MLDCL, SDS, Cascaded T-type, Improved T-type and E-type. The simulation results are validated experimentally by developing various topologies of RSC-MLIs by interconnecting two inverter modules with 24 isolated IGBTs on each. The PWM scheme is implemented on dSPACE MicroLabBox R&D controller. Further to validate the superiority of the proposed PWM scheme, its performance in-terms of computation burden and line-voltage THD is compared with the state-of-the-art PWM schemes reported in the literature.

Another aspect for selection of inverter is its reliability. The ability of an inverter to work under fault conditions plays a vital in ensuring the safety and uninterrupted operation of the overall system. There are several reasons for occurrence of fault in inverters, and every fault will end up with either open-circuit (OC) or short-circuit (SC) of a particular switch or associated unit/bridge. SC fault results in dangerously high current and cause a possible damage to the inverter. To avoid these faults, a fast acting over-current protection circuits are required to by-pass the faulty phase-leg or inverter. On the other hand, OC faults are not severe and can be compensable. Hence, this thesis analyses the affects and compensation of OC faults.

The reduction in switch count of RSC-MLI has reduced the probability of fault occurrence as compared to MLI. However, the extreme reduction in switching redundancies restricted their fault tolerant ability. In literature, SVM and carrier based schemes are reported for compensating single switch fault in RSC-MLI such as T-type. Among these, SVM is an attractive scheme which can achieve fault tolerant operation (FTO) by creating switching redundancies. Nevertheless, its complex implementation acts as a limitation at higher level. In general, the fault tolerant schemes (FTS) generates a new set of modulating signals to reconfigure the inverter to achieve FTO. This FTO is feasible for modular and redundant topologies such as MLDCL.

By-passing method is one of the most feasible FTS to restore balanced operation. However, this method of fault compensation derates the inverter as the healthy units are bypassed. To obtain FTO without derating the inverter, the burden of faulty units of one phase is shared across the healthy units of same phase such that its overall phase-voltage is equal to pre-fault voltage. This method results in non-uniform burdening of healthy units, which effects their dc link voltages and power distribution among operating units. To obtain balanced operation with equal power distribution among the healthy units, neutral shifting (NS) FTS is reported. This scheme modifies the magnitude and angle between phase-voltages such that the inverter produce balanced line-voltages with uniform burden on all healthy units. NS involves manual calculation of modified phase-angles to ensure magnitude and angle balance among line-voltages. This method can compensate multiple switch faults, only if the number of faulty units in any two phases are same. Another approach to achieve NS is to inject a zero-sequence voltage to shift the neutral point of the inverter. The magnitude of injected zero-sequence voltage depends on the number of faulty units. In literature, this method is reported on CHB for compensating single switch fault (per phase), and is not reported for compensating multiple OC faults. Moreover, this scheme is not directly applicable for tolerating OC faults on RSC-MLIs.

Therefore in this thesis, a generalized NS zero-sequence injection FTS is proposed for compensating multiple OC switch faults on MLDCL inverter. Generalised equations are proposed to determine the magnitude of injected zero-sequence voltage and fault tolerant modulating signals, for any fault case. The proposed generalized fault tolerant modulating signals are operated with carrier rotation based reduced carrier PWM scheme to obtain balanced set of line-voltages with uniform power distribution among all the operating units. To investigate the ability of the proposed generalized FTS, simulation study on three-phase fifteen-level MLDCL inverter is performed. The inverter is controlled with the proposed modified reduced carrier PWM scheme and to achieve uniform burden among healthy operating units, the carriers are rotated at the end of each carrier time period. After the initiation of FTO, the balanced operation of the inverter is observed from their line-voltage and current waveforms and their respective RMS values. In addition, power delivered by each unit ensures the uniform performance (power distribution) among all the operating units. To corroborate the simulation results, a nine-level three-phase IGBT based MLDCL inverter is developed and controlled, using OPAL-RT 4500. However, performance of proposed FTS is validated assuming stiff sources in the dc link and the effect of charging and discharging currents on dc link voltages during fault compensation is excluded.

Therefore, to investigate the efficacy of proposed FTS in closed-loop application, an active rectifiers is considered. Multilevel converter (MLC) based active rectifiers gained more

prominence for high-power applications such as UPS, grid-connected applications, BESS, battery chargers and ASD. Owing to challenges such as voltage balance of dc link capacitors, even power sharing and fault tolerant operation, the implementation of RSC-MLI topologies as an active rectifiers is not yet reported.

In literature, various voltage and current control techniques are reported for three-phase regenerative active rectifiers. Among these, direct power control (DPC) and voltage oriented control (VOC) are commonly used control schemes. DPC produces fast and accurate response, and involves either hysteresis, predictive or adaptive controllers, followed by PWM or look-up tables. Practice of predictive or adaptive controllers increases the difficulty in realizing DPC for MLCs/RSC-MLCs based active rectifiers. On the other hand, VOC is simple and more robust, and can be easily implemented for MLCs and RSC-MLCs. The objective behind VOC is to regulate the dc link voltages, irrespective to the load variations. On the other hand, to regulate the power delivered by the converter, irrespective to the load conditions, grid active reactive power control (GARPC) is reported. This method senses and controls the dc link voltage such that a rated power with unity power factor is delivered to the converter for any load condition. GARPC is also known as instantaneous active and reactive power control.

The above control algorithms can be effective only if the converter is able to provide an appropriate path for charging and discharging of dc link capacitors. If the converter operation is faulty, then its operation is restricted and results dc link voltage unbalance. As the design and control of RSC-MLC based active rectifier for healthy and faulty operation of the converter is not yet reported, and therefore an attempt is made in this thesis.

In this thesis, a three-phase, 1 MVA, 3.3 kV, fifteen-level MLDCL based active rectifier is proposed with a comprehensive control scheme. In this scheme, the control objective are achieved by involving modified reduced carrier rotation PWM and proposed fault tolerant scheme with VOC or GARPC algorithms. The pre and post-fault performance of considered MLDCL based active rectifier for dynamic variation in load, change in set-point references and regeneration operation is demonstrated in MATLAB/Simulink environment for VOC and GARPC algorithms under various fault conditions. Further, the efficacy of the proposed scheme in balancing converter dc link voltages, even power distribution of dc sources, and fault tolerant ability is demonstrated on OPAL-RT 4500 real-time controller.

# TABLE OF CONTENTS

---

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| ACKNOWLEDGEMENT .....                                                  | ix        |

| ABSTRACT .....                                                         | i         |

| TABLE OF CONTENTS .....                                                | vii       |

| LIST OF FIGURES.....                                                   | xii       |

| LIST OF TABLES.....                                                    | xviii     |

| LIST OF ACRONYMS.....                                                  | xx        |

| LIST OF SYMBOLS.....                                                   | xxi       |

| <br>                                                                   |           |

| <b>CHAPTER 1: HIGH POWER DC-AC CONVERTERS .....</b>                    | <b>1</b>  |

| 1.1 <b>Introduction .....</b>                                          | <b>1</b>  |

| 1.2 <b>Inverters for high-power medium-voltage applications .....</b>  | <b>3</b>  |

| 1.2.1 Multipulse inverters .....                                       | 3         |

| 1.2.2 Multilevel inverters (MLIs) .....                                | 4         |

| 1.3 <b>Classical topologies of MLIs .....</b>                          | <b>6</b>  |

| 1.3.1 Diode clamped multilevel inverter (DCMLI) .....                  | 6         |

| 1.3.2 Flying capacitor multilevel inverter (FCMLI) .....               | 8         |

| 1.3.3 Cascaded H-bridge multilevel inverter (CHB MLI) .....            | 9         |

| 1.4 <b>Other MLI topologies.....</b>                                   | <b>11</b> |

| 1.5 <b>Limitations of MLIs and significance of RSC-MLIs.....</b>       | <b>11</b> |

| 1.6 <b>Scope of the work and contributions .....</b>                   | <b>13</b> |

| 1.7 <b>Organization of thesis.....</b>                                 | <b>15</b> |

| <br>                                                                   |           |

| <b>CHAPTER 2: TOPOLOGIES OF RSC-MLI.....</b>                           | <b>17</b> |

| 2.1 <b>Introduction .....</b>                                          | <b>17</b> |

| 2.2 <b>Factors considered in proposing new RSC-MLI topology .....</b>  | <b>17</b> |

| 2.3 <b>Classification of RSC-MLI topologies .....</b>                  | <b>18</b> |

| 2.3.1 Based on the physical structure or topological arrangement ..... | 18        |

| 2.3.2 Based on operation and performance .....                         | 20        |

| 2.4 <b>Topologies of RSC-MLIs .....</b>                                | <b>23</b> |

| 2.4.1 Multilevel dc-link (MLDCL) RSC-MLI.....                          | 24        |

| 2.4.2 Switched series parallel sources (SSPS) RSC-MLI.....             | 25        |

| 2.4.3 Reverse voltage (RV) RSC-MLI.....                                | 27        |

| 2.4.4 Series connected switched sources (SCSS) RSC-MLI .....           | 28        |

| 2.4.5 T-type topologies .....                                          | 29        |

|            |                                                            |           |

|------------|------------------------------------------------------------|-----------|

| 2.4.5.1    | T-type RSC-MLI .....                                       | 29        |

| 2.4.5.2    | Half-leg T-type RSC-MLI .....                              | 30        |

| 2.4.5.3    | Cascaded T-type RSC-MLI .....                              | 32        |

| 2.4.6      | Multilevel module (MLM) based RSC-MLI .....                | 33        |

| 2.4.7      | Hybrid T-type RSC-MLI .....                                | 34        |

| 2.4.7.1    | Topology – I .....                                         | 35        |

| 2.4.7.2    | Topology – II .....                                        | 38        |

| 2.4.8      | Cascaded bipolar switched cells (CBSC) based RSC-MLI ..... | 40        |

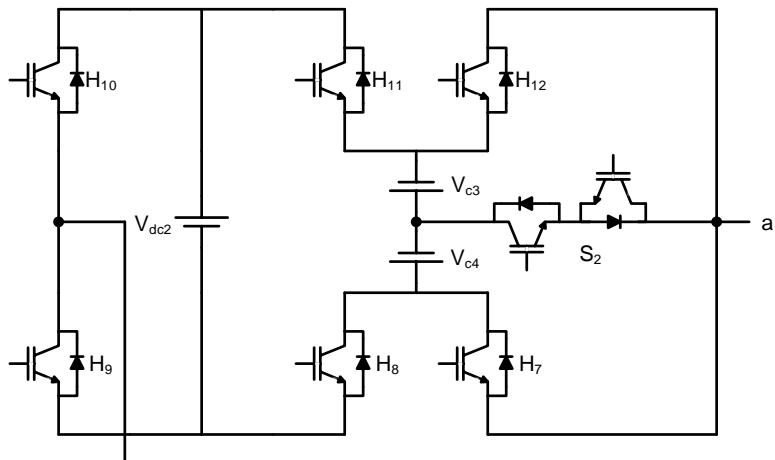

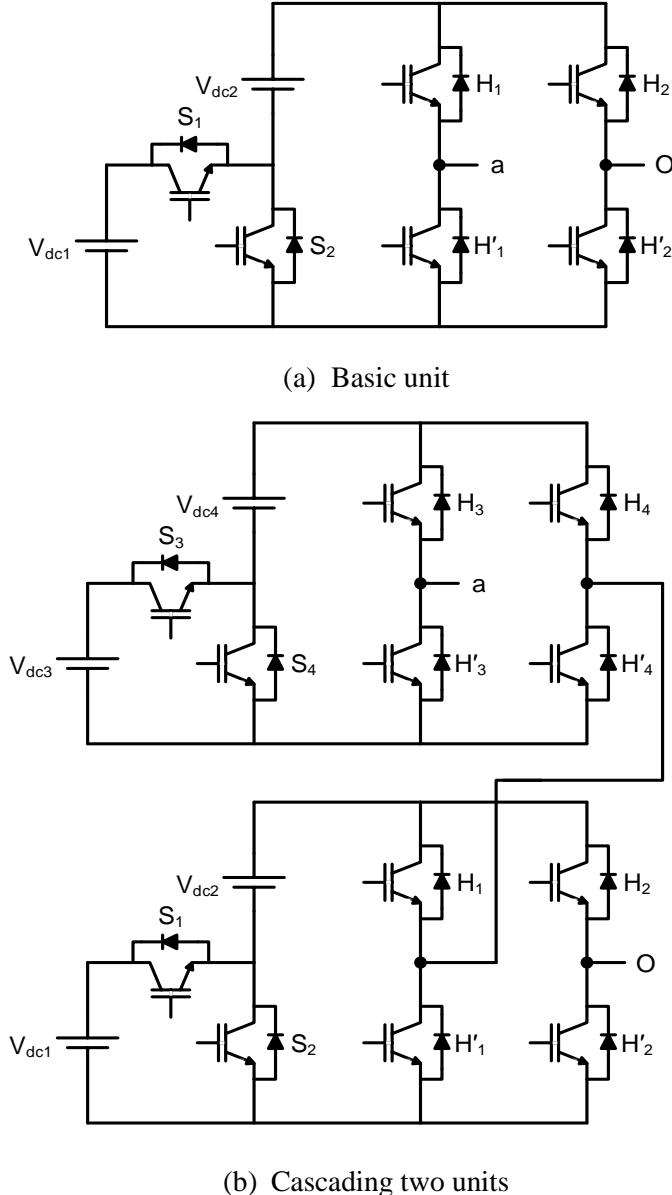

| 2.4.9      | Unit based RSC-MLIs .....                                  | 42        |

| 2.4.9.1    | Basic unit RSC-MLI .....                                   | 42        |

| 2.4.9.2    | Envelope type (E-type) RSC-MLI .....                       | 44        |

| 2.4.9.3    | Square T-type (ST-Type) RSC-MLI .....                      | 46        |

| 2.4.9.4    | Cascaded RSC-MLI: Topology – I .....                       | 48        |

| 2.4.9.5    | Cascaded RSC-MLI: Topology – II .....                      | 49        |

| 2.4.9.6    | Cascaded RSC-MLI with HSC .....                            | 51        |

| 2.4.10     | Switched capacitor topologies .....                        | 52        |

| 2.4.10.1   | Spilt capacitor unit RSC-MLI .....                         | 52        |

| 2.4.10.2   | Switched capacitor RSC-MLI .....                           | 53        |

| 2.4.11     | Nested topologies .....                                    | 55        |

| 2.4.12     | Packed U structures .....                                  | 57        |

| 2.4.12.1   | Switched dc-sources (SDS) RSC-MLI .....                    | 57        |

| 2.4.12.2   | Packed U-cell (PUC) RSC-MLI .....                          | 58        |

| 2.4.13     | Three-phase topologies .....                               | 60        |

| 2.4.13.1   | Topology – I .....                                         | 60        |

| 2.4.13.2   | Topology – II .....                                        | 61        |

| <b>2.5</b> | <b>Comparison of RSC-MLI topologies.....</b>               | <b>64</b> |

| <b>2.6</b> | <b>Summary.....</b>                                        | <b>74</b> |

|                                                            |           |

|------------------------------------------------------------|-----------|

| <b>CHAPTER 3: PWM SCHEMES OF RSC-MLI .....</b>             | <b>75</b> |

| <b>3.1 Introduction.....</b>                               | <b>75</b> |

| <b>3.2 Conventional modulation schemes of RSC-MLI.....</b> | <b>76</b> |

| 3.2.1 Multi reference modulation scheme .....              | 77        |

| 3.2.1.1 Performance evaluation .....                       | 79        |

| 3.2.1.2 Comparative analysis.....                          | 80        |

| 3.2.1.3 Reasons for degraded THD performance .....         | 81        |

|                                                   |                                                                          |            |

|---------------------------------------------------|--------------------------------------------------------------------------|------------|

| 3.2.1.4                                           | Experimental validation .....                                            | 83         |

| 3.2.2                                             | Reduced carrier PWM.....                                                 | 86         |

| 3.2.3                                             | Hybrid switching function PWM .....                                      | 88         |

| <b>3.3</b>                                        | <b>Summary of conventional PWM schemes for RSC-MLIs .....</b>            | <b>89</b>  |

| <b>3.4</b>                                        | <b>Modified PWM schemes for RSC-MLIs .....</b>                           | <b>91</b>  |

| 3.4.1                                             | Modified multi reference dual carrier PWM.....                           | 91         |

| 3.4.1.1                                           | Performance evaluation.....                                              | 92         |

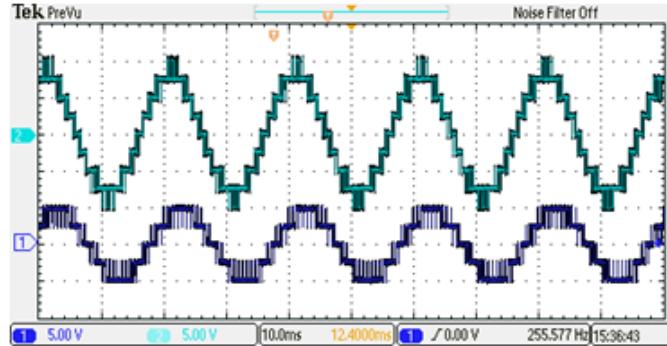

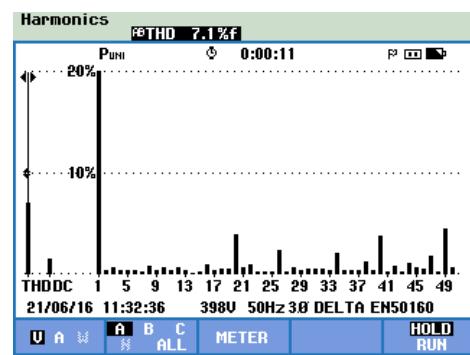

| 3.4.1.2                                           | Experimental validation .....                                            | 94         |

| 3.4.2                                             | Modified reduced carrier PWM .....                                       | 96         |

| 3.4.2.1                                           | Performance evaluation.....                                              | 98         |

| 3.4.2.2                                           | Experimental validation .....                                            | 99         |

| 3.4.3                                             | Comparative performance of the proposed PWM schemes .....                | 100        |

| 3.4.4                                             | Merits and limitations of the modified PWM schemes.....                  | 101        |

| <b>3.5</b>                                        | <b>Proposed reduced carrier PWM with unified logical expression.....</b> | <b>101</b> |

| 3.5.1                                             | Methodology: Proposed unified logical expression.....                    | 103        |

| 3.5.2                                             | Implementation to RSC-MLIs .....                                         | 106        |

| 3.5.3                                             | Performance evaluation.....                                              | 110        |

| 3.5.4                                             | Experimental validation .....                                            | 114        |

| 3.5.5                                             | Comparison with state-of-the-art of PWM schemes .....                    | 120        |

| <b>3.6</b>                                        | <b>Summary .....</b>                                                     | <b>122</b> |

| <b>CHAPTER 4: FTO OF MLDCL BASED RSC-MLI.....</b> |                                                                          | <b>123</b> |

| <b>4.1</b>                                        | <b>Introduction .....</b>                                                | <b>123</b> |

| <b>4.2</b>                                        | <b>Fault analysis of MLDCL based RSC-MLI .....</b>                       | <b>123</b> |

| <b>4.3</b>                                        | <b>Fault tolerant methods for compensating OC faults .....</b>           | <b>126</b> |

| 4.3.1                                             | By-passing method.....                                                   | 127        |

| 4.3.2                                             | Increasing burden .....                                                  | 128        |

| 4.3.3                                             | Neutral shifting .....                                                   | 129        |

| 4.3.4                                             | NS with zero-sequence injection.....                                     | 131        |

| <b>4.4</b>                                        | <b>Proposed generalized NS zero-sequence injection FTS .....</b>         | <b>133</b> |

| 4.4.1                                             | Zero-sequence voltage injection for multiple faults .....                | 133        |

| 4.4.2                                             | Determination of zero-sequence voltage.....                              | 137        |

| 4.4.3                                             | Extraction of fault tolerant modulating signals .....                    | 139        |

| 4.4.4                                             | Limitations of the proposed FTS scheme .....                             | 140        |

| <b>4.5</b>                                        | <b>Performance evaluation on 15-level MLDCL inverter .....</b>           | <b>140</b> |

|                                                      |                                                                            |            |

|------------------------------------------------------|----------------------------------------------------------------------------|------------|

| 4.5.1                                                | <i>Case-1:</i> OC fault on one unit ( $x = 1, y = 0$ and $z = 0$ ).....    | 142        |

| 4.5.2                                                | <i>Case-2:</i> OC fault on two units ( $x = 1, y = 0$ and $z = 1$ ).....   | 146        |

| 4.5.3                                                | <i>Case-3:</i> OC fault on three units ( $x = 3, y = 0$ and $z = 0$ )..... | 149        |

| 4.5.4                                                | <i>Case-4:</i> OC fault on four units ( $x = 3, y = 0$ and $z = 1$ ) ..... | 153        |

| 4.5.5                                                | <i>Case-5:</i> OC fault on six units ( $x = 2, y = 3$ and, $z = 1$ ) ..... | 157        |

| <b>4.6</b>                                           | <b>Experimental validation on nine-level MLDCL inverter .....</b>          | <b>162</b> |

| 4.6.1                                                | <i>Case-1:</i> Failure of one unit ( $x = 1, y = 0$ and $z = 0$ ) .....    | 163        |

| 4.6.2                                                | <i>Case-2:</i> Failure of three units ( $x = 2, y = 1$ and $z = 0$ ) ..... | 165        |

| 4.6.3                                                | <i>Case-3:</i> Failure of four units ( $x = 2, y = 1$ and $z = 1$ ) .....  | 169        |

| <b>4.7</b>                                           | <b>Summary.....</b>                                                        | <b>174</b> |

| <b>CHAPTER 5: MLDCL BASED ACTIVE RECTIFIER .....</b> |                                                                            | <b>175</b> |

| <b>5.1</b>                                           | <b>Introduction.....</b>                                                   | <b>175</b> |

| <b>5.2</b>                                           | <b>VSR based front-end converter .....</b>                                 | <b>176</b> |

| 5.2.1                                                | Control strategies.....                                                    | 177        |

| 5.2.1.1                                              | Voltage oriented control (VOC) .....                                       | 177        |

| 5.2.1.2                                              | Direct power control (DPC) .....                                           | 179        |

| 5.2.2                                                | Significance of RSC-MLC based VSR .....                                    | 180        |

| <b>5.3</b>                                           | <b>MLDCL converter based active rectifier .....</b>                        | <b>182</b> |

| 5.3.1                                                | Selection of dc link voltage .....                                         | 182        |

| 5.3.2                                                | Selection of coupling inductor.....                                        | 183        |

| 5.3.3                                                | Selection of dc link capacitor .....                                       | 184        |

| 5.3.4                                                | Comprehensive control algorithm .....                                      | 185        |

| 5.3.4.1                                              | Decoupled current controller .....                                         | 188        |

| 5.3.4.2                                              | Voltage balancing controller .....                                         | 189        |

| 5.3.4.3                                              | Fault tolerant control .....                                               | 191        |

| 5.3.5                                                | Relation between dc link voltage and load power.....                       | 191        |

| <b>5.4</b>                                           | <b>MLDCL based active rectifier for healthy condition .....</b>            | <b>192</b> |

| 5.4.1                                                | Response with VOC .....                                                    | 193        |

| 5.4.2                                                | Response with GARPC .....                                                  | 195        |

| 5.4.3                                                | Performance observations of VOC and GARPC.....                             | 197        |

| <b>5.5</b>                                           | <b>MLDCL based active rectifier for multiple OC switch faults. .....</b>   | <b>198</b> |

| 5.5.1                                                | Performance with VOC .....                                                 | 198        |

| 5.5.2                                                | Performance with GARPC .....                                               | 200        |

| <b>5.6</b>                                           | <b>Summary.....</b>                                                        | <b>202</b> |

|                                                     |            |

|-----------------------------------------------------|------------|

| <b>CHAPTER 6: CONCLUSION AND FUTURE SCOPE.....</b>  | <b>203</b> |

| <b>6.1 Conclusion .....</b>                         | <b>203</b> |

| <b>6.2 Future scope .....</b>                       | <b>204</b> |

| <b>APPENDIX A: EXPERIMENTAL SETUP.....</b>          | <b>206</b> |

| <b>APPENDIX B: PUBLICATIONS FROM THE WORK .....</b> | <b>212</b> |

| <b>BIBLIOGRAPHY.....</b>                            | <b>213</b> |

---

# LIST OF FIGURES

---

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| Fig. 1.1: Topologies of inverters.....                                                         | 1  |

| Fig. 1.2: Two-level high-power VSI.....                                                        | 2  |

| Fig. 1.3: Performance of two-level VSI.....                                                    | 3  |

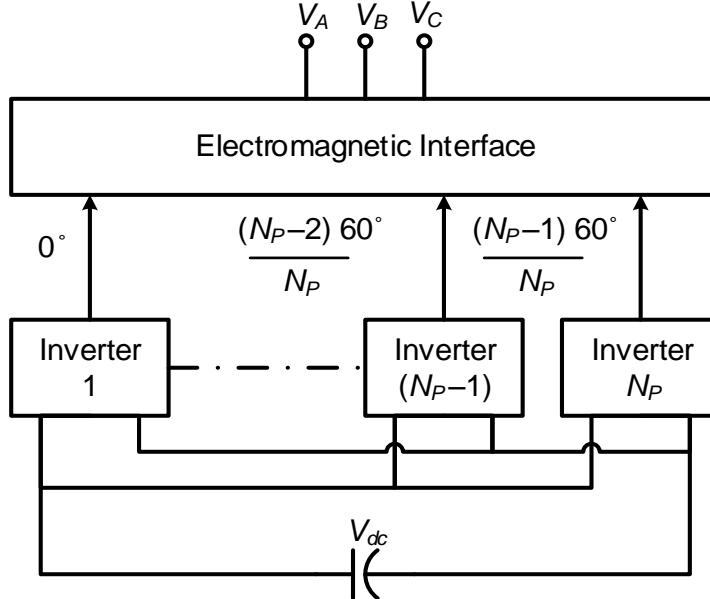

| Fig. 1.4: General structure of multipulse inverter.....                                        | 4  |

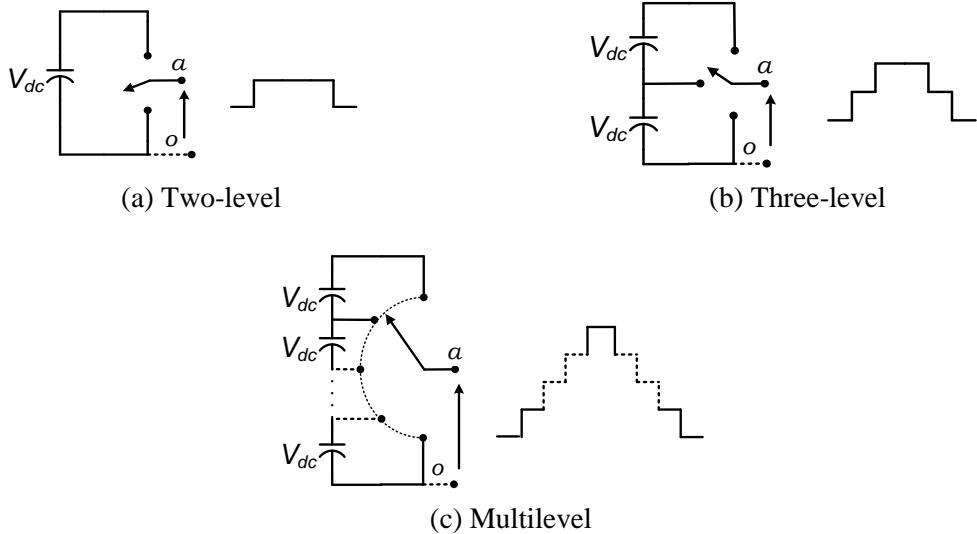

| Fig. 1.5: Multilevel voltage generation.....                                                   | 5  |

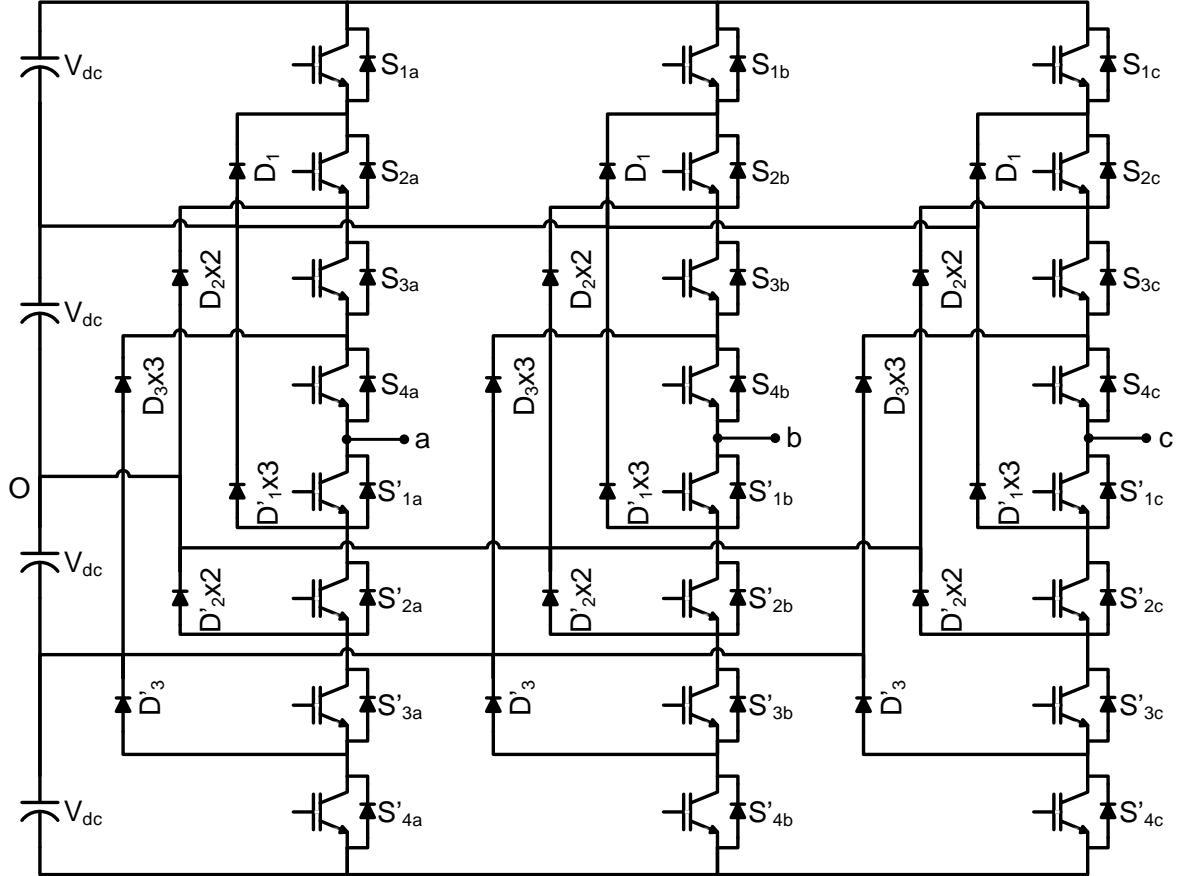

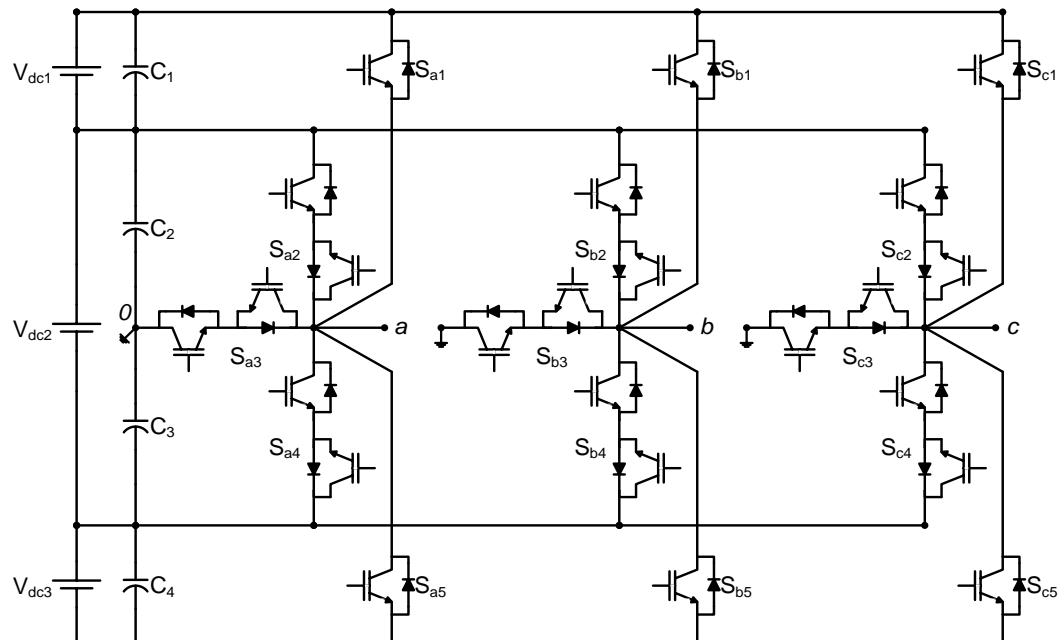

| Fig. 1.6: A three-phase five-level DCMLI.....                                                  | 7  |

| Fig. 1.7: A three-phase three-level active DCMLI .....                                         | 7  |

| Fig. 1.8: A three-phase five-level FCMLI .....                                                 | 8  |

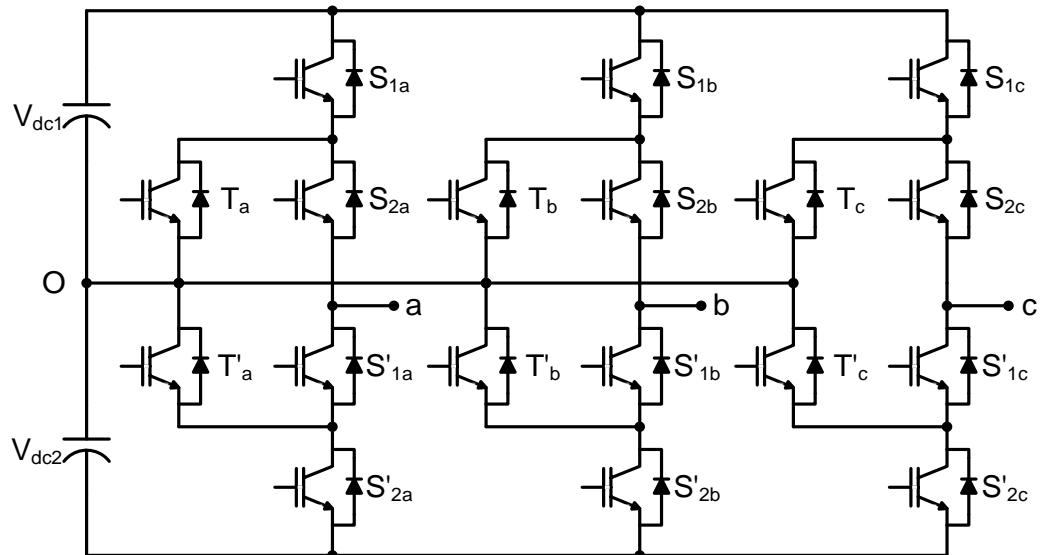

| Fig. 1.9: A three-phase five-level CHB MLI .....                                               | 10 |

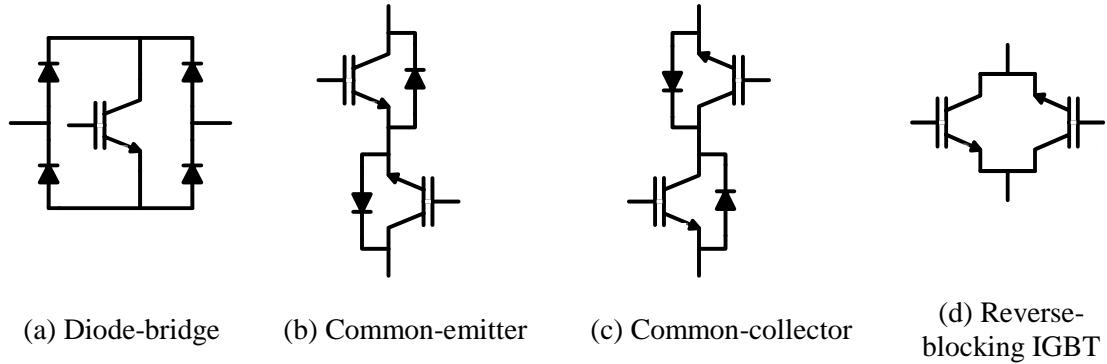

| Fig. 2.1: Possible arrangement of bi-directional switch.....                                   | 20 |

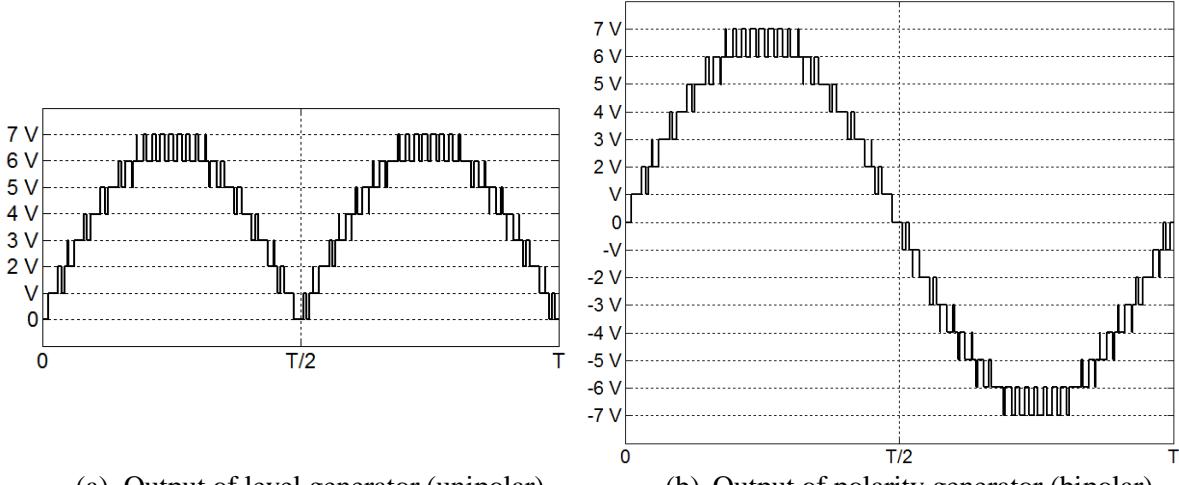

| Fig. 2.2: Output voltage of level and polarity generators. ....                                | 22 |

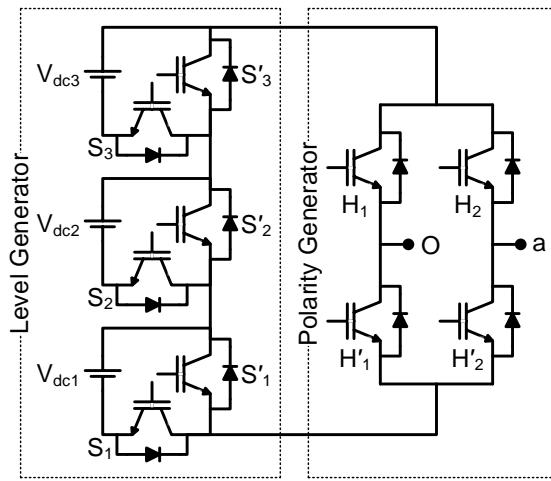

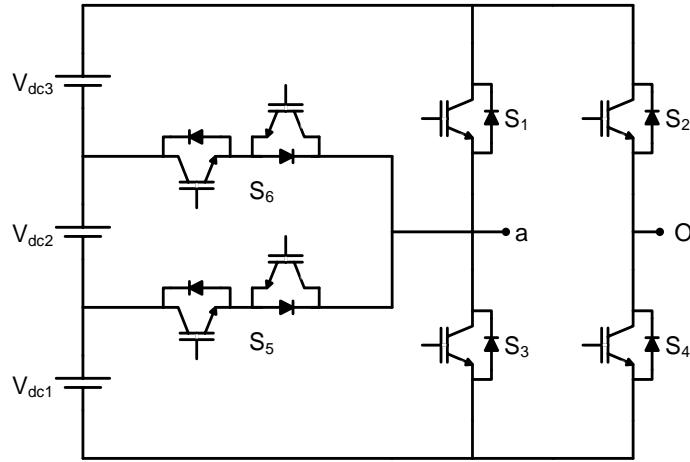

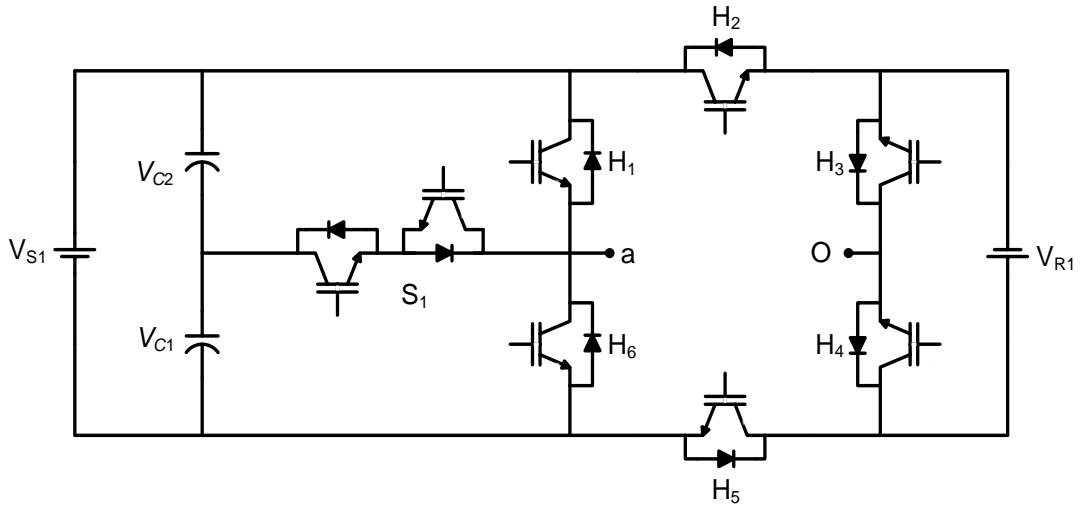

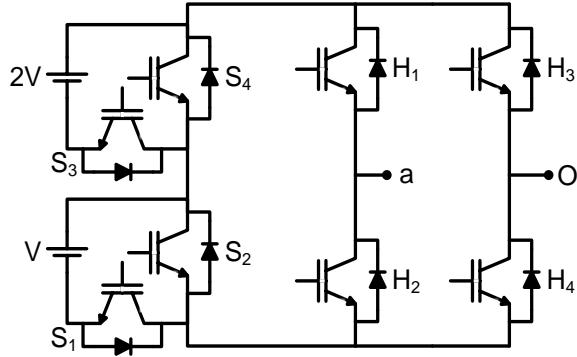

| Fig. 2.3: Multilevel dc link (MLDCL) RSC-MLI with three dc sources.....                        | 24 |

| Fig. 2.4: Switched series parallel sources (SSPS) RSC-MLI with three dc sources.....           | 26 |

| Fig. 2.5: Reverse voltage (RV) RSC-MLI with three dc voltage sources. ....                     | 27 |

| Fig. 2.6: Series connected switched sources (SCSS) RSC-MLI with three dc voltage sources. .... | 28 |

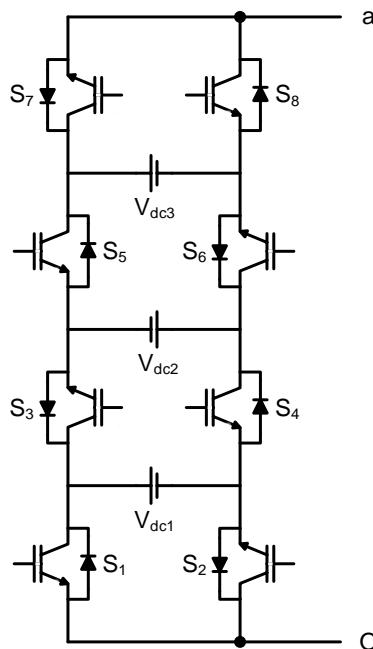

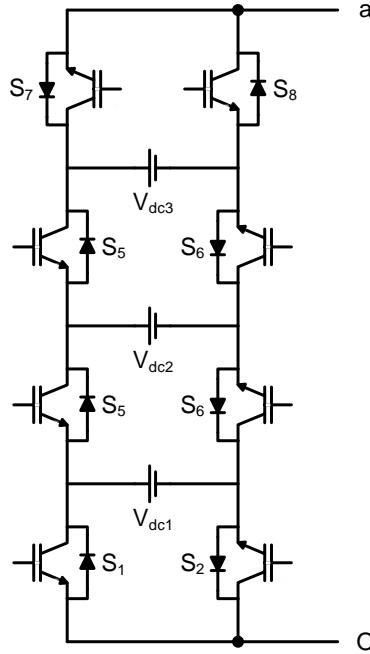

| Fig. 2.7: Seven-level T-type RSC-MLI. ....                                                     | 30 |

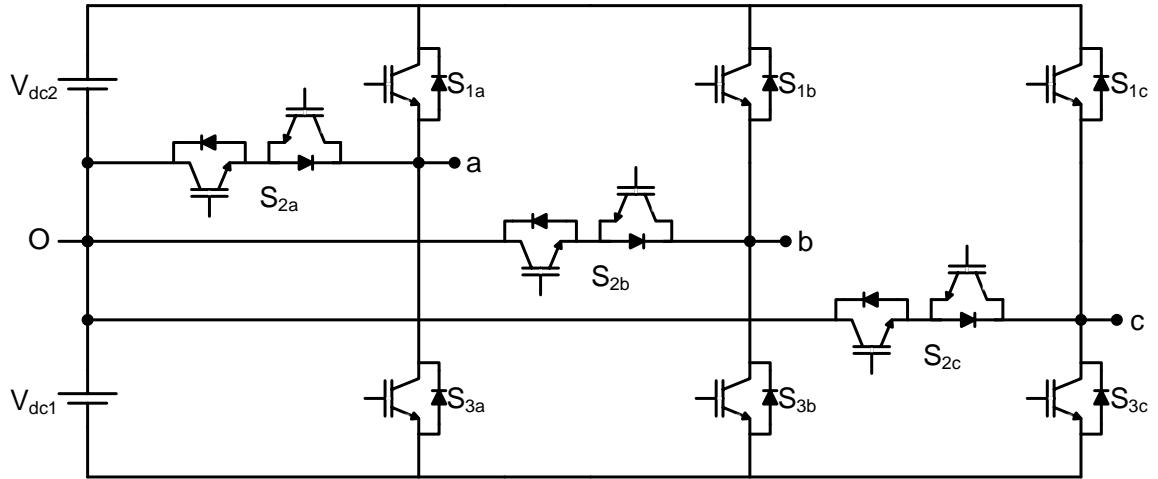

| Fig. 2.8: Three-phase half-leg three-level T-type RSC-MLI. ....                                | 31 |

| Fig. 2.9: Topological structure of cascaded T-type RSC-MLI. ....                               | 32 |

| Fig. 2.10: Multilevel module (MLM) based RSC-MLI topology with three dc sources.....           | 34 |

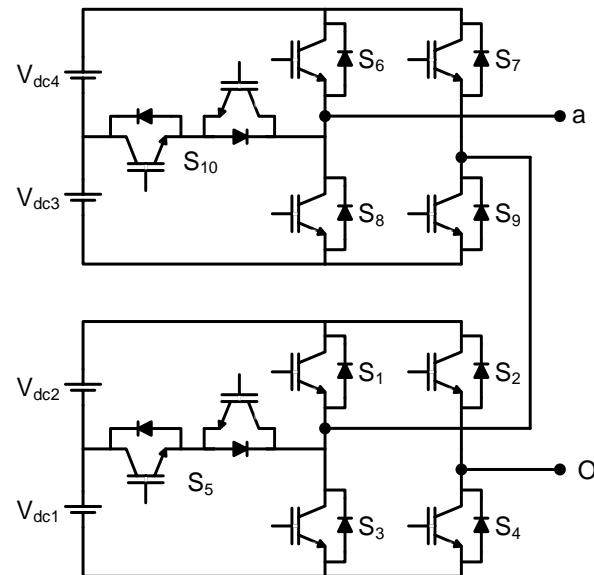

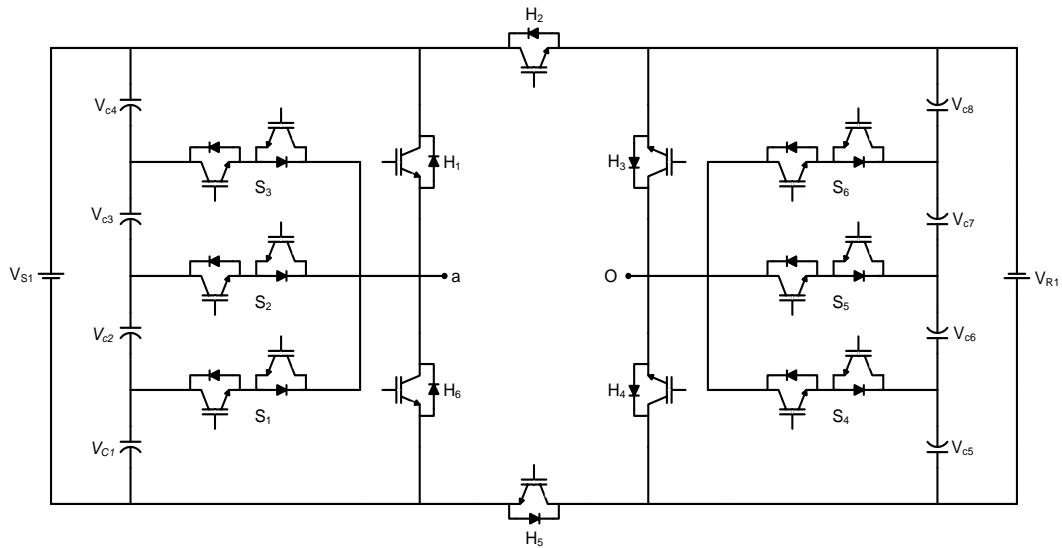

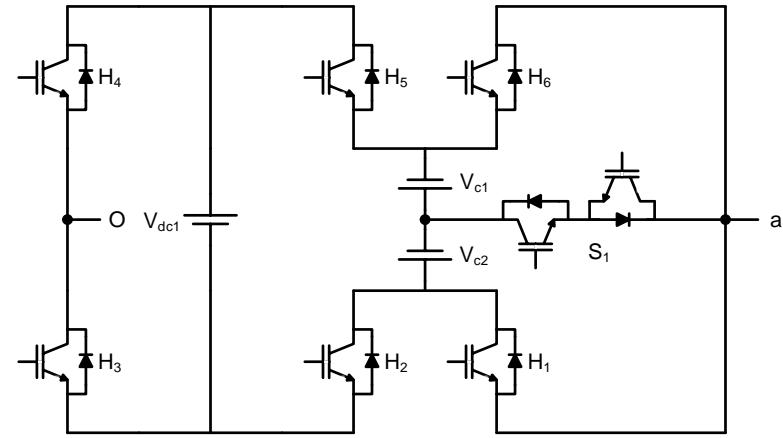

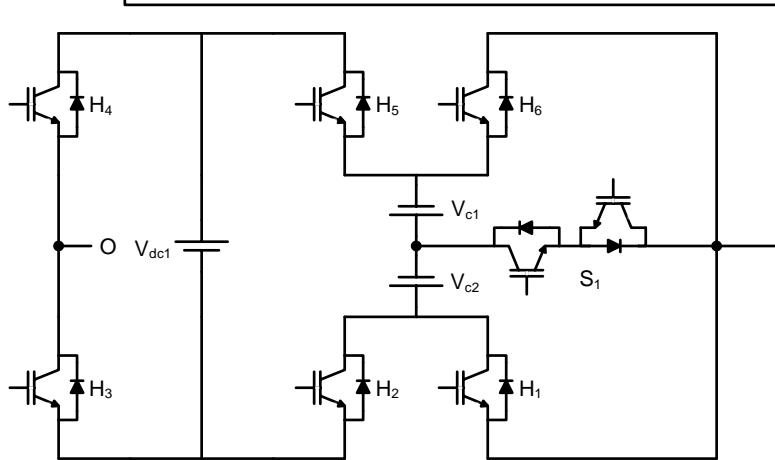

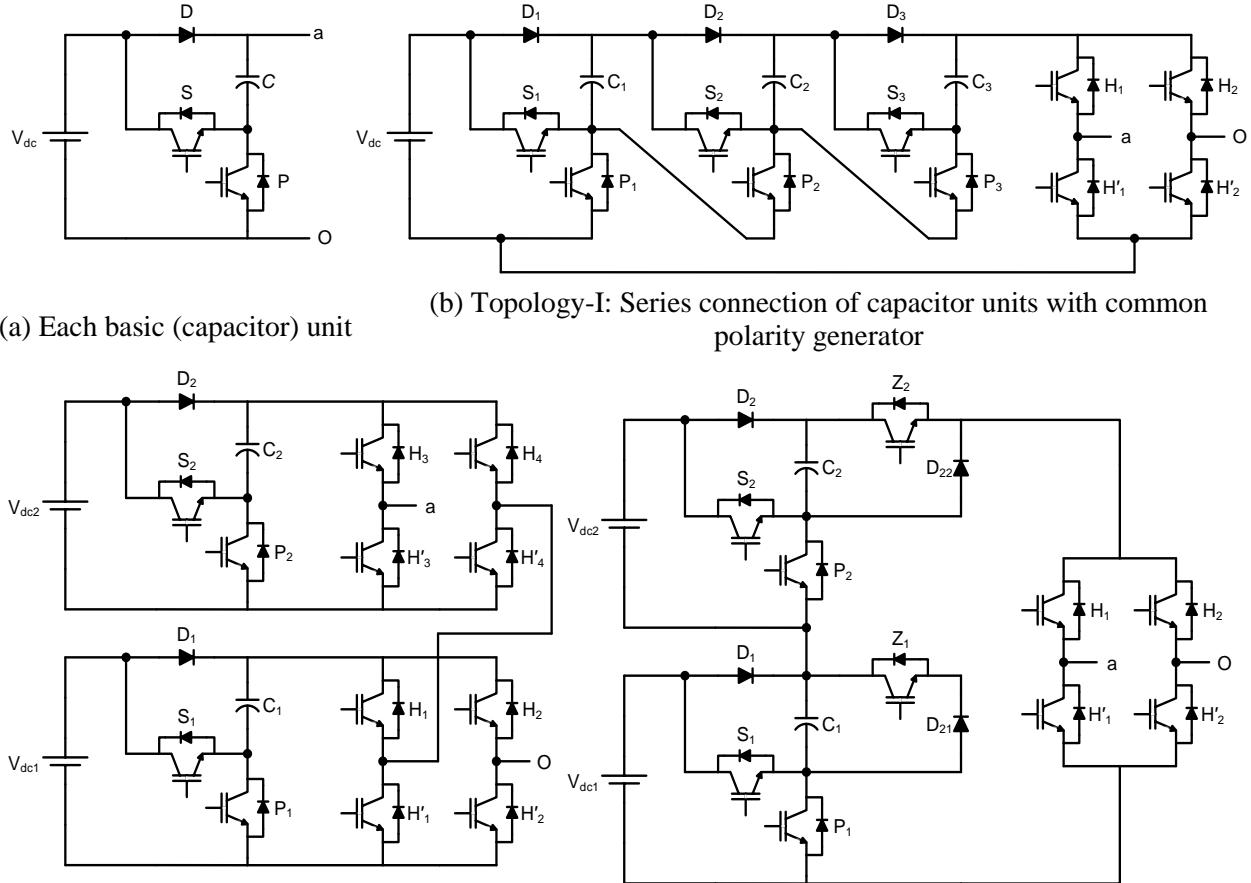

| Fig. 2.11: Hybrid T-type MLI topology – I. ....                                                | 35 |

| Fig. 2.12: Extension of hybrid T-type topology – I to higher levels. ....                      | 37 |

| Fig. 2.13: Hybrid T-type MLI topology – II. ....                                               | 39 |

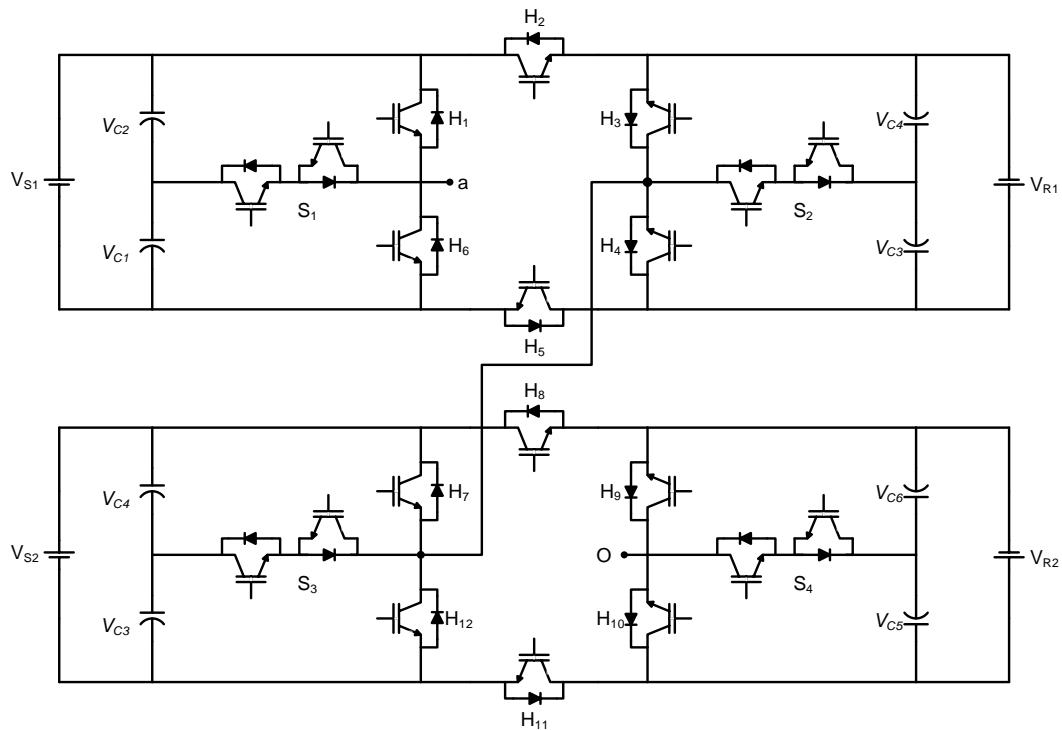

| Fig. 2.14: Cascaded bipolar switched cells (CBSC) RSC-MLI with three dc sources. ....          | 41 |

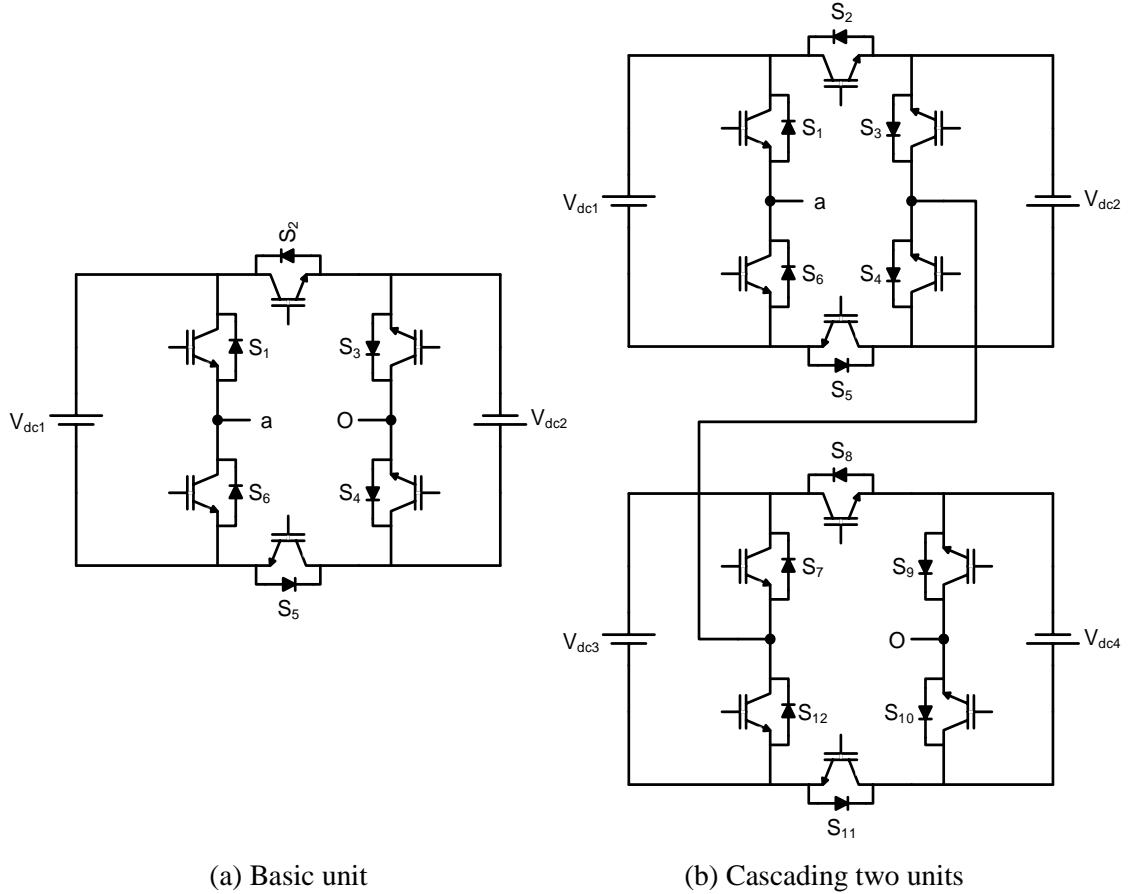

| Fig. 2.15: Topological structure of basic unit RSC-MLI. ....                                   | 43 |

| Fig. 2.16: Extension of basic unit RSC-MLI to higher levels.....                               | 44 |

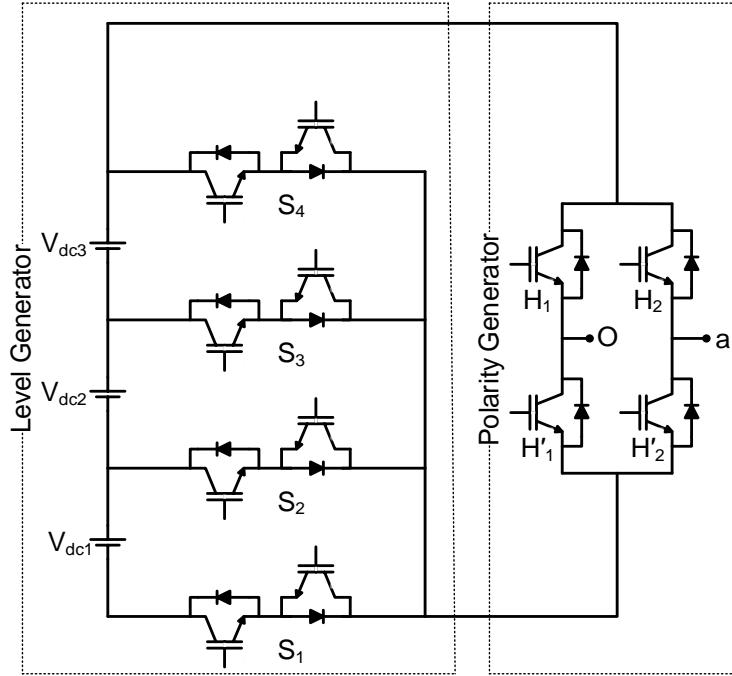

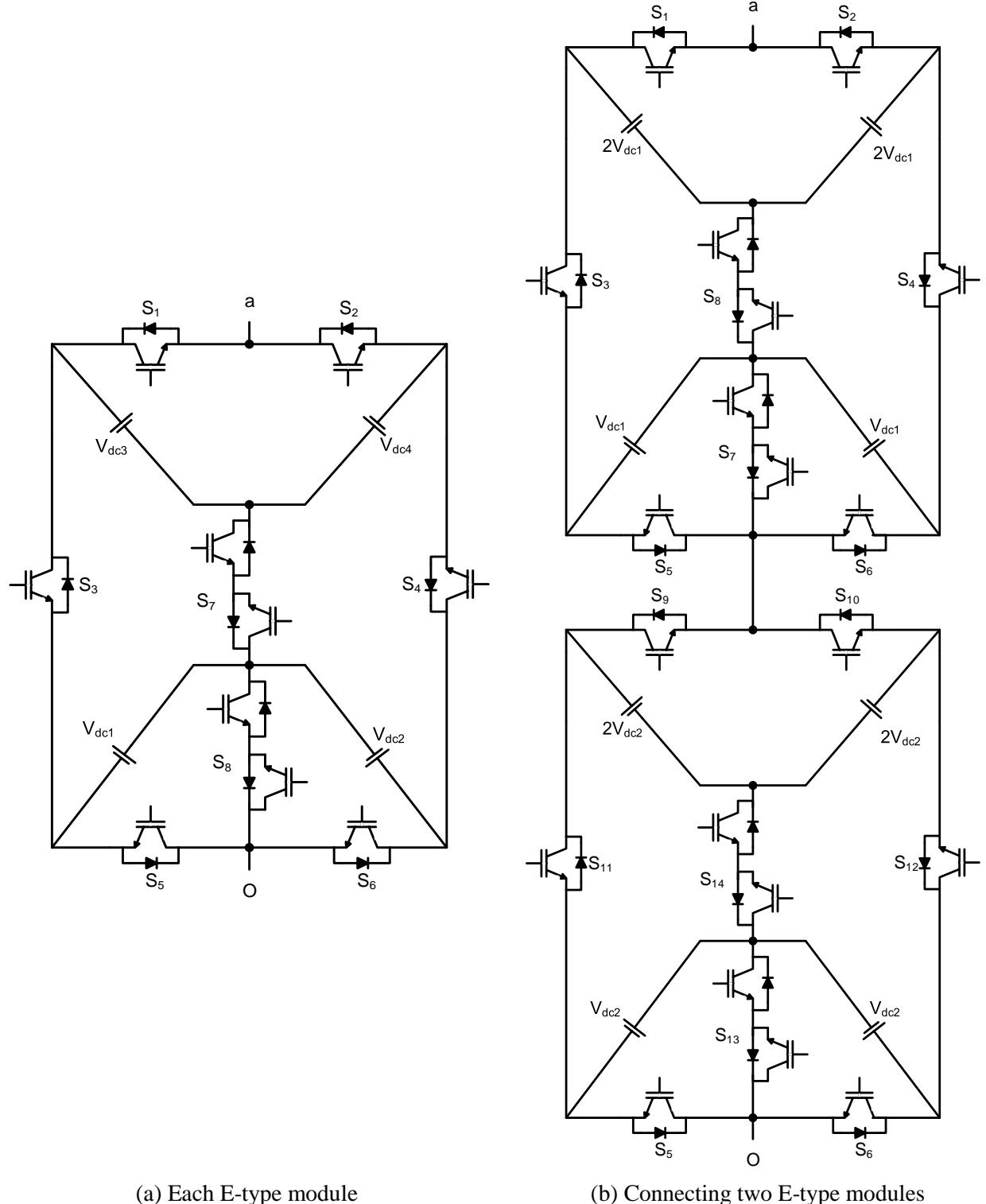

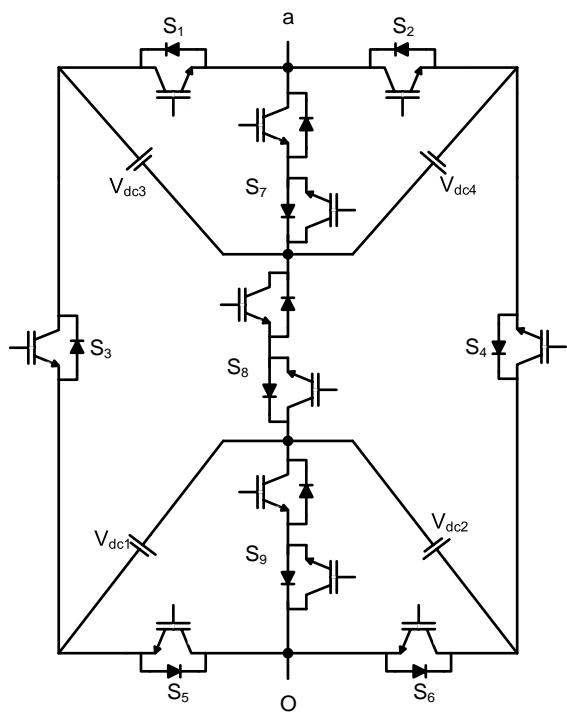

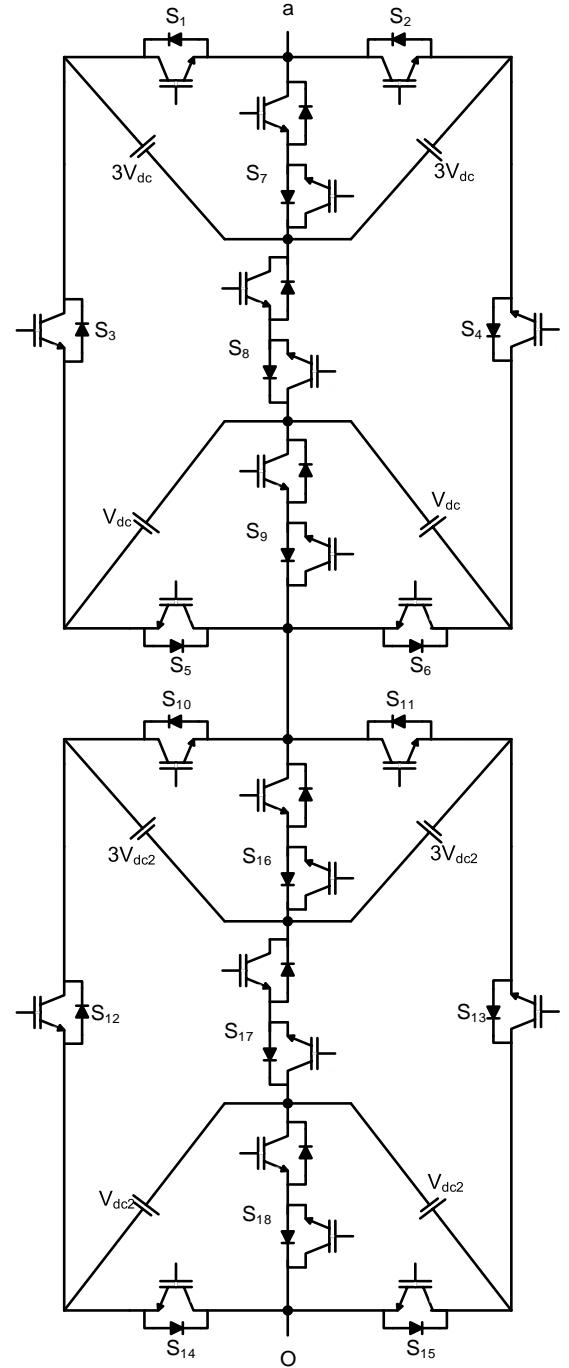

| Fig. 2.17: Topological configuration of E-type RSC-MLI. ....                                   | 45 |

| Fig. 2.18: Square T-type (ST-Type) RSC-MLI. ....                                               | 47 |

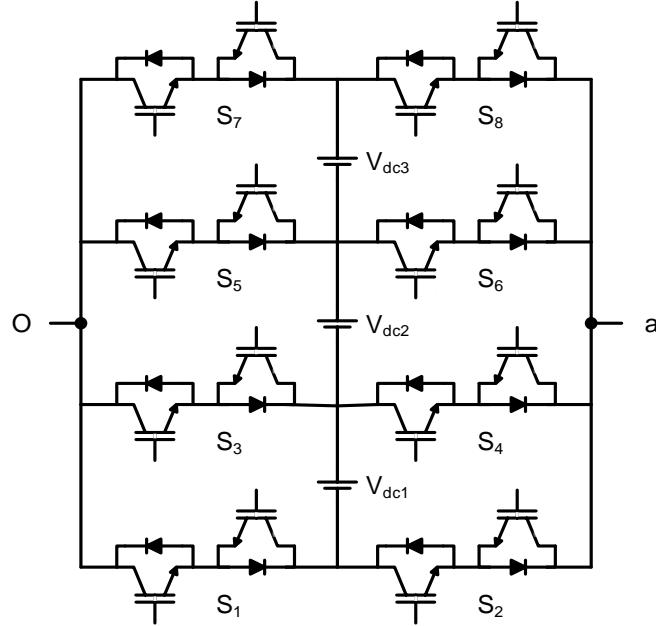

| Fig. 2.19: Cascaded RSC-MLI Topology – I.....                                                  | 49 |

| Fig. 2.20: Cascaded MLI Topology – II. ....                                                    | 50 |

| Fig. 2.21: Cascaded RSC-MLI with HSC based structure.....                                      | 51 |

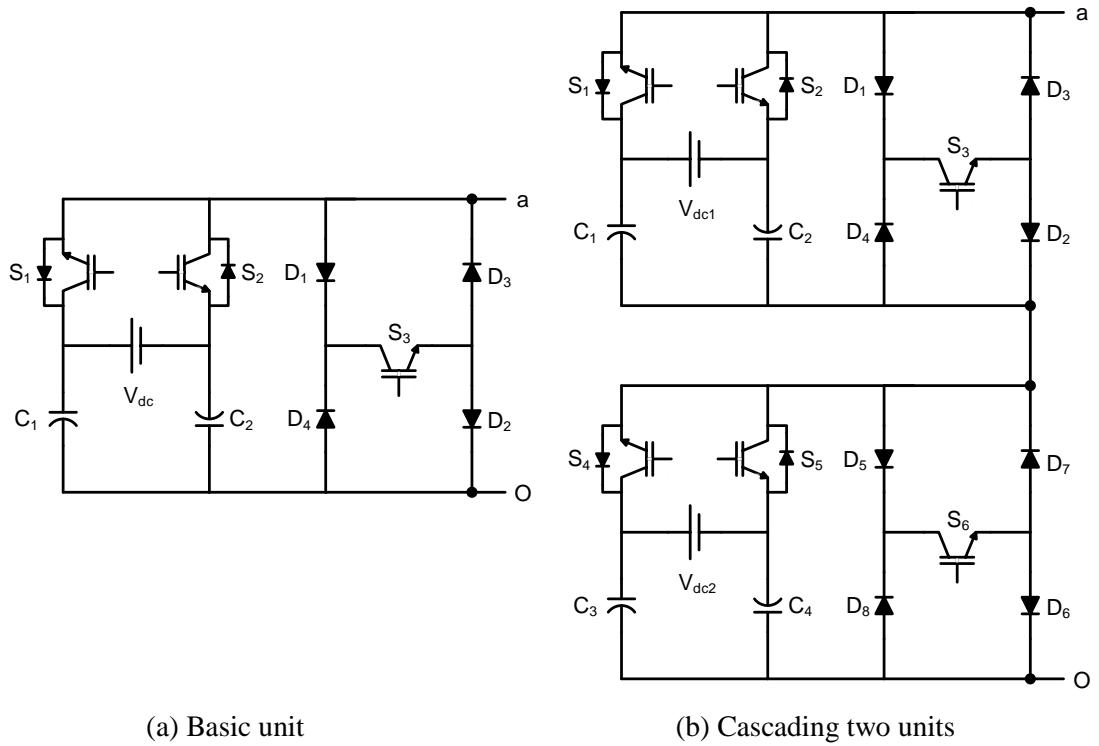

| Fig. 2.22: Split capacitor unit RSC-MLI.....                                                   | 53 |

| Fig. 2.23: Switched capacitor unit RSC-MLI. ....                                               | 54 |

|                                                                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.24: Nested RSC-MLI configurations .....                                                                                                           | 56 |

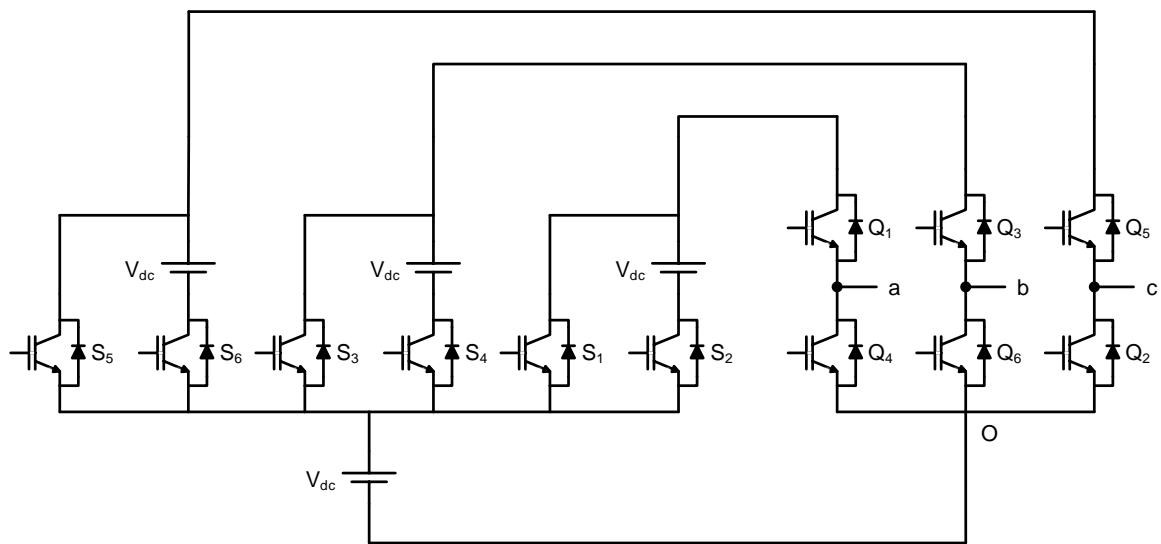

| Fig. 2.25: Switched dc sources (SDS) RSC-MLI with three dc sources. ....                                                                                 | 57 |

| Fig. 2.26: Topological structure of PUC RSC-MLI. ....                                                                                                    | 59 |

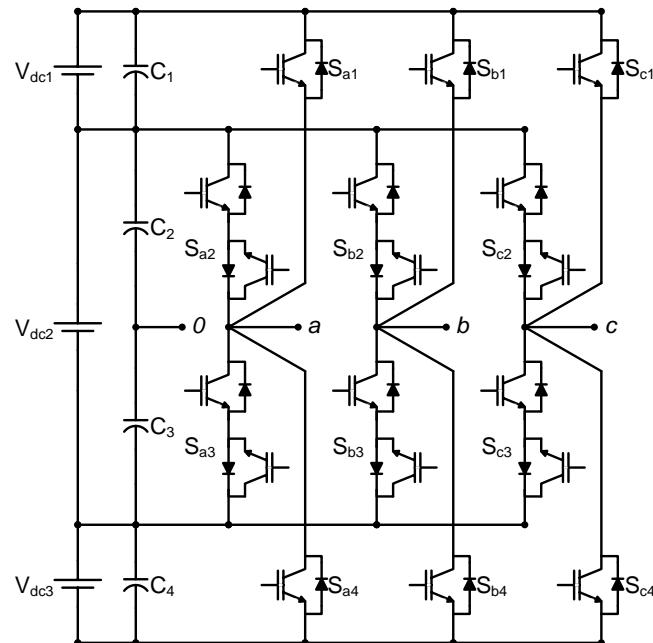

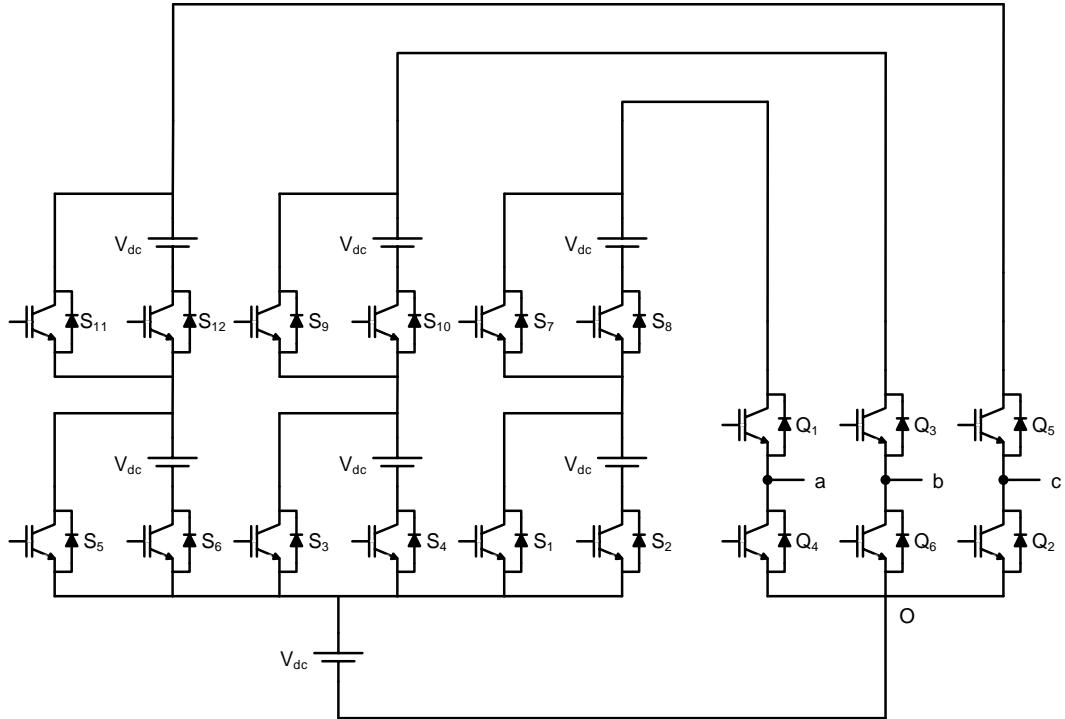

| Fig. 2.27: Five-level three-phase RSC-MLI Topology – I. ....                                                                                             | 60 |

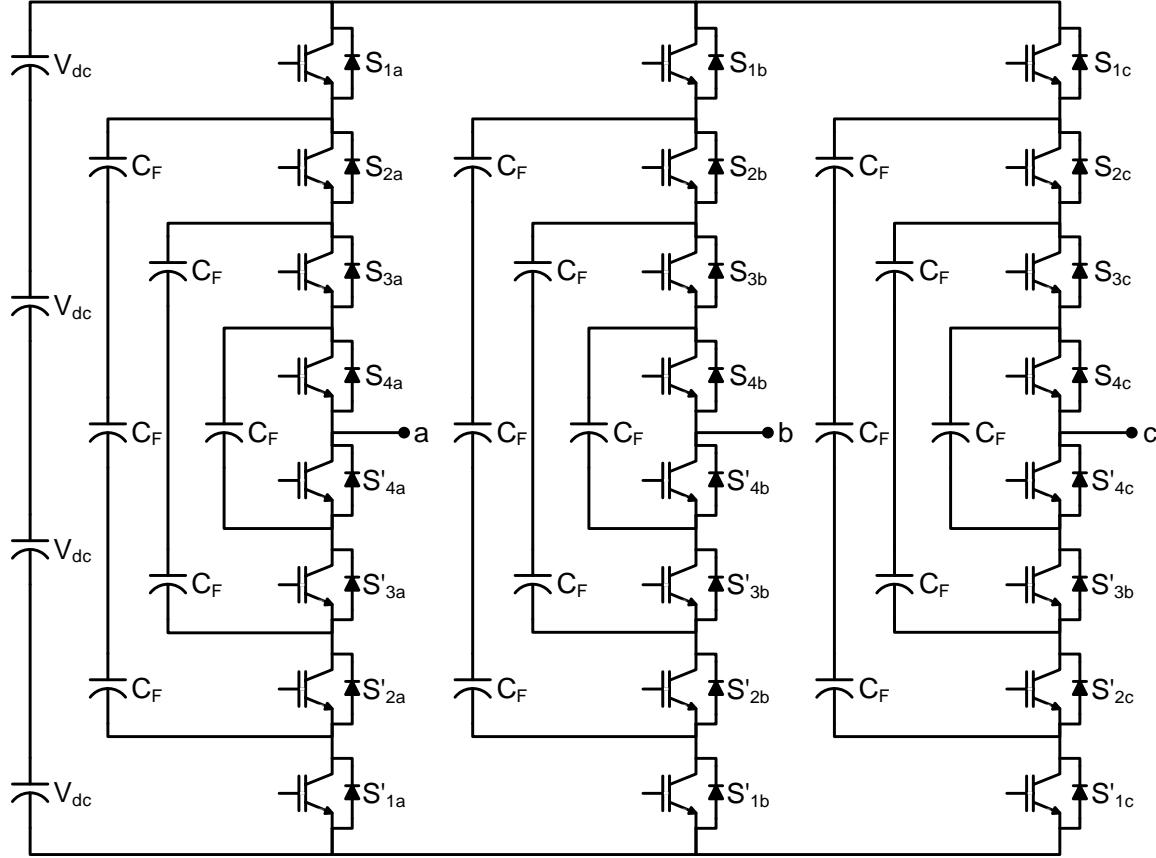

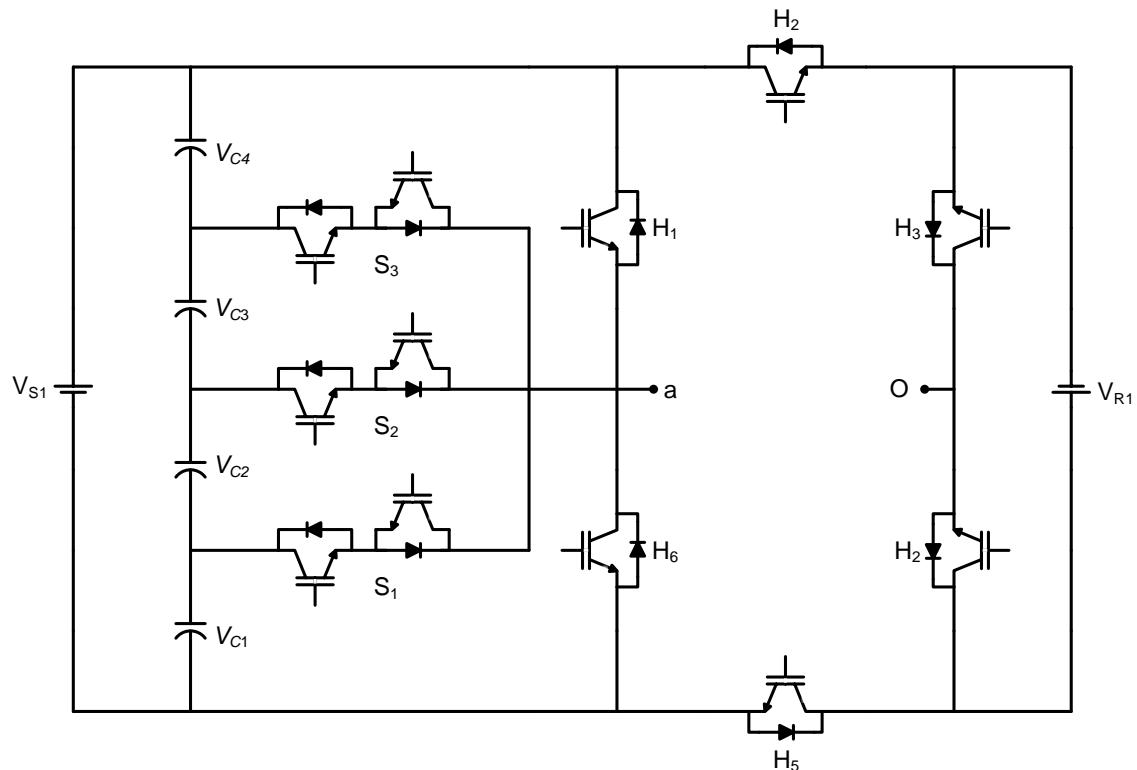

| Fig. 2.28: Seven-level three-phase RSC-MLI Topology – I. ....                                                                                            | 61 |

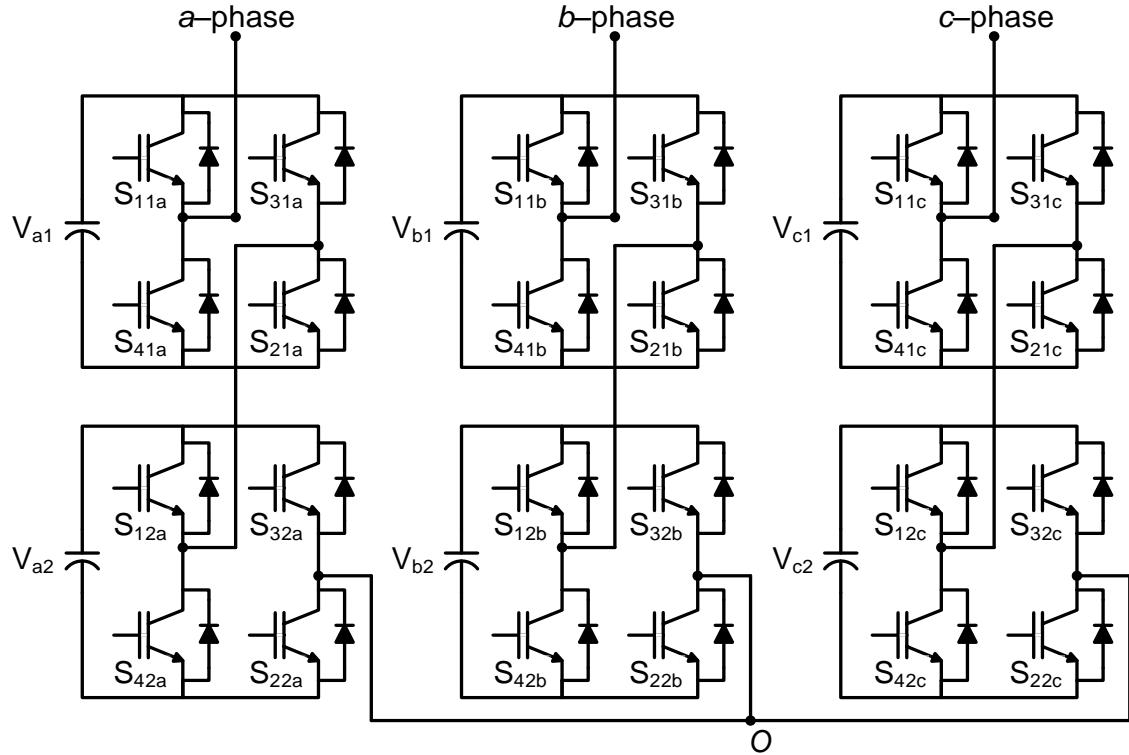

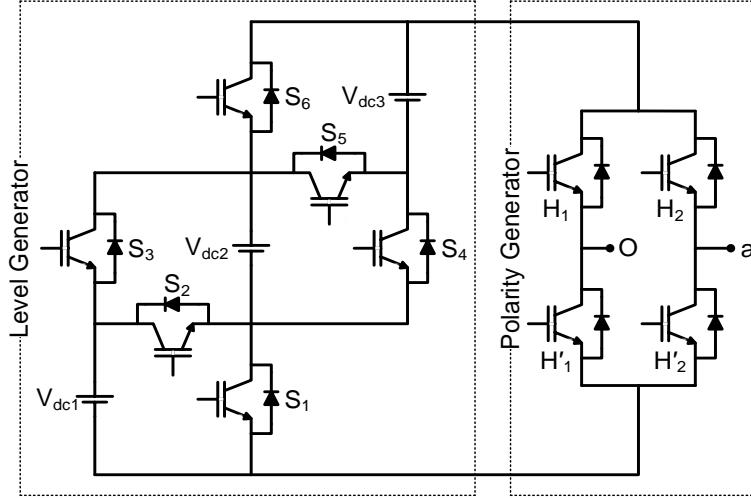

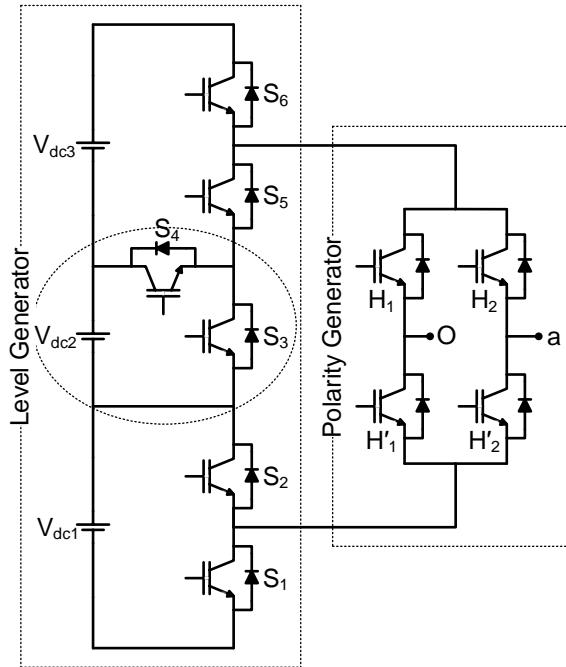

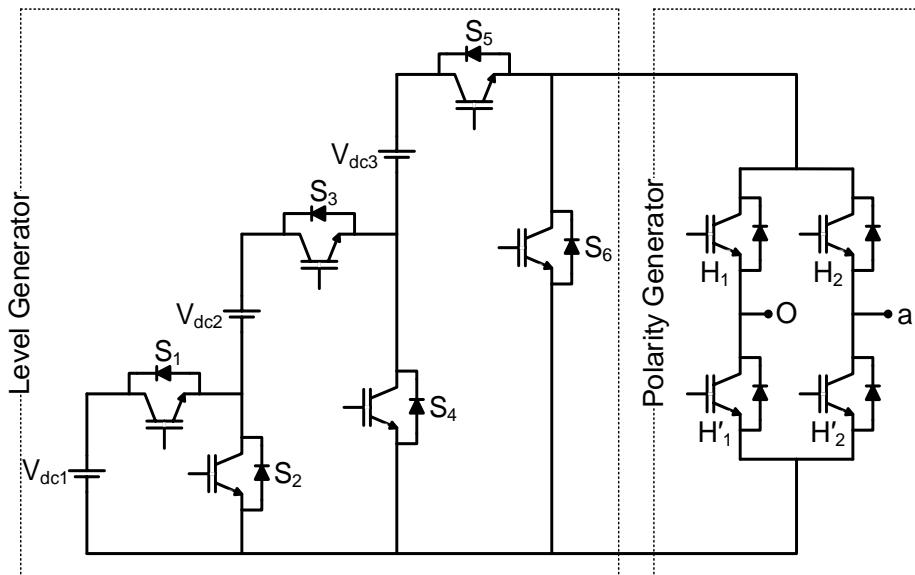

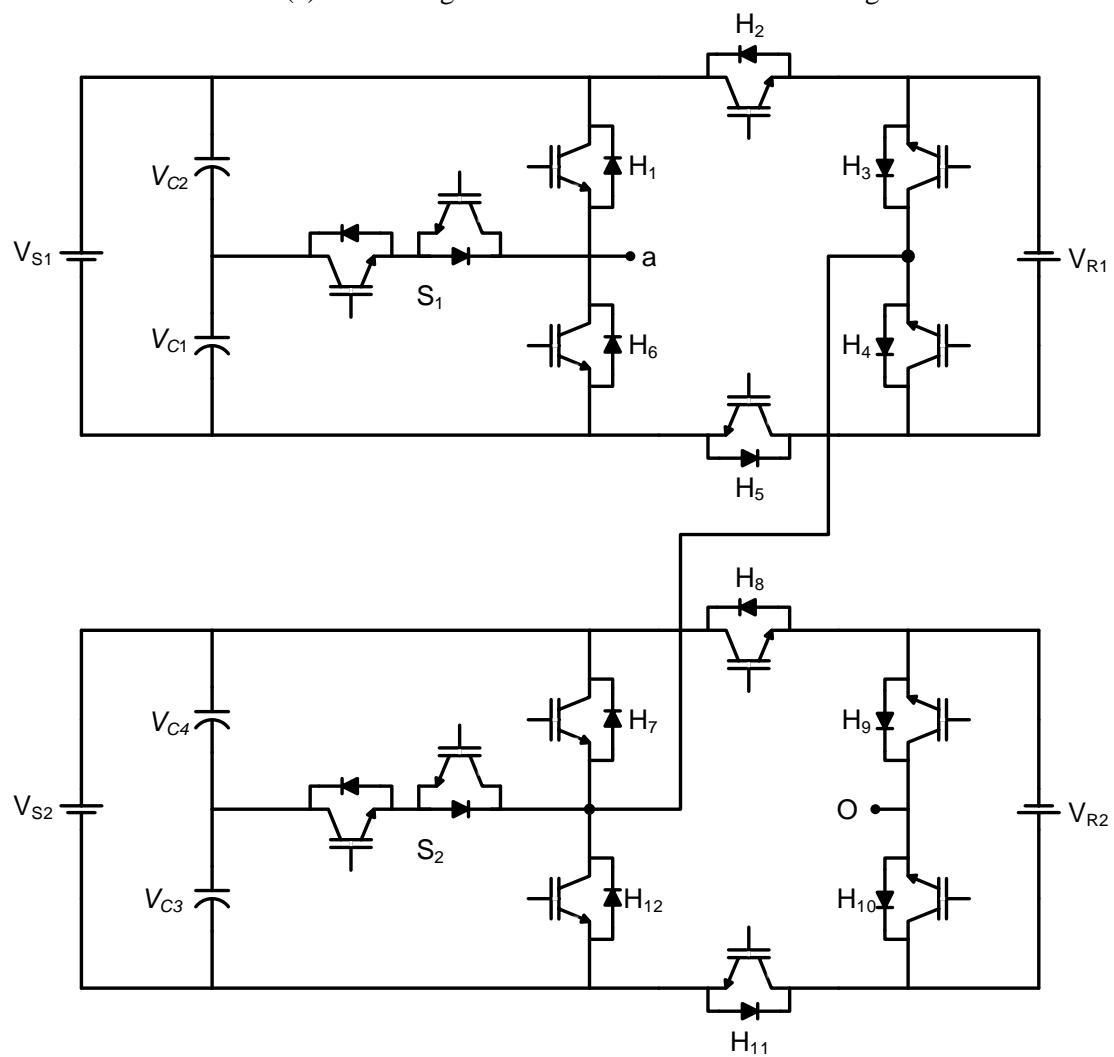

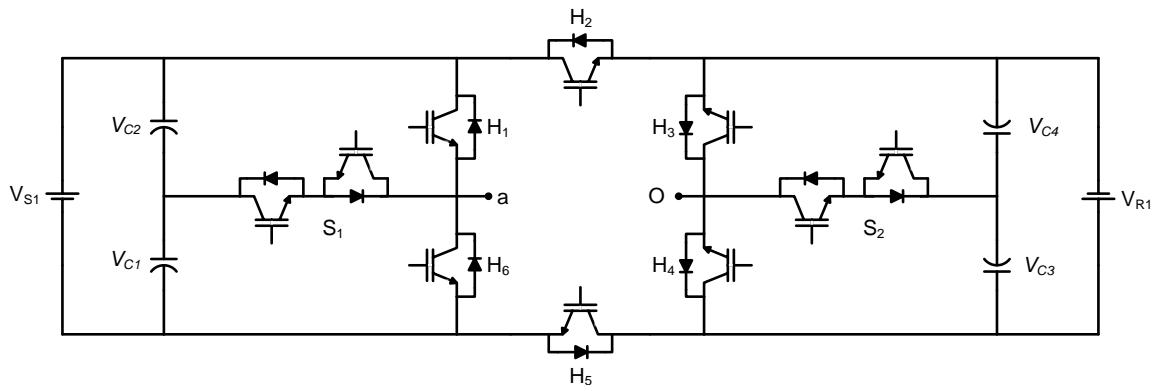

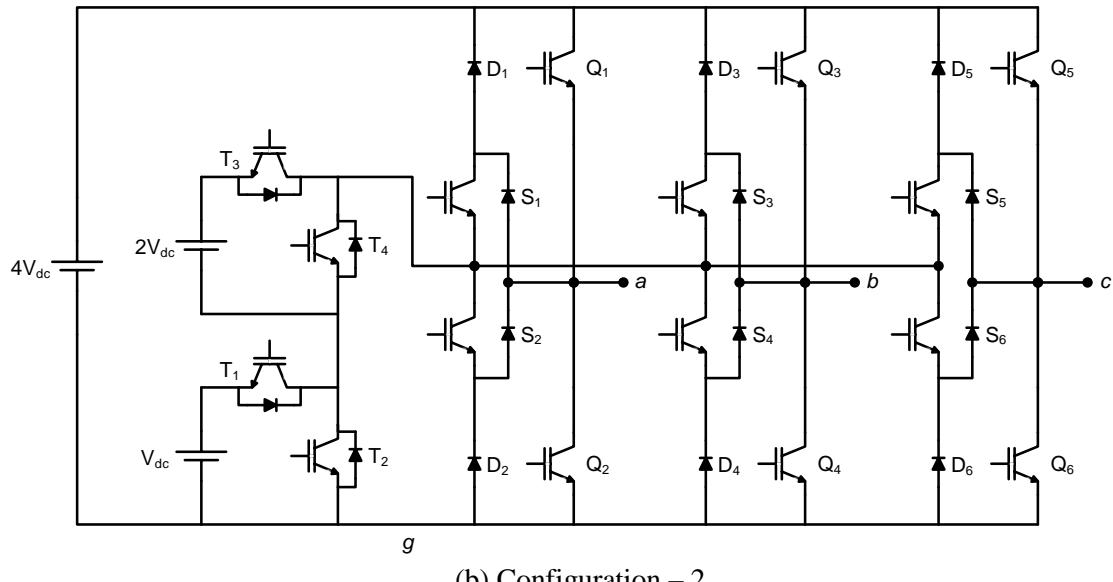

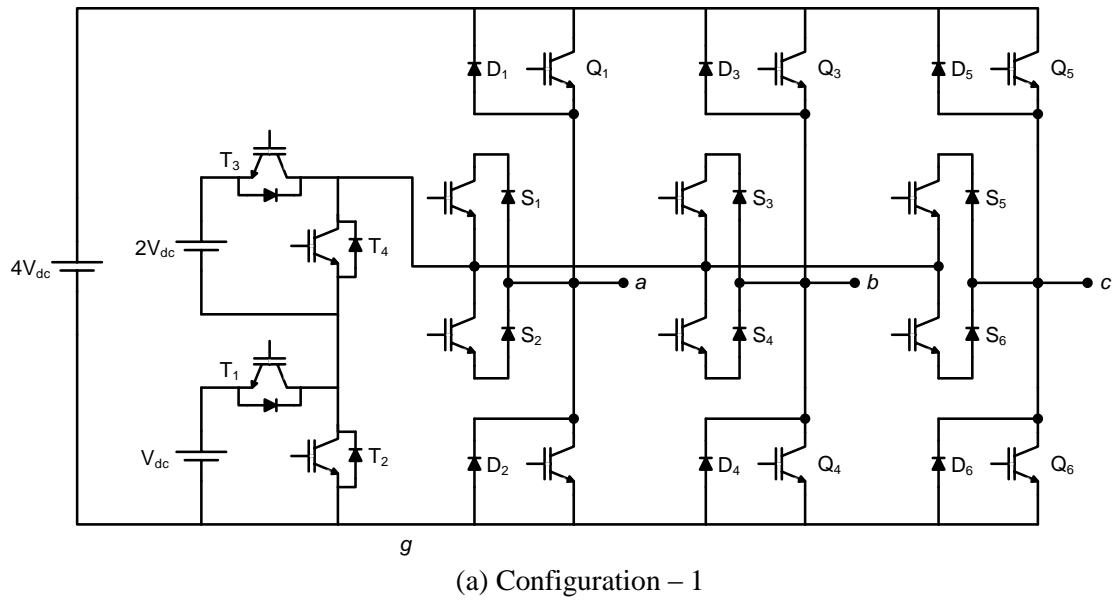

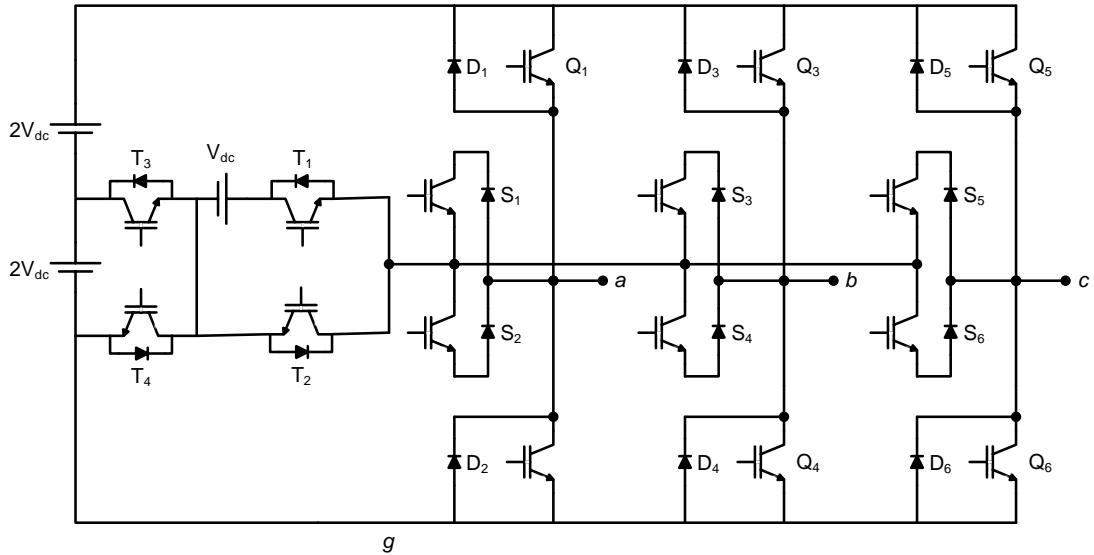

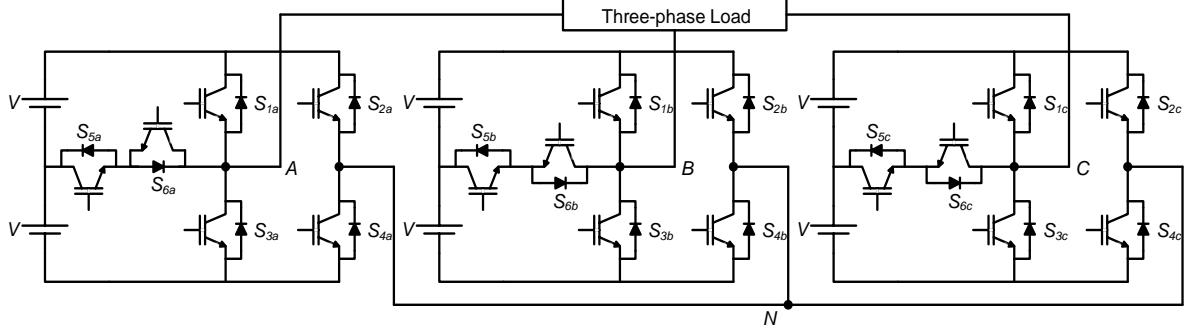

| Fig. 2.29: Three-phase asymmetrical five-level RSC-MLI configurations of Topology – II. .                                                                | 62 |

| Fig. 2.30: Three-phase asymmetrical five-level RSC-MLI configurations of Topology – II. (Contd.)                                                         | 63 |

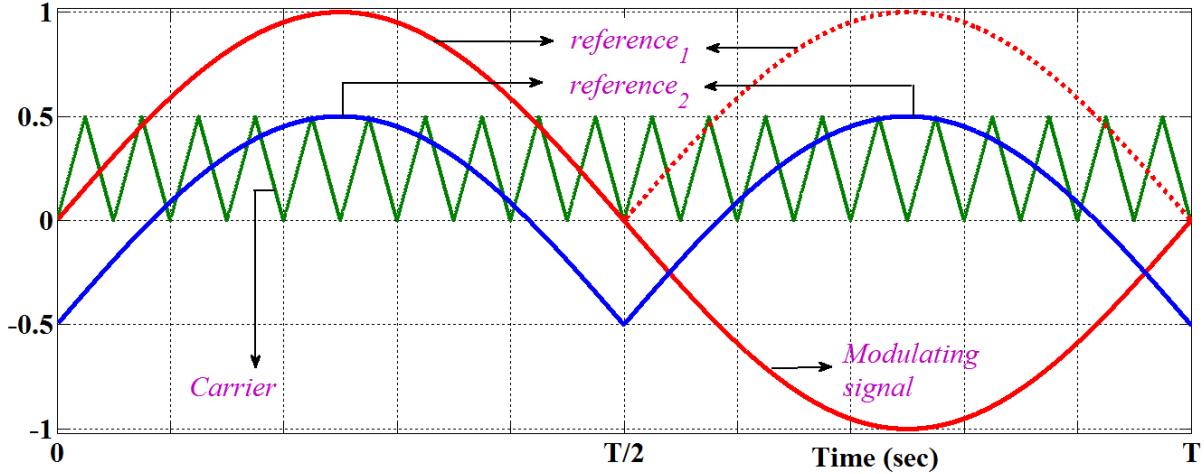

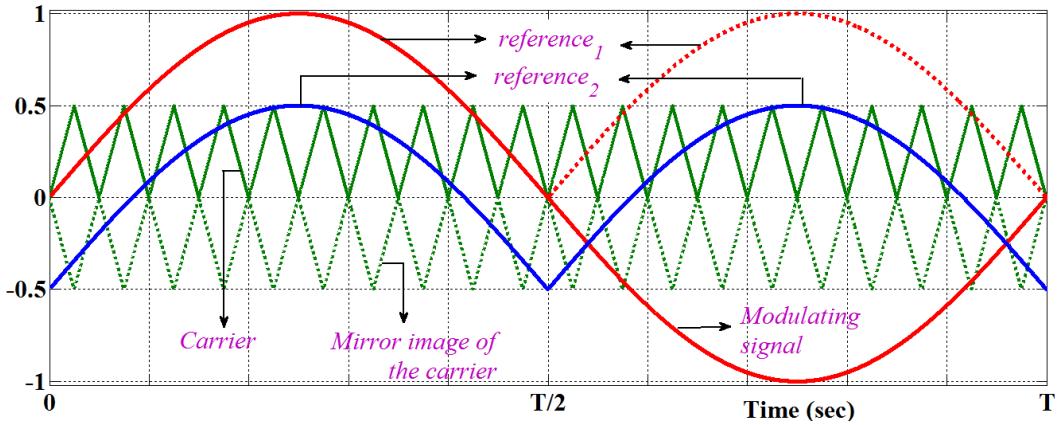

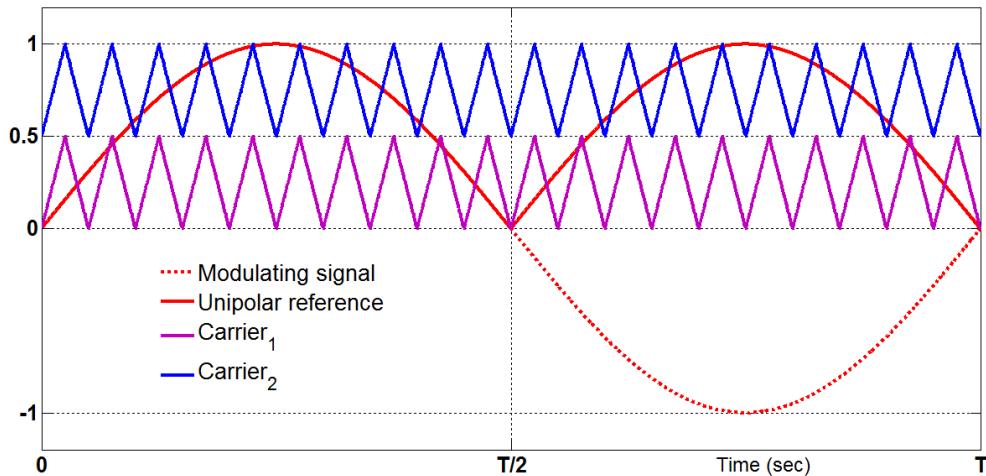

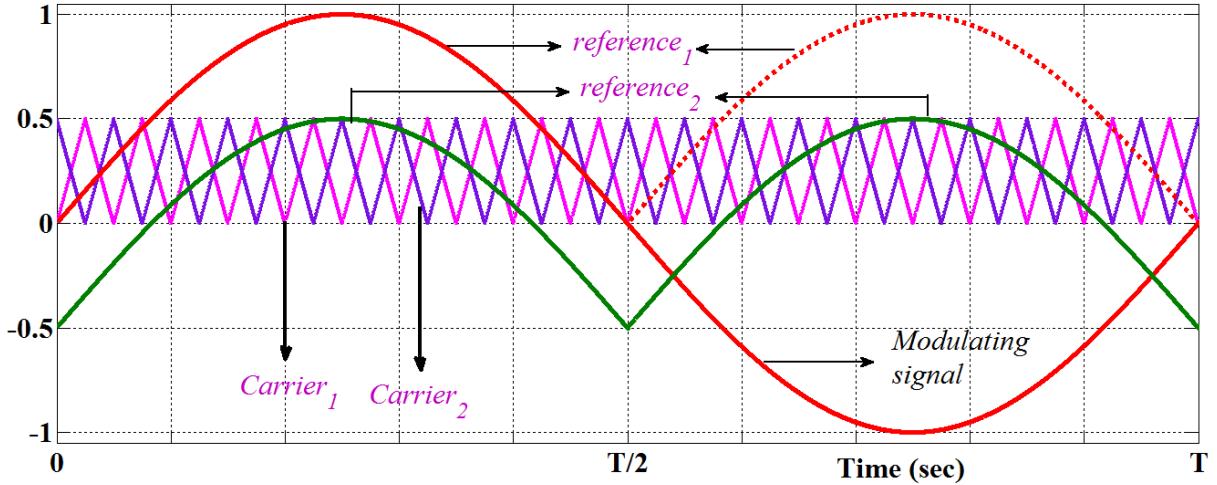

| Fig. 3.1: Carrier and modulating signal arrangement of multi reference modulation scheme to obtain five-levels in phase-voltage. ....                    | 78 |

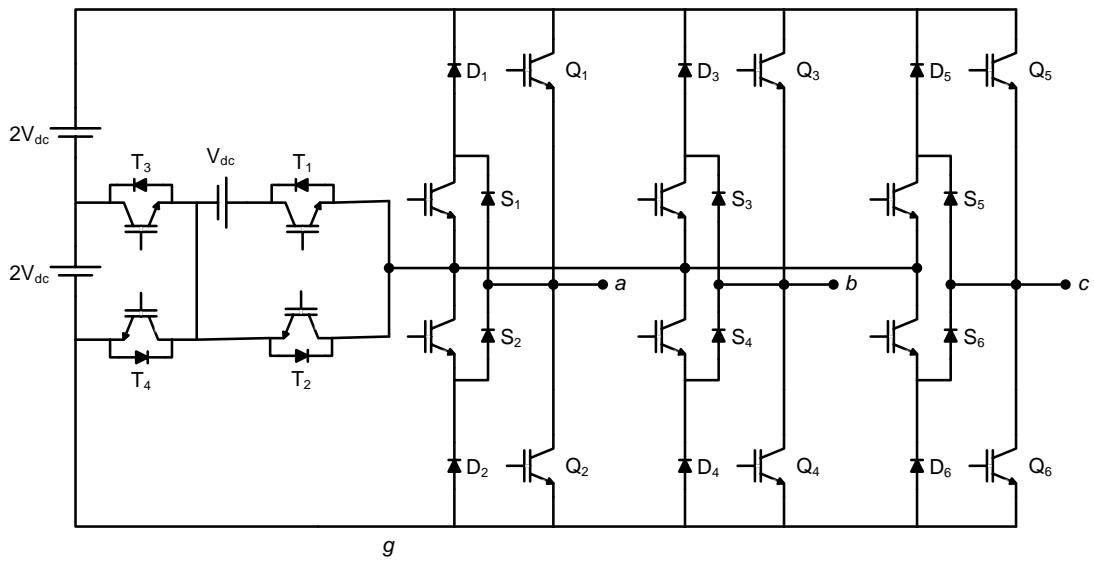

| Fig. 3.2: Three-phase five-level T-type RSC-MLI. ....                                                                                                    | 79 |

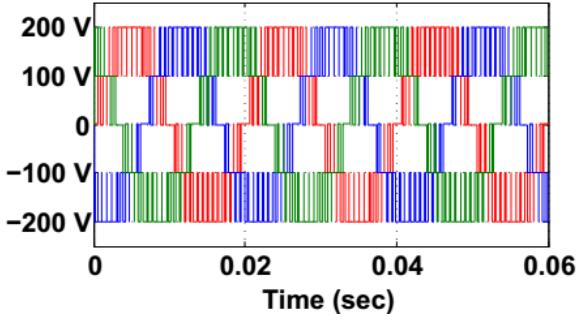

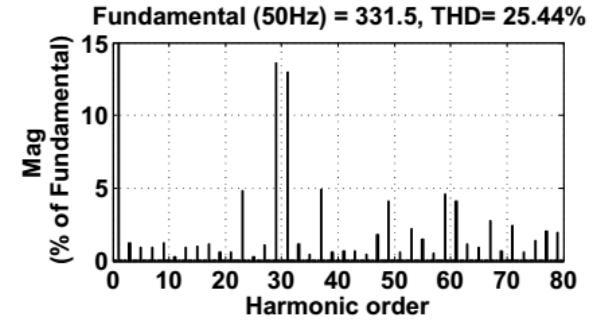

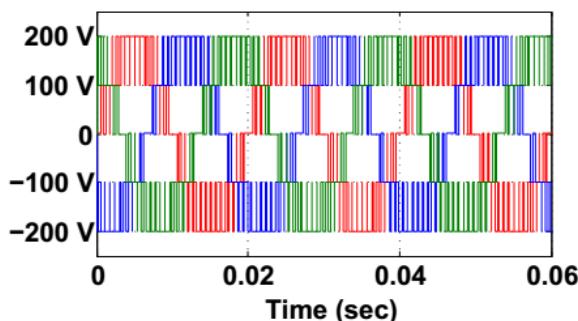

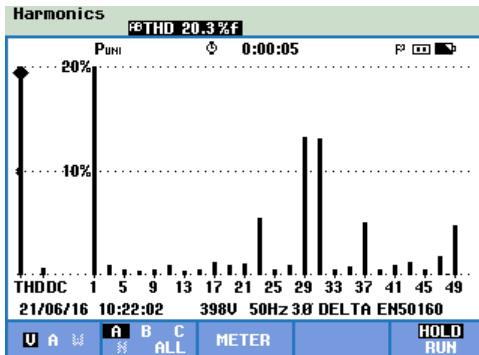

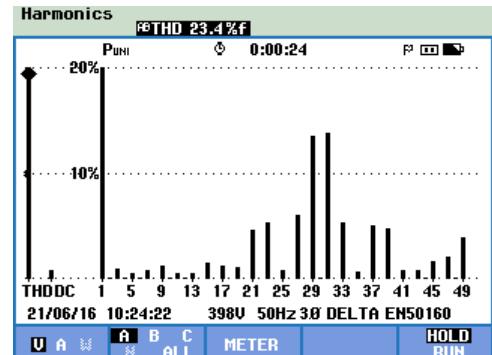

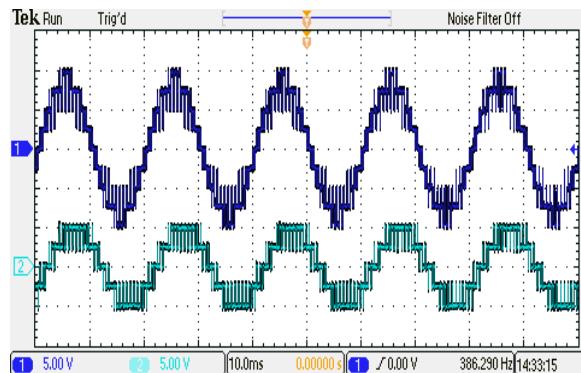

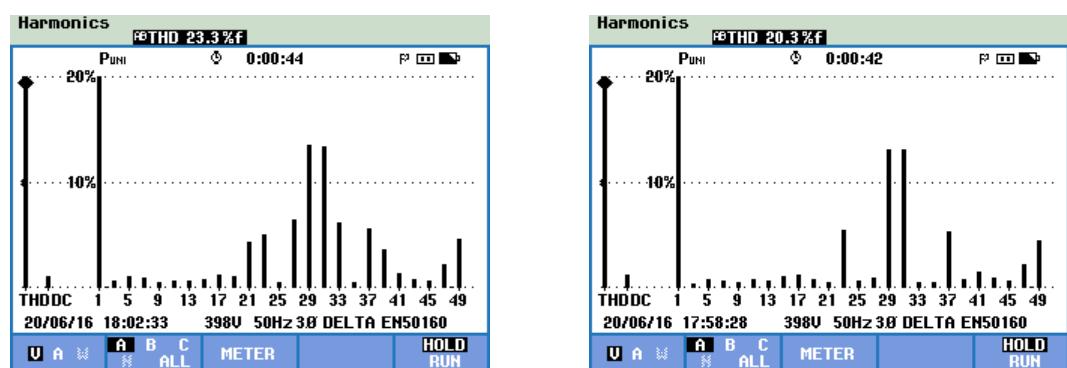

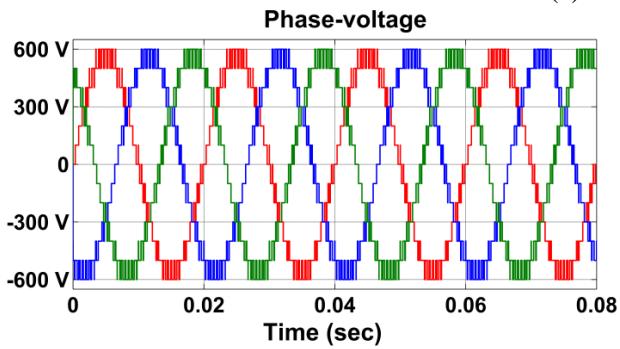

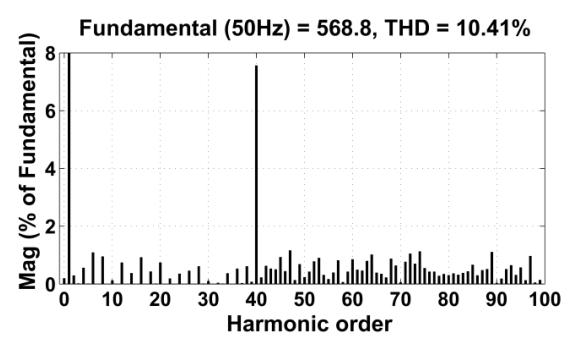

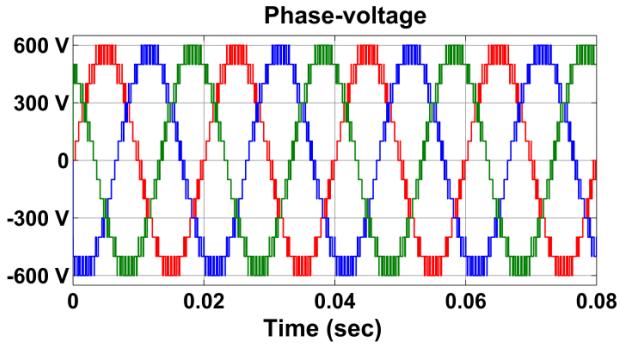

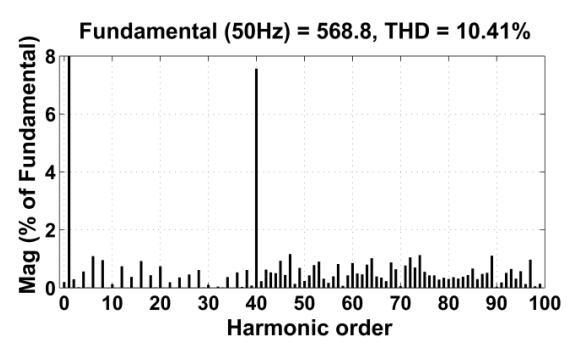

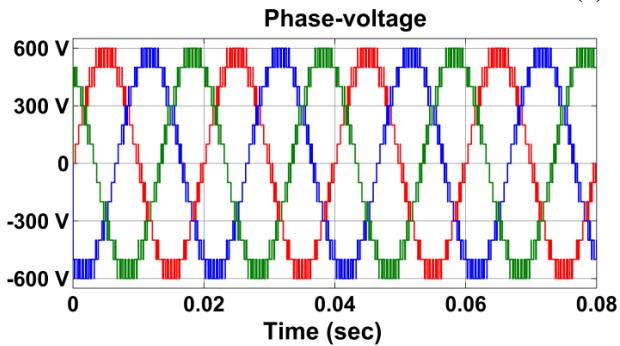

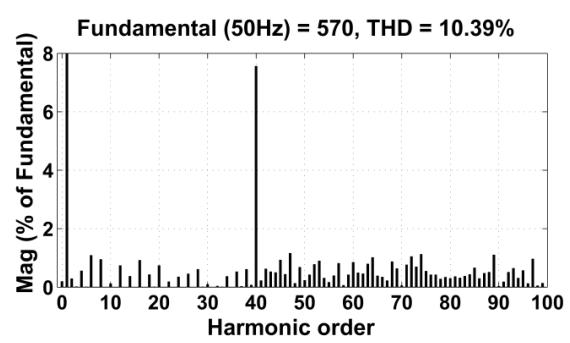

| Fig. 3.3: Performance of five-level T-type RSC-MLI with multi reference modulation scheme. ....                                                          | 80 |

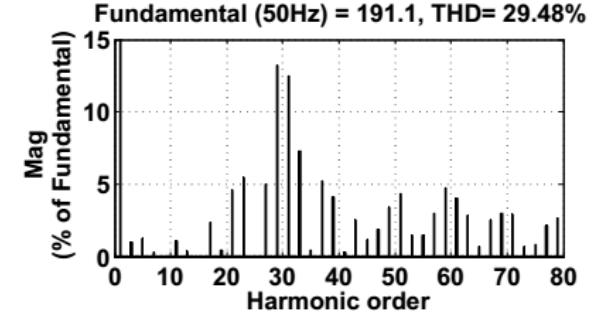

| Fig. 3.4: Line-voltage harmonic performance of multi reference and LSPWM schemes for $m_f = 30$ .....                                                    | 81 |

| Fig. 3.5: Carrier arrangement in multi reference and LSPWM-OPD schemes. ....                                                                             | 82 |

| Fig. 3.6: Performance of LSPWM-OPD on five-level CHB MLI. ....                                                                                           | 82 |

| Fig. 3.7: Experimental performance of LSPWM-IPD scheme on five-level CHB MLI. ....                                                                       | 84 |

| Fig. 3.8: Experimental performance of LSPWM-OPD scheme on five-level CHB MLI. ....                                                                       | 84 |

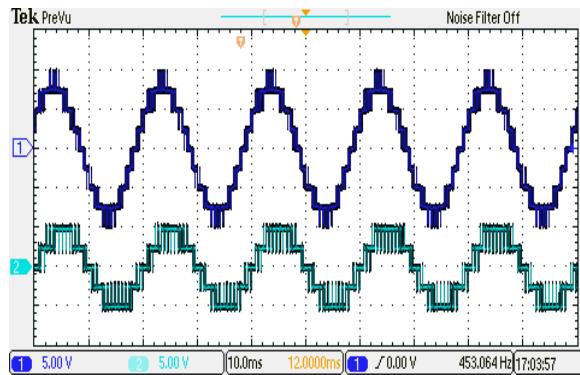

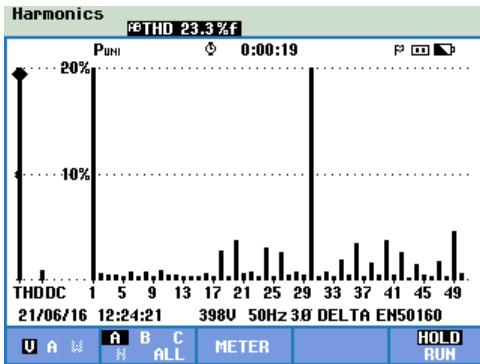

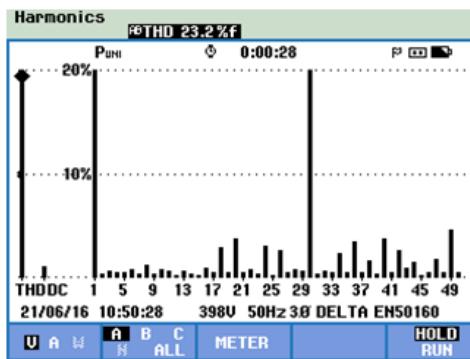

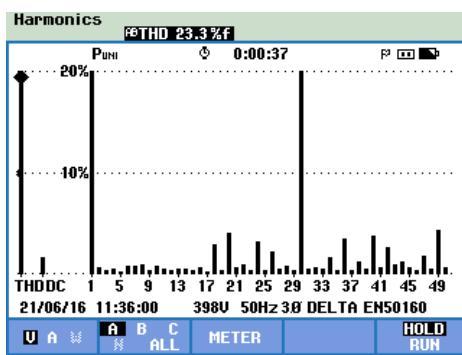

| Fig. 3.9: Experimental performance of multi reference PWM scheme for five-level T-type RSC-MLI. ....                                                     | 85 |

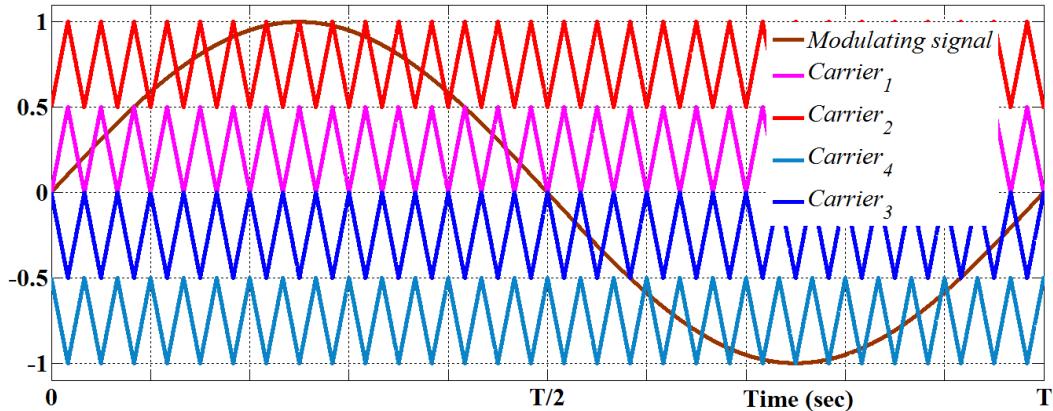

| Fig. 3.10: Carrier and modulating signal arrangement of conventional reduced carrier PWM for five-levels in phase-voltage. ....                          | 86 |

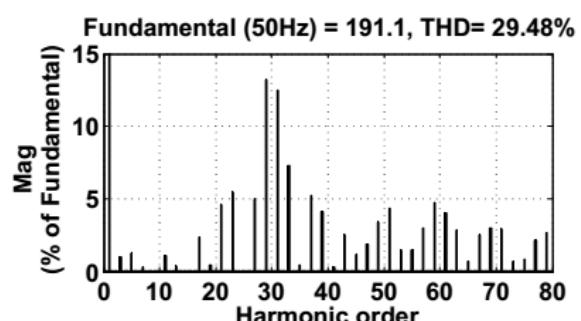

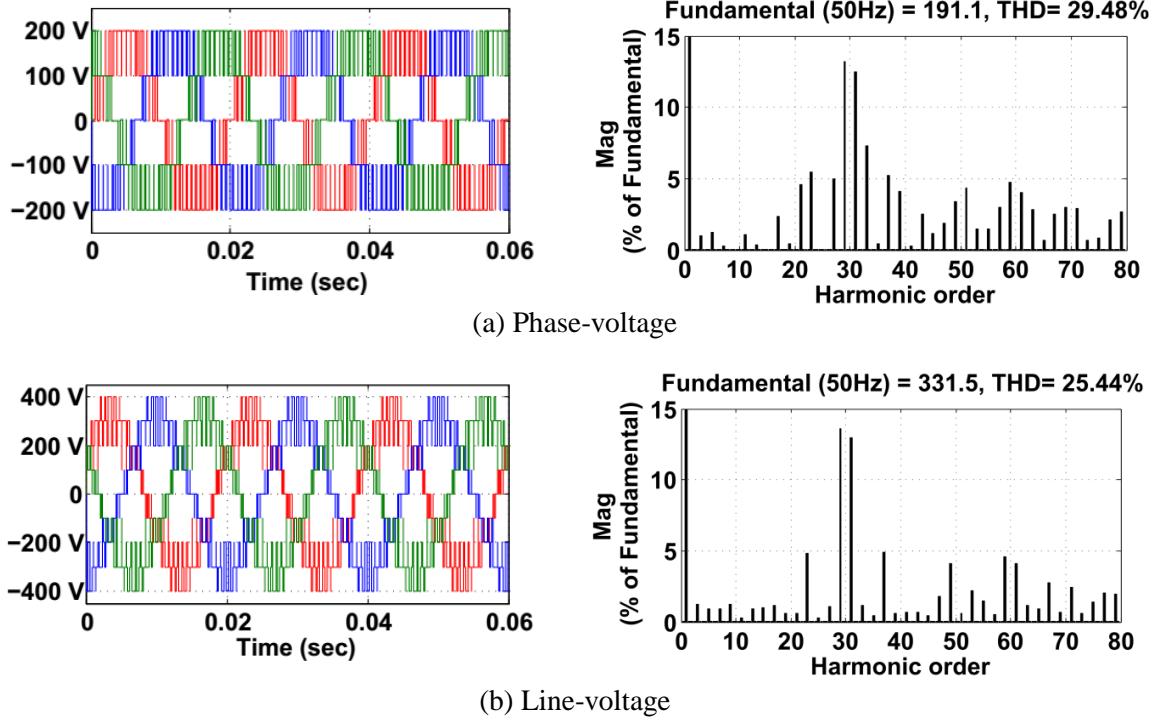

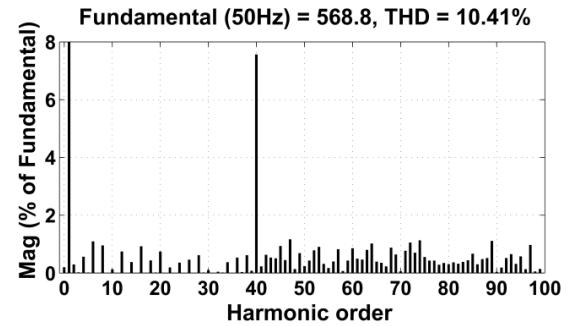

| Fig. 3.11: Harmonic performance of conventional reduced carrier PWM on five-level inverter. ....                                                         | 87 |

| Fig. 3.12: Carrier arrangement of reduced carrier PWM in terms of LSWPWM-OPD. ....                                                                       | 87 |

| Fig. 3.13: Hybrid switching function PWM for five-levels in phase-voltage. ....                                                                          | 88 |

| Fig. 3.14: Carrier and modulating signal arrangement of modified multi reference dual carrier PWM scheme for five-level phase-voltage. ....              | 92 |

| Fig. 3.15: Carrier and modulating signal arrangement of modified multi reference dual carrier PWM in terms of LSPWM-IPD. ....                            | 92 |

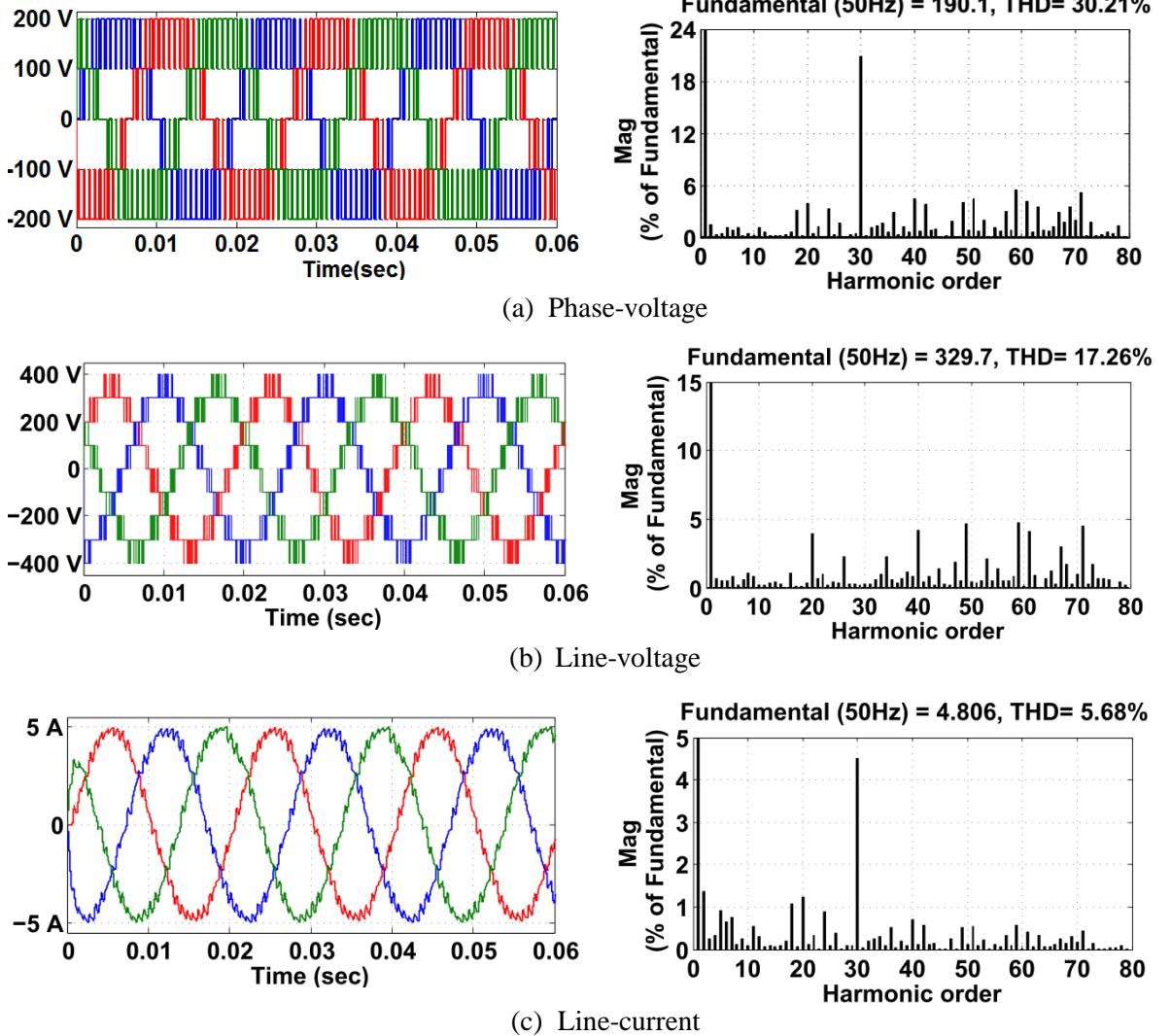

| Fig. 3.16: Performance of modified multi reference dual carrier PWM on five-level T-type RSC-MLI for $m_a = 0.95$ . ....                                 | 93 |

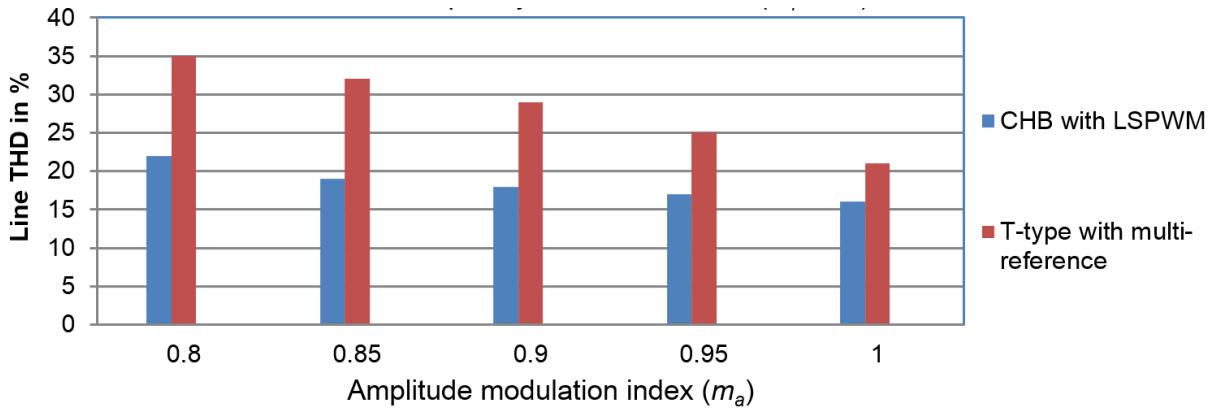

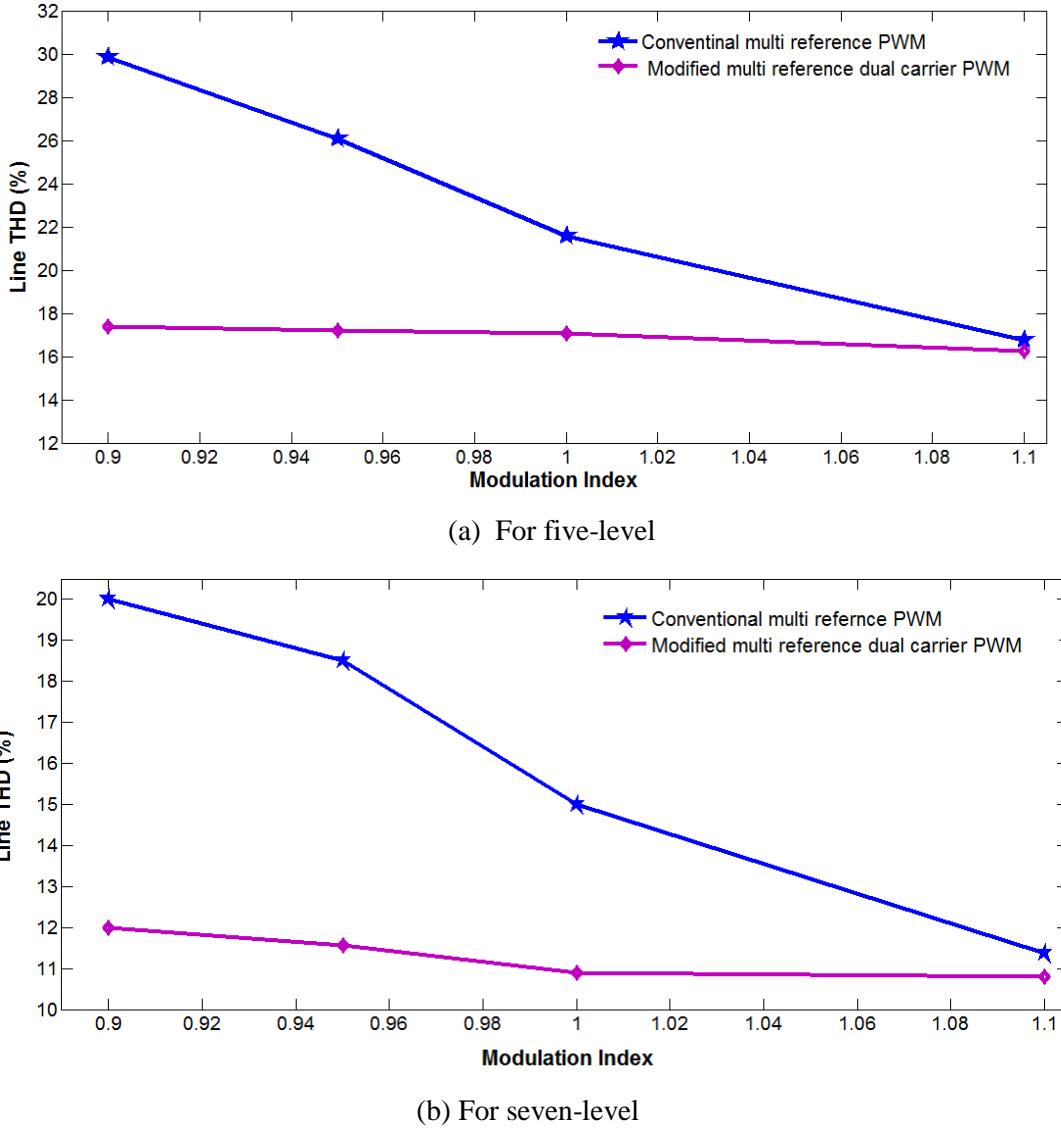

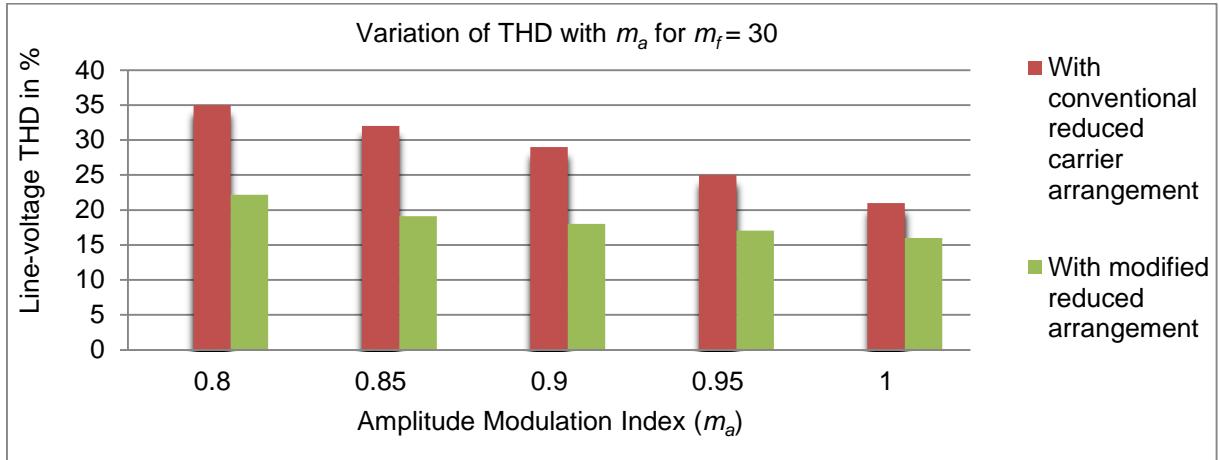

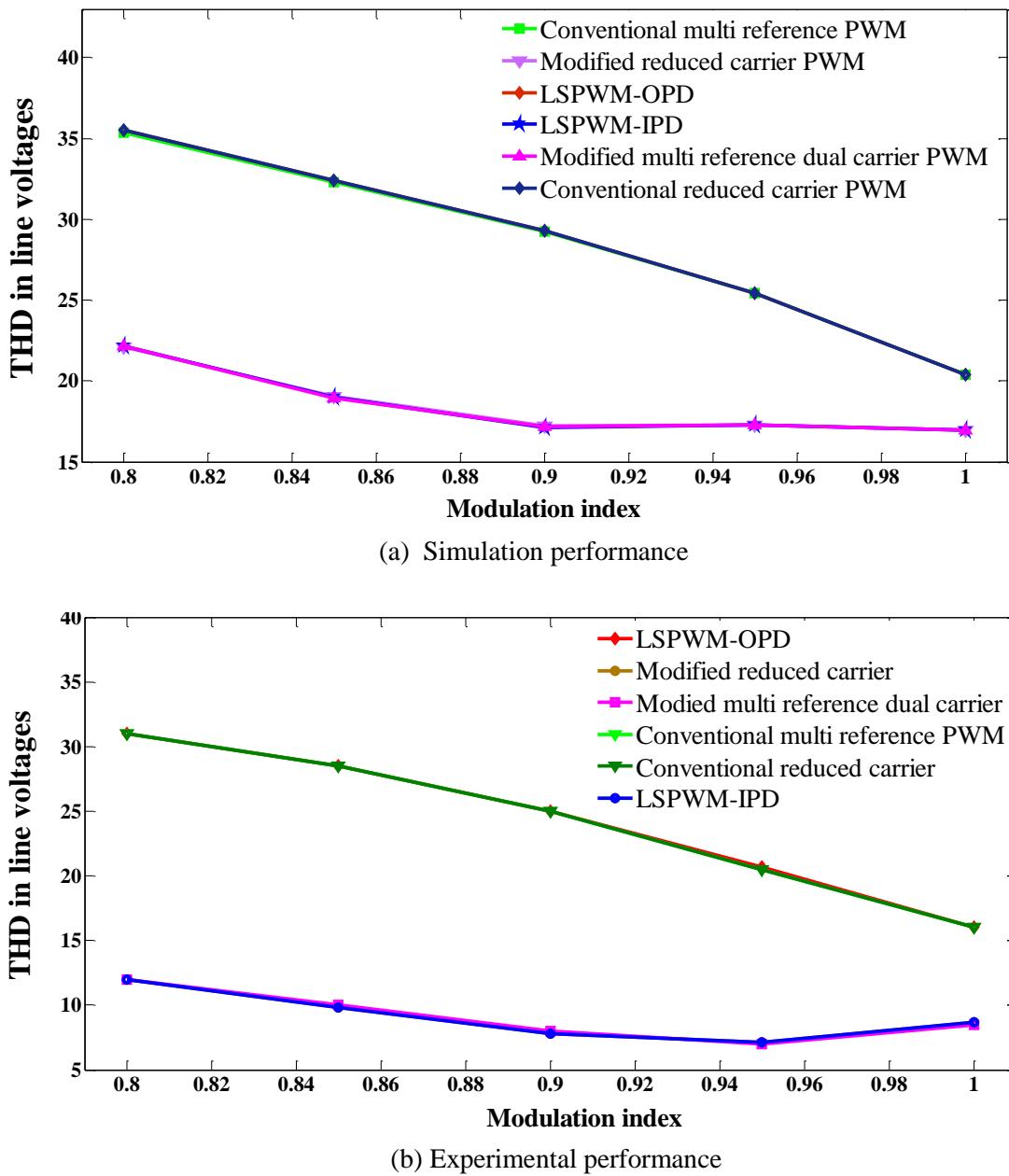

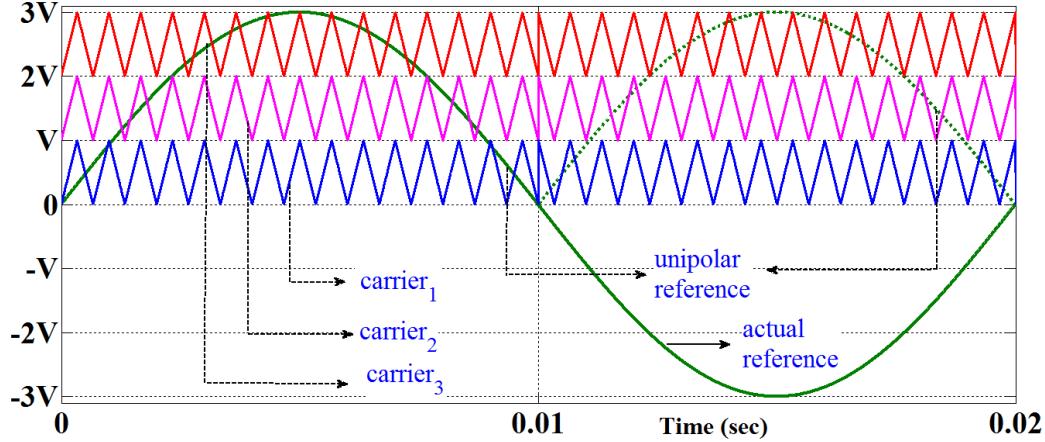

| Fig. 3.17: Comparison of line-voltage THD with modified and conventional multi reference PWM schemes for various values of $m_a$ on T-type RSC-MLI. .... | 94 |

|                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

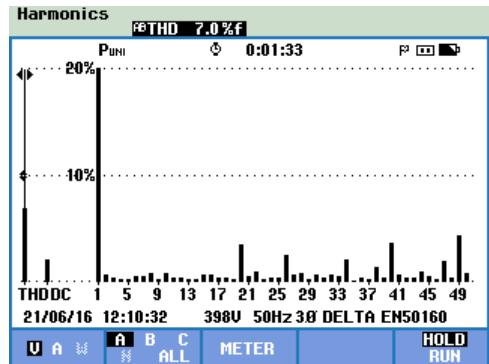

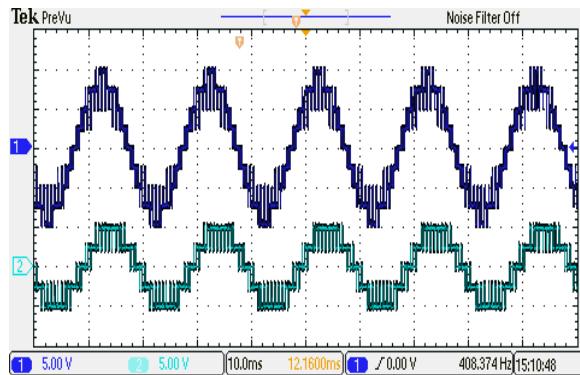

| Fig. 3.18: Experimental performance of modified multi reference dual carrier PWM on five-level T-type RSC-MLI .....                                     | 95  |

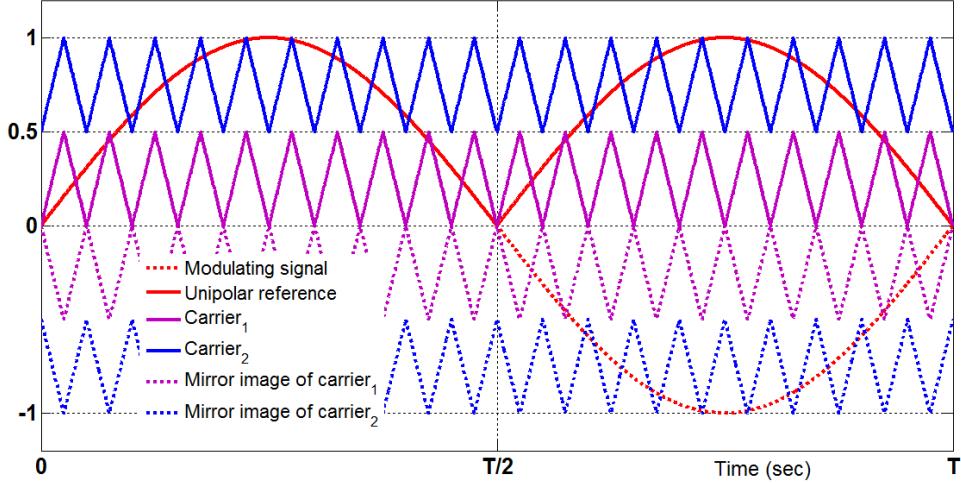

| Fig. 3.19: Carrier and modulating signal arrangement for proposed modified reduced carrier PWM scheme for five-level phase-voltage .....                | 96  |

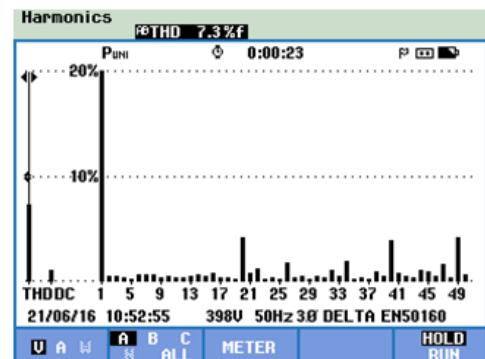

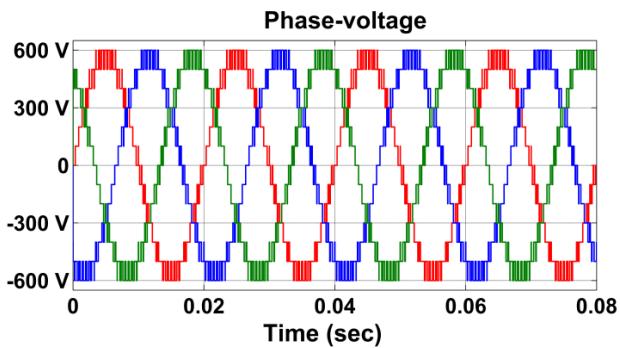

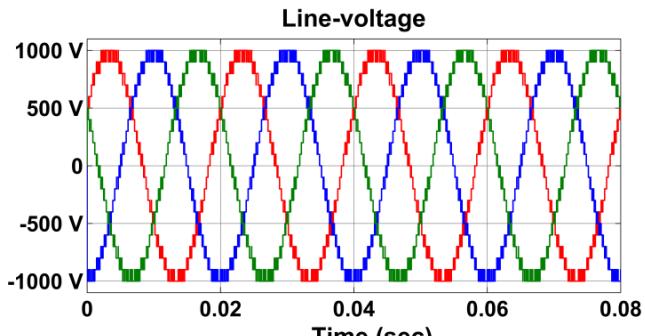

| Fig. 3.20: Simulation performance of modified reduced carrier PWM on five-level T-type RSC-MLI .....                                                    | 98  |

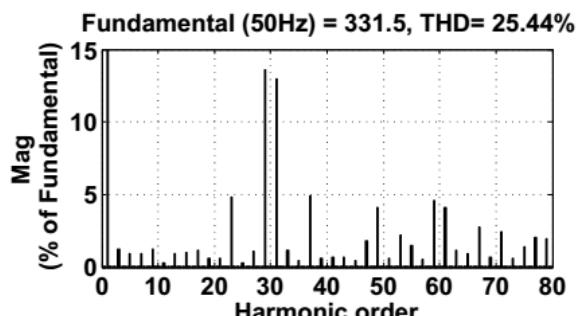

| Fig. 3.21: Line-voltage THD performance of conventional and modified reduced carrier PWM. ....                                                          | 99  |

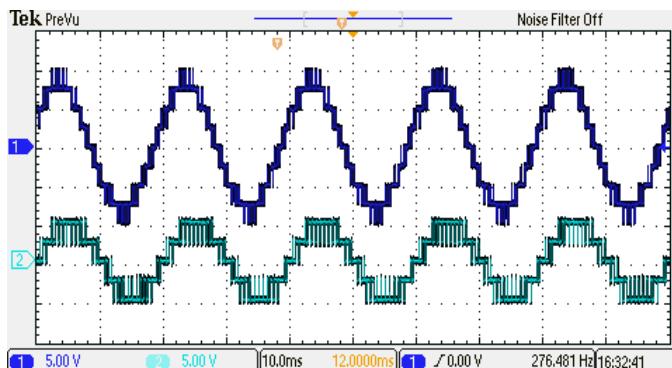

| Fig. 3.22: Experimental performance of the proposed modified reduced carrier PWM. ....                                                                  | 99  |

| Fig. 3.23: Comparative THD performance of the proposed and conventional PWM schemes on five-level inverter.....                                         | 100 |

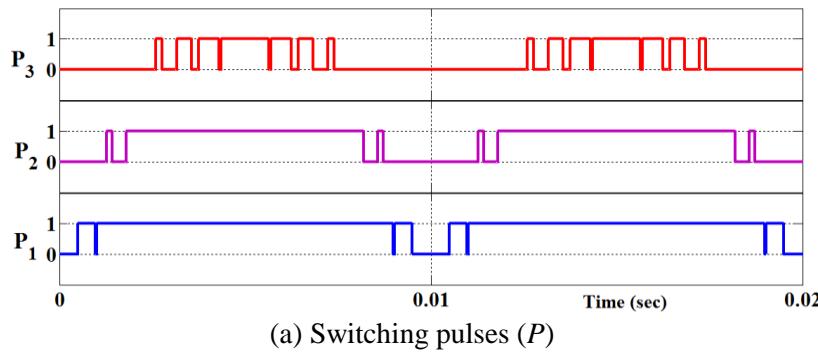

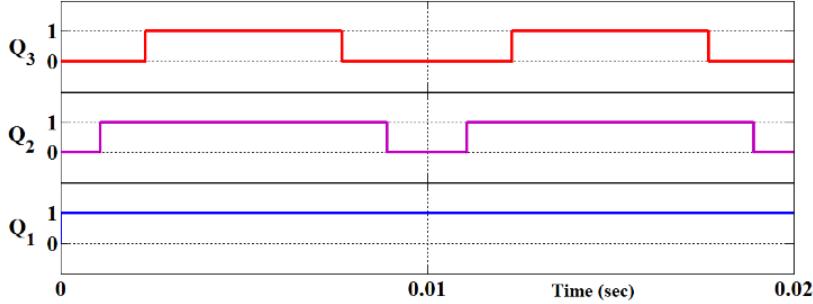

| Fig. 3.24: Carrier and modulating signal arrangement for proposed modified reduced carrier arrangement for obtaining seven-levels in phase-voltage..... | 102 |

| Fig. 3.25: Conventional switching pattern of reduced carrier PWM scheme for seven-level inverter .....                                                  | 102 |

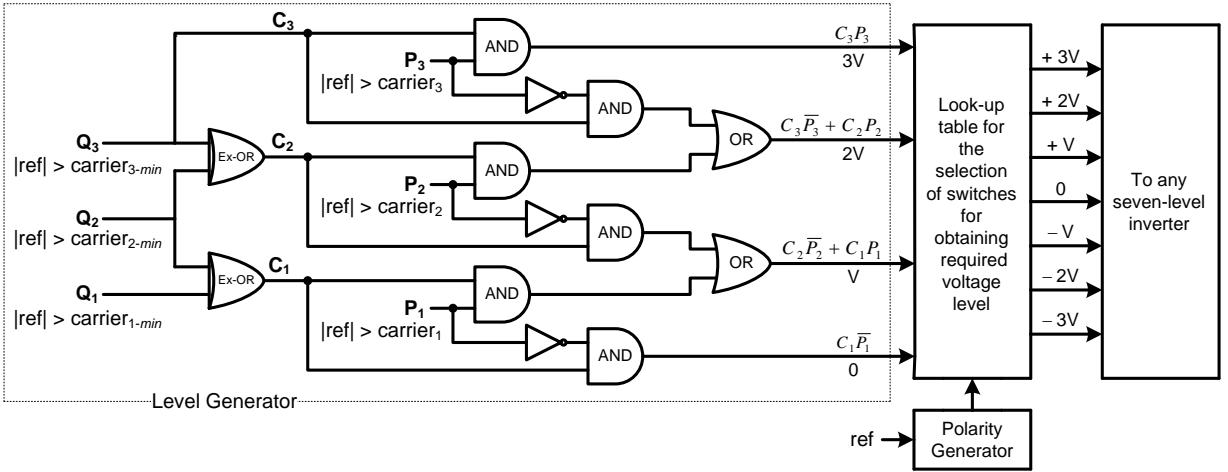

| Fig. 3.26: Desired switching pattern with reduced carrier PWM for obtaining seven-level phase-voltage.....                                              | 103 |

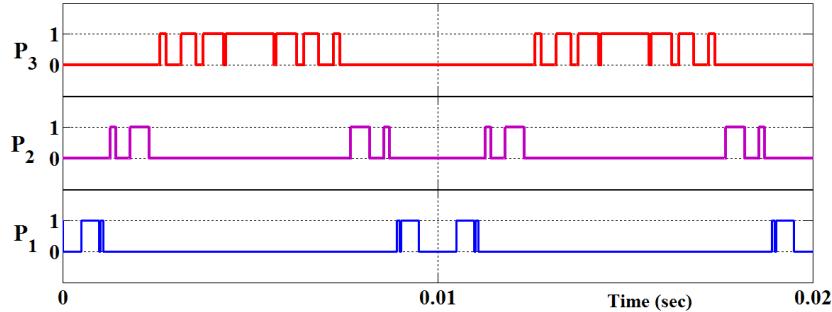

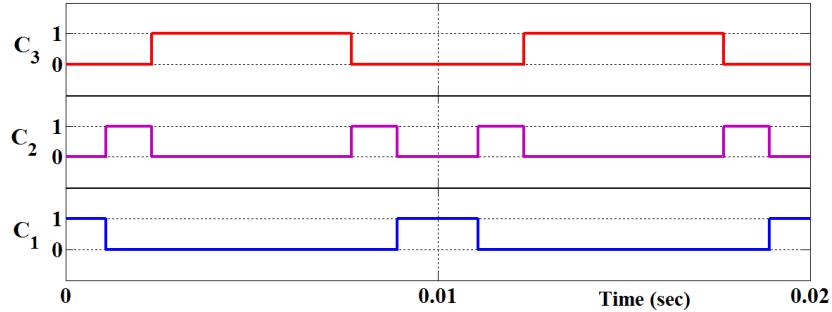

| Fig. 3.27: Mapping of overlapped conduction intervals ( $Q$ ) with non-overlapped conduction intervals ( $C$ ) and their associated K-maps. ....        | 103 |

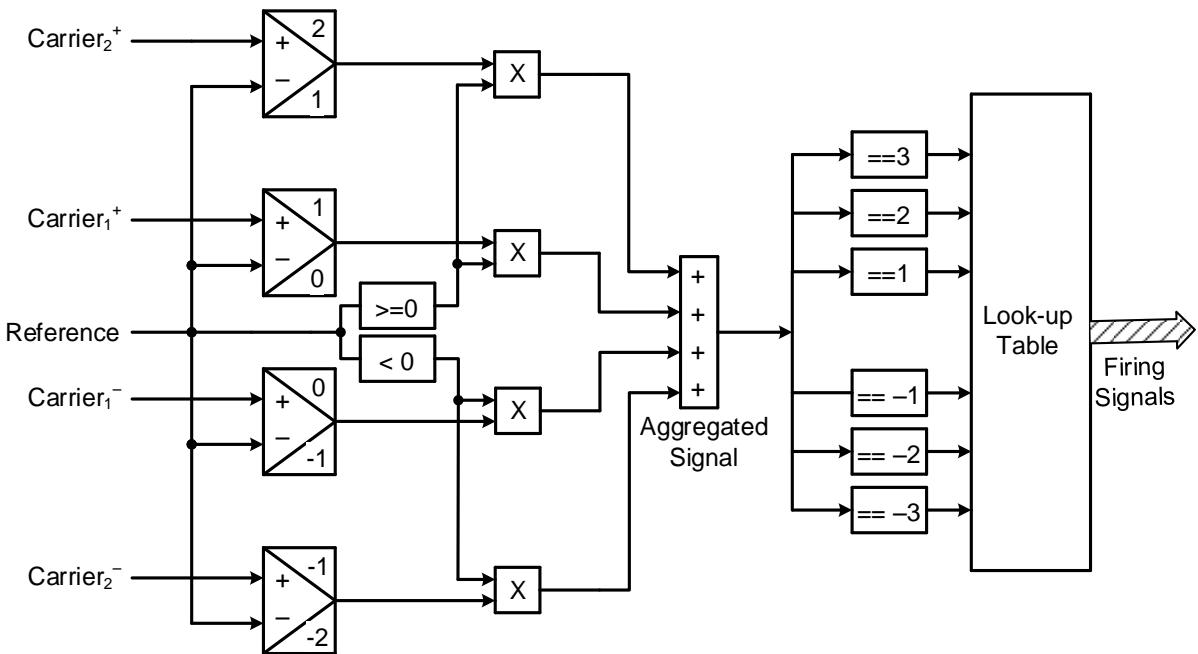

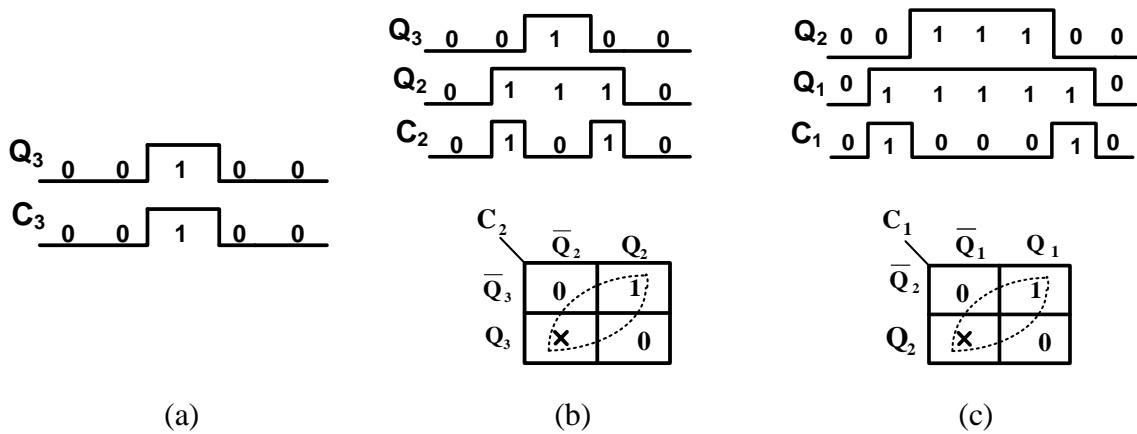

| Fig. 3.28: Implementation of the proposed switching logic for obtaining seven-level phase-voltage.....                                                  | 105 |

| Fig. 3.29: Seven-level single-phase configuration of asymmetrical RSC-MLI based MLDCL. ....                                                             | 106 |

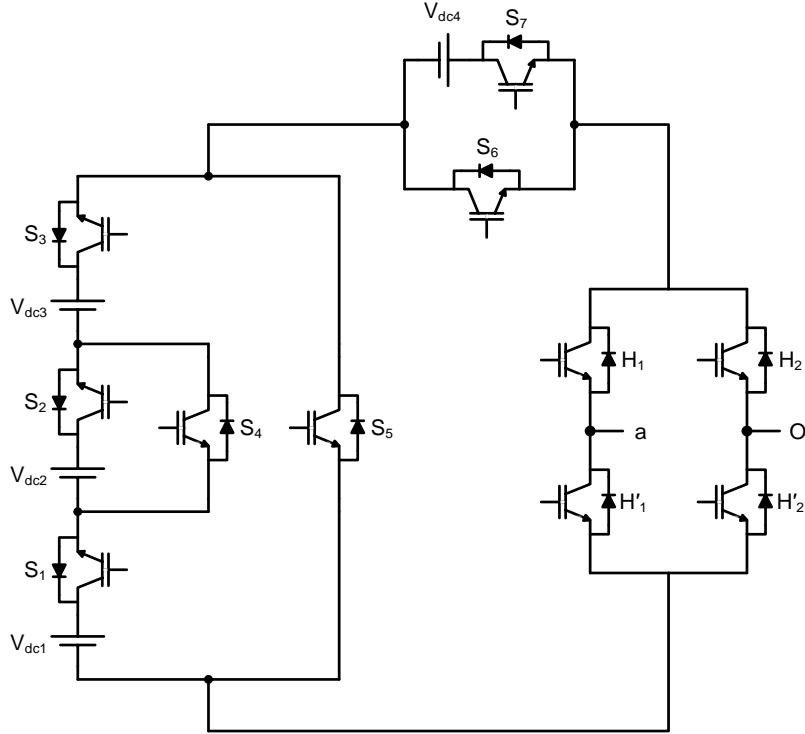

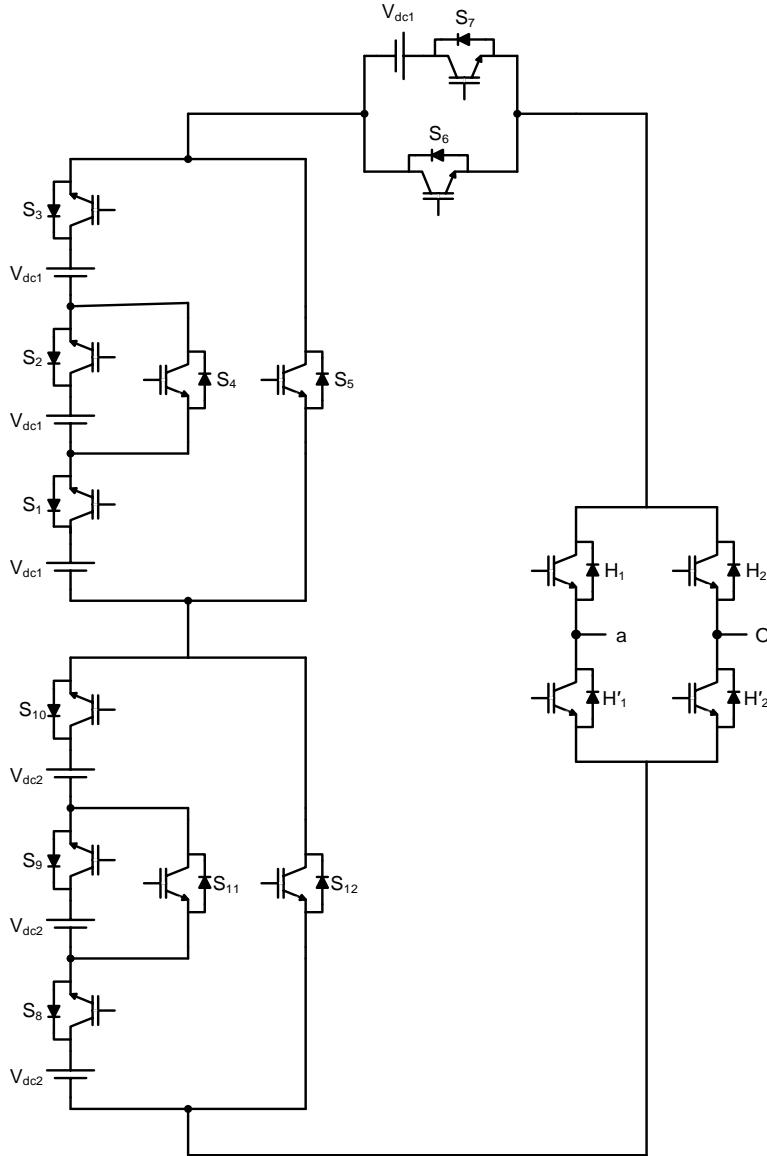

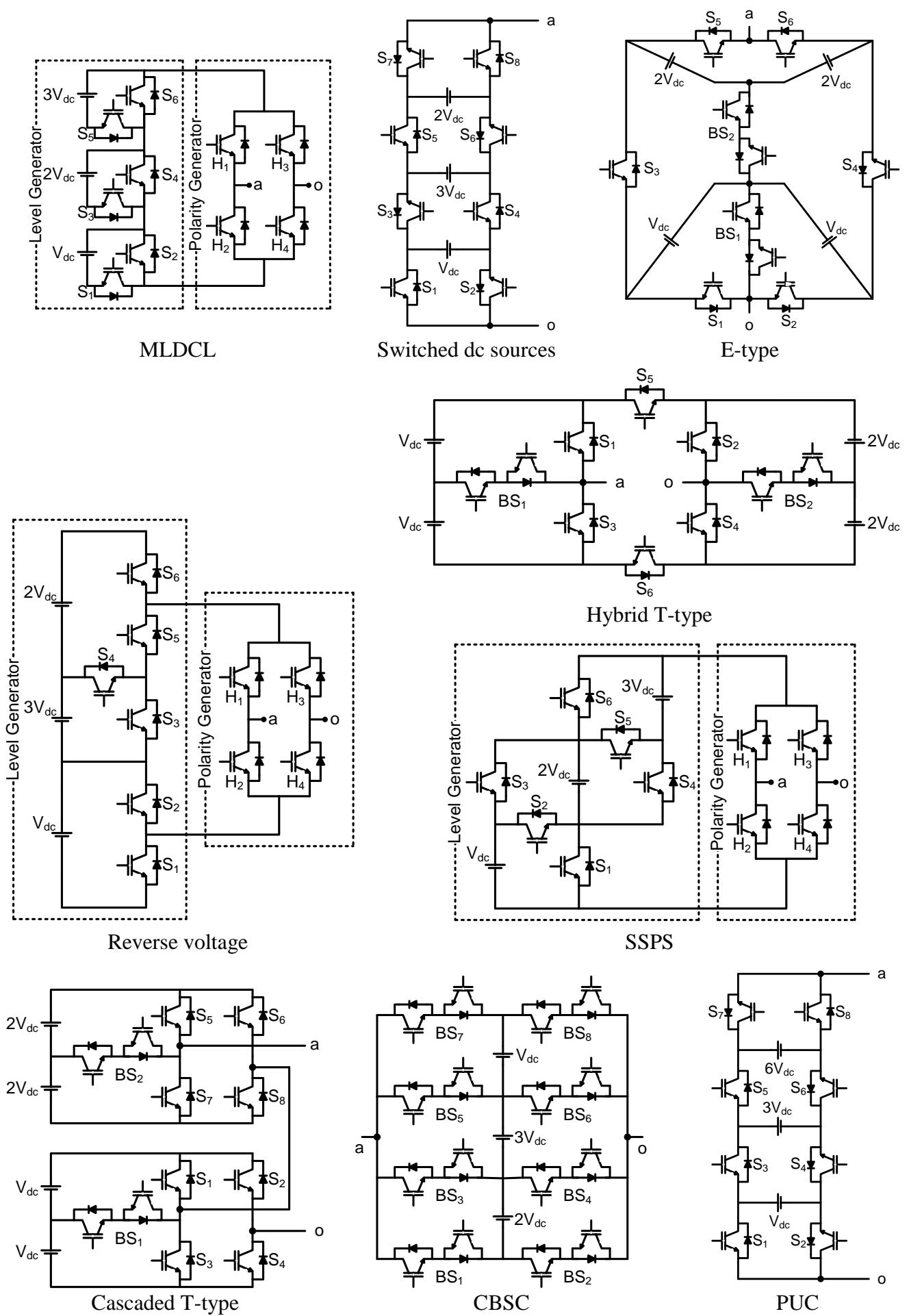

| Fig. 3.30: Single-phase configurations of thirteen-level asymmetrical RSC-MLI topologies. ....                                                          | 107 |

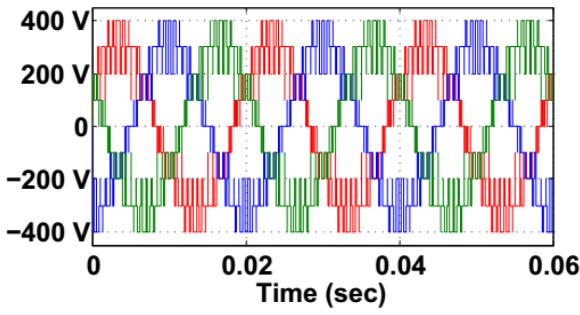

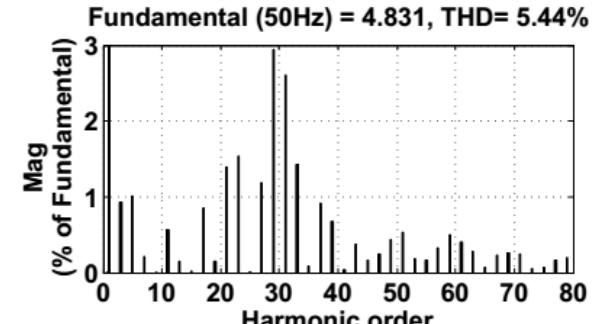

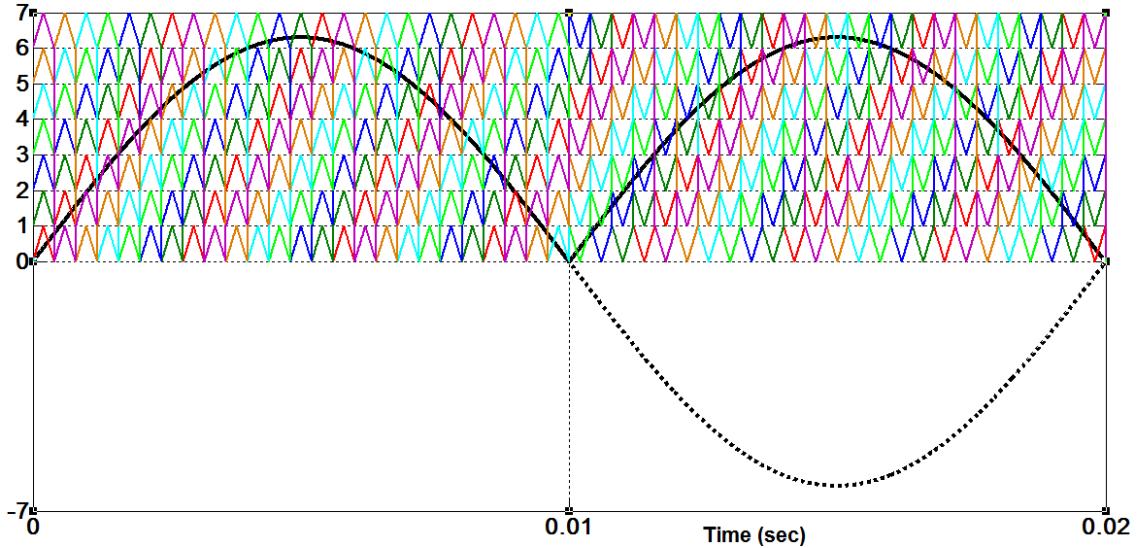

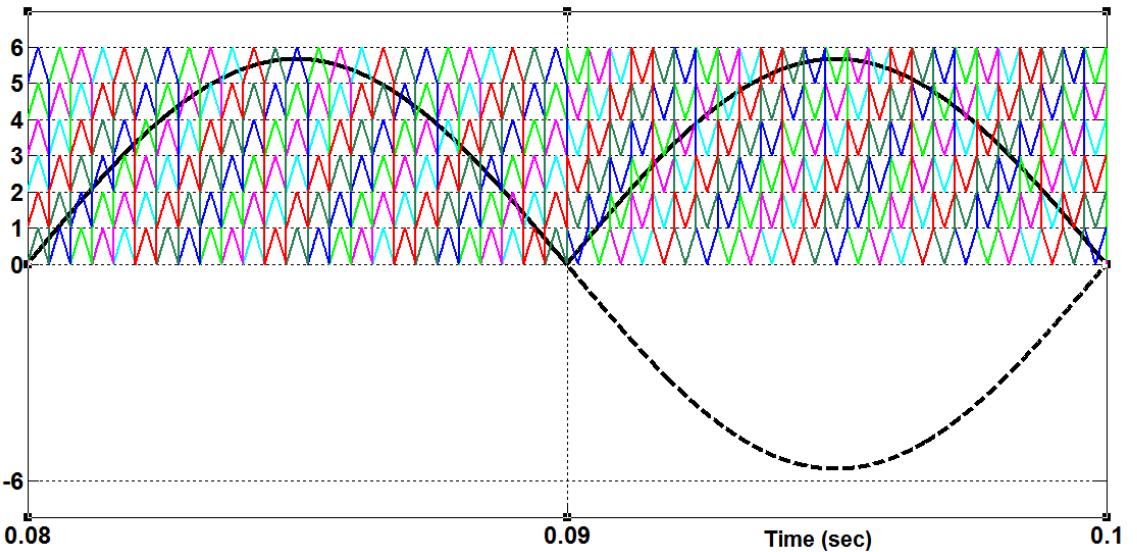

| Fig. 3.31: Phase-voltage performance of various RSC-MLI with the proposed PWM. ....                                                                     | 111 |

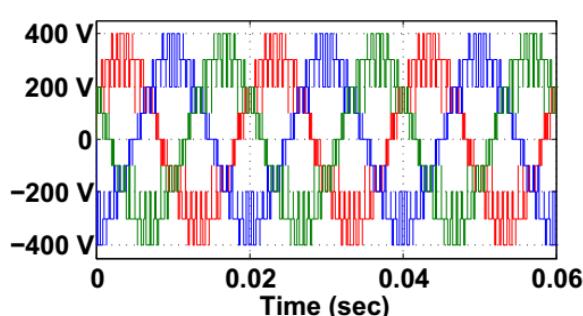

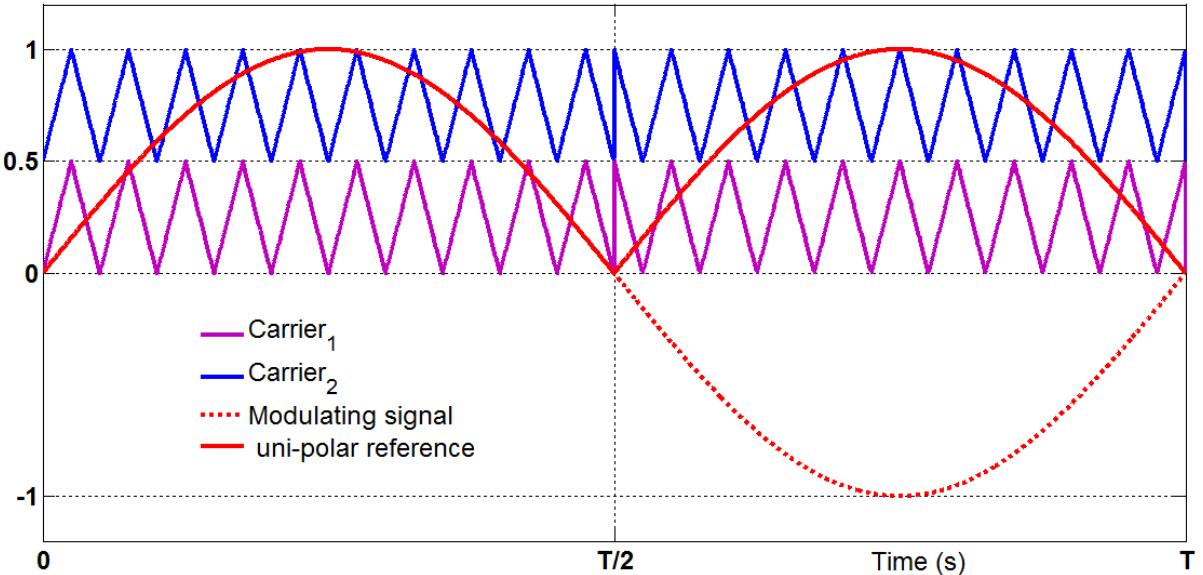

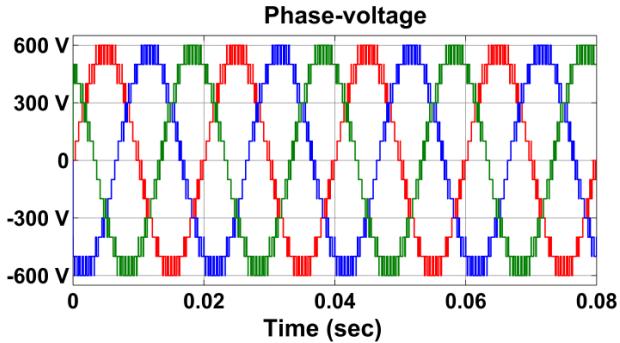

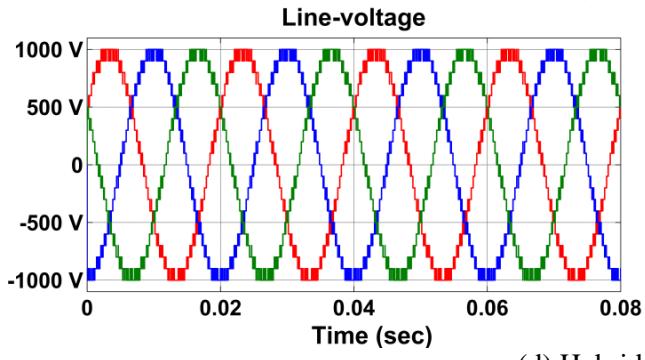

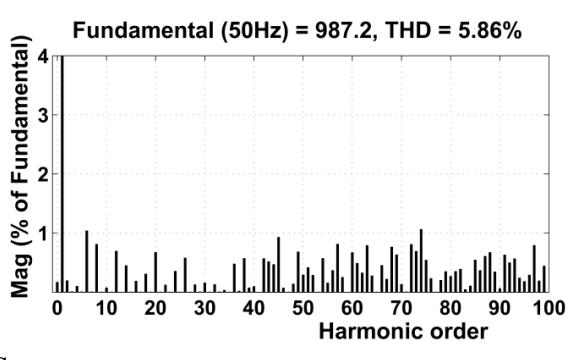

| Fig. 3.32: Line-voltage performance of various RSC-MLI with the proposed PWM. ....                                                                      | 112 |

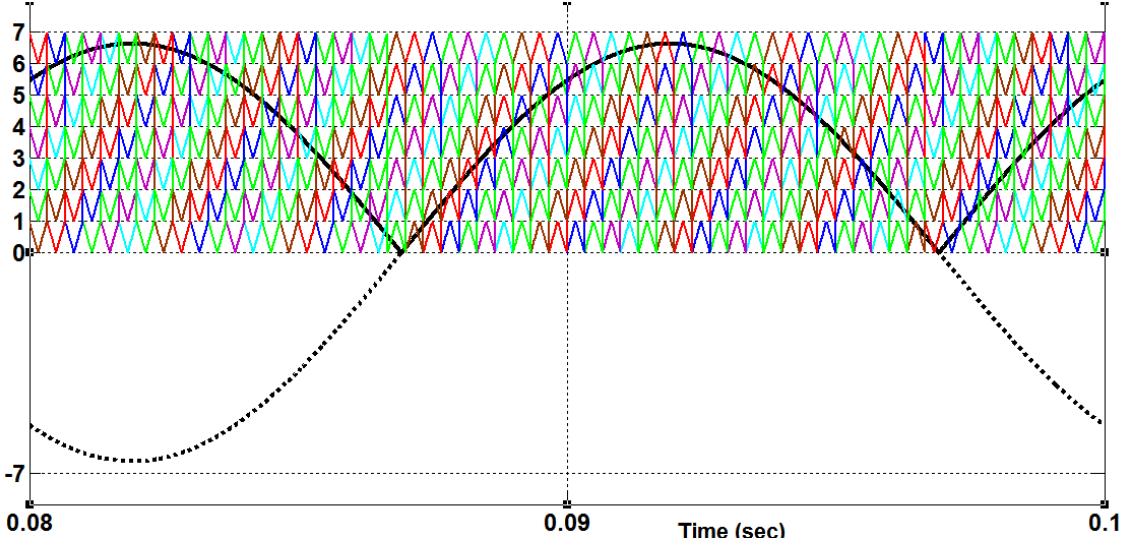

| Fig. 3.33: Performance of MLDCL with conventional reduced carrier arrangement.....                                                                      | 113 |

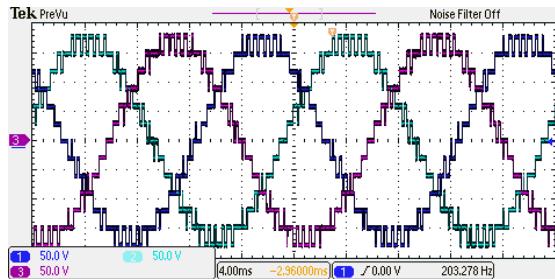

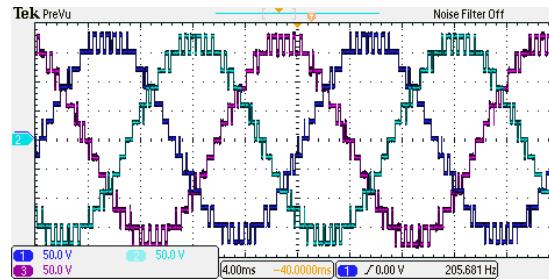

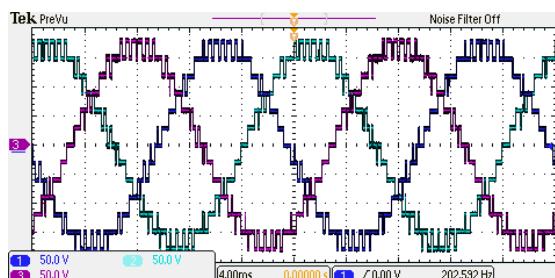

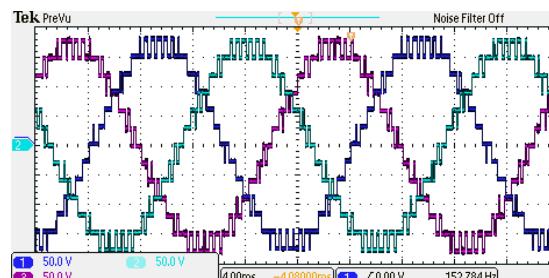

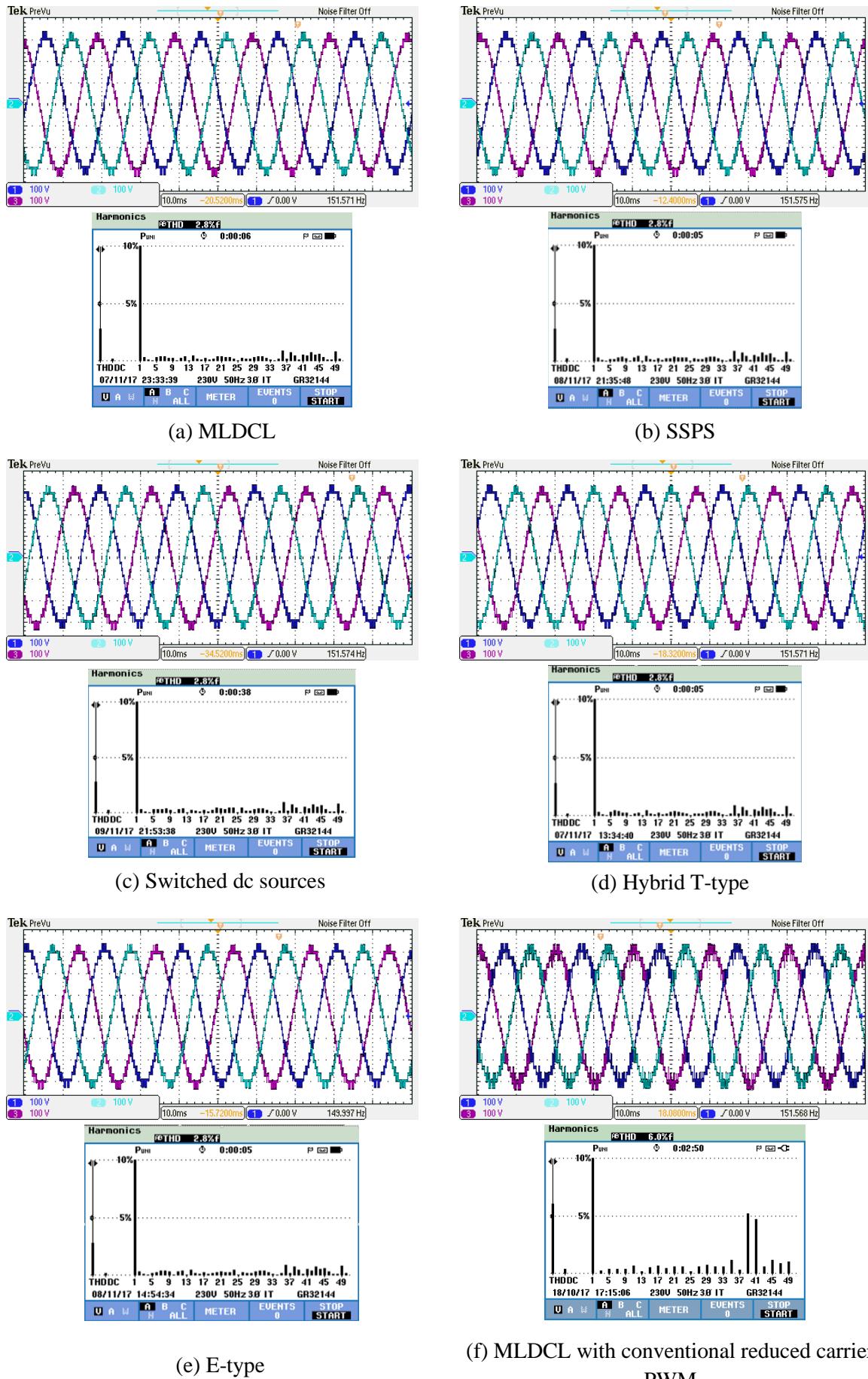

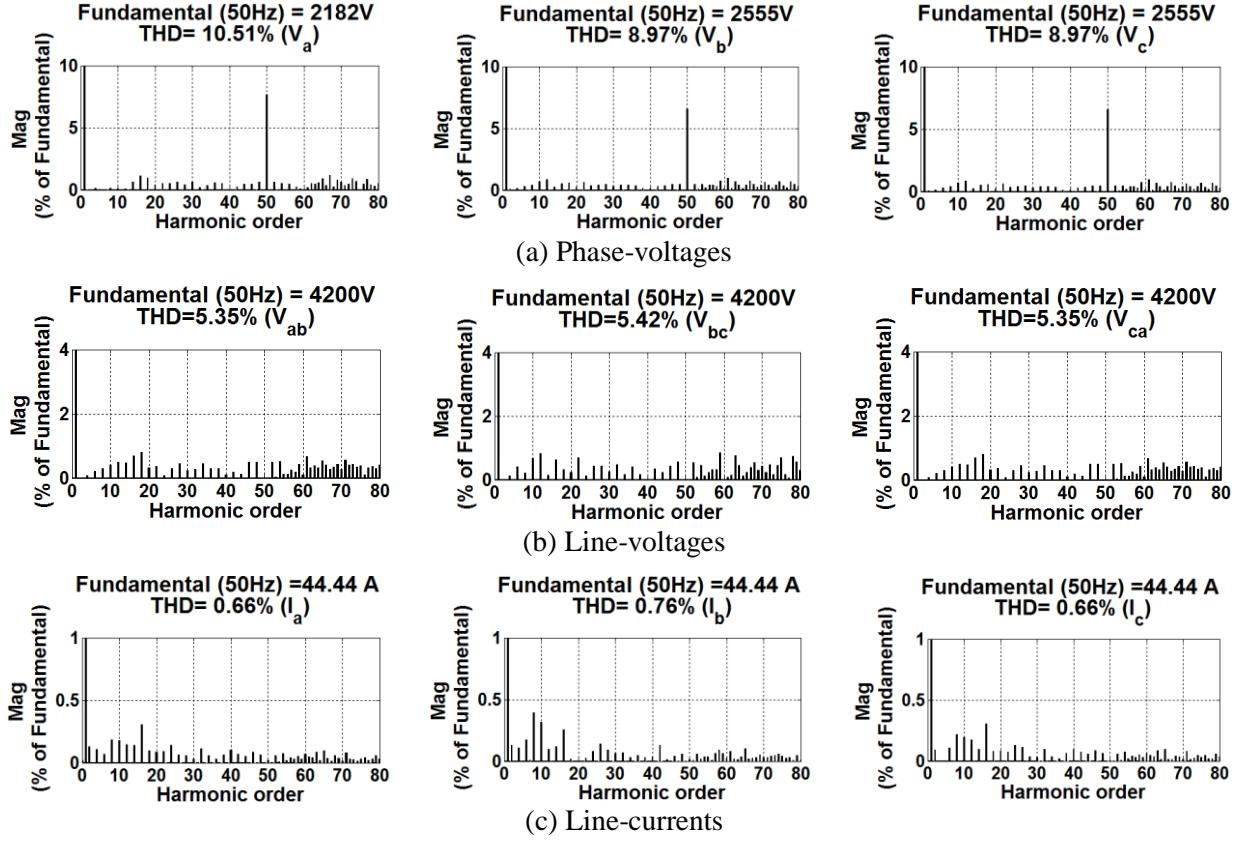

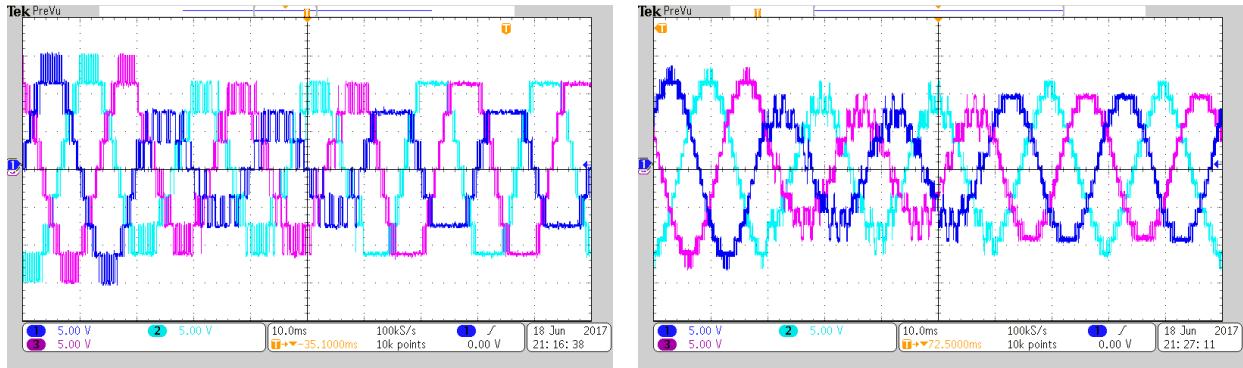

| Fig. 3.34: Experimental phase-voltage performance of various RSC-MLI topologies. ....                                                                   | 116 |

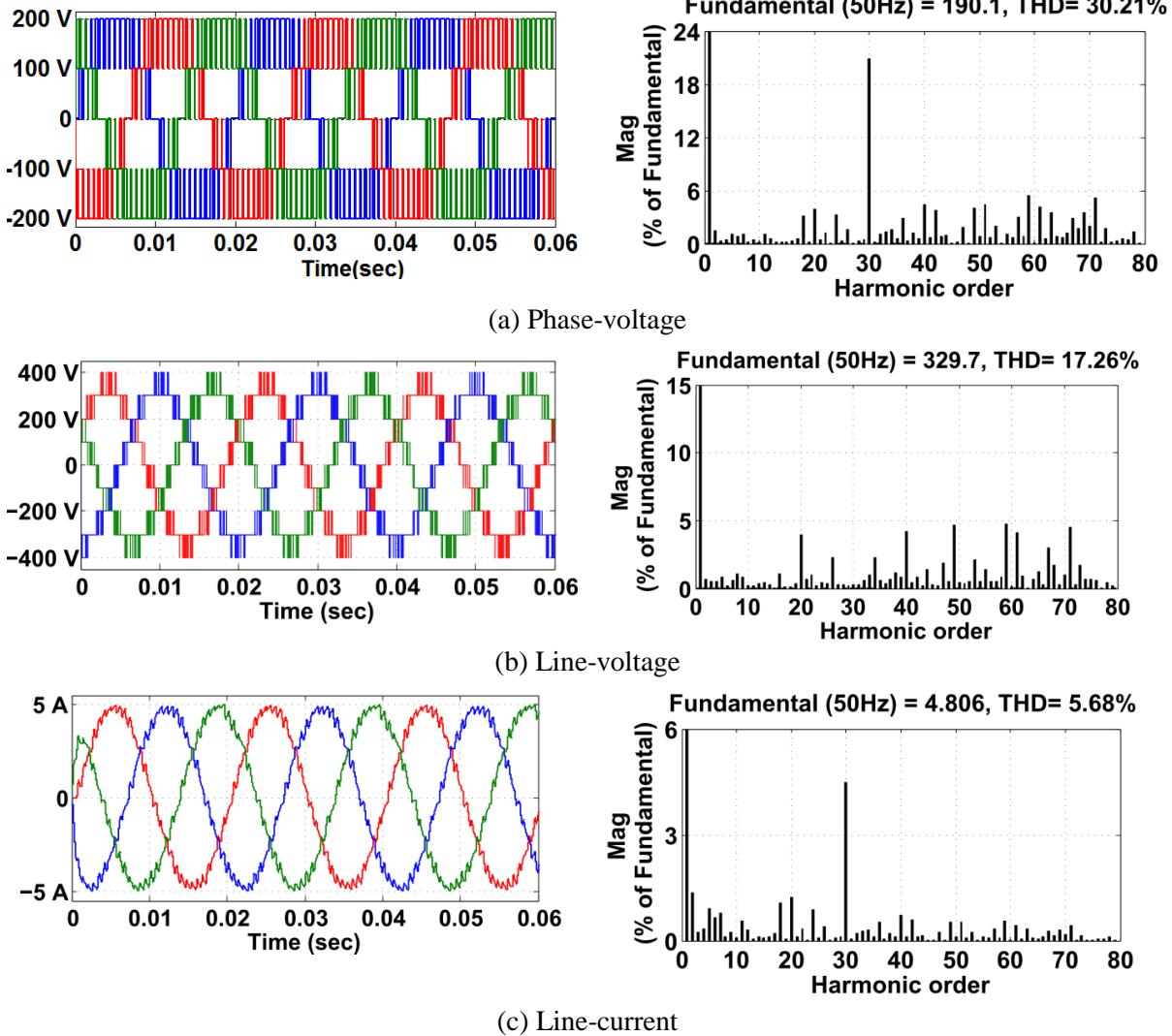

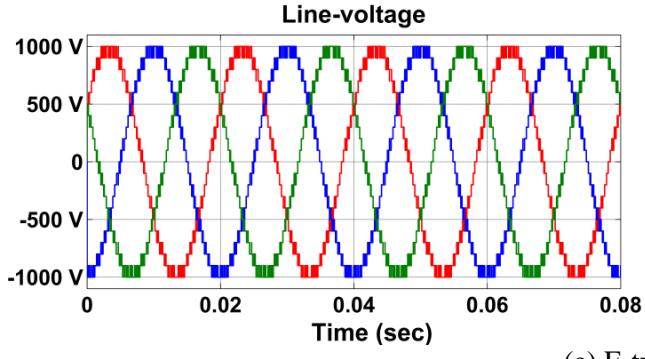

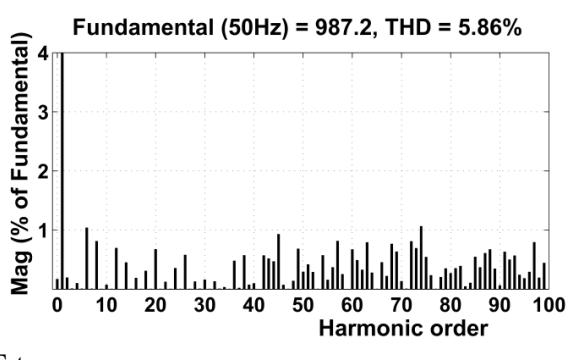

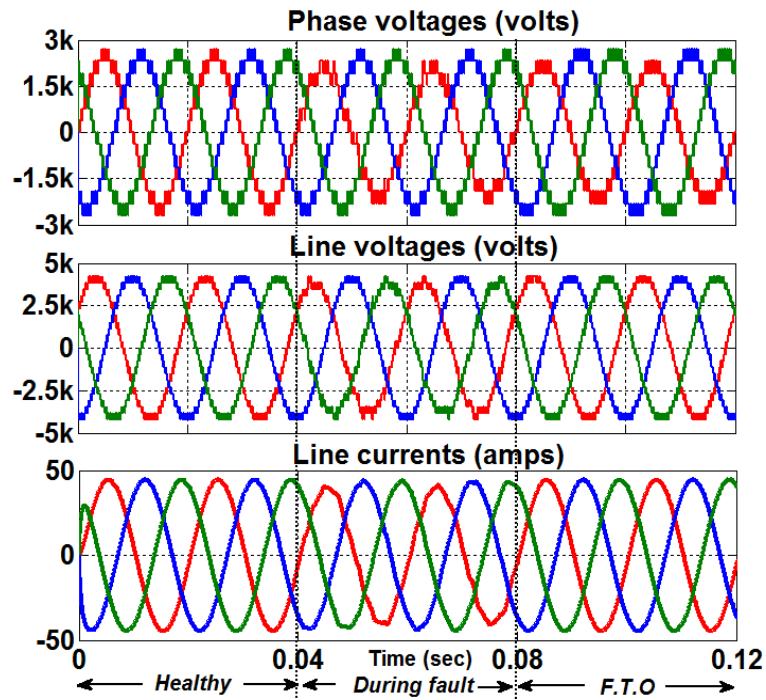

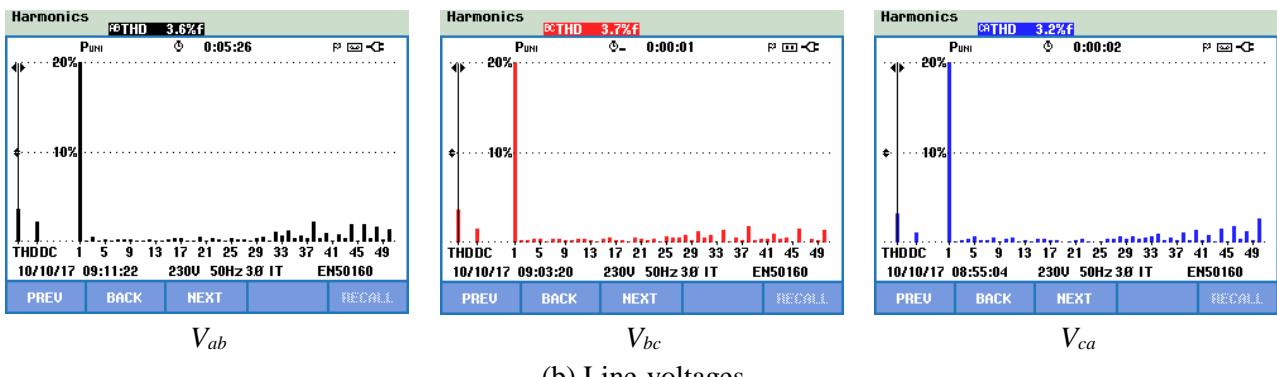

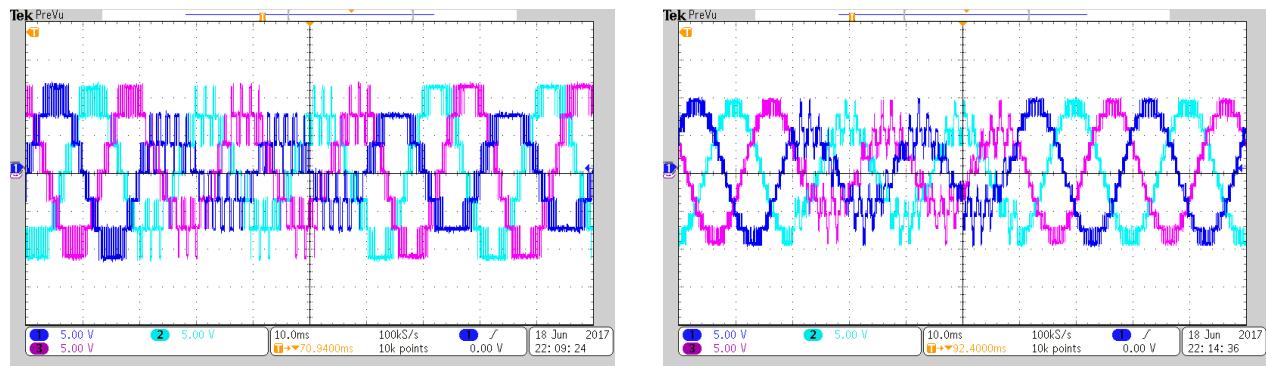

| Fig. 3.35: Experimental line-voltage performance of various RSC-MLI topologies. ....                                                                    | 117 |

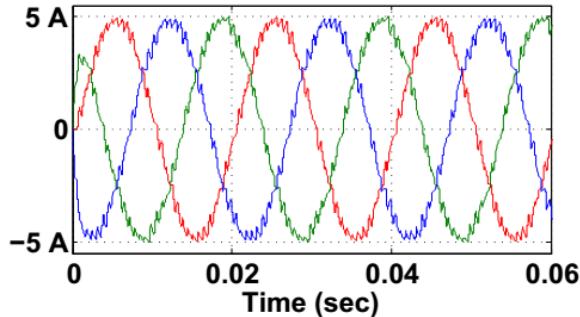

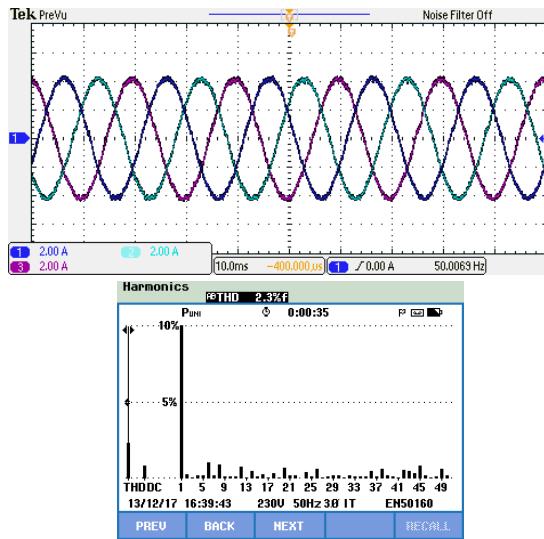

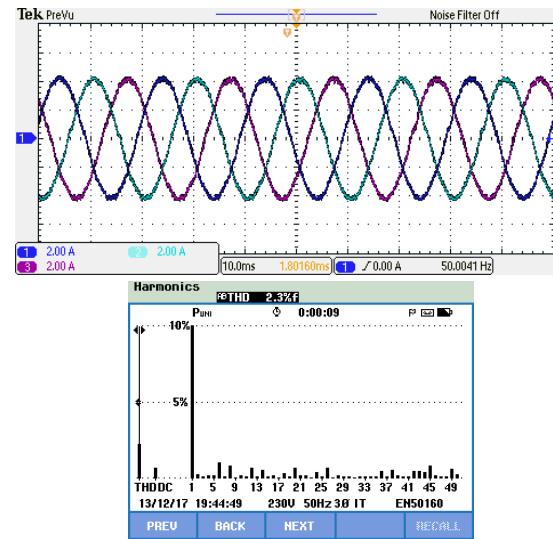

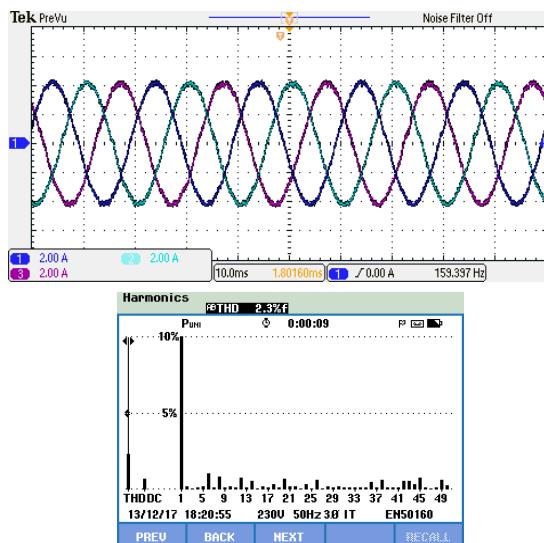

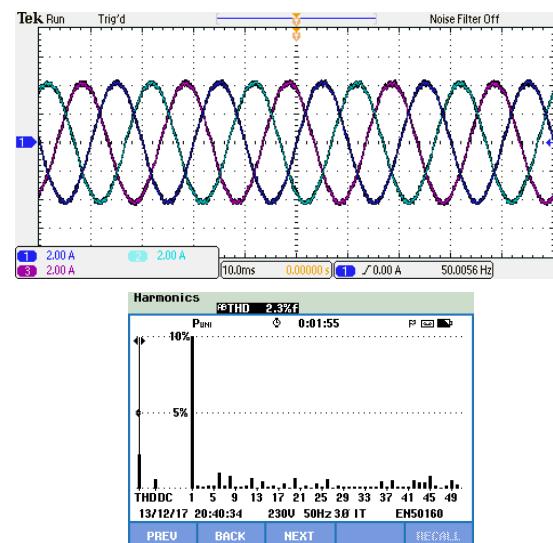

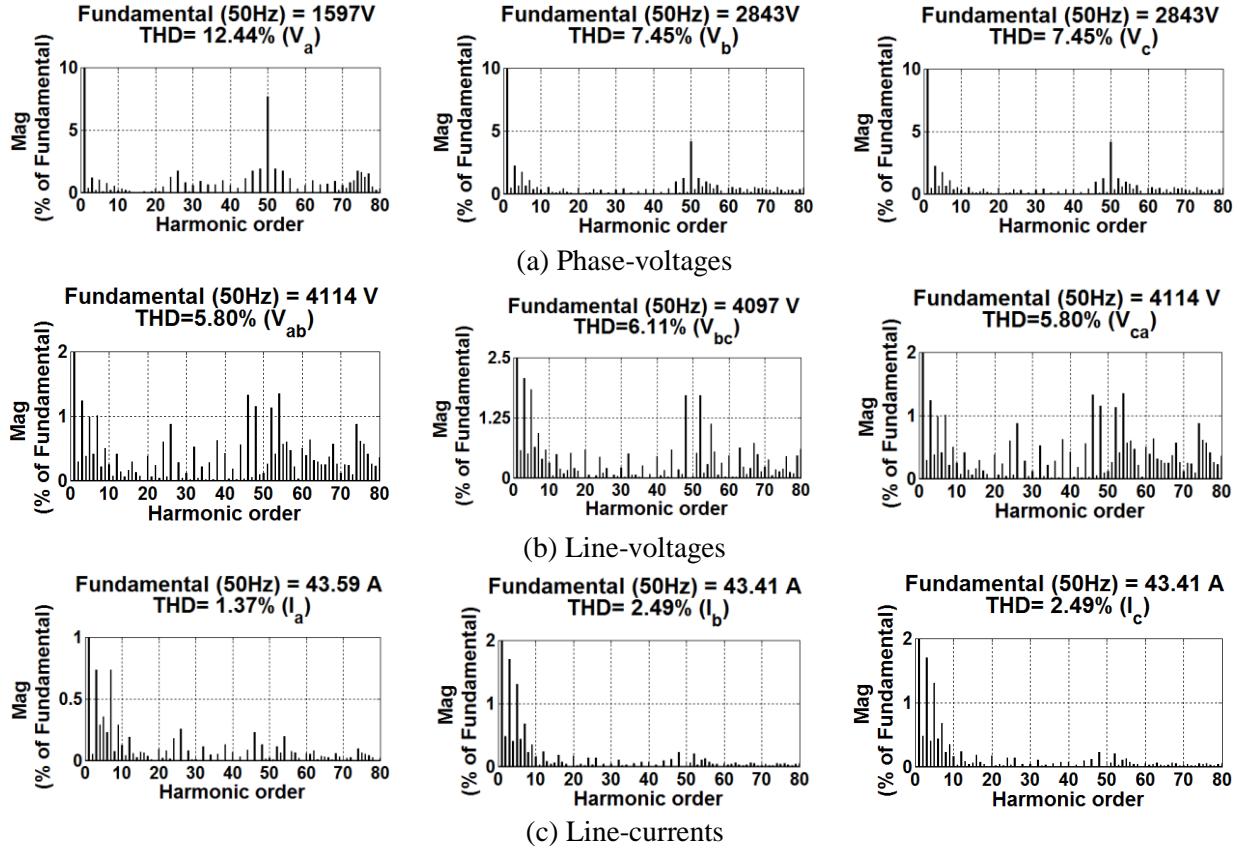

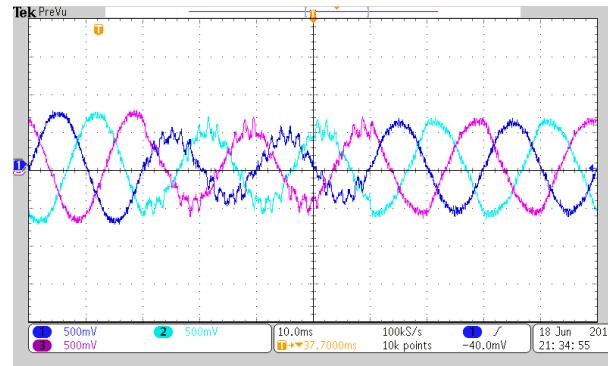

| Fig. 3.36: Experimental line-current performance of various RSC-MLI topologies.....                                                                     | 118 |

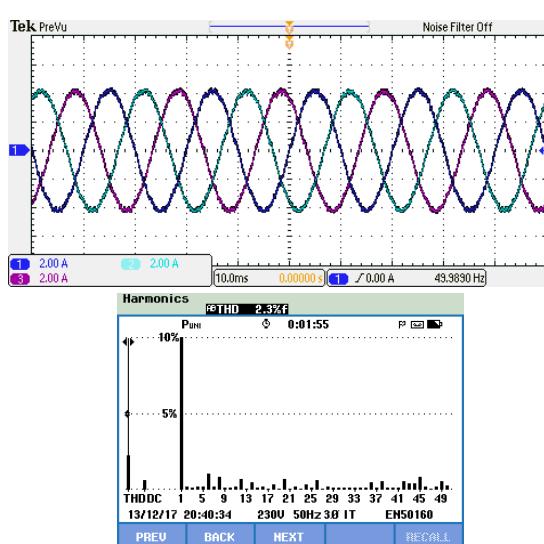

| Fig. 4.1: Generalized structure of MLDCL and its phasor diagram. ....                                                                                   | 124 |

| Fig. 4.2: Illustrating unbalanced operation under faulted condition. ....                                                                               | 126 |

| Fig. 4.3: Illustrating balanced condition with by-passing method. ....                                                                                  | 128 |

| Fig. 4.4: Illustrating fault compensation with increasing burden method. ....                                                                           | 129 |

|                                                                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.5: Implementation of NS-FTS for single unit fault on seven-level CHB MLI .....                                                                              | 130 |

| Fig. 4.6: NS zero-sequence injection FTS for single unit fault on CHB MLI.....                                                                                     | 132 |

| Fig. 4.7: Generalized NS zero-sequence injection FTS for $x$ faulty units in phase- $a$ .....                                                                      | 136 |

| Fig. 4.8: Generalized NS zero-sequence injection FTS for $x$ faulty units in phase- $a$ , and $y$ faulty units in phase- $b$ .....                                 | 136 |

| Fig. 4.9: Generalized NS zero-sequence injection FTS for $x$ faulty units in phase- $a$ , $y$ faulty units in phase- $b$ and, $z$ faulty units in phase- $c$ ..... | 137 |

| Fig. 4.10: Rotation of carriers in phase- $a$ of 15-level MLDCL under healthy operating condition .....                                                            | 141 |

| Fig. 4.11: Rotation of carriers in phase- $a$ of 15-level MLDCL under compensation of 1-0-0 fault.....                                                             | 141 |

| Fig. 4.12: Rotation of carriers in phase- $b$ of 15-level MLDCL under compensation of 1-0-0 fault.....                                                             | 142 |

| Fig. 4.13: Pre and post-fault performance of 15-level MLDCL for 1-0-0 fault with $m_a= 0.9$ . .....                                                                | 143 |

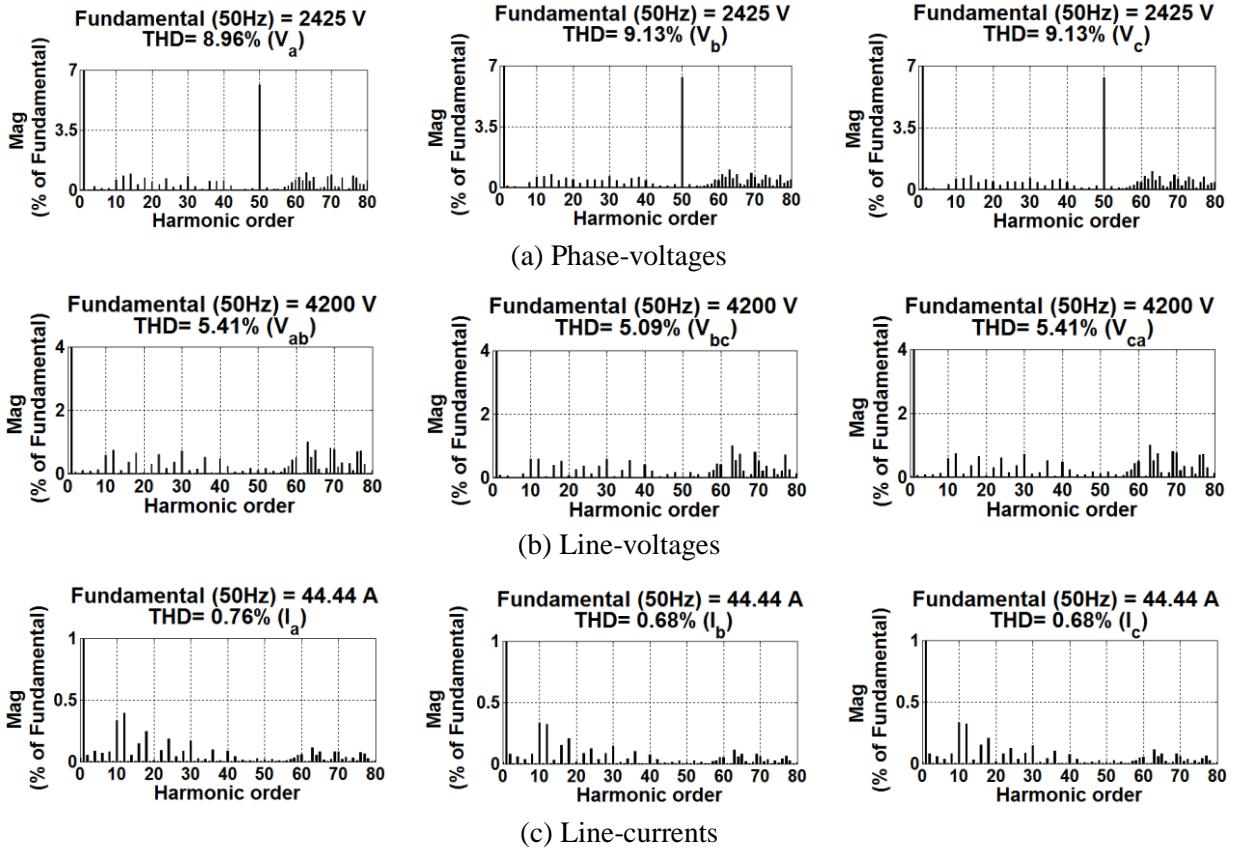

| Fig. 4.14: Harmonic performance of 15-level MLDCL inverter in healthy condition for $m_a= 0.9$ .....                                                               | 144 |

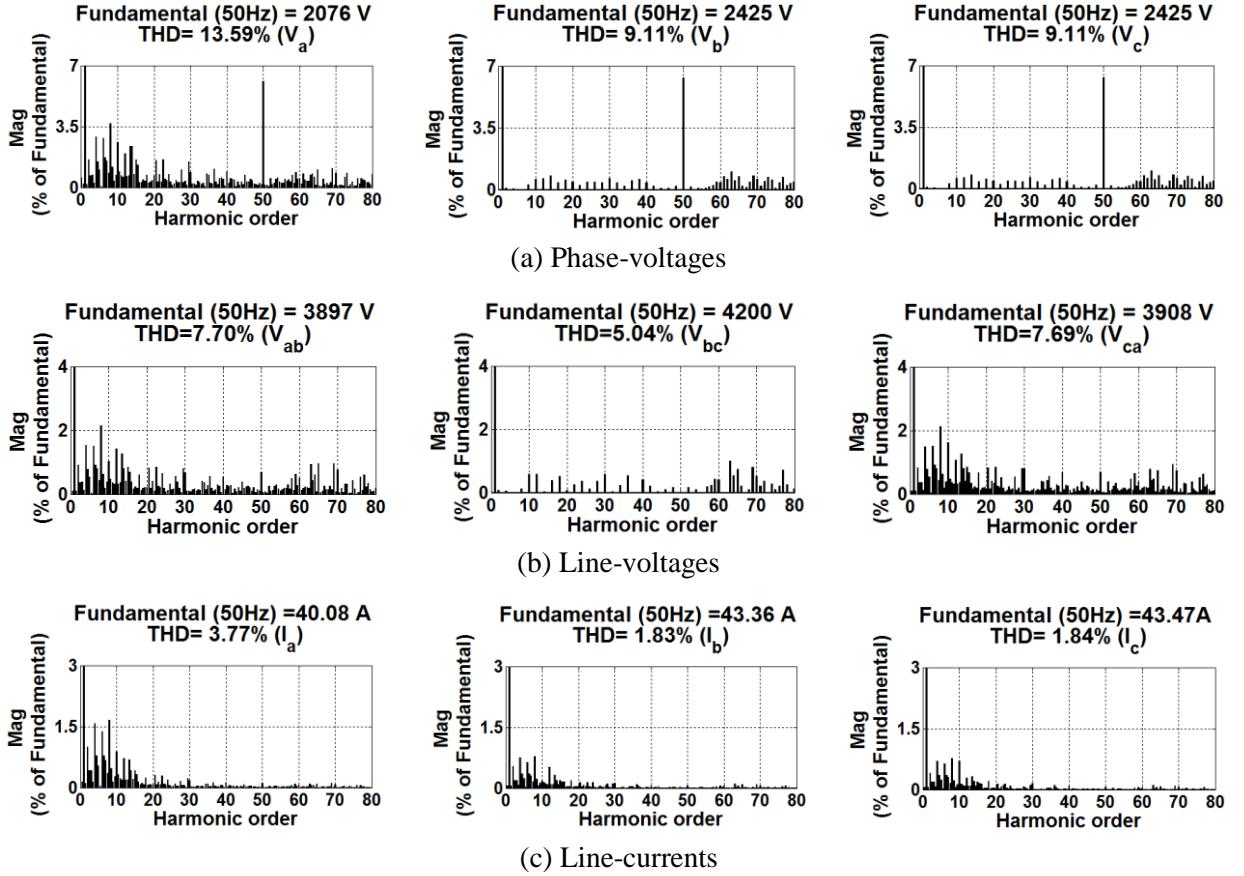

| Fig. 4.15: Harmonic performance of 15-level MLDCL inverter during 1-0-0 fault for $m_a= 0.9$ . .....                                                               | 145 |

| Fig. 4.16: Harmonic performance of 15-level MLDCL inverter after compensation of 1-0-0 fault with proposed FTS for $m_a= 0.9$ .....                                | 146 |

| Fig. 4.17: Pre and post-fault performance of 15-level MLDCL for 1-0-1 fault with $m_a= 0.9$ . .....                                                                | 147 |

| Fig. 4.18: Harmonic performance of 15-level MLDCL inverter after compensation of 1-0-1 fault with proposed FTS for $m_a= 0.9$ .....                                | 148 |

| Fig. 4.19: Pre and post-fault performance of 15-level MLDCL for 3-0-0 fault with $m_a= 0.9$ . .....                                                                | 150 |

| Fig. 4.20: Harmonic performance of 15-level MLDCL inverter after compensation of 3-0-0 fault with proposed FTS for $m_a= 0.9$ .....                                | 151 |

| Fig. 4.21: Pre and post-fault performance of 15-level MLDCL for 3-0-0 fault with $m_a= 0.8$ . .....                                                                | 152 |

| Fig. 4.22: Harmonic performance of 15-level MLDCL inverter after compensation of 3-0-0 fault with proposed FTS for $m_a= 0.8$ .....                                | 153 |

| Fig. 4.23: Pre and post-fault performance of 15-level MLDCL for 3-0-1 fault with $m_a= 0.9$ . .....                                                                | 155 |

|                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.24: Pre and post-fault performance of 15-level MLDCL for 3–0–1 fault with $m_a= 0.8$ .                                   | 156 |

| Fig. 4.25: Harmonic performance of 15-level MLDCL inverter after compensation of 3–0–1 fault with proposed FTS for $m_a= 0.8$ . | 157 |

| Fig. 4.26: Pre and post-fault performance of 15-level MLDCL for 2–3–1 fault with $m_a= 0.9$ .                                   | 159 |

| Fig. 4.27: Pre and post-fault performance of 15-level MLDCL for 2–3–1 fault with $m_a= 0.7$ .                                   | 160 |

| Fig. 4.28: Harmonic performance of 15-level MLDCL inverter after compensation of 2–3–1 fault with proposed FTS for $m_a= 0.7$ . | 161 |

| Fig. 4.29: Pre and post-fault performance of nine-level MLDCL inverter for 1–0–0 fault with $m_a= 0.9$ .                        | 164 |

| Fig. 4.30: Harmonic performance of nine-level MLDCL inverter in healthy condition for $m_a= 0.9$ .                              | 164 |

| Fig. 4.31: Harmonic performance of nine-level MLDCL after compensation of 1–0–0 fault for $m_a= 0.9$ .                          | 165 |

| Fig. 4.32: Pre and post-fault performance of nine-level MLDCL inverter for 2–1–0 fault with $m_a= 0.9$ .                        | 167 |

| Fig. 4.33: Harmonic performance of nine-level MLDCL, after compensation of 2–1–0 fault for $m_a= 0.9$ .                         | 167 |

| Fig. 4.34: Pre and post-fault performance of nine-level MLDCL inverter with 2–1–0 fault for $m_a= 0.7$ .                        | 168 |

| Fig. 4.35: Harmonic performance of nine-level MLDCL, after compensation of 2–1–0 fault for $m_a= 0.7$ .                         | 168 |

| Fig. 4.36: Pre and post-fault performance of nine-level MLDCL inverter for 2–1–1 fault with $m_a= 0.9$ .                        | 170 |

| Fig. 4.37: Pre and post-fault performance of nine-level MLDCL inverter for 2–1–1 fault with $m_a= 0.7$ .                        | 170 |

| Fig. 4.38: Harmonic performance of nine-level MLDCL inverter, after compensation of 2–1–1 fault for $m_a= 0.7$ .                | 171 |

| Fig. 5.1: Single-phase equivalent model of VSR in voltage controlled mode.                                                      | 178 |

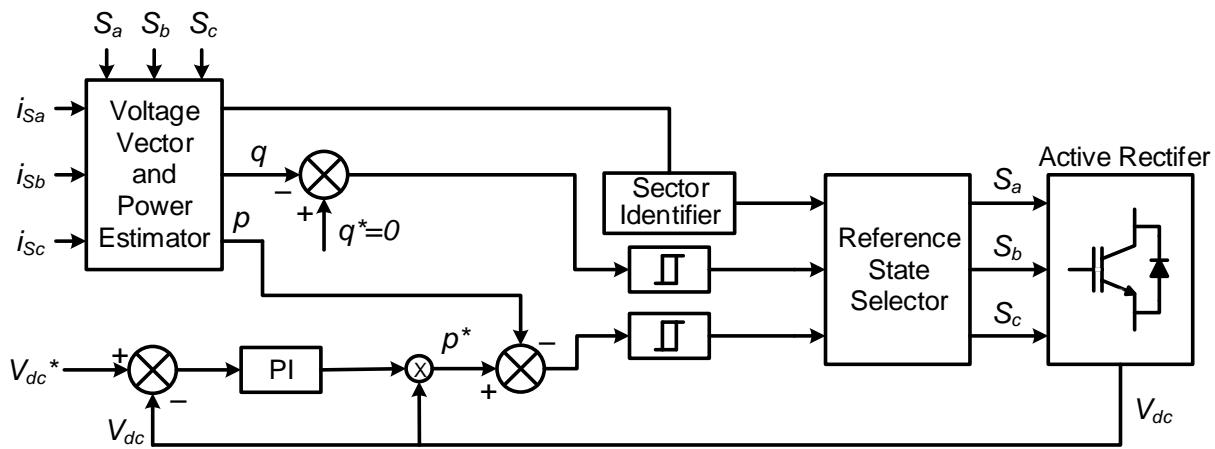

| Fig. 5.2: Schematic diagram of DPC control algorithm.                                                                           | 180 |

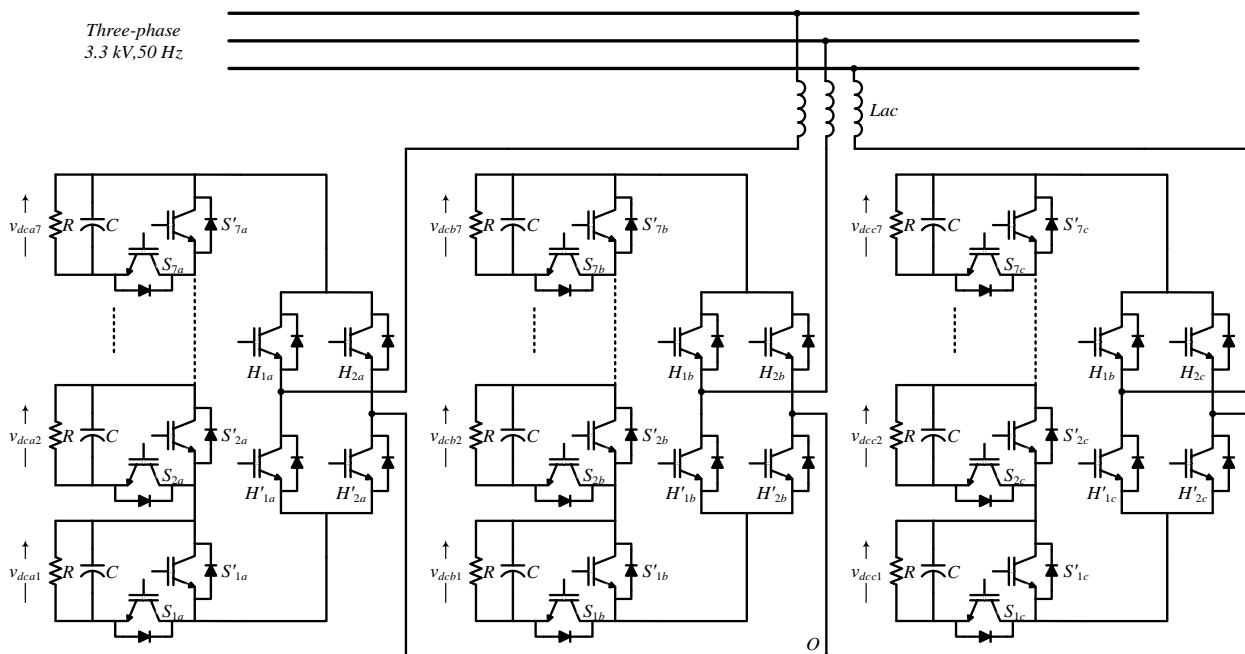

| Fig. 5.3: Circuit configuration of three-phase MLDCL based active rectifier.                                                    | 182 |

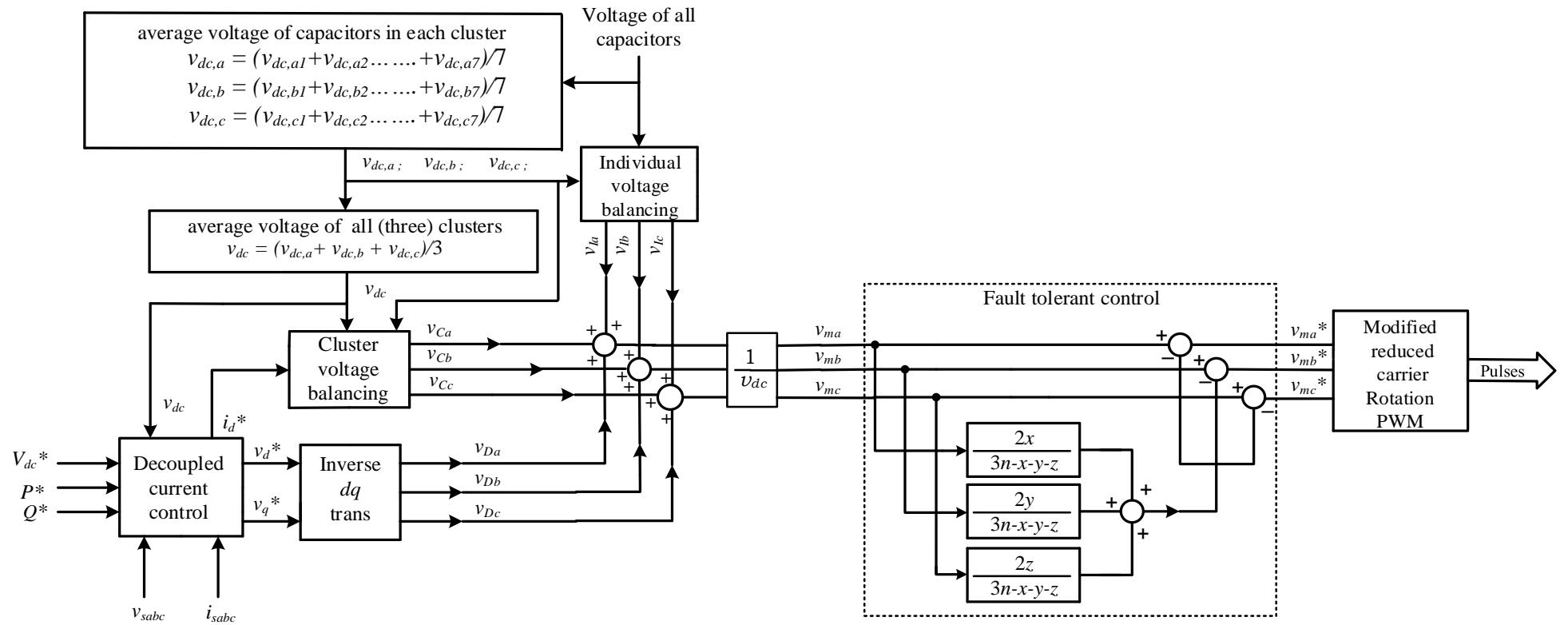

| Fig. 5.4: Block diagram of proposed comprehensive control.                                                                      | 187 |

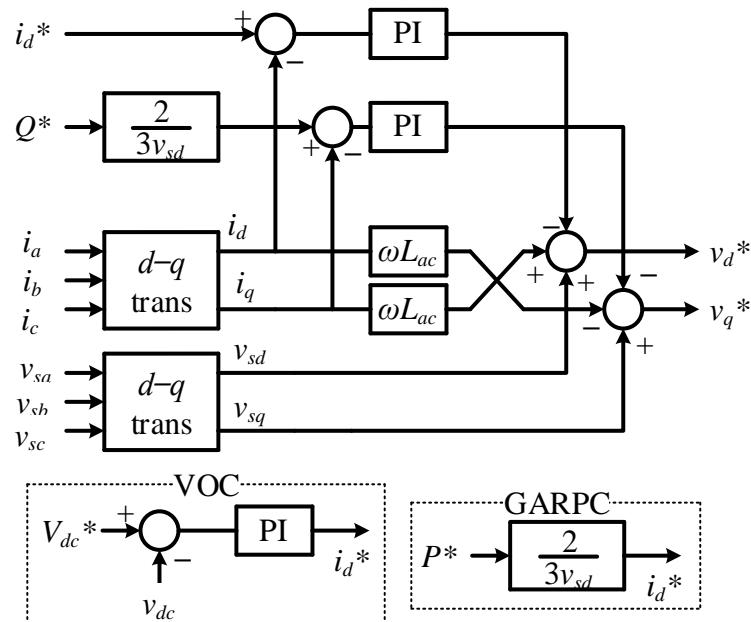

| Fig. 5.5: Schematic diagram of decoupled current controller.                                                                    | 188 |

|                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

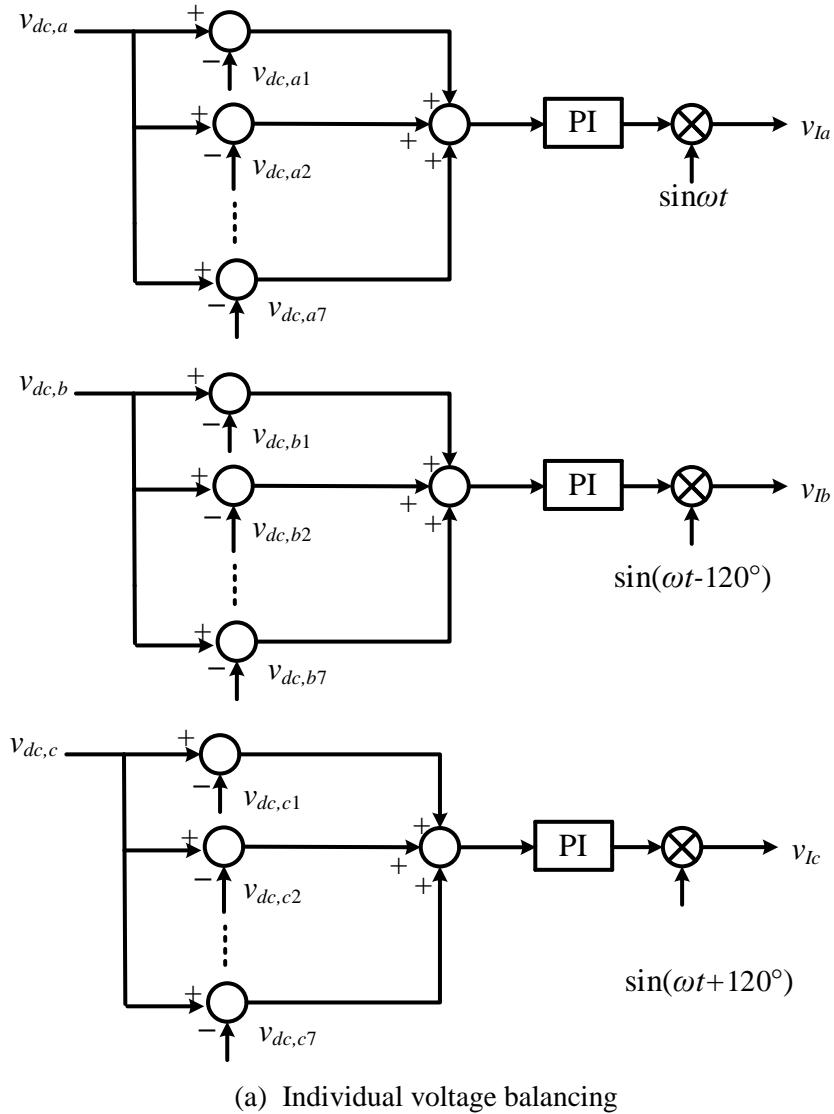

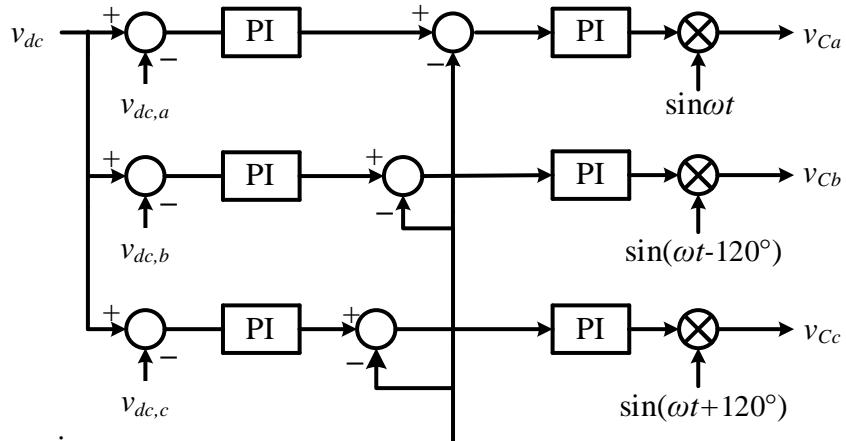

| Fig. 5.6: Block diagrams of individual and cluster voltage balancing controllers.....                              | 190 |

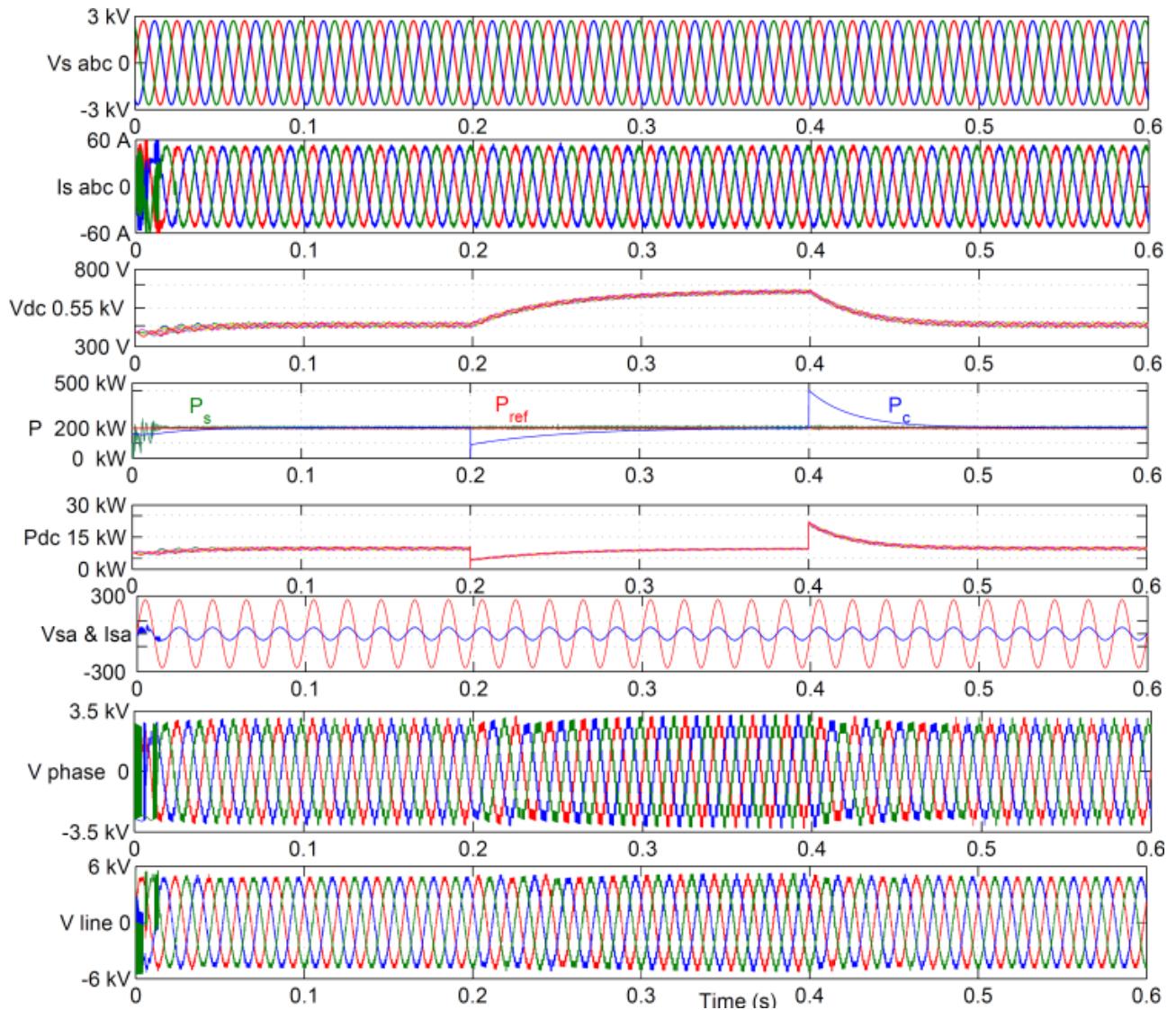

| Fig. 5.7: Performance of MLDCL based active rectifier with VOC for dynamic variation of load.....                  | 194 |

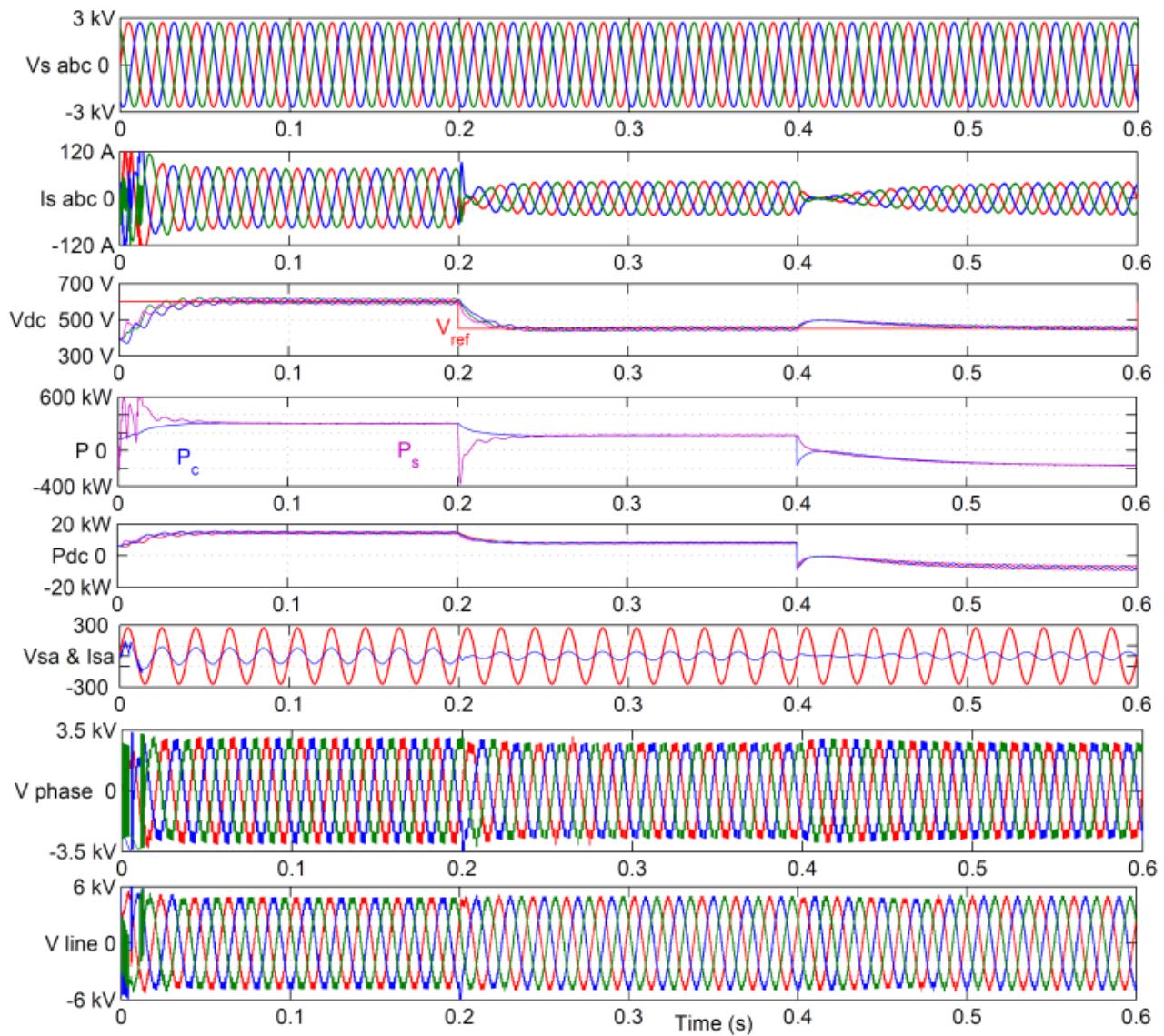

| Fig. 5.8: Performance of MLDCL based active rectifier with VOC for dynamic variation of reference variable.....    | 195 |

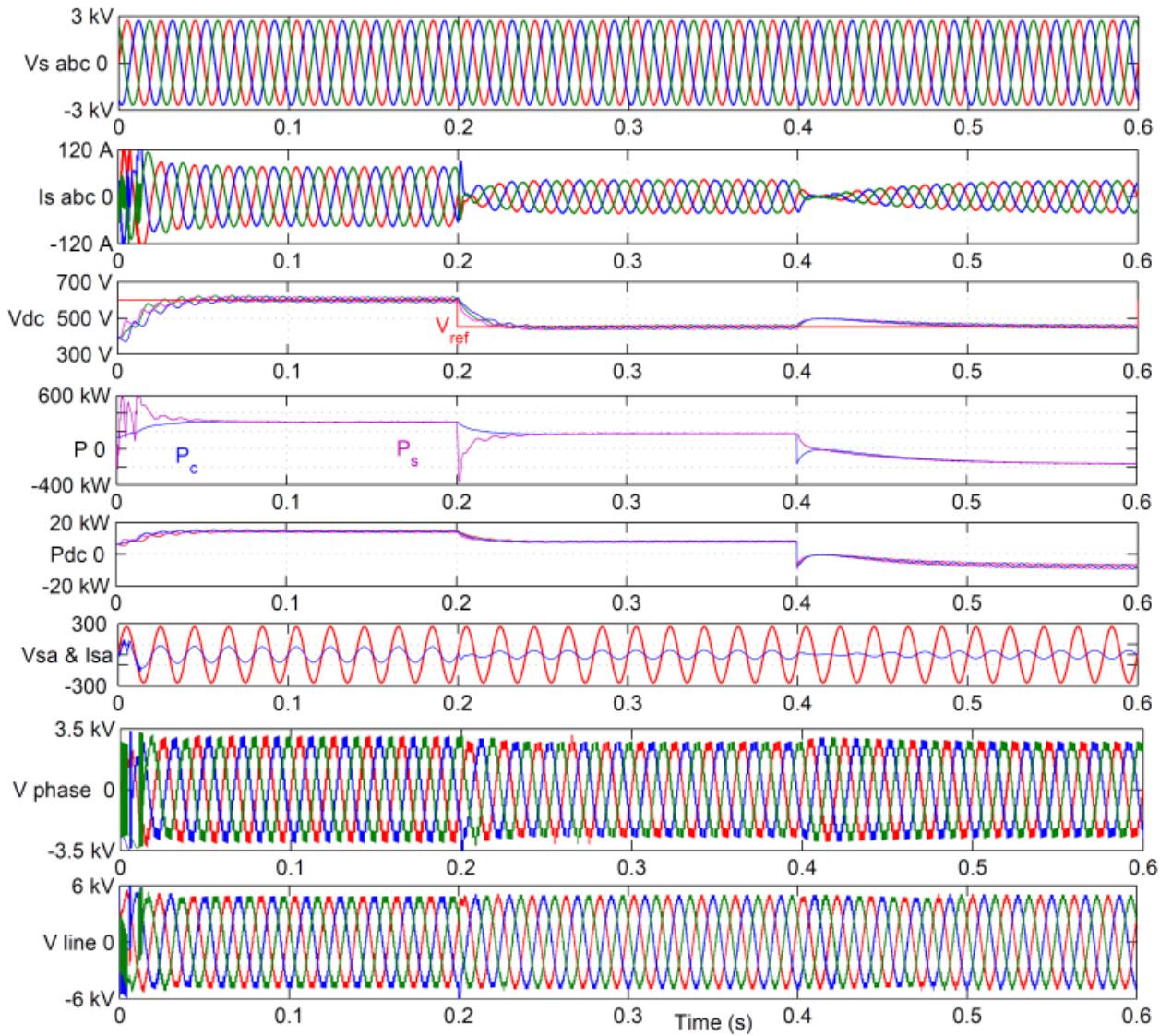

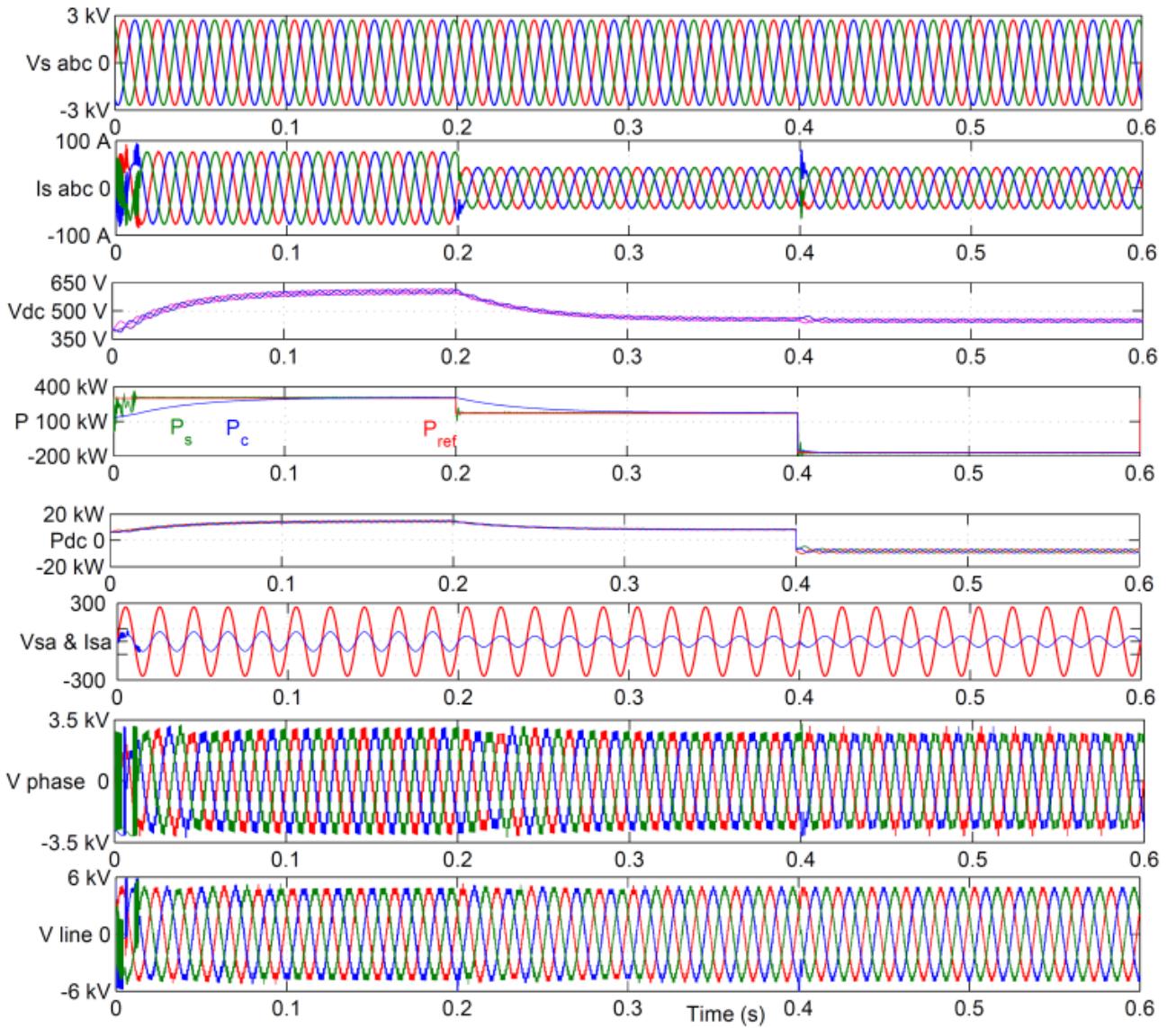

| Fig. 5.9: Performance of 15-level MLDCL based active rectifier with GARPC for dynamic variation in load.....       | 196 |

| Fig. 5.10: Performance of MLDCL based active rectifier with GARPC for dynamic variation in reference variable..... | 197 |

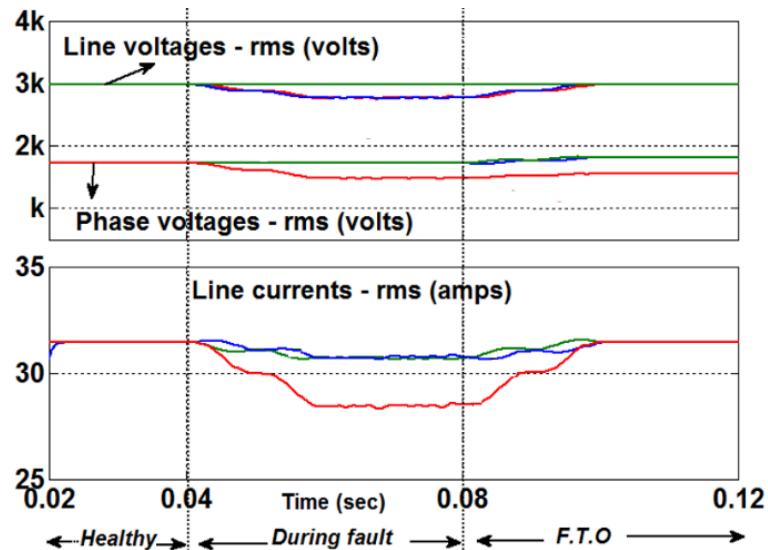

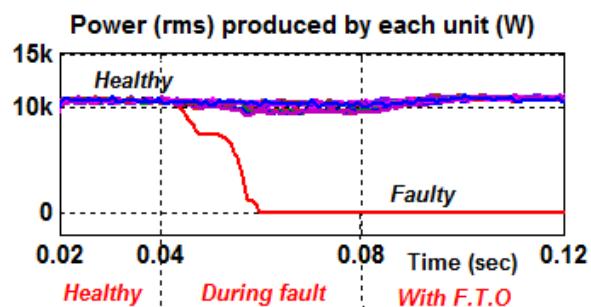

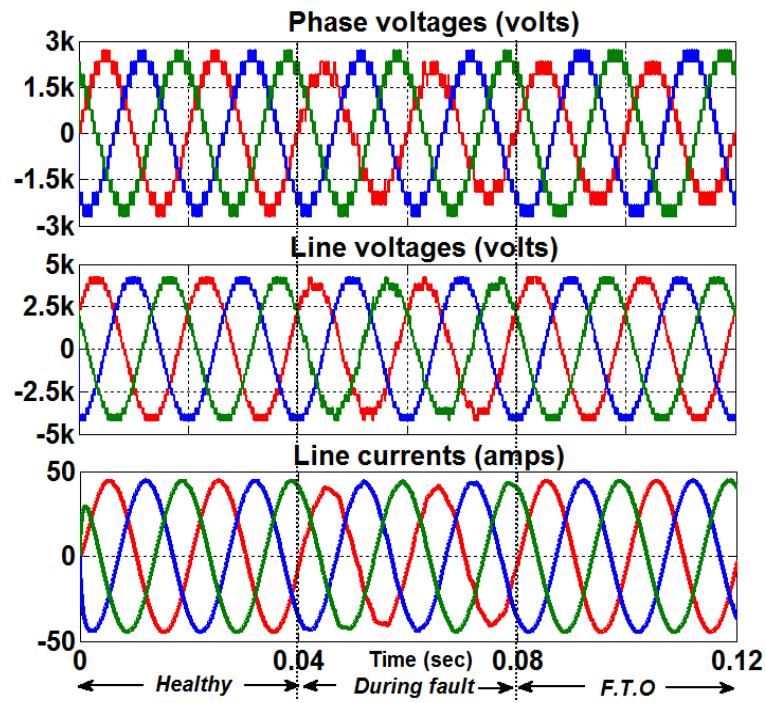

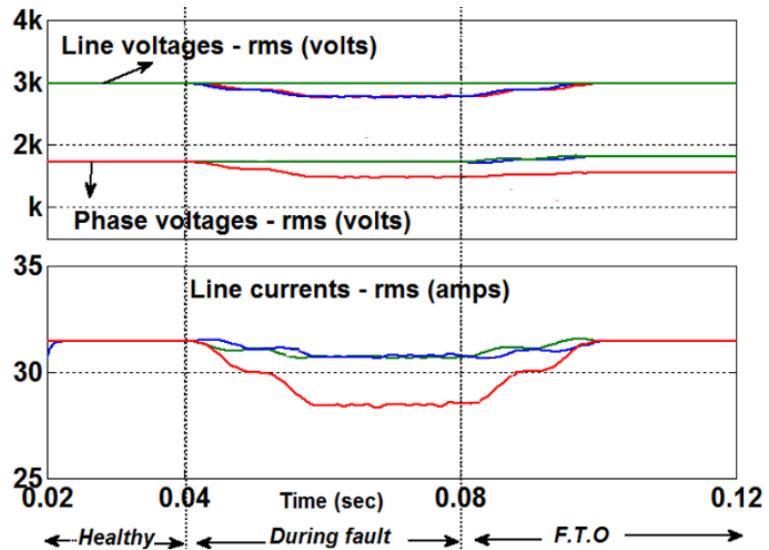

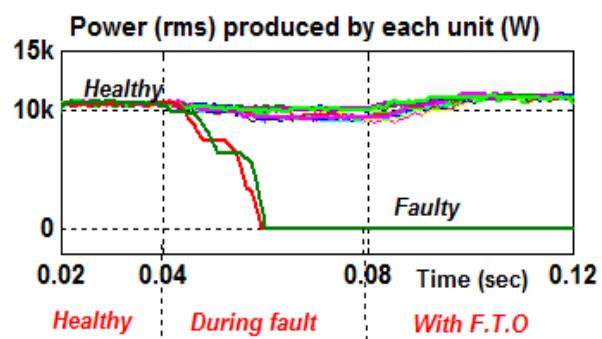

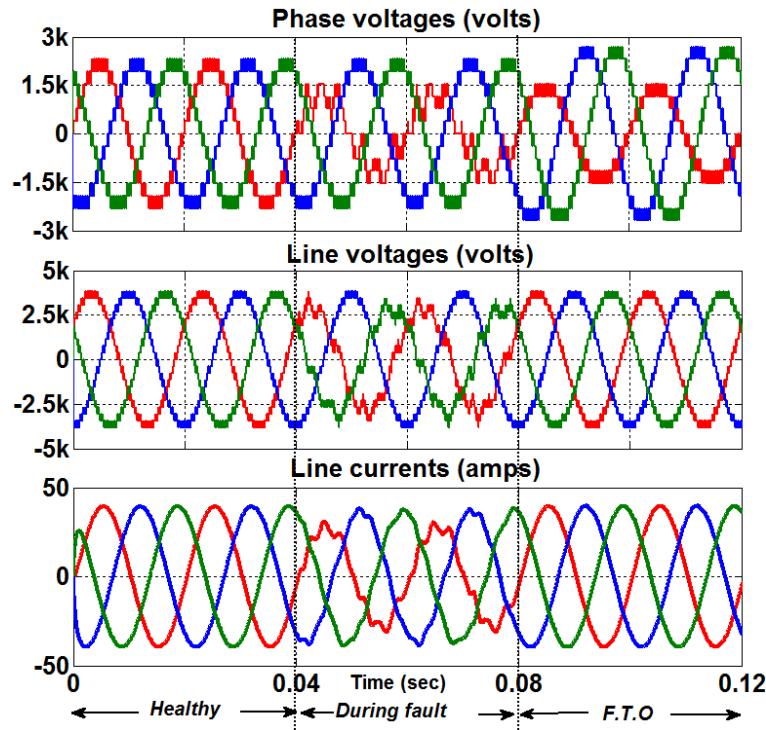

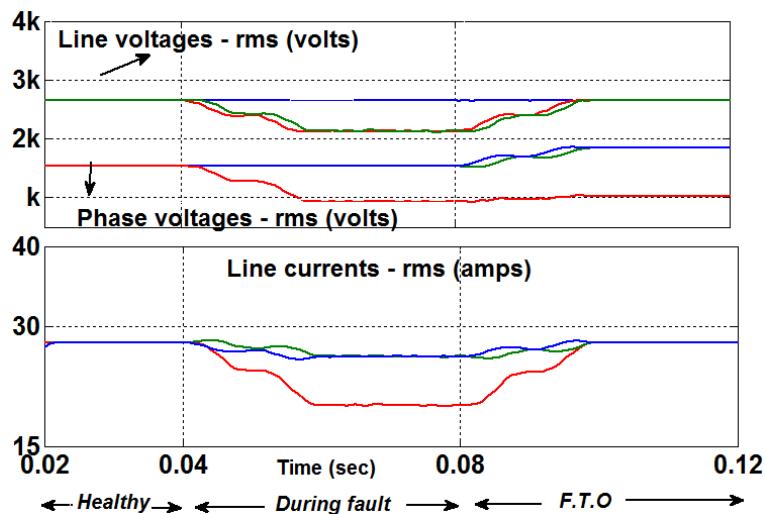

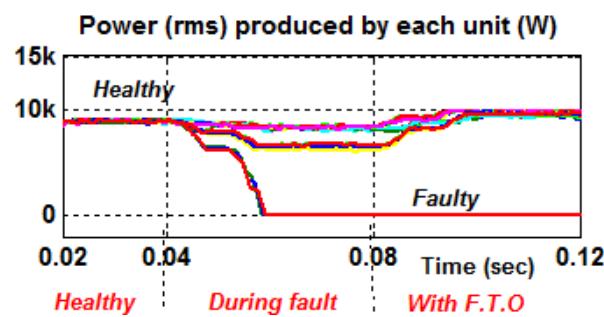

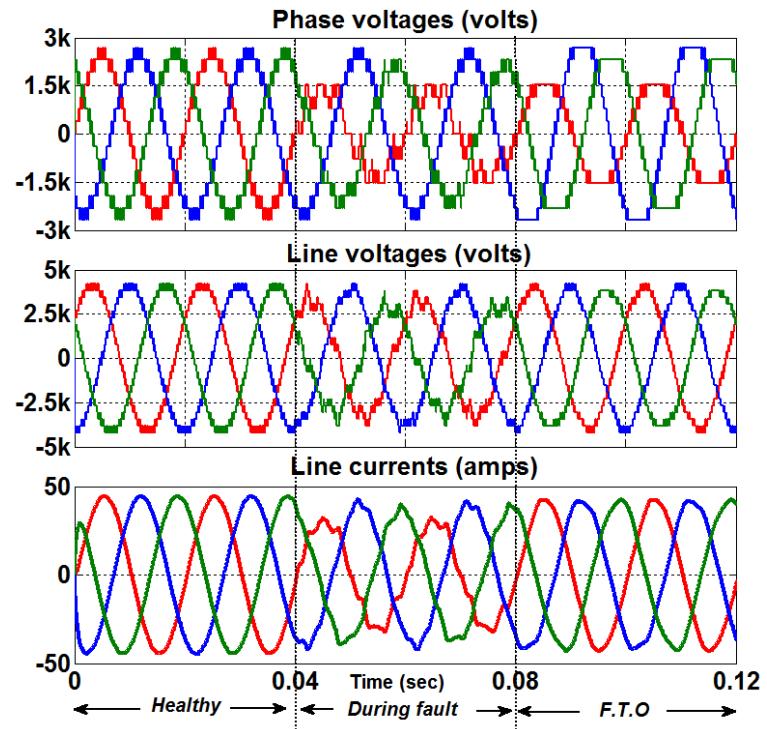

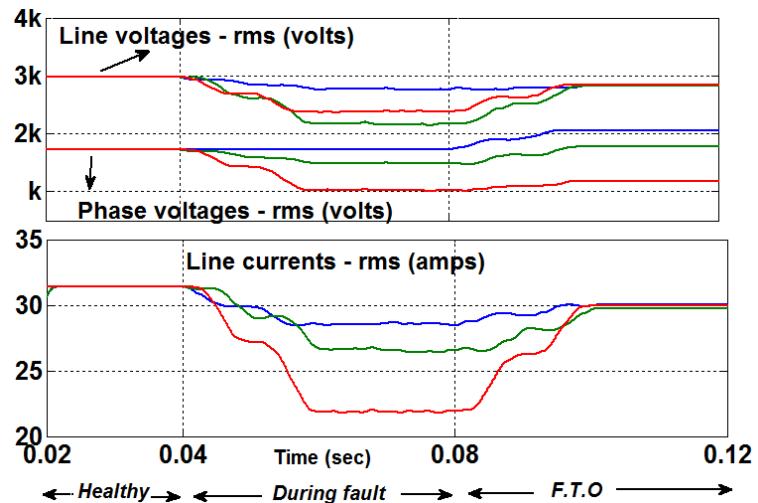

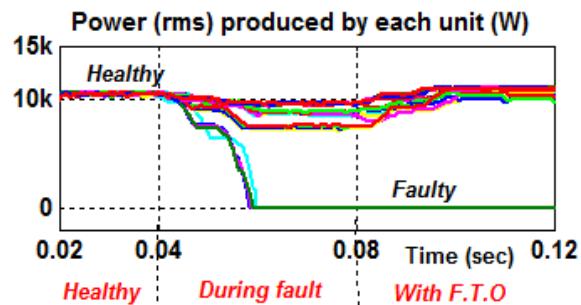

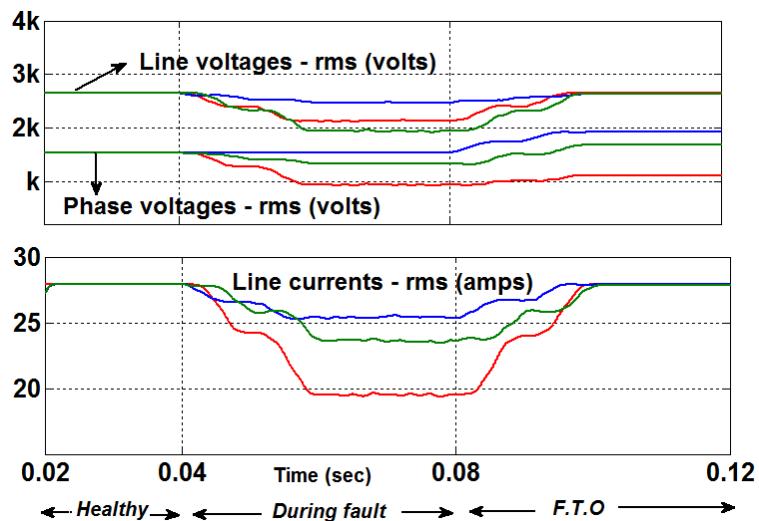

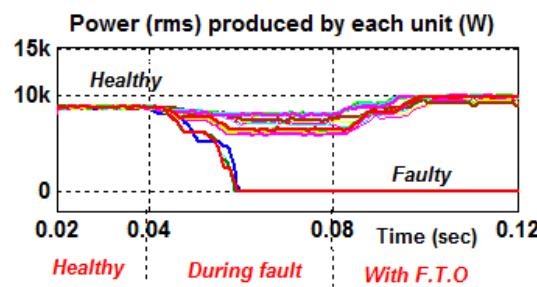

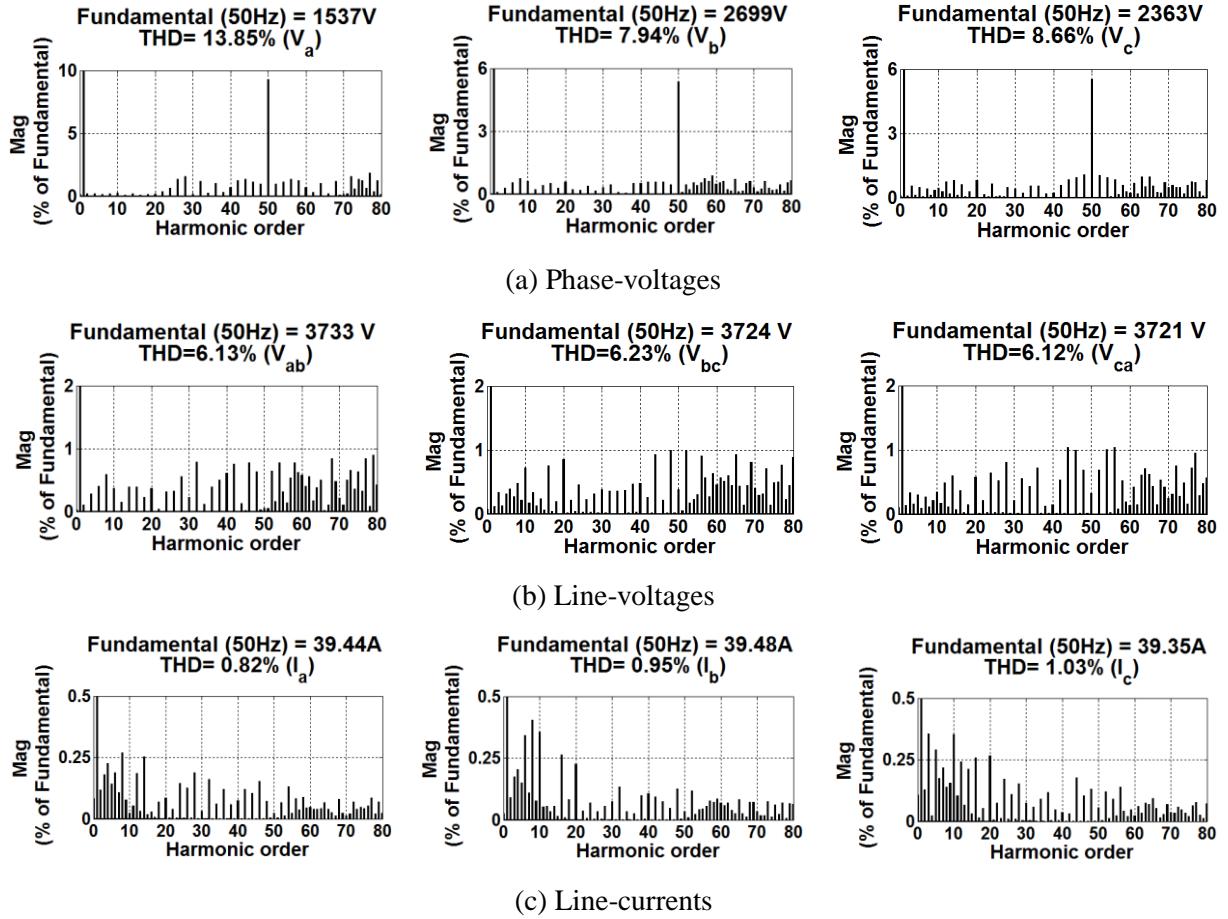

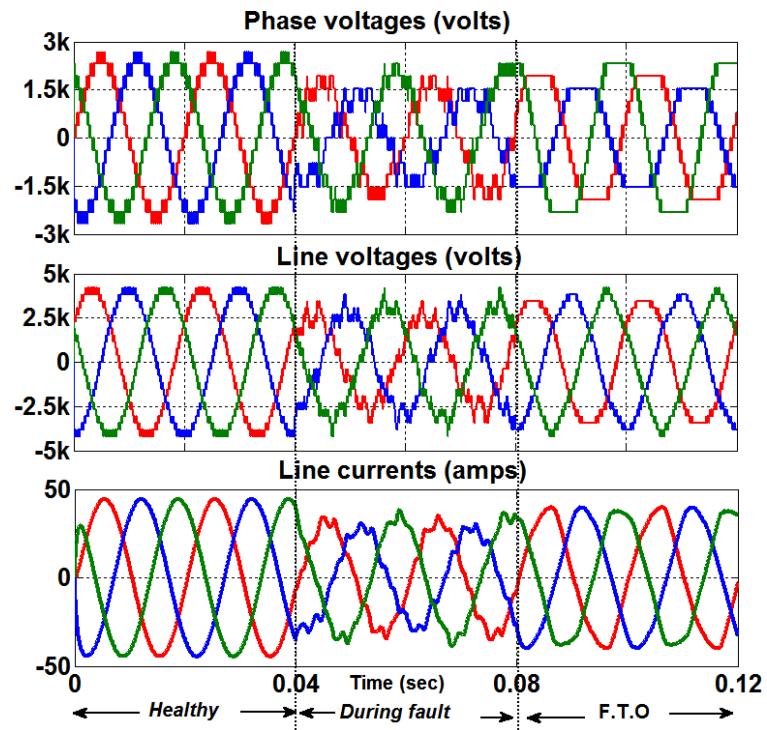

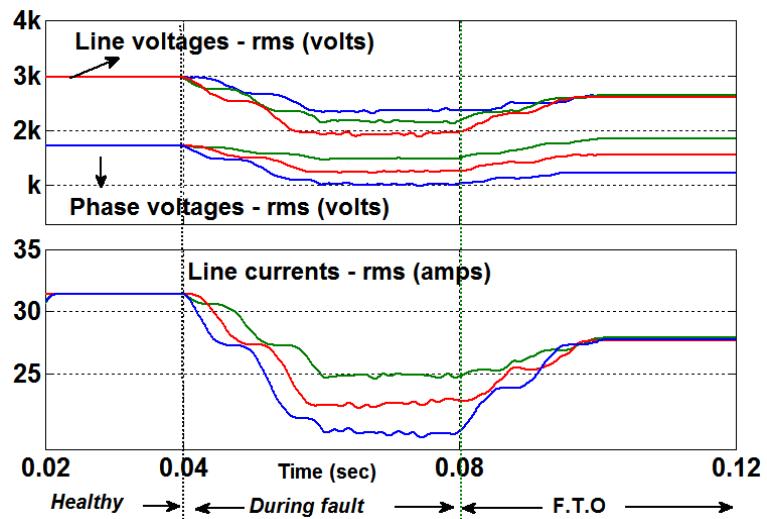

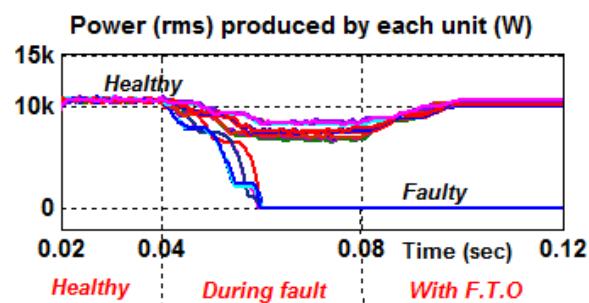

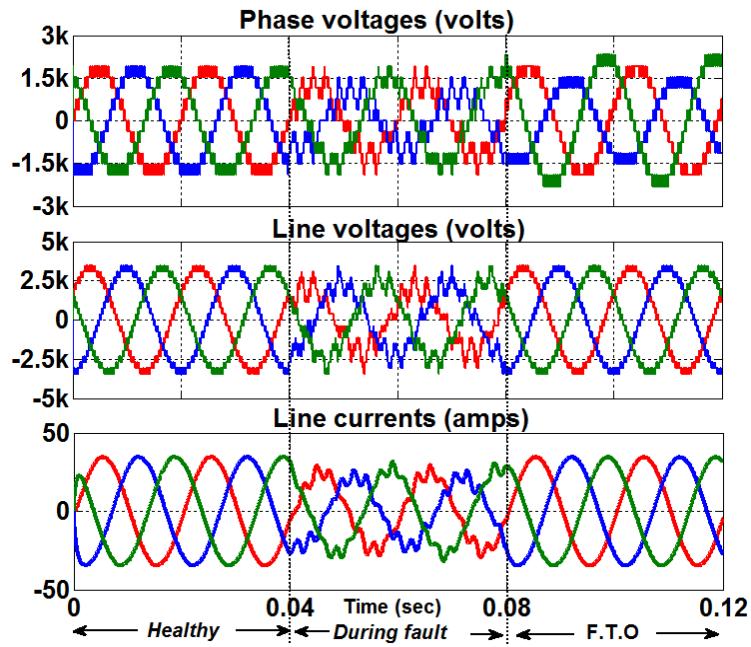

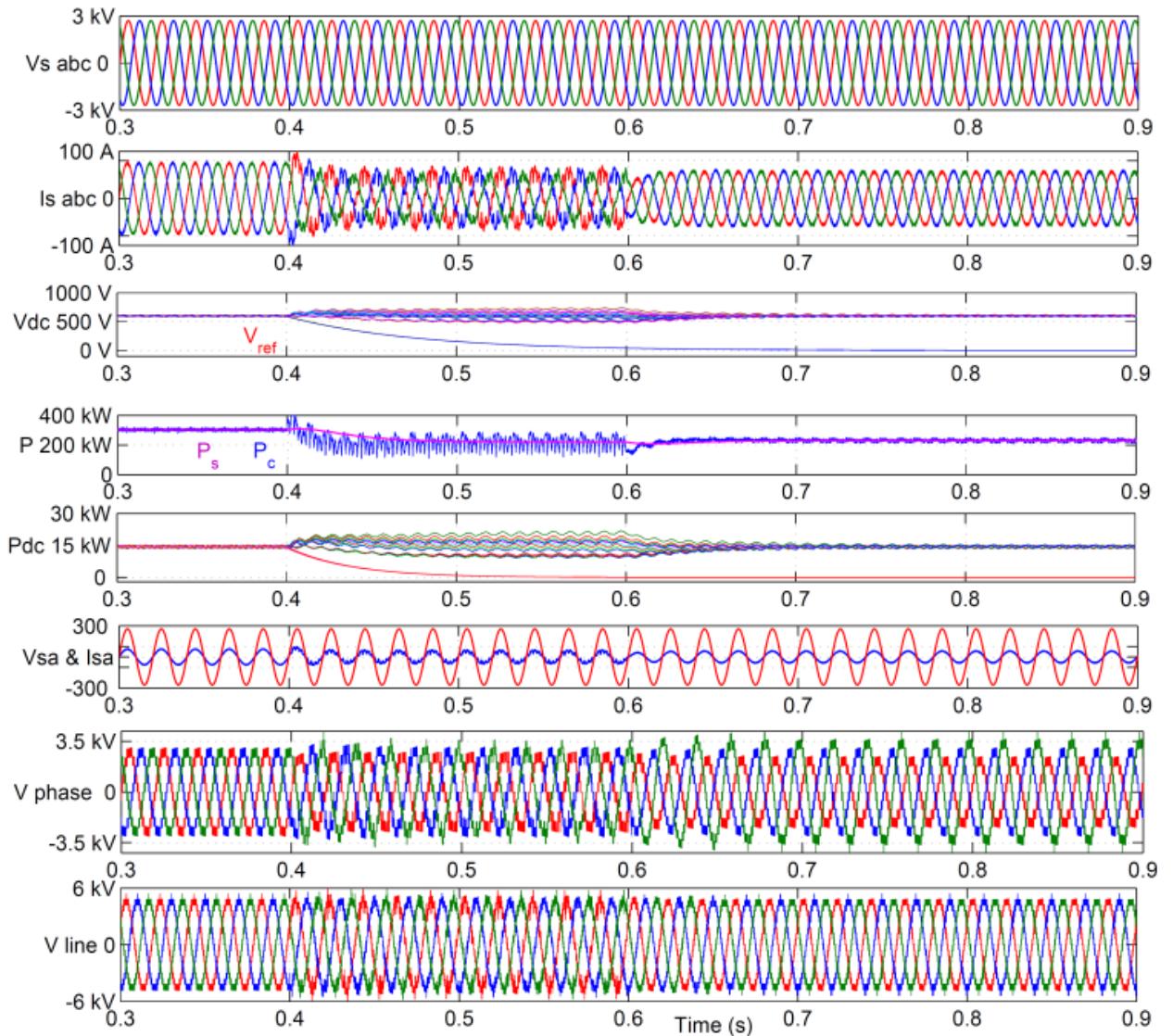

| Fig. 5.11: Pre and post-fault performance of MLDCL based active rectifier with VOC algorithm.....                  | 199 |

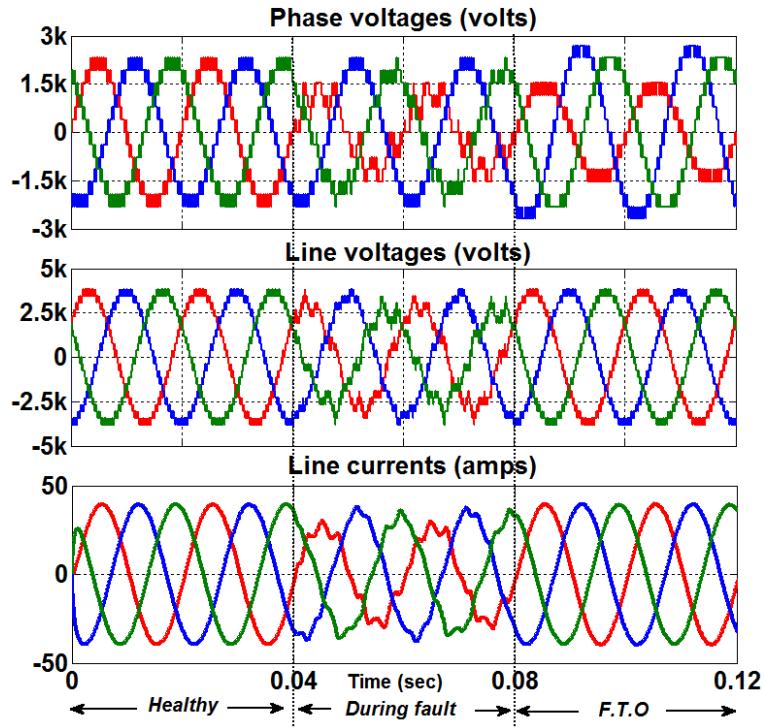

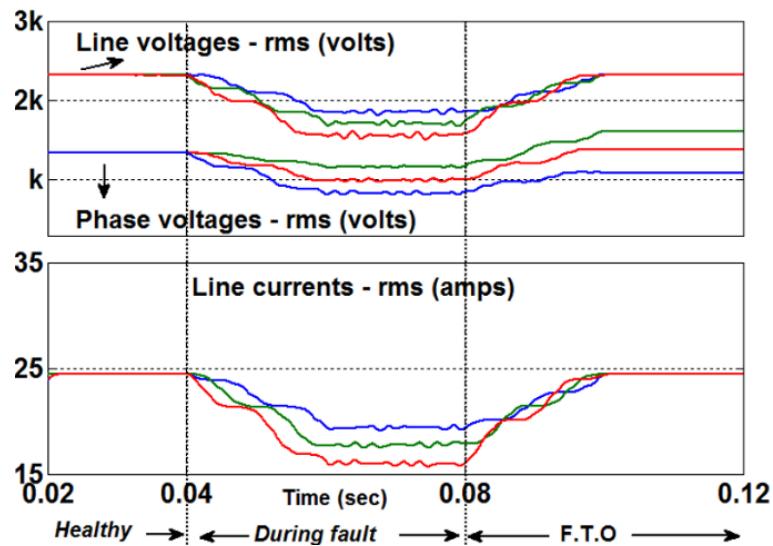

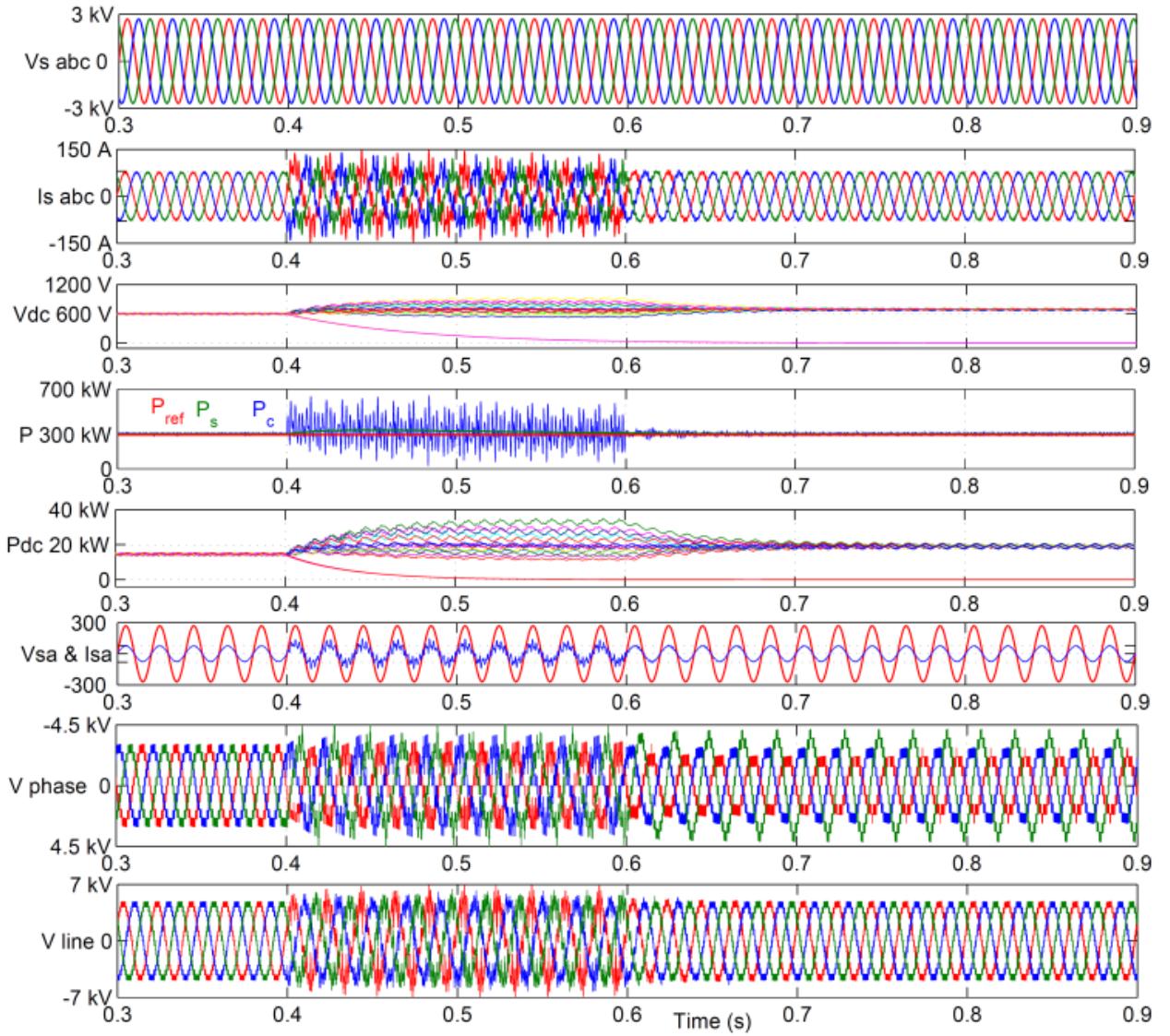

| Fig. 5.12: Pre and post-fault performance of MLDCL based active rectifier involving GARPC algorithm.....           | 201 |

---

## LIST OF TABLES

---

|                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| Table 1.1: Comparison of per phase-leg component requirement of classical MLI topologies.                       | 12 |

| Table 1.2: Comparison of classical MLI topologies based on implementation factors .....                         | 12 |

| Table 2.1: Required switching combinations for even power distribution with three dc sources.                   | 22 |

| Table 2.2: Switching states of MLDCL inverter.....                                                              | 25 |

| Table 2.3: Switching states of SSPS inverter.....                                                               | 26 |

| Table 2.4: Switching states of RV inverter .....                                                                | 28 |

| Table 2.5: Switching states of seven-level SCSS topology .....                                                  | 29 |

| Table 2.6: Switching states of seven-level T-type RSC-MLI.....                                                  | 30 |

| Table 2.7: Switching states of three-level half-leg T-type RSC-MLI.....                                         | 31 |

| Table 2.8: Switching states of cascaded T-type RSC-MLI.....                                                     | 33 |

| Table 2.9: Switching states of MLM based RSC-MLI .....                                                          | 34 |

| Table 2.10: Switching states of hybrid T-Type topology – I .....                                                | 36 |

| Table 2.11: Switching states of hybrid T-type topology – II .....                                               | 40 |

| Table 2.12: Switching states of CBSC RSC-MLI.....                                                               | 41 |

| Table 2.13: Switching states of basic unit RSC-MLI .....                                                        | 43 |

| Table 2.14: Switching states in a single unit of E-type RSC-MLI .....                                           | 46 |

| Table 2.15: Switching states in a unit of Square T-type (ST-Type) RSC-MLI .....                                 | 48 |

| Table 2.16: Switching states of five-level cascaded MLI toplogy – II .....                                      | 50 |

| Table 2.17: Switching states of H-bridge based basic unit .....                                                 | 52 |

| Table 2.18: Switching states of spilt capacitor unit RSC-MLI .....                                              | 53 |

| Table 2.19: Switching states in phase- <i>a</i> of four-level nested RSC-MLI .....                              | 56 |

| Table 2.20: Switching states in phase- <i>a</i> of five-level nested RSC-MLI.....                               | 57 |

| Table 2.21: Switching operation of SDS RSC-MLI .....                                                            | 58 |

| Table 2.22: Switching states of PUC topology.....                                                               | 59 |

| Table 2.23: Switching states of Topology – I for three-level pole-voltage. ....                                 | 61 |

| Table 2.24: Switching states of five-level three-phase RSC-MLIs. ....                                           | 63 |

| Table 2.25: Comparison of device count and salient features of RSC-MLIs topologies reported in literature. .... | 65 |

| Table 3.1: Switching states of five-level T-type RSC-MLI.....                                                   | 79 |

| Table 3.2: Experimental parameters. ....                                                                        | 83 |

| Table 3.3: Summary of various RSC-MLI and their reported modulation schemes. ....                               | 90 |

|                                                                                                                                                  |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.4: Implementation of the proposed switching logic to control seven-level asymmetrical MLDCL RSC-MLI.....                                 | 106 |

| Table 3.5: Implementation of the proposed scheme to control thirteen-level asymmetrical RSC-MLIs.....                                            | 109 |

| Table 3.6: Simulation parameters.....                                                                                                            | 110 |

| Table 3.7: Experimental parameters.....                                                                                                          | 114 |

| Table 3.8: Simulink and experimental performance of the proposed modified reduced carrier PWM on thirteen-level asymmetrical RSC-MLIs.....       | 119 |

| Table 3.9: Performance comparison of proposed unified logic PWM with conventional PWM schemes of RSC-MLI.....                                    | 121 |

| Table 4.1: Effect of Type-1 fault on phase-voltage levels. ....                                                                                  | 125 |

| Table 4.2: Effect on Type-2 fault on phase-voltage levels.....                                                                                   | 126 |

| Table 4.3: RMS values of phase and line-voltages for various fault conditions after fault compensation.....                                      | 162 |

| Table 4.4: Experimental parameters.....                                                                                                          | 162 |

| Table 4.5: Comparison of simulation and experimental studies of the proposed FTS on nine-level MLDCL inverter for various fault conditions. .... | 173 |

| Table 5.1: Simulation parameters.....                                                                                                            | 192 |

---

## LIST OF ACRONYMS

---

|          |                                                    |

|----------|----------------------------------------------------|

| RSC-MLI  | Reduced Switch Count Multilevel Inverter           |

| CSI      | Current Source Inverter                            |

| VSI      | Voltage Source Inverter                            |

| VSR      | Voltage Source Rectifier                           |

| ac, AC   | Alternating Current                                |

| dc, DC   | Direct Current                                     |

| DCMLI    | Diode Clamped Multilevel Inverter                  |

| CHB      | Cascade H-bridge                                   |

| FCMLI    | Flying Capacitor Multilevel Inverter               |

| AFC      | Active Front-end Converter                         |

| ASD      | Adjustable Speed Drive                             |

| HEV      | Hybrid Electric Vehicle                            |

| THD      | Total Harmonic Distortion                          |

| pf, PF   | Power Factor                                       |

| IGBT     | Insulated Gate Bipolar Transistor                  |

| PWM      | Pulsewidth Modulation                              |

| LSPWM    | Level-shifted Pulsewidth Modulation                |

| PSPWM    | Phase-shifted Pulsewidth Modulation                |

| PI       | Proportional and Integral                          |

| rms, RMS | Root Mean Square                                   |

| RSC      | Reduced Switch Count                               |

| MLDCL    | Multilevel dc-link (RSC-MLI topology)              |

| SDS      | Switched dc-sources (RSC-MLI topology)             |

| CBSC     | Cascaded Bi-polar Switched Cell (RSC-MLI topology) |

| MLM      | Multilevel Module (RSC-MLI topology)               |

| E-type   | Envelope Type (RSC-MLI topology)                   |

| DPC      | Direct Power Control                               |

| VOC      | Voltage Oriented Control                           |

| GARPC    | Grid Active Reactive Power Control                 |

| FTS      | Fault Tolerant Scheme                              |

| FTO      | Fault Tolerant Operation                           |

| NS       | Neutral Shifting                                   |

| OC, oc   | Open-Circuit                                       |

| SC, sc   | Short-Circuit                                      |

## LIST OF SYMBOLS

---

|                                                 |                                                           |

|-------------------------------------------------|-----------------------------------------------------------|

| $n$                                             | Number of dc voltage sources per phase                    |

| $m$                                             | Number of levels in phase-voltage of inverter             |

| $f_{cr}$                                        | Carrier signal frequency                                  |

| $f_m$                                           | Modulating signal frequency                               |

| $m_a$                                           | Amplitude modulation index                                |

| $m_f$                                           | Frequency modulation index                                |

| $x$                                             | Number of OC switch faults in phase- $a$                  |

| $y$                                             | Number of OC switch faults in phase- $b$                  |

| $z$                                             | Number of OC switch faults in phase- $c$                  |

| $v_{sabc}$                                      | Three-phase supply voltages                               |

| $i_{sabc}$                                      | Three-phase source currents                               |

| $V_m$                                           | Peak value of modulating signal                           |

| $V_c$                                           | Peak value of carrier signal                              |

| $v_a'', v_b''$ and $v_c''$                      | Post-fault phase-voltages                                 |

| $v_a', v_b'$ and $v_c'$                         | Burdened balanced Phase-voltages                          |

| $v_{Da}, v_{Db}$ and $v_{Dc}$                   | Output signals of decoupled current control block         |

| $v_{Ca}, v_{Cb}$ and $v_{Cc}$                   | Output signals of cluster voltage balancing controller    |

| $v_{Ia}, v_{Ib}$ and $v_{Ic}$                   | Output signals of Individual voltage balancing controller |

| $v_{ma}, v_{mb}$ and $v_{mc}$                   | Normalized modulating signals                             |

| $v_{ma}^*, v_{mb}^*$ and $v_{mc}^*$             | fault tolerant modulating signals                         |

| $v_{dc}$                                        | Mean dc link voltage of all capacitors                    |

| $P^*$                                           | Reference power (total active power demand) in GARPC      |

| $V^*$                                           | Reference voltage (voltage of each dc-link) in VOC        |

| $v_{dca1.3..7}; v_{dcb1.3..7}; v_{dcc1..3..7};$ | Instantaneous voltage of each dc link capacitor           |

| $v_{dca}, v_{dcb}$ and $v_{dcc}$                | Mean voltage of each cluster                              |

# CHAPTER 1: HIGH POWER DC-AC CONVERTERS

*This chapter presents literature survey on dc-ac power converters for high-power medium-voltage applications. It starts with brief background on dc-ac power converters and then discusses the prominence of multilevel inverters (MLIs). Further, investigates the limitations of classical topologies of MLIs and then demonstrates the significance of reduced switch count (RSC) MLIs. Next, scope of the work, contributions and thesis outlines are explained.*

## 1.1 Introduction

DC to AC static power conversion (inverter) plays a vital role in generation, transmission, distribution and utilization of electric power. High-performance and cost-effective inverter is a prerequisite for realization of power electronic applications such as adjustable speed drives (ASD), uninterruptible power supplies (UPS), high-voltage dc (HVDC) transmission, flexible ac transmission system (FACTS), custom power devices (CPD), active front end converters (AFC), battery energy storage systems (BESS), renewable energy generation (REG) and electric vehicles (EV). In early days, static power converters are realized with forced commutating switches such as thyristors. However, with the advent of semiconductor devices and remarkable progress of gate commutated semiconductor devices, attention has been focused on power electronic inverters with self-commutating devices.

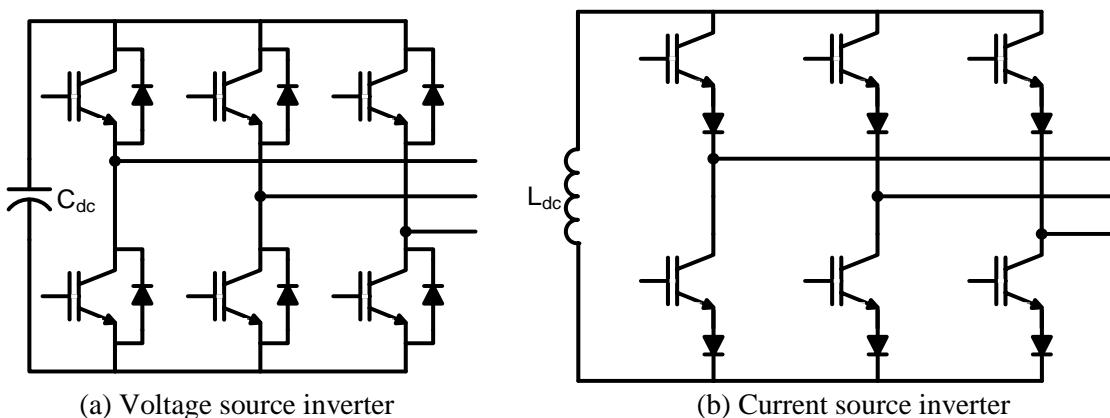

Depending on the dc link energy storage component, the inverters fall under either voltage source inverters (VSIs) or current source inverters (CSIs) [1-3]. The voltage source approach shown in Fig. 1.1(a) uses a capacitor with a regulated dc voltage, while the CSI, shown in Fig. 1.1(b) uses a reactor supplied with a regulated dc current. A critical comparison of VSI and CSI is beyond the scope of this thesis. However, one may prefer CSI due to its robustness or the VSI due to its high efficiency, low initial cost, and smaller physical size [4, 5]. Since VSI technology is widely used in industrial applications, this has also been more common in applications such as FACTS, CPD, ASD and REG [1] and hence, VSI has been considered in this thesis.

Fig. 1.1: Topologies of inverters.

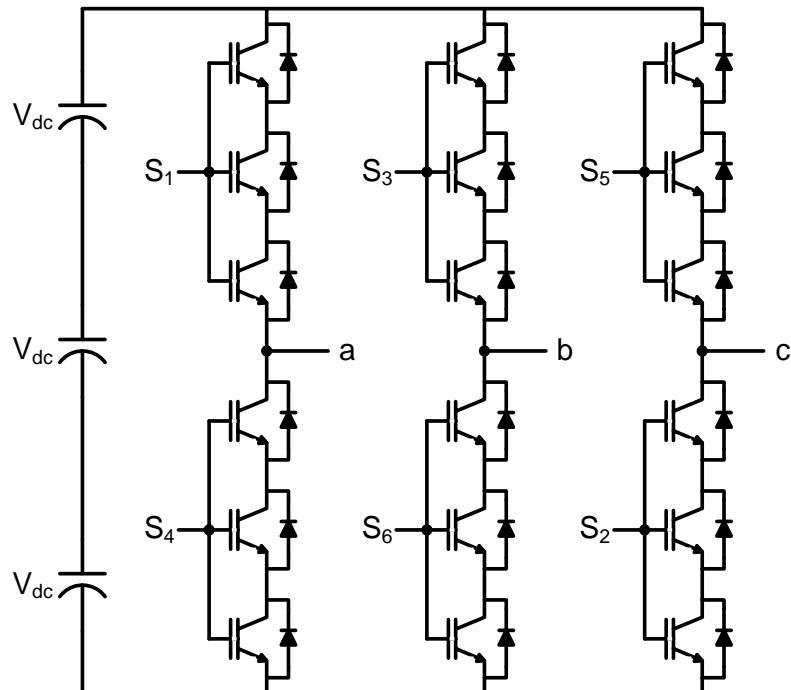

The well-known two-level VSI is also applicable for medium and high-power applications [6]. To cater the required voltage and current level of the inverter, several semiconductor switches are connected in series and parallel respectively. Thus, an inverter leg is comprised of two groups of active switches, each consisting of two or more switches in series/parallel, depending on the ratings of dc link voltage, load current and available switching devices. In addition to this, multiple capacitors in series could be necessary to achieve the desired voltage in dc link [6]. The circuit of high-power two-level VSI is shown in Fig. 1.2. In this circuit, each switch is comprised of three semiconductor devices connected in series and controlled with same gate signal.

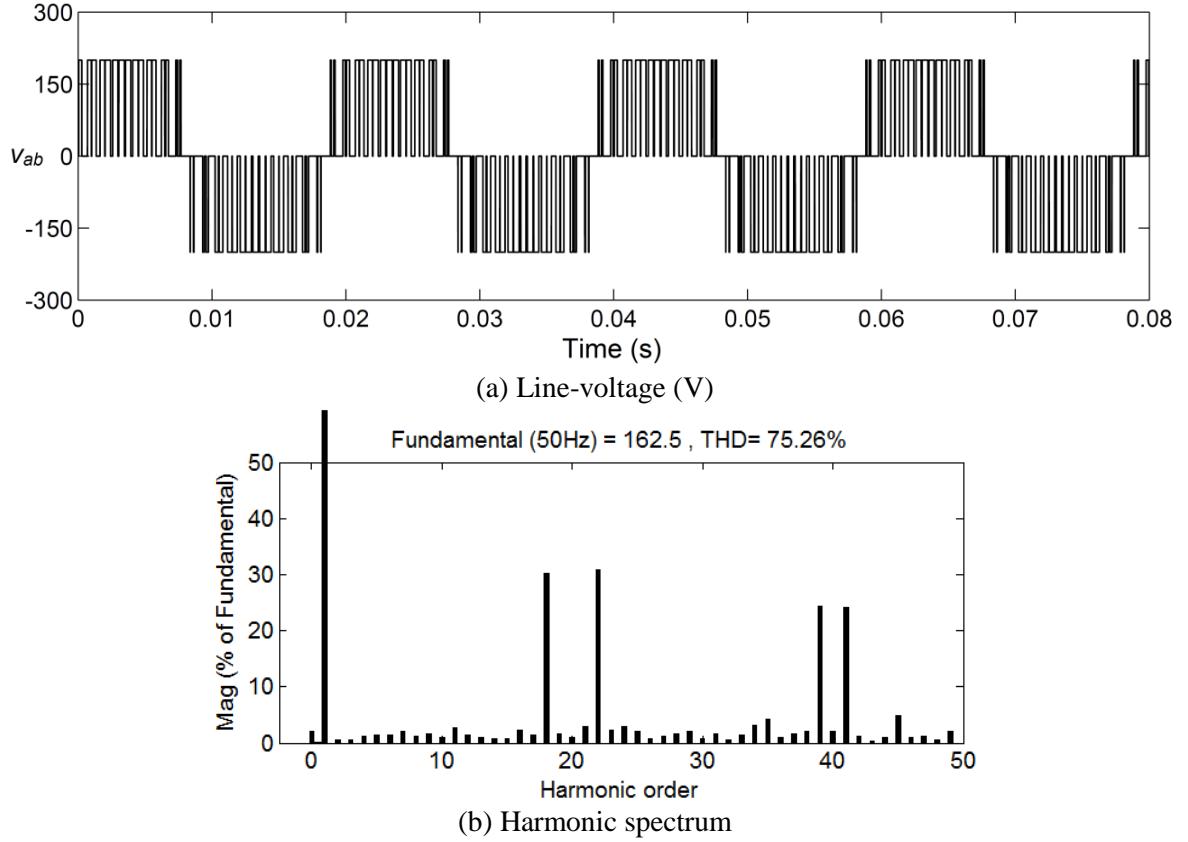

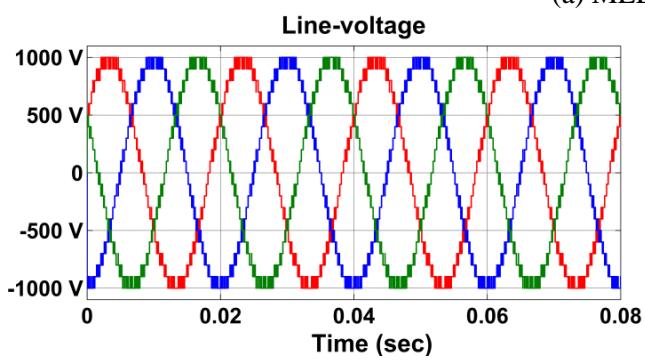

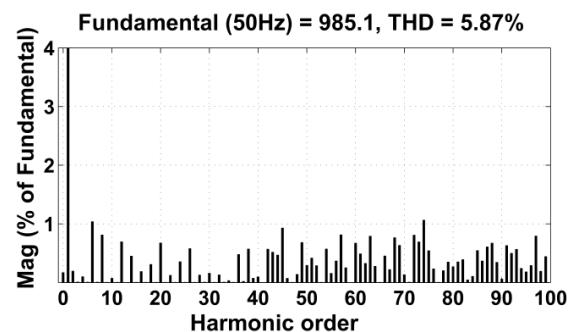

The output voltage of this inverter with sinusoidal pulsewidth modulation technique (SPWM) is shown in Fig. 1.3(a) for 1 kHz carrier signal frequency. The harmonic spectrum of the output voltage is shown in Fig. 1.3(b). The output voltage is of quasi-square nature with a total harmonic distortion (THD) of 75.26%. The high harmonic content of the output voltage and increased number of switching devices makes this simple inverter impractical for direct use in high-power applications [6, 7].

Instead of using filters to improve the output voltage waveform of the basic two-level VSI, various solutions are reported in the literature [6, 7]. Among them, multipulse and multilevel inverters (MLIs) are the most popular. These inverter configurations produce good THD performance and are directly applicable for high-power medium-voltage applications with matured medium-power semiconductor devices [6, 7]. Operating principle, merits and limitations of these high-power VSI configurations are explained below.

Fig. 1.2: Two-level high-power VSI.

Fig. 1.3: Performance of two-level VSI.

## 1.2 Inverters for high-power medium-voltage applications

The different topologies of VSI for high-power medium-voltage applications can be broadly categorized into two groups: multipulse and multilevel inverters (MLIs) [6-11]. These inverters present great advantages in comparison with conventional two-level VSI [11]. These advantages primarily deal with improvement in output signal quality and increase in power rating of the inverter.

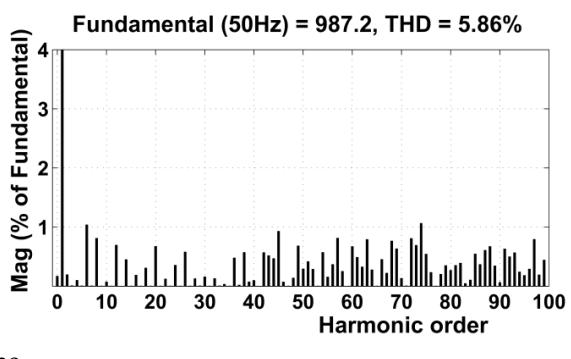

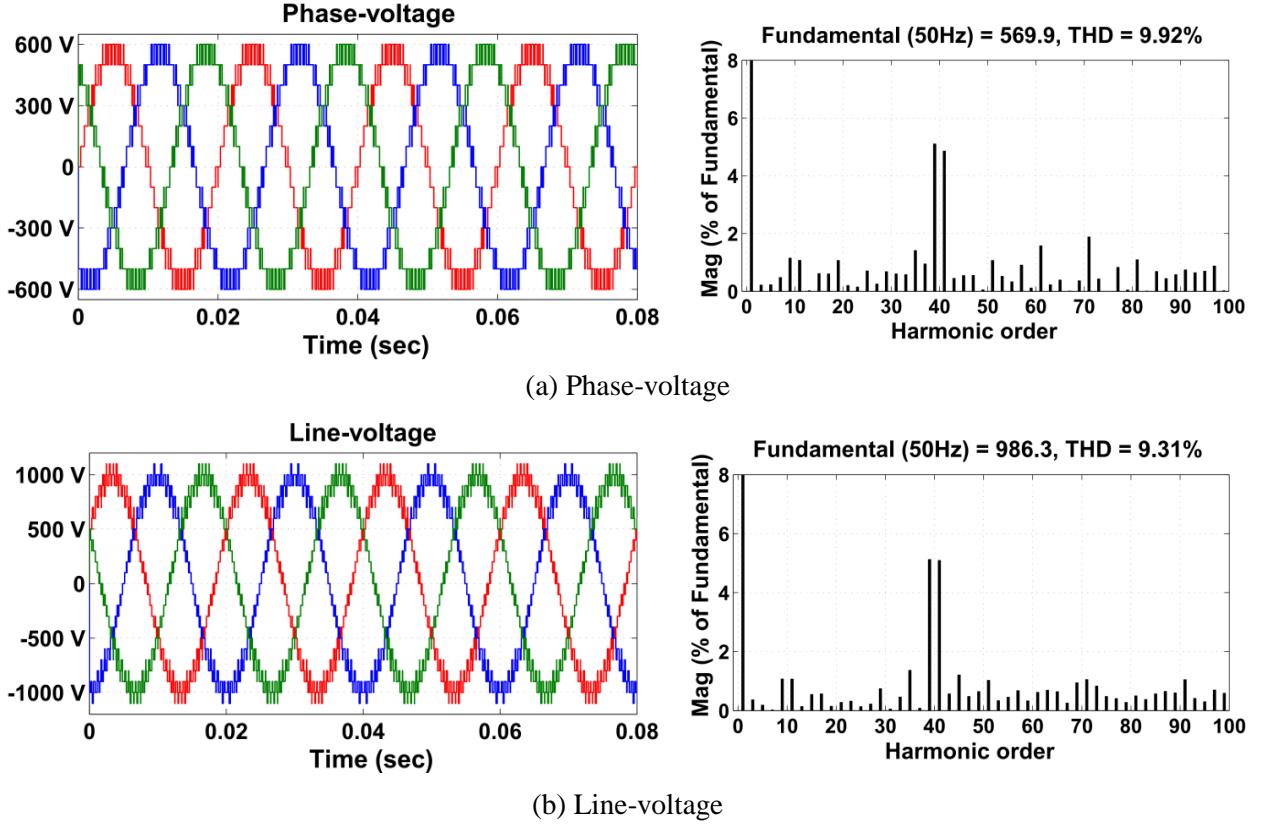

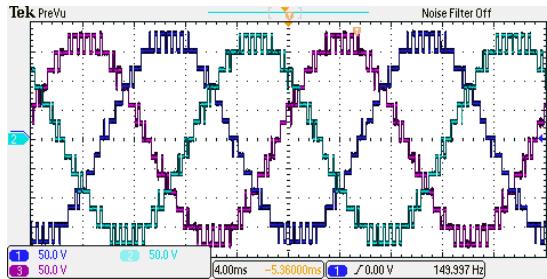

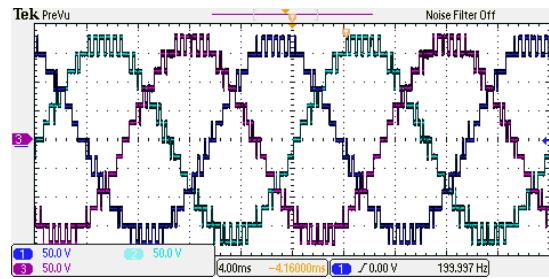

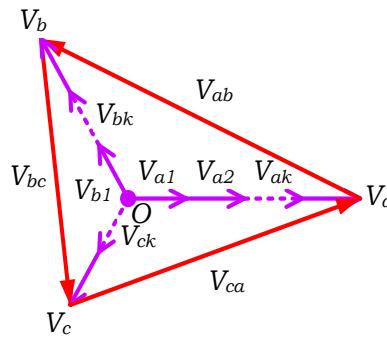

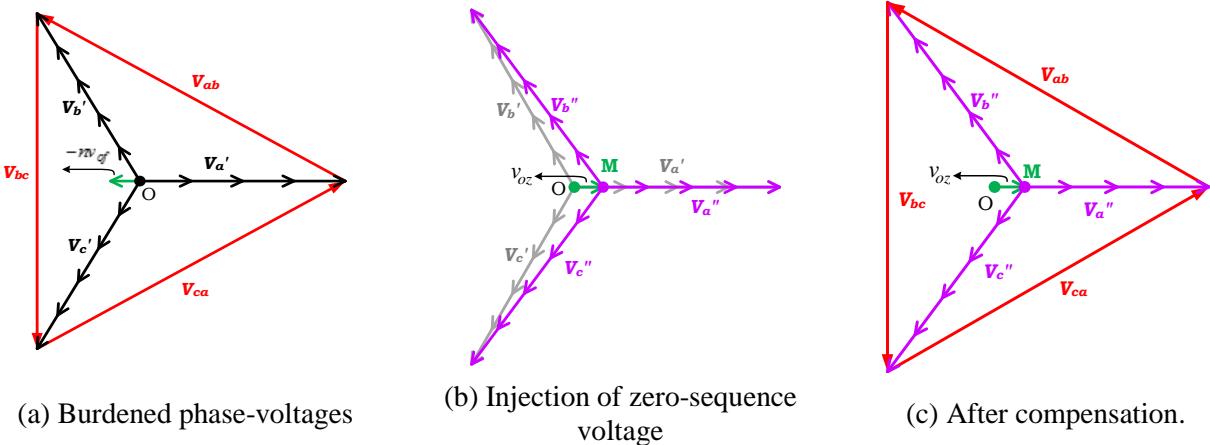

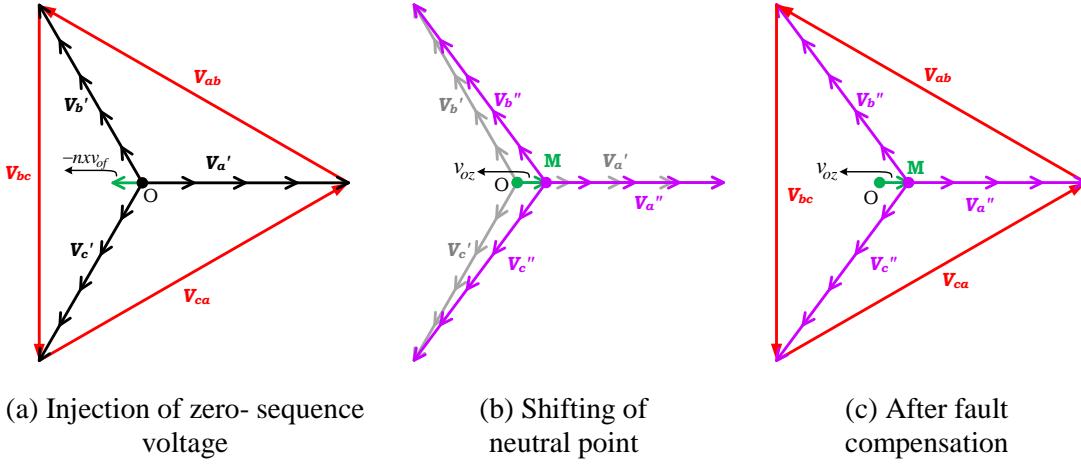

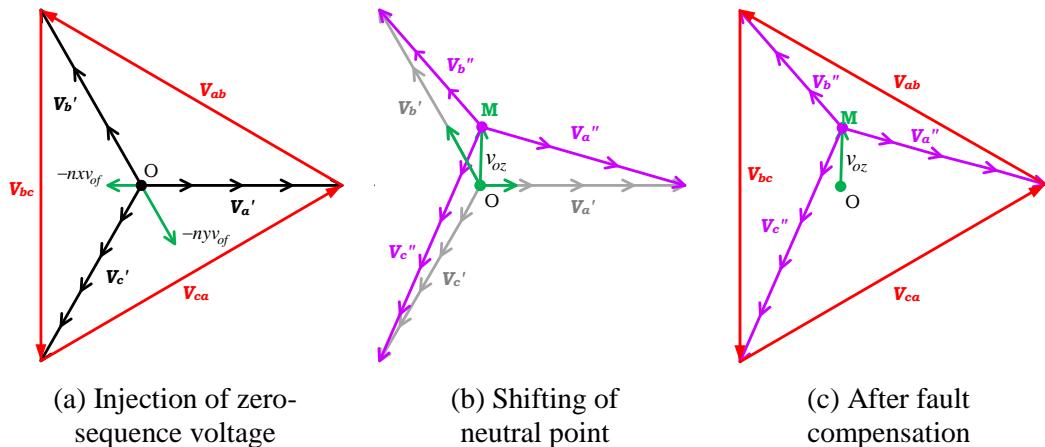

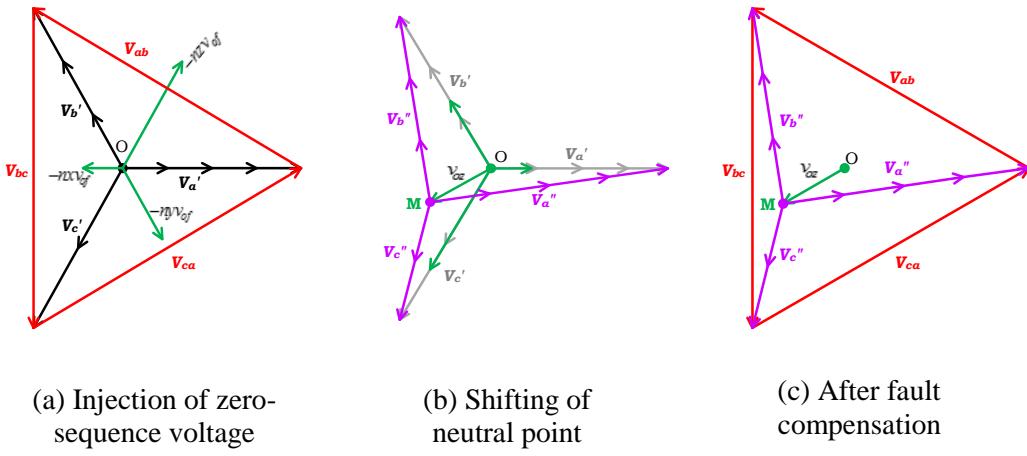

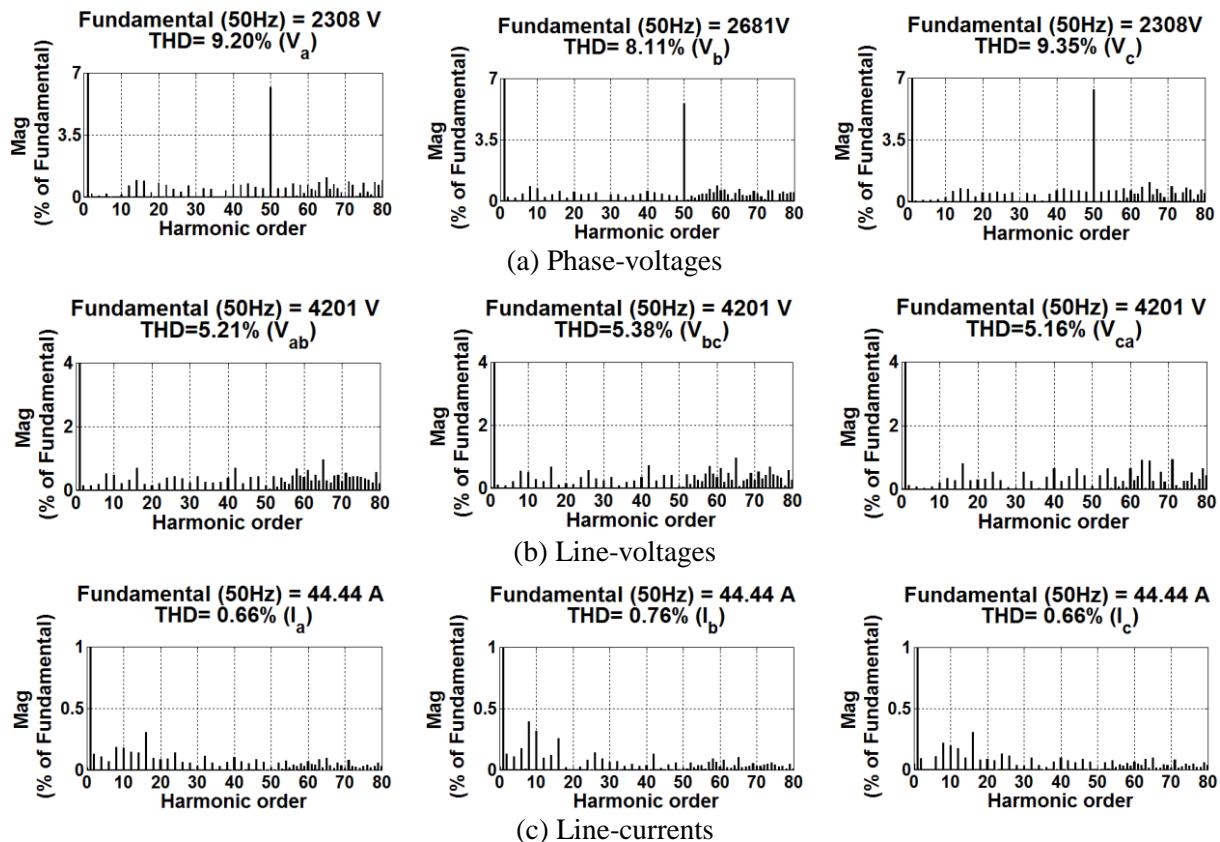

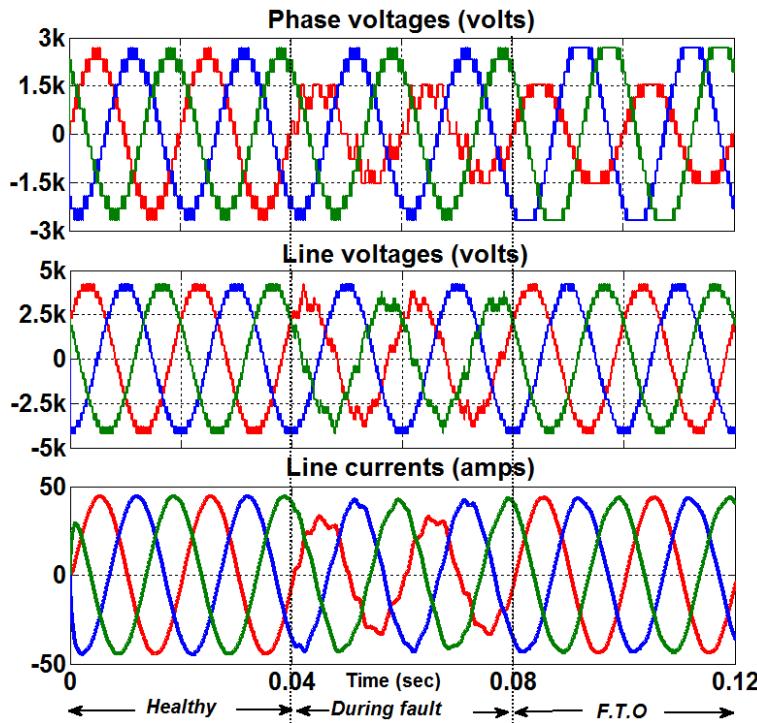

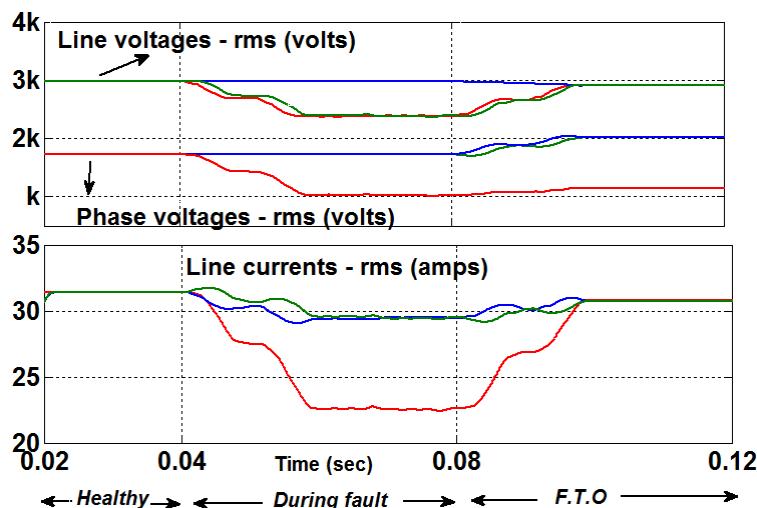

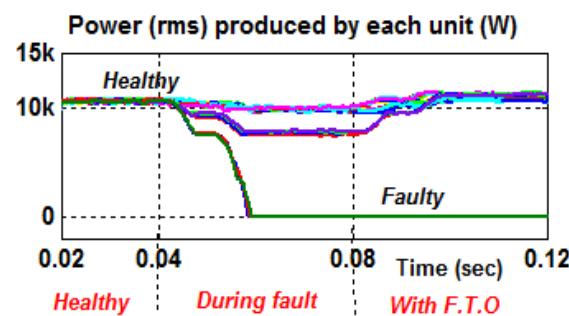

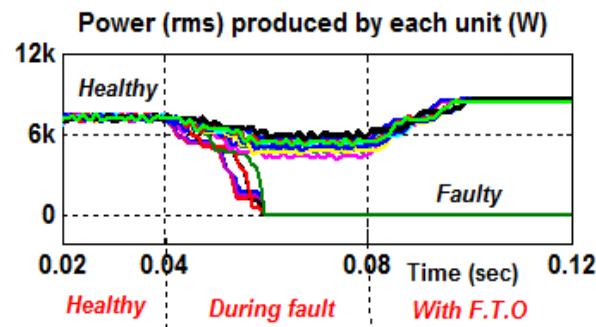

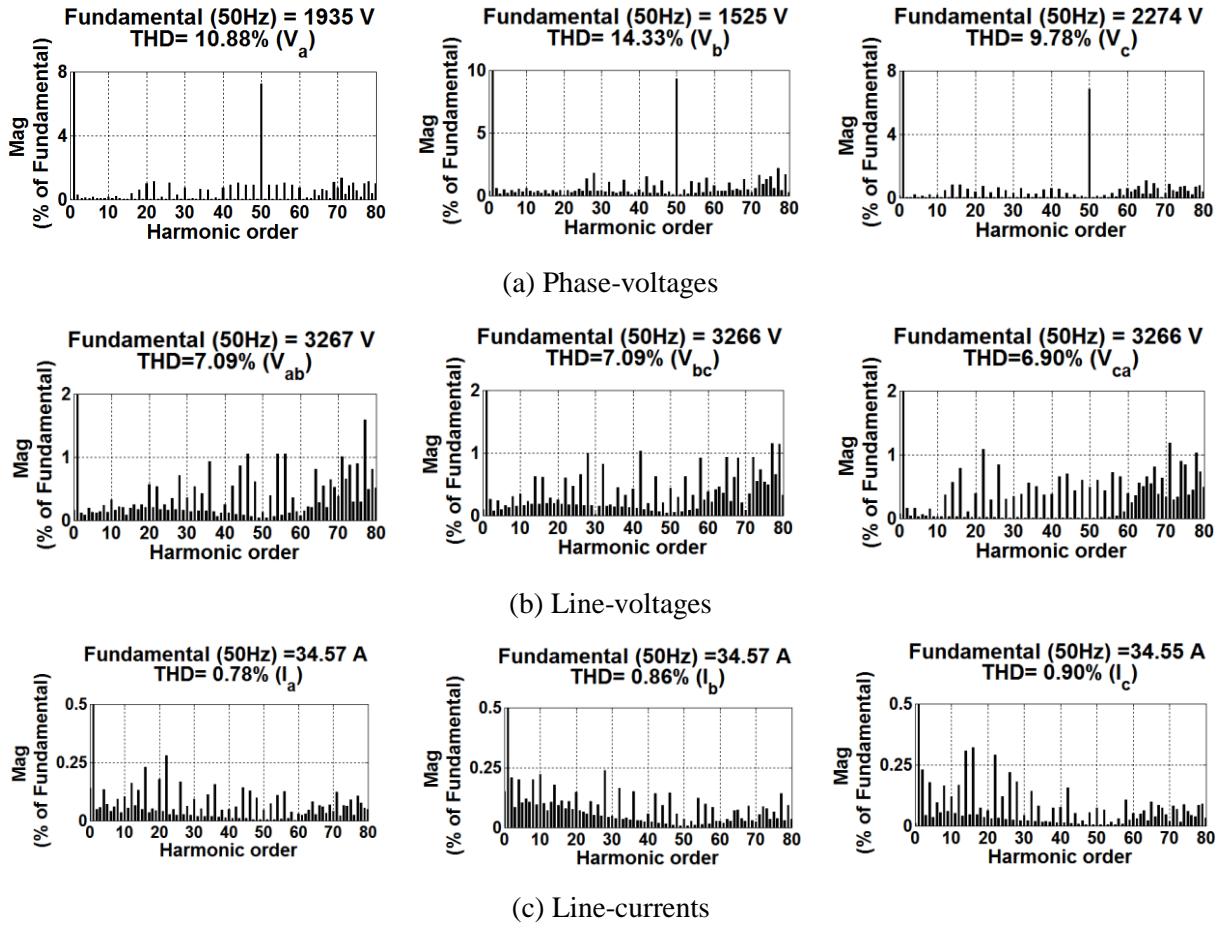

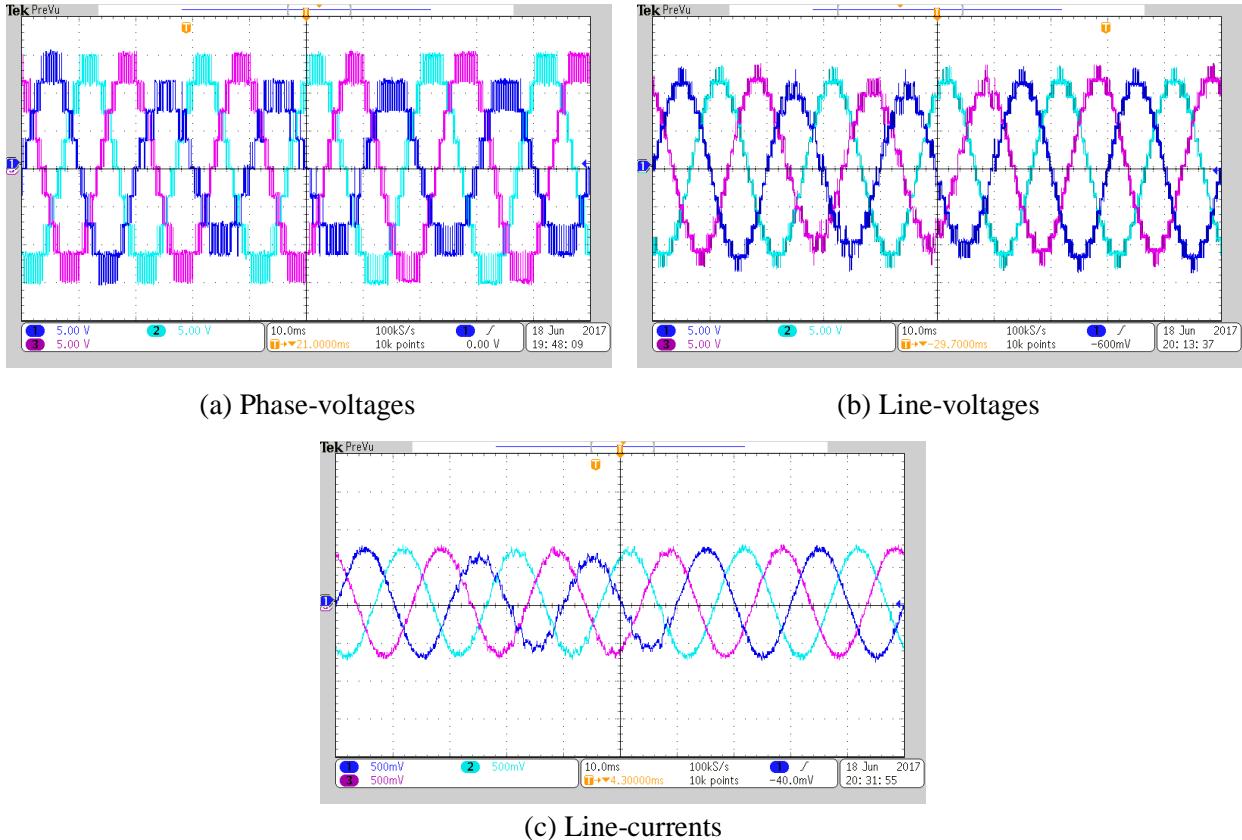

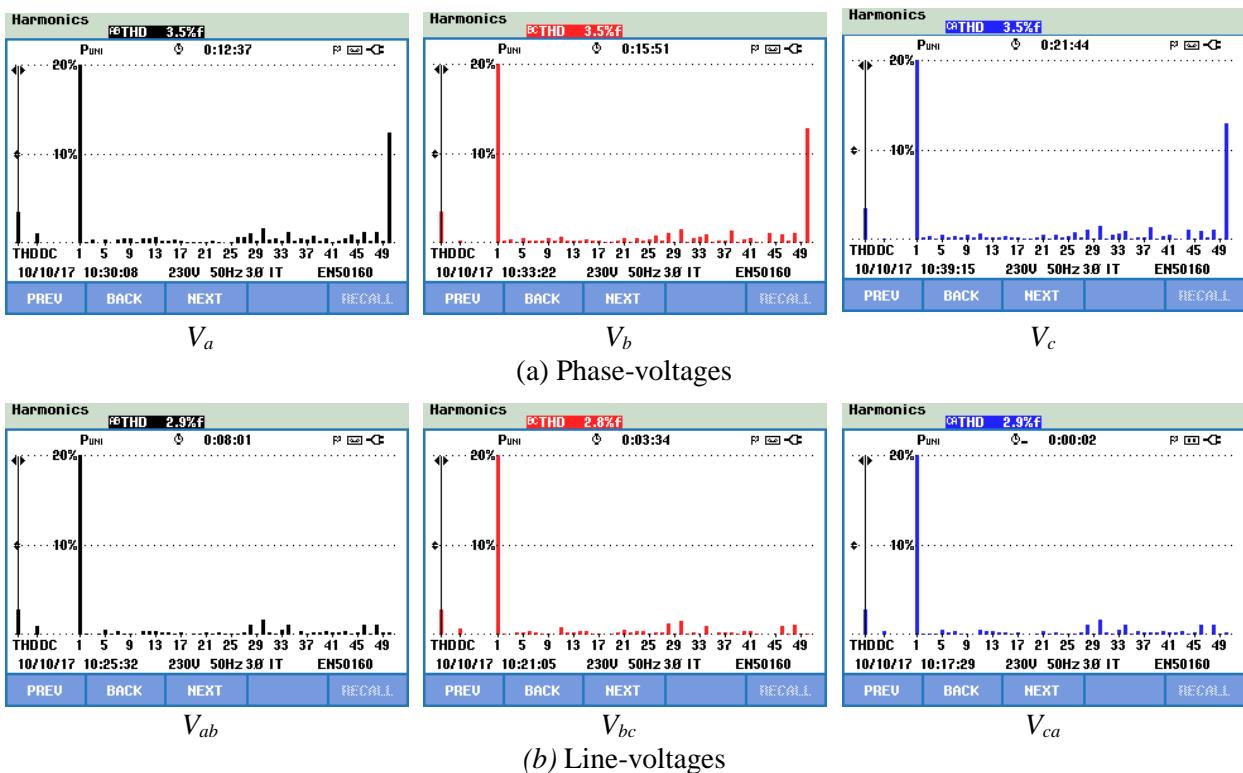

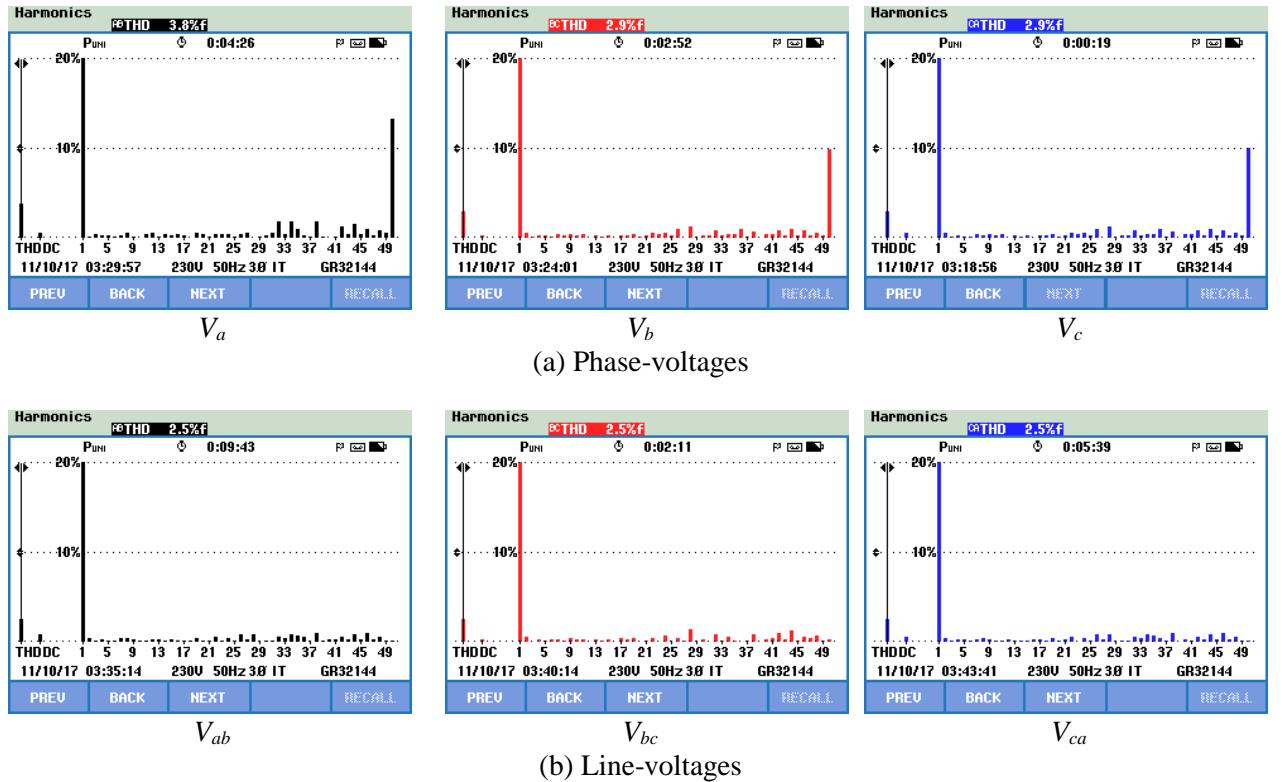

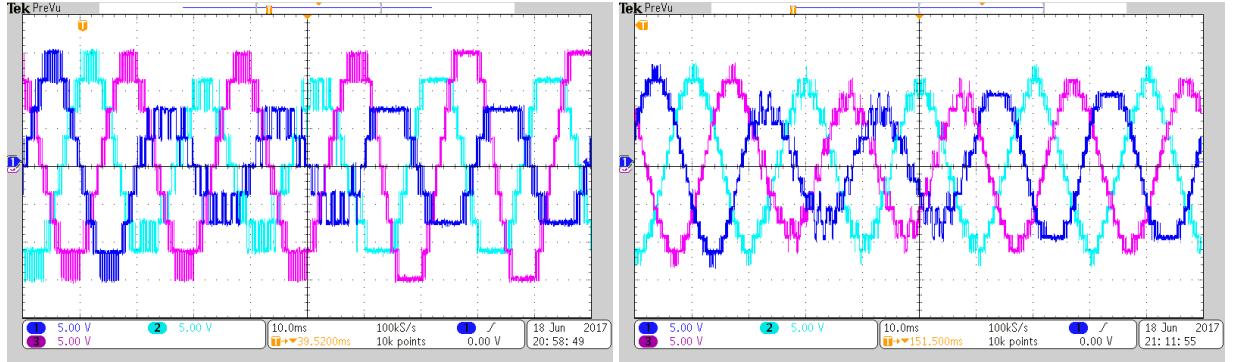

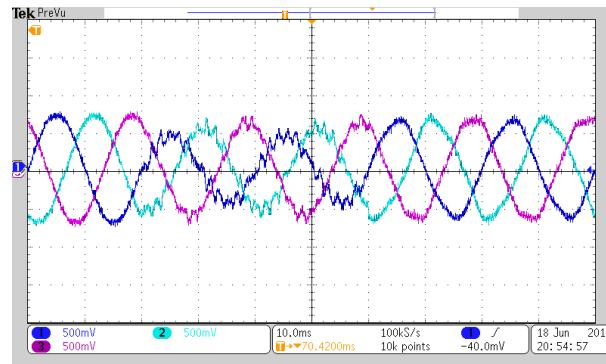

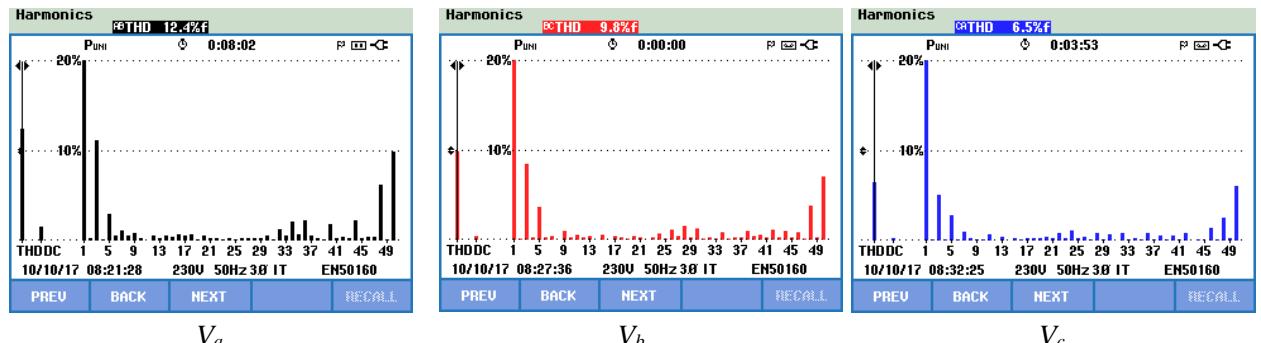

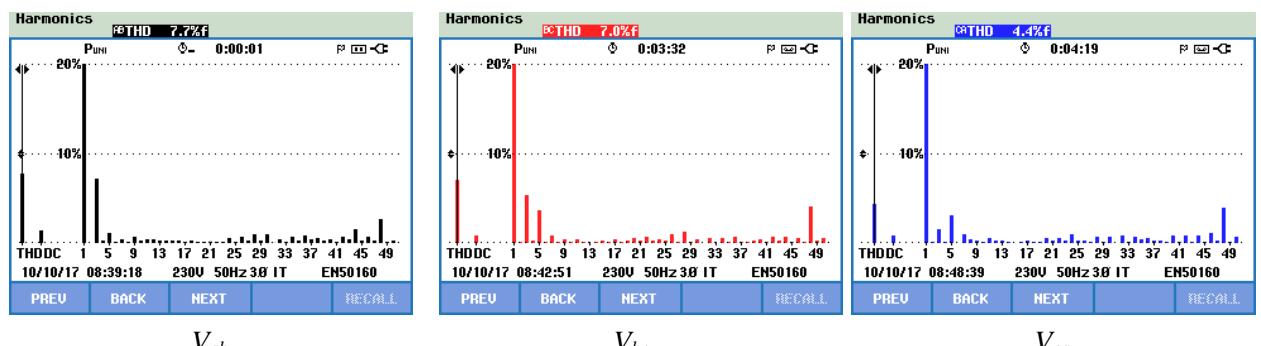

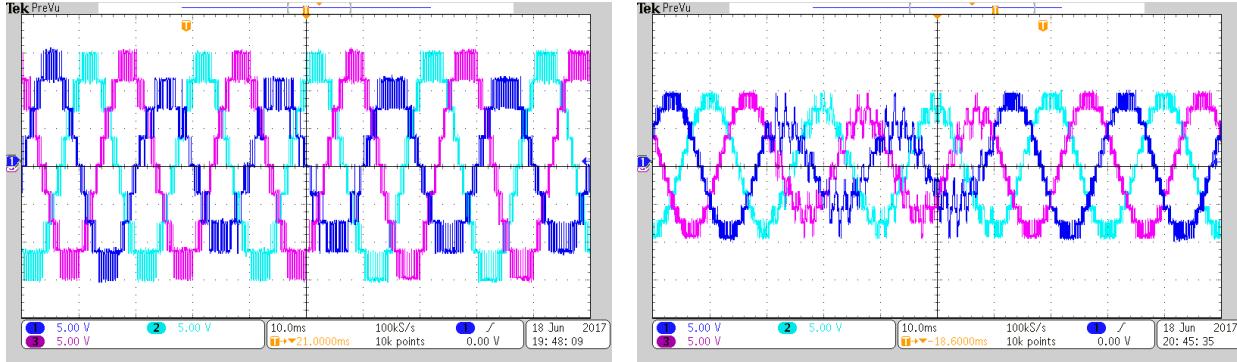

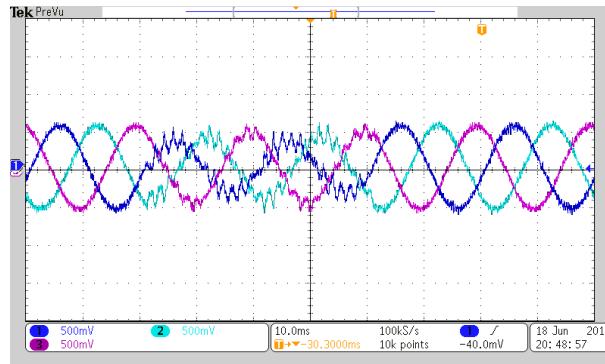

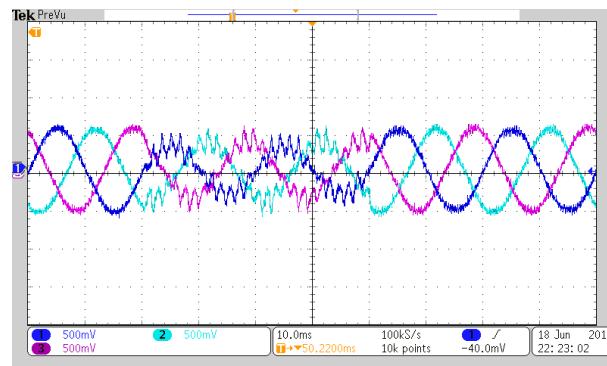

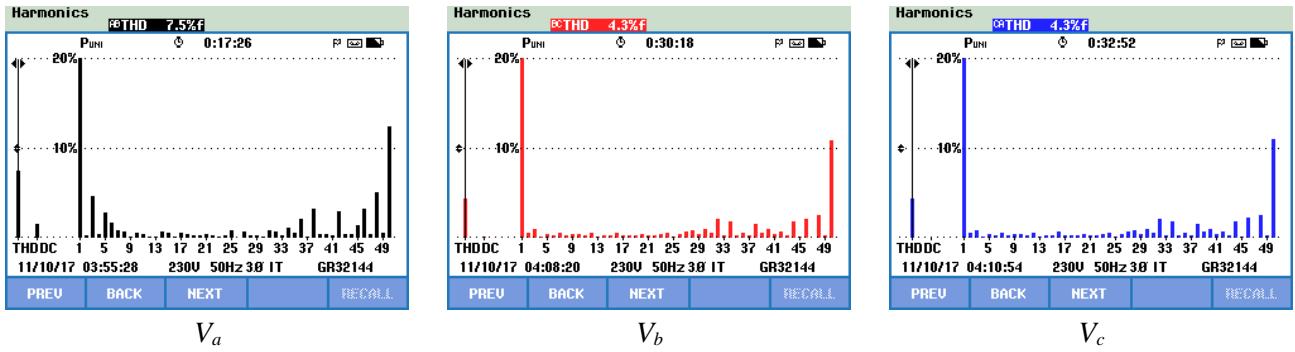

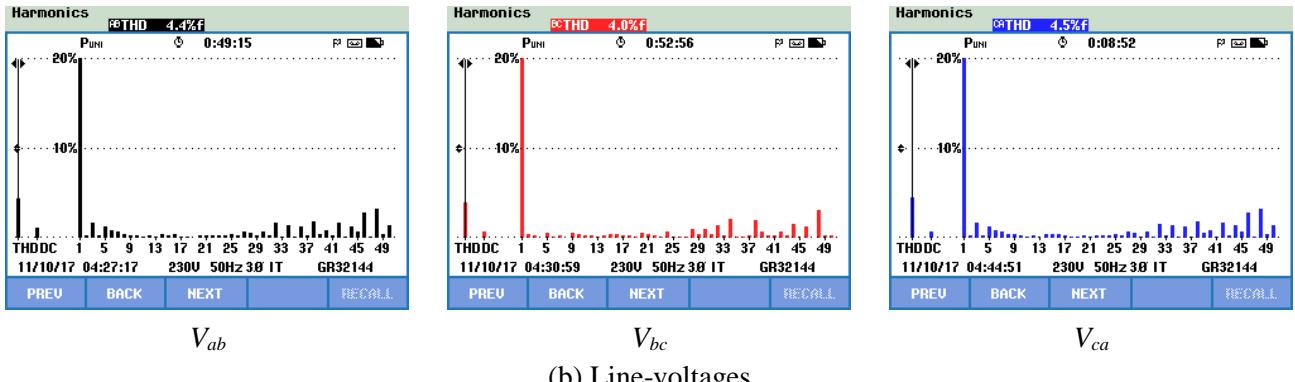

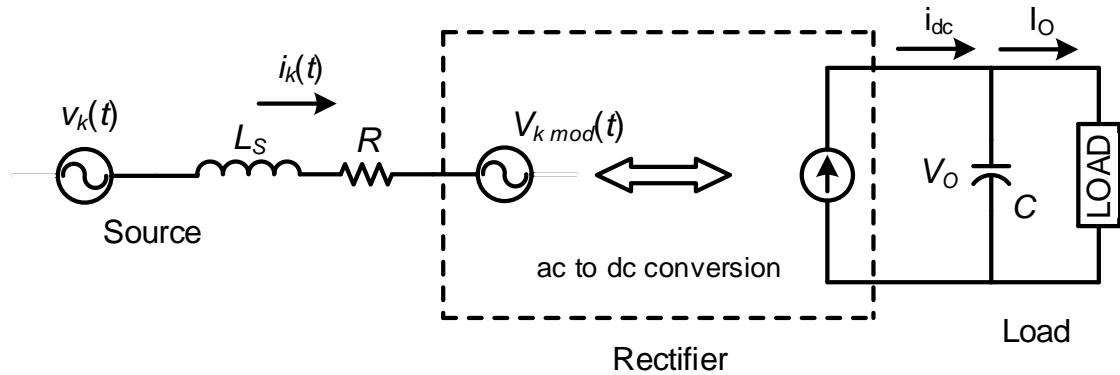

### 1.2.1 Multipulse inverters