# **Investigations on Quasi-Z-Source based Multilevel Inverters for Grid-Tied Photovoltaic Systems**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**Doctor of Philosophy**

**By**

**Pasupuleti Manoj**

**(Roll No. 718019)**

Supervisor

**Dr. V. T. Somasekhar**

Professor (HAG)

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

WARANGAL – 506004, TELANGANA STATE, INDIA

March-2023**

## APPROVAL SHEET

This Thesis entitled "**Investigations on Quasi-Z-Source based Multilevel Inverters for Grid-Tied Photovoltaic Systems**" by **Pasupuleti Manoj** is approved for the degree of Doctor of Philosophy.

### Examiners

---

---

---

### Supervisor

**Dr. V. T. Somasekhar**

Professor (HAG)

EED, NIT Warangal

### Chairman

**Dr. S. Srinivasa Rao**

Professor

EED, NIT Warangal

**Date:** \_\_\_\_\_

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506 004**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**CERTIFICATE**

This is to certify that the thesis entitled "**Investigations on Quasi-Z-Source based Multilevel Inverters for Grid-Tied Photovoltaic Systems**", which is being submitted by **Mr. Pasupuleti Manoj** (Roll No. 718019), is a bonafide work submitted to National Institute of Technology, Warangal in partial fulfilment of the requirement for the award of the degree of **Doctor of Philosophy** in Department of Electrical Engineering. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. V. T. Somasekhar**

(Supervisor)

Professor (HAG)

Department of Electrical Engineering

National Institute of Technology

Warangal – 506004

Date:

Place: Warangal

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Investigations on Quasi-Z-Source based Multilevel Inverters for Grid-Tied Photovoltaic Systems**" is a bonafide work done by me under the supervision of **Dr . V. T. Somasekhar**, Department of Electrical Engineering, National Institute of Technology, Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Pasupuleti Manoj**

**(Roll. No: 718019)**

Date:

Place: Warangal

## ACKNOWLEDGEMENTS

It gives me immense pleasure to express my heartfelt gratitude to my supervisor **Prof. V. T. Somasekhar** for giving me the opportunity to work under his direction. His knowledge, suggestions, and discussions helped me to overcome difficult situations during my thesis work. Without his scholarly guidance, this thesis could not have been completed. I consider myself very fortunate to have worked with him.

I take the opportunity to thank my Doctoral Scrutiny Committee chairman **Dr. S. Srinivasa Rao**, Professor, Department of Electrical Engineering and all Doctoral Scrutiny Committee members, **Dr. A. Kirubakaran**, Associate Professor, Department of Electrical Engineering, **Dr. G. Siva Kumar**, Associate Professor, Department of Electrical Engineering and **Dr. N. Bheema Rao**, Professor, Department of Electronics and Communication Engineering for their detailed review, constructive suggestions and excellent advice during the progress of this research work.

I am very thankful to **Dr. B. L. Narasimharaju**, Head of Department of Electrical Engineering and **Prof. N.V. Ramana Rao**, Director, NIT Warangal for their support and cooperation.

I am highly grateful to my seniors Dr. Suresh Lakhimsetty, Dr. Sumon Dhara and Dr. Patnana Hema Kumar for their constant support and suggestions during my Ph.D work. I convey my special thanks to my contemporary Research Scholars Mr. K. Hema Sundar, Mr. M. Madhu Babu, Mr. K. Ashok Kumar, Mr. M F Baba, Mr. Chinmay Kumar Das, Mr. C.R. Arun Kumar for constant support throughout my journey. I thank my juniors Mr. K.V.V.S Ramana kumar and Mr. K. Srikanth Reddy for their cooperation and encouragement.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal. They have always been encouraging and supportive.

Finally, I would like to thank my parents Shri. Manga Raju, Smt. Rajya Lakshmi and my sister Ms. Vasavi, for their love, patience and moral support during my research work.

**Pasupuleti Manoj**

## ABSTRACT

The importance of renewable energy sources need not be overemphasized in the present scenario of the dwindling resources of conventional energy. The efforts to contain environmental pollution resulted in the emergence of solar photovoltaic (PV) systems. Declining costs, durability, and lower maintenance are the contributing factors to the proliferation of solar energy systems. Solar PV systems are operated in stand-alone mode for water pumping, rural electrification, and street lighting applications. Also, grid-tied PV systems are gaining momentum due to the ever-increasing nature of electrical energy.

Conventionally, in grid-tied PV systems, the objectives of boosting the inadequate PV input voltage and the DC-AC conversion are achieved with a two-staged system, consisting of a boost converter and conventional VSI. These systems display a good maximum power point tracking (MPPT) capability due to the availability of an additional DC/DC boost converter. However, the demerits of these systems are low reliability, less efficiency, and increased complexity. In recent times, quasi-z-source-based solar PV systems attract the attention of researchers. Owing to their single-staged nature, these topologies can accomplish both boosting and inversion with reduced switching resources, smaller sizes of passive components, lower cost, and enhanced efficiency.

In the past two decades, multilevel inverters gained much attention as they are suitable for high power and high voltage applications. With an increased number of voltage levels, multilevel inverters (MLIs) reduce the voltage stress across the power semiconductor switching devices and derive a superior harmonic performance compared to the conventional two-level VSIs. However, owing to their buck-typed nature, conventional multilevel inverters require that the input DC voltage be higher than the desired peak value of the AC output voltage. Therefore single-stage systems aim to overcome this disadvantage by fusing a multilevel inverter with a quasi-z-source network.

This thesis presents the investigation of single-stage quasi-z-source-based multilevel inverter configurations for both multi-string and single-string applications. The thesis attempts to address some major challenges associated with the quasi-z-source-based multilevel inverters which are: (i) achieving higher voltage boosting and inversion simultaneously (ii) the reduction of leakage current, (iii) reactive power capability (iv)

multilevel operation with reduced switching devices, etc. In an attempt to address these challenges, four single-stage multilevel inverter topologies have been proposed in this thesis.

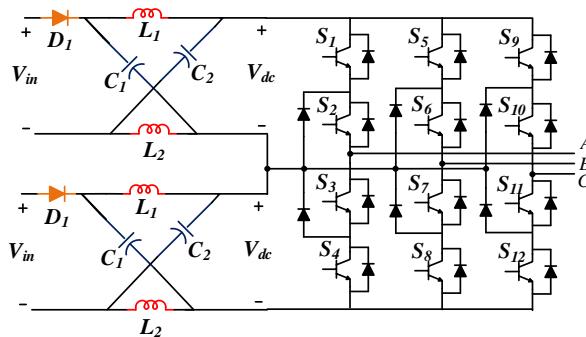

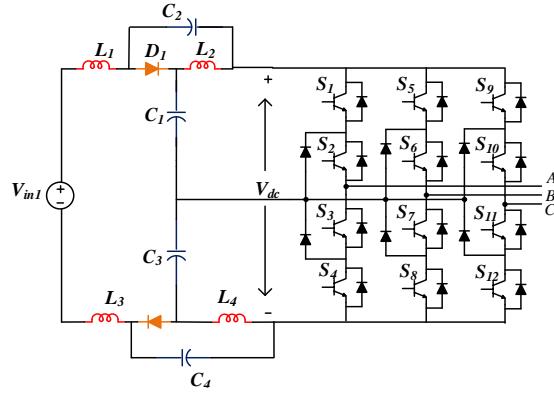

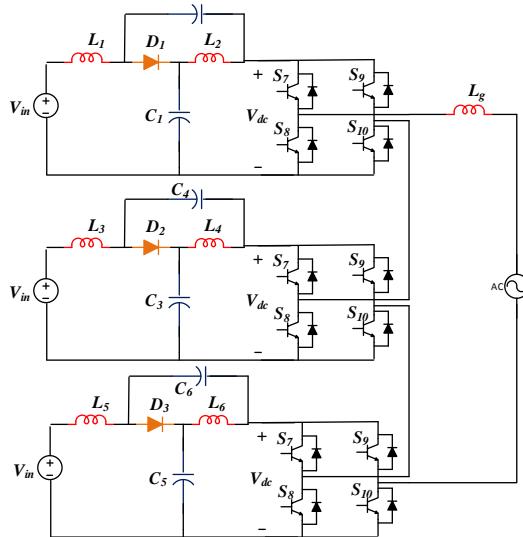

Firstly, a single-stage, four-level, cascaded multilevel inverter is proposed for multi-string photovoltaic applications. The proposed configuration achieves voltage boosting using three quasi-z-source networks, which are fused with the cascaded multilevel configuration. The power converter employs a level-shifted space vector modulation technique. In comparison with the conventional qZS-based cascaded H-bridge and Neutral point clamped inverters, the power converter achieves a 50% higher boost factor. Moreover, compared to the aforementioned configurations, the proposed converter outputs a higher number of voltage levels, resulting in better spectral performance and alleviating the voltage stress across the switches. Further, it is shown that the employed control technique implements the shoot-through without any additional power loss in qZS inverters. Moreover, the performance characteristics of the proposed inverter were compared with existing topologies to highlight its merits. However, the control complexity associated with the MPPT tracking with multiple PV sources, DC-link voltage regulation, and the requirement of a large number of switching devices to synthesize a 4-level output voltage waveform is the major demerits of the topology.

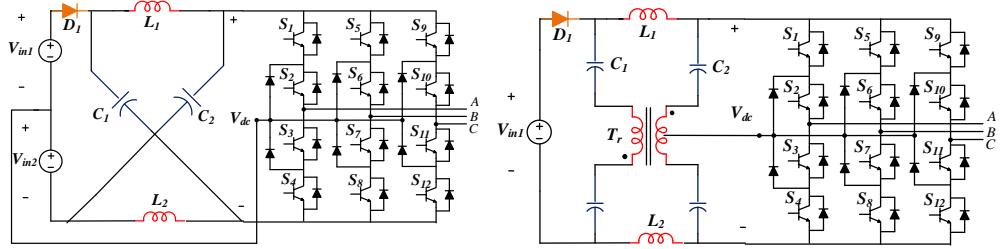

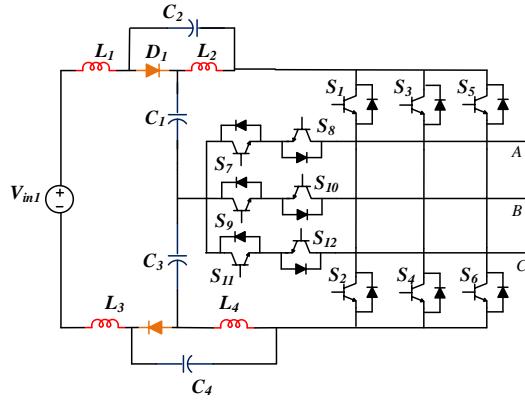

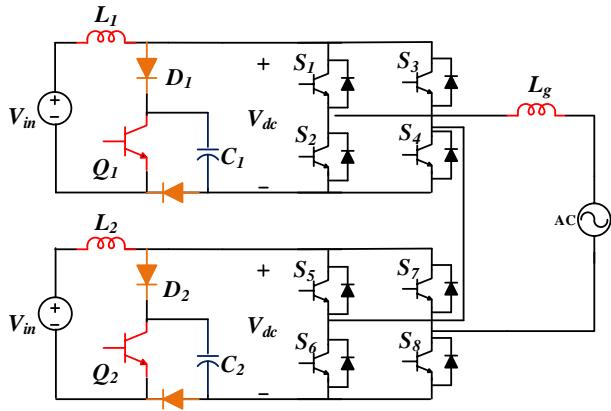

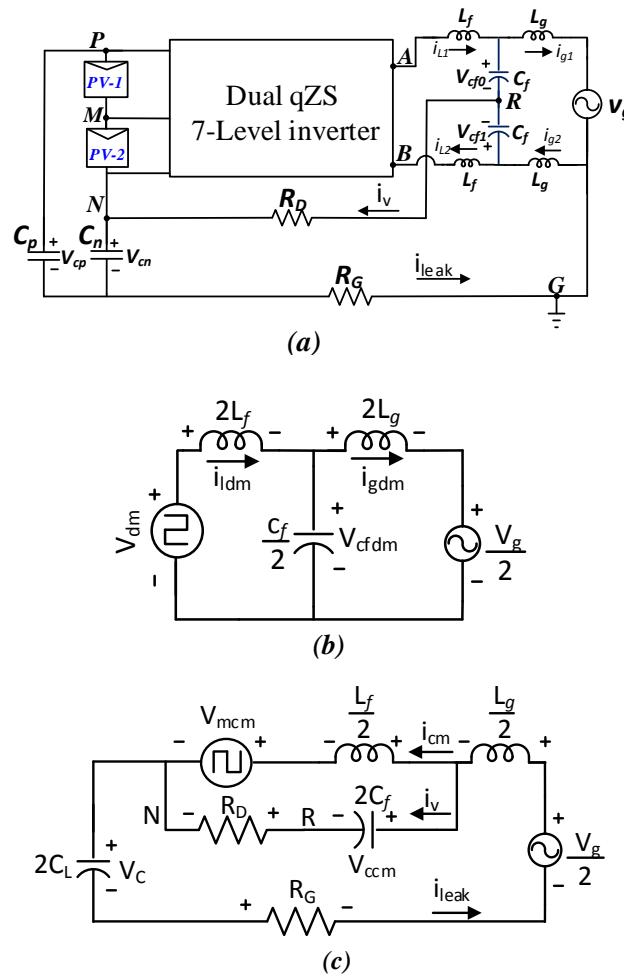

In the second proposal, a single-stage seven-level quasi-z-source-based MLI is investigated to minimize the aforementioned drawbacks. The power converter employs only two PV sources and requires a lower number of devices to generate a 7-level output voltage waveform. Further, the power converter employs a modified level-shifted PWM scheme, which achieves the twin objectives of boosting the input voltage and the generation of 7 levels in the output voltage waveform. Moreover, this work aims to minimize the leakage current, which is one of the major issues in transformerless inverters, by reducing the magnitude of voltage transitions in the parasitic capacitor and the suppression of higher-order harmonics in the ground leakage current.

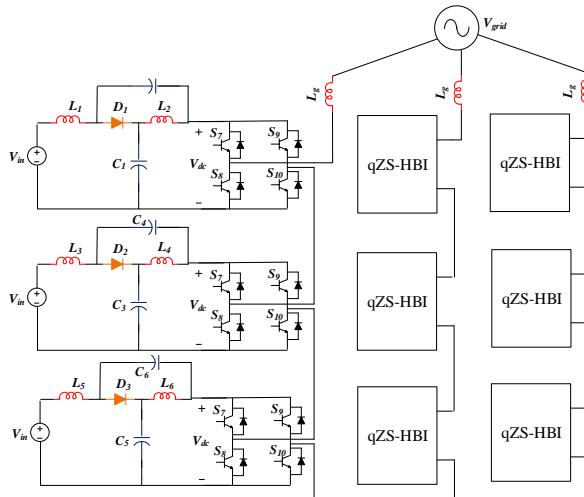

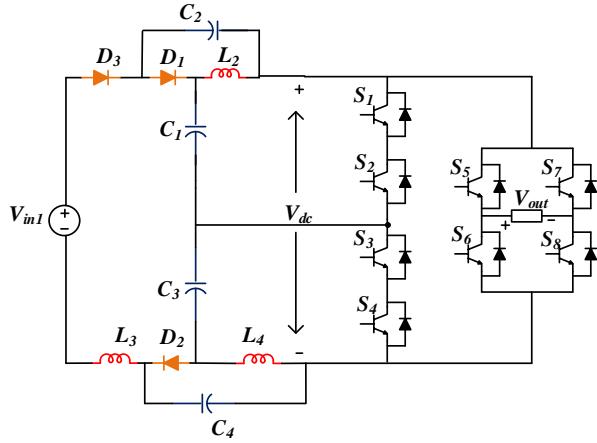

To further, minimize the input PV sources and semiconductor devices a five-level qZS-based PV inverter is proposed. In this topology, two symmetrical qZS networks with a single DC source are fused with a 5-level hybrid inverter. Similar to the aforementioned topology, the proposed power converter employs a modified level-shifted PWM to achieve boosting and five-level operation. When compared to the existing qZS-based 5-level inverters in the literature, the proposed power converter employs fewer semiconductor switching

devices, enhancing its reliability. Further, the power converter also minimizes the leakage current to less than the standards dictated by *VDE-0126-1-1*.

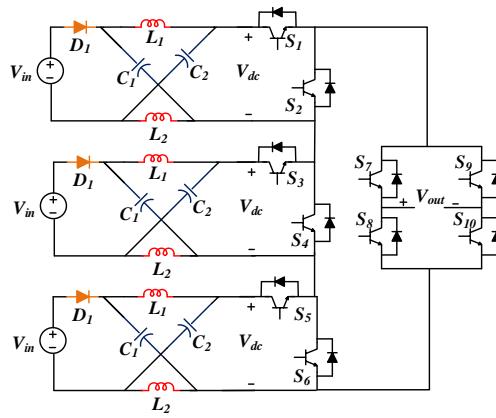

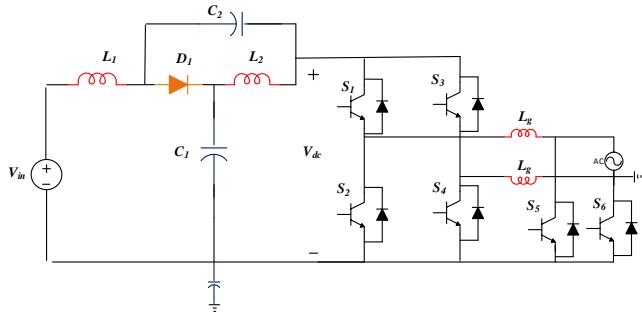

Both the proposed qZS-based seven-level and five-level inverters suffer from high voltage THD and conventional voltage boosting. To minimize these drawbacks a quasi-switched capacitor-based five-level inverter is proposed. The proposed power converter comprises two quasi-z-source networks and switched capacitor-based five-level inverter with a single PV source. With the aid of a modified LSPWM scheme and switched capacitor network the power converter achieves higher voltage boosting and five-level voltage inversion. Further, the power converter minimizes the leakage current without any additional need for filter components.

All the above-mentioned power configurations in this thesis are verified with laboratory prototypes in the stand-alone as well as the grid-tied modes of operation. Experimental studies validate the working principles of the proposed power converter configurations along with the proposed modulation strategies in steady-state as well as dynamic conditions.

# Table of Contents

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| <b>Acknowledgement</b> .....                                                  | <b>i</b>   |

| <b>Abstract</b> .....                                                         | <b>ii</b>  |

| <b>Table of Contents</b> .....                                                | <b>v</b>   |

| <b>List of Figures</b> .....                                                  | <b>ix</b>  |

| <b>List of Tables</b> .....                                                   | <b>xv</b>  |

| <b>Abbreviations</b> .....                                                    | <b>xvi</b> |

| <b>List of Symbols</b> .....                                                  | <b>xix</b> |

| <b>Chapter-1</b> <b>Introduction</b> .....                                    | <b>1-1</b> |

| 1.1    General overview .....                                                 | 1-2        |

| 1.2    Classification of PV inverters .....                                   | 1-3        |

| 1.2.1    Central inverters.....                                               | 1-3        |

| 1.2.2    String inverters.....                                                | 1-3        |

| 1.2.3    Microinverter .....                                                  | 1-3        |

| 1.3    Interfacing PV source with grid .....                                  | 1-4        |

| 1.3.1    Number of power processing stages .....                              | 1-4        |

| 1.3.2    Isolated/Non-Isolated inverter.....                                  | 1-5        |

| 1.4    Leakage current.....                                                   | 1-6        |

| 1.5    Single-stage non-isolated power converters with voltage boosting ..... | 1-7        |

| 1.6    PV inverter standards in grid-tied operation .....                     | 1-8        |

| 1.7    Organization of the thesis.....                                        | 1-9        |

| <b>Chapter-2</b> <b>Literature survey</b> .....                               | <b>2-1</b> |

| 2.1    Introduction .....                                                     | 2-2        |

| 2.2    The Impedance source inverter .....                                    | 2-2        |

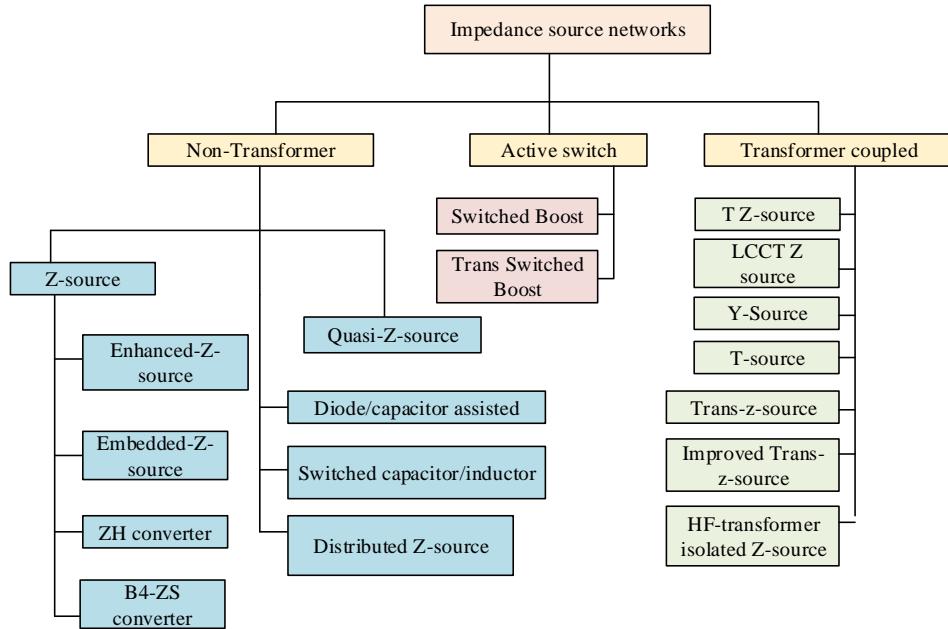

| 2.3    Classification of impedance source networks .....                      | 2-5        |

| 2.3.1    Non-transformer impedance networks .....                             | 2-5        |

| 2.3.2    Transformer-coupled impedance networks .....                         | 2-7        |

| 2.4    Multilevel Inverters .....                                             | 2-8        |

| 2.5    Impedance source Multilevel Inverter.....                              | 2-9        |

| 2.5.1    Three-phase impedance source multilevel inverter topologies .....    | 2-9        |

| 2.5.2    Single-phase impedance source multilevel inverter topologies .....   | 2-12       |

| 2.6    Motivations .....                                                      | 2-15       |

| 2.7    Objectives.....                                                        | 2-16       |

|                                                                                                                                 |      |

|---------------------------------------------------------------------------------------------------------------------------------|------|

| <b>Chapter-3 A Quasi-Z-Source Based Space Vector Modulated Cascaded Four-Level Inverter for Photovoltaic Applications .....</b> | 3-1  |

| 3.1 Introduction .....                                                                                                          | 3-2  |

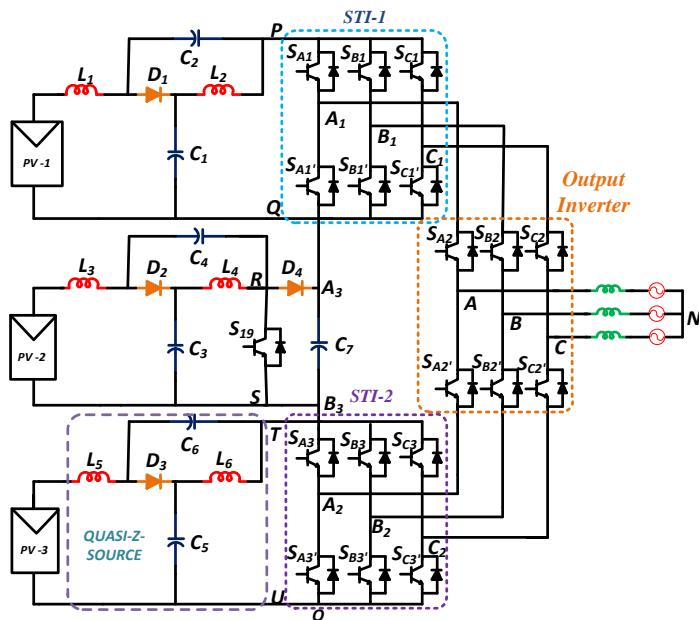

| 3.2 The proposed Quasi-z-source based four-level cascaded MLI(QZS-FCMI) .....                                                   | 3-3  |

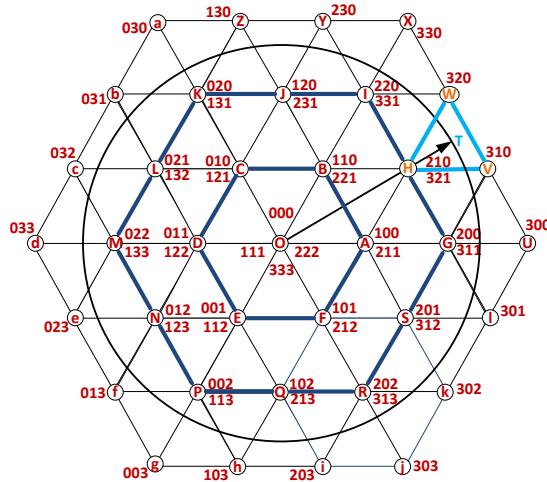

| 3.2.1 Switching states and the output voltage of the Four-level Inverter .....                                                  | 3-4  |

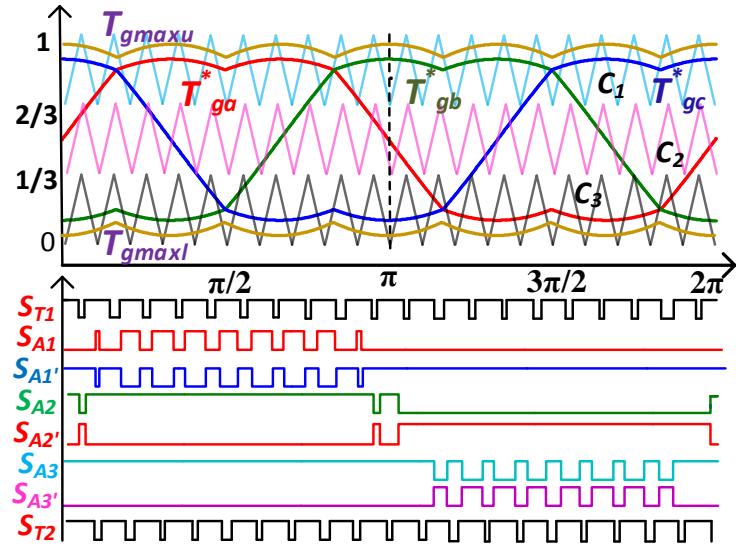

| 3.3 Control strategy for the proposed QZS-FCMI .....                                                                            | 3-5  |

| 3.3.1 Implementation of the SVPWM scheme .....                                                                                  | 3-5  |

| 3.3.2 Insertion of the shoot-through in the FCMI .....                                                                          | 3-6  |

| 3.3.3 Analysis of the Boost factor of the Quasi-Z-source with the proposed PWM Scheme.....                                      | 3-10 |

| 3.4 The control scheme of QZS-FCMI for stand-alone and grid-connected operation.....                                            | 3-12 |

| 3.4.1 Standalone mode .....                                                                                                     | 3-12 |

| 3.4.2 The Grid-connected mode of operation .....                                                                                | 3-13 |

| 3.5 Experimental Results.....                                                                                                   | 3-14 |

| 3.6 Comparison with the proposed QZS FCMI .....                                                                                 | 3-21 |

| 3.7 Power loss analysis for the proposed QZS-FCMI.....                                                                          | 3-23 |

| 3.8 Summary .....                                                                                                               | 3-24 |

| <b>Chapter-4 An Asymmetrical Dual Quasi-Z-Source Based 7-Level Inverter for PV Applications .....</b>                           | 4-1  |

| 4.1 Introduction .....                                                                                                          | 4-2  |

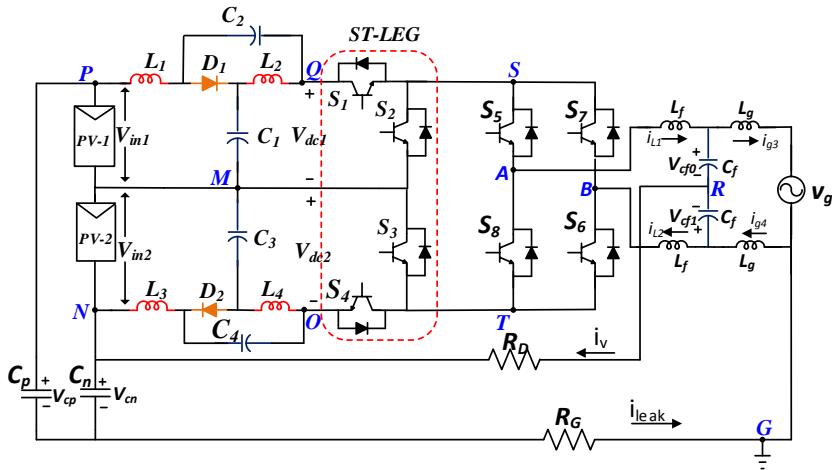

| 4.2 The proposed DQZS-7LI .....                                                                                                 | 4-3  |

| 4.2.1 Proposed Power converter .....                                                                                            | 4-3  |

| 4.2.2 Output voltage levels and corresponding switching states of the power converter                                           | 4-3  |

| 4.3 The control scheme for the proposed dual QZS 7-level inverter .....                                                         | 4-5  |

| 4.3.1 Implementation of the MLS-PWM scheme .....                                                                                | 4-5  |

| 4.3.2 Boost factor of the proposed DqZS-5LI.....                                                                                | 4-7  |

| 4.3.3 Design of qZS network of proposed DqZS-7LI.....                                                                           | 4-8  |

| 4.4 Standalone and grid-connected control strategies of DQZS-7LI .....                                                          | 4-9  |

| 4.4.1 Stand-alone mode.....                                                                                                     | 4-9  |

| 4.4.2 The Grid-connected mode of operation .....                                                                                | 4-10 |

| 4.5 Reduction of leakage current.....                                                                                           | 4-11 |

| 4.6 Experimental Results.....                                                                                                   | 4-13 |

| 4.7 Comparison with the proposed DQZS-7LI .....                                                                                 | 4-18 |

| 4.8 The Loss analysis for the DQZS-7LI .....                                                                                    | 4-20 |

| 4.9 Summary .....                                                                                                               | 4-21 |

|                                                                                                                      |      |

|----------------------------------------------------------------------------------------------------------------------|------|

| <b>Chapter-5 A Single-Stage Quasi-Z-Source Based 5-Level Grid-tied PV Inverter with Reduced Leakage Current.....</b> | 5-1  |

| 5.1    Introduction .....                                                                                            | 5-2  |

| 5.2    The QZS-Based 5-level Hybrid inverter .....                                                                   | 5-3  |

| 5.2.1    Power converter .....                                                                                       | 5-3  |

| 5.2.2    Switching states and corresponding output levels of the power converter .....                               | 5-3  |

| 5.2.3    Boost factor .....                                                                                          | 5-5  |

| 5.3    Modulation scheme .....                                                                                       | 5-6  |

| 5.4    Proposed control strategy for standalone and grid-connected 5L-QZSI .....                                     | 5-7  |

| 5.4.1    Standalone mode .....                                                                                       | 5-7  |

| 5.4.2    The grid-connected mode of operation .....                                                                  | 5-8  |

| 5.5    Reduction of leakage current.....                                                                             | 5-9  |

| 5.6    Experimental Results.....                                                                                     | 5-12 |

| 5.7    Comparison of proposed topology with 5-Level qZSI.....                                                        | 5-18 |

| 5.8    Power Loss for the 5L-QZSI.....                                                                               | 5-20 |

| 5.9    Summary .....                                                                                                 | 5-21 |

| <b>Chapter-6 A Quasi-Switched Capacitor Based Grid-connected PV Inverter with a Reduced Leakage Current.....</b>     | 6-1  |

| 6.1    Introduction .....                                                                                            | 6-2  |

| 6.2    The QSC-Based five-level T-type inverter .....                                                                | 6-3  |

| 6.2.1    Power Converter .....                                                                                       | 6-3  |

| 6.2.2    Switching logic of the qSC-5LI .....                                                                        | 6-3  |

| 6.3    Modulation Technique .....                                                                                    | 6-5  |

| 6.3.1    Proposed modulation technique for qSB-5LI.....                                                              | 6-5  |

| 6.3.2    Analysis of the Boost Factor.....                                                                           | 6-6  |

| 6.4    Proposed closed-loop control schemes for qSB-5LI.....                                                         | 6-7  |

| 6.4.1    Standalone mode .....                                                                                       | 6-7  |

| 6.4.2    Grid-connected mode .....                                                                                   | 6-8  |

| 6.5    Reduction of Leakage current .....                                                                            | 6-9  |

| 6.6    Experimental results .....                                                                                    | 6-10 |

| 6.7    Comparison between the proposed qSC-5LI and the qZS-based five-level inverter topologies .....                | 6-15 |

| 6.8    Loss Distribution in qSC-5LI.....                                                                             | 6-16 |

| 6.9    Summary .....                                                                                                 | 6-17 |

| <b>Chapter-7 Conclusion and Future Scope .....</b>                                                                   | 7-1  |

| 7.1    Conclusion.....                                                                                               | 7-2  |

| 7.2    Future Scope.....                                                                                             | 7-3  |

|                          |            |

|--------------------------|------------|

| <b>Appendix-1 .....</b>  | <b>A-1</b> |

| <b>References .....</b>  | <b>R-1</b> |

| <b>Publications.....</b> | <b>P-1</b> |

## List of Figures

|            |                                                                                             |      |

|------------|---------------------------------------------------------------------------------------------|------|

| Fig. 1.1:  | General layout of a grid-tied PV inverter.                                                  | 1-2  |

| Fig. 1.2:  | Overview of PV inverters (a) Central inverter (b) string inverter (c) Microinverter.        | 1-4  |

| Fig. 1.3:  | Block diagram of (a) Two-stage power converter (b) Single-stage power converter.            | 1-5  |

| Fig. 1.4:  | Parasitic capacitances in a typical PV Panel.                                               | 1-6  |

| Fig. 2.1:  | The Z-source inverter                                                                       | 2-2  |

| Fig. 2.2:  | Quasi-Z-source inverter                                                                     | 2-4  |

| Fig. 2.3:  | Classification of impedance source networks                                                 | 2-5  |

| Fig. 2.4:  | Embedded Z-source network                                                                   | 2-6  |

| Fig. 2.5:  | Switched inductor Z-source network                                                          | 2-6  |

| Fig. 2.6:  | Capacitor/diode assisted qZS network                                                        | 2-6  |

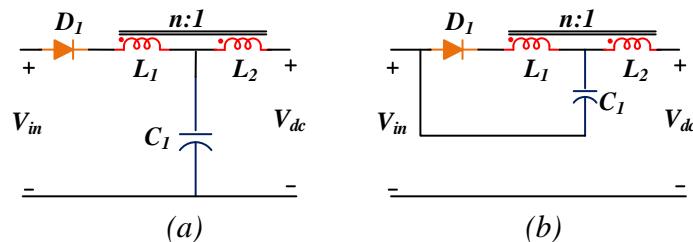

| Fig. 2.7:  | (a) Switch Boost inverter (b) Trans-switch boost inverter                                   | 2-7  |

| Fig. 2.8:  | (a) Trans. ZSN (b) Trans.QZSN                                                               | 2-7  |

| Fig. 2.9:  | (a) LCCT ZSI (b) LCCT QZSI                                                                  | 2-8  |

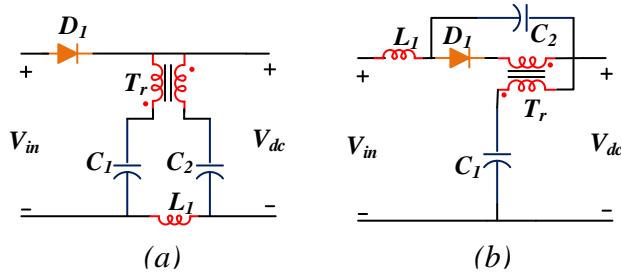

| Fig. 2.10: | Z-source NPC three-level inverter                                                           | 2-9  |

| Fig. 2.11: | (a) Single Z-source NPC three-level inverter (b) Modified Z-source NPC three-level inverter | 2-10 |

| Fig. 2.12: | Quasi-Z-source NPC three-level inverter                                                     | 2-10 |

| Fig. 2.13: | A three-level Quasi-Z-source based T-type inverter.                                         | 2-11 |

| Fig. 2.14: | Quasi-Z-source CHB inverter                                                                 | 2-11 |

| Fig. 2.15: | Z-source seven-level inverter                                                               | 2-12 |

| Fig. 2.16: | Quasi-Z-source single-phase CHB inverter                                                    | 2-13 |

| Fig. 2.17: | Quasi-switched boost inverter                                                               | 2-13 |

|            |                                                                                                                                                                                                                  |      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2.18: | Modified quasi-Z-source five-level inverter                                                                                                                                                                      | 2-14 |

| Fig. 2.19: | Quasi-Z-source with additional switches                                                                                                                                                                          | 2-15 |

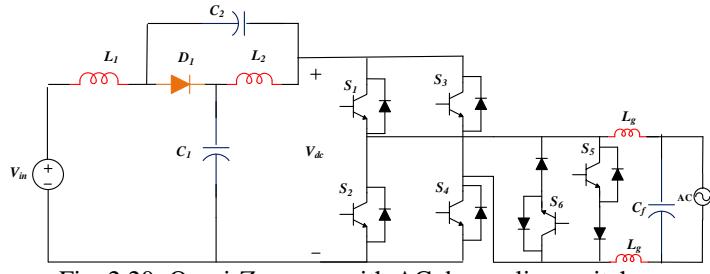

| Fig. 2.20: | Quasi-Z-source with AC decoupling switches                                                                                                                                                                       | 2-15 |

| Fig. 3.1:  | Proposed qZS-FCMI.                                                                                                                                                                                               | 3-3  |

| Fig. 3.2:  | Implementation of phase-A switching for qZS-FCMI.                                                                                                                                                                | 3-6  |

| Fig. 3.3:  | Space vector diagram of FCMI.                                                                                                                                                                                    | 3-7  |

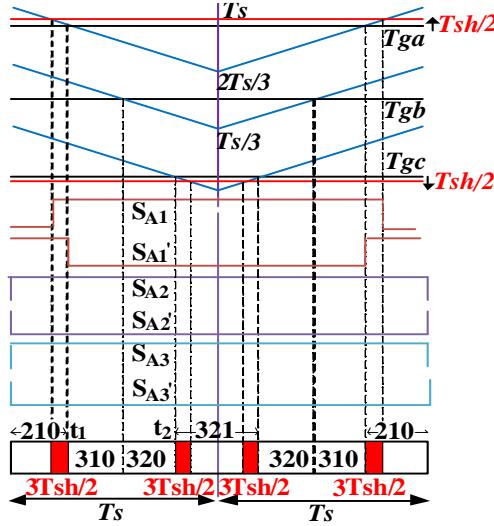

| Fig. 3.4:  | Switching sequence of FCMI when reference phasor is in sector HVW.                                                                                                                                               | 3-8  |

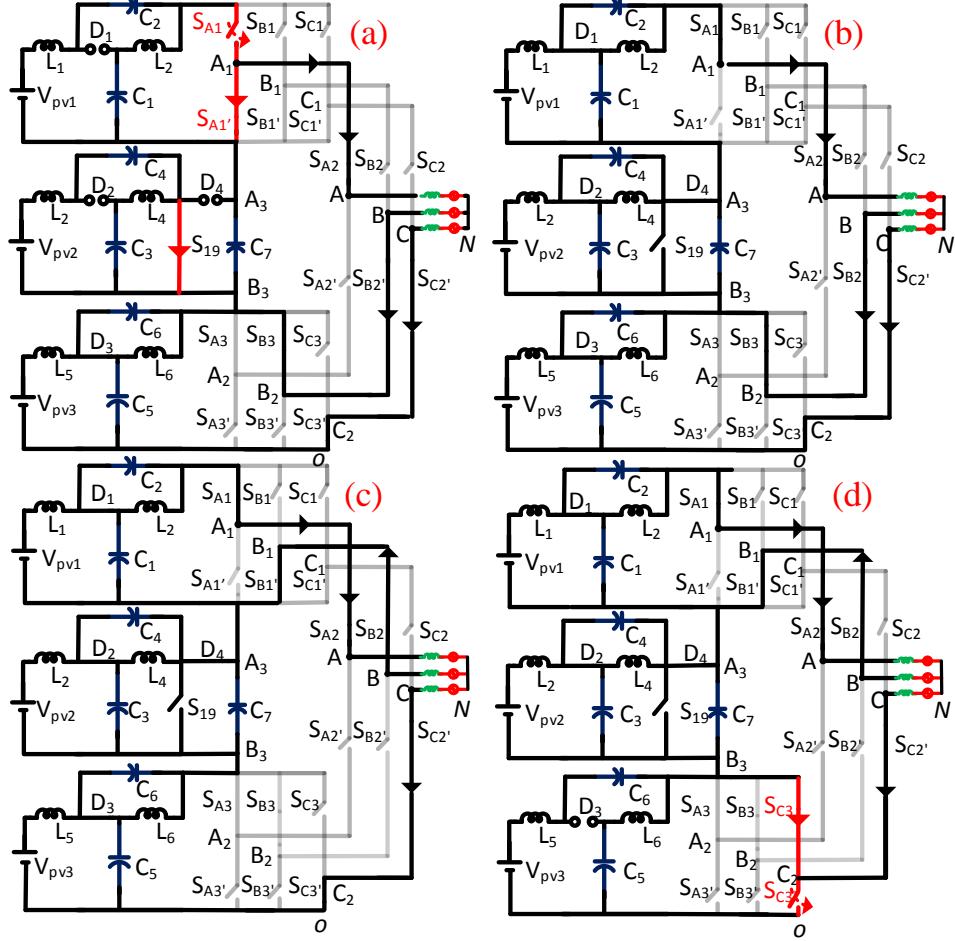

| Fig. 3.5:  | Circuit diagrams for switching states mentioned in Fig. 3.4 (a) [210] state (b) [310] state (c) [320] state (d)[321] state in a given sample time $T_s$ .                                                        | 3-9  |

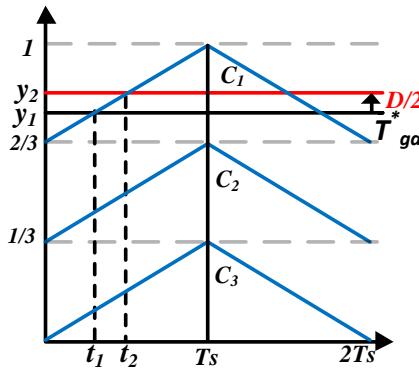

| Fig. 3.6:  | Scaling of boost factor by LSPWM technique.                                                                                                                                                                      | 3-10 |

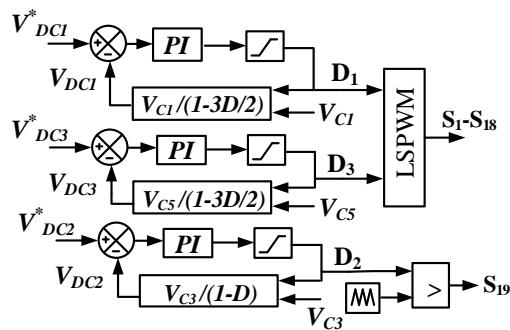

| Fig. 3.7:  | DC-link voltage control scheme for the proposed FCMI.                                                                                                                                                            | 3-12 |

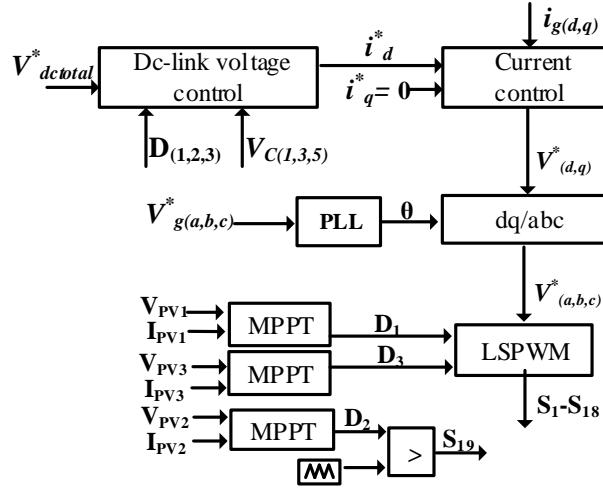

| Fig. 3.8:  | Block diagram of the grid control scheme.                                                                                                                                                                        | 3-14 |

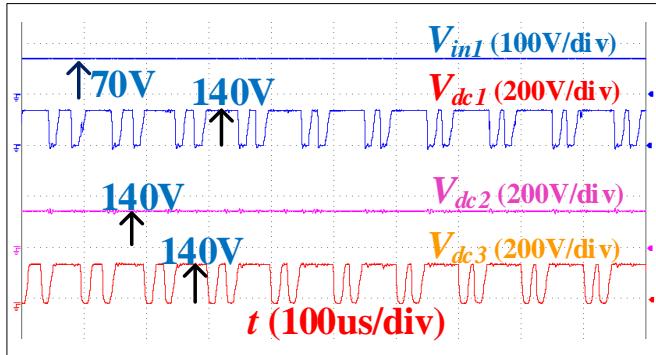

| Fig. 3.9:  | Experimental results of input voltage ( $V_{in1}$ ) and DC-link voltages ( $V_{dc1}$ , $V_{dc2}$ , $V_{dc3}$ ) of FCMI.                                                                                          | 3-15 |

| Fig. 3.10: | Experimental results of input voltage ( $V_{in1}$ ) and DC-link voltages ( $V_{dc1}$ , $V_{dc2}$ , $V_{dc3}$ ) of FCMI.                                                                                          | 3-16 |

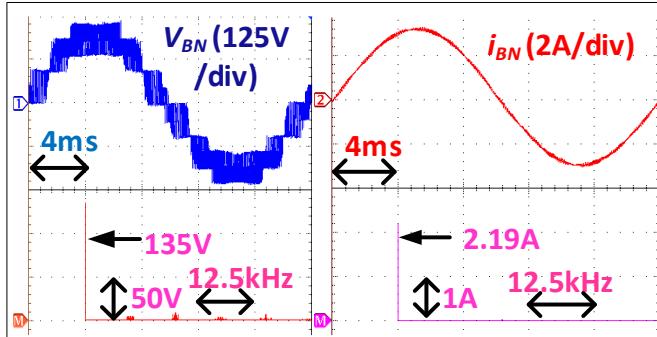

| Fig. 3.11: | Experimental results of Pole voltage waveform ( $V_{BO}$ ), Line voltage ( $V_{BC}$ ), Phase voltage ( $V_{BN}$ ), and Phase current ( $i_B$ ) of FCMI.                                                          | 3-16 |

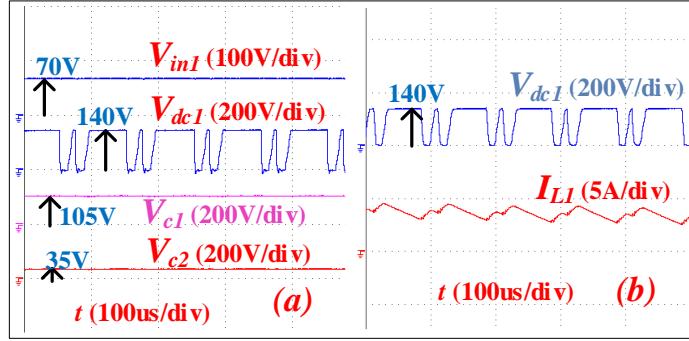

| Fig. 3.12: | Harmonic spectrum of the output phase voltage ( $V_{BN}$ ) and phase current( $i_{BN}$ ).                                                                                                                        | 3-17 |

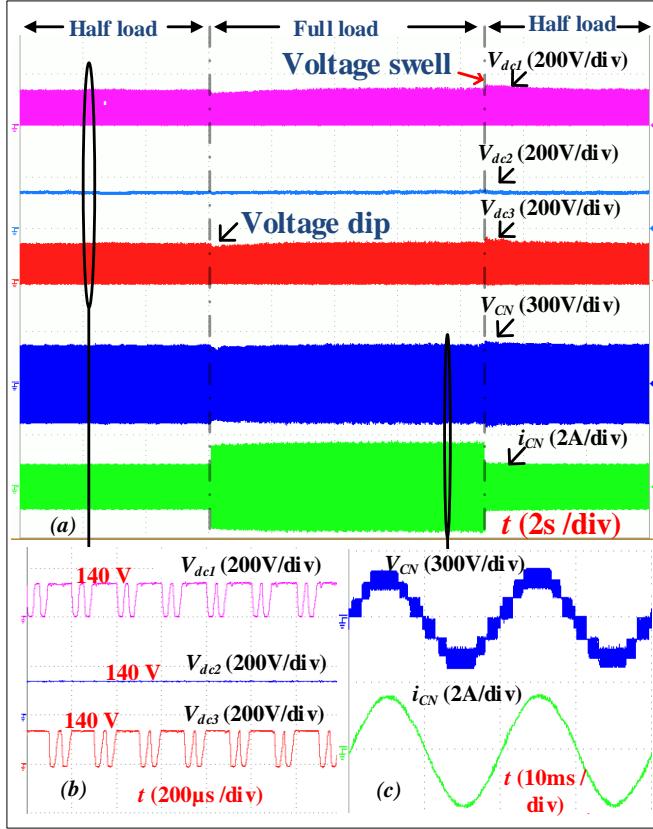

| Fig. 3.13: | Experimental results (a) DC-link voltage waveforms of qZS-FCMI and the load voltage and current in phase C (b) Zoom-in view of the DC-link voltages (C) Zoom-in view of the load voltage and current in phase C. | 3-18 |

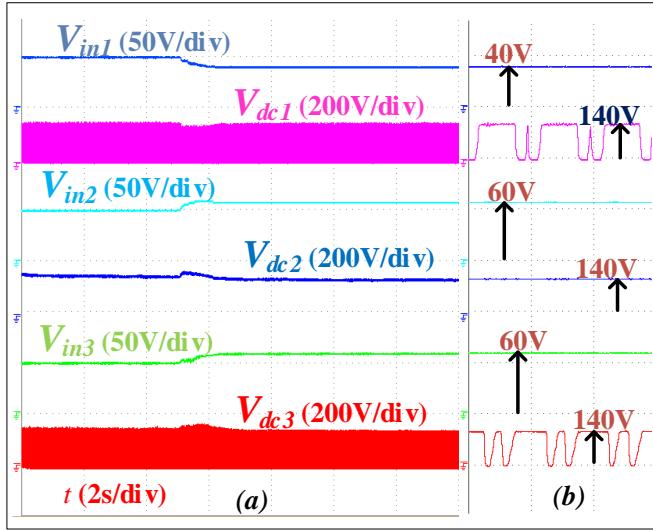

| Fig. 3.14: | Experimental results (a) DC-link voltages and input voltage waveforms of FCMI during source disturbance (b) Zoom-in view of the DC-link voltages of the FCMI.                                                    | 3-18 |

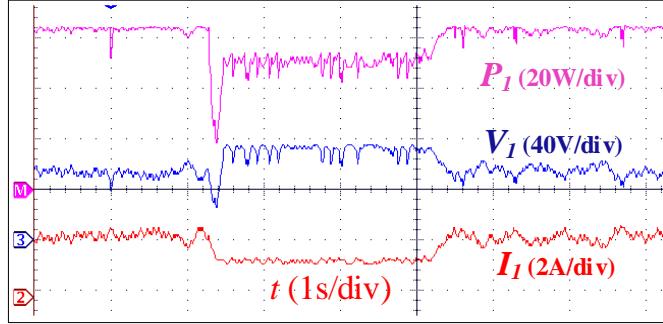

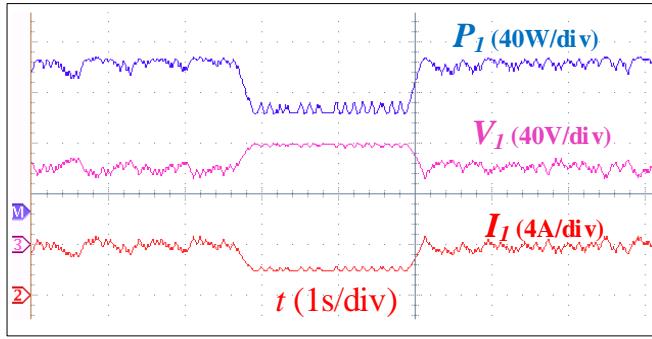

| Fig. 3.15: | Experimental results of MPPT control of PV-1                                                                                                                                                                     | 3-19 |

|            |                                                                                                                                                                                                   |      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3.16: | Experimental results of MPPT control of PV-2.                                                                                                                                                     | 3-19 |

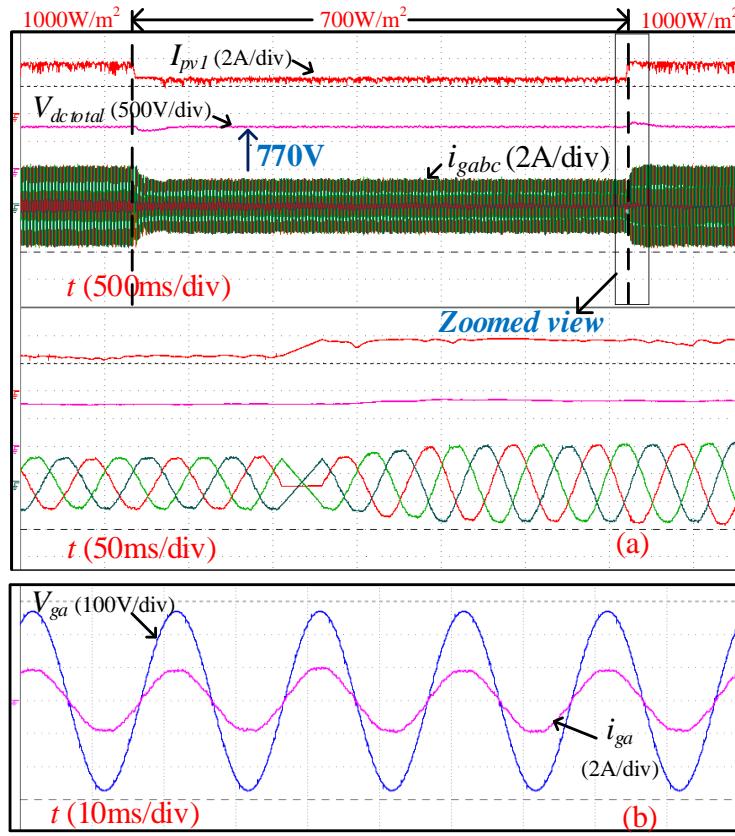

| Fig. 3.17: | Experimental results (a) PV current ( $I_{pv1}$ ), total dc-link voltage ( $V_{dc\text{total}}$ ), grid currents ( $I_{gabc}$ ) (b) grid voltage and grid current.                                | 3-20 |

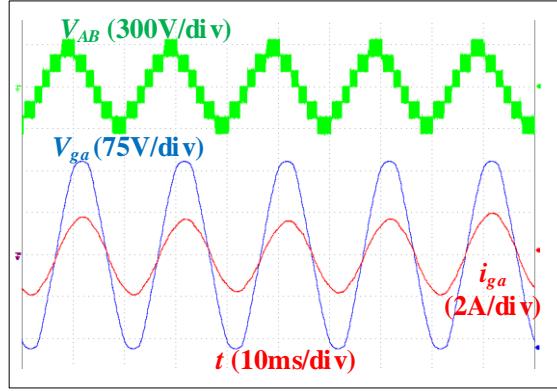

| Fig. 3.18: | Experimental result of inverter line voltage ( $V_{AB}$ ) and grid voltage ( $V_{ga}$ ) and grid current ( $i_{ga}$ ) waveforms.                                                                  | 3-21 |

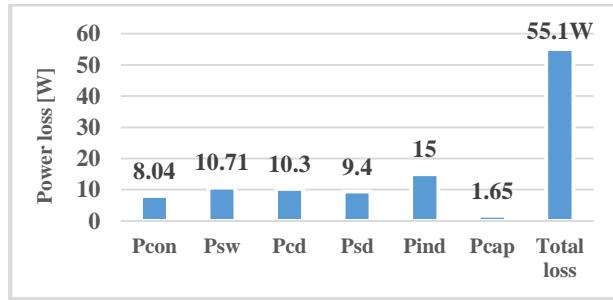

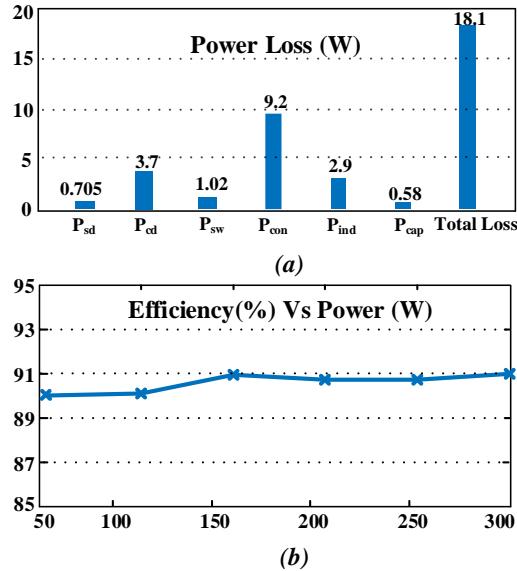

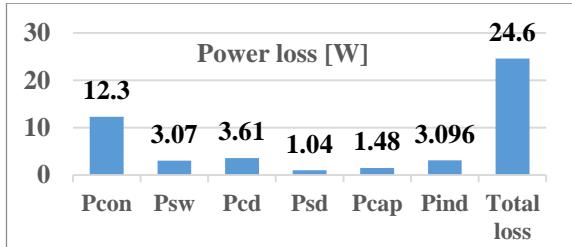

| Fig. 3.19: | Loss distribution in the device for qZS-FCMI.                                                                                                                                                     | 3-23 |

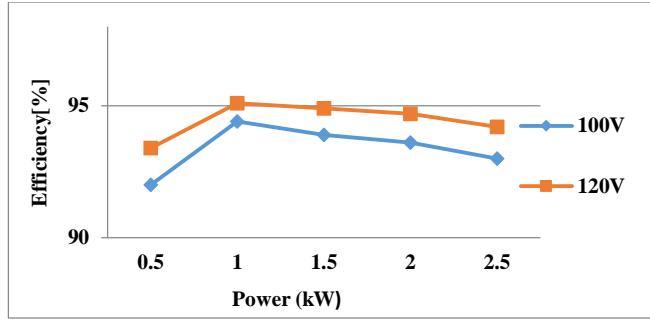

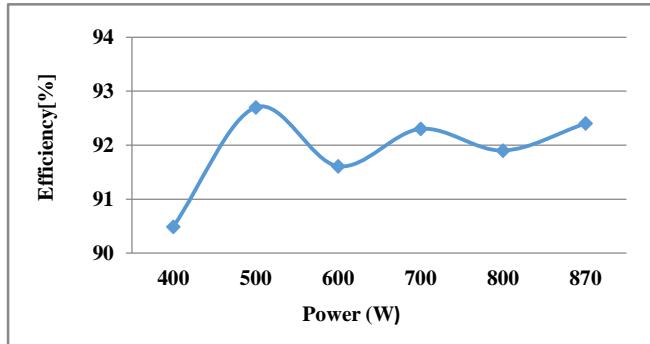

| Fig. 3.20: | Calculated efficiency of the proposed qZSI-FLI for two different input voltages.                                                                                                                  | 3-24 |

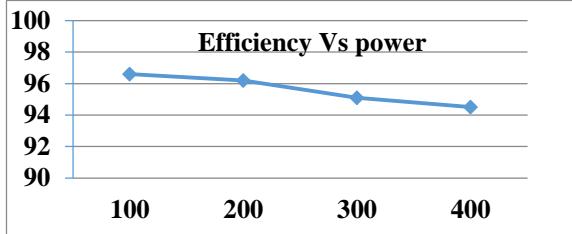

| Fig. 3.21: | Experimental efficiency of the proposed qZSI-FLI                                                                                                                                                  | 3-24 |

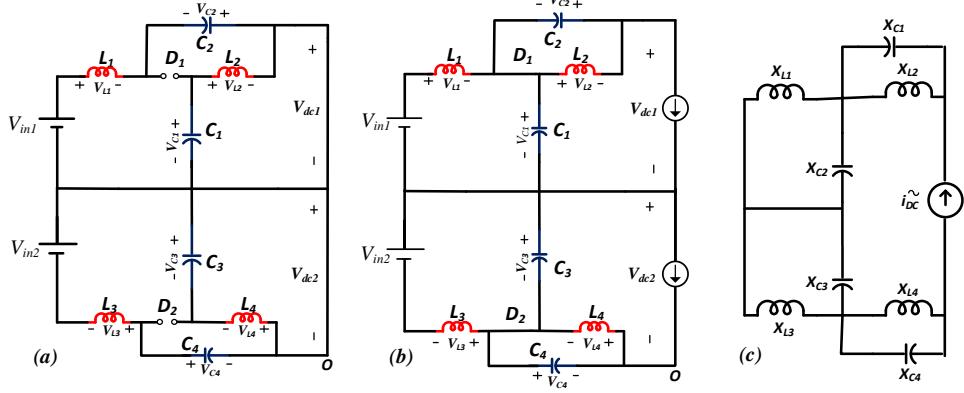

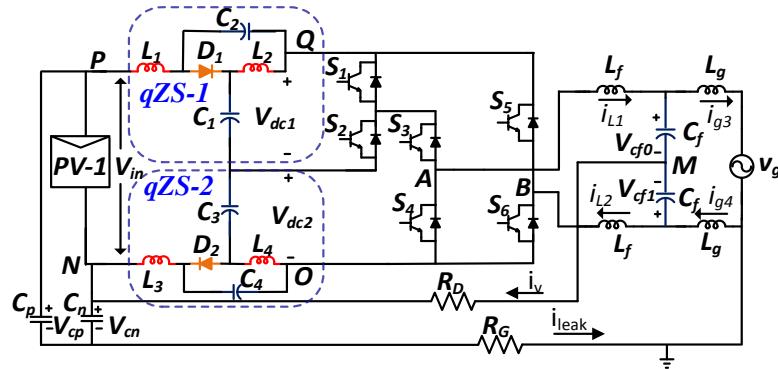

| Fig. 4.1:  | Proposed DqZS-7LI.                                                                                                                                                                                | 4-3  |

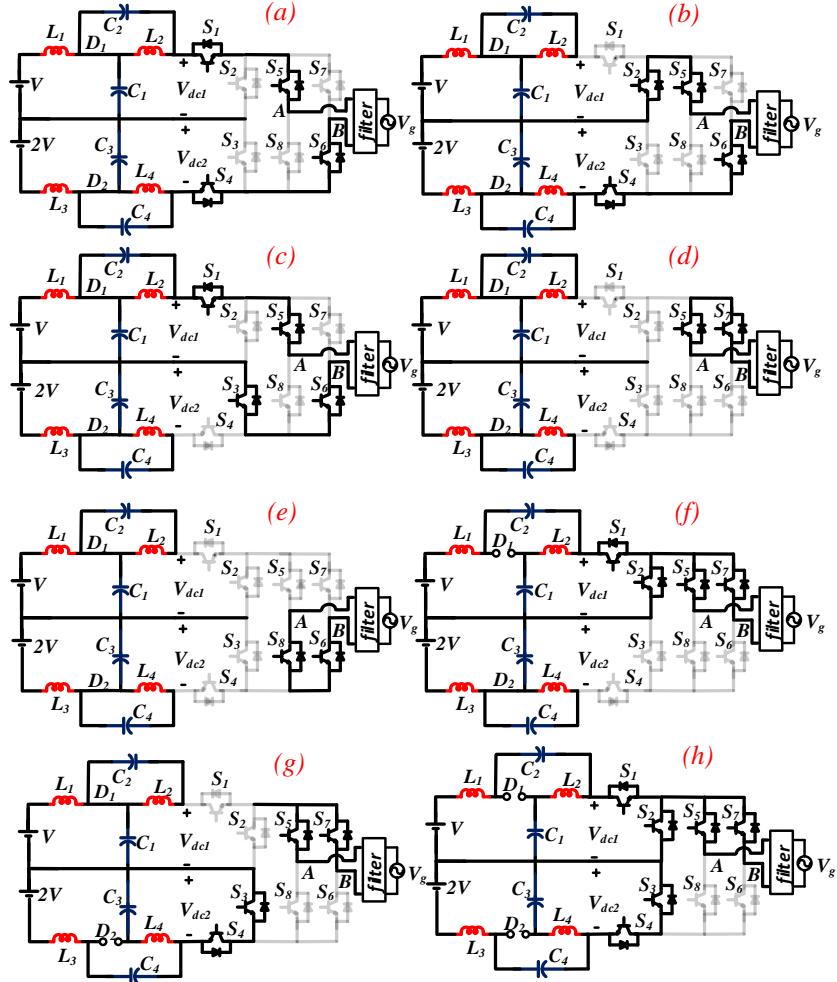

| Fig. 4.2:  | Circuit diagrams for NST and ST states of the power converter.                                                                                                                                    | 4-5  |

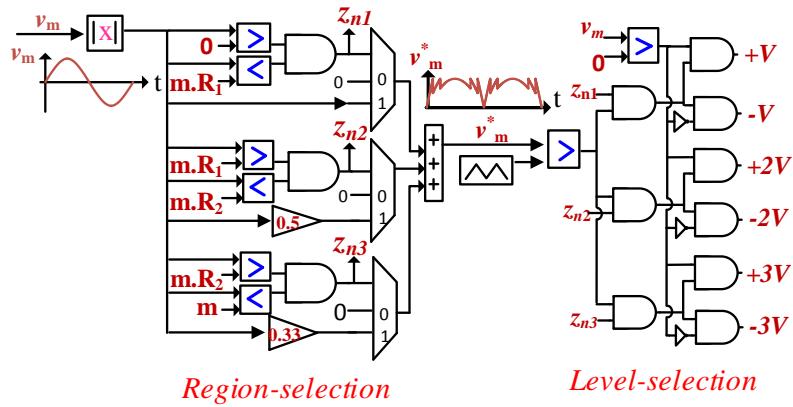

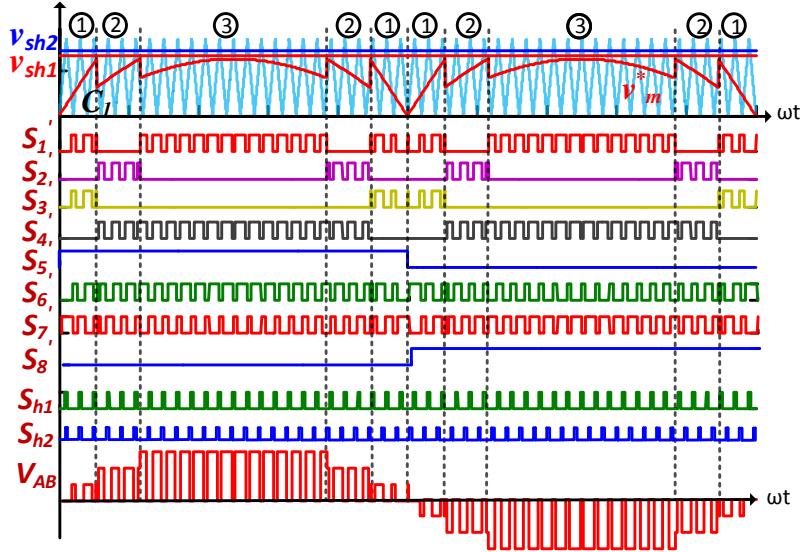

| Fig. 4.3:  | Implementation of modified reference wave ( $v_m^*$ ) for DqZS-7LI.                                                                                                                               | 4-6  |

| Fig. 4.4:  | Implementation of modulation technique.                                                                                                                                                           | 4-7  |

| Fig. 4.5:  | Equivalent circuit of DqZS-7LI during (a) shoot-through state (ST) (b) non-shoot-through (NST) state. (c) Simplified equivalent circuit.                                                          | 4-8  |

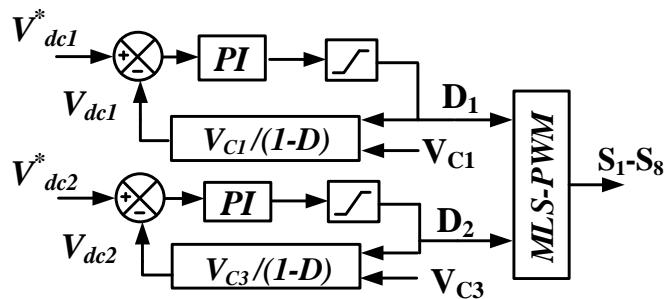

| Fig. 4.6:  | Closed-loop DC-link voltage control for the proposed DqZS-7LI.                                                                                                                                    | 4-9  |

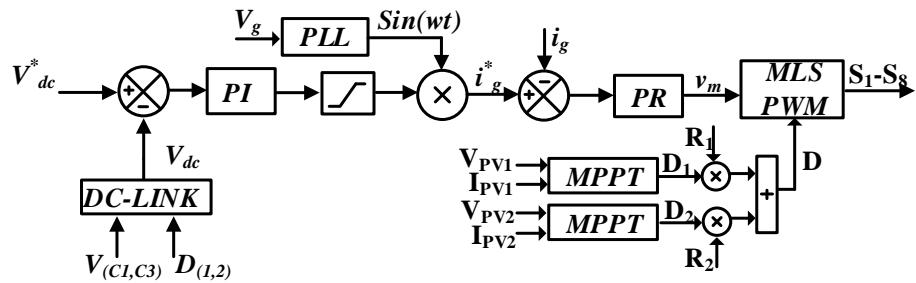

| Fig. 4.7:  | The grid control scheme for DqZS-7LI.                                                                                                                                                             | 4-10 |

| Fig. 4.8:  | (a) DqZS-7LI with leakage ground current path (b) equivalent circuit of the differential-mode model(c) equivalent circuit of the common-mode model.                                               | 4-12 |

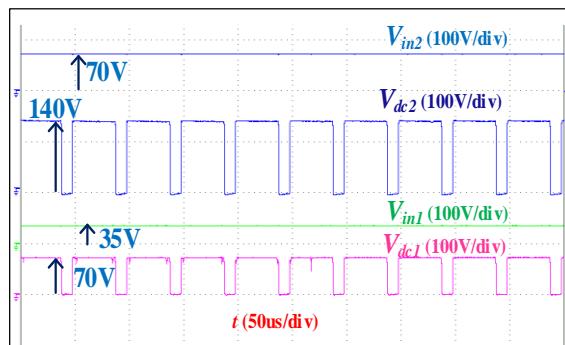

| Fig. 4.9:  | Experimental results of DC-input voltages ( $V_{in1}$ , $V_{in2}$ ) and DC-link voltages ( $V_{dc1}$ , $V_{dc2}$ ) of DqZS-7LI.                                                                   | 4-14 |

| Fig. 4.10: | Experimental results of the DC input voltage ( $V_{in2}$ ), DC-link voltage ( $V_{dc2}$ ) and inductor current ( $i_{L4}$ ), and capacitor voltages ( $V_{c3}$ , $V_{c4}$ ) of the qZS-1 network. | 4-15 |

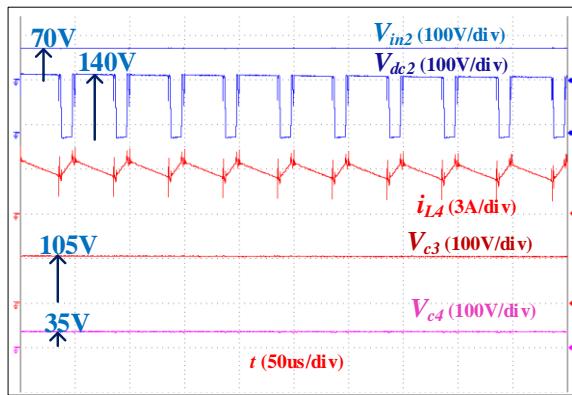

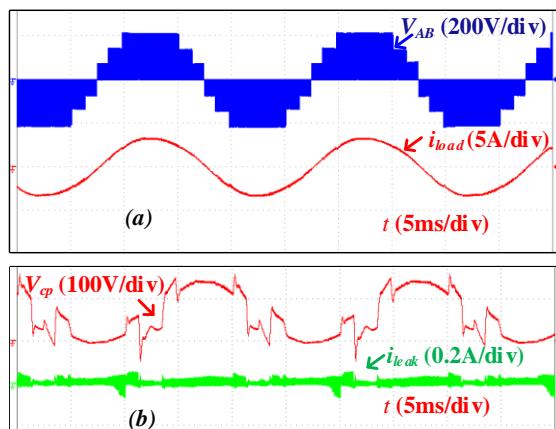

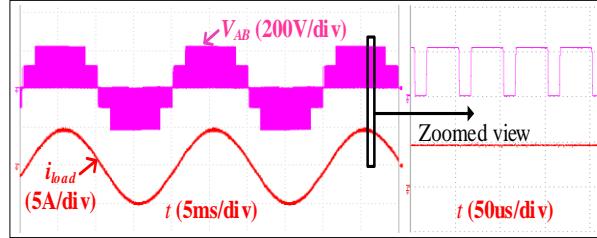

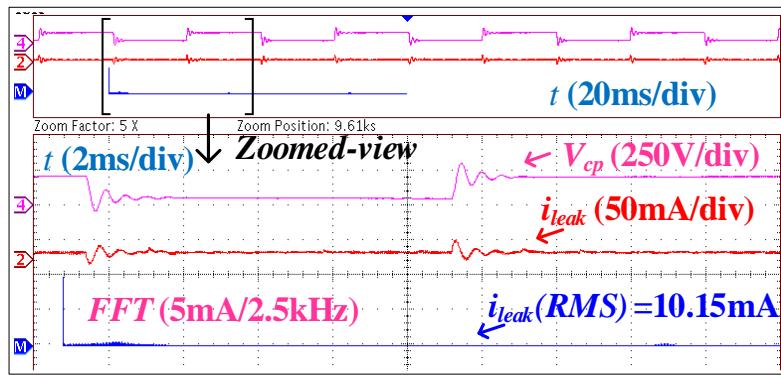

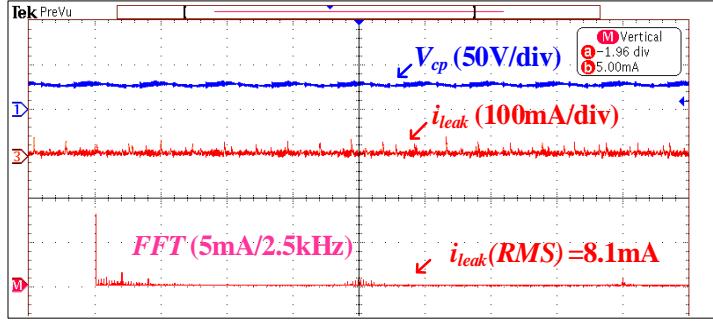

| Fig. 4.11: | Experimental results of (a) Output voltage waveform ( $V_{AB}$ ), Load voltage ( $i_{Load}$ ) (b) Parasitic capacitor voltage ( $V_{cp}$ ), and Leakage current ( $i_{leak}$ ) of DqZS-7LI.       | 4-15 |

|            |                                                                                                                                                                                                                            |      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

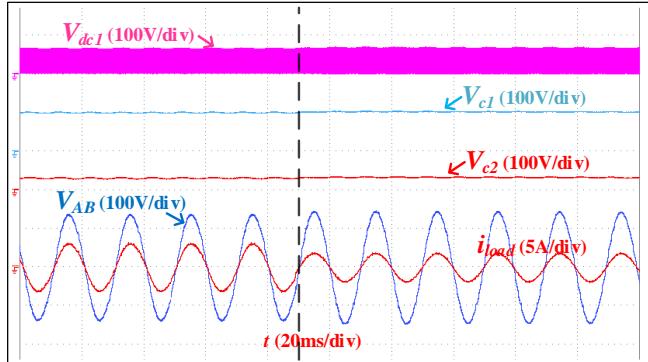

| Fig. 4.12: | Experimental results of DC-link voltage ( $V_{dc1}$ ), capacitor voltages ( $V_{c1}$ , $V_{c2}$ ), output voltage ( $V_{AB}$ ), and the load current ( $i_{load}$ ).                                                       | 4-16 |

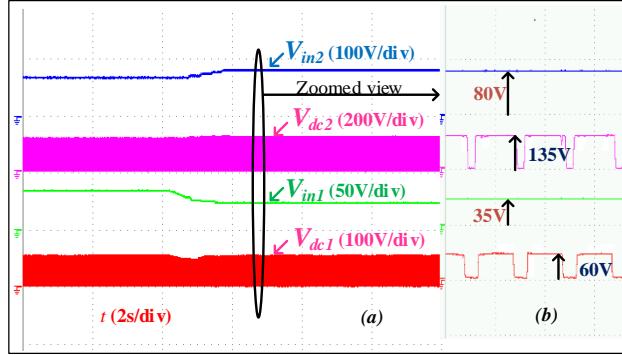

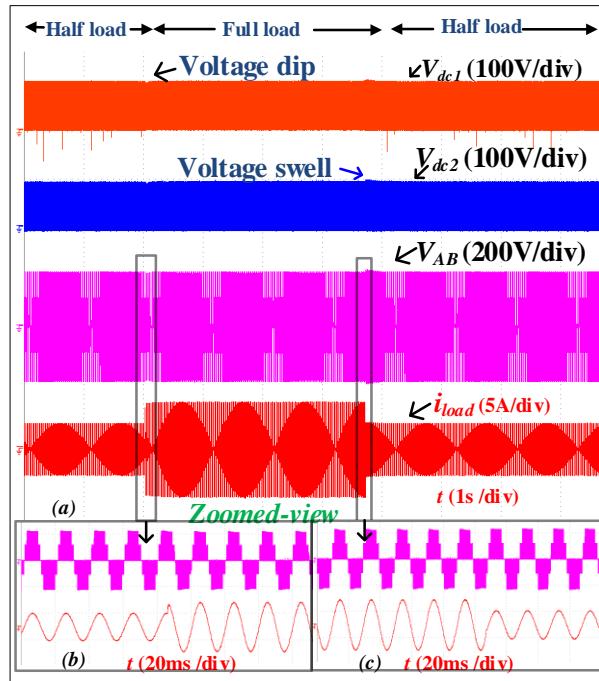

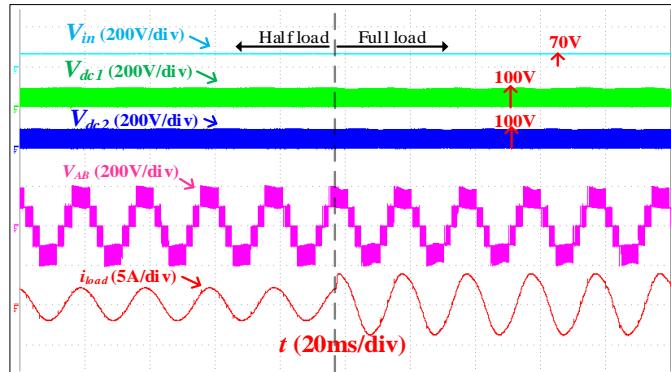

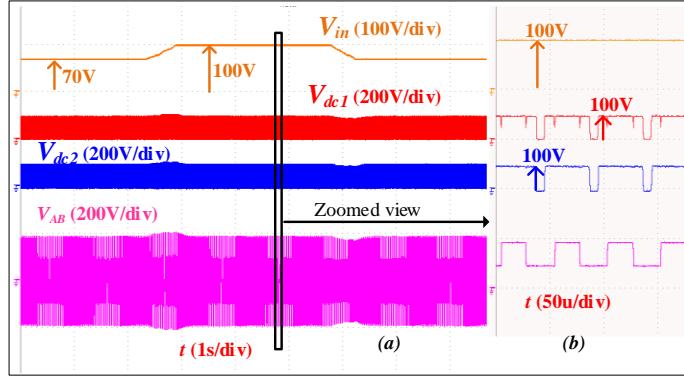

| Fig. 4.13: | Experimental results of (a) DC input voltages ( $V_{in1}$ , $V_{in2}$ ) and DC-link voltages waveforms of DqZS-7LI in the course of source disturbance (b) Zoomed view of the DC-link and DC input voltages of the DqZS-7L | 4-17 |

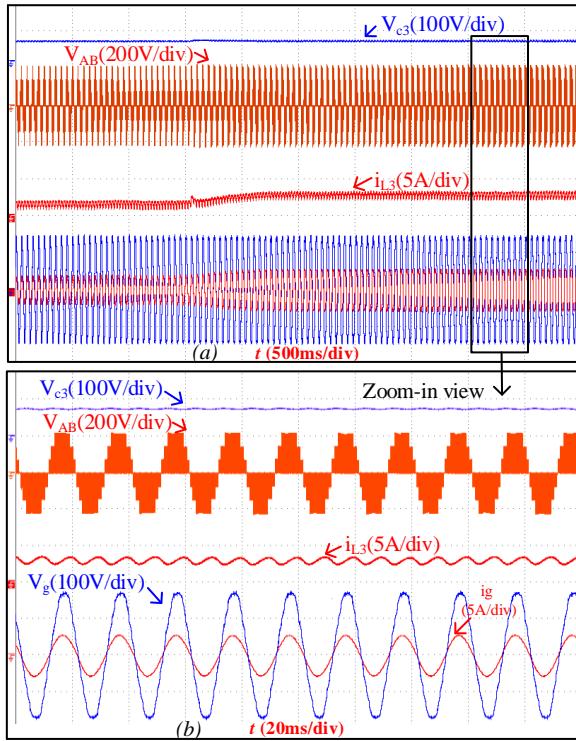

| Fig. 4.14: | Experimental results (a) Capacitor voltage ( $V_{c3}$ ), Phase voltage ( $V_{AB}$ ), Inductor current ( $i_{L3}$ ) Grid voltage ( $V_g$ ), and Grid current ( $i_g$ ) (b) Zoom-in view at 300W.                            | 4-17 |

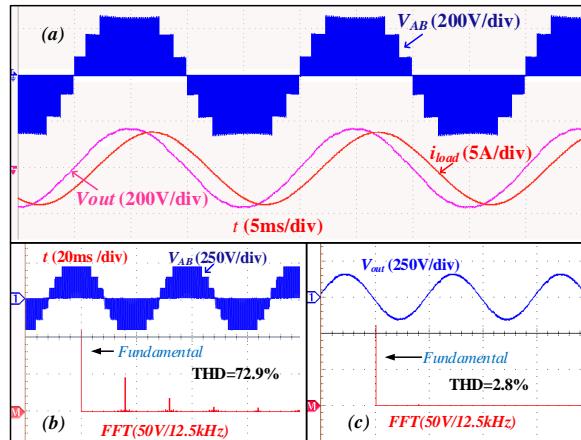

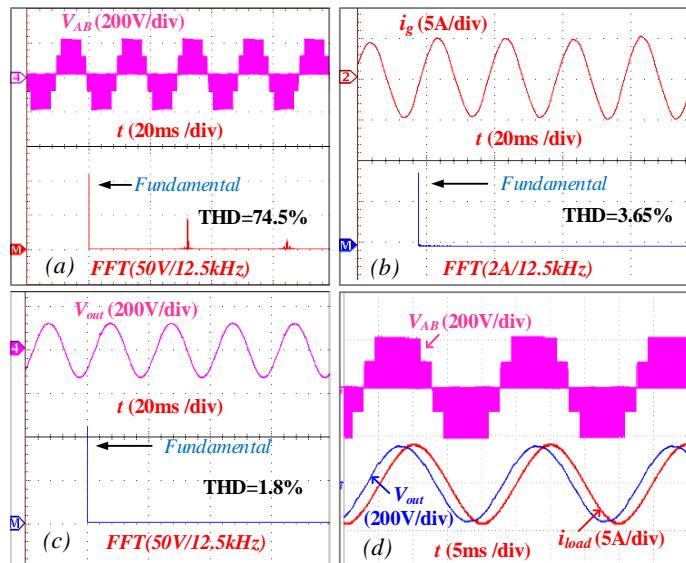

| Fig. 4.15: | (a) Output voltage ( $V_{AB}$ ), load voltage ( $V_{out}$ ), and load current ( $i_{load}$ ) for 0.8 lagging power factor (b) FFT of inverter output voltage ' $V_{AB}$ ' (c) FFT of output voltage ' $V_{out}$ '          | 4-18 |

| Fig. 4.16: | (a). Power Loss distribution in DqZS-7LI at 300W. (b) Experimental efficiency of the proposed DqZS-7LI.                                                                                                                    | 4-21 |

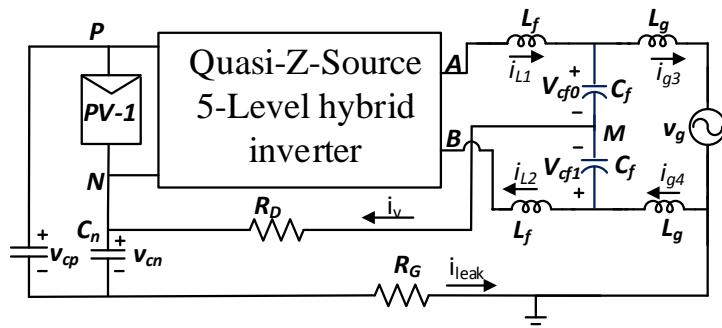

| Fig. 5.1:  | The Proposed 5L-qZSI                                                                                                                                                                                                       | 5-3  |

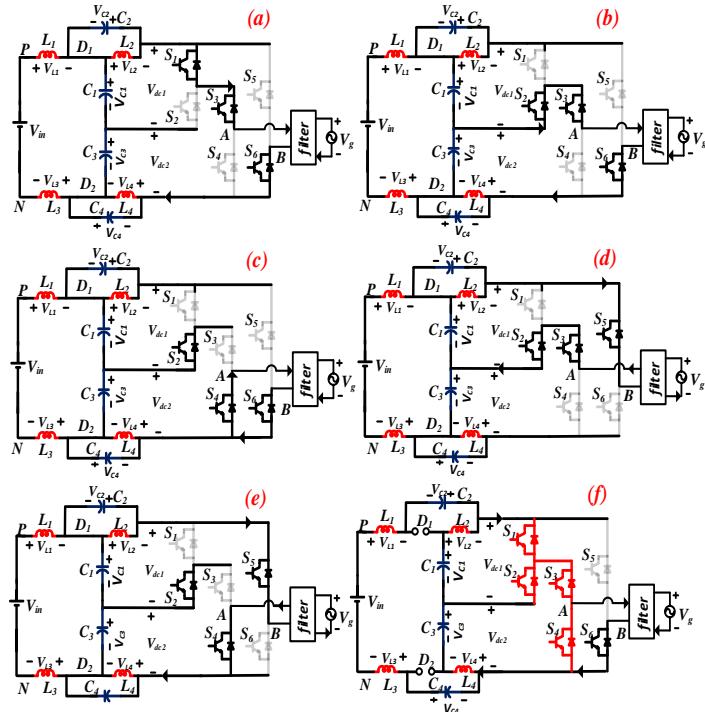

| Fig. 5.2:  | Circuit diagrams for NST and ST states of the power converter.                                                                                                                                                             | 5-4  |

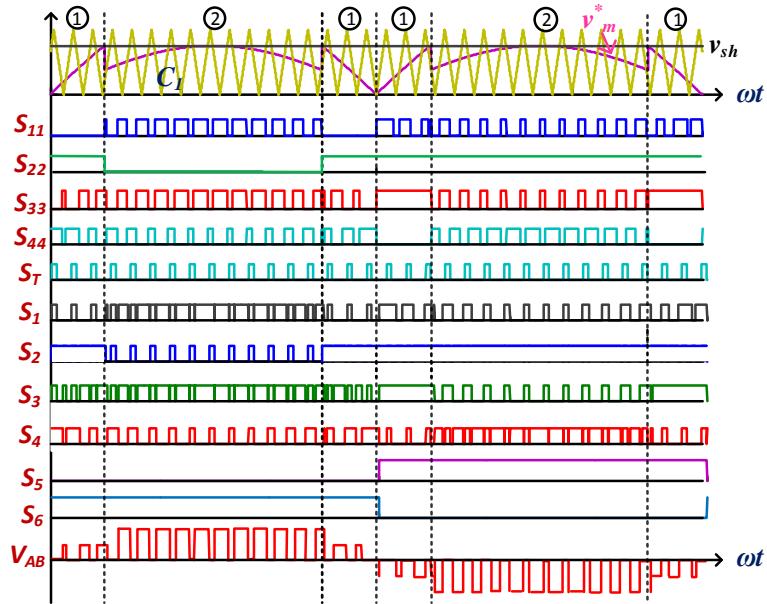

| Fig. 5.3:  | Implementation of the modulation scheme for 5L-qZSI.                                                                                                                                                                       | 5-6  |

| Fig. 5.4:  | Implementation of the modulation technique.                                                                                                                                                                                | 5-7  |

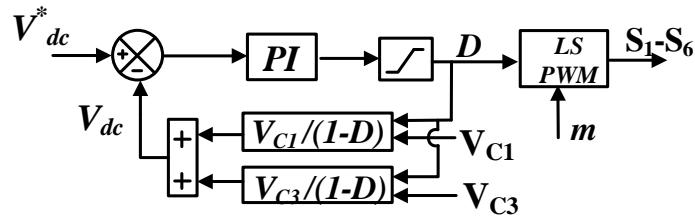

| Fig. 5.5:  | Indirect DC-link voltage regulation of the proposed 5L-qZSI.                                                                                                                                                               | 5-8  |

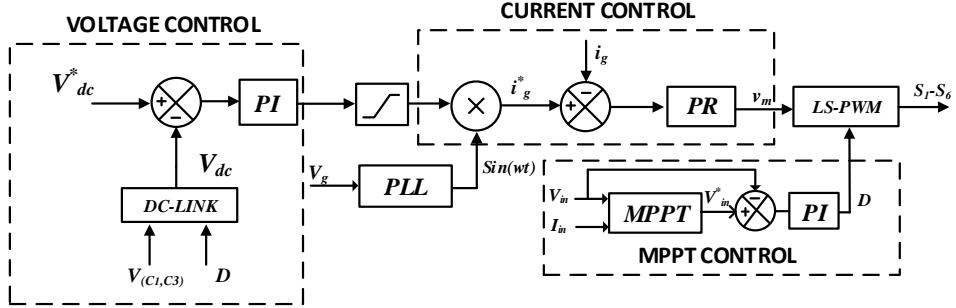

| Fig. 5.6:  | The control scheme for grid-tied 5L-qZSI.                                                                                                                                                                                  | 5-9  |

| Fig. 5.7:  | 5L-qZSI with leakage current path.                                                                                                                                                                                         | 5-11 |

| Fig. 5.8:  | Equivalent circuit of the common-mode model.                                                                                                                                                                               | 5-11 |

| Fig. 5.9:  | The simplified equivalent circuit.                                                                                                                                                                                         | 5-12 |

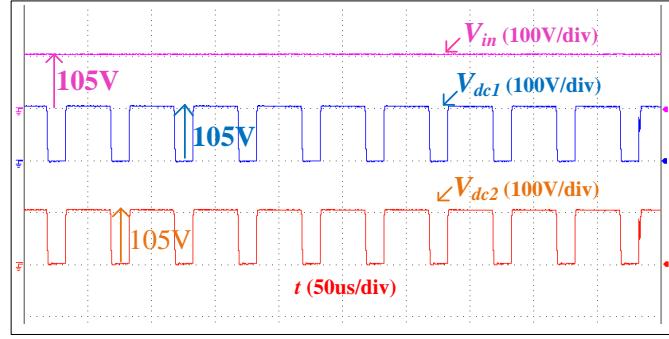

| Fig. 5.10: | Experimental results of input voltage ( $V_{in}$ ) and DC-link voltages $V_{dc1}$ & $V_{dc2}$ .                                                                                                                            | 5-14 |

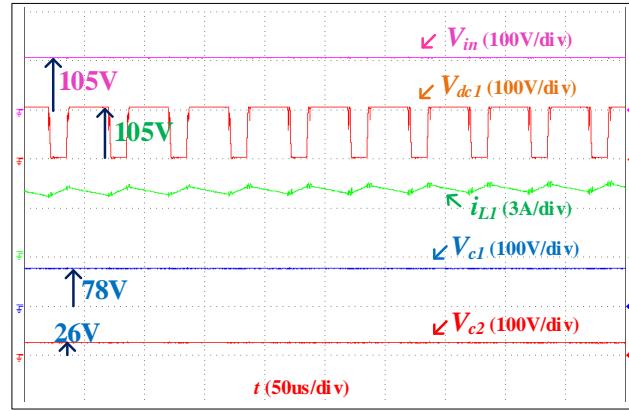

| Fig. 5.11: | Experimental results of the input voltage ( $V_{in1}$ ), DC-link voltage ( $V_{dc1}$ ), inductor current ( $i_{L1}$ ), and capacitor voltages ( $V_{c1}$ , $V_{c2}$ ).                                                     | 5-14 |

| Fig. 5.12: | Experimental waveforms of output voltage ( $V_{AB}$ ) and load current ( $i_{load}$ ).                                                                                                                                     | 5-15 |

| Fig. 5.13: | Experimental results of parasitic capacitor voltage ( $V_{cp}$ ), leakage current ( $i_{leak}$ ) of the PV source, and harmonic spectrum of leakage current.                                                               | 5-15 |

|            |                                                                                                                                                                                                                                                     |      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 5.14: | Experimental results of DC-link voltages ( $V_{dc1}$ & $V_{dc2}$ ), output voltage ( $V_{AB}$ ) and load current ( $i_{load}$ ).                                                                                                                    | 5-16 |

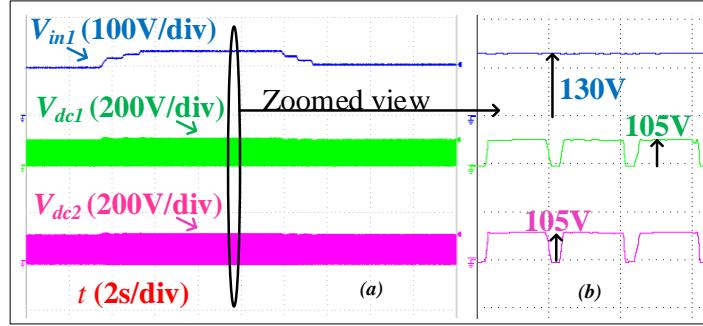

| Fig. 5.15: | Experimental results of (a) input voltages ( $V_{in1}$ ) and DC-link voltages ( $V_{dc1}$ & $V_{dc2}$ ) (b) Zoomed view of the plot (a).                                                                                                            | 5-17 |

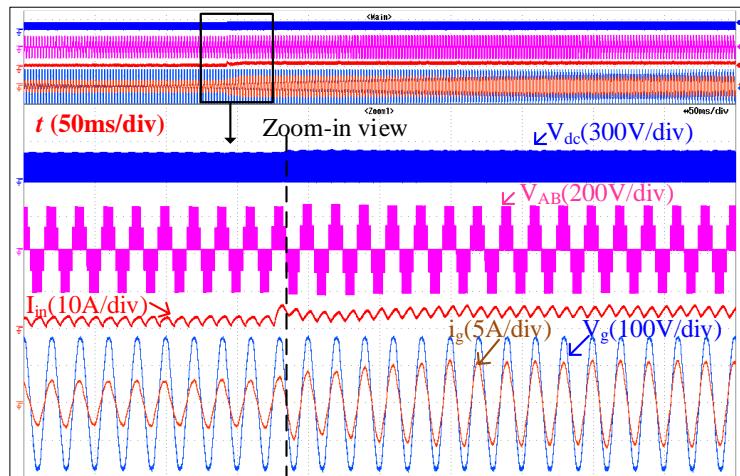

| Fig. 5.16: | Experimental results of the total DC link voltage, output voltage of the inverter ( $V_{AB}$ ), grid voltage ( $V_g$ ), and current ( $i_g$ ).                                                                                                      | 5-17 |

| Fig. 5.17: | (a) FFT of inverter output voltage ' $V_{AB}$ ' (b) FFT of grid current ' $i_g$ ' (c) FFT of output voltage ' $V_{out}$ ' (d) output voltage ( $V_{AB}$ ), load voltage ( $V_{out}$ ) and load current ( $i_{load}$ ) for 0.8 lagging power factor. | 5-18 |

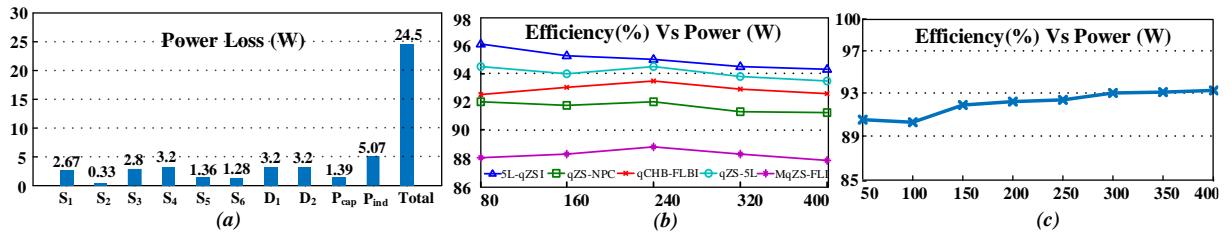

| Fig. 5.18: | (a) Power Loss distribution in 5L-qZSI. (b) Efficiency comparison with the 5L-qZSI (c) Experimental efficiency of the 5L-qZSI                                                                                                                       | 5-21 |

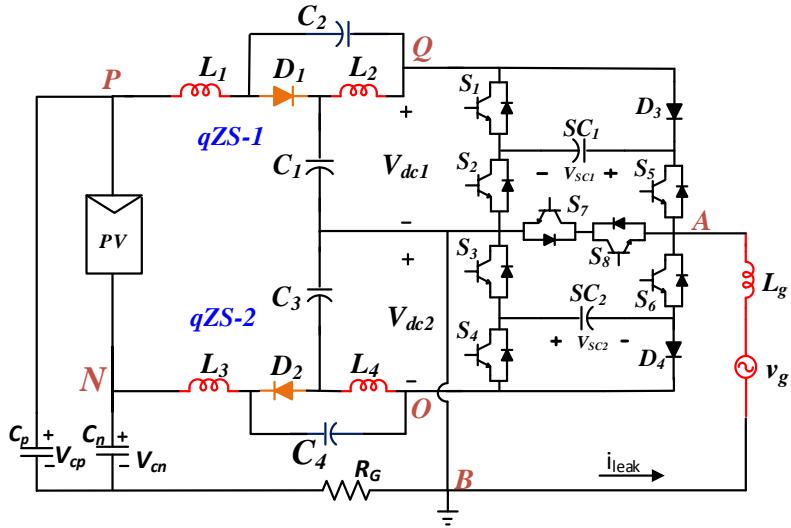

| Fig. 6.1:  | The Proposed qSC-5LI                                                                                                                                                                                                                                | 6-3  |

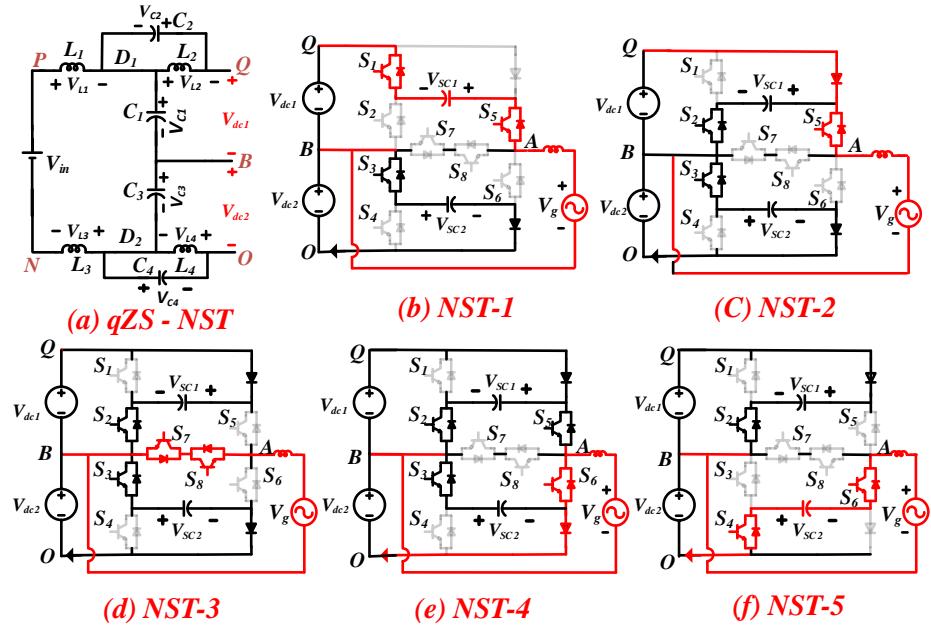

| Fig. 6.2:  | (a) Schematic of qZS network during NST states (b-f) Schematic of MLI during NST-1 to NST-6.                                                                                                                                                        | 6-4  |

| Fig. 6.3:  | (a) Schematic of qZS network during ST states (b-d) Schematic of MLI during ST-1 to ST-3.                                                                                                                                                           | 6-5  |

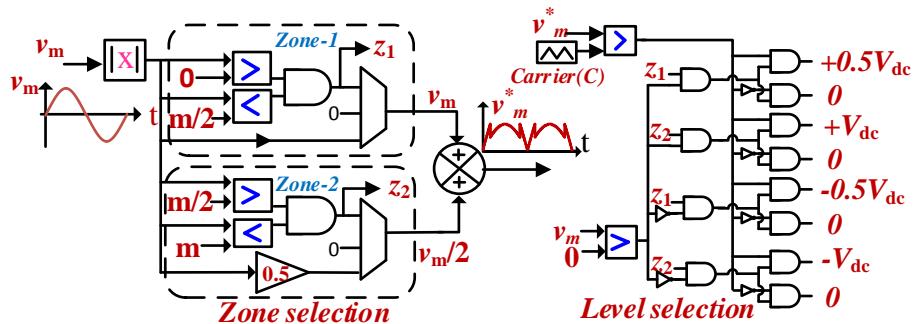

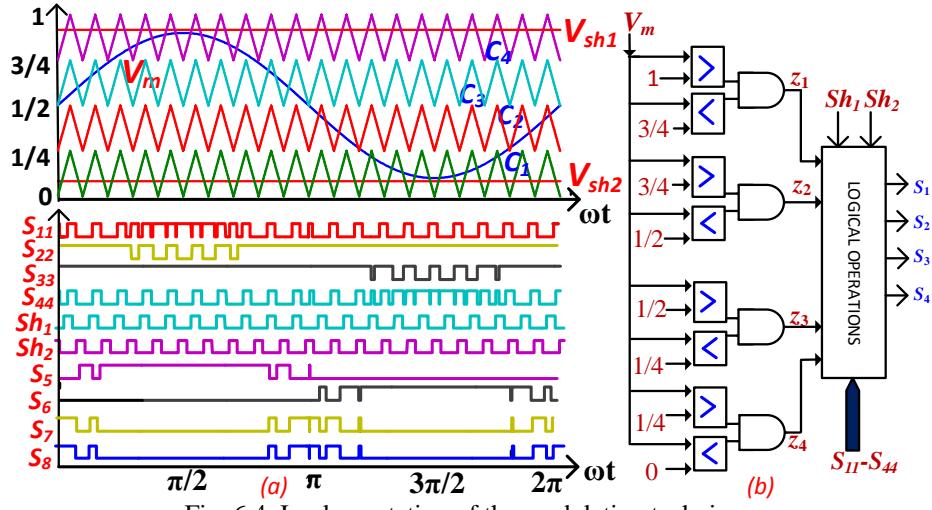

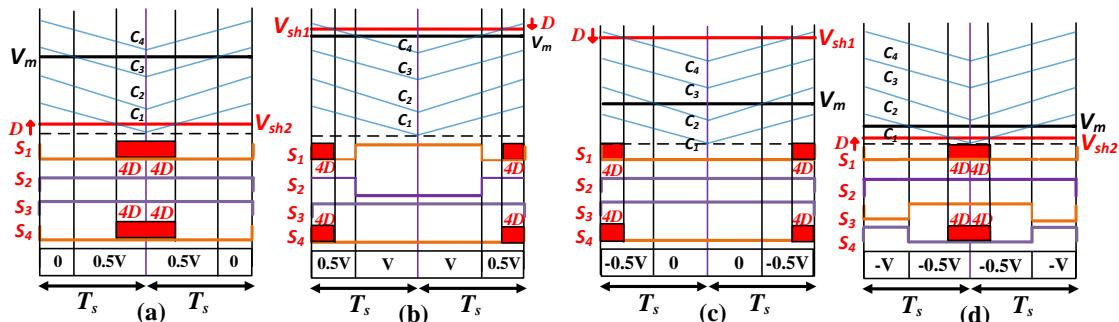

| Fig. 6.4:  | Implementation of the modulation technique.                                                                                                                                                                                                         | 6-6  |

| Fig. 6.5:  | Implementation of the modulation technique.                                                                                                                                                                                                         | 6-6  |

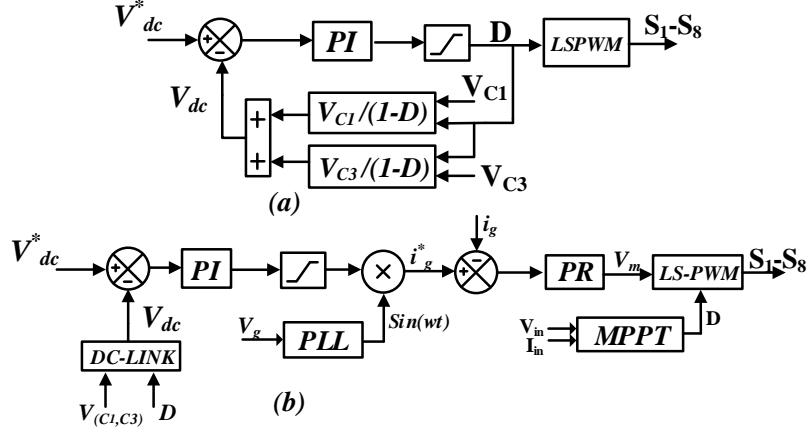

| Fig. 6.6:  | (a) Control strategy for standalone mode and (b) Control strategy for a grid-connection mode of operation.                                                                                                                                          | 6-8  |

| Fig. 6.7:  | (a) Common-mode model of qSC-5LI (b) Simplified common-mode model.                                                                                                                                                                                  | 6-10 |

| Fig. 6.8:  | Input voltage ( $V_{in}$ ), DC-link voltage ( $V_{dc1}$ ), capacitor voltages ( $V_{c1}$ , $V_{c2}$ ), and inductor current ( $i_{L1}$ ) of the qSC-5LI.                                                                                            | 6-12 |

| Fig. 6.9:  | Input voltage ( $V_{in}$ ), DC-link voltage ( $V_{dc1}$ ), capacitor voltages ( $V_{c1}$ , $V_{c2}$ ), and inductor current ( $i_{L1}$ ) of the qSC-5LI.                                                                                            | 6-12 |

| Fig. 6.10: | Input voltage ( $V_{in1}$ ), DC-link voltage ( $V_{dc1}$ ) and switched capacitor voltages ( $V_{sc1}$ , $V_{sc2}$ ) of the qSC-5LI.                                                                                                                | 6-12 |

| Fig. 6.11: | PV capacitor voltage ( $V_{cp}$ ) and leakage current ( $i_{leak}$ ) of the qSB-5LI.                                                                                                                                                                | 6-13 |

| Fig. 6.12: | Input voltage ( $V_{in}$ ), DC-link voltages ( $V_{dc1}$ & $V_{dc2}$ ), output voltage ( $V_{AB}$ ) and load current ( $i_{load}$ ) during load disturbance.                                                                                        | 6-13 |

Fig. 6.13: Input voltages ( $V_{in1}$ ) and DC-link voltages ( $V_{dc1}$  &  $V_{dc2}$ ) and output voltage ( $V_{AB}$ ) (b) Zoom-in view of the plot (a). 6-14

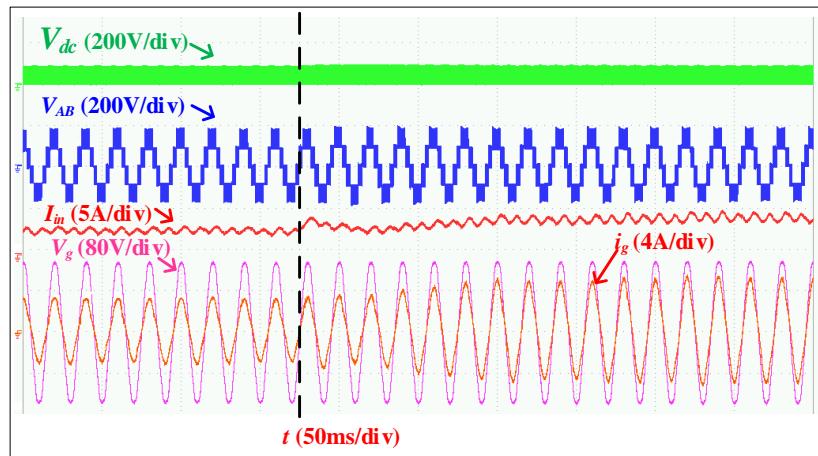

Fig. 6.14: Total DC link voltage ( $V_{dc}$ ), Inverter output voltage ( $V_{AB}$ ), input voltage ( $V_{in}$ ), grid voltage ( $V_g$ ) and grid current ( $i_g$ ). 6-14

Fig. 6.15: Efficiency curve of qSC-5LI. 6-17

Fig. 6.16: Loss distribution in switches, diodes, inductor, and capacitors at 400W in qSC-5LI. 6-17

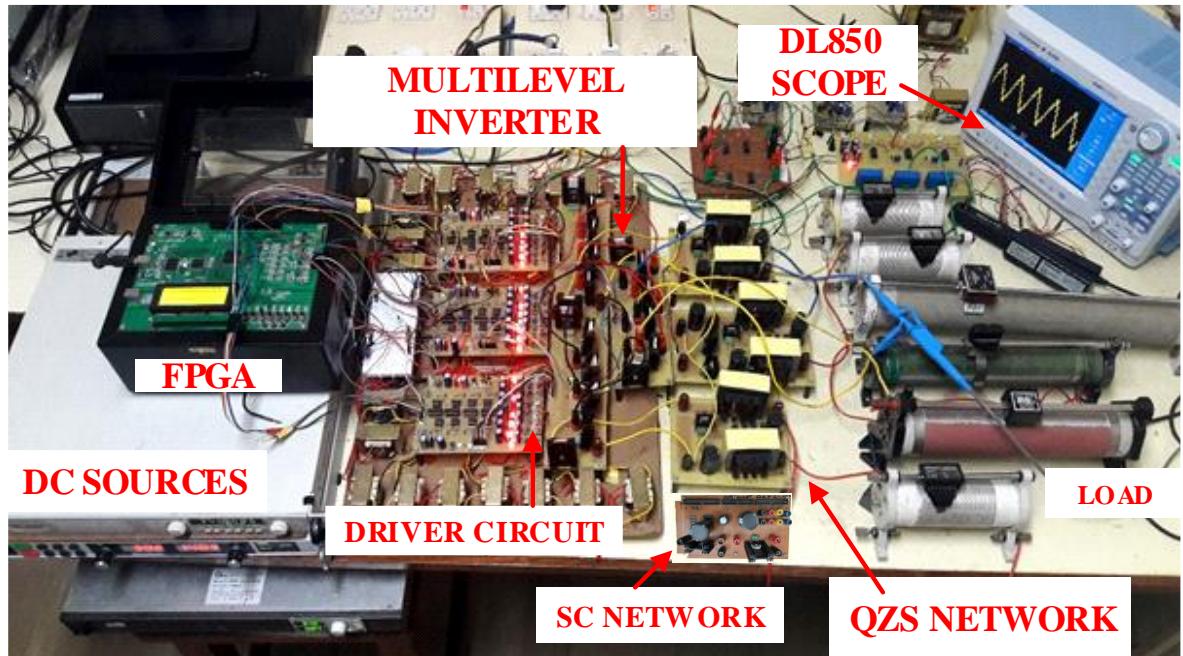

Fig.A.1: A view of the fabricated laboratory prototype A-1

## LIST OF TABLES

|           |                                                                               |      |

|-----------|-------------------------------------------------------------------------------|------|

| Table 1.1 | Various codes and standards for PV system                                     | 1-8  |

| Table 3.1 | Pole voltage ( $V_{AO}$ ) for different switching combinations                | 3-4  |

| Table 3.2 | Hardware Prototype Parameters                                                 | 3-14 |

| Table 3.3 | Comparison of different impedance topologies with the proposed topology       | 3-22 |

| Table 4.1 | switching combinations to achieve 7-level operation                           | 4-4  |

| Table 4.2 | Hardware Prototype Specifications                                             | 4-14 |

| Table 4.3 | Comparison of the proposed power converter with qZS topologies                | 4-19 |

| Table 5.1 | Different switching logic to obtain 5-level operation                         | 5-4  |

| Table 5.2 | Effective CMV of the power converter for $D=0.25$                             | 5-10 |

| Table 5.3 | Experimental Specifications                                                   | 5-13 |

| Table 5.4 | Comparison of the proposed power converter with 5-level qZS topologies        | 5-19 |

| Table 6.1 | Switching states to achieve five-level operation                              | 6-4  |

| Table 6.2 | Parasitic voltage of the power configuration for $D=0.1$ .                    | 6-10 |

| Table 6.3 | Operating parameters of hardware prototype                                    | 6-11 |

| Table 6.4 | Comparison of the QSC-5LI with five-level quasi-z-source Multilevel inverters | 6-16 |

## Abbreviations

|                  |                                        |

|------------------|----------------------------------------|

| FCMI             | Four-level CMI                         |

| LSPWM            | Level-shifted Space Vector PWM         |

| VSI <sub>s</sub> | voltage source inverters               |

| ZSI              | Z-source inverter                      |

| qZS              | Quasi-Z-source                         |

| qZSI             | Quasi-Z-source inverter                |

| STI-1            | Shoot-Through Inverter-1               |

| STI-2            | Shoot-Through Inverter-2               |

| CHB              | Cascaded H-Bridge                      |

| CHB-MLI          | Cascaded H-Bridge Multilevel inverters |

| CMI              | Cascaded Multilevel Inverter           |

| FC               | Flying capacitor                       |

| SVPWM            | Space Vector Pulse Width Modulation    |

| STPWM            | sine-triangle PWM                      |

| PD               | phase disposed                         |

| TSV              | Total Standing Voltage                 |

| NST              | Non-shoot-through                      |

| ST               | Shoot-through                          |

| MLSPWM           | Modified level-shifted PWM             |

| CMV              | Common-mode voltage                    |

|        |                                                        |

|--------|--------------------------------------------------------|

| PSIM   | Powersim                                               |

| FPGA   | Field Programmable Gate Arrays                         |

| LSPWM  | Level Shifted Pulse Wish Modulation                    |

| MATLAB | Matrix Laboratory                                      |

| MLI    | Multilevel Inverter                                    |

| MOSFET | Metal–oxide semiconductor with field-effect transistor |

| MPPT   | Maximum Power Point Tracking                           |

| MPP    | Maximum Power Point                                    |

| NPC    | Neutral Point Clamped                                  |

| P&O    | Perturb and Observe                                    |

| PF     | Power Factor                                           |

| PI     | Proportional Integral                                  |

| PLECS  | Piecewise Linear Electrical Circuit Simulation         |

| PLL    | Phase Locked Loop                                      |

| PR     | Proportional Resonant                                  |

| PV     | Photovoltaic                                           |

| PWM    | Pulse Width Modulation                                 |

| RMS    | Root Means Squares                                     |

| SOGI   | Second Order Generalized Integrator                    |

| SPWM   | Sinusoidal Pulse Width Modulation                      |

| SVPWM  | Space Vector Pulse Width Modulation                    |

|     |                            |

|-----|----------------------------|

| SC  | Switched Capacitor         |

| THD | Total Harmonic Distortion  |

| UPF | Unity Power Factor         |

| ESR | Equivalent series resistor |

## List of Symbols

|                      |                                    |

|----------------------|------------------------------------|

| $V_{X0}$             | pole voltage                       |

| $V_{XN}$             | Phase voltage                      |

| $V_{CM}$             | Common-mode voltage                |

| $T_{gx}^*$           | Normalized modulating signal       |

| $T_s$                | Sampling time period               |

| $T_{sh}$             | Shoot-through time                 |

| $S_{hx}$             | Shoot-through pulses               |

| $B$                  | Boost factor                       |

| $M$                  | Modulation index                   |

| $D$                  | Shoot-through duty ratio           |

| $V_{dcx}$            | DC-link voltages                   |

| $V_{dctotal}^*$      | Reference total DC-Link voltage    |

| $V_{dctotal}$        | Total DC-Link voltage              |

| $S_1, S_2 \dots S_n$ | Switching devices of the inverter. |

| $i_d^*$              | d-axis reference current           |

| $i_q^*$              | q-axis reference current           |

| $V_d^*$              | d-axis reference voltage           |

| $V_q^*$              | q-axis reference voltage           |

| $V_{in}$             | Input voltage                      |

| $V_{cx}$             | Capacitor voltages                 |

|            |                              |

|------------|------------------------------|

| $I_{L1}$   | Inductor current             |

| $i_x$      | Phase current.               |

| $V_{PV}$   | PV voltage.                  |

| $I_{PV}$   | PV current                   |

| $V_g$      | Grid voltage                 |

| $i_g$      | Grid current                 |

| $i_g^*$    | Reference grid current       |

| $V_{dc}^*$ | reference DC-link voltage    |

| $V_{AB}$   | Load voltage                 |

| $V_{out}$  | Output voltage               |

| $N_L$      | No of levels                 |

| $N_{sw}$   | No of switches               |

| $P_{sw}$   | Mosfet switching losses      |

| $P_{con}$  | Mosfet conduction losses     |

| $P_{sd}$   | Diode switching losses       |

| $P_{cd}$   | Diode conduction losses      |

| $P_{ind}$  | Inductor conduction loss     |

| $P_{cap}$  | Capacitor ESR loss           |

| $v_m$      | Sinusoidal modulating signal |

| $v_m^*$    | modified reference signal    |

|                 |                                   |

|-----------------|-----------------------------------|

| C               | Carrier signal                    |

| $V_{Lx}$        | Inductor voltages                 |

| $i_g^*$         | Reference grid current            |

| $V_{mcm}$       | Effective CMV                     |

| $R_D$           | Damping resistor                  |

| $C_p$ and $C_n$ | Parasitic capacitor               |

| $V_{cp}$        | Voltage of PV parasitic capacitor |

| $V_{scx}$       | Switched capacitor voltage        |

| $V_{shx}$       | DC reference signal               |

| $i_{leak}$      | Leakage current                   |

| $i_{load}$      | Load current                      |

| $S_{cx}$        | Switched capacitor voltages       |

# **Chapter 1**

## **Introduction**

# Chapter 1

## Introduction

### 1.1 General overview

The impending shortage of conventional sources of electric power has accelerated the prominence of research and development of alternative forms of energy. Of the available renewable forms of energy, solar and wind display massive potential to supplement conventional sources of energy. In particular, power generation with solar photovoltaic (PV) panels offers several advantages such as reliability of the source and clean energy. Reduced electricity bills and low maintenance costs are the contributing factors to the proliferation of solar energy systems.

With these benefits, PV-based power generation is increasingly becoming popular around the world, resulting in several large-scale installations with significant investments. Most developed and developing countries have consistently promoted solar PV energy systems through governmental support. Of all the nonconventional energy sources available, PV power occupies 24.3% of the total share [1]. In India, solar power installations have increased from 2.6 GW to more than 61is GW in the last 7 years. India is now in the 4th global Position for overall installed renewable energy capacity [2].

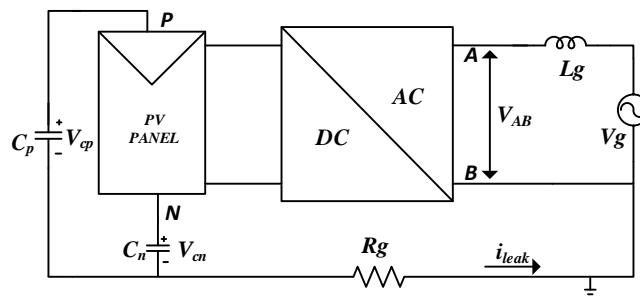

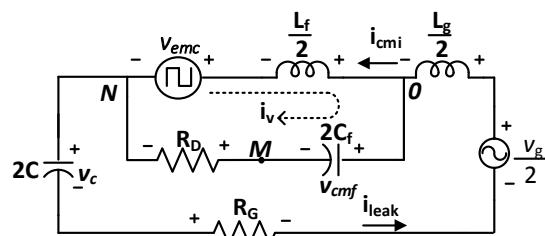

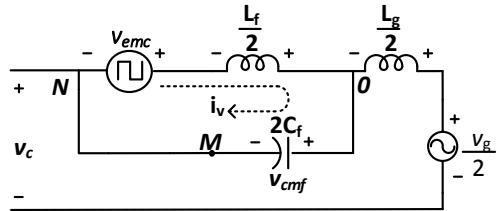

In general, PV systems are configured either as stand-alone systems or grid-connected applications. As the PV power is produced at low DC voltage, there is a need for a power electronic interface between the PV source and load/grid to obtain the AC output voltage of the required magnitude and frequency as shown in Fig .1.1. In this figure, ' $C_p$ ' and ' $C_n$ ' represent the parasitic capacitors of the PV panel, ' $L_g$ ' represents the grid inductance and ' $R_g$ ' represents the ground resistance.

Fig .1.1: General layout of a grid-tied PV inverter.

Further, there are also some disadvantages associated with PV generation. The major drawbacks are the huge installation cost and low conversion efficiency of the PV source. Therefore, the design and selection of the power electronic interface employed in the PV system should offer higher efficiency. Hence, in recent years, researchers have proposed several power configurations to achieve higher efficiency. The following sections discuss the different types of power converters based on the modular structure of the PV source [3-4].

## **1.2 Classification of PV inverters**

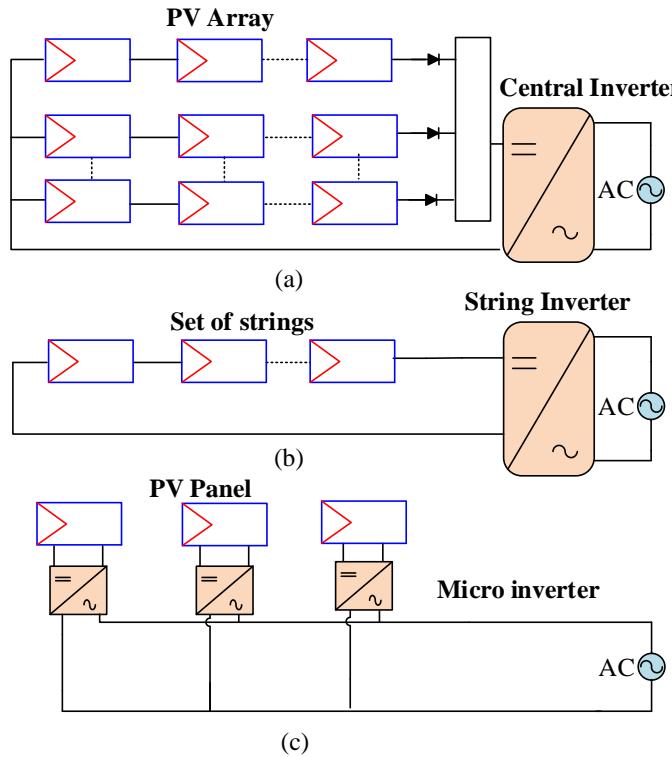

The grid-connected PV systems can be classified into the central inverter, string inverter, and microinverter based on the modular structure of the PV panels [5].

### **1.2.1 Central inverters**

The central inverters are the primitive PV inverters that are used in PV farms. A large number of PV panels are interconnected in series and parallel to provide high power level (MW) and DC voltage to avoid further amplification (shown in Fig.1.2 (a)). However, the drawbacks associated with these power converters are: (i) the requirement of high voltage DC cables between inverter and PV modules (ii) higher power loss incurred due to centralized MPPT (iii) the requirement of string diodes (iv) development of hotspots in the PV panels up on the occurrence of significant unequal shading.

### **1.2.2 String inverters**

These inverters are scaled-down versions of centralized inverters. Several PV modules are connected in series to form a string that is directly interfaced with the inverter (shown in Fig.1.2 (b)). There is no need for additional string diodes which improves efficiency. Further, each string of PV panels can be associated with an individual MPPT controller thereby improving the overall efficiency when compared to centralized inverters. However, the following are the drawbacks associated with these converters (i) a higher number of components (ii) each string requires a separate inverter (iii) the shaded PV panel restricts the amount of power the PV string can produce.

### **1.2.3 Microinverter**

The microinverter is an integration of a PV panel and inverter working as a single entity (shown in Fig.1.2 (c)). As each PV panel is associated with an individual inverter, separate

MPPT control can be implemented to improve the effectiveness of the MPPT [6]. Further, the ‘plug and play’ feature of the microinverter simplifies the tasks of maintenance and installation. The effect of shading is minimized on the overall system as all PV modules are isolated. However, the following are the drawbacks associated with these converters (i) high component count (ii) cost per watt increases (iii) a two-stage system is employed to boost the input DC voltage and invert the DC to AC.

Fig .1.2: Overview of PV inverters (a) Central inverter (b) string inverter (c) Microinverter.

### 1.3 Interfacing PV source with grid

This section discusses the modifications in the PV inverter topologies based on the number of power processing stages and the employment of a transformer [7].

#### 1.3.1 Number of power processing stages

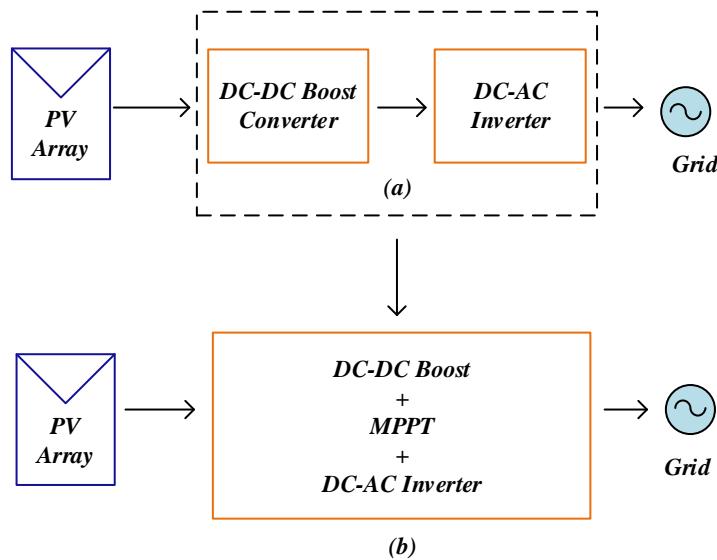

Solar PV systems often require the conversion of low output voltages of PV panels into AC of required voltage and frequency to cater to the requirements of consumers. In practice, it is often accomplished by a two-stage conversion process. Firstly, the low DC voltage output by the PV panels is boosted to attain the required DC voltage level using a DC-DC boost converter. Apart from voltage boosting, this converter plays the pivotal role of rendering the

maximum power point tracking (MPPT) capability to the solar PV system. The DC voltage, thus boosted, is then converted into AC using a conventional voltage source inverter (VSI) to deliver AC power of the required voltage and frequency to the end-users (as shown in Fig.1.3(a)). Despite its popularity, the two-stage conversion system increases the cost and complexity, taxing the efficiency and reliability of the power circuit.

The improvement of system efficiency, decreasing the cost and increasing the power density demands for the reduction of power stages of the converter. In contrast to the two-stage conversion, the PV power is directly processed to load/grid through the inverter in the single-stage conversion. A single-stage inverter executes both maximum power tracking and grid current control through a single-power processing stage (as shown in Fig.1.3 (b)). These incorporate advantages such as good MPP tracking, high efficiency, low component requirement, compact design, and high reliability when compared to the two-stage inverter.

Fig .1.3: Block diagram of (a) Two-stage power converter (b) Single-stage power converter.

### 1.3.2 Isolated/Non-Isolated inverter

The aforementioned single-stage and double-stage inverters are further classified into isolated and non-isolated inverters. In isolated inverters, a high-frequency transformer is employed in a DC-DC converter, or a line-frequency transformer is connected across the grid. Galvanic isolation can be provided by both high-frequency and low-frequency transformers, which eliminates the flow of leakage current. However, the utilization of a low-frequency transformer increases the overall cost and makes the system bulky. Further,

the inclusion of the high-frequency DC-DC isolation stage increases the number of power processing stages in the system, which results in reduced efficiency.

In non-isolated power converters, due to the absence of a transformer, the power converter becomes lighter, has a higher power density, and is more efficient. However, the absence of galvanic isolation creates a resonant path that generates leakage current.

From the aforementioned discussion, it can be concluded that a single-stage non-isolated power converter is the most viable solution to achieve high efficiency with less component count. Therefore, the problem of leakage current should be addressed by modulation techniques and semiconductor rearrangement.

## 1.4 Leakage current

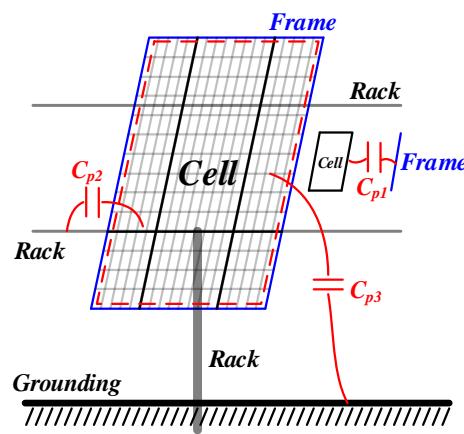

Fig.1.1 shows the single-stage non-isolated inverter for a grid-connected PV system. It may be noticed that, without the isolation transformer, there exists a direct ground current path between the PV panel and the grid [8]. As PV cells accumulate a considerable charge on their surfaces, parasitic capacitances are formed between the cell-to-frame ( $C_{p1}$ ), cell-to-rack ( $C_{p2}$ ), and cell-to-ground ( $C_{p3}$ ) as shown in Fig 1.4. These capacitances depend on the physical dimensions of the panel and atmospheric conditions. In a practical PV system, the frame of the PV panel, and the mounting rack are grounded. Hence they assume equal potential. Therefore, all three parasitic capacitances are connected in parallel and the equivalent value of the parasitic capacitance is the summation of all partial capacitances ( $C_{p1}$ ,  $C_{p2}$ , and  $C_{p3}$ ).

Fig 1.4: Parasitic capacitances in a typical PV Panel.

Further, the common-mode voltage of the power converter results in high-frequency voltage transitions across this parasitic capacitor. In the absence of galvanic isolation, this capacitive coupling facilitates the flow of leakage current from the PV panel to the ground. This leakage current is constituted by both low-frequency and high-frequency switching components which injects harmonics into the grid. This results in an increased power loss in the system, reduced longevity of PV panels, and a compromise in the safety issues to operating personnel [9].

Therefore, to ensure the safety of the operating personnel, this leakage current should be limited to less than 300mA as per the stipulation laid out by the standard VDE0126-1-1[10]. Since the parasitic capacitance varies greatly depending on atmospheric conditions and construction, a lumped equivalent value of 100nF/kW was chosen for the experimental studies of the proposed power converters in this thesis.

## **1.5 Single-stage non-isolated power converters with voltage boosting**

In the last two decades, considerable research work has been carried out in the area of *single-stage non-isolated boost inverters* to circumvent the disadvantages associated with the traditional two-stage inverter topologies. The motivation behind this research is to improve the performance of the single-stage power converter regardless of its efficiency, size, and complexity.

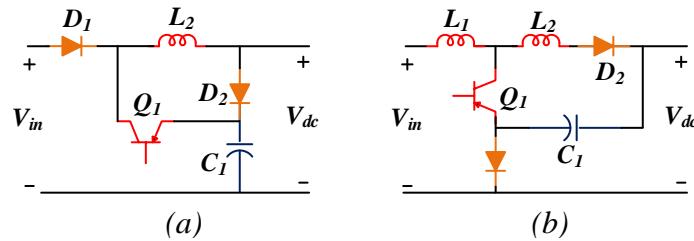

These single-stage boost topologies are categorized into the following topologies (i) current source inverters (ii) active buck-boost inverters (iii) impedance inverters [11]. The current source inverter is inherently a single-stage boosting converter. However, it requires a bulky inductor at the input. The buck-boost functionality can be derived with the employment of an additional *Active Boost Network* to buck-boost inverter. These power converters typically employ an inverter that is cascaded to an AC/AC boosting network. These power converters avail AC/AC boosting at an expense of additional active switches. The disadvantages of bulky inductors and an excess number of switching devices for boosting are overcome with the impedance source inverters. They are capable of handling low PV voltages with a wide variation in voltage while providing inherent protection from shoot-through faults [12-13]. In the year 2003, *Peng* introduced the first impedance power converter namely the Z-source inverter (ZSI). This converter is capable of achieving the twin objectives of boosting and inversion simultaneously. These impedance-based power

converter has been extensively researched in the past two decades. Subsequently, researchers have suggested various topological and modulation-based modifications to improve the performance of the conventional ZSI. Among these, the quasi-Z-source inverters are the most prominent. The disadvantage associated with the conventional ZSI, namely the discontinuous input current, is successfully overcome with the quasi-Z-source (qZS) inverters [14]. Furthermore, the voltage rating of one of the capacitors is significantly reduced in qZSIs, compared to the conventional ZSIs.

Based on the limitations of various transformerless power circuit configurations and their modulation schemes reported in the earlier literature, this thesis investigates different qZS-based topologies to improve their performance.

## 1.6 PV inverter standards in grid-tied operation

The PV inverters should be designed to comply with various international standards [15-19] while injecting power into the grid. The following is the list of important parameters, which should be considered for grid-tied operation (i) grid current THD (ii) injected direct current (iii) range of grid frequency (iv) power factor (v) leakage current.

As per the PV standards (IEEE 1547, AS4777, EN 61000-3-2), the maximum THD allowable in the grid current should be restricted to 5%. This improves the power quality at the distribution feeder. Further, the injected DC into the grid is limited to 0.22% to 1% of the rated output current. The range of grid frequency varies with different countries as shown in Table 1.1. According to the standard stipulated by VDE-AR-N-4105, the inverter should be capable of delivering reactive power within the power factor range of 0.8 to 0.95. Finally, the leakage current should be limited to less than 300mA (RMS) according to the standard stipulated by VDE 0126-1-1. Further, the circuit should be opened within 0.3sec when the RMS current is higher than 300mA.

TABLE 1.1 VARIOUS CODES AND STANDARDS FOR PV SYSTEM

|                     | <b>THD</b> | <b>DC current injected</b>  | <b>Grid frequency(Hz)</b> | <b>Power factor</b> |

|---------------------|------------|-----------------------------|---------------------------|---------------------|

| <b>IEEE 1547</b>    | < 5%       | <0.5% of rated output power | 57 -60.5                  | 0.9 to 0.97         |

| <b>AS4777</b>       | < 5%       | <0.5% of rated output power | 48-52                     | 0.8-0.95            |

| <b>EN 61000-3-2</b> | < 5%       | <0.5% of rated output power | 47.5-50.2                 | NA                  |

## 1.7 Organization of the thesis

This thesis is structured into seven chapters, which are summarized as follows:

**Chapter 2** presents a comprehensive review of several Z-source and quasi-Z-source three-phase and single-phase topologies. The motivation for the problem formulation and objectives of the thesis are also presented in this chapter.

**Chapter 3**, presents a three-phase quasi-Z-source based four-level cascaded MLI for Photovoltaic application. In this chapter, a detailed view of the working principle of the power converter along with the proposed modulation scheme is presented. Further, the improved boost factor of the four level inverter is obtained using mathematical analysis. It is shown that in the stand-alone mode of operation, the output voltage can be regulated by controlling the shoot-through duty ratio of the quasi-Z-sources networks. In addition, it is also shown that, during grid-tied mode of operation the twin objectives of MPPT and active power injection into the grid is achieved by controlling the shoot-through duty ratio and modulation index. Further, the experimental studies validates the concept and performance of the proposed inverter. Finally, the proposed configuration is compared with the existing multilevel inverter configurations to emphasize its features and merits.

**Chapter 4**, presents a single-stage dual quasi-Z-source 7-level inverter along with its PWM technique. The working principle and various modes of operation of the proposed seven-level inverter are presented. Further, the implementation of the proposed PWM scheme, analysis of the boost factor, and design of the qZS network of the power converter are presented. In addition, it is also shown that the proposed topology can regulate the output voltage in the stand-alone mode, and can inject active power into the grid in the grid-tied mode of operation. This chapter also addresses how to minimise high-frequency voltage transitions across the parasitic capacitor to reduce leakage current. The experimental studies are presented to validate the operation of the power converter. Finally, the comparison of the proposed power converter with the other existing qZS inverter is presented to highlight its benefits.

**Chapter 5**, proposes a single-staged quasi-Z-source-based five-level inverter topology, as well as a modulation technique. The working principle and different modes of operation of the proposed power converter are presented. Analysis of leakage current is also presented for

the proposed inverter. Furthermore, in this chapter, the performance of closed-loop control schemes for the proposed power converter in both stand-alone and grid-tied modes of operation is assessed. Experimental results are presented to validate the operation of the proposed power converter. Finally, the benefits obtained by the proposed power converter, compared to the other converters reported in the literature are presented.

**Chapter 6**, presents a single-stage quasi-switched capacitor-based five-level inverter for PV systems. Various modes of operation of the proposed configuration are presented along with its proposed PWM scheme. Also, the reduction of the leakage current in the proposed power converter is analyzed with common mode and differential mode analyses of the power converter. Experimental results are presented to validate the proposed configuration. Further, a comparison with existing qZS-5LI is presented to highlight the features of the proposed configuration.

**Chapter 7**, summarizes the important findings of the research work reported in this thesis and suggests possible extensions for future work.

# **Chapter 2**

## **Literature survey**

## Chapter 2

### Literature survey on Impedance source inverters

#### 2.1 Introduction

As mentioned in the preceding chapter, impedance-source inverters belong to the category of single-stage power converters. Power converters belonging to this class are capable of deriving the twin objectives of voltage boosting as well as inversion from a single entity. Two-stage power converters are currently being used required for low or variable-voltage renewable energy sources. In such a scenario, it makes an interesting study as to how the impedance-source inverters compare vis-à-vis the two-stage converters.

This chapter comprehensively reviews various impedance source networks and different single-phase and three-phase impedance source inverters for PV systems.

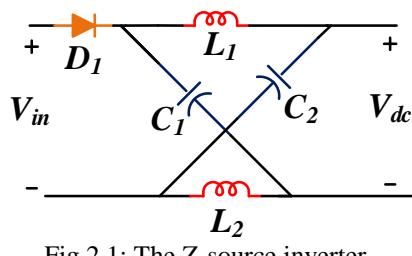

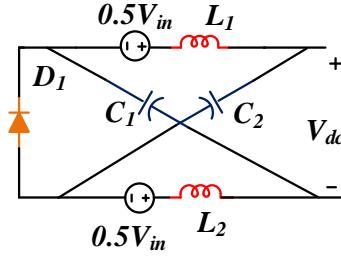

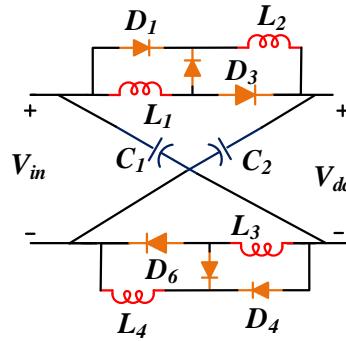

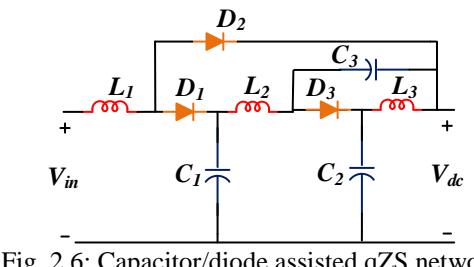

#### 2.2 The Impedance source inverter

The first impedance source inverter namely the “Z-source inverter” was introduced in 2002[12]. This power converter consists of the impedance network, which is made up of inductors, capacitors, and diodes to boost or buck the voltage. The impedance network employs two inductors ( $L_1$  and  $L_2$ ) and two capacitors ( $C_1$  and  $C_2$ ) connected in an X shape to interface the inverter to the DC source as shown in Fig.2.1.

Fig 2.1: The Z-source inverter

To illustrate the operating principle of the Z-source inverter a three-phase voltage-fed Z-source inverter is used as an example. In a conventional three-phase inverter we have six active states and two zero states. In addition to these states, the Z-source inverter has a state known as the “shoot-through state” where a single leg or multiple legs of the inverter are short-circuited in an instant. The shoot-through states are forbidden in conventional VSIs as it leads to the short-circuiting of the input source and damage the switches.

It should be noted that the conventional VSIs and CSIs are capable of operating as buck and boost converters respectively. The shoot-through state is strictly forbidden for a VSI making it work exclusively as a buck-type converter. On the other hand, the CSI uses the shoot-through states to obtain the boost capability. In contrast, the impedance-source inverters, with the shoot-through states can provide the buck-boost capability, which is unique to this class of converters.

To analyze the voltage gain offered by the Z-source inverter, a brief mathematical analysis regarding the operation of the power converter is presented below.

Z-source inverter operates in two modes namely, (i) shoot-through mode and (ii) non-shoot-through mode. During the shoot-through mode, the inverter output terminals are short-circuited and no energy is transferred from source to load. Further, the input source is disconnected from the inverter, and both the inductors store energy from the capacitors. This stored energy along with the input DC supply is fed to the load during the non-shoot-through state.

Applying voltage sec balance during shoot-through and non-shoot-through states, and considering the symmetry of the Z-source network the following voltage equations are derived.

During Non-shoot-through

$$V_L = V_{in} - V_C \quad (2.1)$$

$$V_{dc} = (2V_C) - (V_{in}) \quad (2.2)$$

During Shoot-through

$$V_L = V_C \quad (2.3)$$

$$V_{dc} = 0 \quad (2.4)$$

Application of the volt-sec balance to all of the inductor voltages over one switching time period paves the way to the derivation of the boost factor obtained with the Z-source inverter. Each switching time period consists of one of the NST modes (equations 2.1-2.2) & the ST mode (equations 2.3-2.4). It may be noted that the symmetry of the Z-source networks results in  $V_{C1}=V_{C2}=V_C$  and  $V_{L1}=V_{L2}=V_L$ .

The voltages across the capacitors are expressed as:

$$V_{C1}=V_{C2} = \frac{(1-D)}{(1-2D)} V_{in} \quad (2.5)$$

Where 'D' is the shoot-through duty ratio, defined as  $T_{sh}/T_s$ . (where  $T_{sh}$  and  $T_s$  respectively denote the shoot-through time and the time period of the switching cycle).

Hence, the boosted DC-link voltage from equation (2.2) is expressed as:

$$V_{dc} = \frac{1}{(1-2D)} V_{in} \quad (2.6)$$

Where  $B = \frac{1}{(1-2D)}$  is the boost factor of ZSI.

Therefore, the peak fundamental output phase voltage of the inverter is expressed as:

$$\hat{V} = \frac{1}{2} * M * B * V_{in} \quad (2.7)$$

Where 'M' is the modulation index and 'B' is the boost factor.

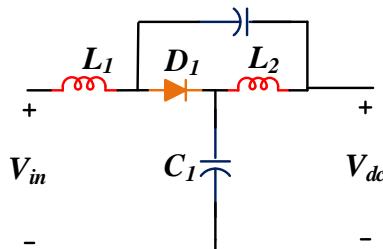

Despite these advantages of boosting, inherit shoot-through immunity, and single-stage conversion, the ZSI also suffers from the following drawbacks (i) discontinues input current due to the presence of input diode (ii) huge component size (iii) no common ground. Therefore to address these drawbacks a modified ZSI known as a quasi-Z-source inverter (qZSI) is proposed in [14]. Fig. 2.2 shows the schematic of the qZSI, it may be observed that an input inductor is always in connection with the source which results in continuous input current waveform. Further, the voltage rating of one of the capacitors is decreased in comparison with ZSI which leads to reduce the size of the capacitor.

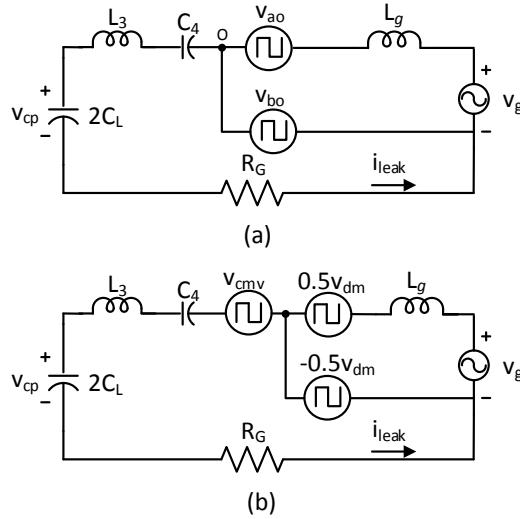

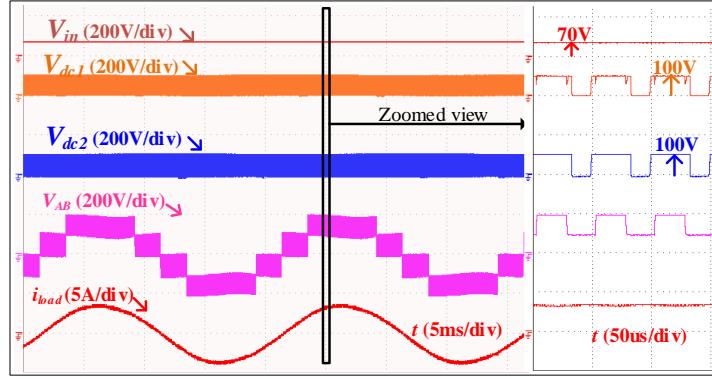

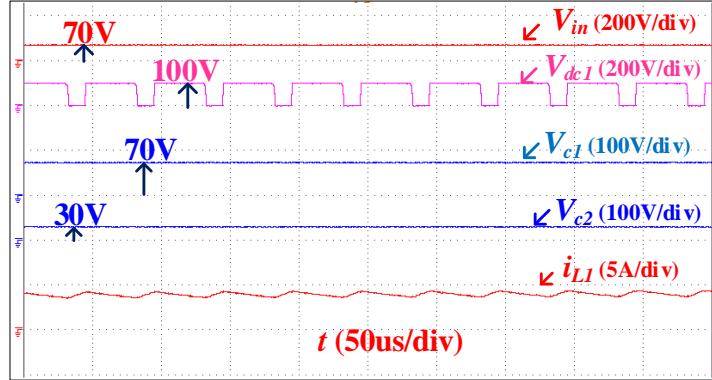

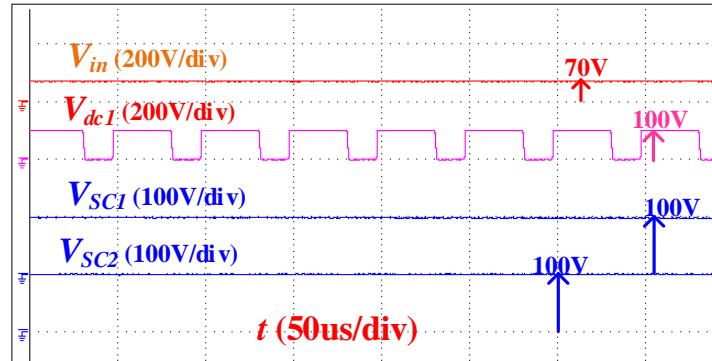

Fig .2.2: Quasi-Z-source inverter