# **DESIGN AND CIRCUIT PERFORMANCE ANALYSIS OF ENCLOSED CIRCULAR DOUBLE GATE MOSFETS**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**Doctor of Philosophy**

by

**Kallepelli Sagar**

(Roll No. 718142)

Supervisor

**Dr. Maheshwaram Satish**

Assistant Professor

Department of Electronics and Communication Engineering

**Department of Electronics & Communication Engineering**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL – 506004, T.S, INDIA**

**August-2023**

## APPROVAL SHEET

This thesis entitled "**Design and Circuit Performance Analysis of Enclosed Circular Double Gate MOSFETs**" by **Mr. Kallepelli Sagar** is approved for the degree of **Doctor of Philosophy**.

### Examiners

---

---

### Supervisor

---

#### **Dr. Maheshwaram Satish**

Assistant Professor, Department of Electronics & Communication Engineering,

NIT WARANGAL

### Chairman

---

#### **Prof. D. Vakula**

Head, Department of Electronics & Communication Engineering,

NIT WARANGAL

**Date: 07-08-2023**

**Place: Warangal**

## **DECLARATION**

I hereby declare that the matter embodied in this thesis entitled "**Design and Circuit Performance Analysis of Enclosed Circular Double Gate MOSFETs**" is based entirely on the result of the investigation and research work carried out by me under the supervision of **Dr. Maheshwaram Satish**, Department of Electronics and Communication Engineering, National Institute of Technology, Warangal. I declare that this work is original and has not been submitted in part or full, for any degree or diploma to this or any other university and was not submitted elsewhere for the award of any degree.

I also declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will cause disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Kallepelli Sagar**

**Roll No: 718142**

**Date: 07-08-2023**

**Place: Warangal**

**Department of Electronics and Communication Engineering**

**National Institute of Technology**

**Warangal – 506 004, Telangana, India**

**CERTIFICATE**

This is to certify that the thesis work entitled "**Design and Circuit Performance Analysis of Enclosed Circular Double Gate MOSFETs**", which is being submitted by Mr. Kallepelli Sagar (Roll No.718142), is a bonafide work submitted to National Institute of Technology Warangal in partial fulfilment of the requirement for the award of the degree of *Doctor of Philosophy in Electronics and Communication Engineering of National Institute of Technology, Warangal* is a record of bonafide research work carried out by him under my supervision.

To the best of our knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. Maheshwaram Satish**

Supervisor

Department of ECE

National Institute of Technology

Warangal – 506004

This Thesis is Dedicated to My

Family, Gurus, & Friends

# Contents

|                                                                       |              |

|-----------------------------------------------------------------------|--------------|

| <b>Contents .....</b>                                                 | <b>vi</b>    |

| <b>ACKNOWLEDGEMENTS.....</b>                                          | <b>ix</b>    |

| <b>ABSTRACT .....</b>                                                 | <b>xi</b>    |

| <b>List of Figures.....</b>                                           | <b>xiii</b>  |

| <b>List of Tables .....</b>                                           | <b>xvii</b>  |

| <b>Nomenclature.....</b>                                              | <b>xviii</b> |

| <b>1. Introduction .....</b>                                          | <b>1</b>     |

| 1.1. History.....                                                     | 1            |

| 1.2. Developments of MOS Technologies .....                           | 3            |

| 1.3. Motivation.....                                                  | 6            |

| 1.4. Problem Statement .....                                          | 6            |

| 1.5. Research Objectives .....                                        | 7            |

| 1.6. Thesis Organization.....                                         | 7            |

| <b>2. Literature Survey .....</b>                                     | <b>9</b>     |

| 2.1. Review on Possible Solutions .....                               | 9            |

| 2.1.1. Review on Advanced Structures .....                            | 10           |

| 2.1.2. Review on Non-standard Devices .....                           | 14           |

| 2.1.3. Review on Circular MOSFETs .....                               | 15           |

| 2.2. Review on Radiation Effects.....                                 | 19           |

| 2.3. Research Gaps.....                                               | 20           |

| <b>3. TCAD Calibration and Simulation Setups .....</b>                | <b>22</b>    |

| 3.1. Visual Technology Computer Aided Design: Visual TCAD .....       | 22           |

| 3.2. Calibration Setup.....                                           | 26           |

| 3.2.1. 30 nm Technology Node .....                                    | 27           |

| 3.2.2. 10 nm Technology Node .....                                    | 29           |

| 3.3. Simulation Setups for Radiation Effects Analysis .....           | 31           |

| 3.3.1. Simulation Setup for TID Effect in Semiconductor Devices ..... | 31           |

|                                                                                       |           |

|---------------------------------------------------------------------------------------|-----------|

| 3.3.2. Simulation Setup for Single Event Effects (SEE) in CMOS Circuits .....         | 34        |

| <b>4. Design of Circular MOSFETs.....</b>                                             | <b>35</b> |

| 4.1. Circular Single Gate Transistor (CSGT).....                                      | 35        |

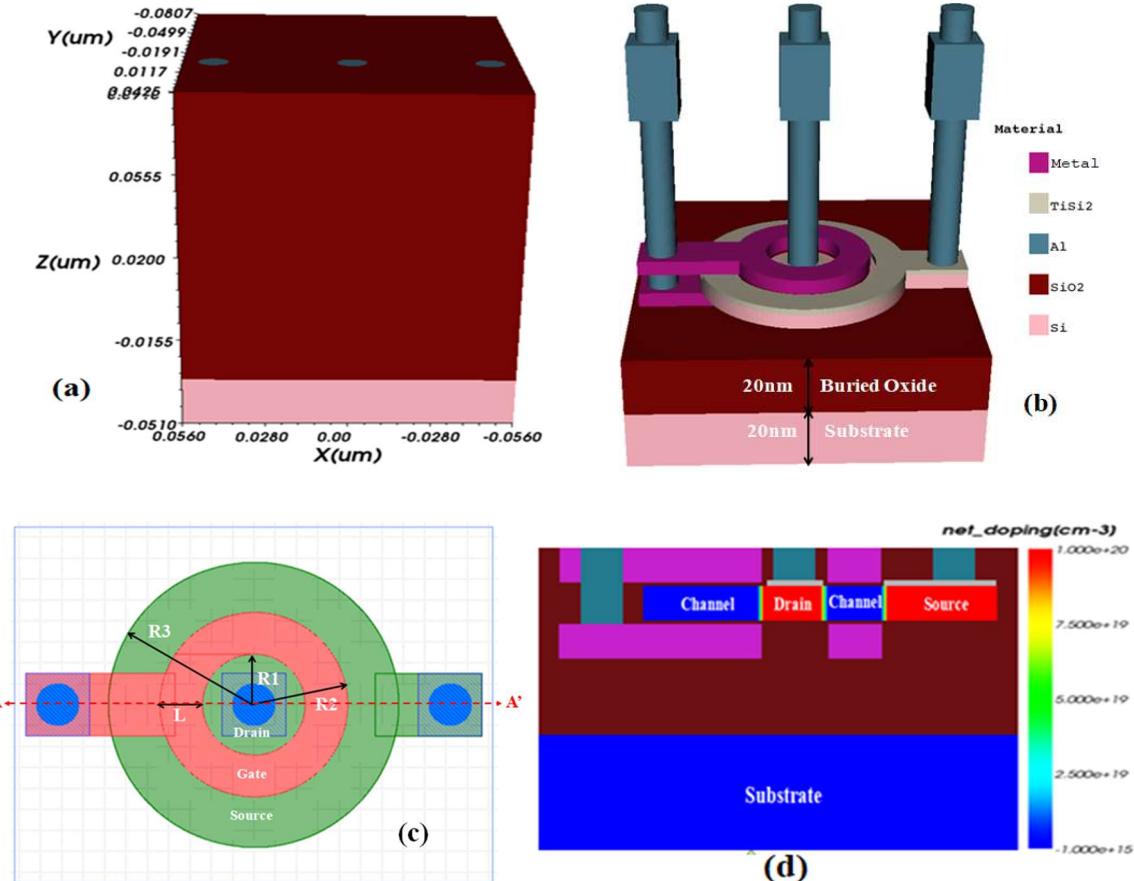

| 4.2. Circular Double Gate Transistor (CDGT).....                                      | 36        |

| 4.2.1. CDGT Device Structure .....                                                    | 36        |

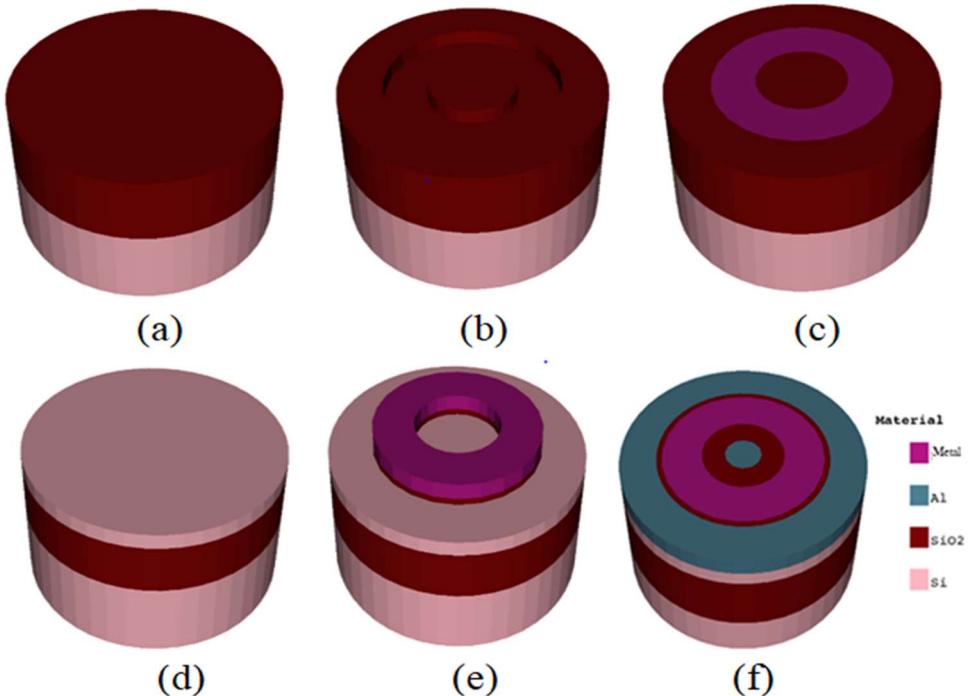

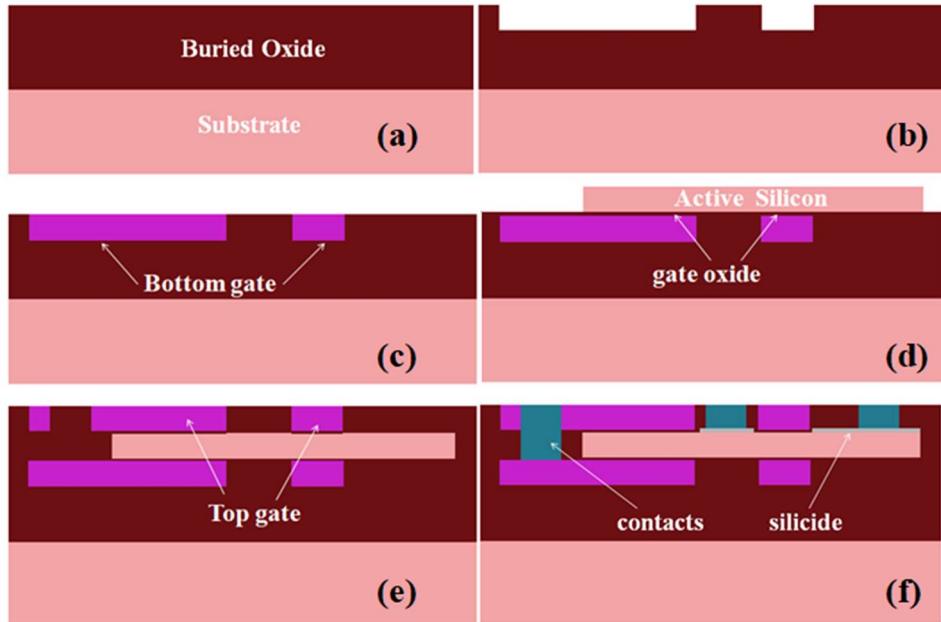

| 4.2.2. CDGT Fabrication Process.....                                                  | 36        |

| 4.3. Simulation Methodology of CSGT and CDGT Devices.....                             | 38        |

| 4.4. Raised Source/Drain CDGT Structures.....                                         | 40        |

| 4.5. JL Mode Analysis of Raised ‘both’ CDGT MOSFETs .....                             | 43        |

| 4.6. Performance Analysis of CSGT/CDGT Devices at Sub 10 nm Node .....                | 45        |

| 4.7. Summary .....                                                                    | 49        |

| <b>5. CDGT Device Optimization and Scaling Performance .....</b>                      | <b>50</b> |

| 5.1. CDGT Device Optimization.....                                                    | 50        |

| 5.2. Performance Analysis of Underlap (UL) .....                                      | 53        |

| 5.3. Performance Enhancement with High-k Dielectric.....                              | 58        |

| 5.4. Benchmarking of CDGT device.....                                                 | 60        |

| 5.5. CDGT Device Scaling Performance .....                                            | 61        |

| 5.5.1. Technology Node (7 nm) .....                                                   | 64        |

| 5.5.2. Technology Node (5 nm) .....                                                   | 66        |

| 5.6. Impact of Geometrical Variations on CDGT Performance.....                        | 68        |

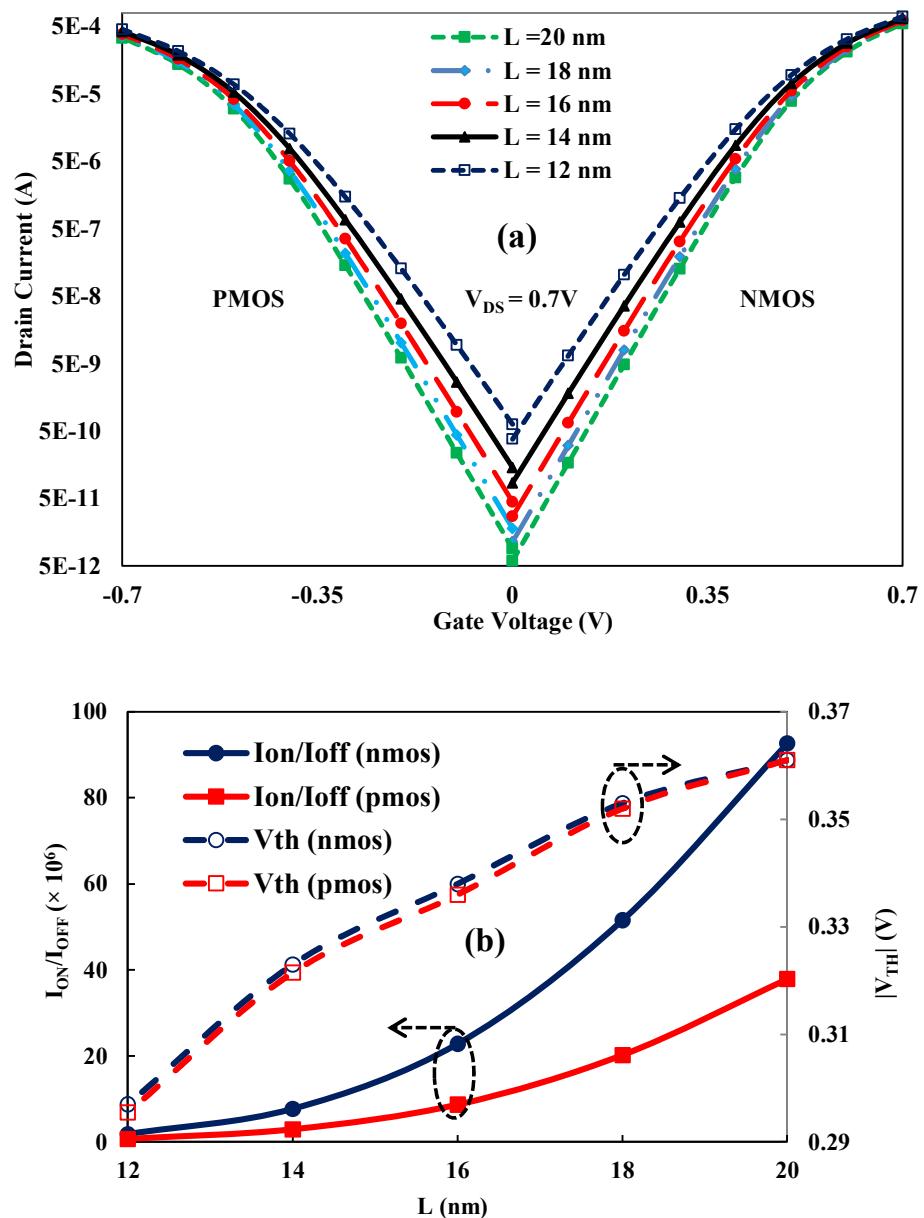

| 5.6.1. Gate Length (L).....                                                           | 68        |

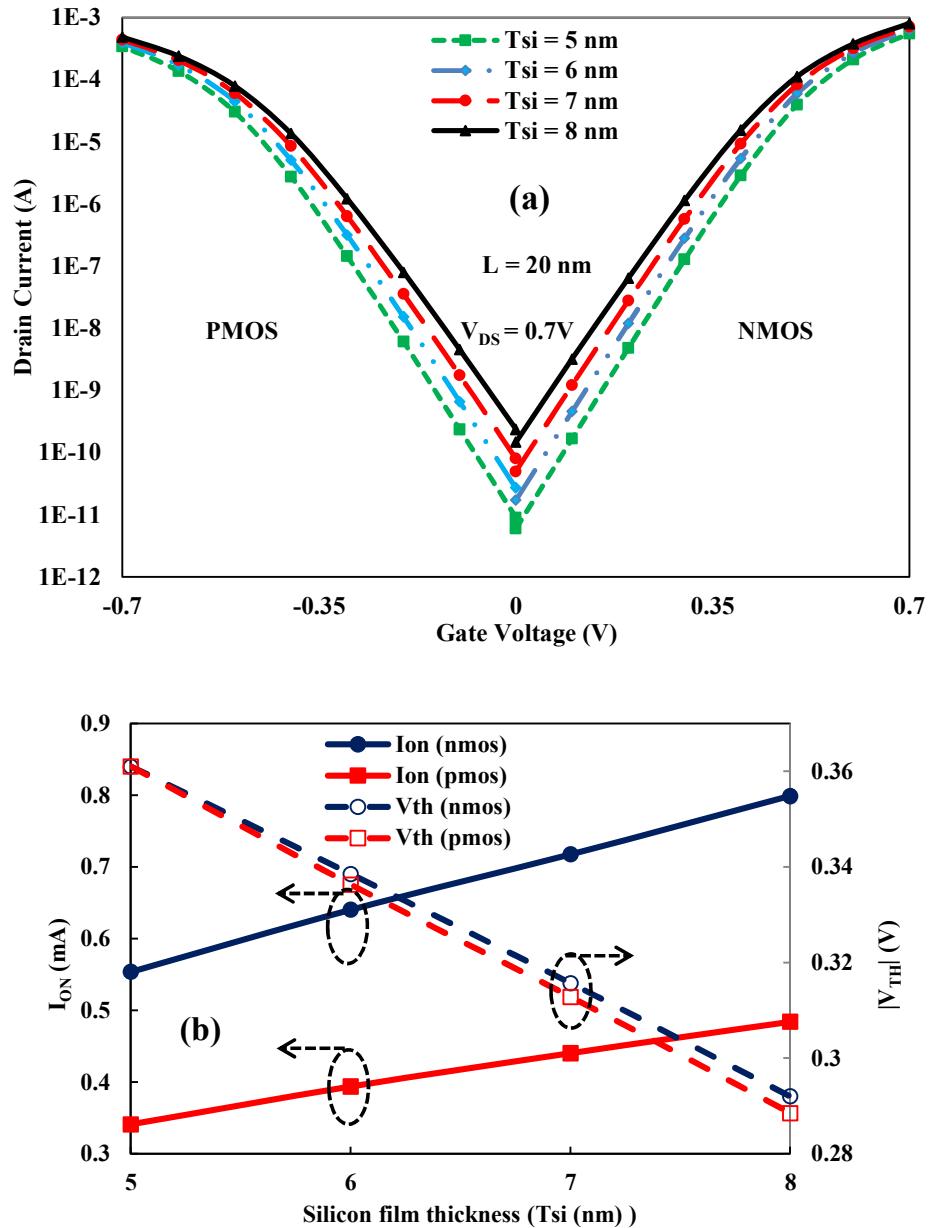

| 5.6.2. Silicon film thickness ( $T_{si}$ ) .....                                      | 70        |

| 5.7. Circular Nanosheet MOSFETs (C- NSFETs).....                                      | 72        |

| 5.7.1. Device Structure and Fabrication Process.....                                  | 72        |

| 5.7.2. Simulation Methodology.....                                                    | 74        |

| 5.8. Stacked Circular Nanosheet MOSFET (SC-NSFETs).....                               | 76        |

| 5.9. Summary .....                                                                    | 80        |

| <b>6. Circuit Performance and Radiation Effects analysis of Circular MOSFETs.....</b> | <b>82</b> |

| 6.1. Circuit Performance Analysis of Circular MOSFETs.....                            | 82        |

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| 6.1.1. Inverter Performance Analysis at 30 nm Technology Node .....       | 82         |

| 6.1.2. Inverter Performance Analysis at 10 nm Technology Node .....       | 85         |

| 6.2. Radiation Effects in Circular MOSFETs.....                           | 90         |

| 6.2.1. Radiation Basics.....                                              | 90         |

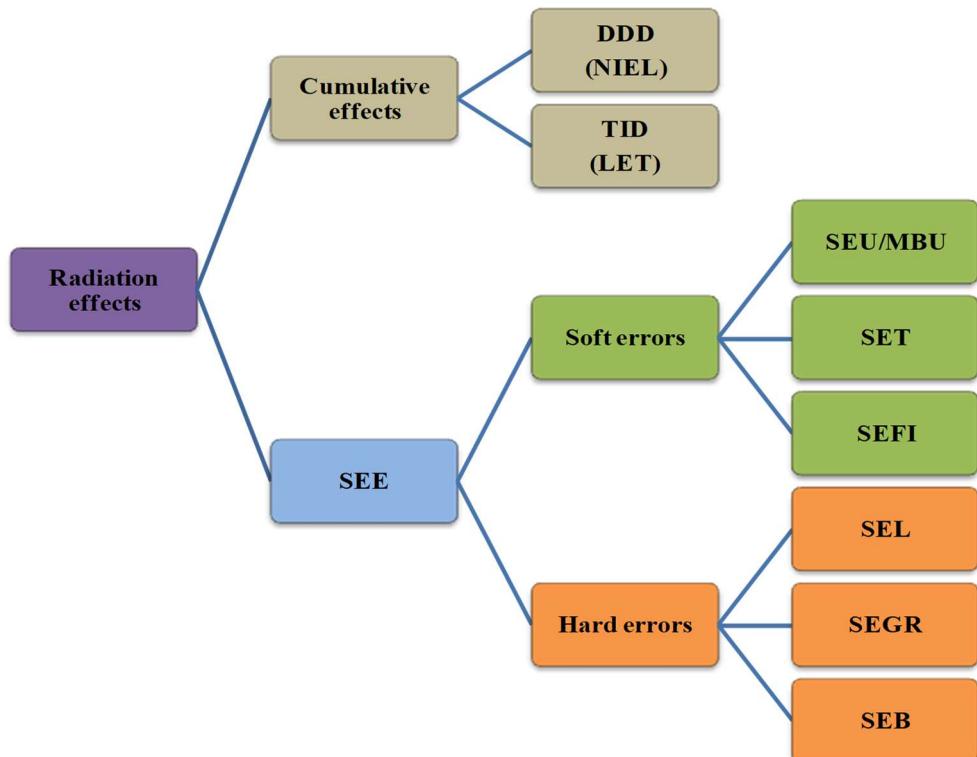

| 6.2.2. Types of Radiation Effects in Electronics .....                    | 91         |

| 6.2.2.1. Cumulative Effects.....                                          | 91         |

| 6.2.2.2. Single Event Effects (SEEs).....                                 | 93         |

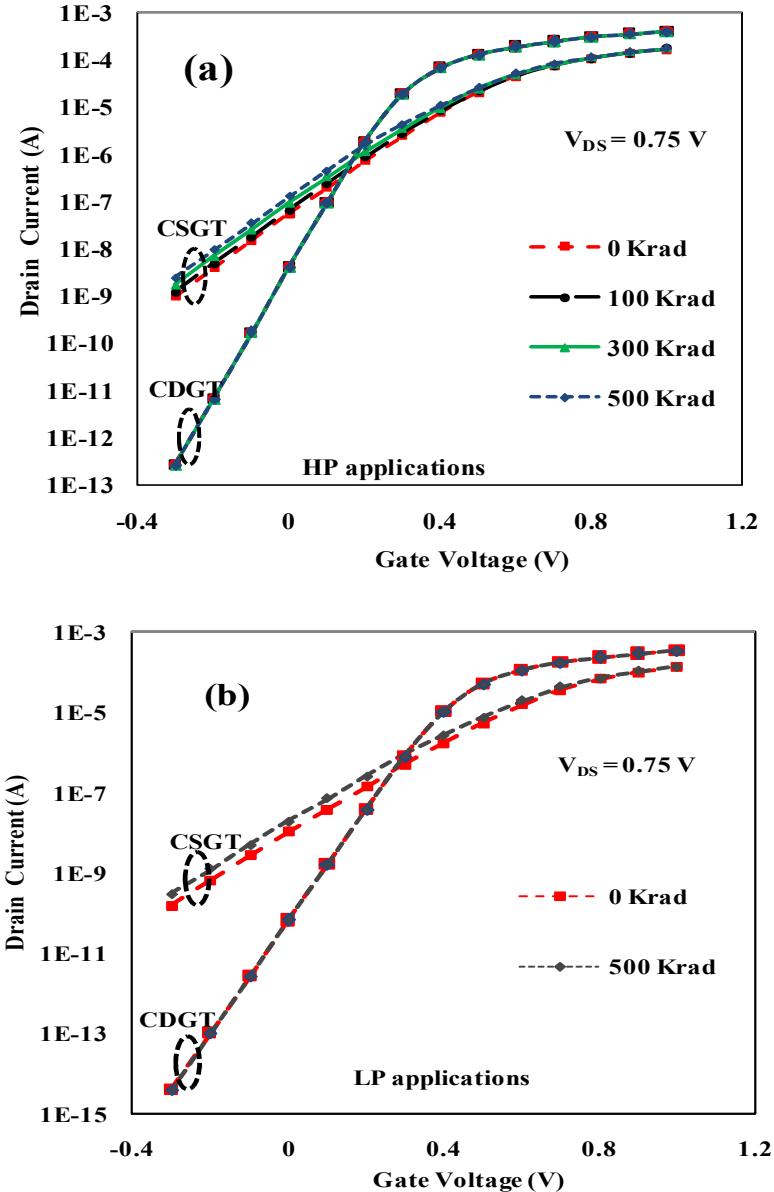

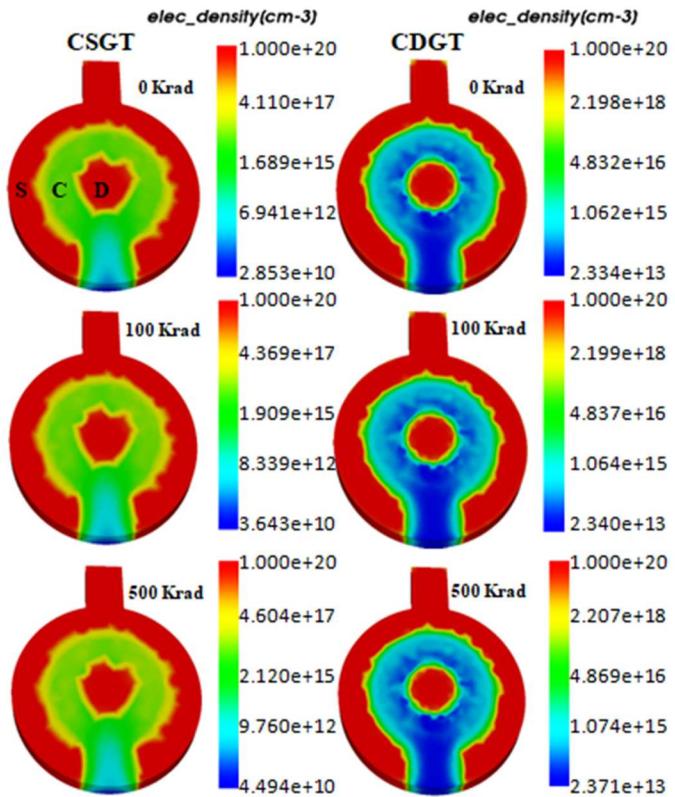

| 6.2.3. Analysis of TID Effects on Circular MOSFETs .....                  | 96         |

| 6.2.4. Analysis of SEEs on Inverter Performance of Circular MOSFETs ..... | 99         |

| 6.3. Summary .....                                                        | 103        |

| <b>7. Conclusions and Future Scope .....</b>                              | <b>104</b> |

| 7.1. Conclusions .....                                                    | 104        |

| 7.2. Future Scope.....                                                    | 106        |

| <b>Bibliography .....</b>                                                 | <b>107</b> |

| <b>List of Publications.....</b>                                          | <b>126</b> |

| <b>Appendix .....</b>                                                     | <b>127</b> |

## ACKNOWLEDGEMENTS

I am grateful to many people who made this work possible and helped me during my Ph.D studies. I am greatly indebted to my research supervisor Dr. Maheshwaram Satish for giving me excellent support during my research activity at NIT Warangal. He encouraged me in choosing my research topic, his vision in my research area leads to successful investigations. I am very much thankful for giving research freedom and guidance, support in non-academic matters and for the humanity shown to me. With his inimitable qualities as a good teacher, he chiseled my path towards perfection. Ever since I met him, he has been an eternal source of motivation, inspiration, encouragement, and enlightenment. He is responsible for making the period of my research work an educative and enjoyable learning experience. The thesis would not have seen the light of the day without his insistent support and cooperation.

I am also grateful to Prof. D. Vakula, Head of the Department, Dept. of Electronics and Communication Engineering, for his valuable suggestions and support that he shared during my research tenure.

I take this privilege to thank all my Doctoral Scrutiny Committee members, Prof. D. Dinakar, Department of Physics, Prof. P. Sreehari Rao, Department of Electronics and Communication Engineering, Dr. V. Narendar, Assistant Professor, Department of Electronics and Communication Engineering for their detailed review, constructive suggestions and excellent advice during the progress of this research work.

I am grateful to the former Heads of the ECE department Prof. N. Bheema Rao, Prof. L. Anjaneyulu and Prof. P. Sreehari Rao for their continuous support and encouragement. I would also appreciate the encouragement from teaching, non-teaching members and fraternity of Dept. of E.C.E. of N.I.T. Warangal. They have always been encouraging and supportive.

I take this opportunity to convey my regards to my well-wishers and co-scholars for being always next to me. Thanks to Dr. G. Arun Kumar, Dr. V. Rama, V.L. Kiranmai, Dr. Ch. Balaram Murthy, K. Ravi, R. Srikanth, and N. Pradeep Department of Electronics and Communication Engineering for their motivation and support throughout my work.

I acknowledge my gratitude to all my teachers, colleagues, and relatives at various places for supporting and cooperating with me to complete this work.

I would like to thank my family members (my father Sathya Narayana, my mother Sharadha, my wife Srujana, my son Saharsh Sai, my sister Mounika, my brother-in-law Satish, my niece Sri Dhatri, and my nephew Devarsh), and closest friends (Gym walkers association members, Kishore, and Raj Kumar) for giving me mental support and inspiration. They have motivated and helped me to complete my thesis work successfully.

Finally, I thank God, for filling me every day with new hopes, strength, purpose, and faith.

**Kallepelli Sagar**

# ABSTRACT

Over the last decade, the migration of commercial planar CMOS technology to multigate technologies has enabled continuing scaling of feature size to below 20 nm gate length while controlling short channel effects (SCEs) & reducing the leakage current. To address SCEs, multigate MOSFET architectures like FinFETs, gate-all-around (GAA) FETs, nanowire (NW) FETs, and Nanosheet (NS) FETs have been proposed. The multigate FETs with rectangular structure suffer from the corner effect (CE) problem, which is responsible for lowering the threshold voltage ( $V_{TH}$ ) at the channel corners due to a decrease in the longitudinal electric field (LEF). One more issue with multigate rectangular MOSFETs is, they suffer from radiation effects like Total Ionizing dose (TID) and Single event effects (SEE).

To overcome these limitations, alternative solutions have been explored with respect to the device's layout geometry (circular, octagonal, and hexagonal, etc.). The circular gate transistor (CGT) is one such layout based solution that can extend the traditional CMOS process while using less silicon area. Owing to the circular structure they are immune to CE and radiation effects. Due to their asymmetric enclosed design, the inner/outer silicon pad can be configured as Source/Drain or Drain/Source. With the internal drain configuration these CGTs can enhance the LEF along the channel and improve the device performance.

In this thesis, initially, the performance of a novel circular double gate (CDGT) silicon on insulator (SOI) metal oxide semiconductor field effect transistor (MOSFET) to mitigate the SCEs is presented and the compared with existing circular single gate (CSGT) device at 30 nm technology node by using fully calibrated TCAD. In addition, the effects of various device configurations, such as raised S/D topologies and junctionless mode analysis, on CCGT device performance have been investigated.

At sub 10 nm technology nodes a similar comparison is performed between CSGT and CCGT for Low power (LP) and High performance (HP) applications. Among these two, the best device i.e., CCGT is benchmarked against popular multigate architectures. The proposed CCGT device is a suitable substitute for the NS FET in HP applications by offering a higher ON-current ( $I_{ON}$ ) for future technology nodes. The investigation of various CCGT architectures has been carried out further. Among all architectures, the  $HfO_2$  based CCGT architecture with 2 nm of underlap length provides good electrical properties, with an  $I_{ON}/I_{OFF}$

ratio greater than  $10^7$ , near-ideal subthreshold slope (SS), and reduced drain induced barrier lowering (DIBL).

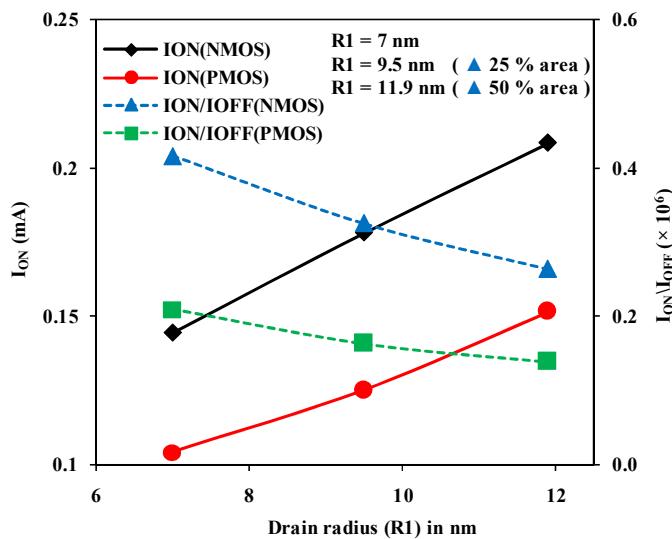

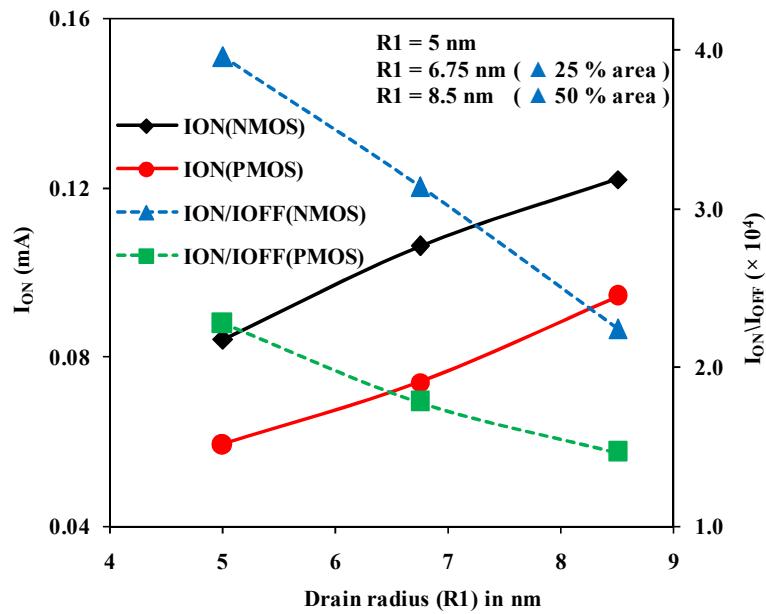

CDGT is further optimized for ON current, by increasing the device area(inner drain radius). Using this concept, increasing the device area by 25% and 50% improves the total ON current by 19% and 39%, respectively. Further, similar analysis is performed at lower nodes 7 nm & 5 nm. The findings indicate that a similar improvement in ON current is observed for future scaling. The influence of source/drain doping concentration is also been investigated on proposed CDT device.

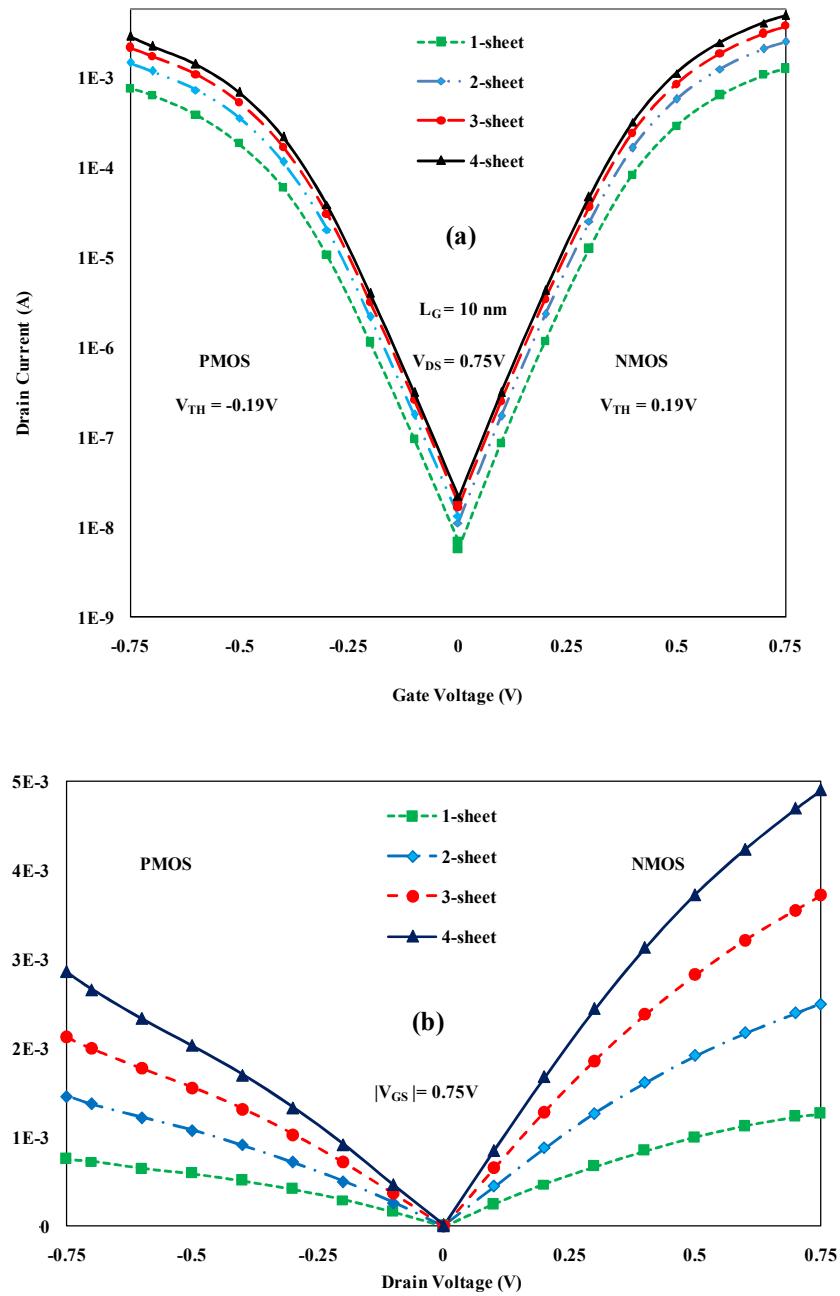

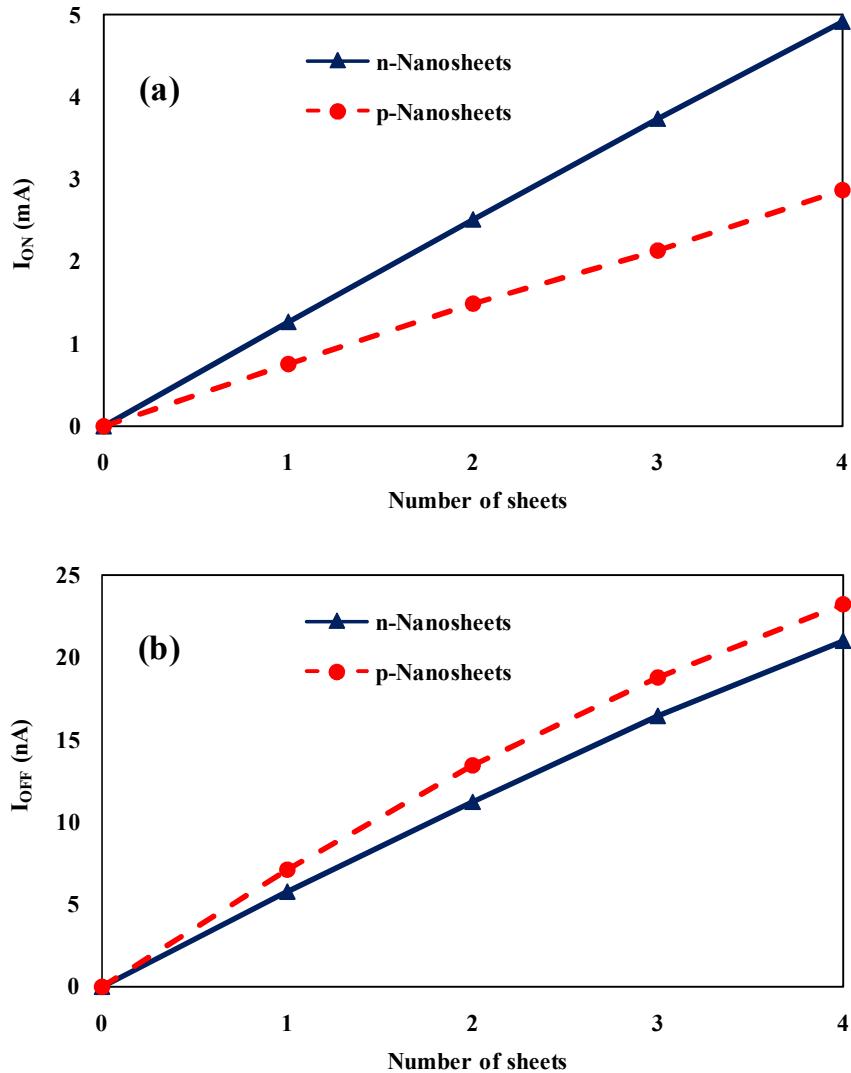

Furthermore, novel NSFETs with circular layout geometry, i.e., Circular Nanosheet MOSFETs (C-NSFETs) are proposed for HP applications at 10 nm gate length. Further, the C-NSFETs performance by vertically stacking the circular sheets (2-sheet, 3-sheet, and 4-sheet) are explored and named them as Stacked Circular NSFETs (SC-NSFETs) and analyzed the variations of their device performance. It is observed that the device drive current is further improved by stacking multiple nanosheets within the same footprint.

Circuit performance is estimated on different circular MOSFETs using the effective current method at the 30 nm technology node, and then detailed analysis is performed using transient simulations at the 10 nm technology node.

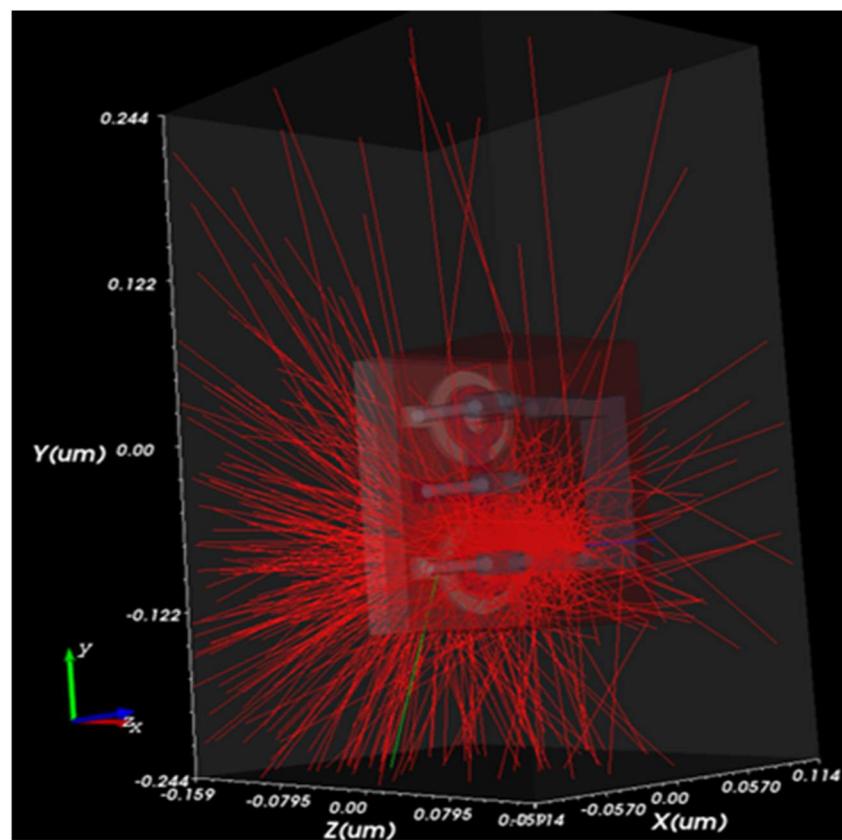

Finally, analyzed the effects of radiation such as TID and SEEs, on electrical characteristics of the enclosed circular layout transistors like CSGT and CDT, at 10 nm gate length ( $L_G$ ). The results show that TID has minimal effect on the electrical properties of enclosed circular layout transistors and is insignificant in the case of CDT. During the SEEs simulation, the alpha particles with low energy of 1.5 MeV-  $\text{cm}^2/\text{mg}$  Linear energy transfer (LET) and heavy ion particles with the high energy of 35 MeV- $\text{cm}^2/\text{mg}$  LET are employed. The CDT devices are less sensitive to the Single event transient (SET) in the inverter analysis due to their strong gate controllability by two gates and enclosed circular geometry. These circular FETs show superior immunity to radiation effects due to the enclosed layout. The CDT outperforms the CSGT in terms of electrical performance and is less sensitive to the TID effect and SEEs. This TCAD based simulation study proves the suitability of CDT devices in aerospace and military applications.

# List of Figures

|                                                                                                                                                                                                                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.1: Moore's Law and More [4].....                                                                                                                                                                                                                                                                                                                                          | 2  |

| Fig. 1.2: The New Ecosystem of the Electronics Industry [5] .....                                                                                                                                                                                                                                                                                                                | 2  |

| Fig. 1.3: (a) Rectangular MOSFET layout (b) Circular MOSFET layout, (c) Structure of Circular MOSFET.....                                                                                                                                                                                                                                                                        | 5  |

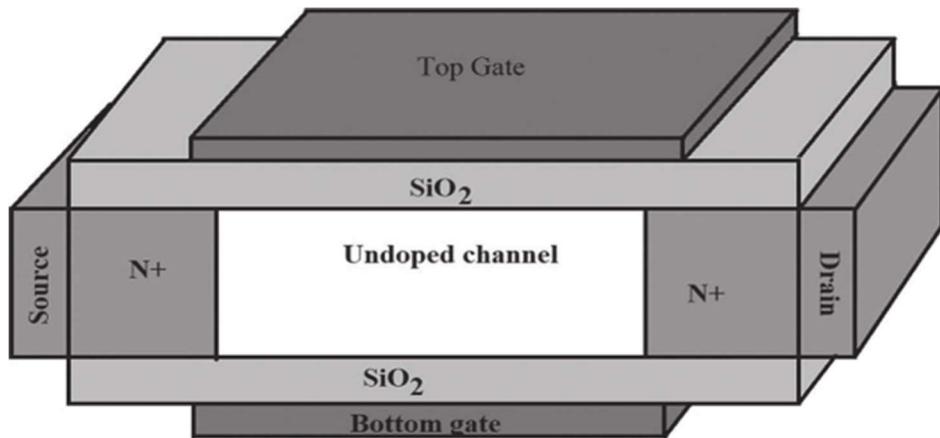

| Fig. 2.1: Structure of Double gate MOSFET [72].....                                                                                                                                                                                                                                                                                                                              | 11 |

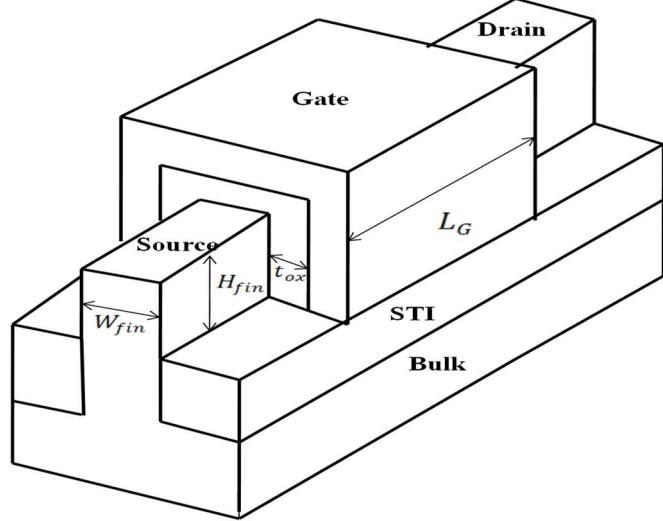

| Fig. 2.2: Structure of FinFET.....                                                                                                                                                                                                                                                                                                                                               | 12 |

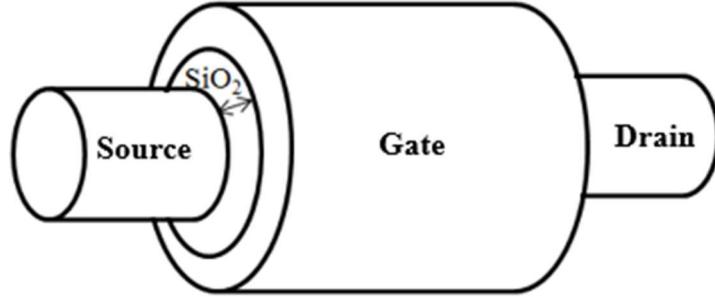

| Fig. 2.3: Structure of NWFET.....                                                                                                                                                                                                                                                                                                                                                | 12 |

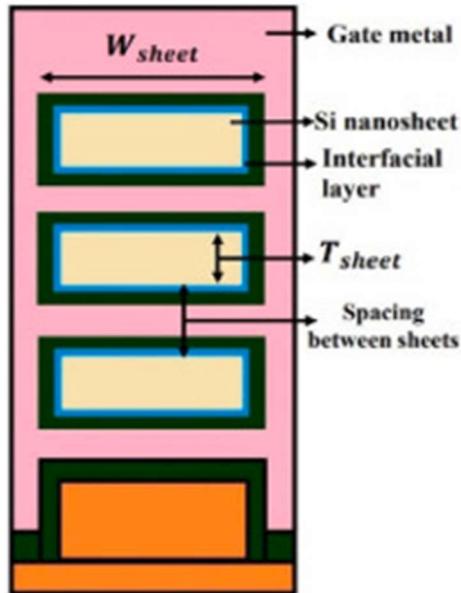

| Fig. 2.4: Structure of NSFET.....                                                                                                                                                                                                                                                                                                                                                | 13 |

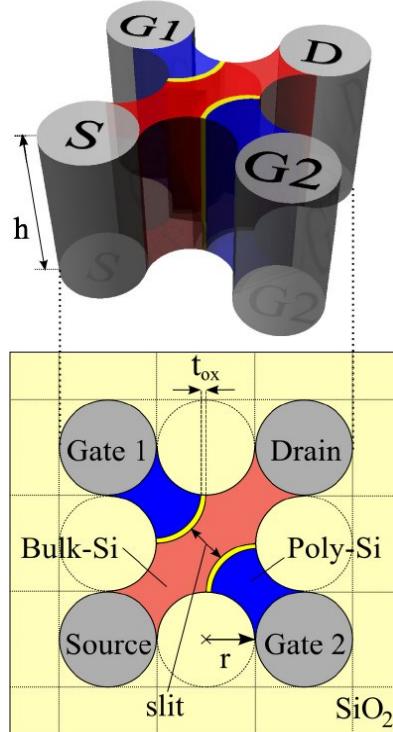

| Fig. 2.5: Structure of VeSFET [30].....                                                                                                                                                                                                                                                                                                                                          | 14 |

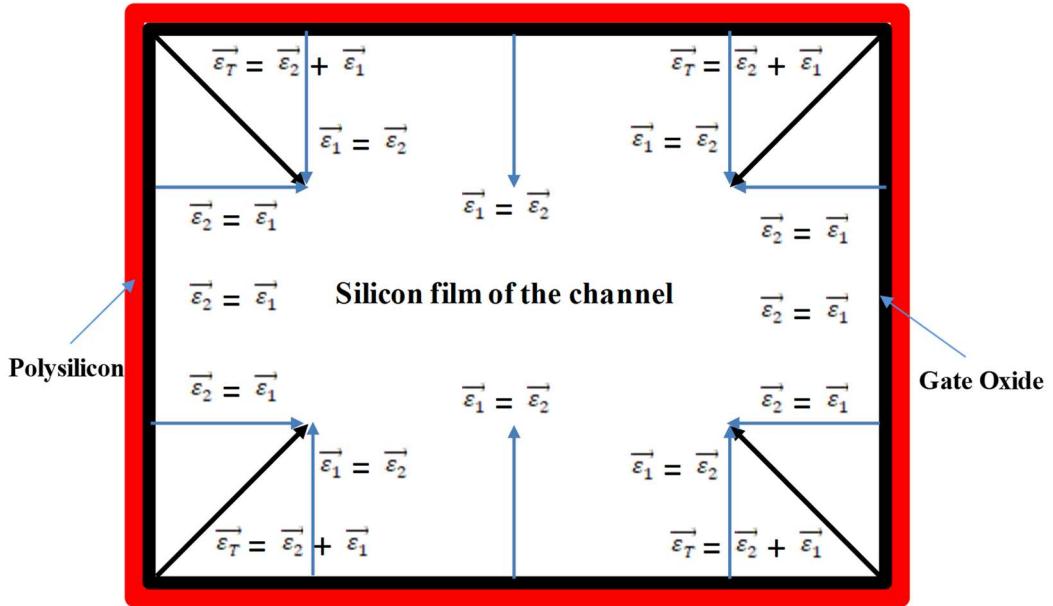

| Fig. 2.6: The PEF vector components ( $\varepsilon_1$ and $\varepsilon_2$ ) and their outcomes. ....                                                                                                                                                                                                                                                                             | 15 |

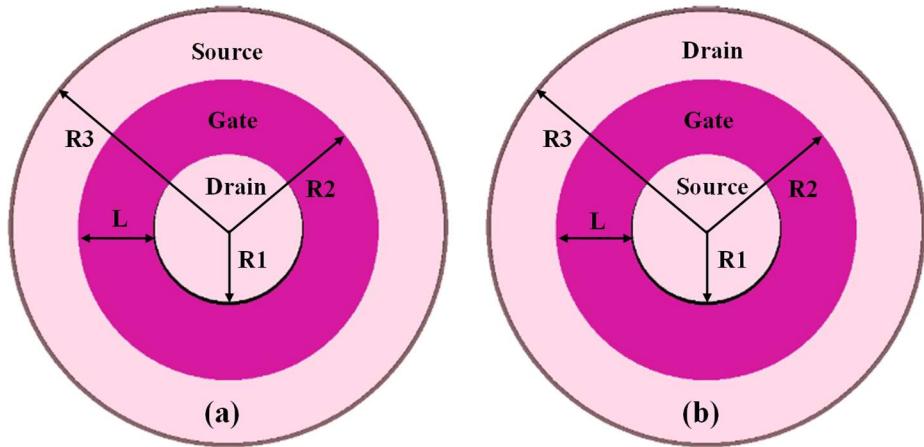

| Fig. 2.7: CGT MOSFETs which is operating in a) Internal drain configuration, b) External drain configuration. ....                                                                                                                                                                                                                                                               | 16 |

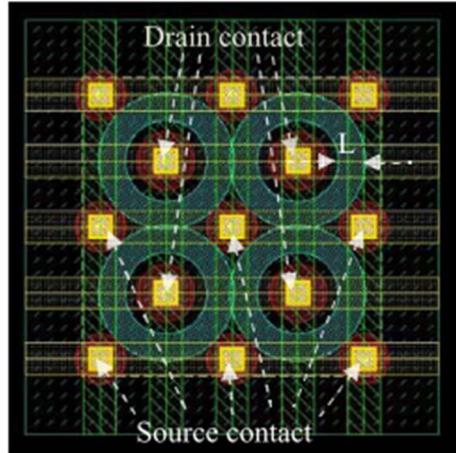

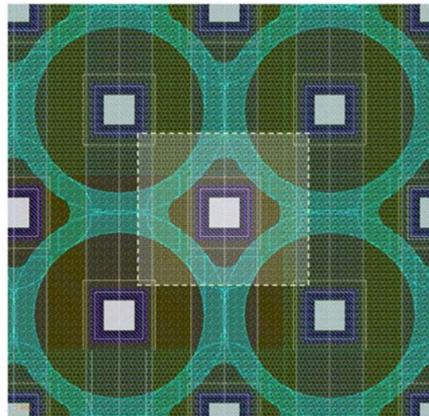

| Fig. 2.8: 2 $\times$ 2 array of O-CGT [94].....                                                                                                                                                                                                                                                                                                                                  | 17 |

| Fig. 2.9: Alternative overlapping CGT structure [95].....                                                                                                                                                                                                                                                                                                                        | 17 |

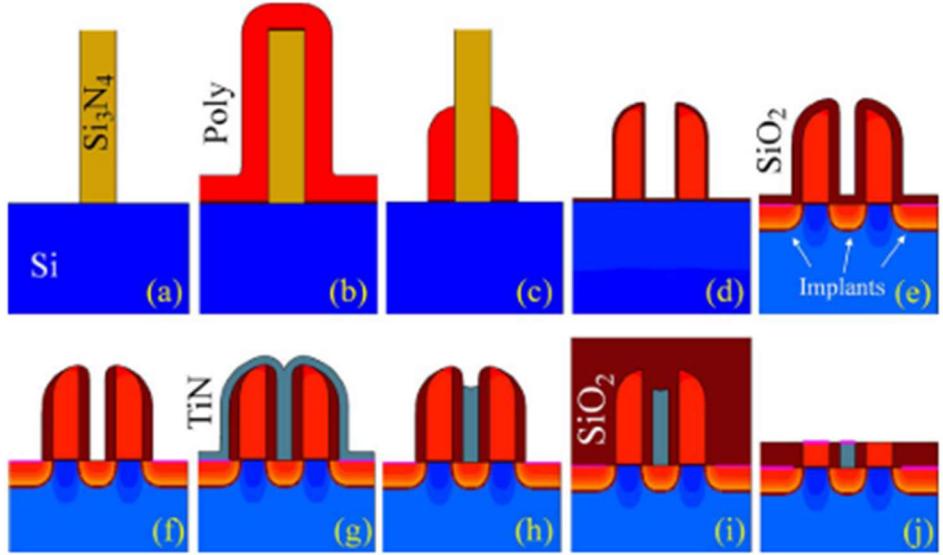

| Fig. 2.10: Process setups (a) Lithography Reactive Ion Etch (RIE) Si <sub>3</sub> N <sub>4</sub> , (b) Deposit SiO <sub>2</sub> /poly, (c) RIE poly/SiO <sub>2</sub> , (d) Grow SiO <sub>2</sub> , (e) Implant, deposit, SiO <sub>2</sub> , (f) RIE SiO <sub>2</sub> , (g) Deposit metal, (h) Etch metal, (i) Deposit SiO <sub>2</sub> , (j) Chemical Mechanical Polishing. .... | 18 |

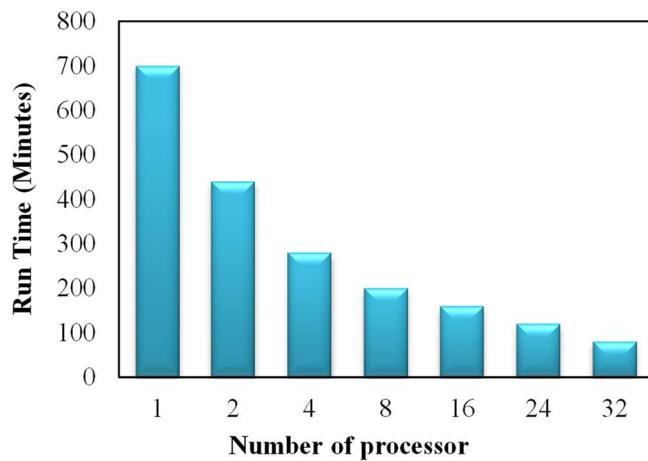

| Fig. 3.1: Processor core (vs) Simulation time in minutes of a CMOS inverter in Genius [120].....                                                                                                                                                                                                                                                                                 | 23 |

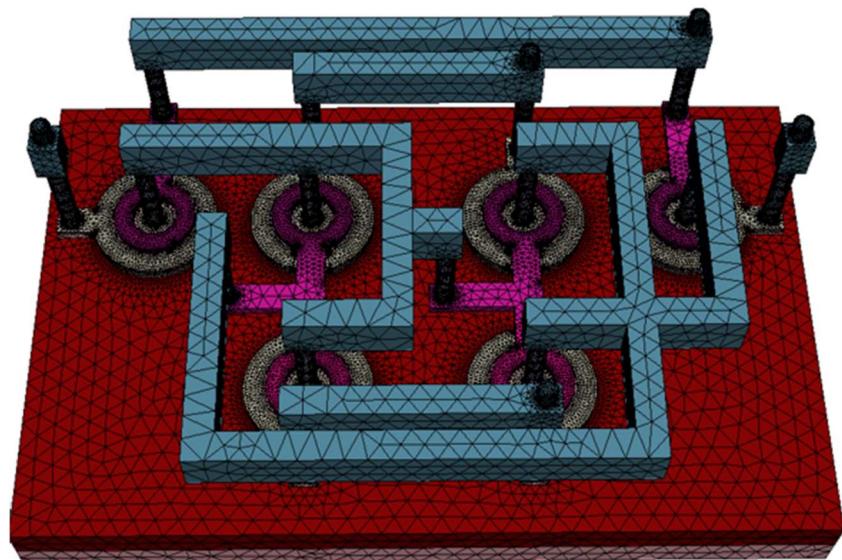

| Fig. 3.2: Device modeling and mesh generation during Genius simulation. ....                                                                                                                                                                                                                                                                                                     | 23 |

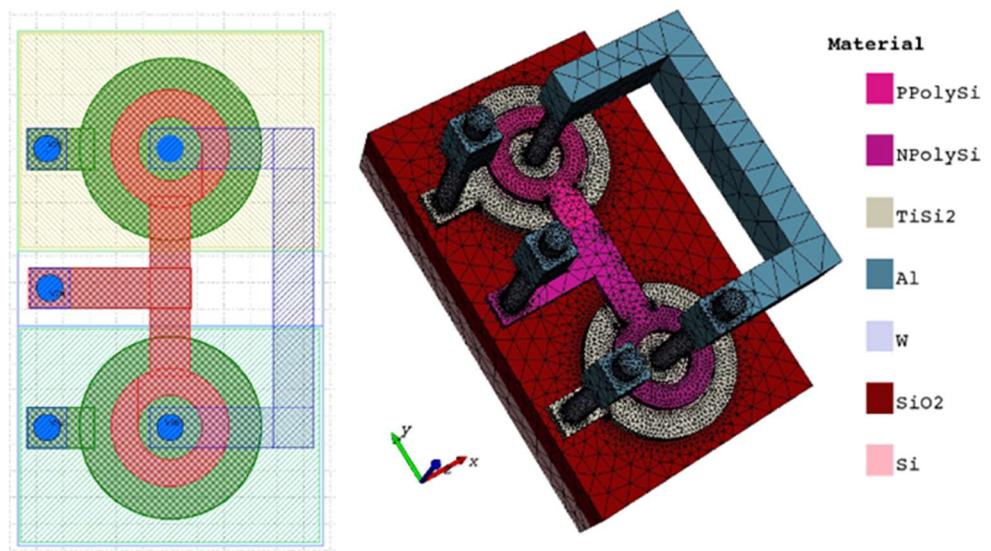

| Fig. 3.3: (a) Layout of inverter, (b) corresponding 3D inverter. ....                                                                                                                                                                                                                                                                                                            | 24 |

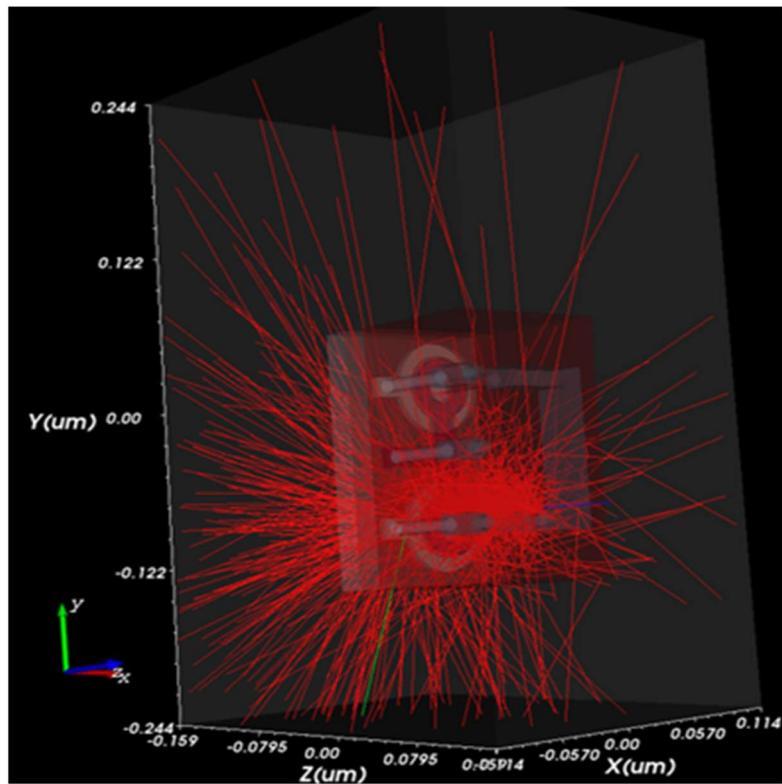

| Fig. 3.4: Radiation tracks due to incident particles. ....                                                                                                                                                                                                                                                                                                                       | 25 |

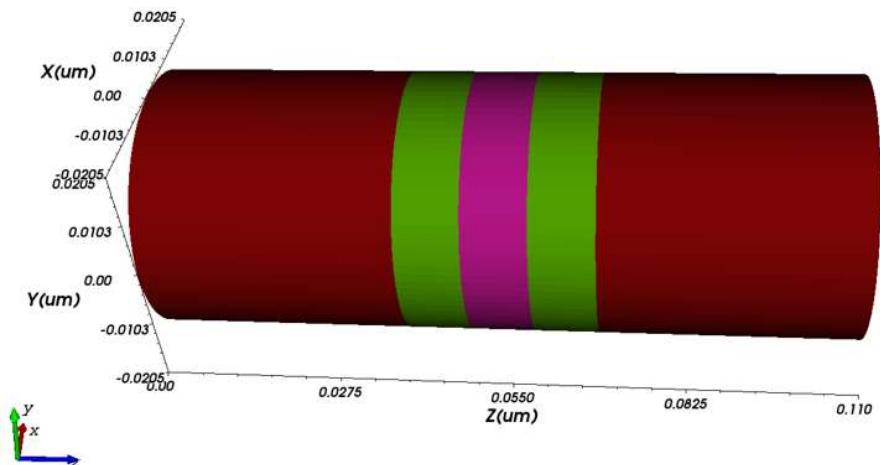

| Fig. 3.5: 3D schematic view of calibrated NWFET structure at 30 nm node. ....                                                                                                                                                                                                                                                                                                    | 27 |

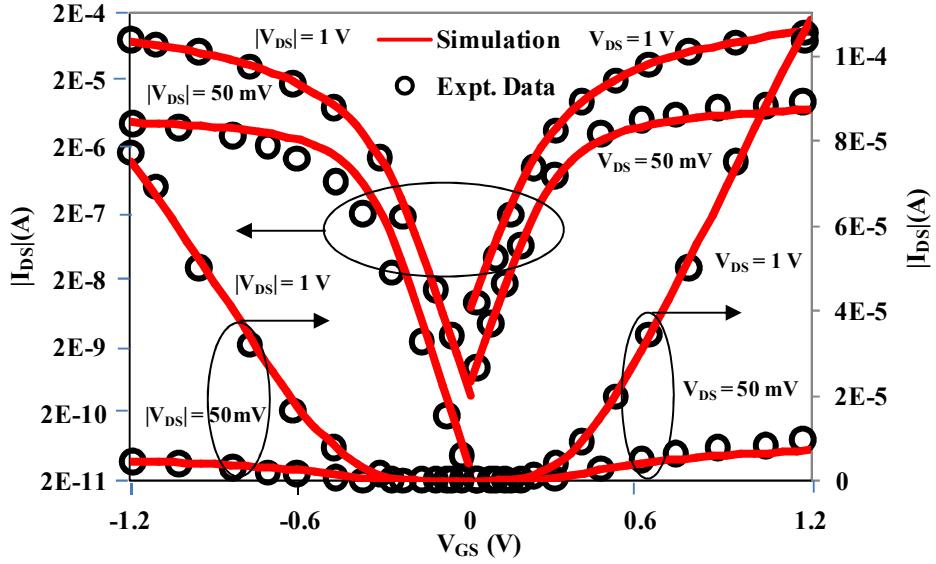

| Fig. 3.6: Calibration with an experimental nanowire FET [48] at 30 nm. ....                                                                                                                                                                                                                                                                                                      | 27 |

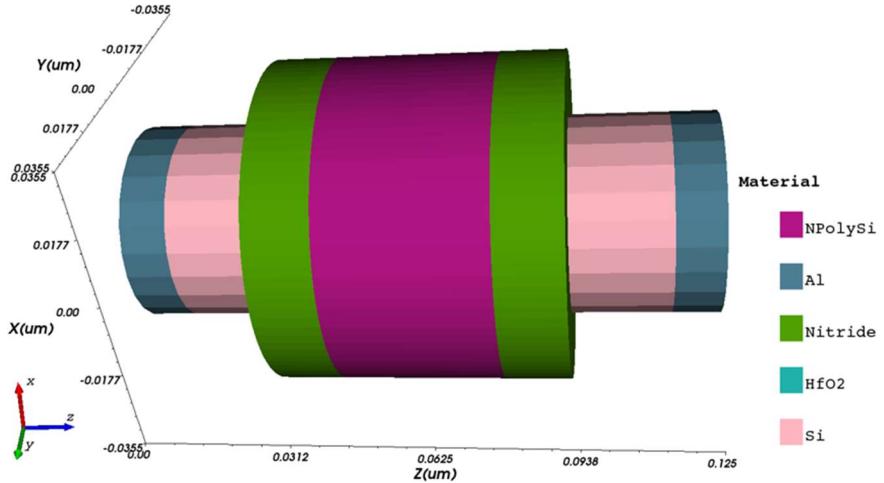

| Fig. 3.7: 3D schematic view of calibrated NWFET structure at 10 nm node. ....                                                                                                                                                                                                                                                                                                    | 29 |

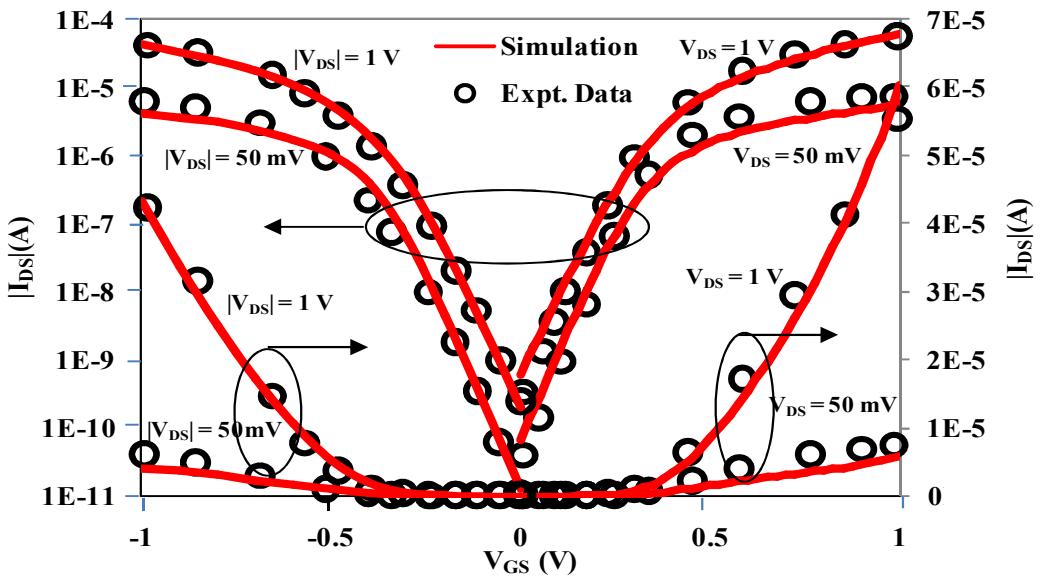

| Fig. 3.8: Calibration with an experimental nanowire FET [49] at 10 nm. ....                                                                                                                                                                                                                                                                                                      | 30 |

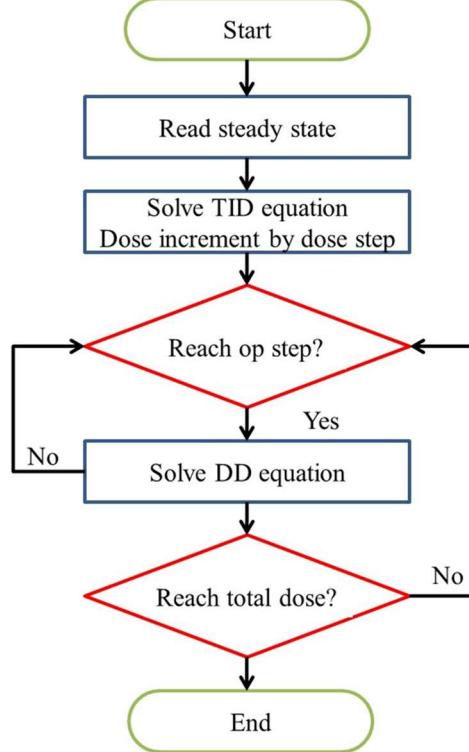

| Fig. 3.9: TID command flow chart [126]. ....                                                                                                                                                                                                                                                                                                                                     | 32 |

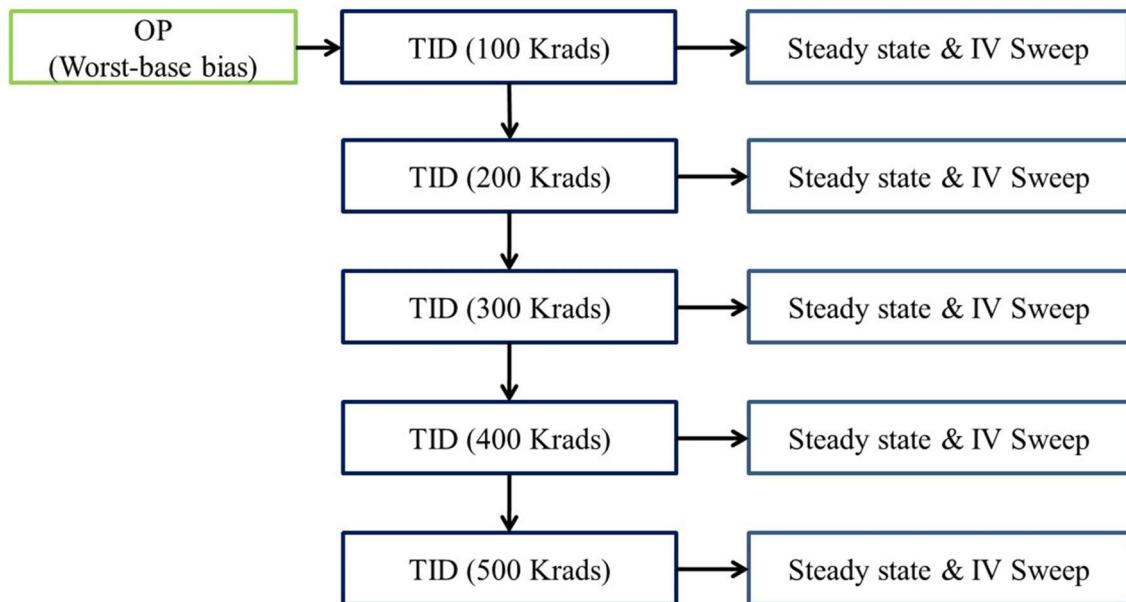

| Fig. 3.10: TID simulation flow chart [126]. ....                                                                                                                                                                                                                                                                                                                                 | 33 |

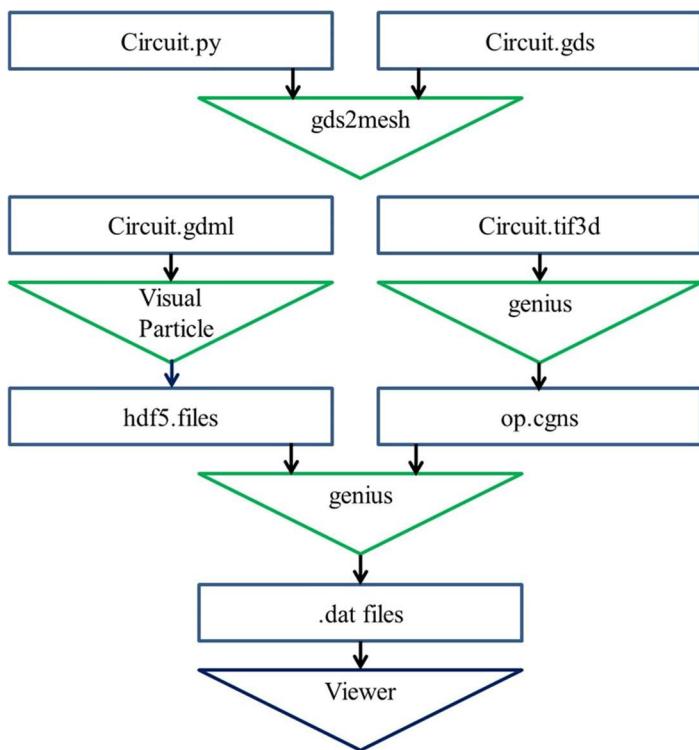

| Fig. 3.11: Modeling flow (steps and tools) [130]. ....                                                                                                                                                                                                                                                                                                                           | 34 |

| Fig. 4.1: (a) 3D view of a circular gate SOI MOSFET, (b) 3D-CSGT, (c) 2D-CSGT with doping profiles.....                                                                                                                                                                                                                                                                          | 35 |

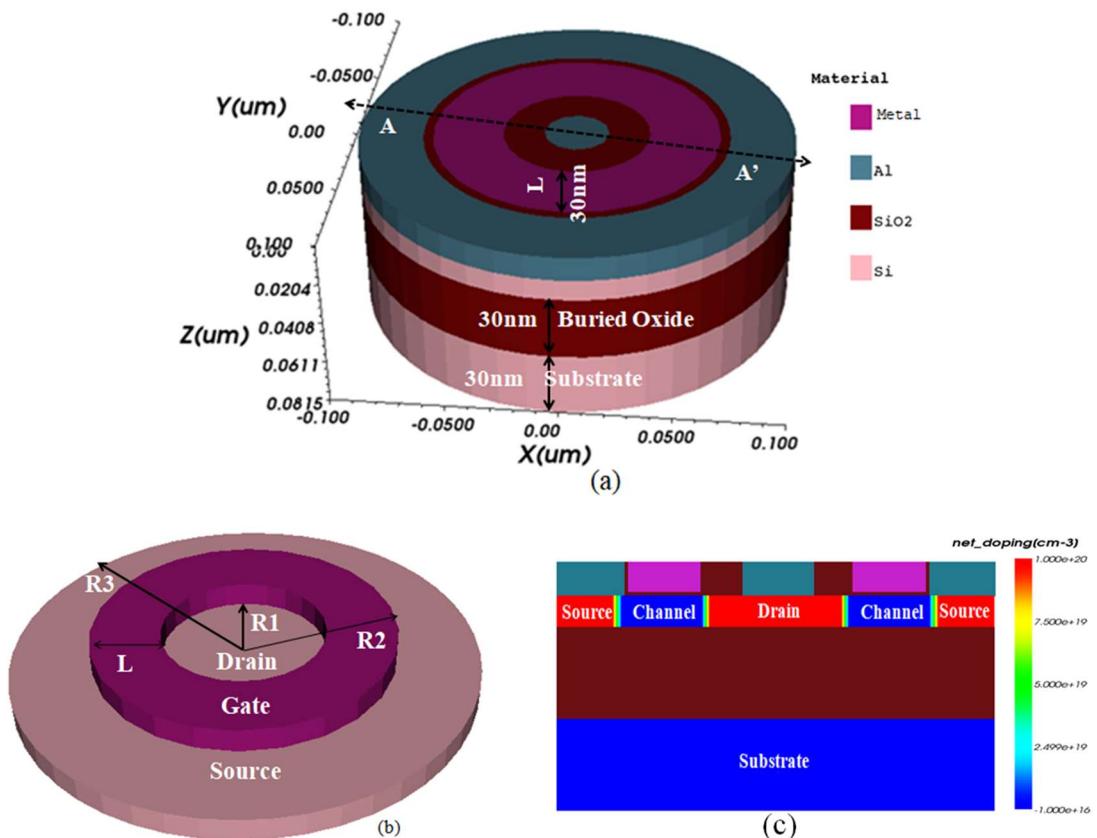

| Fig. 4.2: (a) 3D view of a circular double gate SOI MOSFET, (b) 2D-CSGT with doping profiles....                                                                                                                                                                                                                                                                                 | 36 |

| Fig. 4.3: Fabrication process of the CDGT SOI MOSFET. (a) Bulk silicon wafer is thermally oxidized, (b) Lithography and patterning the bottom gate cavities, (c) bottom metal gate deposition and                                                                                                                                                                                |    |

|                                                                                                                                                                                                                                             |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| patterning, (d) deposition of active silicon and patterning, (e) top gate oxidation, metal gate deposition, patterning, and doping, (f) metallization.....                                                                                  | 37 |

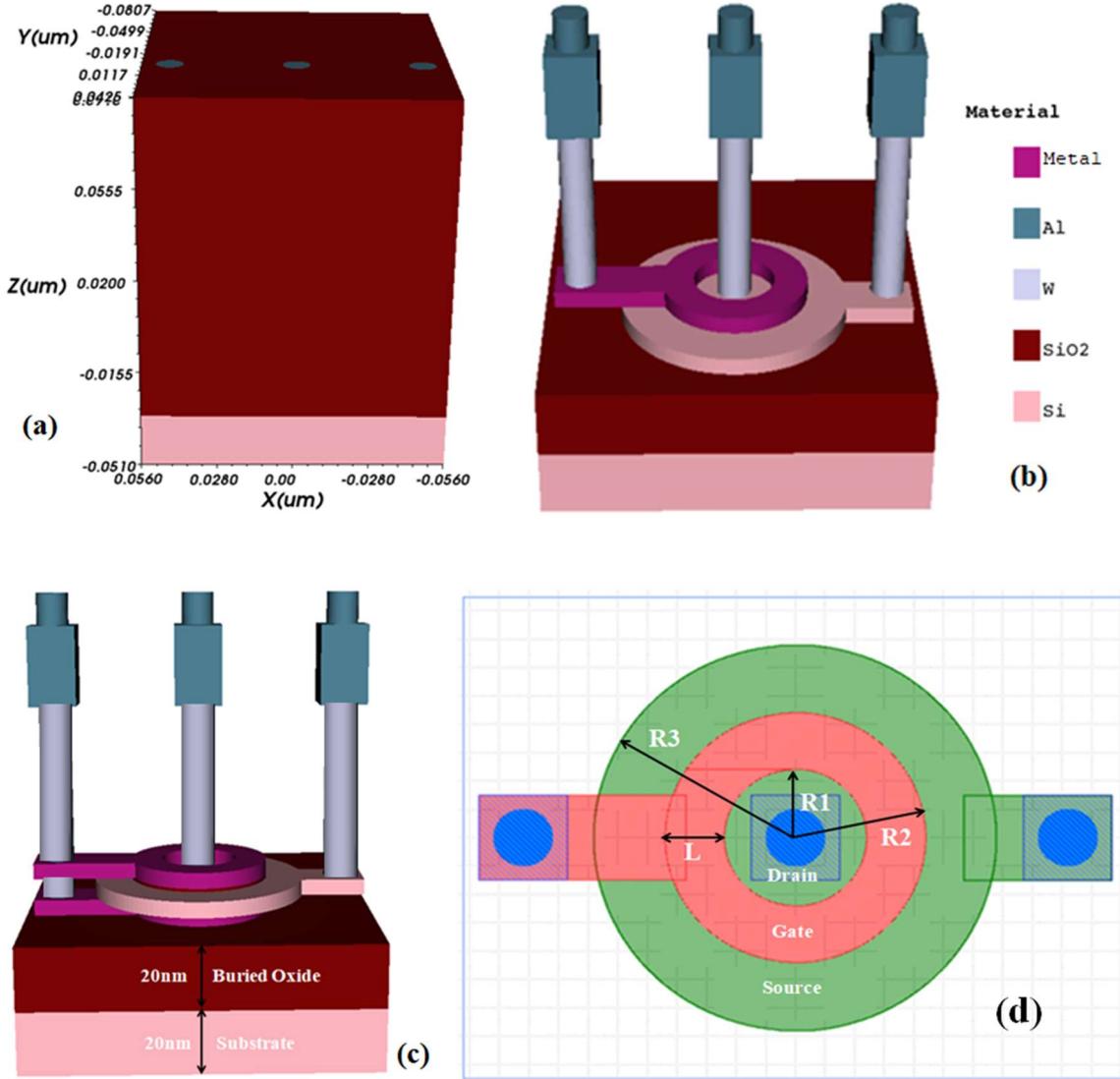

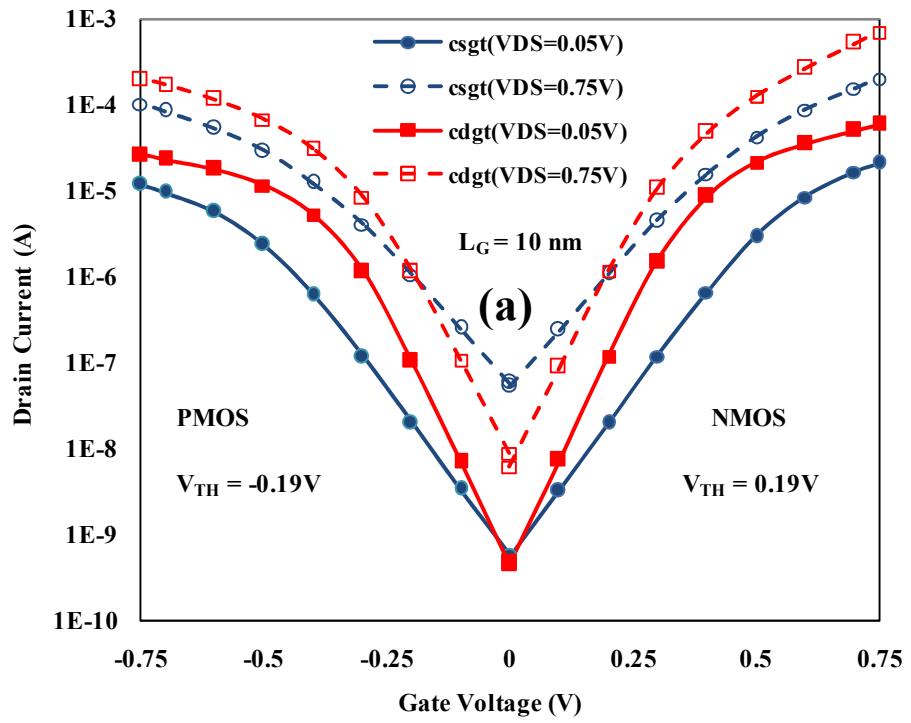

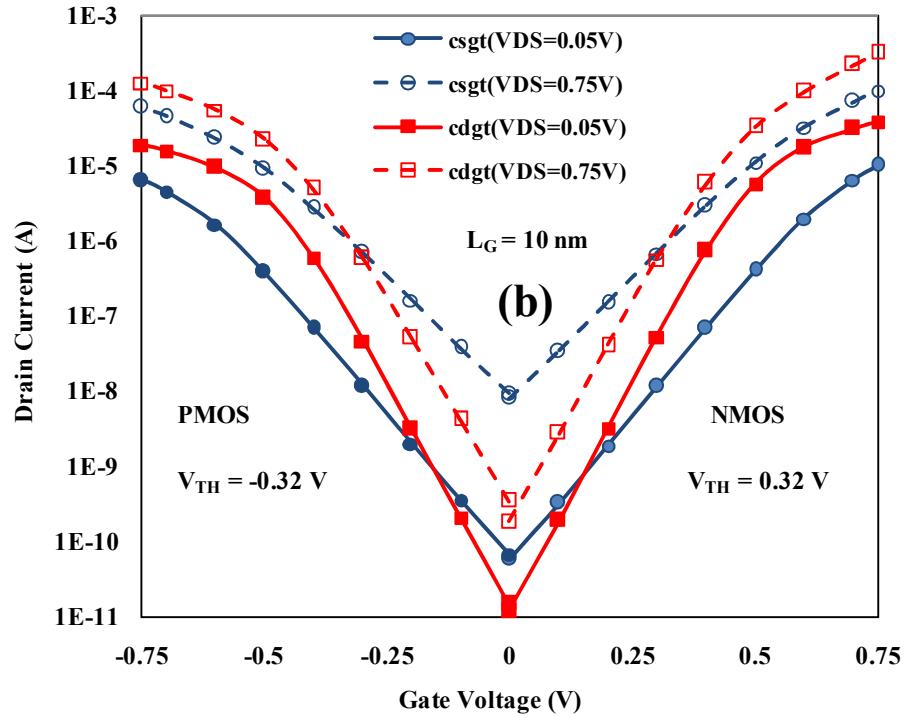

| Fig. 4.4: (a) $I_{DS}$ - $V_{GS}$ of the CSGT and the CDGT for both NMOS and PMOS devices with L and $V_{TH}$ values shown inset, (b) $I_{DS}$ - $V_{DS}$ of the CSGT and the CDGT devices.....                                             | 39 |

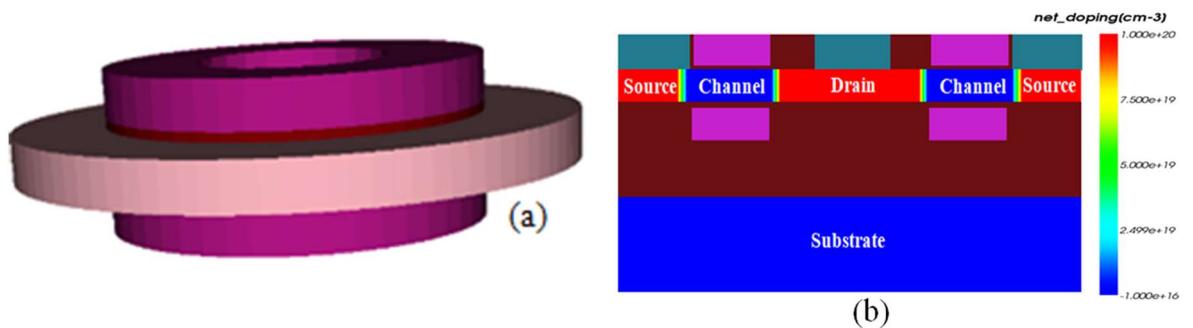

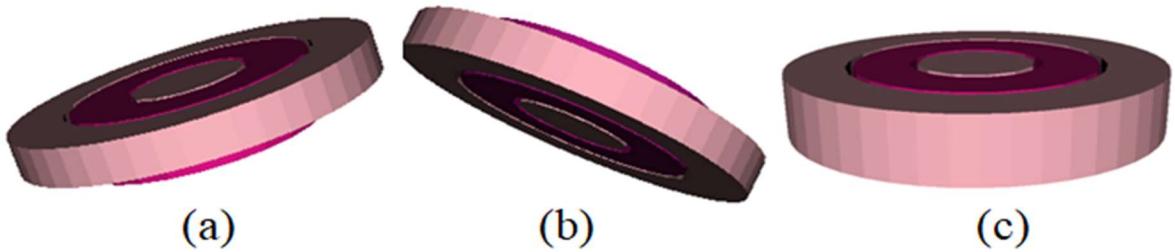

| Fig. 4.5: 3D view of CDGT SOI MOSFET with Source/Drain (a) raised top, (b) raised bottom, (c) raised top and bottom ('both') structures.....                                                                                                | 40 |

| Fig. 4.6: 2D cut view of raised top, raised bottom, and raised 'both' CDGT SOI MOSFETs.....                                                                                                                                                 | 40 |

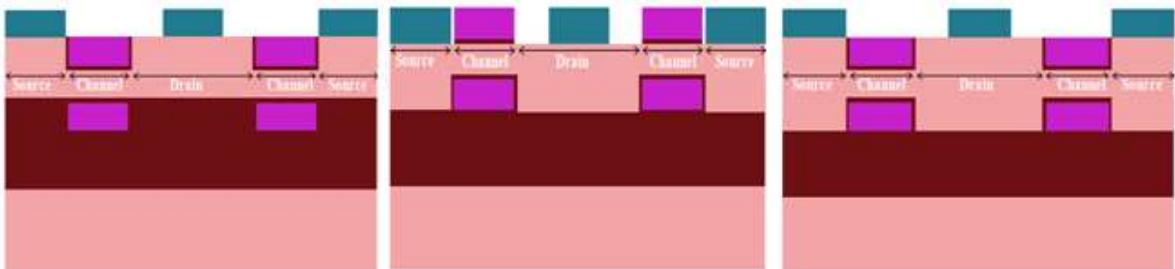

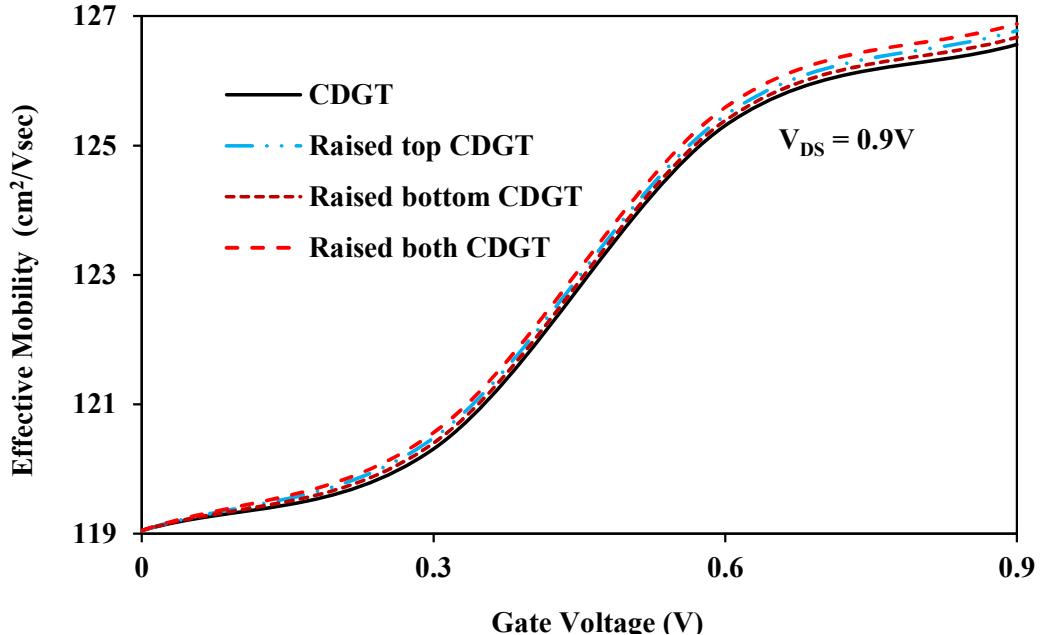

| Fig. 4.7: (a) Surface Potential, (b) Electric field along the channel for various raised structures.....                                                                                                                                    | 41 |

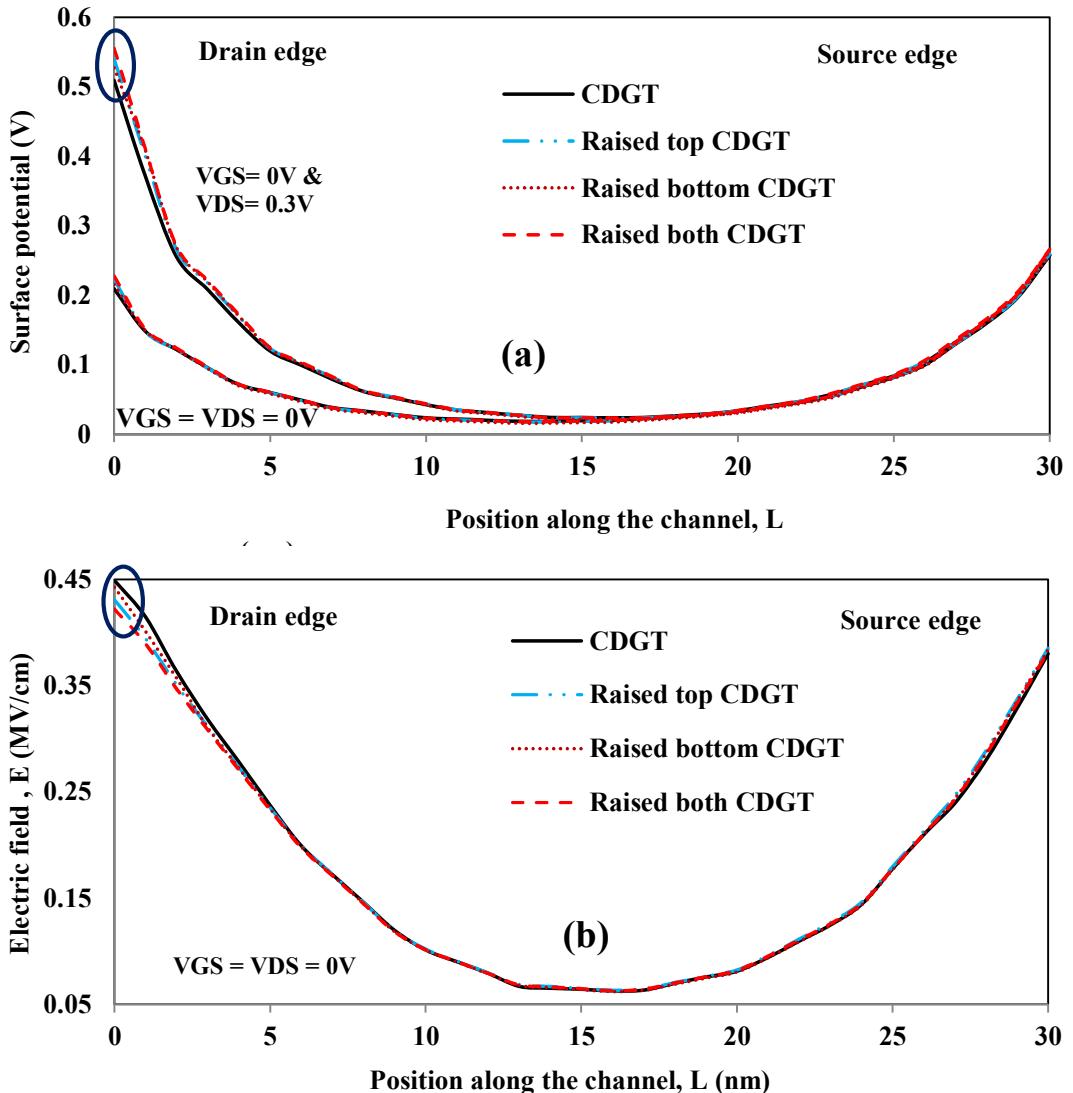

| Fig. 4.8: Effective mobility (vs) $V_{GS}$ for different raised CDGT structures.....                                                                                                                                                        | 42 |

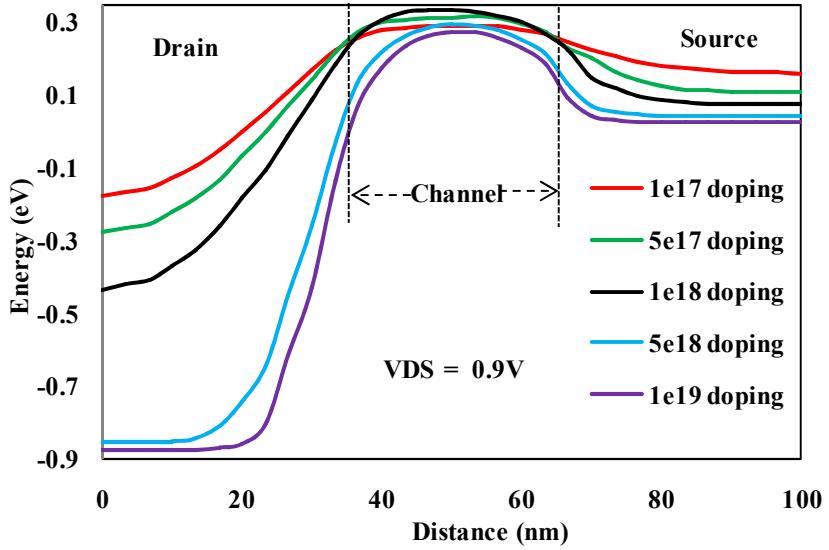

| Fig. 4.9: Conduction band energy in the lateral direction for various doping concentrations. ....                                                                                                                                           | 44 |

| Fig. 4.10: Variation of (a) SS, and (b) $I_{ON}/I_{OFF}$ and DIBL versus various doping concentrations.....                                                                                                                                 | 45 |

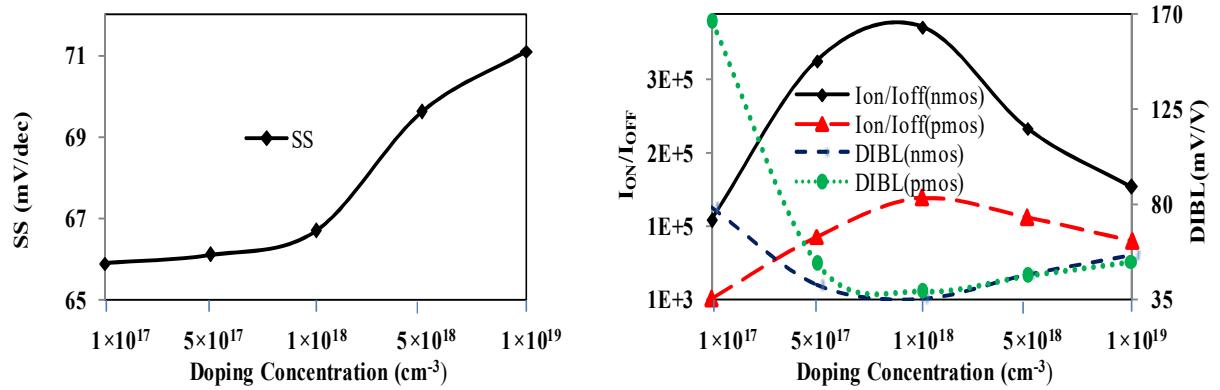

| Fig. 4.11: (a) 3-D design view of Circular SOI MOSFET, (b) & (c) CSGT and CDGT after removing passivation oxide layer respectively, (d) proposed layout of Circular MOSFET. ....                                                            | 46 |

| Fig. 4.12: $I_{DS}$ - $V_{GS}$ characteristics of both CSGT and CDGT SOI MOSFETs for HP applications....                                                                                                                                    | 48 |

| Fig. 4.13: $I_{DS}$ - $V_{GS}$ characteristics of both CSGT and CDGT SOI MOSFETs for LP applications. ....                                                                                                                                  | 48 |

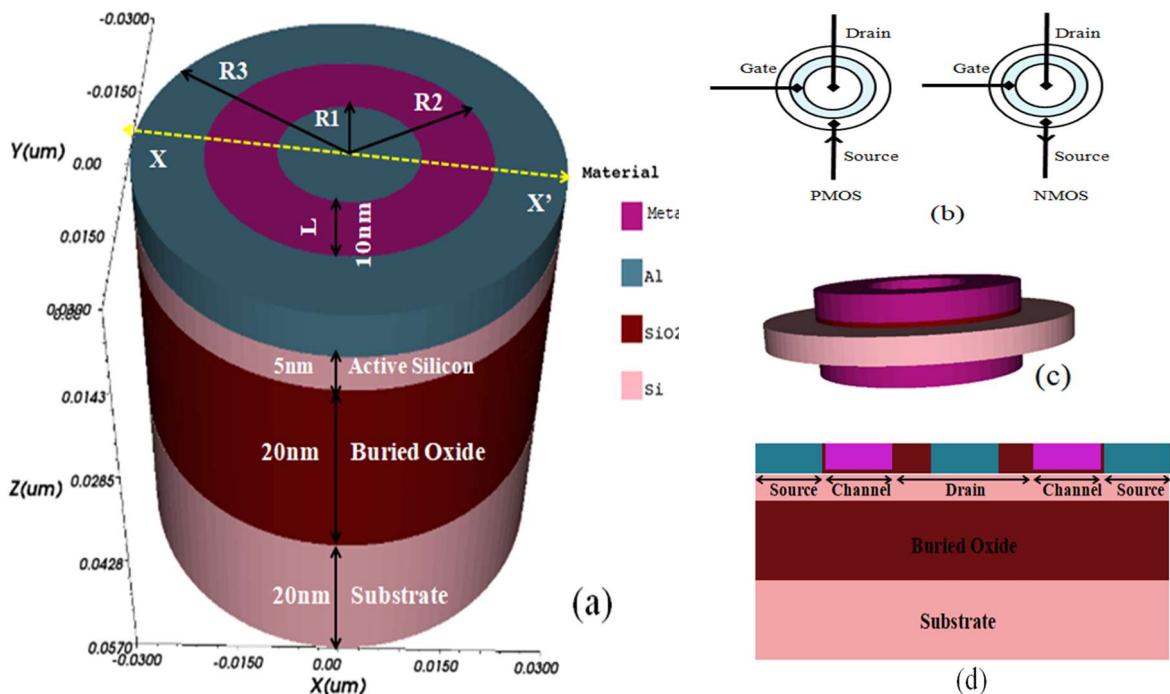

| Fig. 5.1: (a) 3-D schematic view of CDGT, (b) Symbol of Circular MOSFET, (c) 3D - CDGT, (d) 2D - CDGT.....                                                                                                                                  | 50 |

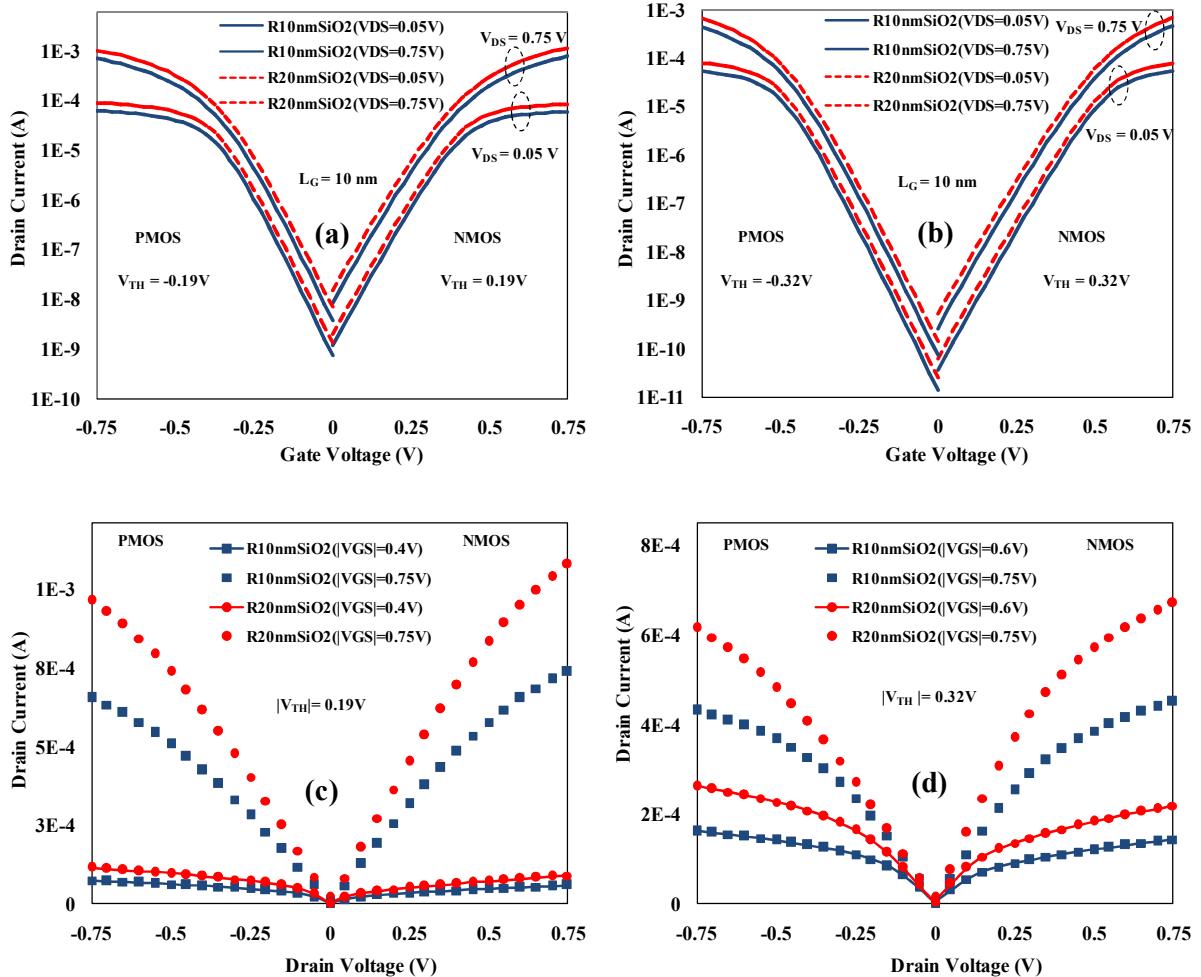

| Fig. 5.2: (a), (b) $I_{DS}$ - $V_{GS}$ of CDGT with $R1=10$ nm & 20 nm for both NMOS&PMOS devices. (c), (d) $I_{DS}$ - $V_{DS}$ of CDGT with $R1=10$ nm & 20 nm for both NMOS&PMOS devices & corresponding $V_{TH}$ values given inset..... | 52 |

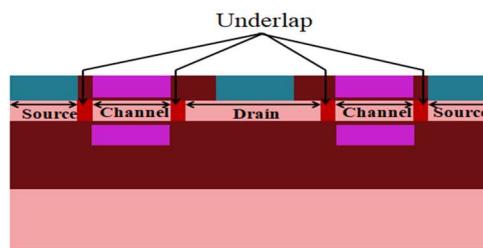

| Fig. 5.3: 2D – CDGT with underlap.....                                                                                                                                                                                                      | 53 |

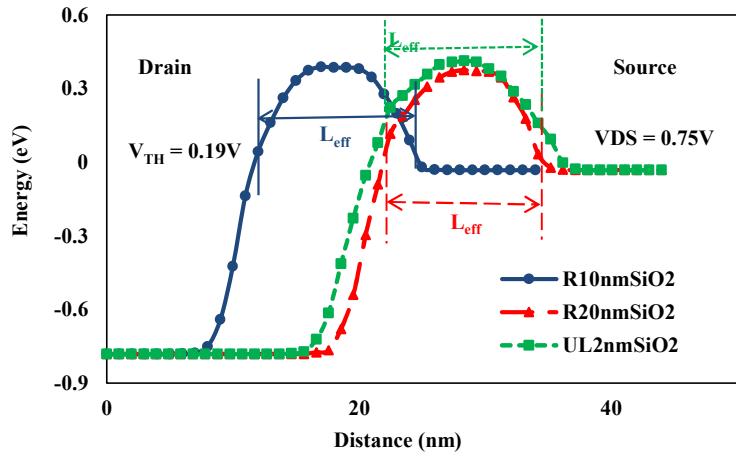

| Fig. 5.4: Conduction energy band profiles along the lateral direction for different CDGT devices....                                                                                                                                        | 55 |

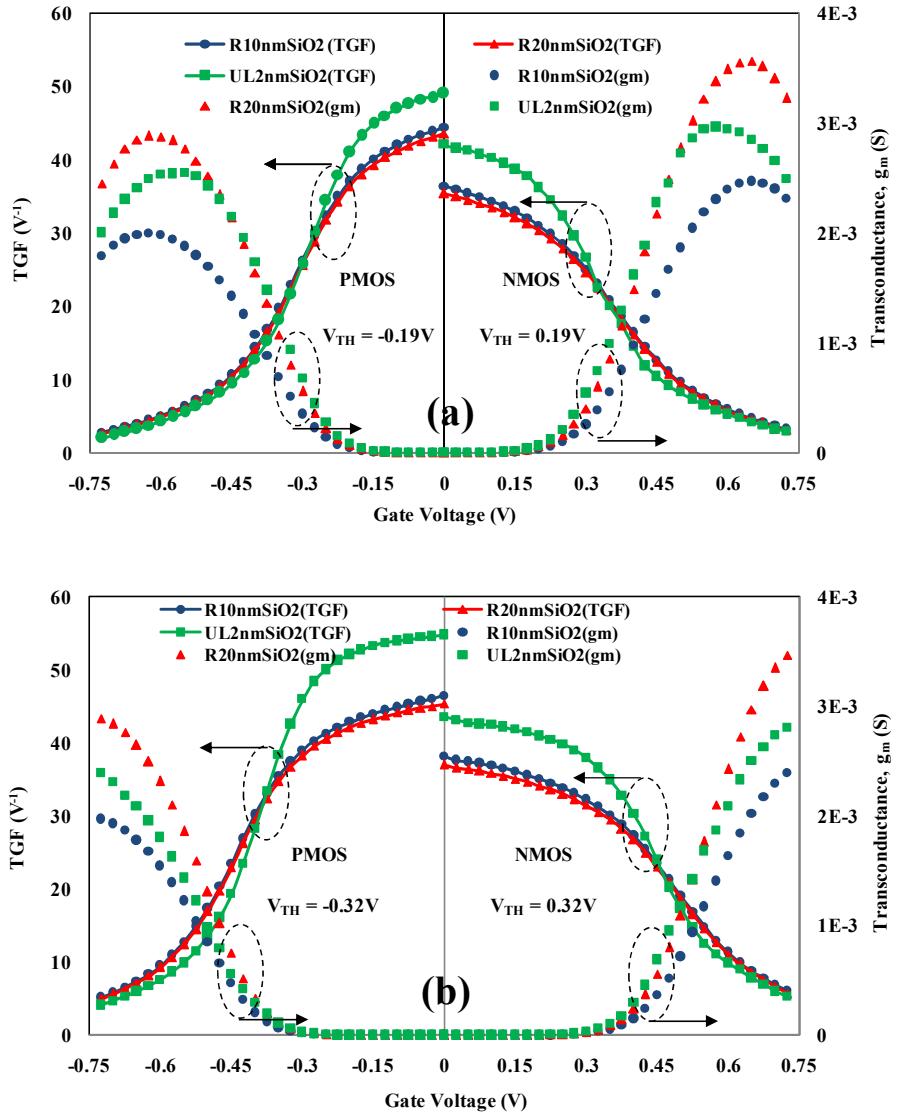

| Fig. 5.5: (a), (b) $g_m$ & TGF of CDGT with $R1=10$ nm, 20 nm, & UL2nm for both NMOS&PMOS devices, corresponding $V_{TH}$ values shown inset.....                                                                                           | 56 |

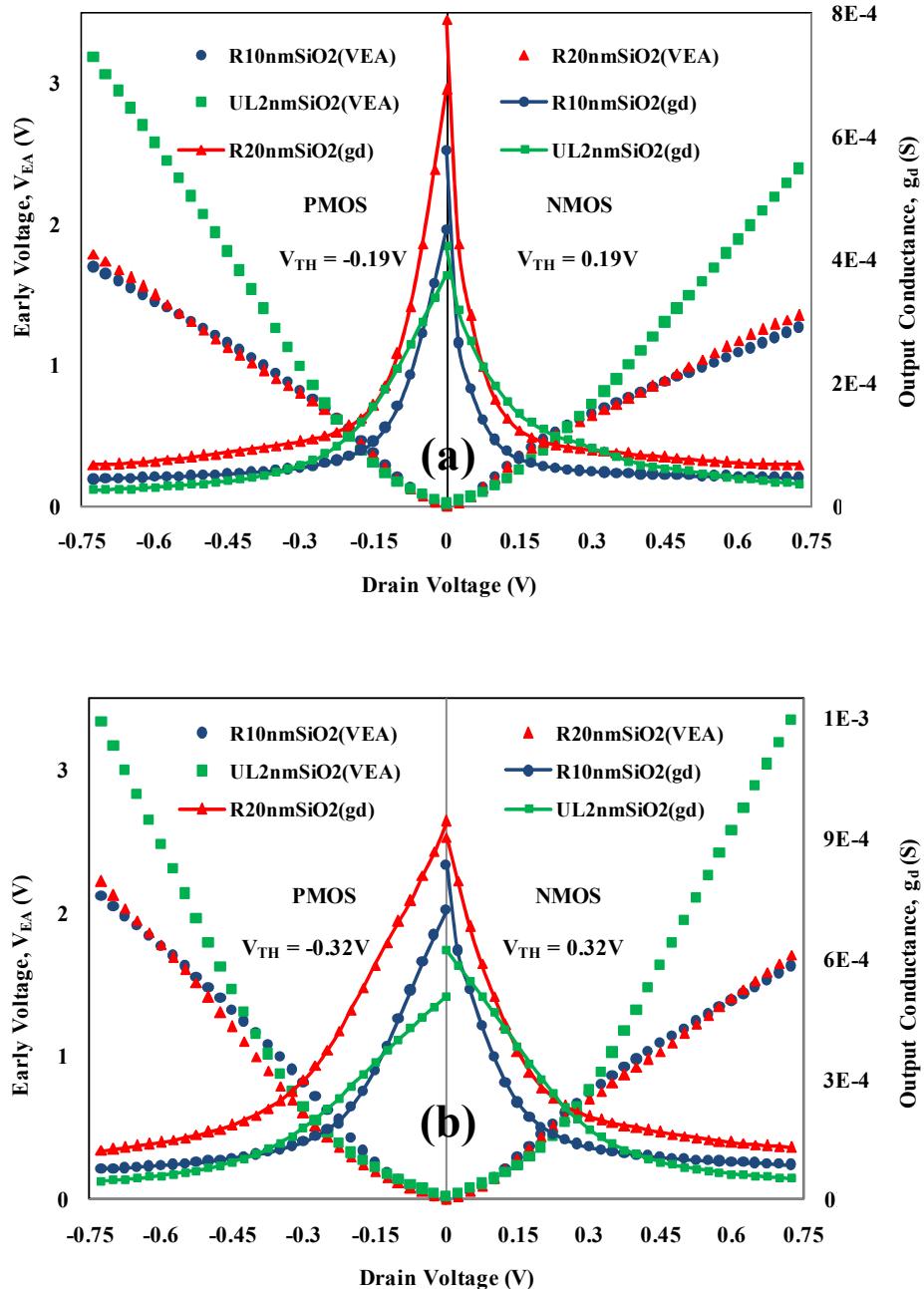

| Fig. 5.6: (a), (b) $g_d$ & $V_{EA}$ of CDGT with $R1=10$ nm, 20 nm, & UL2nm for both NMOS & PMOS devices, corresponding $V_{TH}$ values shown inset.....                                                                                    | 57 |

| Fig. 5.7: Percentage improvement in performance (%) using high-k dielectric on various device metrics.....                                                                                                                                  | 59 |

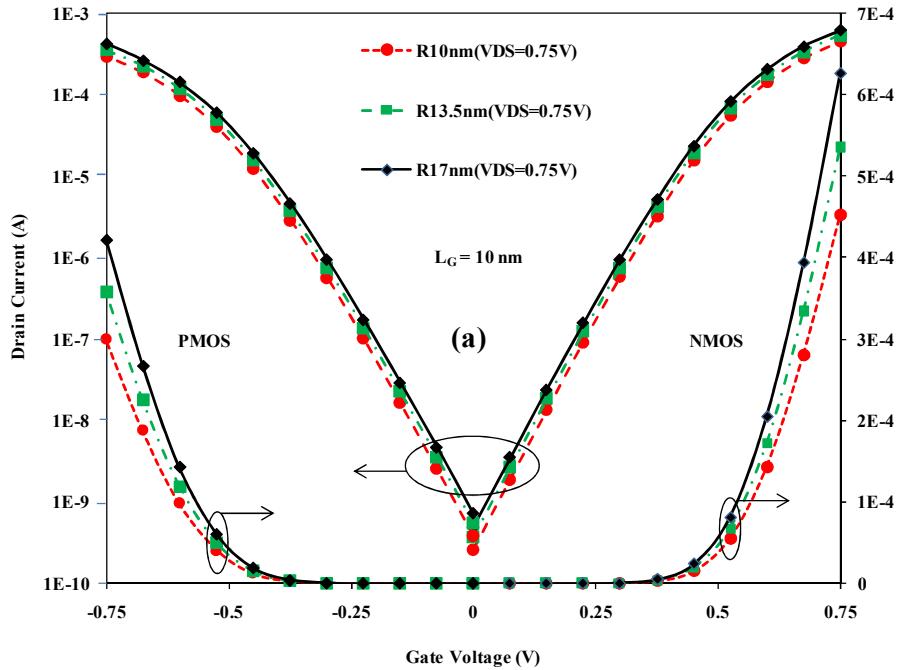

| Fig. 5.8: $I_{DS}$ - $V_{GS}$ characteristics for the 10 nm gate length with different inner radiiuses $R1 = 10$ nm, 13.5 nm, and 17 nm, on both linear (right) and logarithmic (left) scales, at high $V_{DS} = 0.75$ V....                | 62 |

| Fig. 5.9: Comparison of ON current and $I_{ON}/I_{OFF}$ ratios at 10 nm node.....                                                                                                                                                           | 63 |

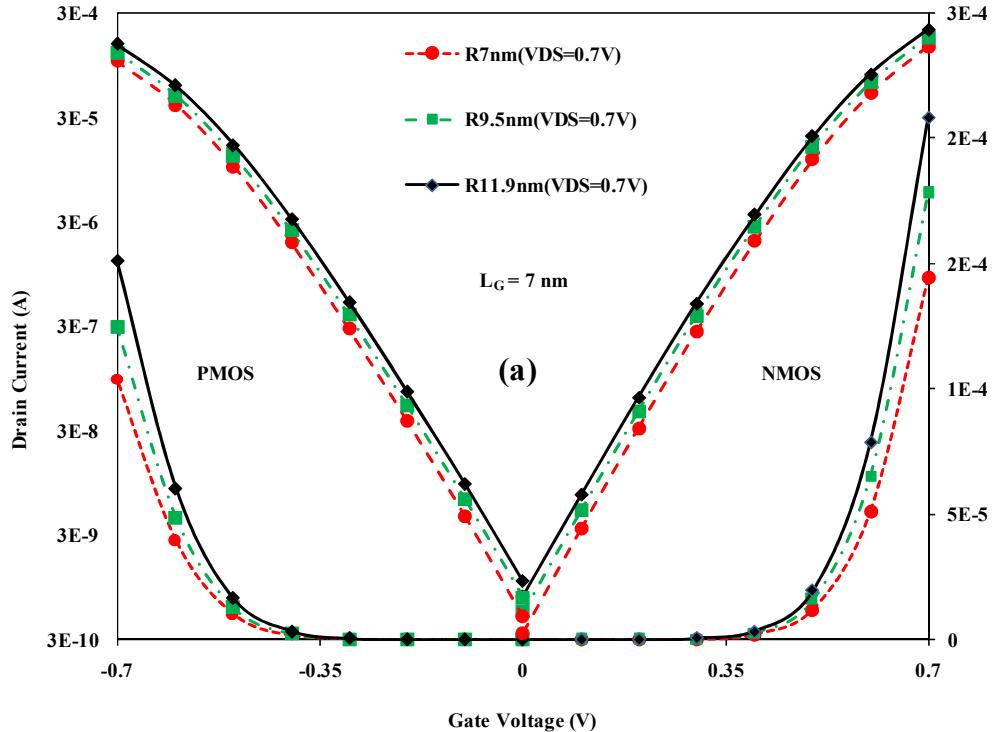

| Fig. 5.10: $I_{DS}$ - $V_{GS}$ characteristics for the 10 nm gate length with different inner radiiuses $R1 = 7$ nm, 9.5 nm, and 11.9 nm, on both linear (right) and logarithmic (left) scales, at high $V_{DS} = 0.7$ V....                | 64 |

| Fig. 5.11: Comparison of ON current and $I_{ON}/I_{OFF}$ ratios at 7 nm node.....                                                                                                                                                           | 64 |

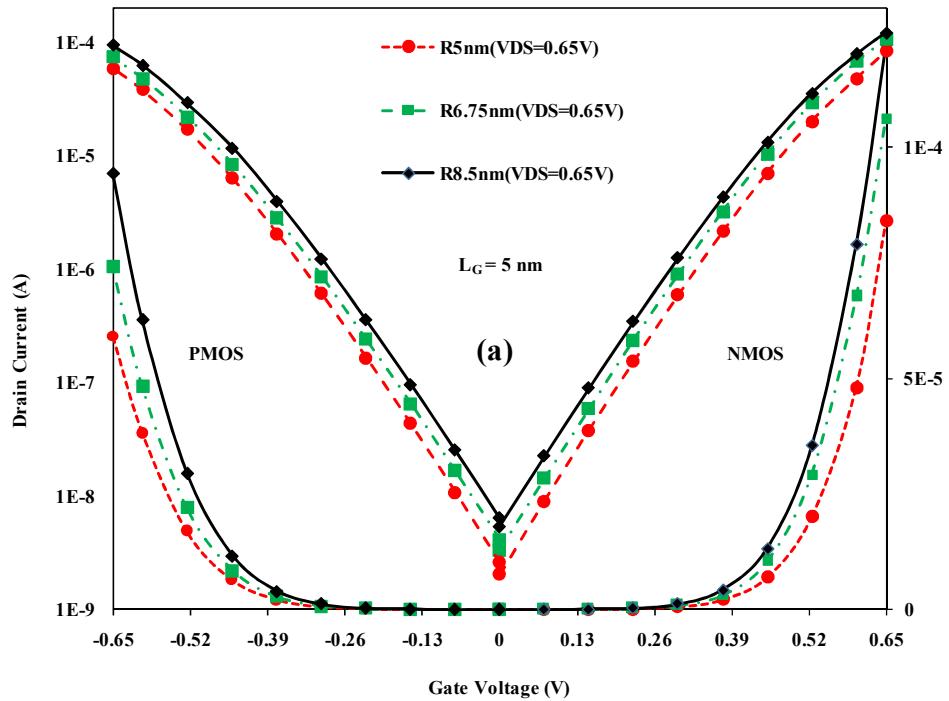

| Fig. 5.12: $I_{DS}$ - $V_{GS}$ characteristics for the 10 nm gate length with different inner radiiuses $R1 = 5$ nm, 6.5 nm, and 8.75 nm, on both logarithmic (left) and linear (right) scales, at high $V_{DS} = 0.65$ V...                | 66 |

|                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 5.13: Comparison of ON current and $I_{ON}/I_{OFF}$ ratios at 5 nm node.....                                                                                                                                                                                                                                                                               | 66 |

| Fig. 5.14: Electrical behavior of CDGT for various gate lengths, (a) ON current (b) Switching ratio and $V_{TH}$ of proposed CDGT devices.....                                                                                                                                                                                                                  | 68 |

| Fig. 5.15: Electrical behavior of CDGT with Tsi variations, (a) $I_{DS}$ - $V_{GS}$ (b) ON current and $V_{TH}$ (c) SS of proposed CDGT devices.....                                                                                                                                                                                                            | 70 |

| Fig. 5.16: (a) 3-D design view of Circular Nanosheet FET, (b) C-NSFET after removing passivation layer, (c) layout of C-NSFET, (d) 2D cut view of C-NSFET across the AA' cutline with doping profiles.....                                                                                                                                                      | 73 |

| Fig. 5.17: Fabrication process of proposed C-NSFET in 2D view, (a) Thermal oxidation of bulk silicon, (b) lithography & RIE bottom gate cavities, (c) Deposition of bottom metal gate& RIE, (d) Active Silicon island deposition &patterning, (e) Oxidation of the top gate, metal gate deposition and doping (f) Silicidation, deposit metal and RIE etch..... | 74 |

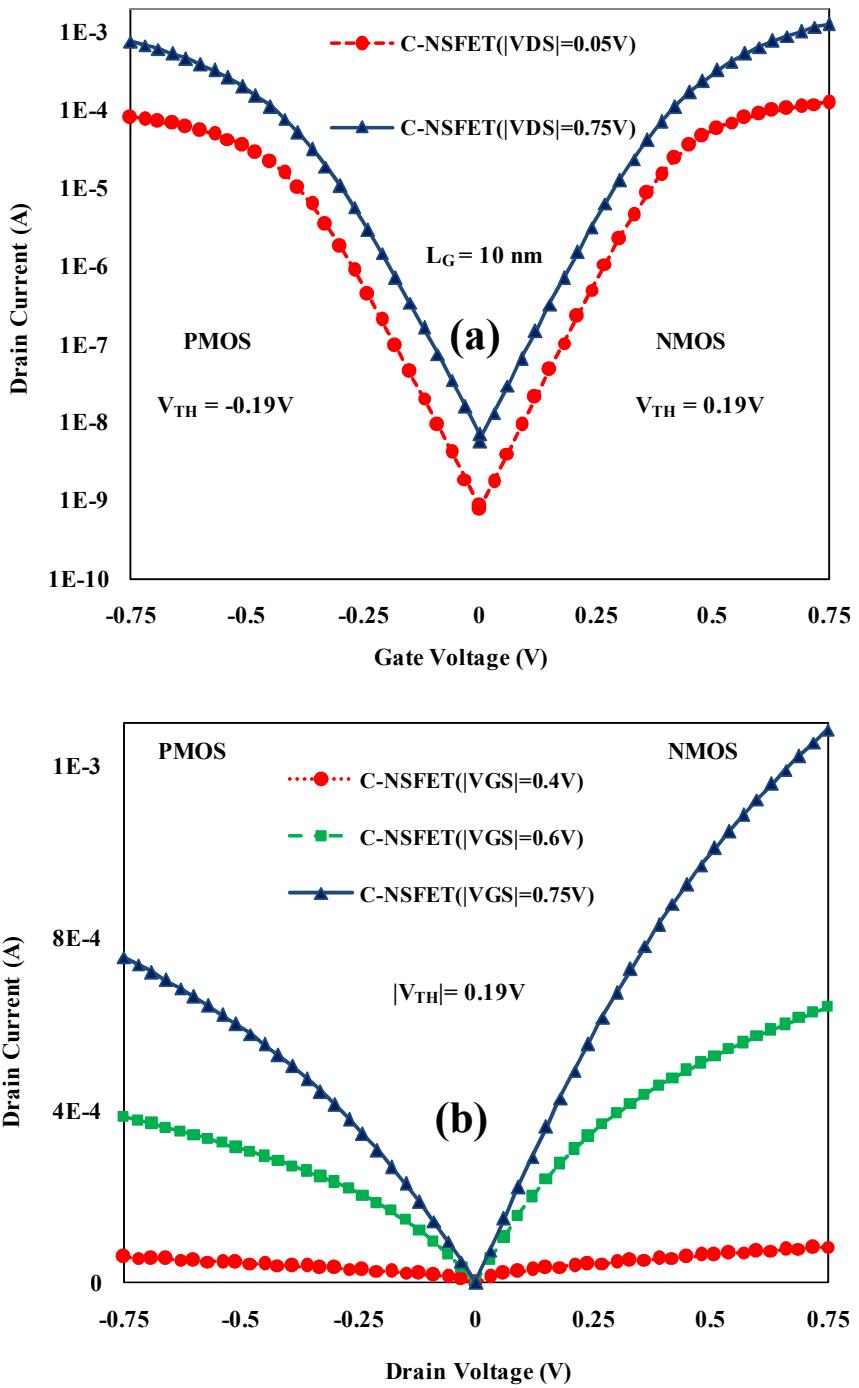

| Fig. 5.18: (a) $I_{DS}$ - $V_{GS}$ of C-NSFETs for both N-type & P-type devices for $L_G=10$ nm, corresponding $V_{TH}$ values given in legend, (b) $I_{DS}$ - $V_{DS}$ of C-NSFETs for both NMOS & PMOS devices.....                                                                                                                                           | 75 |

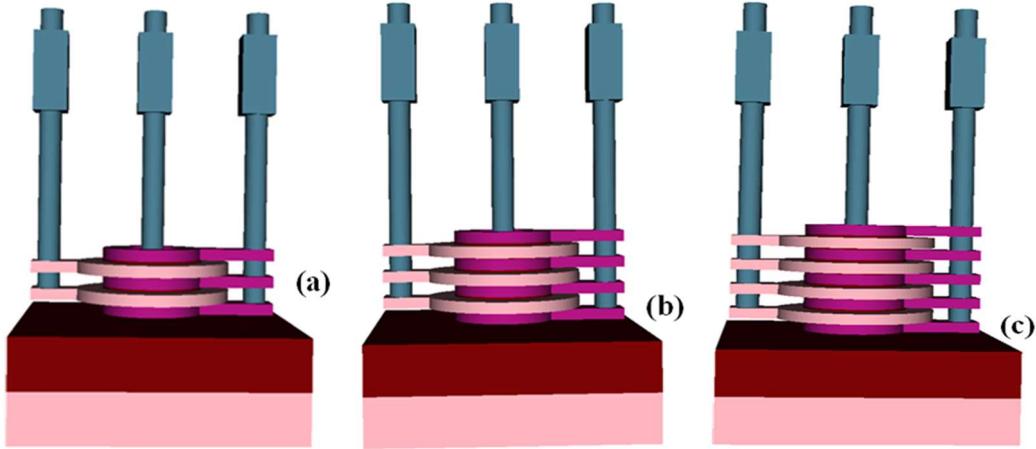

| Fig. 5.19: 3-D schematic view of stacked Circular Nanosheet FET, (a) 2-sheet (b) 3-sheet, (c) 4-sheet C-NSFETs.....                                                                                                                                                                                                                                             | 77 |

| Fig. 5.20: (a) $I_{DS}$ - $V_{GS}$ of stacked C-NSFETs, (b) $I_{DS}$ - $V_{DS}$ of stacked C-NSFETs ON current comparison of different stacked C-NSFETs for both NMOS &PMOS devices .....                                                                                                                                                                       | 78 |

| Fig. 5.21: (a) ON current comparison of different stacked C-NSFETs, (b) OFF current comparison of different stacked C-NSFETs for both NMOS & PMOS devices .....                                                                                                                                                                                                 | 79 |

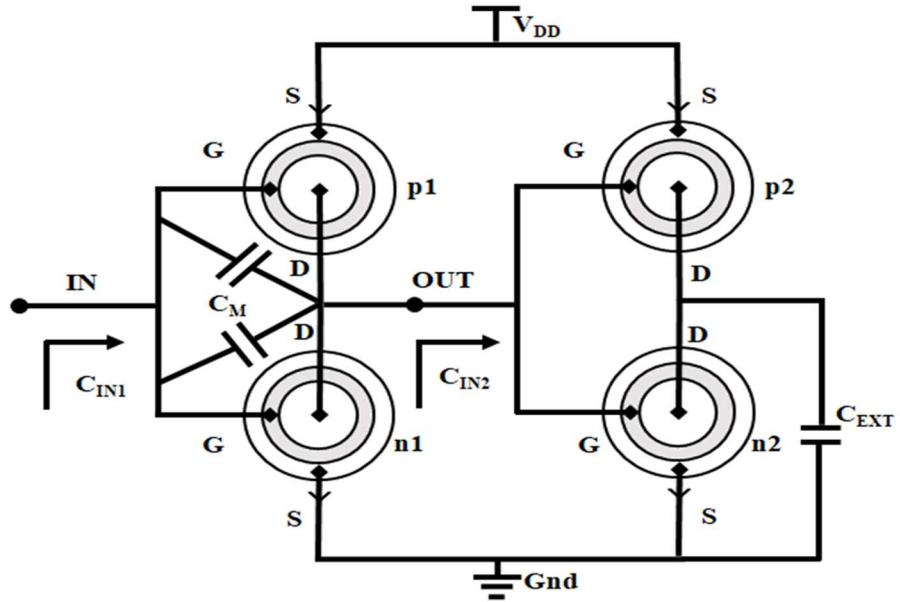

| Fig. 6.1: Schematic view of a two-stage inverter.....                                                                                                                                                                                                                                                                                                           | 83 |

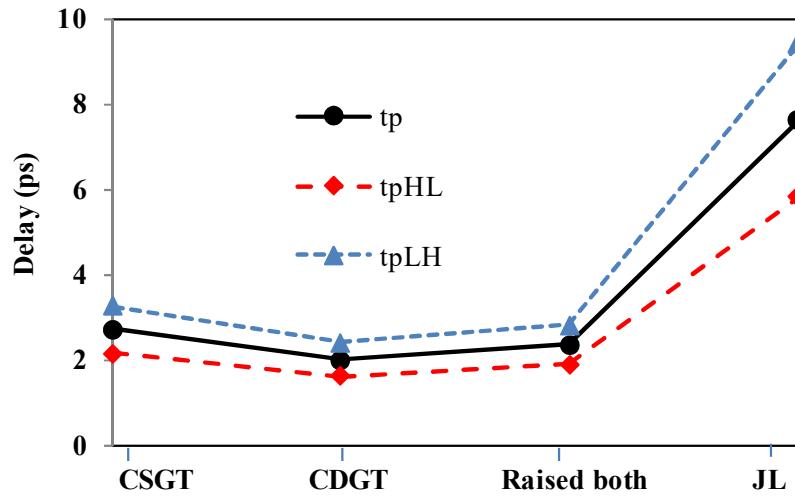

| Fig. 6.2: Delay characteristics of different circular MOSFETs.....                                                                                                                                                                                                                                                                                              | 84 |

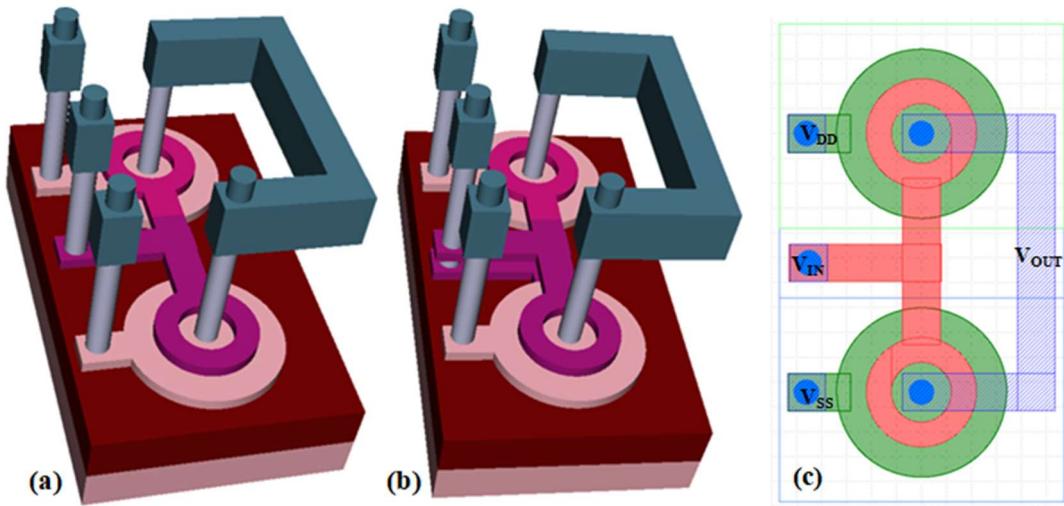

| Fig. 6.3: (a) & (b) CSGT and CDGT inverters respectively, (c) corresponding layout.....                                                                                                                                                                                                                                                                         | 85 |

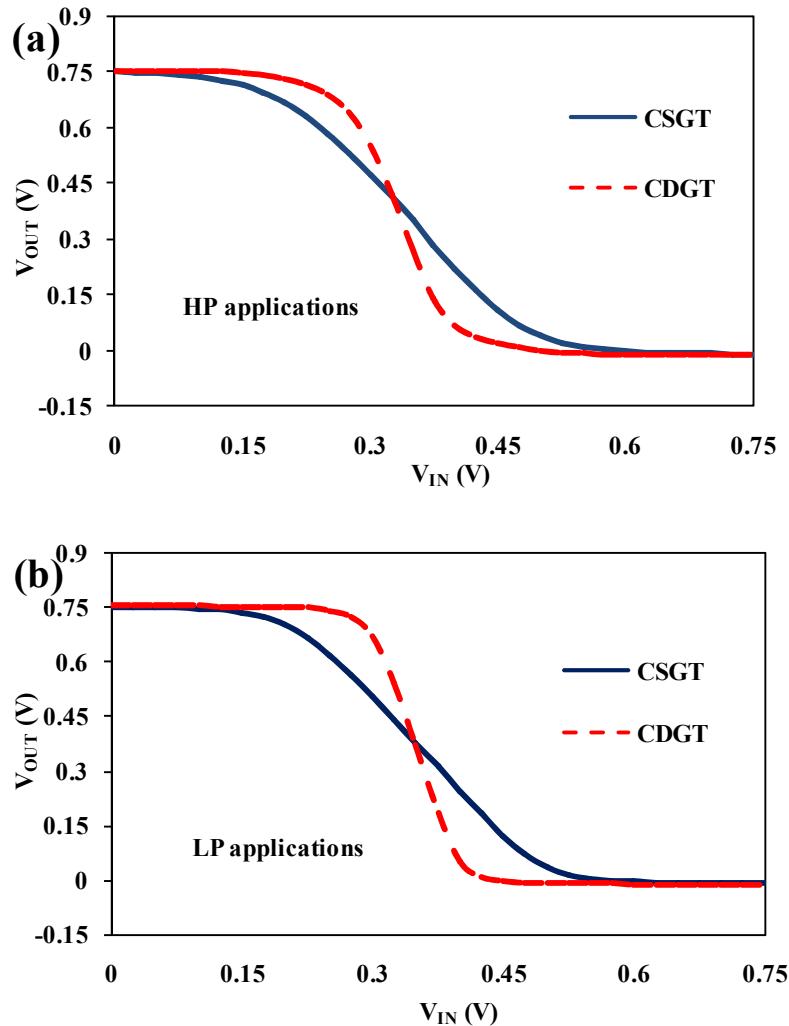

| Fig. 6.4: DC characteristics of CSGT and CDGT CMOS inverters, (a) HP, (b) LP applications.....                                                                                                                                                                                                                                                                  | 86 |

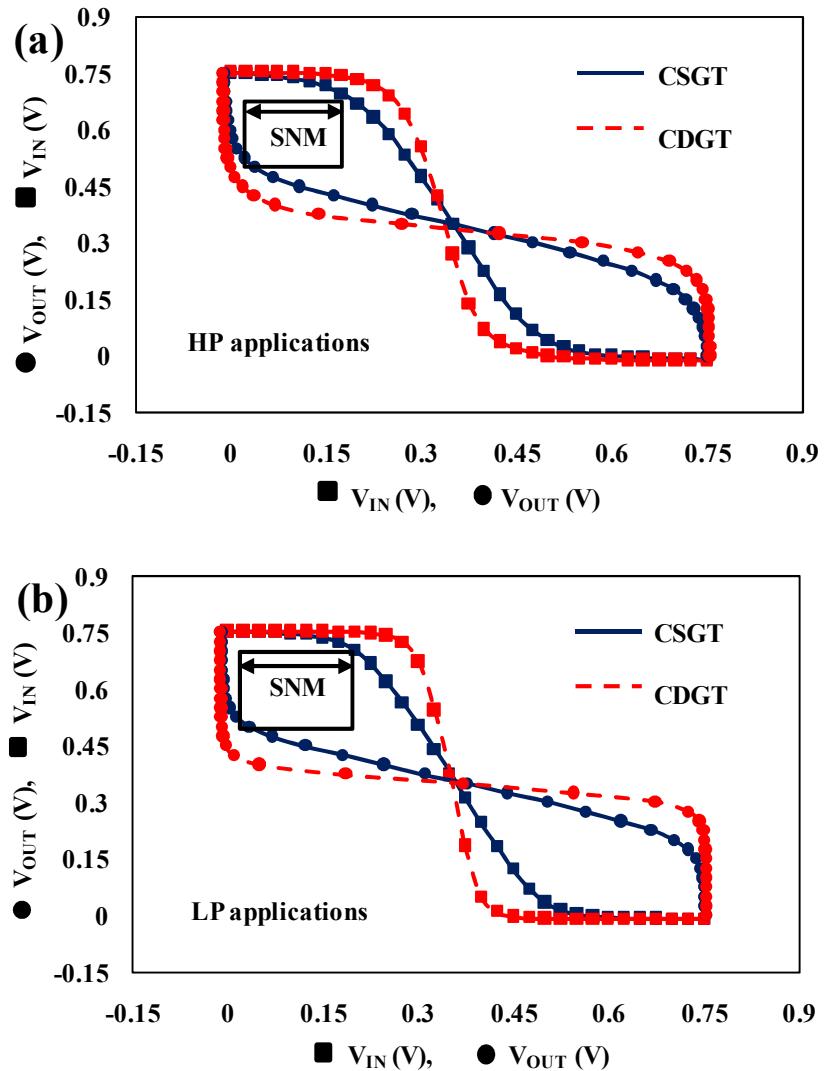

| Fig. 6.5: Butterfly curves and SNMs of CSGT and CDGT CMOS inverters, (a) HP, (b) LP applications .....                                                                                                                                                                                                                                                          | 87 |

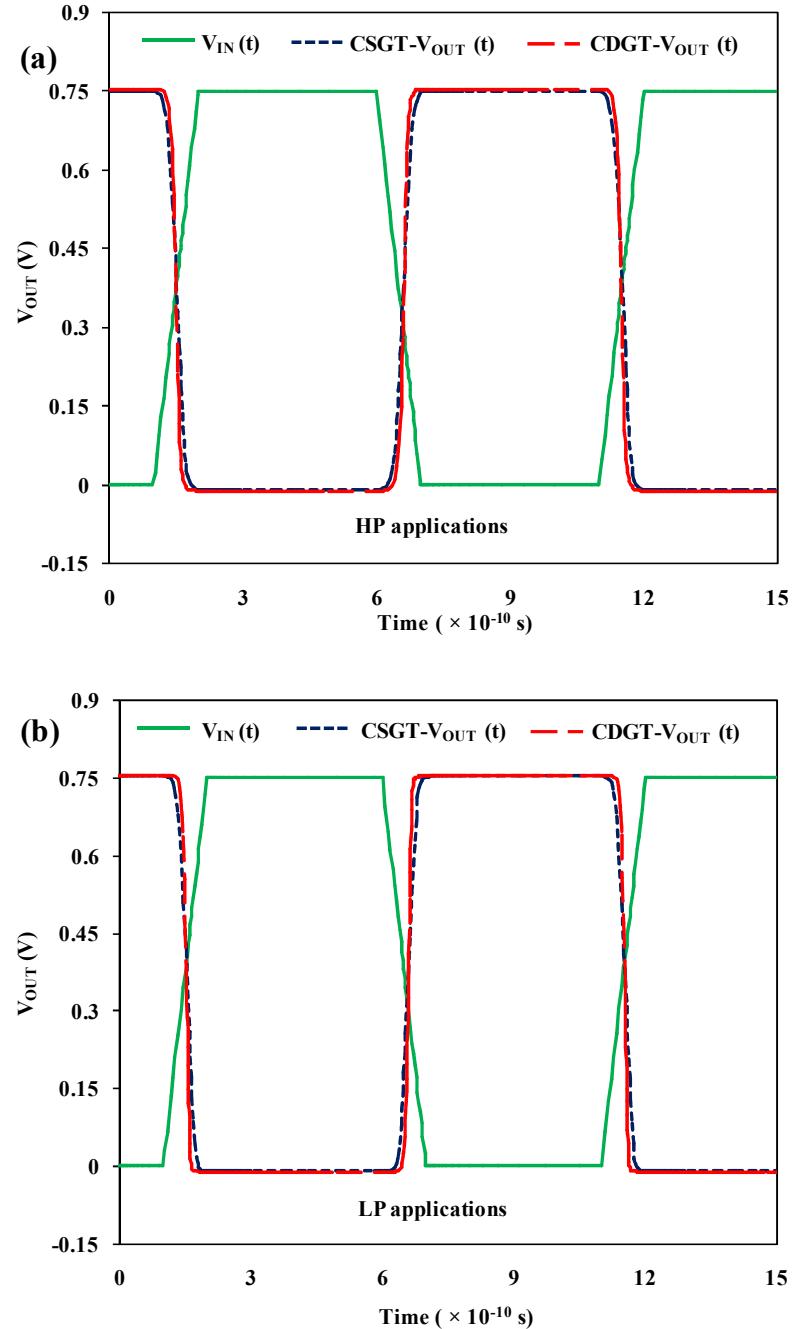

| Fig. 6.6: Transient responses ( $V_{OUT}$ (t)) of CSGT and CDGT CMOS inverters, (a) HP, (b) LP applications .....                                                                                                                                                                                                                                               | 88 |

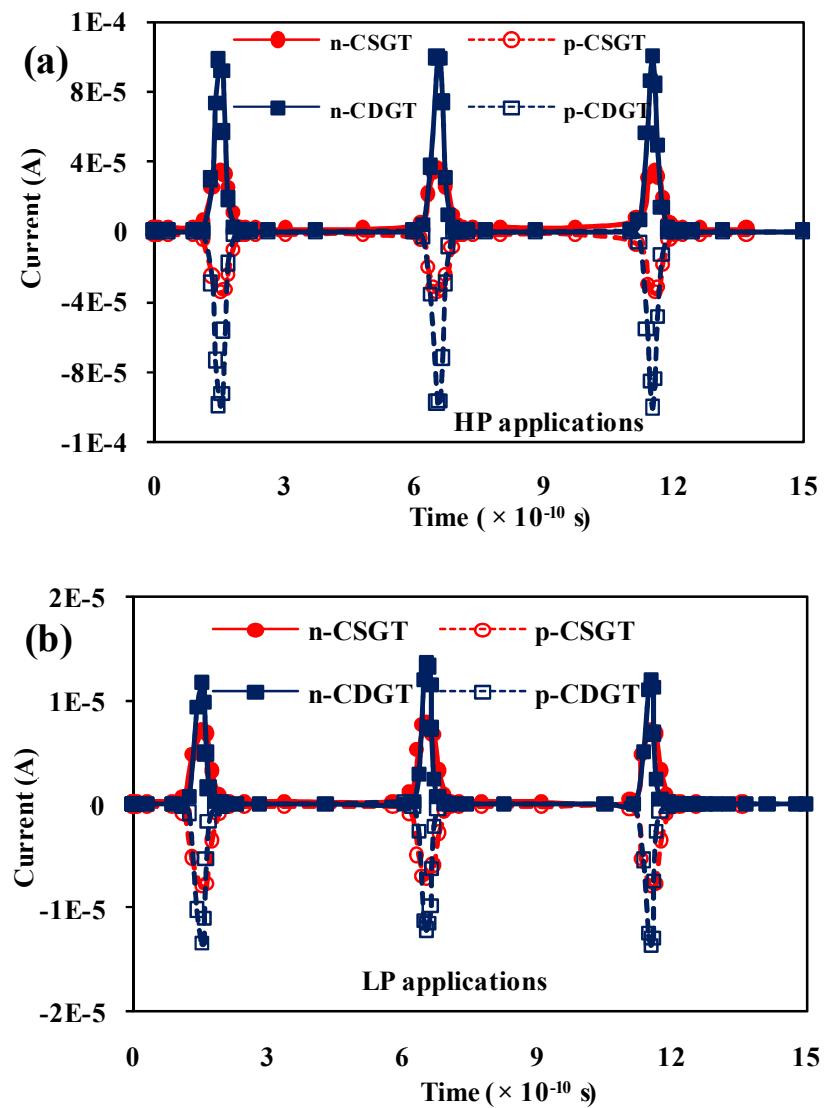

| Fig. 6.7: Transient response of currents ( $I_p$ (t) and $I_n$ (t)) in CSGT and CDGT CMOS inverters, (a) HP, (b) LP applications .....                                                                                                                                                                                                                          | 89 |

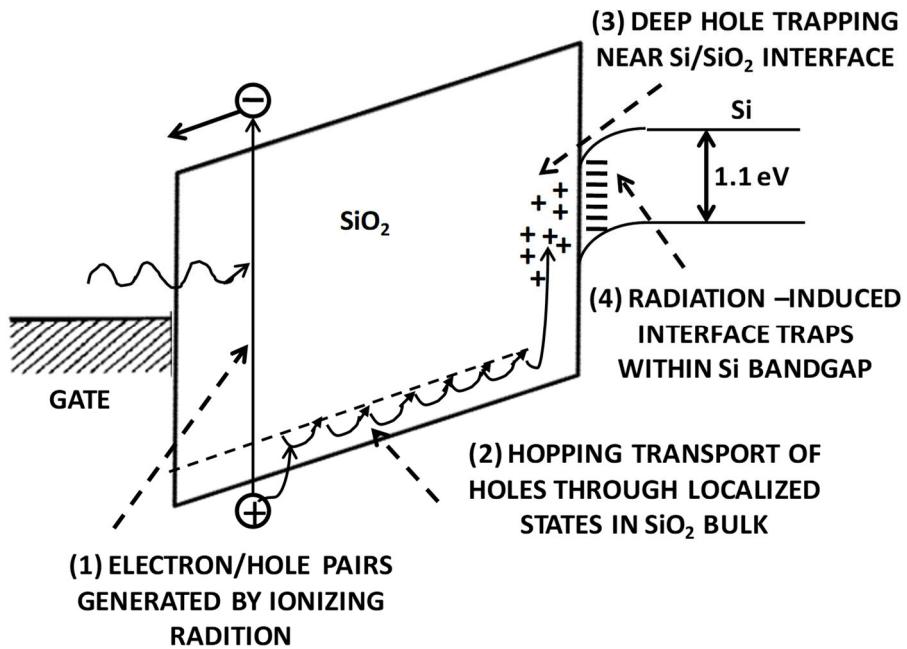

| Fig. 6.8: An illustration of a MOS structure's energy band diagram, highlighting the primary physical mechanisms underpinning the radiation response [106]. .....                                                                                                                                                                                               | 92 |

| Fig. 6.9: Radiation effect classification.....                                                                                                                                                                                                                                                                                                                  | 95 |

| Fig. 6.10: Effect of radiation dose on device characteristics of CSGT and CDGT, (a) HP, (b) LP applications (NMOS devices). .....                                                                                                                                                                                                                               | 97 |

| Fig. 6.11: Charge density distributions under the TID effect with different doses.....                                                                                                                                                                                                                                                                          | 98 |

|                                                                                                                                                                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

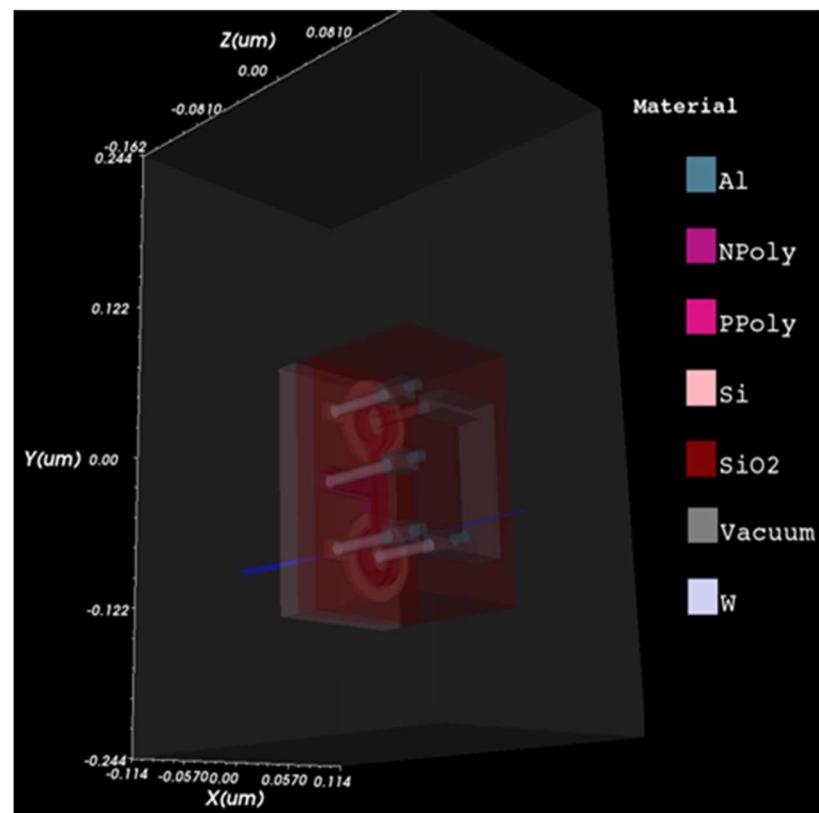

| Fig. 6.12: 3D-view of CDGT CMOS inverter with particle strike on the drain of an NMOS device for SEE simulation a) low-energy particle (top) b) high-energy particle (bottom). .....                                                                                                 | 100 |

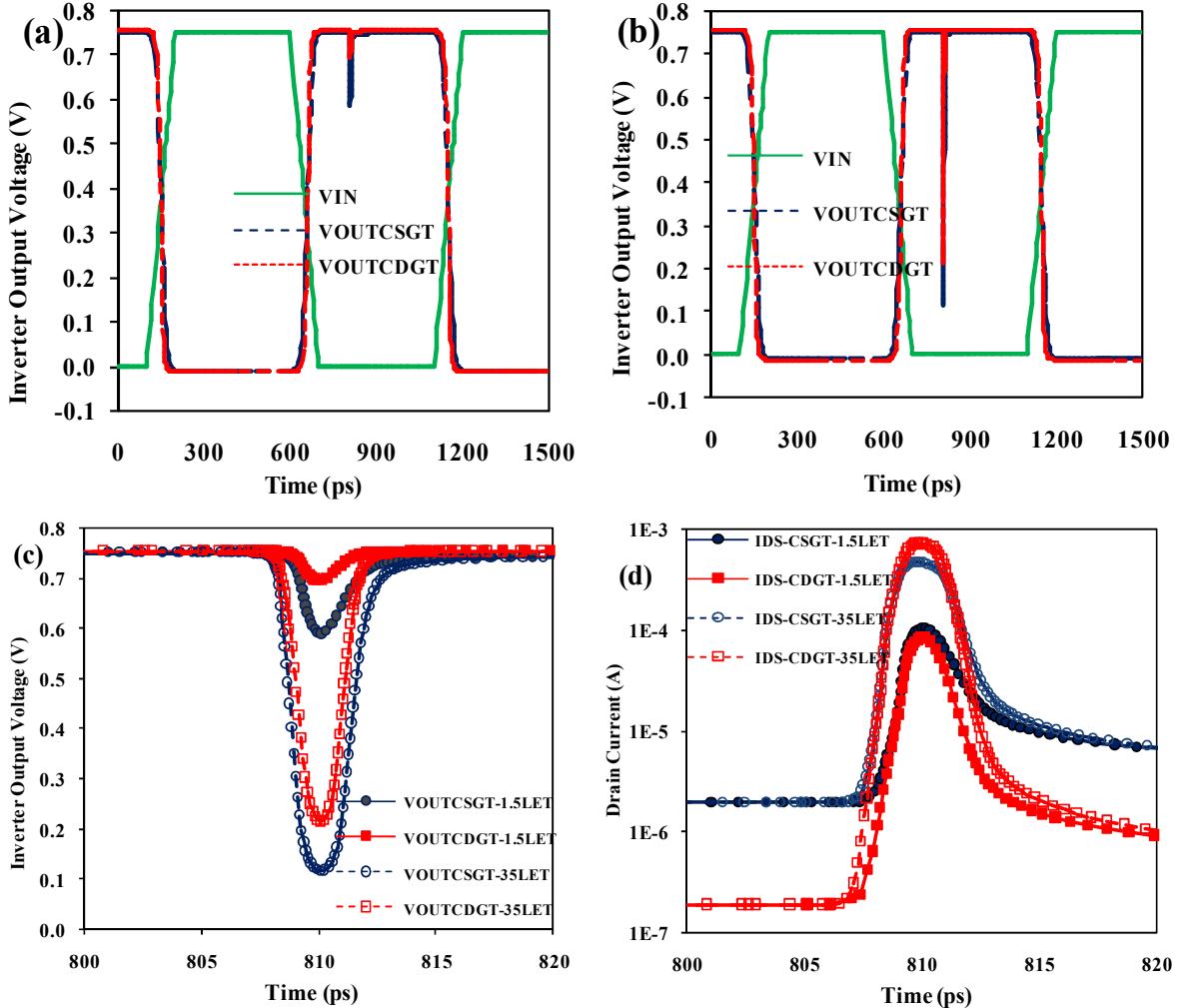

| Fig. 6.13: Transient responses of CSGT and CDGT CMOS inverters with SEEs, a) transient response due to incident of low-energy particle, b) transient response due to incident of high-energy particle, c) SET pulses, d) drain current transients due to both low and high LETs..... | 102 |

# List of Tables

|                                                                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1: Geometrical details of CSGT and CDGT devices used in the simulation. ....                                                                                           | 38 |

| Table 4.2: Performance Comparison of CSGT & CDGT SOI MOSFETs.....                                                                                                              | 39 |

| Table 4.3: Important simulated numerical values for 30 nm gate length CDGT SOI MOSFETs with normal and raised S/D structures (raised top, raised bottom and both raised). .... | 43 |

| Table 4.4: Performance Comparison of Raised both CDGT SOI MOSFET with various Doping Concentrations.....                                                                       | 45 |

| Table 4.5: FoM comparison of both CSGT and CDGT SOI MOSFETs for LP and HP applications..                                                                                       | 49 |

| Table 5.1: Performance analysis of CDGT with R1=10 nm & R1=20 nm. ....                                                                                                         | 53 |

| Table 5.2: Performance analysis of R20nmSiO <sub>2</sub> with different underlap lengths for HP applications. ....                                                             | 54 |

| Table 5.3: Performance analysis of R20nmSiO <sub>2</sub> with different underlap lengths LP applications....                                                                   | 54 |

| Table 5.4: Overall Performance analysis of different CDGT architectures for HP applications. ....                                                                              | 58 |

| Table 5.5: Overall Performance analysis of different CDGT architectures for LP applications.....                                                                               | 58 |

| Table 5.6: A comparison of the proposed CDGT's performance with advanced novel devices. ....                                                                                   | 60 |

| Table 5.7: Performance comparison of CDGT device with existing novel devices at different doping concentrations. ....                                                          | 61 |

| Table 5.8: Electrical characteristics comparison of CDGT with different inner radiiuses at 10 nm node.....                                                                     | 63 |

| Table 5.9: Electrical comparison of CDGT with different inner radiiuses at 7 nm node.....                                                                                      | 65 |

| Table 5.10: Electrical characteristics comparison of CDGT with different inner radiiuses at 5 nm node.....                                                                     | 67 |

| Table 5.11: Performance comparison of proposed CDGT with different gate lengths. ....                                                                                          | 69 |

| Table 5.12: A comparative analysis of proposed CDGT for various thicknesses (T <sub>Si</sub> ). ....                                                                           | 71 |

| Table 5.13: Geometrical details of C-NSFETs devices used in the simulation. ....                                                                                               | 73 |

| Table 5.14: Performance analysis of proposed C-NSFET with existing novel structures. ....                                                                                      | 76 |

| Table 5.15: Geometrical parameters for 10-nm node SC-NSFETs.....                                                                                                               | 77 |

| Table 5.16: Performance analysis of SC-NSFETs. ....                                                                                                                            | 80 |

| Table 6.1: Noise margin of CSGT and CDGT CMOS inverters for HP and LP applications. ....                                                                                       | 87 |

| Table 6.2: Impact of TID effects on device threshold voltage and leakage currents. ....                                                                                        | 99 |

# Nomenclature

|                  |                                                     |

|------------------|-----------------------------------------------------|

| 2D               | Two-Dimensional                                     |

| 3D               | Three-Dimensional                                   |

| BOX              | Buried Oxide                                        |

| CDGT             | Circular Double Gate Transistor                     |

| CE               | Corner Effects                                      |

| CGT              | Circular Gate Transistor                            |

| CMOS             | Complementary Metal Oxide Semiconductor             |

| C-NSFETs         | Circular Nanosheet FETs                             |

| CSGT             | Circular Single Gate Transistor                     |

| DIBL             | Drain Induced Barrier Lowering                      |

| DG               | Double Gate                                         |

| EOT              | Equivalent Oxide Thickness                          |

| FoM              | Figures of Merit                                    |

| GAA              | Gate-All-Around                                     |

| GDSII            | Geometric Data Stream for Information Interchange   |

| GDML             | Geometry Description Markup Language                |

| $g_d$            | Output Conductance                                  |

| $g_m$            | Transconductance                                    |

| GSeat            | Genius Single Event Analysis Tool                   |

| GUI              | Graphical User Interface                            |

| HCEs             | Hot Carrier Effects                                 |

| HfO <sub>2</sub> | Hafnium Oxide                                       |

| HP               | High-Performance                                    |

| IC               | Integrated Circuit                                  |

| IGFET            | Insulated-Gate Field-Effect Transistor              |

| $I_{OFF}$        | OFF/Leakage Current                                 |

| $I_{ON}$         | ON/Drive Current                                    |

| IRDS             | International Roadmap for Devices and Systems       |

| ITRS             | International Technology Roadmap for Semiconductors |

| JL               | Junctionless                                        |

| L or $L_G$       | Channel/Gate Length                                 |

| LET              | Linear Energy Transfer                              |

| LP               | Low power                                           |

| MOSFETs          | Metal Oxide Semiconductor Field Effect Transistors  |

|                  |                                                |

|------------------|------------------------------------------------|

| MuGFET           | Multiple-Gate Field-Effect Transistors         |

| NM <sub>H</sub>  | Noise Margin High                              |

| NM <sub>L</sub>  | Noise Margin Low                               |

| NSFETs           | Nanosheet Field-Effect Transistors             |

| NTRS             | National Technology Roadmap for Semiconductors |

| NW               | Nanowire                                       |

| PEF              | Perpendicular Electric Field                   |

| RGTs             | Rectangular-Gate Transistors                   |

| RIE              | Reactive Ion Etching                           |

| SCEs             | Short Channel Effects                          |

| SC-NSFETs        | Stacked Circular NSFETs                        |

| SEEs             | Single Event Effects                           |

| SET              | Single Event Transient                         |

| SNM              | Static Noise Margin                            |

| SOI              | Silicon-On-Insulator                           |

| SS               | Subthreshold Slope                             |

| TCAD             | Technology Computer Aided Design               |

| T <sub>d</sub>   | Propagation Delay/ Delay Time                  |

| TGF              | Transconductance Generation Factor             |

| T <sub>f</sub>   | Falling Edge Time Constant                     |

| TID              | Total Ionizing Dose                            |

| T <sub>ox</sub>  | Gate Oxide                                     |

| T <sub>r</sub>   | The Rising Edge Time Constant                  |

| V <sub>EA</sub>  | Early Voltage                                  |

| VeSFET           | Vertical Slit Field Effect Transistors         |

| VeSTICs          | Vertical Slit Transistor-based ICs             |

| VLSI             | Very Large-Scale Integration                   |

| V <sub>TH</sub>  | Threshold Voltage                              |

| W <sub>EFF</sub> | Effective Width                                |

# Chapter-1

## 1. Introduction

### 1.1. History

The Semiconductor industry has expanded significantly in recent decades, owing to the micro/nano electronics revolution. Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) have been a major element in the semiconductor industry due to their higher package density, low power dissipation, and superior performance for industrial and commercial applications. Complex circuits that have billions of transistors functioning as switches are now integrated on a single chip. This progress in the semiconductor industry has led to the invention of novel electronic circuits and advanced processors for a variety of applications [1].

The concept of semiconductor devices being embedded in a thin silicon film that is supported mechanically by an insulating substrate has been around for decades. Historically, the first transistor was found in the patent of Lilienfeld dating 1926 and named it as Insulated-Gate Field-Effect Transistor (IGFET). The active section of this device is made of a thin semiconductor film placed on top of an insulator. Thus, the silicon-on-insulator (SOI) device can be said to as the first MOSFET. Unfortunately, the technology at that time was incapable of creating the device. Lilienfeld IGFET technology was forgotten and totally ignored & overshadowed for a period by the introduction of the bipolar transistor in 1947 and its major success. A few years later, advancements in technology led to the production of high-quality Gate Oxides (Tox). In 1960, Kahng and Atalla created the first operational MOSFET based on Lilienfield's IGFET. MOSFET technology became more essential as monolithic integrated circuits improved, and Complementary Metal Oxide Semiconductor (CMOS) technology is still the leading technology in the nanotechnology industry.

Over the last 60 years, specialists have put a lot of attention into research and development since the introduction of the first electronic integrated circuit (IC) built by Jack St. Claire Kilby at Texas Instruments in 1958. For his efforts, he received the Nobel Prize in

Physics in the year 2000. Following the development of the first planar IC, the Gordon Moore proposed the Moore's law in 1965, which is still in use today. Moore revised his prediction in 1975, that the numbers of transistors should double every two years. Moore's law projected that the number of transistors per integrated circuit will increase exponentially with CMOS technology, resulting in increased density, speed, and power improvement [2] [3].

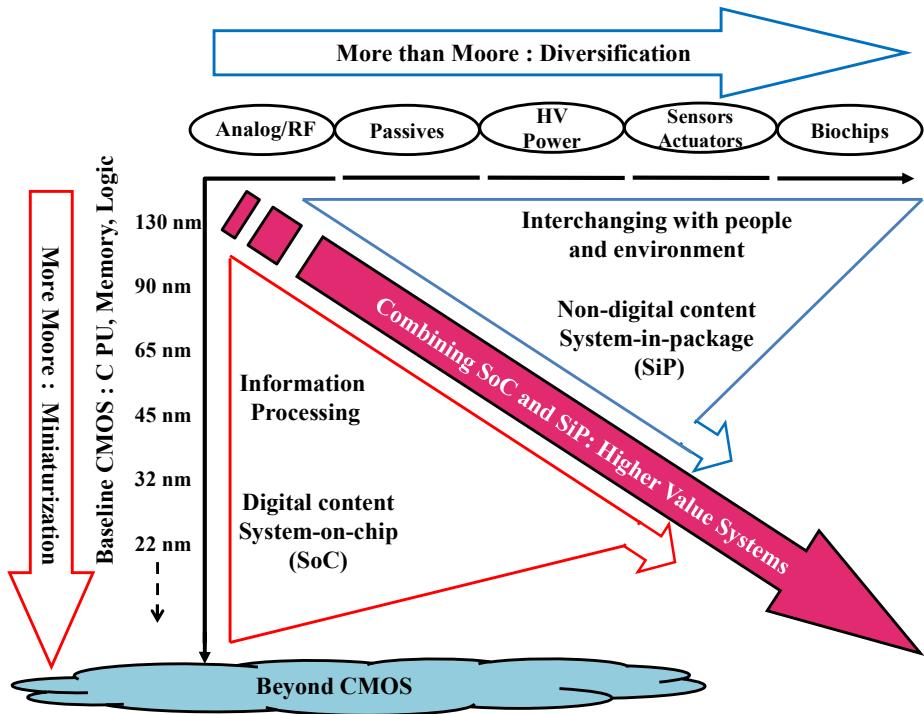

Fig. 1.1: Moore's Law and More [4].

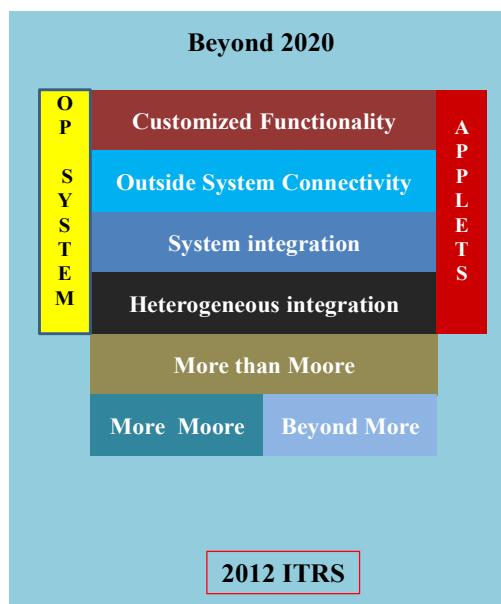

Fig. 1.2: The New Ecosystem of the Electronics Industry [5].

The Semiconductor Industry Association issued the "National Technology Roadmap for Semiconductors (NTRS)" in 1992, which presented a 15-year forecast on important semiconductor industry trends. The roadmap was a useful reference guide for semiconductor production companies, with expectations on materials and software projections, and provides clear goals for researchers in the coming years. The NTRS was upgraded in 1994 and 1997 with alternative solutions and possible requirements. To take advantage of contributions from across the world, the NTRS was modified in 1998 to "International Technology Roadmap for Semiconductors (ITRS)". Since 1998, ITRS has published or revised roadmaps annually till 2015.

As illustrated in Fig. 1.1, the ITRS issued the first white paper in 2005, in which the keywords "More than Moore" and "More Moore" [4] were introduced for the first time. This announcement promised the invention of the iPhone and iPad in later years. Therefore, the ITRS agreed to restructure in December 2012, during its annual meeting in Taiwan, to address the rebuilt ecosystem of the microelectronics sector. In May 2016, the transition and growth of the roadmap from the ITRS to the International Roadmap for Devices and Systems (IRDS) resulted in significant attention to systems [5]. As shown in the Fig. 1.2, priority has been given to architectures and applications that vary from the conventional model of device → circuit → logic gate → functional block → system. All of these efforts have resulted in the evolution of MOSFET dimensions from millimeter to nanometer scale, i.e., a change of six orders of magnitude in roughly 60 years, or almost one order of magnitude of MOSFET dimension decrease every decade.

## 1.2. Developments of MOS Technologies

In general, the primary goals of research & development were to shrink the dimensions and improve the electrical performance of MOSFETs and hence improve their ICs performance [6]. The scaling down of the size of transistors has followed Moore's law, and due to shrinking of the device, the electronic industry has benefited significantly over the last 4 to 5 decades in terms of increasing data throughput per chip. Long channel MOSFETs virtually has ideal characteristics, but as device geometries shrink, they deviate significantly from ideal characteristics. When the device's channel length is limited to depletion widths of source and drains junctions, several Short Channel Effects (SCEs) [7], including Drain Induced Barrier Lowering (DIBL), Threshold voltage ( $V_{TH}$ ) roll-off, mobility reduction, and bulk punch

through, degrade the device performance [8]. To overcome the SCEs while maintaining device length as short as possible, for many years, research & development in micro/nano electronics has been divided into three broad groups.

- i) New manufacturing techniques to implement MOSFETs (nanoimprint photolithography [9], plasma deposition [10], lightly doped drain [11], elevated or raised source/drain [12] etc.),

- ii) New materials (High-k material [13], metal gate [14], Germanium [15], SOI [16], Silicon-on-Sapphire [17], Silicon-Germanium [18], Ferroelectric materials [19], etc.), and

- iii) Advanced innovative architectures (Double gate (DG) MOSFET [20], Ultra-thin body [21], FinFET [22], Multiple-Gate Field-Effect Transistors (MuGFET) [23], Gate-All-Around (GAA) or Nanowire (NW) [24][25], Junctionless (JL) [26], Tunnel FET [27], and Nanosheet [28], VeSFET [29] [30] etc.).

The developments in the manufacturing process and the use of new materials gave the freedom to the researchers to scale down the transistors up to the 100 nm technology node while keeping SCEs under control. Traditional planar MOSFETs, on the other hand, suffer greatly from SCEs at technology nodes less than 50 nm and beyond [31]. Thus, to overcome SCEs, advanced novel structures are being used with multiple gates.

To expand CMOS technology beyond sub 45 nm, SOI MOSFETs are a potential candidate to replace traditional planar MOSFETs [32]. However, SOI MOSFETs are not immune to SCEs when further scaled down to sub 30 nm technology nodes [33]. Due to their enhanced performance and superior electrostatic gate control over the conduction channel, DG MOSFETs [34] are an alternative design for replacing planar MOSFETs in sub 20 nm technology nodes. Because of misalignment and the complex manufacturing process, a new structure known as FinFET has emerged as a suitable device in High-Performance (HP) applications. FinFETs, on the other hand, have several difficulties in designing, functionality, layout, and cost for subsequent scaling [35] [36]. However, in order to maintain SCE control, the fin thickness and gate length must be scaled, which can lead to  $V_{TH}$  variation [37]. Because of their enhanced short-channel control and high current density, GAA/NW MOSFETs are expected to provide even further device scalability [38]. Meanwhile, as compared to the standard GAA structure, Nanosheet field-effect transistors (NSFETs) display improved performance, higher drive currents, and better process efficiency due to the stacking process. As a result, the NSFET is gaining popularity as the most promising candidate for

future devices [39]. The Vertical Slit Field Effect Transistors (VeSFET) is another intriguing novel device that has been suggested in the literature to replace the conventional MOSFET [40]. It is an unconventional device with a non-standard layout that offers low power (LP) consumption and high package density for analog and digital applications [41].

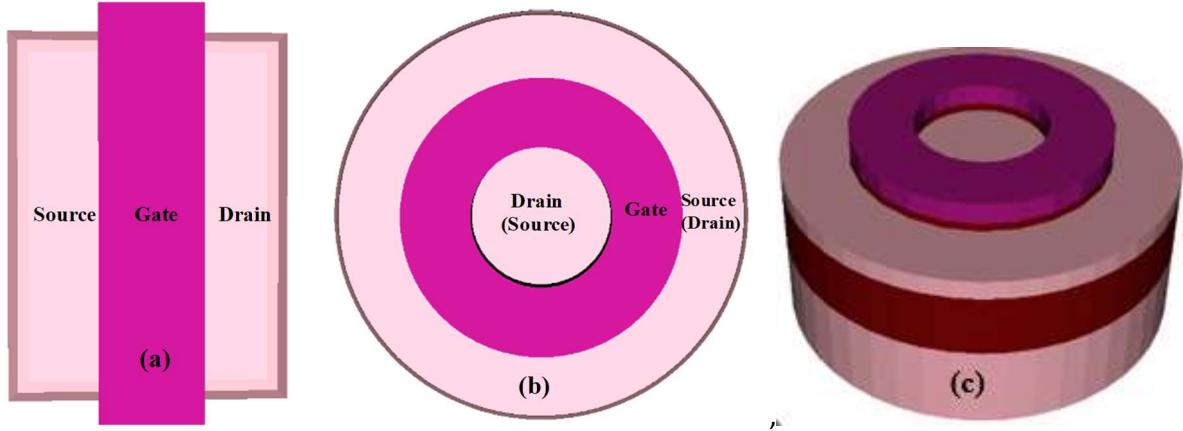

Fig. 1.3: (a) Rectangular MOSFET layout (b) Circular MOSFET layout, (c) Structure of Circular MOSFET.

Apart from these various non-planar devices (novel advanced innovative architectures), reduction in leakage currents & SCEs can also be achieved from non-standard enclosed geometries (circular, hexagonal, octagonal, and ellipsoidal, etc.) [42]. These are developed based on the layout of the device. These non-standard layout devices can improve electrical performance, reducing the longitudinal corner effects, and boosting tolerance towards ionizing radiation. The circular/ring/annular gate MOSFET is one of the most popular non-standard layouts. Fig. 1.3 depicts traditional rectangular MOSFET and circular edgeless MOSFET. It has a circular gate layout, which provides higher immunity to SCEs than traditional planar MOSFETs, owing to the absence of side interface areas, which cause trap-induced leakages. Three Dimensional (3D) view of the Circular gate MOSFET is shown in Fig. 1(c). The structural difference between circular gate MOSFET with other existing technologies is discussed in Chapter 2.

This thesis investigates the enclosed circular layout transistor based on both structural and material variations. Further, it analyzes the behaviour of circuit level performance and also radiation effects.

### 1.3. Motivation

Naturally, the developments of advanced CMOS (novel advanced innovative architectures) have led to a desire to utilize the technology in a range of applications, including military, aerospace, and terrestrial [43]. One of the most typical issues that ICs encounter in the space environment is the TID effect, which is the accumulation of the ionizing dose over time. The influence of total ionizing dose (TID) on device performance is a major problem for space-based applications, as it can affect crucial device operating parameters such as shift in  $V_{TH}$ , off-state leakage, mobility, subthreshold slope (SS), and transconductance ( $g_m$ ) [44]. One more major issue is corner effects (CE), which is prominent in MuGFETs with three or more gates. The gate voltage in MuGFETs causes the CE to increase the resultant electric field in the areas close to the vertices of the junctions of two different gate regions. This effect lowers the  $V_{TH}$  of multigate FETs in these gate regions and consequently, it reduces the electrostatic controllability of the gate of the transistor (undesired effect). Because of these reliability issues like TID and CE effects in non-planar multigate devices, we need to innovate new fabrication processes, techniques, devices, and materials that can mitigate the degradation of ionizing radiation (protons, heavy ions, and electromagnetic waves) in semiconductor device parameters and avoid potential electrical failures [45]. These effects can be eliminated/minimized using enclosed layout transistors. One such layout is the non-standard enclosed circular geometry (circular gate transistor (CGT)), which has the added advantage of an increase in the effective width of a transistor for a given silicon area [46]. CGTs are capable of improving the Longitudinal electric field along a channel that reduces the CE and enhances radiation hardening [47]. Therefore, with these advantages, the circular layout has been used with the multiple gates concept to create ICs at lower technology nodes and investigate their radiation hardness analysis.

### 1.4. Problem Statement

The primary goal of this thesis is to perform a detailed simulation-based analysis of circular double gate transistors (CDGT) SOI MOSFETs for LP and HP applications to mitigate the SCEs, as well as their radiation-hardness analysis. Also, the impact of various device-level variations such as raised topologies, Junctionless mode, and high-k materials on CDTG device behavior. Further the design of stacked nanosheet MOSFETs in a circular geometry for building high-current-rate integrated circuits.

## 1.5. Research Objectives

To mitigate the SCEs along with CE and TID effects and implement radiation tolerance circuits for space and military applications, we have considered several objectives, which are mentioned below during the period of research.

1. Implementation of CSGT and CDGT SOI MOSFET devices and analyze the DC performance with several device level variations such as raised source/drain topologies, Junctionless mode analysis at 30 nm technology node.

2. Implementation of CDGT SOI MOSFET with under lap and high-k dielectric material concepts and analyze the Analog/RF performance.

3. Benchmarking, optimization, and scaling of CDGT SOI MOSFET at sub 10 nm technology nodes.

4. Design and analysis of circular nanosheet MOSFETs and stacking of circular nanosheet MOSFETs.

5. Design and analysis of inverter to analyze the circuit level performance of circular MOSFETs.

6. Analysis of radiation effects (TID effects on device performance and SEEs on circuit performance) of different circular MOSFETs.

## 1.6. Thesis Organization

The thesis presents circular single and double gate MOSFETs device design and radiation hardened analysis for use in aerospace and military applications. The thesis is organized into seven chapters. The following section gives the summary of the chapters.

**Chapter 1** presents an introduction to the work, motivation, reasons for choosing the problem and contributions of the thesis.

**Chapter 2** This chapter deals with a detailed literature review of circular layout transistors with a notable amount of most recent literature. It covers the history of circular layout transistors, as well as their evolution in the semiconductor industry. It also discusses several viable solutions for SCEs. Finally, this chapter concludes with a discussion of research gaps in the available literature.

**Chapter 3** In this chapter, A well-calibrated TCAD setup with various simulated physical models is established to implement the circular layout transistors are discussed. To validate

the models used for the device simulation studies at different technology nodes, device structures identical to the reported experimental devices [48] & [49] were created, and matching their V-I characteristics. Further, detailed information about relevant physics models is provided for carrier generation, carrier recombination, band-to-band tunneling, and velocity saturation along with density gradient for quantum corrections. This chapter also contains details of simulation setup requirements for TID effects on device performance as well as SEE (Single event effects) on circuit transient simulations.

**Chapter 4** This chapter describes the detailed implementation of SOI circular layout transistors such as circular single gate transistors (CSGT) and CDGT MOSFETs at 30 nm technology node. Analyzes the performance of these devices in terms of the device-level figures of merit (FoM) such as device ON current ( $I_{ON}$ ), leakage current ( $I_{OFF}$ ),  $I_{ON}/I_{OFF}$  current ratio, SS, and DIBL. It also contains device level variations like raised source/drain topologies and JL behavior on CDGT devices. This study provides the need of use of multiple gates concept in circular geometry (CDGT devices) to improve the device electrical performance. Finally, this chapter ends with the performance analysis of CSGT and CDGT devices at 10 nm technology node.

**Chapter 5** This chapter mainly discusses the CDGT device at the 10 nm node with the impact of its device-level & material variations such as underlap concept, and high-k dielectric materials on device performance. Furthermore, the CDGT device is benchmarked against advanced novel structures and CDGT's device optimization and scaling are discussed. Finally, this chapter concludes with a discussion of the novel implementation of a stacked nanosheet MOSFET in circular geometry. This study of stacked circular nanosheet MOSFET gives the guidelines for building high-current-rate integrated circuits, such as current drivers and power stages.

**Chapter 6** This chapter discusses a detailed circuit analysis of various circular layout transistors by analyzing the CMOS inverter. Further, the radiation effects such as TID effects on device performance of both CSGT and CDGT devices, as well as SEEs on their circuit performance are analyzed. Because of its high radiation tolerance, this study can provide guidelines to researchers to use circular layout transistors in radiation environments such as military and aerospace applications.

**Chapter 7** This chapter summarizes the overall work done in this thesis and proposes some potential future work trends to take this research to the next level.

# Chapter-2

## 2. Literature Survey

CMOS devices have been progressively scaled down, together with breakthroughs in CMOS processing technology, resulting in advancements in Very Large Scale Integration (VLSI) design methodologies. By using advanced CMOS VLSI technology and high density novel architectures, high performance computer system chips are integrated with proper functionality at a low cost. Due to the downsizing of CMOS devices, the related power consumption has been reduced. However, the issues associated with MOSFET scaling, such as SCEs, are becoming more prevalent. As discussed in Chapter 1, several solutions were deployed to address the SCEs due to scaling.

### 2.1. Review on Possible Solutions

SOI MOSFETs are one of the first alternative solutions to replace conventional rectangular MOSFETs to further expand CMOS technology by controlling SCEs. SOI technology has major advantages over planar MOS technology [50][32]. These benefits include low leakage current, faster switching speed, reduced subthreshold swing, better isolation, decreased latch-up, and improved short channel immunity [51]. However, SOI MOSFETs are not immune to short channel effects when further scaled down [33]. Several issues need to be solved to produce high performance SOI devices. Oxide leakage and high series resistance are two of the most significant problems [52].

The SOI MOSFET performance is limited due to the source and drain contact resistances in the sub 32 nm regime. This is because while contact resistance increases with the scaling of the contact area, the on-state resistance of a MOSFET decreases with the scaling of the transistor. One common method for reducing the series resistance component is by raised S/D engineering [53]. Raised S/D structures have shown promise in mitigating the parasitic resistances associated with the source and drain, improving ON current, reducing the lateral electric field, controlling hot carrier effects, and improving device performance [12].

Modifying the doping concentration and obtaining high quality junctions is difficult in thin SOI layers when the device is scaled down to sub 30 nm nodes [54]. Hence, the JL

concept, which is a better doping choice for short channel devices. The JL concept has gained much attention in recent years, using high and uniform doping in the channel and S/D regions. This has several benefits over traditional planar MOSFETs, such as enhanced performance against SCEs, high scalability, a low thermal budget, and a simplified fabrication process [55] [56]. Such gains are only achieved because of the high current drive with no barrier in JL devices.

One of the methods to reduce SCEs and leakage currents is the use of gate source/drain underlap concept. Because of the underlap concept, the series resistance will increase, resulting in a reduction in total device current (both  $I_{ON}$  &  $I_{OFF}$ ). It offers an optimum  $I_{ON}/I_{OFF}$  ratio [57][58]. It offers desirable characteristics like greater break-down voltage, decreased electric field at the drain and source regions, smaller gate leakage current, and so on, making it better suited for limiting the influence of drain potential on source barrier (DIBL effect) and reducing hot carrier effect.

The biggest advancement in transistor technology since the invention of polysilicon-gate MOS transistors has been the using of high-k and metal materials. The various High-k gate dielectric materials such as ( $Al_2O_3$ ,  $La_2O_3$ ,  $HfO_2$ , etc.) have attracted the interest of many researchers over the last two decades due to their significant potential for maintaining further downscaling in Equivalent Oxide Thickness (EOT) with a physically thicker film and a lower gate leakage current [13]. All these approaches are related to the process variations (raised source/drain, Underlap, JL), and new materials (SOI, high – k). Along with these solutions, to reduce SCEs, advanced novel devices are proposed with multiple gates.

### **2.1.1. Review on Advanced Structures**

In recent years, the microelectronics sector has made huge investments in revolutionary technologies aimed at the production of devices with exceedingly small dimensions [59]. The lack of gate control over the channel in very short channel devices (owing to the closeness of the source and drain regions) makes the usage of traditional MOSFETs in ultra-scaled transistors difficult. As a result, alternative technologies like multigate architectures are explored and reported in the literature [60].

The continuous scaling of planar MOSFETs to sub 30 nm ranges drastically degrades device performance, resulting in increased leakage currents & off-state power, both of which

are critical design criteria for next-generation CMOS [61]. The mitigation of off-state leakage current and SCEs in the conventional planar transistor becomes complicated technological challenge as the MOSFET channel length is shortened. The SCEs including SS deterioration,  $V_{TH}$  roll-off, and high DIBL restricts the device performance for smaller channel lengths. Various advanced MOSFET designs [62][63][64][65] and better quality channel materials are now in demand [18] [22] to overcome the scaling limits. In recent years, modern architectures such as multigate devices like DG [20], FinFET [66], GAA FETs [67] [68], and NSFETs [69][70] have gained popularity, which lowers drain-to-source leakage currents [71] and improves device performance with some fabrication complexity.

DG MOSFETs is an alternate structure for replacing planar MOSFETs in sub 30 nm technology nodes, due to their high performance and enhanced electrostatic gate control over the conduction channel as shown in Fig. 2.1. It also exhibits reduced SCEs and provides an improved drive current because, in DG MOSFETs, two gates control the channel [72].

Fig. 2.1: Structure of Double gate MOSFET [72].

FinFETs have effectively enabled continuous technological scaling from conventional devices by increasing additional gate controllability over the channel at lower technology nodes, leading to an enhanced performance at lower supply voltages [66]. Due to complex fabrication and alignment in DG MOSFETs, this new structure such as FinFET is developed to lower SCEs with better gate controllability on three sides by three gates as shown in Fig. 2.2. FinFET technology has many advantages over bulk CMOS, including high drive current for a given similar footprint, resulting in high speed, low leakage, low power consumption, no random dopant fluctuations, resulting in better mobility and transistor scaling beyond 20 nm.