# **Design and Analysis of Dual Material Gate Junctionless FinFET for Analog IC Applications**

*Submitted in partial fulfilment of the requirements*

*for the award of the degree of*

**Doctor of Philosophy**

by

**Rambabu Kusuma**

(Roll No: 718044)

Under the supervision of

**Prof. TVK Hanumantha Rao**

**Department of Electronics & Communication Engineering**

**National Institute of Technology Warangal**

**Telangana, India - 506004**

**2023**

## APPROVAL SHEET

This Dissertation Work entitled "**Design and Analysis of Dual Material Gate Junctionless FinFET for Analog IC Applications**" by **Rambabu Kusuma, Roll No. 718044** is approved for the degree of Doctor of Philosophy.

Examiners

---

**Dr. Asutosh Kar**

Associate Professor, Department of Electronics & Communication Engineering,

NIT, Jalandhar

Supervisor

---

**Prof. T.V.K. Hanumantha Rao**

Professor, Electronics and Communication Engineering Department,

NIT Warangal

Chairman

---

**Prof. D. Vakula**

Head, Electronics and Communication Engineering Department,

NIT Warangal

Date: \_\_\_\_\_

Place: \_\_\_\_\_

---

Dedicated

To

My Family,

Teachers & Friends

## Declaration

This is to certify that the work presented in the thesis entitled **Design And Analysis Of Dual Material Gate Junctionless FinFET For Analog IC Applications** is a bonafide work done by me under the supervision of **Prof. T.V.K Hanumantha Rao**, Professor, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed

Place:

Date:

Rambabu Kusuma

Research Scholar

Roll No.: 718044

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL, INDIA-506004

Department of Electronics & Communication Engineering

**CERTIFICATE**

This is to certify that the thesis work entitled **Design And Analysis Of Dual Material Gate Junctionless FinFET For Analog IC Applications** is a bonafide record of work carried out by **Rambabu Kusuma** submitted to the faculty of **Electronics & Communication Engineering** department, in partial fulfilment of the requirements for the award of the degree of **Doctor of Philosophy** in **Electronics and Communication Engineering, National Institute of Technology Warangal, India-506004**. The contributions embodied in this thesis have not been submitted to any other university or institute for the award of any degree.

Prof. T.V.K Hanumantha Rao

Place: Research Supervisor

Date: Department of ECE

NIT Warangal, India-506 004.

## Acknowledgements

First of all, I would like to express my sincere gratitude to my supervisor Prof. T.V.K Hanumantha Rao for his guidance and support. His extreme energy, encouragement, and immense knowledge that resolved all my queries have always been a constant source of motivation throughout my Ph.D. study and research. His passion and enthusiasm for teaching, sharing his knowledge and motivating students have not only inspired me, but has also made every individual an ardent academic disciple who has been taught by him. Being student-responsive and an effective mentor, his guidance helped me throughout thick and thin periods of my research, for which I am honestly indebted and thankful throughout my career and lifetime.

I am also grateful to Prof. Patri Sreehari Rao, Head of the department, Department of Electronics and Communication Engineering, NIT Warangal for his valuable suggestions and support that he shared during my research tenure.

Besides my supervisor, I take this privilege to thank Doctoral Scrutiny Committee members, Prof. N.Bheema Rao, Department of Electronics and Communication Engineering, NIT Warangal, Prof. Patri Sreehari Rao, Department of Electronics and Communication Engineering, NIT Warangal and Prof. N. Vishwanathan, Department of Electrical Engineering, NIT Warangal for their continuous support, suggestions and advices during my research period whenever required.

It is my pleasure to show my indebtedness to my co-scholars at NIT like Rsoshan Bodile, Santhosh.V, Saikumar Aruri, P. Hari, P. Santhosh, Sagar, Dr. Bharath for their help during the course of this work.

I find no words inadequate to express any form of acknowledgment to my father, mother, brother and sister for their love, support and patience for making my dream come

true.

Finally, I thank God, for filling me every day with new hopes, strength, purpose and faith.

**Rambabu Kusuma**

---

## Abstract

The era of Internet of Things (IoT) and Big data are the major driving forces to develop intelligent systems. Specifically, these systems are designed by Complementary Metal Oxide Semiconductor (CMOS) technology with proper scaling of the device ratios. Even though, the CMOS scaling trend has reached its atomistic limit the short channel effects and fabrication difficulty have worsened the MOS devices' aggressive scaling. Junctionless (JL) technology has been suggested as one of the likely methods to get around this scaling barrier. Homogeneous doping concentration is used in all three regions by JL-based FETs. This idea not only makes manufacturing simpler and less expensive, but it also exhibits better short channel behaviour than typical junction-based devices. Due to their promising attributes, JL based FinFETs are chosen for this research work.

However, due to the high electric field in the nano-scaled device, the electrical characteristics deteriorate due to the short channel effects (SCEs). Moreover, channel potential, position of minimum threshold voltage, and subthreshold characteristics of the FinFET are altered because of SCEs. To reduce this SCEs problem, the gate material engineering, such as dual metal gate structure are incorporated into the FinFET. To further reduce SCEs, the gate stack engineering is employed into the dual material gate JL FinFET.

The main objective of the thesis is to design and simulation analysis of the dual material gate junctionless FinFET (DMG JLFinFET). In this thesis, the DC performance parameters of DMG JLFinFET i.e.  $I_{on}$ ,  $I_{off}$ ,  $I_{on}/I_{off}$  ratio, subthreshold swing (SS) and drain induced barrier lowering(DIBL) is presented. Besides, the analog/RF figures of merit of the proposed DMG JLFinFET, including the transconductance, transconductance generation factor, The Cut-off frequency, Intrinsic delay , Transconductance frequency product , Gain bandwidth product are evaluated for different values of device parameters. Also, the linearity performance metrics such as second order transconductance coefficient ( $g_{m2}$ ), third order transconductance coefficient ( $g_{m3}$ ), second and third-

---

## Abstract

---

order voltage intercept points VIP2, VIP3, third-order power intercept point (IIP3), and 1-dB compression point of the proposed DMG JLFinFET are evaluated for different values of device parameters. Furthermore, temperature variability analysis of DMG JLFinFET analyzed. It is investigated that the proposed DMG JLFinFET has better performance than SMG JLFinFET. The proposed device verified against numerical results obtained from TCAD simulations obtained from Visual TCAD, which is a device simulator from Cogenda.

# Contents

|                                                       |             |

|-------------------------------------------------------|-------------|

| <b>Declaration</b>                                    | <b>ii</b>   |

| <b>Acknowledgements</b>                               | <b>iv</b>   |

| <b>Abstract</b>                                       | <b>vi</b>   |

| <b>List of Figures</b>                                | <b>xi</b>   |

| <b>List of Tables</b>                                 | <b>xiii</b> |

| <b>List of Abbreviations</b>                          | <b>xv</b>   |

| <b>1 Introduction</b>                                 | <b>1</b>    |

| 1.1 Evaluation of Transistors . . . . .               | 1           |

| 1.1.1 Integrated Circuits (ICs) . . . . .             | 3           |

| 1.2 MOSFET Scaling . . . . .                          | 4           |

| 1.2.1 Scaling challenges . . . . .                    | 5           |

| 1.2.2 Drain-Induced Barrier Lowering (DIBL) . . . . . | 5           |

| 1.2.3 Punch through . . . . .                         | 5           |

| 1.2.4 Carrier mobility degradation . . . . .          | 6           |

| 1.2.5 Threshold voltage roll-off . . . . .            | 6           |

| 1.3 CMOS boosters . . . . .                           | 6           |

---

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| 1.3.1    | Gate material engineering . . . . .                              | 6         |

| 1.3.2    | Graded channel engineering . . . . .                             | 7         |

| 1.3.3    | High-k insulating material . . . . .                             | 7         |

| 1.3.4    | Non-conventional MOSFETs . . . . .                               | 8         |

| 1.4      | Motivation . . . . .                                             | 8         |

| 1.5      | Problem Statement . . . . .                                      | 9         |

| 1.6      | Research Objectives . . . . .                                    | 9         |

| 1.7      | Thesis Organization . . . . .                                    | 9         |

| <b>2</b> | <b>Literature Survey</b>                                         | <b>11</b> |

| 2.1      | Introduction . . . . .                                           | 11        |

| 2.2      | Junctionless technology beyond CMOS . . . . .                    | 12        |

| 2.3      | Features of Junctionless technology . . . . .                    | 12        |

| 2.4      | Review of various Junctionless FETs . . . . .                    | 14        |

| 2.5      | Review of various Dual Material Gate Junctionless FETs . . . . . | 21        |

| 2.6      | Summary . . . . .                                                | 27        |

| <b>3</b> | <b>Design and Analysis of DMG JLFinFET: DC Perspective</b>       | <b>29</b> |

| 3.1      | Introduction . . . . .                                           | 29        |

| 3.2      | Device Structure and Simulation Setup . . . . .                  | 30        |

| 3.3      | Results And Discussions . . . . .                                | 32        |

| 3.3.1    | Gate Oxide Engineering . . . . .                                 | 33        |

| 3.3.2    | Fin Width Variation . . . . .                                    | 36        |

| 3.3.3    | Fin Height Variation . . . . .                                   | 37        |

| 3.4      | Conclusions . . . . .                                            | 44        |

---

|                                                                                        |           |

|----------------------------------------------------------------------------------------|-----------|

| <b>4 Analog and RF Performance Analysis of DMG JLFinFET</b>                            | <b>46</b> |

| 4.1 Introduction . . . . .                                                             | 46        |

| 4.2 Device Srtructure And Simulation Frame Work . . . . .                              | 48        |

| 4.2.1 Results And Discussion . . . . .                                                 | 50        |

| 4.2.2 Analog/RF Performance . . . . .                                                  | 52        |

| 4.3 Conclusions . . . . .                                                              | 56        |

| <b>5 Temperature assessment of Analog/RF and Linearity parameters on DMG JL FinFET</b> | <b>58</b> |

| 5.1 Introduction . . . . .                                                             | 58        |

| 5.2 Device structure and simulation setup . . . . .                                    | 60        |

| 5.3 Simulation results and discussion . . . . .                                        | 62        |

| 5.3.1 Comparison behavior of SMG JLFinFET with DMG JLFinFET .                          | 62        |

| 5.3.2 Impact of Temperature on DC Parameter . . . . .                                  | 63        |

| 5.3.3 Impact of Temperature on Analog/RF Parameter . . . . .                           | 66        |

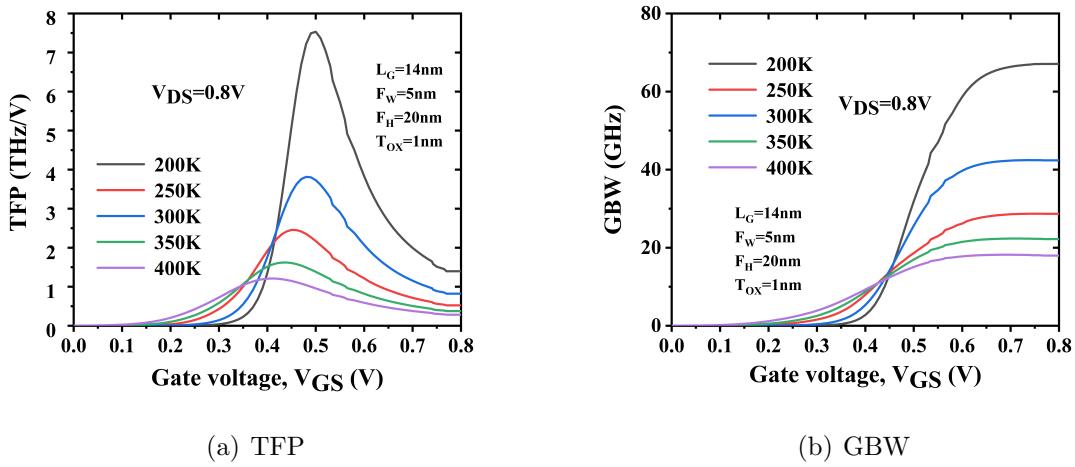

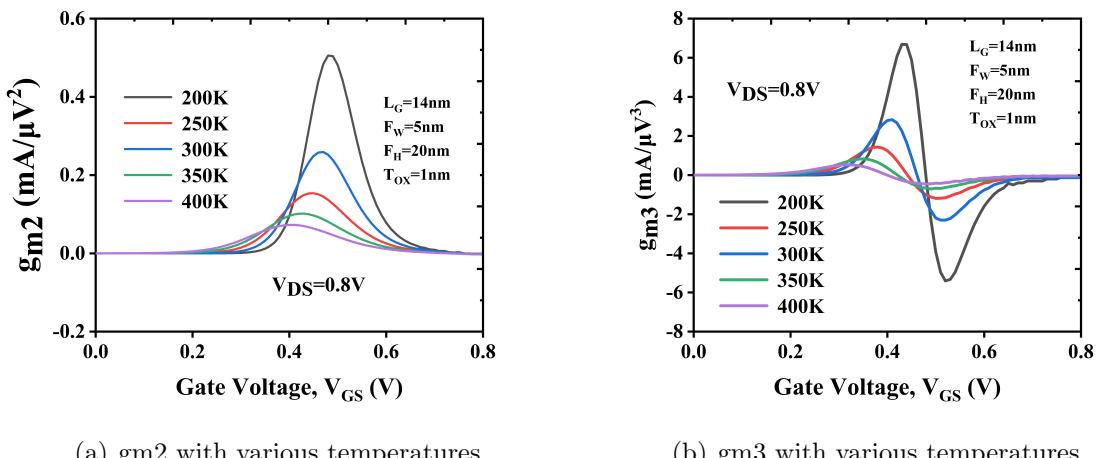

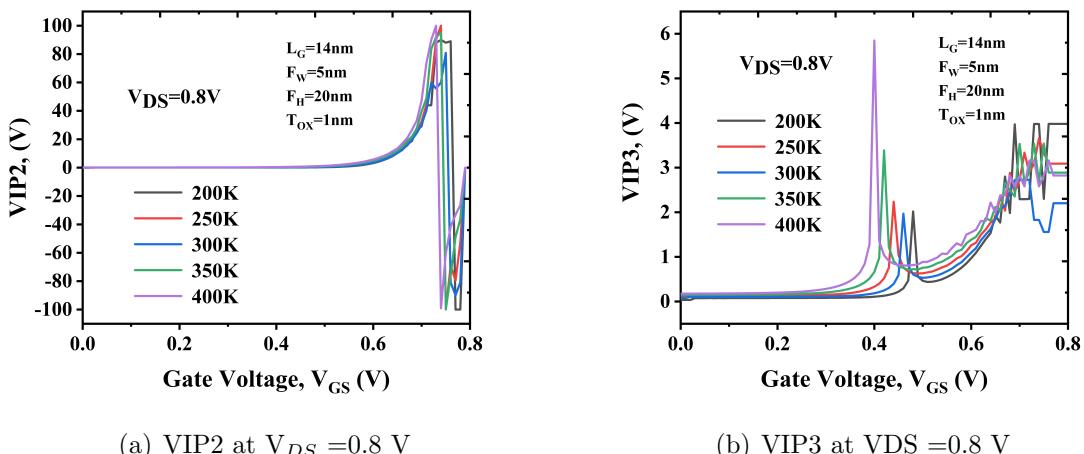

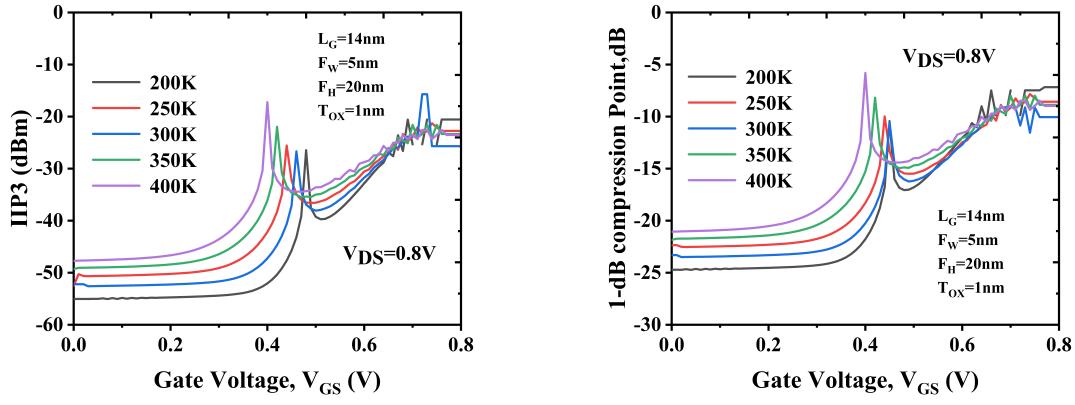

| 5.3.4 Impact of Temperature on Linearity Parameter . . . . .                           | 70        |

| 5.4 Conclusion . . . . .                                                               | 75        |

| <b>6 Conclusion and Future scope</b>                                                   | <b>76</b> |

| 6.1 Conclusions . . . . .                                                              | 76        |

| 6.2 Future Scope . . . . .                                                             | 77        |

| <b>Publications</b>                                                                    | <b>79</b> |

| <b>Bibliography</b>                                                                    | <b>81</b> |

# List of Figures

|      |                                                                                                                      |    |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Historical growth of the electronic devices [6]                                                                      | 3  |

| 1.2  | Thesis organaization in pictorial representation                                                                     | 10 |

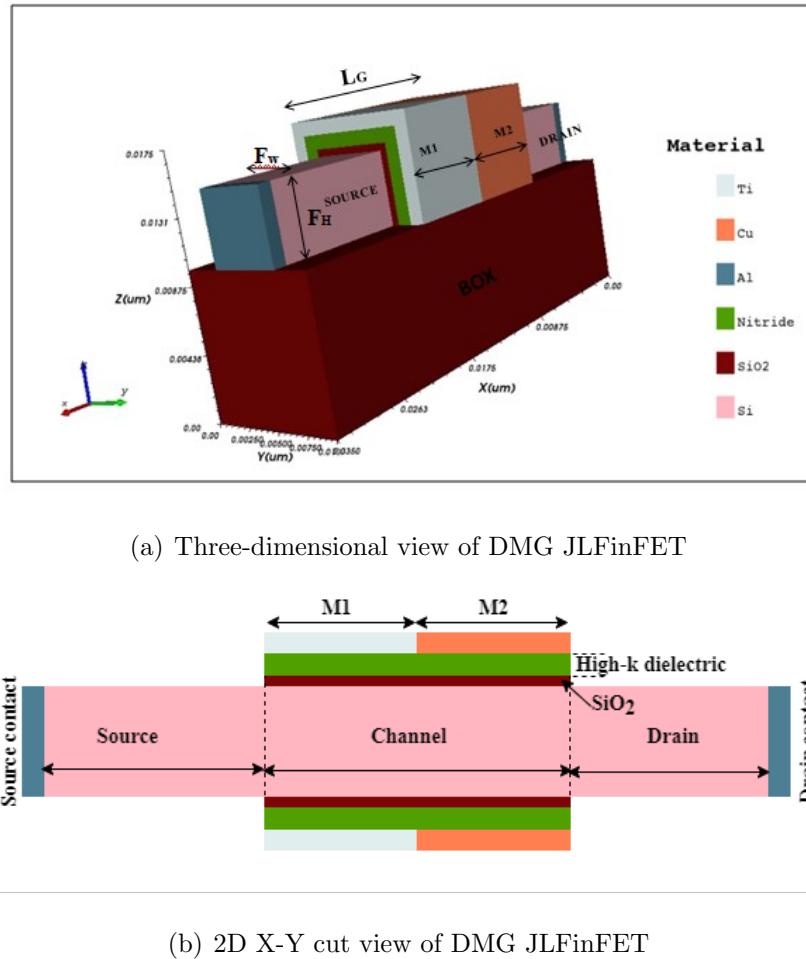

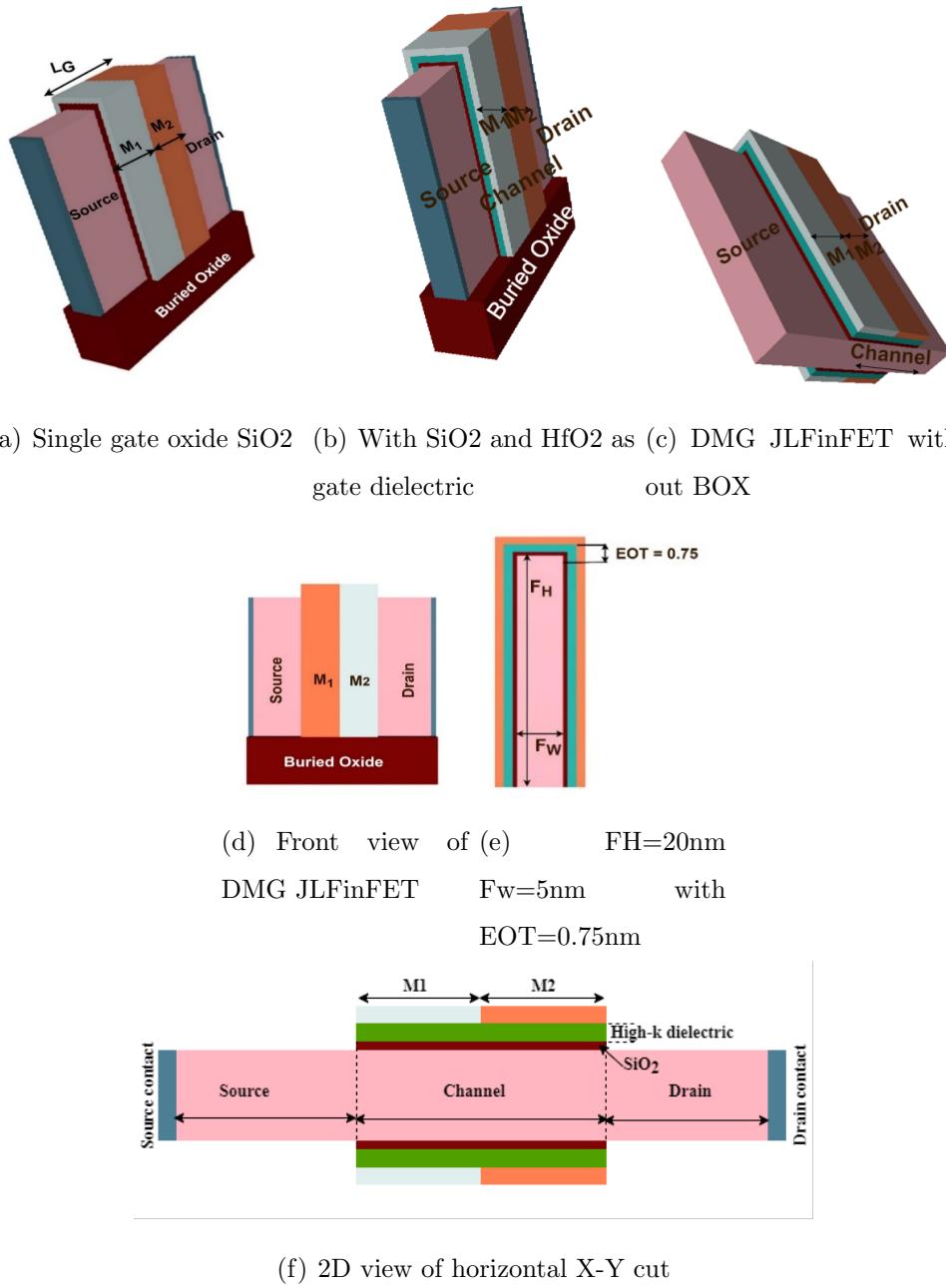

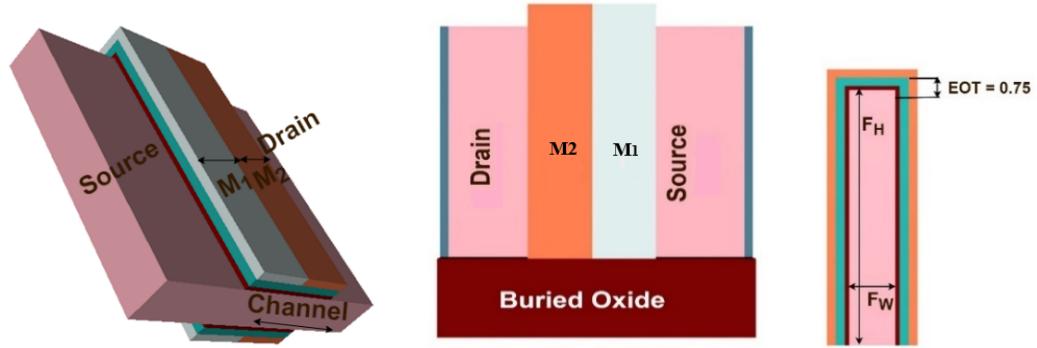

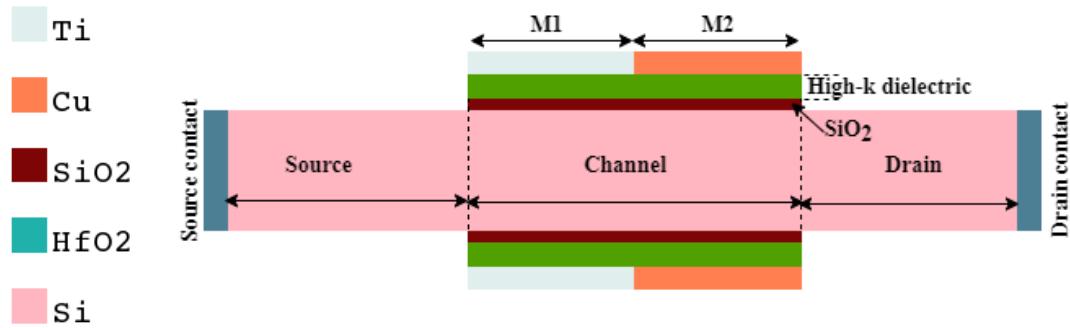

| 3.1  | Structure of DMG JLFinFET                                                                                            | 31 |

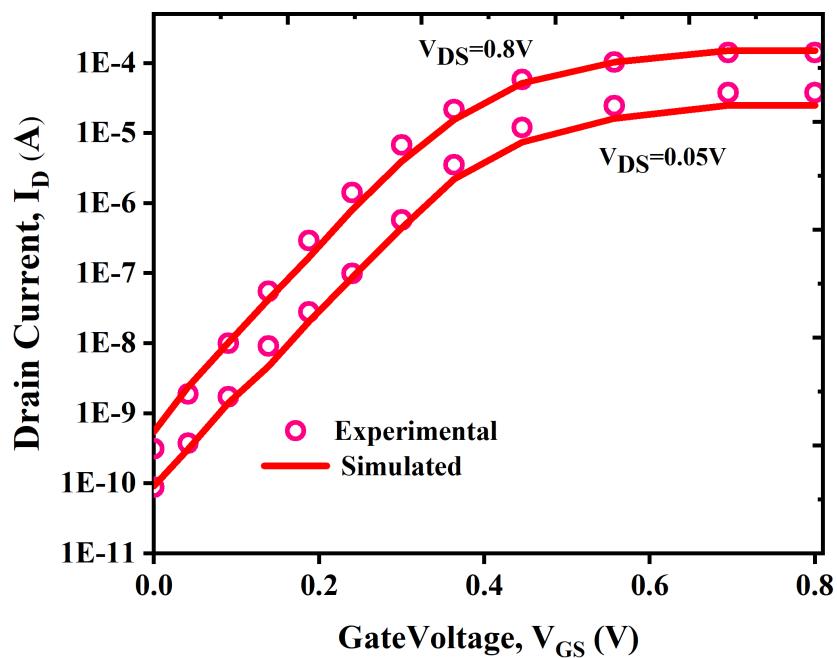

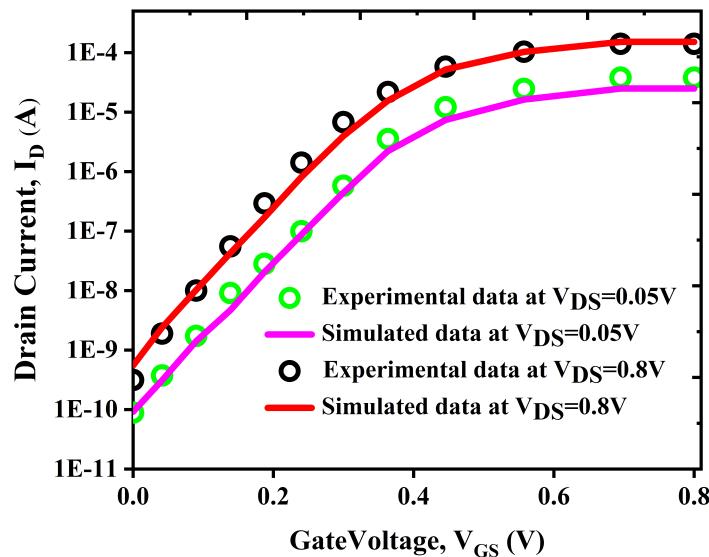

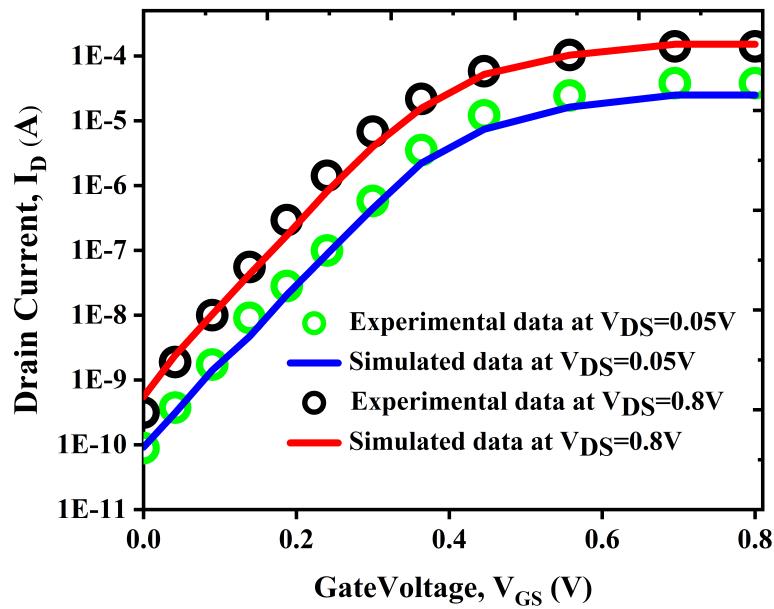

| 3.2  | Calibrated Drain Characteristics of DMG JLFinFET [122]                                                               | 32 |

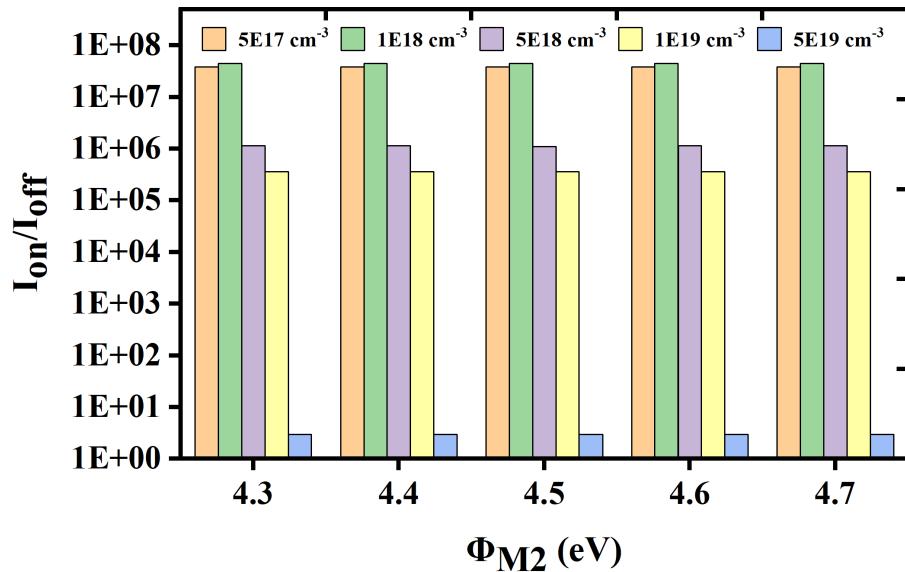

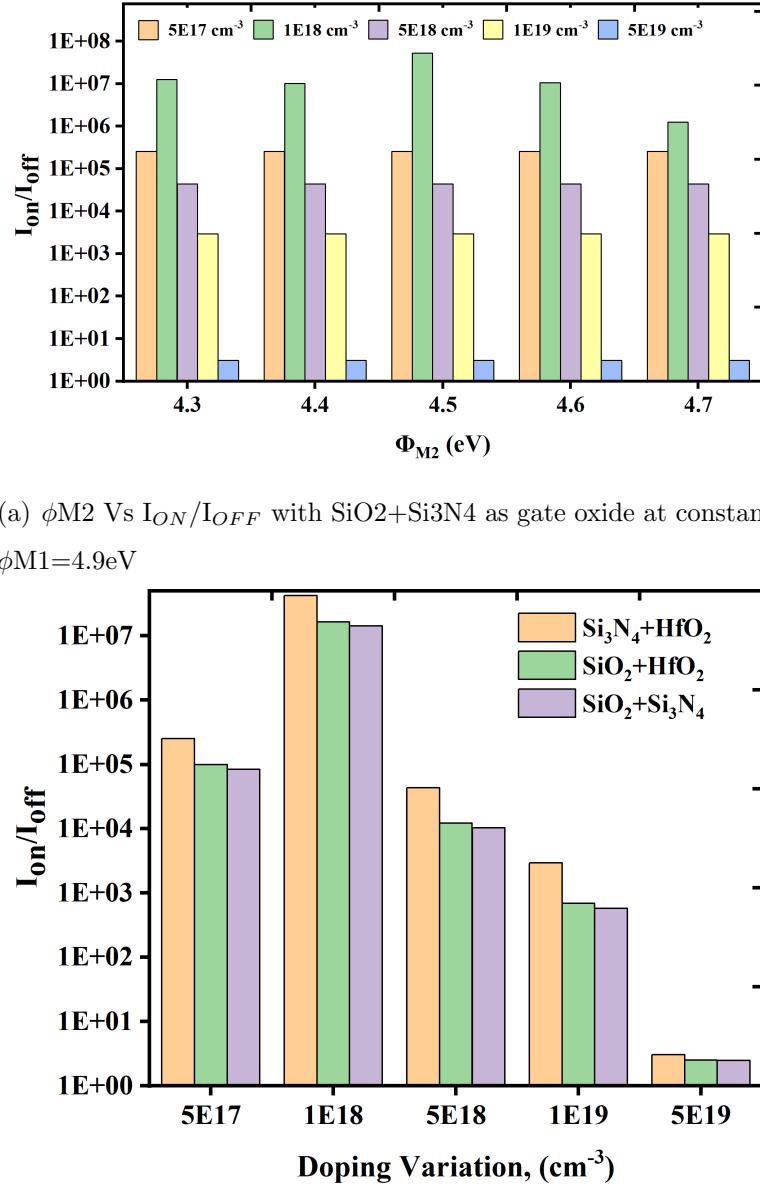

| 3.3  | $\phi M2$ Vs $I_{on}/I_{off}$ with $SiO_2$ as gate oxide at constant $\phi M1=4.9eV$                                 | 33 |

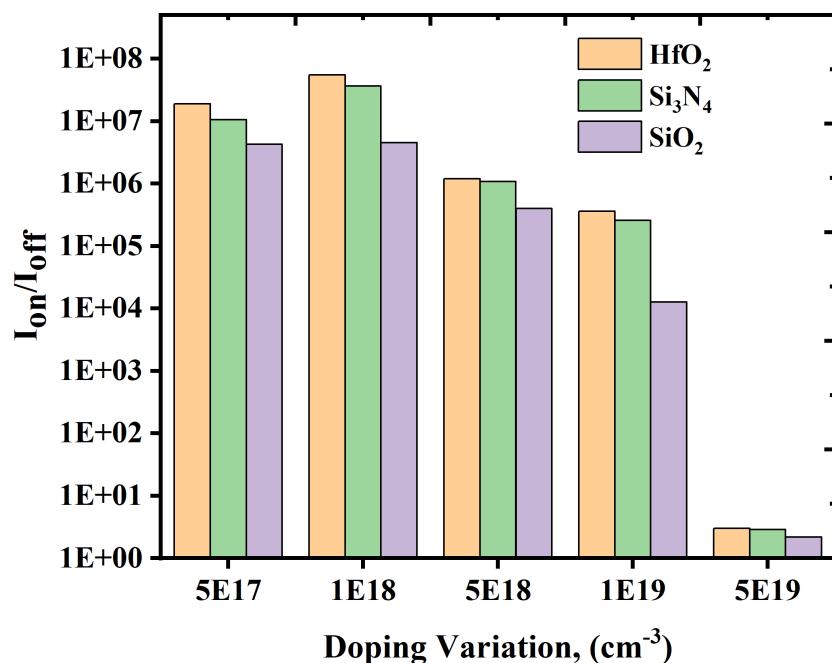

| 3.4  | $I_{on}/I_{off}$ Vs Doping Variation with fixed $\phi M1=4.9eV$ and $\phi M2=4.5eV$ for different single gate oxides | 34 |

| 3.5  | Doping concentration levels                                                                                          | 35 |

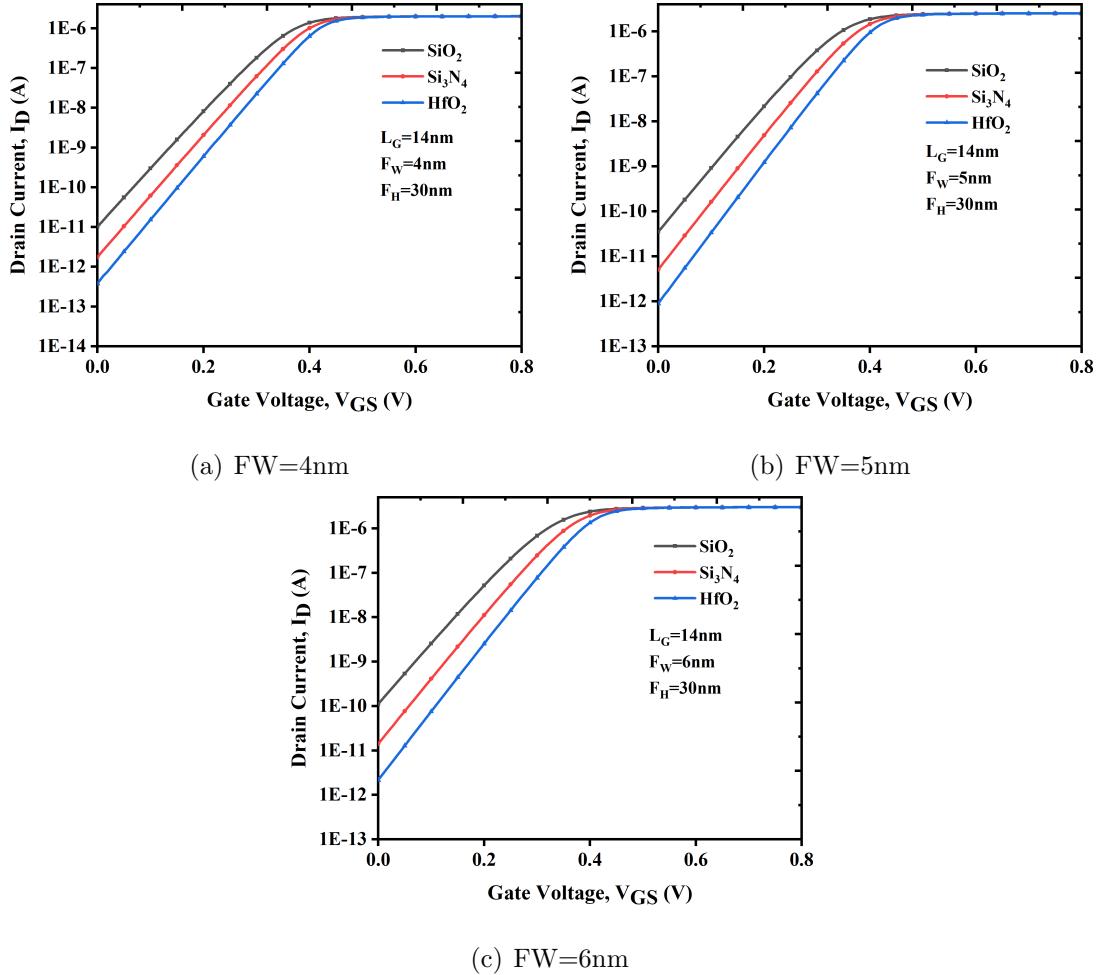

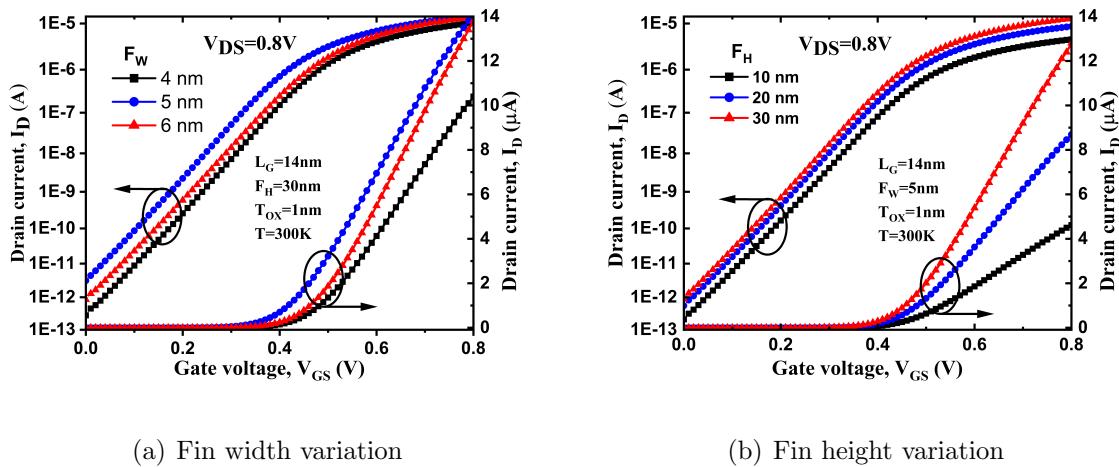

| 3.6  | Fin width variation of DMG JLFinFET with single gate oxides                                                          | 36 |

| 3.7  | Fin width variation of DMG JLFinFET with dual gate oxides                                                            | 37 |

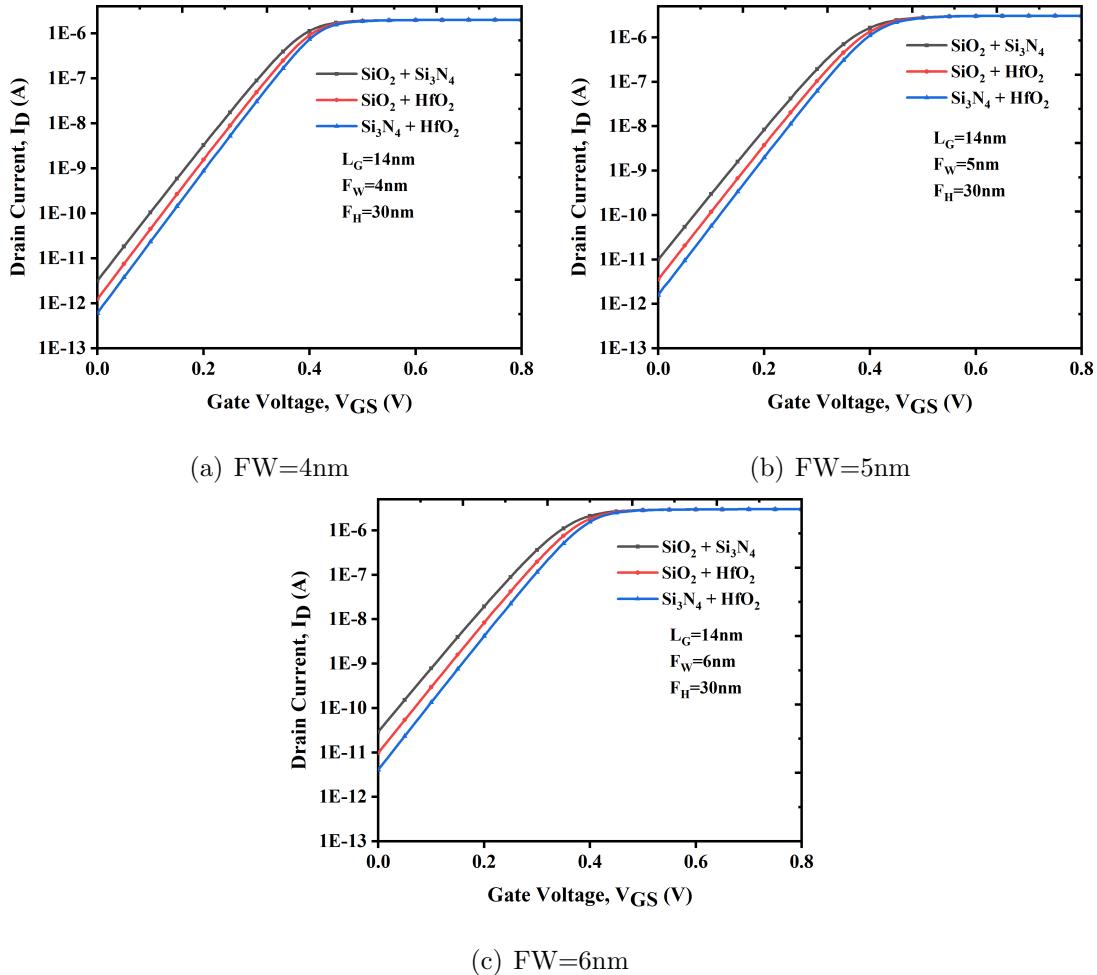

| 3.8  | Fin height variation of DMG JLFinFET with single gate oxides                                                         | 38 |

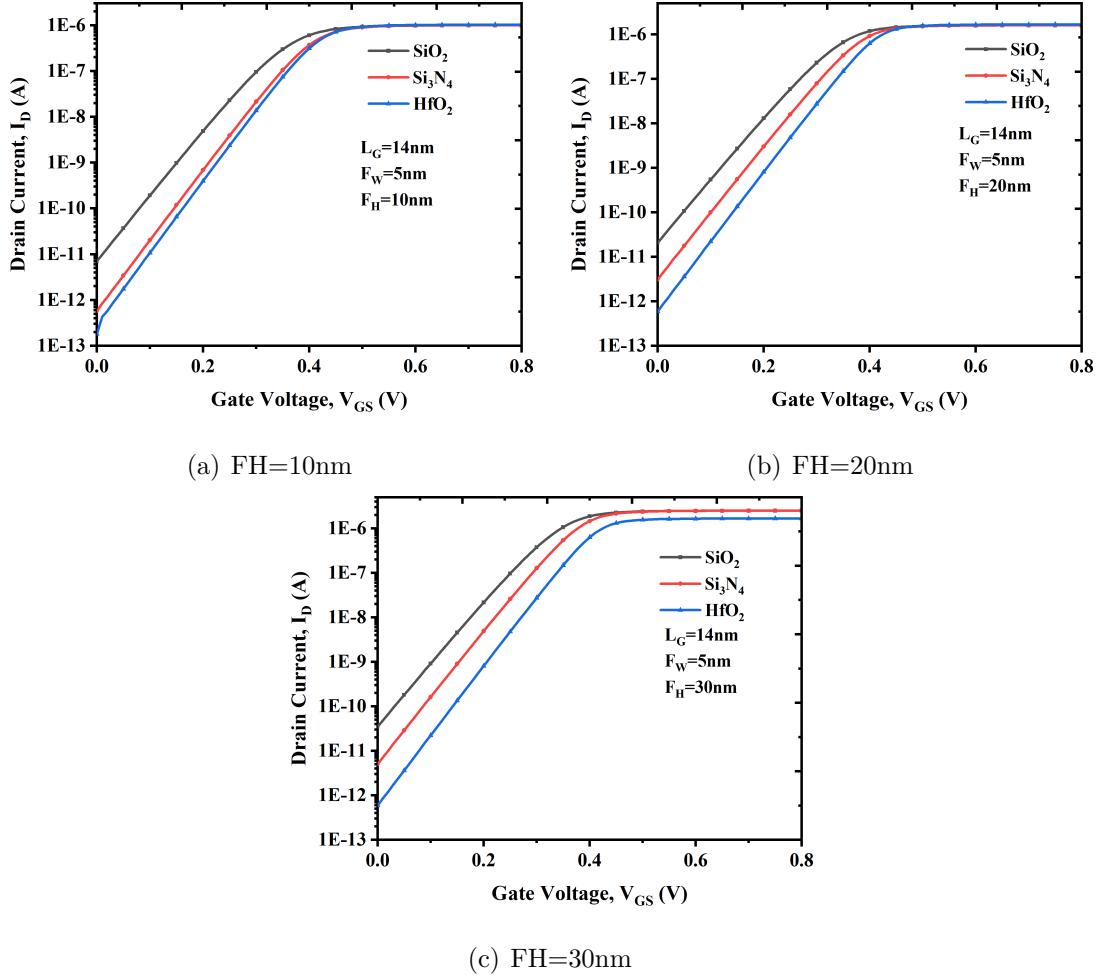

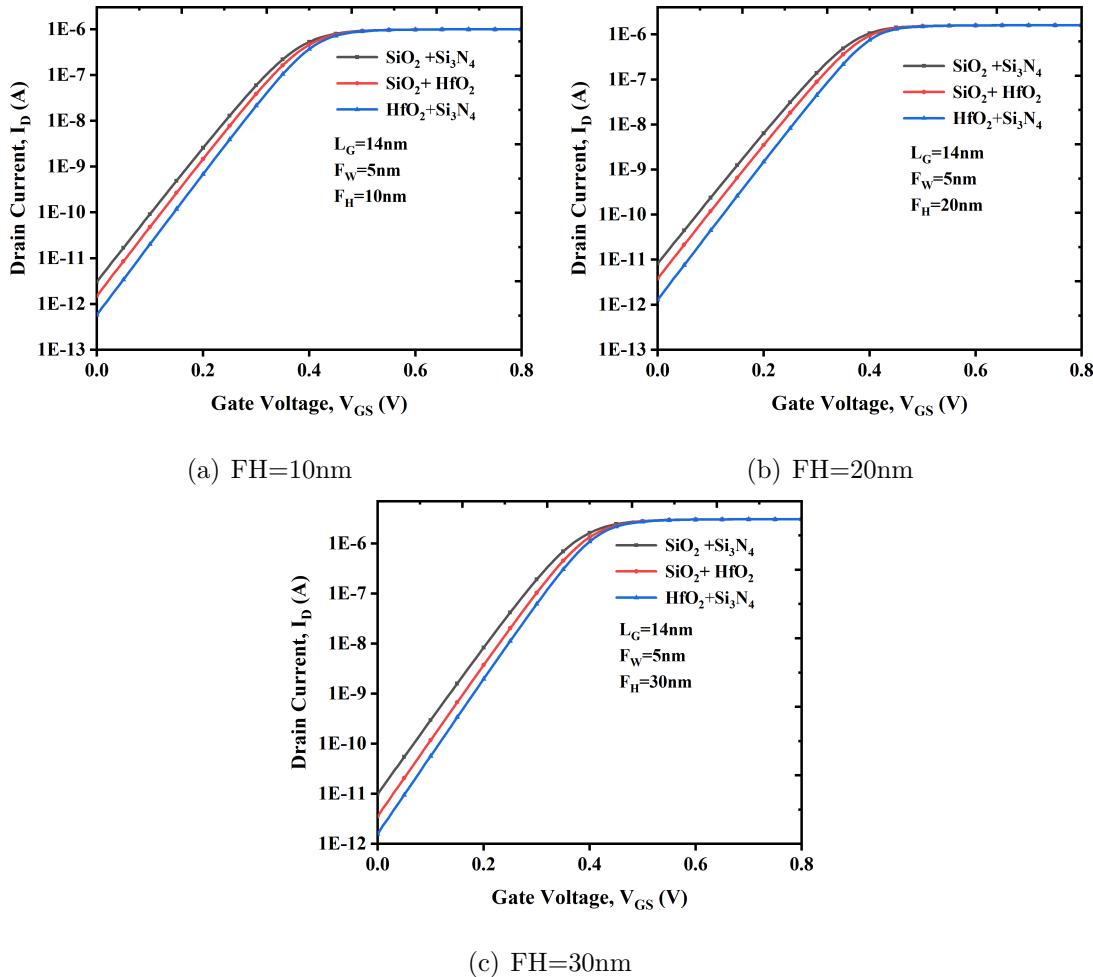

| 3.9  | Fin height variation of DMG JLFinFET with dual gate oxides                                                           | 39 |

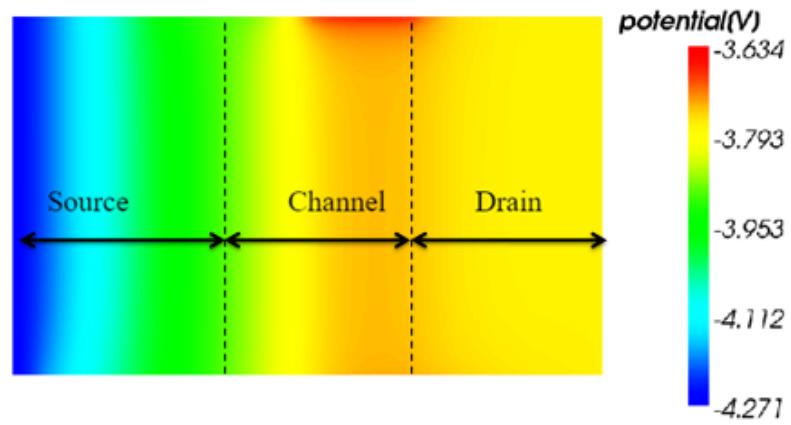

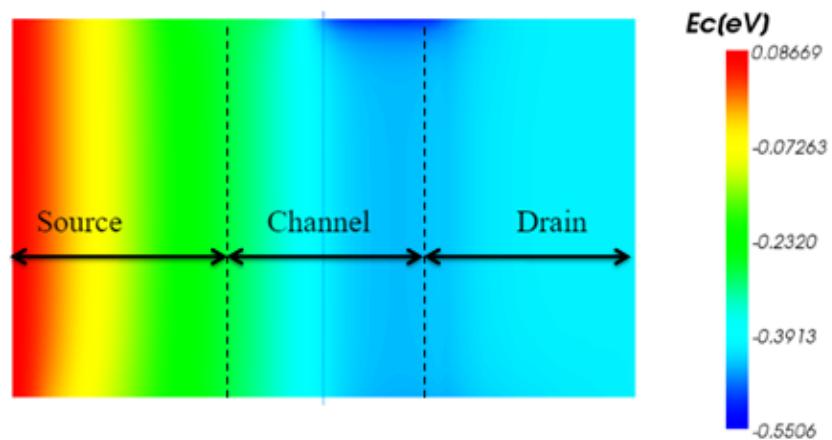

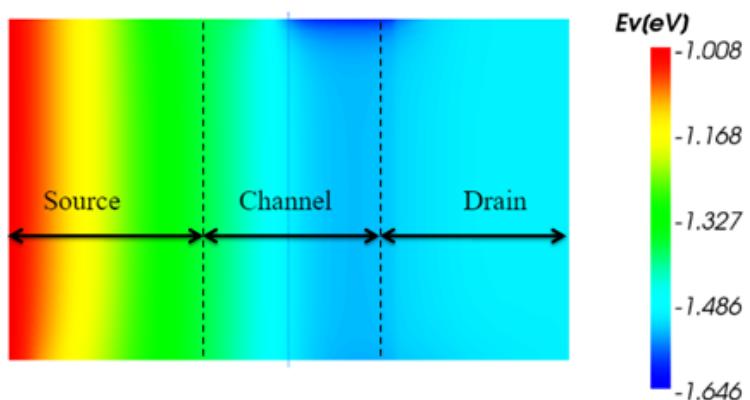

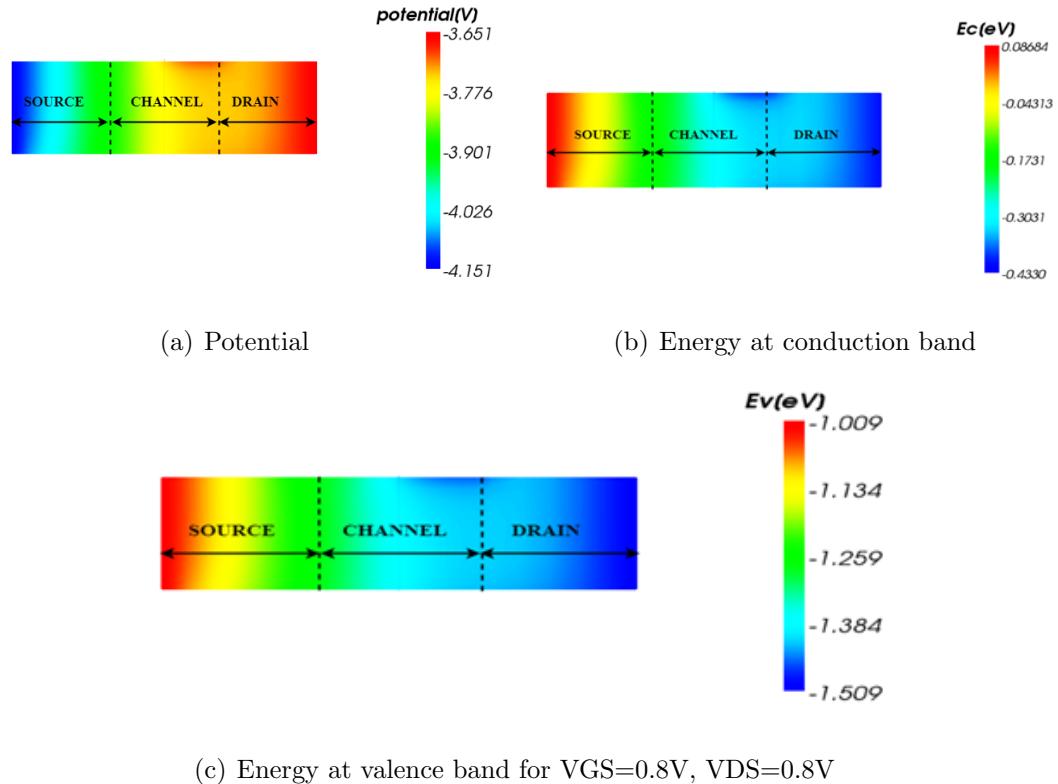

| 3.10 | Distribution of potential occurred in DMG JLFinFET                                                                   | 40 |

| 4.1  | 3D schematic view of DMG JLFinFET                                                                                    | 48 |

| 4.2  | Calibration of ID-VGS characteristics of DMG JLFinFET [122]                                                          | 49 |

| 4.3  | Drain characteristics                                                                                                | 50 |

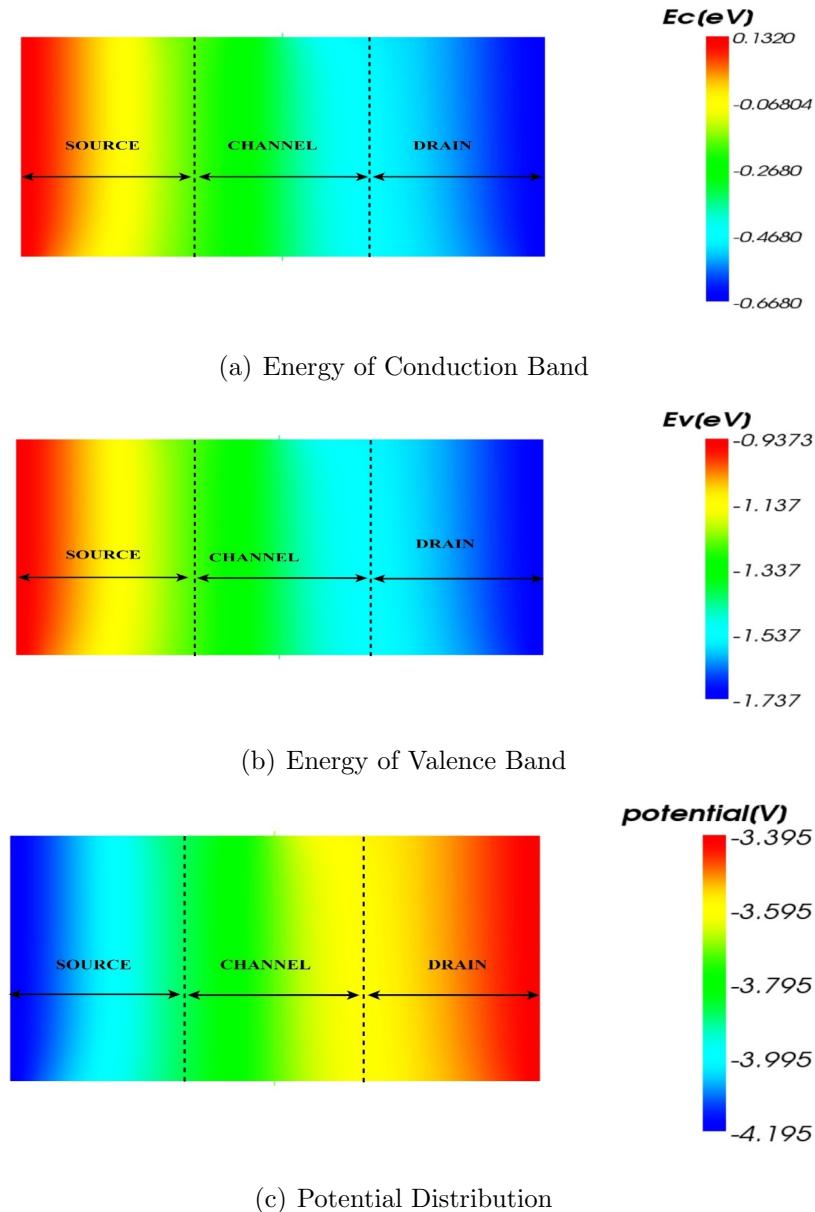

| 4.4  | Contour plots of DMG JLFinFET                                                                                        | 51 |

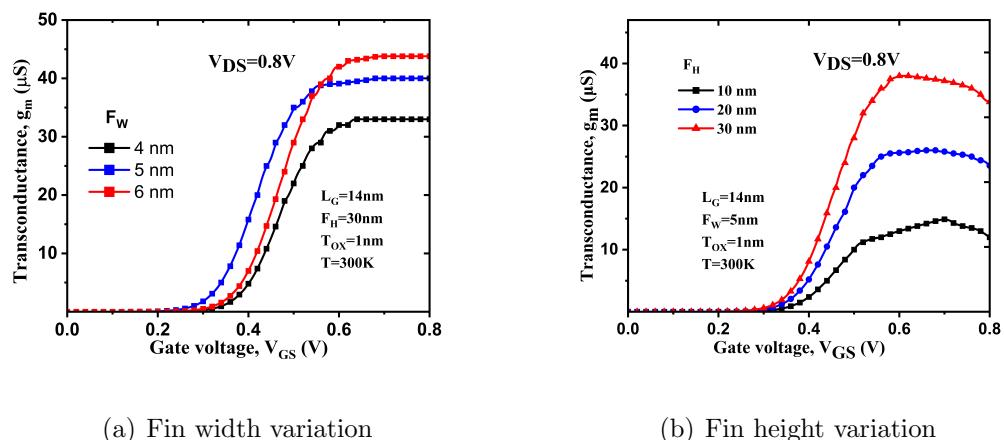

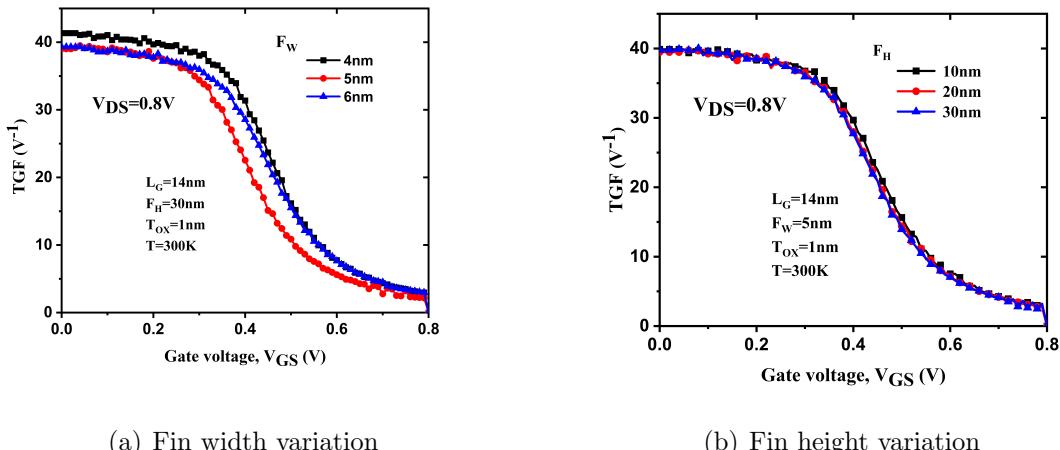

| 4.5  | Transconductance                                                                                                     | 51 |

---

|      |                                                                                           |    |

|------|-------------------------------------------------------------------------------------------|----|

| 4.6  | TGF                                                                                       | 52 |

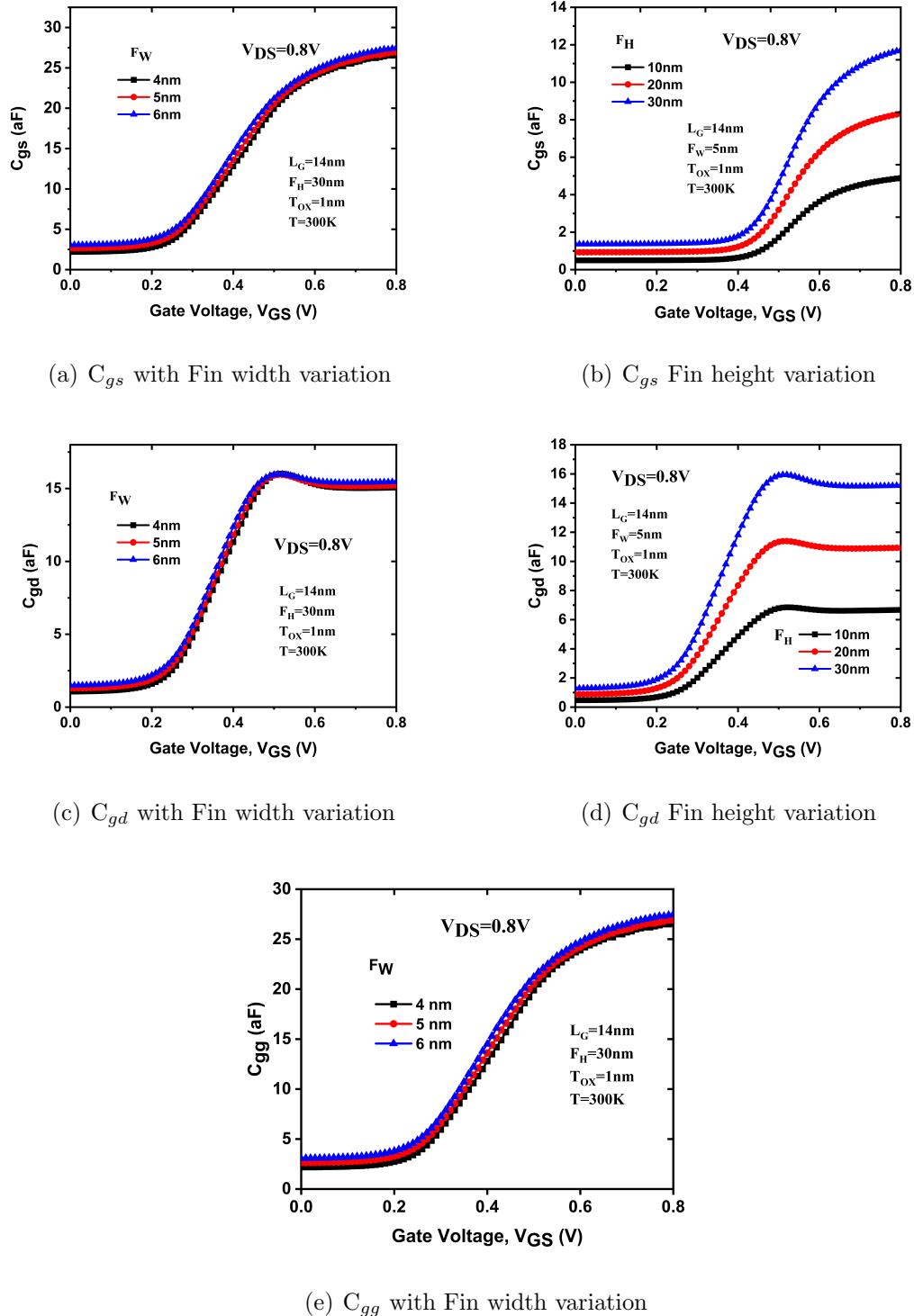

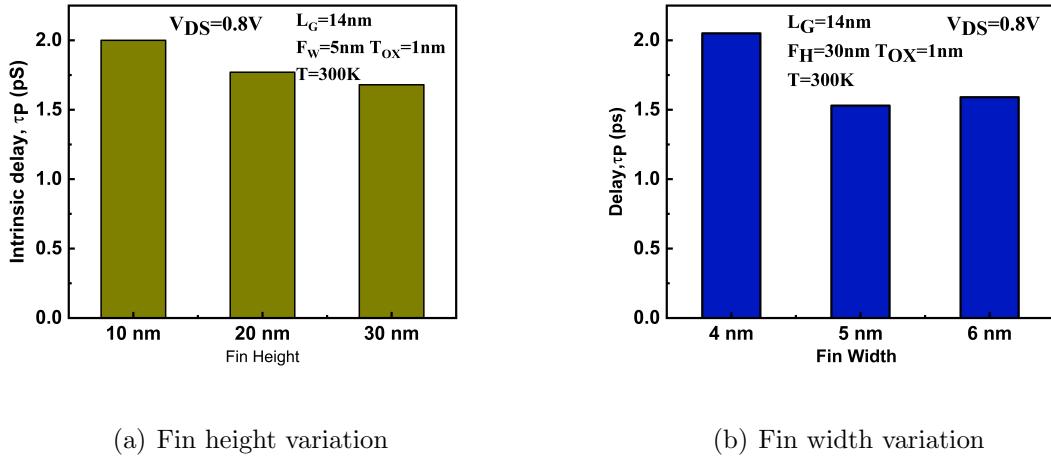

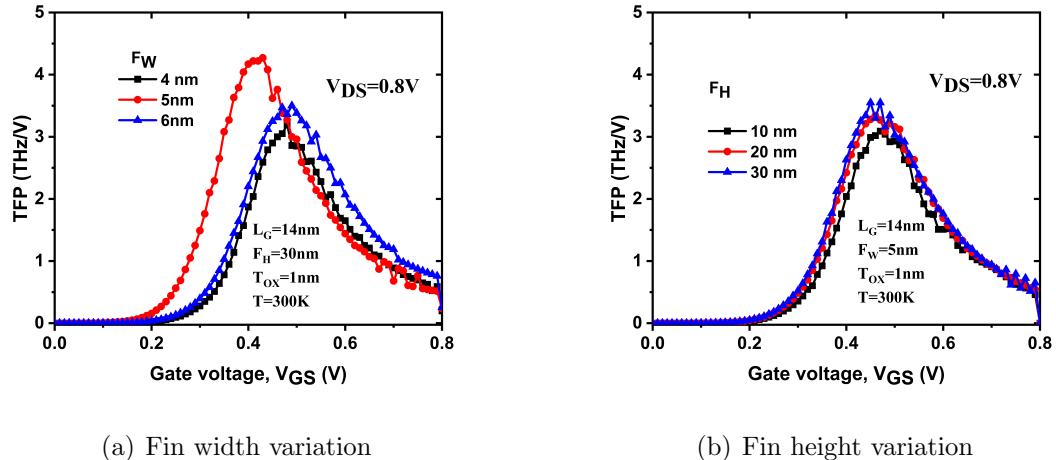

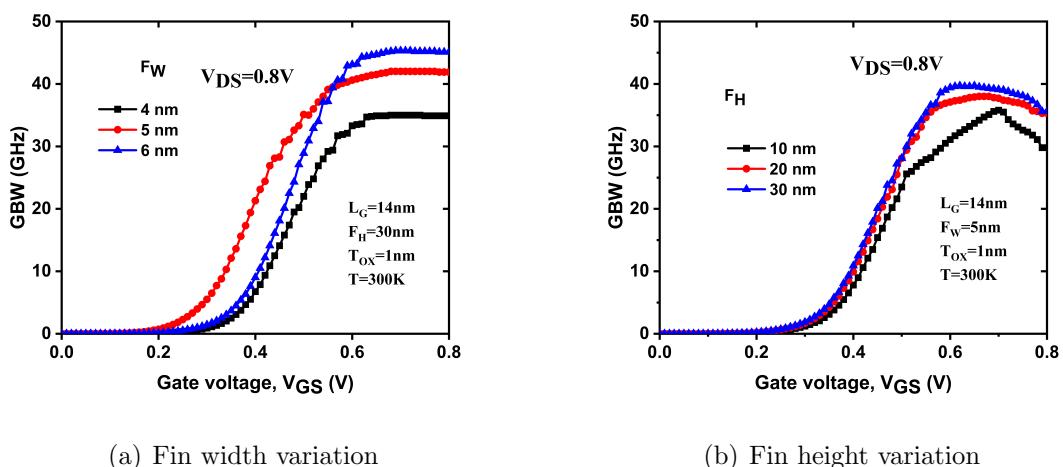

| 4.7  | Effect of Fin width and height variation                                                  | 53 |

| 4.8  | Cut-off frequency                                                                         | 54 |

| 4.9  | Intrinsic delay                                                                           | 55 |

| 4.10 | Transconductance frequency product                                                        | 55 |

| 4.11 | Gain bandwidth product(GBW)                                                               | 56 |

| 5.1  | 3D schematic view of DMG JLFinFET                                                         | 61 |

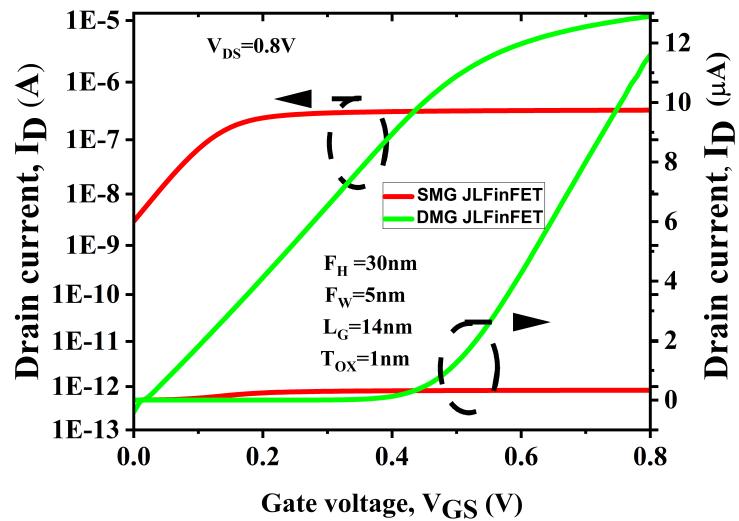

| 5.2  | Comparison between SMG JLFinFET and DMG JLFinFETs                                         | 63 |

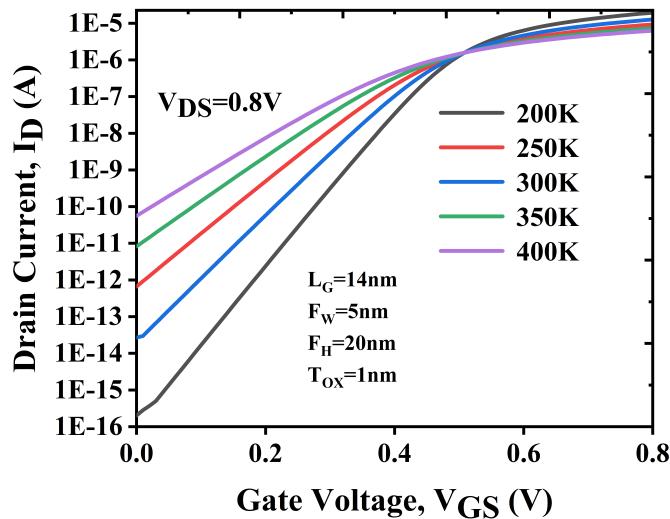

| 5.3  | Transfer characteristics of DMG JLFinFET with temperature variation                       | 63 |

| 5.4  | Contour plots of DMG JLFinFET with VGS=0.8V and VDS=0.8V at 400K<br>in horizontal X-Y cut | 66 |

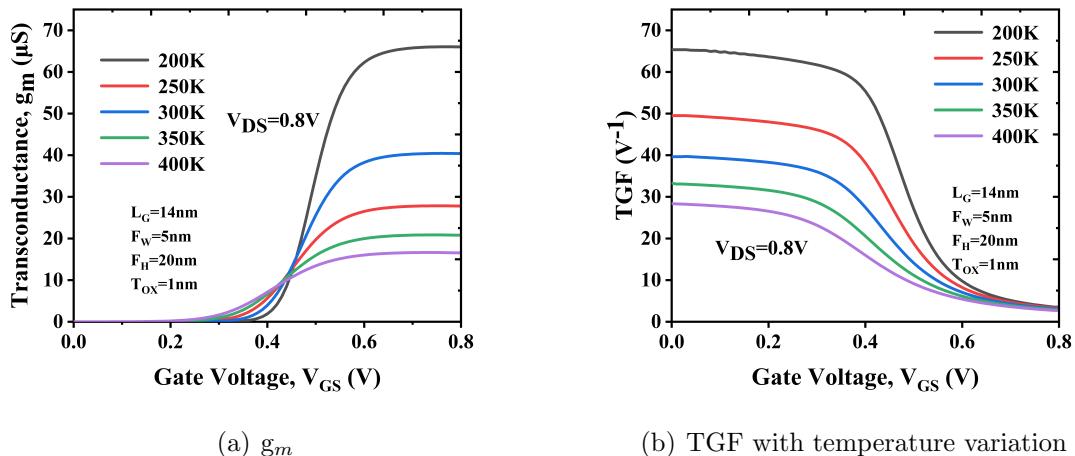

| 5.5  | DMG JLFinFET analog/RF characteristics                                                    | 67 |

| 5.6  | The temperature effect                                                                    | 68 |

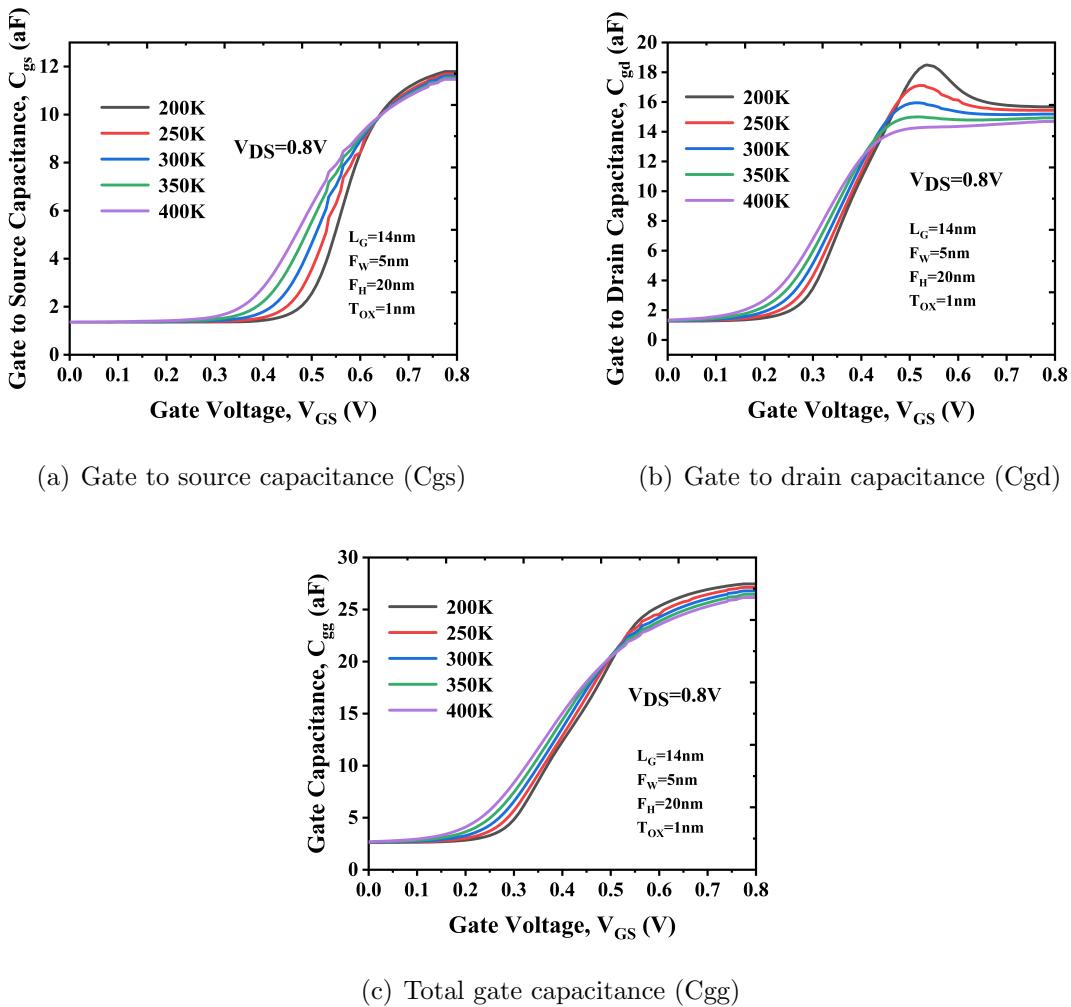

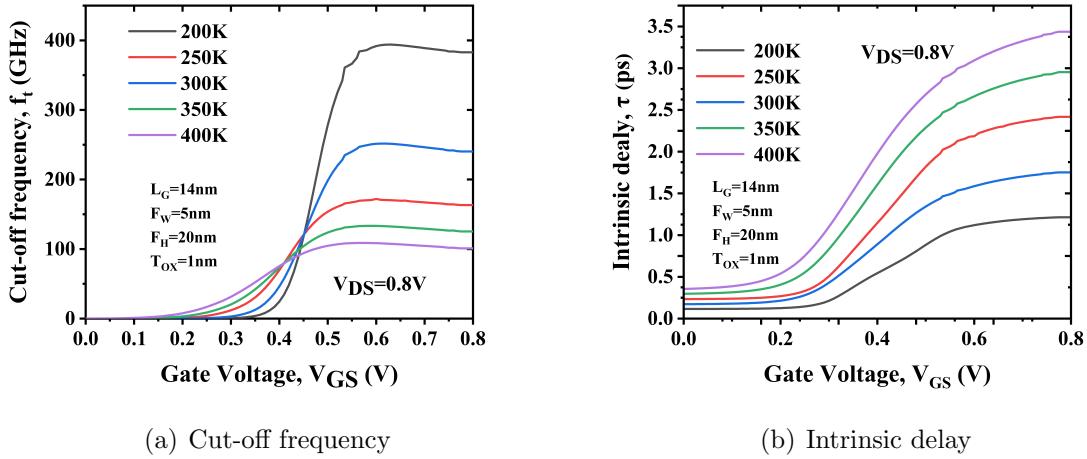

| 5.7  | Impact of temperature                                                                     | 69 |

| 5.8  | The change with the variation of temperature                                              | 70 |

| 5.9  | The variation of on higher-order harmonics                                                | 71 |

| 5.10 | The temperature dependency on Voltage Intercept Points                                    | 72 |

| 5.11 | The temperature dependency                                                                | 73 |

## List of Tables

|     |                                                                                                                   |    |

|-----|-------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Device dimensions and parameters used . . . . .                                                                   | 32 |

| 3.2 | Performance Parameters of DMG JLFinFET with $L_G=14\text{nm}$ , $F_H=30\text{nm}$ ,<br>$F_W=6\text{nm}$ . . . . . | 41 |

| 3.3 | Performance Parameters of DMG JLFinFET with $L_G=14\text{nm}$ , $F_H=30\text{nm}$ ,<br>$F_W=5\text{nm}$ . . . . . | 41 |

| 3.4 | Performance Parameters of DMG JLFinFET with $L_G=14\text{nm}$ , $F_H=30\text{nm}$ ,<br>$F_W=4\text{nm}$ . . . . . | 42 |

| 3.5 | Performance Parameters of DMG JLFinFET with $L_G=14\text{nm}$ , $F_W=5\text{nm}$ ,<br>$F_H=20\text{nm}$ . . . . . | 42 |

| 3.6 | Performance Parameters of DMG JLFinFET with $L_G=14\text{nm}$ , $F_W=5\text{nm}$ ,<br>$F_H=10\text{nm}$ . . . . . | 42 |

| 3.7 | Performance Comparison of Single Metal and Dual Metal Gate JLFinFET                                               | 43 |

| 3.8 | Comparison of proposed device DC parameters with existing results . . . . .                                       | 44 |

| 4.1 | Device dimensions and parameters used . . . . .                                                                   | 50 |

| 4.2 | Comparison of proposed device analog parameters with existing results . .                                         | 57 |

| 5.1 | Device parameters used for simulation . . . . .                                                                   | 62 |

| 5.2 | Extracted parameters with variation in Temperature . . . . .                                                      | 65 |

| 5.3 | Comparison of proposed device analog parameters while varaying tempera-<br>ture with existing results . . . . .   | 70 |

|     |                                                                             |    |

|-----|-----------------------------------------------------------------------------|----|

| 5.4 | Summary performance of DMG JLFinFET in the comparison with T=300K           | 74 |

| 5.5 | Comparison of proposed device linear parameters with existing results . . . | 75 |

## List of Abbreviations

|         |                                                     |

|---------|-----------------------------------------------------|

| 2D      | Two Dimensional                                     |

| BJT     | Bipolar Junction Transistor                         |

| CMOS    | Complementary Metal Oxide Semiconductor             |

| DIBL    | Drain-Induced Barrier-Lowering                      |

| DMG     | Dual-Material-Gate                                  |

| FD      | Fully-Depleted                                      |

| FOM     | Figure Of Merit                                     |

| Ge      | Germanium                                           |

| HCEs    | Hot-Carrier Effects                                 |

| IC      | Integrated Circuit                                  |

| ITRS    | International Technology Roadmap for Semiconductors |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor   |

| MuGFETs | Multi-Gate Field Effect Transistors                 |

| PD      | Partially Depleted                                  |

| QMEs    | Quantum Mechanical Effects                          |

| RF      | Radio Frequency                                     |

| SCEs    | Short-Channel Effects                               |

| Si      | Silicon                                             |

| SOI     | Silicon-On-Insulator                                |

| SoC     | System On-Chip                                      |

| VLSI    | Very Large Scale Integration                        |

| ULSI    | Ultra-Large Scale Integration                       |

| UTB     | Ultra-Thin Body                                     |

# Chapter 1

## Introduction

FinFET (Fin Field-Effect Transistor) is a type of transistor technology that has become popular in recent years for use in integrated circuits. It is a three-dimensional transistor architecture that is designed to provide improved performance, power efficiency, and transistor density over traditional planar transistors. In a FinFET, the gate of the transistor wraps around a vertical silicon "fin," which protrudes from the surface of the silicon wafer. This three-dimensional design allows the gate to control the flow of current on three sides of the fin, providing improved performance and control over the flow of electrons. FinFETs are commonly used in modern microprocessors, memory chips, and other high-performance digital circuits. They are also used in radio-frequency (RF) and analog circuits, where their low power consumption and high switching speeds make them an attractive option. Overall, FinFET technology has played a crucial role in enabling the continued progress of Moore's Law, which states that the number of transistors on a chip will double every two years, by allowing for the creation of smaller and more efficient transistors.

### 1.1 Evolution of Transistors

The transistor is a significant invention that fundamentally altered the development of computers. Vacuum tubes were employed in the first generation of computers; transistors in the second generation; integrated circuits in the third generation; and microprocessors in the fourth generation. In an effort to replace vacuum tubes as mechanical relays

in telecommunications, scientists John Bardeen, William Shockley, and Walter Brattain at the Bell Telephone Laboratories in Murray Hill, New Jersey, studied the behaviour of crystals (germanium) as semiconductors. The vacuum tube, which was used to amplify music and voice and enabled long-distance calling, consumed electricity, produced heat, and burned out quickly, necessitating heavy maintenance. When a final attempt to use a purer substance as a contact point resulted in the creation of the "point-contact" transistor amplifier, the team's research was about to come to a fruitless end. The group won the Nobel Prize in Physics in 1956 for inventing the transistor.

A semiconductor material, such as silicon and germanium, that has the ability to conduct electricity and act as insulation, is used to make transistors. Electronic current is modulated and switched by transistors. Digital circuits previously used vacuum tubes before transistors. Discover all the drawbacks of vacuum tubes in computers by reading the tale of the ENIAC(Electronic Numerical Integrator And Computer). The transistor was the first gadget made to function as both a resistor and a transmitter, transforming sound waves into electronic waves and managing electronic current respectively. Transistor is used as transmitter and also used to transfer the resistance. For their transistor, John Bardeen and Walter Brattain filed a patent. The transistor effect and a transistor amplifier were both the subject of William Shockley's patent application. The computer architecture had a significant effect by the revolution of transistors. Semiconductor-based transistors replaced tubes leading to improved computer design. Same task could be done by transistors, which use less power and space than large and unstable vacuum tubes.

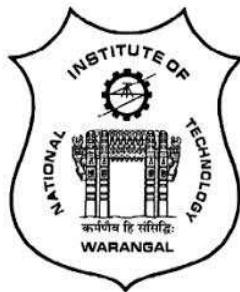

The first functional silicon insulated-gate field effect transistor, or MOSFET as it is called today, was created by Atalla and Kahng in 1960, which had been long expected by Lilienfeld [1]. The device's three main layers - silicon semiconductor as the base material, thermally generated native oxide as an insulator, and the metallic gate electrode serving as the controlling terminal - are stacked one on top of the other to form the overall structure. Because they discovered that silicon's oxidation process is more comfortable than germanium's, they used silicon crystals. Since that time, silicon has dominated the semiconductor industry [2]. By utilizing the Schottky theory, which clarified the rectification between the semiconductor and metal junction [3], Mead proposed the construction of the metal-semiconductor field effect transistor (MESFET) in 1966. Finally, employing

---

an n-type gallium arsenide (GaAs) epitaxial layer on a semi-insulating GaAs substrate, Hooper and Lehrer created the first MESFET prototype [4]. The historical development of electronic devices from the invention of vacuum tubes to the start of the nanoscale period is summarized in Figure 1.1 [6].

**Figure 1.1** Historical growth of the electronic devices [6]

### 1.1.1 Integrated Circuits (ICs)

Jack Kilby proposed in 1958 that transistors and other electronic components may be produced simultaneously on a single semiconductor chip as opposed to separately. This concept made it possible to build electronic components using the same method and supplies. In this method, the p-n junction and bulk semiconductor could both be used to make capacitors and resistors. Kilby was able to construct a flipflop using two transistors and a germanium wafer. Integrated circuits were created in this way [5]. Inventing integrated circuits six months after Kilby, Robert Noyce overcame a number of Kilby's circuit's real-world challenges, including as the issue of interconnectivity between the chip's components. This improved the integrated circuits' ability to be produced in large quantities.

The number of IC components has increased to hundreds of millions as a result of

Wanlass and Sah's invention of Complementary Metal Oxide Semiconductor (CMOS). Since then, chips' component counts have started to rise and integrated circuits have progressively grown in complexity. Gordon Moore made a forecast about the development of integrated circuits in 1965 that became known as Moore's law. According to Moore's law, an integrated chip would have twice as many transistors per square inch every two years. According to Moore's law, the transistor geometry must be reduced every 18 to 24 months. Strong process technology and significant investment in semiconductor foundry R&D are needed for this. VLSI technology has mostly followed Moore's law during the past 50 years as a result of the quick advancements in photolithography techniques, tools, pattern transfer procedures, and equipment.

Over the past few decades, increased complexity, faster production, and lower cost of integrated circuits have been pursued to satisfy the never-ending demand for improved device performance. The smallest feature size in an IC surpassed the submicron dimension in the early 1980s, and Intel debuted its microprocessor that featured transistors manufactured using 14nm technology in 2015. Today's microprocessors have about a billion transistors, while a 256 GB Secure Digital (SD) memory card, which weighs less than a gram has  $10^{12}$  transistors, assuming each transistor can store two bits [6].

## 1.2 MOSFET Scaling

The electronic industry has been extremely benefiting from scaling down the dimensions of MOSFET for the last four decades. The shrinking of MOSFETs to sub-nano meter scale enables integration of the billions of the components on a small substrate area. Initially, the constant electric field scaling theory was introduced in 1974 [7]. In this theory, the scaling was done to the dimensions and voltage of the device with same scaling factor  $S$  while keeping electric field constant. Hence, the speed of device increases by a factor  $S$  and the power dissipation of the device decreases by a factor of  $S^2$ . The other major scaling is constant voltage scaling. In this theory, the operating voltage of the device is unchanged and scaling is applied to all other parameters of the device.

In 2015, International Technology Roadmap for Semiconductors (ITRS) presented that the scaling of the MOSFET more than Moore beyond CMOS technology node could

---

be a challenging task, since the planar MOSFET has already reached its scaling limited [8]. Moreover, more Moore beyond CMOS is further continuing the scaling of MOSFETs leads to high hot carrier effects (HCEs) and short channel effects (SCEs) such as subthreshold swing, drain induced barrier lowering (DIBL), threshold voltage roll-off, and interface charges[9].

### **1.2.1 Scaling challenges**

Modern devices and circuits have emerged in recent years as a result of advancements in semiconductor materials and device architecture. A lot of these become workhorses in the mainstream, albeit just a few are still in their infancy. According to the International Technology Roadmap for Semiconductors (ITRS) trends, transistor gates currently measure 14–10 nm [10-11] and are expected to get smaller to 7 nm in the upcoming years. Beyond the 20 nm technological node, the semiconductor industry faces a number of issues that need to be resolved. Reduced transistor size lead to faster switching, lower power dissipation, lower fabrication costs, and an increase in package density.

### **1.2.2 Drain-Induced Barrier Lowering (DIBL)**

The source and drain regions of a transistor get closer to one another as it is down-scaled. As a result, the potential barrier between the source and channel region is lowered, and the drain voltage begins to dominate the electrostatic potential of the channel. As a result, it raises the sub-threshold leakages, which raise the transistor's static power requirement. This result restricts transistor scaling [12].

### **1.2.3 Punch through**

A sudden increase in device current due to avalanche multiplication occurs when two depletion zones spanning the source-channel junction and drain-channel junction touch and cause the punch through effect leading to permanent damage of the device.

---

#### 1.2.4 Carrier mobility degradation

Carrier mobility is one of the most crucial elements that affects the device's present performance. Mobility is described in the definition as the relationship between drift velocity and electric field. As a result, for short channel devices, the drift velocity and ON-current performance are eventually saturated by the lateral field across the channel. Scaling causes a rise in the normal electric field, which worsens carrier mobility due to increased impurity scattering in the channel region [12-13]. To counteract current leakage, which worsens the scattering phenomena, the channel doping is enhanced for scaled devices [14].

#### 1.2.5 Threshold voltage roll-off

The electrostatic potential profile of the channel in highly scaled MOSFET designs depends on the vertical and lateral fields, which are controlled by the gate and drain voltages, respectively. Therefore, as the influence of the drain electric field on the channel increases, the gate voltage necessary for channel inversion decreases. Threshold voltage roll-off, which results in the reduction of threshold voltage, rises with channel length scaling.

### 1.3 CMOS boosters

As explained in preceding section, a major challenging task in nano-scaled CMOS scaling is eliminating the SCEs and HCEs. To suppress SCEs and HCEs, CMOS boosters are incorporated into the nano-scaled device. They are strained-silicon (s-Si), channel engineering, gate material engineering, high-k dielectric material, non-conventional MOSFET structures, etc. Some of them are illustrated below.

#### 1.3.1 Gate material engineering

Dual-Metal-Gate (DMG) structure, which is one of the notable CMOS technology boosters, was proposed by Long et al.[15]. The gate material of the DMG MOSFET

---

consists of control gate work function as  $\phi_{m1}$  and screen gate work function as  $\phi_{m2}$ , where  $\phi_{m1} > \phi_{m2}$  for n-type device, and vice versa for p-type device. Consequently, the step-equivalent curve is attained in the channel potential. When device operates in the saturation region, the channel region under control gate layer is screened from a drain to source voltage ( $V_{DS}$ ) as the channel region under screening gate layer absorbs any excess  $V_{DS}$ . Therefore, the SCEs and HCEs of the MOSFET are suppressed by employing DMG structure.

### 1.3.2 Graded channel engineering

If the doping profile in the Silicon channel decreases uniformly in a stepwise manner from the source/channel interface to the drain/channel interface then it is considered as graded channel (GC) structure [16]. By employing GC structure in the MOSFET, high threshold voltages and low SCEs are obtained. Moreover, the HCEs are also reduced due to the lower built-in potential at the drain/channel interface

### 1.3.3 High-k insulating material

In a process of scaling CMOS devices, the thickness of the dielectric material has reached 10 Angstrom. With the reduction of channel length below 32nm, the gate dielectric thickness has to be scaled down to an ultra-thin size (i.e., less than 1 nm approximately, which is equivalent to five atomic layers). This very thin dielectric layer results in a huge amount of OFF current, thereby increasing the standby power consumption. Therefore, a need of thick dielectric material is required in order to prevent electrons tunnelling through gate oxide[17] i.e the physical thickness of the dielectric material has to be high, whereas its electrical thickness has to be low. Hence, high-k dielectric materials could be one of the best solutions for the issues discussed. The effective oxide thickness of the high-k dielectric material is given as  $t_{eff} = t_{high-k}[\epsilon_{SiO2} / \epsilon_{high-k}]$ , where  $\epsilon_{SiO2}$  and  $\epsilon_{high-k}$  are permitivities of silicon dioxide material and high-k dielectric layer, respectively and  $t_{high-k}$  hickness of high-k dielectric layer.

### 1.3.4 Non-conventional MOSFETs

The multiple-gate (MuG) MOSFETs are categorized as the double gate (DG) conventional SOI MOSFET, DG non-conventional FinFET, Tri-gate MOSFET, Quadruple Gate MOSFET, surrounding gate MOSFET, and Nanowire MOSFET. The MuG-MOSFET structures can have high gate control over the silicon channel. Consequently, reduction of leakage current and SCEs of the device can be attained. Nevertheless, several process flow issues of MuG-MOSFETs must be resolved before using the MuG-MOSFETs in VLSI systems. Moreover, MuG-MOSFETs require modern fabrication methods such as enhanced etching accuracy, corner effects, reliability, and ultra-thin fin effects, etc.

## 1.4 Motivation

In nano-scaled regime, MOSFETs suffer from SCEs and HCEs. To suppress SCEs and HCEs, both DMG with GC engineering and gate stack structure are employed in DMG JL FinFET. In the light of above discussion, an effort is done to investigate the subthreshold performance of DMG JL FinFET. Moreover, the effect of various device parameters on the subthreshold characteristics of DMG JL FinFET is investigated. Besides, CMOS technology boosters like DMG with GC engineering and high-k dielectric material help to enhance ON current of DMG JL FinFET. Therefore, these techniques are employed in the DMG JL FinFET to examine their effects on subthreshold behavior of the DMG JL FinFET

1. In nano scale regime CMOS technology is suffering from SCEs like Subthreshold slope, drain induced barrier lowering and facing problem in analog and RF analysis while moving to subthreshold scaling.

2. To avoid these problems dual material gate concept is employed in FinFET to investigate the SCEs effect.

## 1.5 Problem Statement

The objective is to present a detailed simulation based study of the subthreshold characteristics of dual material gate junctionless FinFET with Gate Oxide, Work Function, and Dimensional Effect, and to analyze Analog RF and Linearity Performance.

## 1.6 Research Objectives

- Design and Optimization of Dual Material Gate Junctionless FinFET Using Dimensional Effect, Gate Oxide and Work function Engineering at 7 nm Technology Node.

- Study of DMG JL FinFET: Analog/RF Perspective at 7nm Technology Node

- Design and Temperature assessment of Analog/RF and Linearity parameters on Dual Material Gate Junctionless FinFET at 7nm Technology node for nanoscale Applications

## 1.7 Thesis Organization

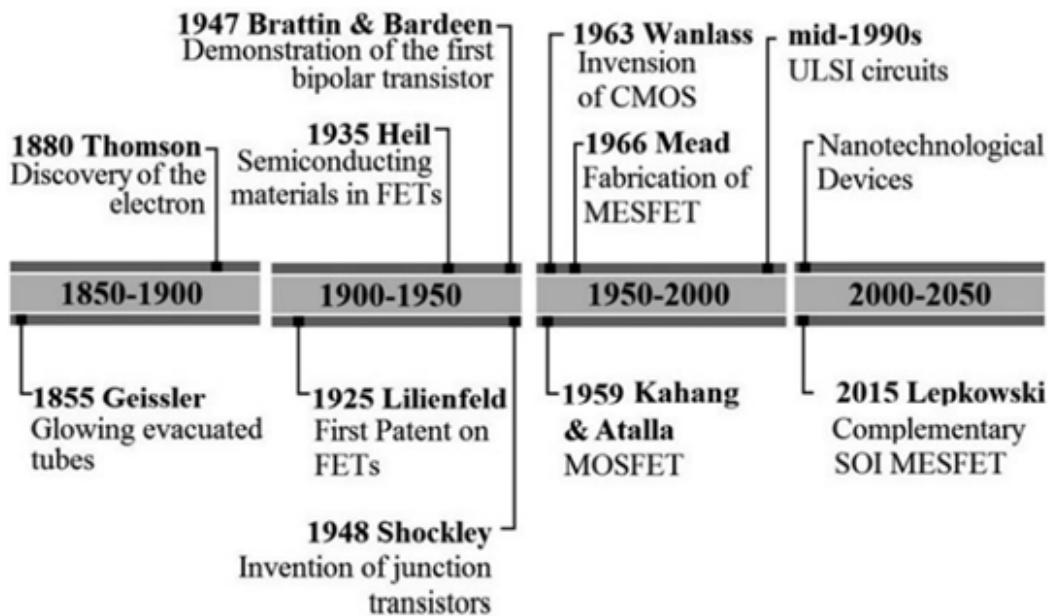

The main aim of this thesis is to demonstrate a simulation based analysis of the subthreshold performance of DMG JL FinFET with DC, Anlog and RF performance and temperature variability analysis. The thesis comprises six chapters containing the present Chapter. The contents of other chapters of the thesis are outlined as follows:

**Chapter 2** reviews the notable amount of most updated literature of the modeling and simulation of MOSFET and FinFETs with junction and junctionless and DMG JL FinFET in detail.

**Chapter 3** deals with the simulation of DMG JL FinFET with dimensional effects and evaluating the performance parameters SS, DIBL,  $I_{ON}$ ,  $I_{OFF}$ ,  $I_{ON}/I_{OFF}$ .

**Chapter 4** presents a detailed analysis of analog/RF performance DMG JL FinFET.

**Chapter 5** presents a detailed study of temperature variability analysis DMG JL FinFET with DC, analog/RF and linearity characteristics performance.

---

**Chapter 6** gives conclusions of the work done and provides direction for the upcoming work.

The thesis organization is shown in Figure 1.2

**Figure 1.2** Thesis organization in pictorial representation

# Chapter 2

## Literature Survey

### 2.1 Introduction

Very Large Scale Integration (VLSI) technology has advanced significantly over the past two decades, paving the path for a new era in human civilization. Continuous device downscaling has provided great chip density, multi-functionality, and high speed for electronic systems, as anticipated by G. Moore [18]. It is now clear that the usual scaling trend cannot last indefinitely, making it exceedingly difficult for device developers to continue improving device performance and reliability. For deeply scaled devices, generating ultra-sharp junctions proves to be a serious challenge in addition to short channel effects (SCE) degradation, which calls for the development of complex fabrication and process approaches. Recently, "Junctionless (JL) technology" a very efficient and dependable solution has been discovered. This technology is compatible with the CMOS process. This innovative idea eliminates the necessity for the source/drain (S/D) implantation phase during fabrication, relaxing the thermal budget and simplifying the fabrication process.[19–21].

The JL concept is based on a straightforward idea that was patented in 1925 by well-known physicist J. E. Lilienfeld. Numerous research groups' interest in Junctionless FETs (JL FETs) has recently been rekindled. To address current fabrication issues and SCEs, extensive research is currently being done on various JL device architectures. These include bulk junctionless transistors (JLTs)[22], Junctionless nanowire transistors (JNTs) [23], gate all around (GAA) JNTs [24], vertically stacked JNTs [25], JL FinFETs[26], JL

Tunnel FETs [27], JL Vertical slit FET (VesFETs) [28], and more. This chapter provides a thorough overview of the research work done thus far on JL devices by highlighting its potential and problems.

## 2.2 Junctionless technology beyond CMOS

Despite the fact that several device architectures have been proposed in the literature, many of them remain restricted to the theoretical realm and are not yet ready for mass production due to the complexity and cost of fabrication [14]. A brand-new idea for a Junctionless Field Effect Transistor (JL FET) has been put out in this context of device engineering [29]. J.P. Colinge and his group at Tyndall National Institute in Ireland created and described a tri-gate JL FET in 2010[20]. These special devices use ultra-thin silicon channels with homogenous doping concentration in the source, drain, and channel regions. This significantly lowers the cost of manufacture and streamlines the fabrication process [8]. An overview of the working theory and the benefits and drawbacks are provided in the following subsections.

## 2.3 Features of Junctionless technology

1. Ease of fabrication: JL FETs' very simplified device architecture is its main benefit [19]. From a manufacturing standpoint, it can be difficult to create a high-quality, ultra-shallow p-n junction at a deep nanoscale level for typical MOSFETs. It calls for a brief transition between n-type doping concentrations of the order of  $10^{19} \text{ cm}^{-3}$  and p-type doping concentrations of the order of  $10^{18} \text{ cm}^{-3}$ . This has a lot of drawbacks, including a large heat budget and pricy annealing methods [21]. JL design does away with the requirement for a S/D diffusion stage during fabrication, which naturally simplifies and lowers the cost of manufacture[26].

2. Design constraint: A high work function gate material ( $>5.0 \text{ eV}$ ) and strongly doped ultra-thin silicon sheet ( $10^{19}\text{--}10^{20} \text{ cm}^{-3}$ ) are needed for the JL device to operate well [19,20,29]. Even if the JL idea made the production process simpler, producing a material with such a high work function is difficult from a fabrication standpoint.

Additionally, it is challenging to maintain the evenly doped ultrathin silicon-on-insulator substrate.

3. Bulk conduction mechanism: JL FETs function in partial depletion mode, which differs from Inversion Mode (IM) MOSFETs in that the conduction channel forms at the bulk of the silicon film, which is separated from the surface by a depletion area. Because of this, JL FETs exhibit completely different performance than IM MOSFETs. JL FETs are less impacted by silicon/oxide interface traps because the bulk area of the device receives the majority of the charge carriers [26]. Ionized impurity scattering, however, unquestionably becomes the predominant mobility degradation mechanism that impacts the ON-current performance of JL FETs because of the high doping concentration needed in JL devices [27]. The vertical electric field at the silicon/oxide interface of the JL devices, which mostly operate in partial depletion mode [25]. Furthermore, the vertical electric field at the silicon/oxide interface is minimal since the JL devices mostly function in partial depletion mode. As a result, they are less vulnerable to BTI (Bias Temperature Instability) and reliability problems [30].

4. Improved short channel and noise behavior: The interaction between source and drain areas is reduced in the absence of depletion regions. As a result, JL FETs have a much enhanced DIBL [20]. In addition, as compared to IM MOSFETs, the bulk conduction mechanism in JL FETs minimizes the electric field at the silicon/oxide and channel/drain interfaces. As a result, the JL FETs are more resistant to the impacts of hot electrons [22]. The JL FETs also outperform MOSFETs in terms of noise performance. When compared to IM MOSFETs, JL FETs have been shown to have reduced  $1/f$  noise and Random Telegraph Noise (RTN) [31–33]. This is brought on by the JL device’s bulk channel’s low field lines, which noticeably lengthen the average time it takes to catch mobile carriers in traps, close to the gate electrode.

5. Enhanced carrier ballisticity: Without any barrier height, JL FETs offer a seamless transition from the source to the drain area. In JL FETs, the possibility of carrier back scattering is eliminated by the lack of a source to channel barrier height in the ON-state. As a result, JL devices have improved carrier ballisticity when compared to IM devices in the ON-state [34].

## 2.4 Review of various Junctionless FETs

The Lilienfeld's first transistor principle, which was proposed by Lee et al. in 2009 [29], is the foundation of the JL structure idea. Excellent switching ability and superior short channel behaviour have been reported for multi-gate JL FET in comparison to conventional multi-gate FET. Although the results were very encouraging, there was still some uncertainty regarding device variability. Later in 2010, Lee et al. [35] looked at how high temperatures affected the electrical characteristics of multi-gate JL FETs. When compared to multi-gate transistors, operating in accumulation mode (AM) or inversion mode (IM), the effect of JL FETs on threshold voltage ( $V_{TH}$ ) is shown to be two times greater. In addition, a very little decrease in channel mobility is seen in the JL device. In turn, this causes the constant increase in current drive with temperature. The defect density around the drain-channel junction is also decreased by the lack of S/D implantation, which lowers the total gate-induced drain leakage currents.

The enhanced electrical properties of JL FETs over traditional MOSFETs with gate lengths down to 20 nm have been demonstrated in several research publications that are available in the literature [22,26,36]. In the year 2010 [20], Colinge et al. of Tyndall National Institute carried out the first experimental investigation on 1 nm tri-gate JNT in response to these simulation studies. The reported long channel JL device has demonstrated full CMOS capability, good  $I_{ON}/I_{OFF}(>10^6)$ , near-ideal sub-threshold swing (SS) at room temperature (64 mV/dec), and extremely low leakage current. Additionally, JL FET has been discovered to have less mobility deterioration with temperature than IM FET. However, it has also been shown that the  $V_{TH}$  variability in JL devices is two times worse than that in IM devices. Later, Lee et al. produced short channel (50 nm) JNT using a similar process flow, and the measured findings revealed very modest SCEs (SS 60 mV/dec and DIBL 7 mV/V).

The analogue performance of JL and IM multi-gate transistors was compared by Doria et al. in 2011 [37]. They offered a physical explanation of the analogue behaviour of the JL devices as well as information on how temperature affected it. When comparing the electrical properties of JL and IM devices, it was found that the JL structure had a lower drain current, which is connected to the JLT's poor field channel mobility due to its

heavy doping. Additionally, due to heavy doping, JL devices were shown to have a more significant effect of fin width variation on early voltage ( $V_{EA} = I_D/G_D$ ) and intrinsic voltage gain ( $A_V = G_m/G_D$ ) than IM devices. However, JL FETs have demonstrated to have superior VEA and greater AV than IM devices for all fin widths evaluated. Additionally, because JL devices lack the Zero Temperature Coefficient (ZTC) point (a bias point in the IV curve at which MOSFETs cease to be temperature-dependent), they behave analogically significantly differently from IM devices.

JL FETs, in contrast to IM devices, can sustain a steady drain current across a wide temperature range. However, the JL FET's reduced bulk mobility causes its drain output conductance ( $G_D$ ) and transconductance values to be lower ( $G_m$ ). Both junction-based and JL devices showed  $G_D$  deterioration as the temperature dropped. But the temperature dependency in the JL device has been shown to be weaker than in IM FETs. As a result, the JL device has demonstrated that  $V_{EA}$  and  $A_V$  are linearly dependent on temperature. However, these IM device performance measures saturate at about 300 K. For the JL device, it was demonstrated that the performance measure  $G_m/I_{DS}$  represents the efficiency of the transistor to convert drain current into transconductance and is nearly independent of temperature (between 223 K and 473 K) in the ON-state. This is quite beneficial for many analogue applications. Of contrast to IM devices, the unity-gain frequency in JL devices was shown to be lower. As a result, JL devices may have restrictions when used to RF applications. By using highly doped S/D extension areas in JL structures, the analogue and RF performance metrics including  $G_m$ ,  $A_V$  cut off frequency, and current drivability may be further enhanced. The authors of this study did not take into account how the device's noise behaviour would be impacted by its only concentration on analogue characteristics.

The behaviour of JL devices in Low Frequency (LF) and Random Telegraph Noise (RTN) has received little attention in recent years [31–33,38]. According to a 2011 study by Nazarov et al. [31], the JL structure has a lesser RTN amplitude than IM devices. This is based on by the JL FET's bulk channel's low field lines, which noticeably lengthen the average time it takes for mobile carriers to be captured in traps close to the gate electrode. The JL multi-gate structure's LF noise behaviour was studied by Jang et al. the same year [33]. The findings showed that, in spite of the bulk conduction mechanism, the

Carrier Number Fluctuation (CNF) model provides a satisfactory explanation for the LF noise behaviour of the JL structure. The two types of noise sources that the CNF model is concerned with are: the first is variations in channel thickness brought on by a reduction in depletion width during partial depletion mode operation and the second is variations in carrier concentration at the silicon-oxide interface during accumulation mode operation. The JL devices' extracted trap density was observed to be nearly identical to IM devices. Degraded channel mobility caused by increased ionized-impurity scattering becomes a severe concern since the JL devices need a high doping concentration for effective device functioning. Lou et al. [39] have proven the JL structure with dual material gate (DMG) to enhance mobility degradation. They suggested a design, with two gates made of materials, with various work functions. According to reports, the usage of DMG was more successful in reducing the hot carrier effect and SCEs. Additionally, it has been demonstrated that DMG structures have lower  $G_m$  below  $V_{TH}$  and greater  $G_m$  in the ON-state compared to traditional single material gate JL structures, which is extremely helpful for quicker turn-off and higher ON-state speeds of the electronics devices.

The maximum oscillation frequency ( $f_{max}$ ) and unity-gain cutoff frequency ( $f_T$ ) may both be increased with the suggested structure while maintaining low gate bias, which is advantageous for high frequency applications. The optimization of numerous physical parameters, such as the size of two separate gate materials and their respective work functions, is necessary for such a structure. In several recent papers, Band To Band Tunneling (BTBT) between the drain and channel regions, which causes the parasitic bipolar junction effect in JL devices and considerably raises the OFF-state leakage current to an unbearable level, was also raised as a serious issue [40,41]. Additionally, the performance of the BTBT current was examined for the DMG structure [42]. By using DMG design in JNT, it was discovered that OFF state current may be enhanced by approximately two orders of magnitude. Although the exhibited results showed the DMG structure's great potential, it is highly difficult and demanding to produce DMG structures at the nanoscale size. Therefore, to lessen the complexity associated in the construction of DMG structures, new fabrication technologies must be developed. For the first time, Gnudi et al. evaluated the  $V_{TH}$  variability of JL devices [43]. Under the assumption of constant mobility, they developed an analytical model for  $V_{TH}$  variability in JL cylindrical silicon

nanowire (SiNW) and planar DG transistors. In highly scaled 20 nm JL SiNW FETs, it has been demonstrated that discrete dopant variations may induce  $V_{TH}$  variability to reach roughly 115 mV.

In JL devices, discrete dopant variation has become a significant issue. They did not, however, investigate the JL transistor's drain current variability or the effects of other causes of variability. Aldegunde et al. used 3D non-equilibrium Green's function simulations in 2012 to analyse the variability of the JL GAA SiNW transistor [44]. Along with  $V_{TH}$ , they also took into account  $I_{OFF}$ ,  $I_{ON}$ , and SS variation brought on by random dopant fluctuations (RDF). It has been noted that JL structure exhibits more sub-threshold variability than their IM counterparts. Later, using the Impedance Field Method (IFM), Giusi et al. examined the fluctuation of the drain current caused by RDF in the JL DG structure [45]. They claimed that compared to the OFF regime, the current dispersion in the ON regime is significantly smaller. Additionally, it has been discovered that scaling—caused by rising SCEs—increases the variability of both the current and the  $V_{TH}$ . Additionally, they have created a mathematical link between the unpredictability of drain current and  $V_{TH}$  variability, also takes into account SCE and carrier degeneration corrections. They did, however, presuppose that RDF is the only source of variability.

The simulation analysis was carried out in 2013 by Parihar et al. to evaluate the potential of DG JLTs for ultra-low power (ULP) applications [46]. According to reports, DG JL devices can perform better than traditional DG MOSFETs in ULP (ultra-low power) applications. They also demonstrated that the JL device had the lowest sensitivity to gate length and the highest sensitivity to doping concentration. It has been suggested that using JL devices will make exact  $V_{TH}$  matching challenging. Choi et al. [47] also published a comparable study for the GAA JL structure. The GAA JL device has been discovered to be more vulnerable to  $V_{TH}$  variations brought on by width change than its IM equivalents. A modified JLT structure with moderate doping ( $10^{18} \text{ cm}^{-3}$ ) in the channel was proposed by Parihar et al. in 2014 [48]. Improved sub-threshold features have been seen in the simulation findings, however simultaneously, current performance is also impacted. They also noted a reduction in gate work function requirements and an improvement in  $V_{TH}$  variability (between 70% to 90%). The disadvantage of lowering channel doping is surface roughness scattering, which happens as a result of the silicon

body's conduction channel moving from the bulk area to the surface (accumulation mode), and a reduced drive current, which restricts its use to the ultra-low power domain.

In order to address the  $V_{TH}$  variability and impact ionization issue of heavily doped JL FET, Sahu et al. evaluated the performance of doping-less JLT in 2014 [49]. It has been discovered that undoped silicon channel JLTs are more resistant to RDF and process fluctuations. Additionally, the channel mobility has been much enhanced. The contact characteristics of metal/undoped-silicon must be difficult to manage throughout the production of doping-less JLT, nevertheless. In order to improve JL FET's current performance, materials other than silicon channel material have also been investigated. Germanium (Ge), a high mobility channel material, has the following significant flaws:

- 1) It is challenging to manufacture high-quality gate oxide ( $\text{GeO}_2$ );

- 2) there is more tunneling leakage because the direct bandgap is narrower; and

- 3) low resistance contacts can emerge on n-type Ge substrates.

However, in the case of the JL structure, it is anticipated that oxide tunnelling, surface imperfections, and gate oxide thickness will have less of an impact on carrier transport dynamics. The effectiveness of multi-gate Ge JNTs was assessed by Yu et al. [50]. The findings showed that the Ge bulk JNT offered competitive ON-state current similar to its counterparts, simpler production, and enhanced electrostatic gate control. Bulk Ge JNT exhibit a little deterioration in gate control when compared to silicon, but an increase in ON-current performance is more important for enhancing gate responsiveness. Guo et al. [51] have also investigated Indium Gallium Arsenide, another high mobility material. The results of the experimental measurements have demonstrated good electrical properties for the suggested device design and the efficiency of the Indium Gallium Arsenide channel in lowering external resistance and therefore boosting driving current. Song et al. experimentally proved the effectiveness of III-V JNT in 2014 [52]. In order to prevent mobility deterioration and produce low S/D resistance, the device used in their study was constructed using an implantation-free method in which the S/D area was grown again, using Metal Organic Chemical Vapor Deposition (MOCVD).

In the III-IV JNT structure, high linearity has been reported with minimal bias dependency. This indicated that it was a good candidate for low power, high linearity

RF applications. Several analytical models for better understanding JL FETs' electrical behaviour have been presented in the literature. In the recent years, a number of analytical methods have been put out to address the channel potential distribution among JL DG FETs, including the variable separation methodology [53,54], parabolic approximation [55,56], Schwarz-Christoffel transformation [57], and series expansion method [58]. Asymmetric DG JL structures have also been modelled by Jin et al. [53,59] and Jazaeri et al. [60]. Using the conformal mapping approach, Kumari et al. published an enhanced 2D analytical model for DG JL FETs in 2015 [61]. The source and drain regions were assumed to be completely isolated when the concept was introduced.i.e., when the simulation is going on to focus mainly on channel region source and drain regions are kept in isolate position. Trevisoli et al. devoted their studies towards modeling JNTs [62,63] The drain current model for tri-gate JNTs was put out in[62] . For long channel devices, they solved the 2D Poisson equation to get the surface potential distribution, which was then utilized to calculate the charge density along the channel and the drain current. The 3D Laplace equation solution has been added to the 2D model, which also takes into account the effects of SCEs. They suggested a method to extract the  $V_{TH}$  of JNT and a physically based definition for it in [64]. On the basis of the same concept, an analytical model for the  $V_{TH}$  has also been created. The proposed methodology, however, was only applicable to long channel devices.

An intriguing investigation of planar SOI JLTs with non-uniform vertical channel doping was conducted by Mondal et al. [65]. This improved structure has been seen as being closer to a real-world device where the vertical distribution of impurities implanted with ions is not uniform. And the Gaussian distribution function has been used to describe this non-uniformity in the doping profile. The suggested structure improves leakage current, increasing  $I_{ON}/I_{OFF}$  ratio. The same group later conducted a similar study for non-planar structure in 2015 [66]. However, the Gaussian factors, namely segregation length ( $\sigma$ ) and projection range (RP), on which the doping distribution depends heavily, were not taken into account in any of the publications.

The effect of temperature on the DC and AC performance of DG JL FETs with vertical Gaussian doping profiles at temperatures between 200 K and 400 K was examined by B. Singh et al. in 2016 [67]. It has been demonstrated that the ON-state current

increases approximately linearly with temperature whereas the OFF current of the suggested structure significantly reduces at 200 K in contrast to a uniformly doped structure. Additionally, it was discovered that between 200 K and 400 K, the influence of temperature on SCEs such as threshold voltage roll off, subthreshold swing, and DIBL of Gaussian doped DG JL FETs was less pronounced than that of their uniformly doped counterparts. At all temperatures, the suggested structure was also shown to perform better in terms of AC performance parameters such as total gate capacitance, transconductance, transconductance generation efficiency, and cutoff frequency.

In a recent study, Ferhati et al. [68] looked at the durability of Gaussian-doped DG JL MOSFETs against Self Heating Effects (SHEs). According to reports, the Gaussian profile has a significant impact on the  $I_{ON}/I_{OFF}$  ratio, the device immunity to SHEs, and the lattice temperature. This suggested design has demonstrated to have a greater capacity to close the gap between high electrical performances and higher device dependability, making it a potential replacement for dependable nano electronic applications. For the first time, B. Singh et al. established an analytical 2D model for channel potential and  $V_{TH}$  of DG JL FETs with vertical Gaussian doping distribution [69], in consideration of the benefits provided by Gaussian doped structure.

The 2D Poisson equation was solved using the evanescent mode analysis, and the electrostatic potential distribution throughout the channel was obtained. Instead of using a true non-analytic Gaussian function, they used a Gaussian-like function to make the derivation simpler. Additionally, they ignored the source/drain (S/D) depletion width by assuming the S/D length to be zero, which undoubtedly produced incorrect results for devices with shorter gate lengths.

Later, utilizing the superposition approach, Kumari et al. provided an analytical model of Gaussian doped DG JL FETs taking into account the S/D area [70]. The suggested model, however, was predicated on the supposition that the S/D area was entirely depleted, which is not necessarily true. They have also demonstrated how altering non-uniform doping profile parameters may optimize the leakage current and SCEs in DG JL FETs.

## 2.5 Review of various Dual Material Gate Junctionless FETs

In [15], W. Long et al. suggested Dual material gate (DMG) FETs as a general new form of field effect transistor (FET). The threshold voltage near the source is higher than that near the drain in this innovative gate arrangement because of the material work function difference (for n-channel FETs, the opposite is true for p-channel FETs). Charge carriers consequently move more quickly through the channel, and a screening effect is created to lessen short-channel effects. The theory, computer simulation findings, design recommendations, processing, and characterization of the DMGFET are thoroughly presented using the hetero structure FET as a vehicle.

In [71] Wei Long et al. the dual material gate field effect transistor (DMGFET), a brand-new category of device, is introduced. Two laterally contacting materials with various work functions make up the DMGFET's gate. In order to accelerate charge carriers in the channel more quickly and decrease short channel effects, this new gate construction takes use of the difference in material work functions by making the threshold voltage near the source more positive than that near the drain.

In [72], G. Venkateshwar Reddy et al, describe the special characteristics of a modified asymmetrical double-gate (DG) silicon-on-insulator (SOI) MOSFET. The front gate is made of two different materials, unlike the asymmetrical DG SOI MOSFET, which has a similar structure. When compared to the DG SOI MOSFET, the improved structure that is the dual-material double-gate (DMDG) SOI MOSFET displays much less short-channel effects (SCEs). This structure's SCEs have been investigated through the development of an analytical model. The surface potential, electric field, threshold voltage, and drain-induced barrier lowering are all calculated using the model. Also included is a model for the voltage gain, drain conductance, transconductance, and current drain.

The perceptible step in the surface-potential profile, which filters the drain potential, is observed to inhibit SCEs in this configuration. Demonstrated that, in comparison to the DG structure, the DMDG structure offers a simultaneous gain in transconductance and a drop in the drain conductance. To check the correctness of the analytical model, the results acquired via two-dimensional simulation are compared with those predicted by the model. In [73]. T. K. Chiang et al. a new two-dimensional model for asymmetrical dual

gate material double-gate (ADMDG) MOSFETs has been created, which includes surface channel potential, subthreshold swing, and threshold voltage. The simulation results that closely match those of the two-dimensional numerical simulator serve as proof that the model is accurate. The model offers fundamental ADMDG MOSFET designing guidelines in addition to providing physical insight into device physics.

In [74], T. K. Chiang et al. A novel two-dimensional model including channel potential, threshold voltage, and subthreshold swing for the dual material surrounding-gate (DMSG) MOSFETs is successfully created on the basis of the solution of the two-dimensional Poisson's equation. The simulation results that closely match those of the two-dimensional numerical simulator serve as proof that the model is accurate. The model offers fundamental designing guidelines for the DMSG MOSFETs in addition to providing physical insight into device physics.

In [75], Ravneet Kaur et al. suggested Dual Material Gate Insulated Shallow Extension Gate Stack (DMG ISEGaS) MOSFET structural design, combining the integration of Dielectric Pocket (DP) and Dual Material Gate (DMG) onto the traditional MOSFET which has been researched for increasing the analogue performance of scaled MOS devices. According to simulation studies, dual material gate engineering improves the analogue performance of the design in terms of intrinsic gain ( $g_m/g_d$ ), early voltage ( $V_{EA}$ ), and  $g_m/i_d$ .

In [76], Muhammad Mustafa Hussain et al. the integration complexity has been addressed for the first time by integrating a group of complementary metal oxide semiconductor (CMOS) FinFET devices with two separate high-k/metal gate stacks with dual work function on the same wafer. In a procedure that also involves dual metal gate etching and gate stack integration, two entirely distinct metals that were created by atomic layer deposition have been combined. With reasonably symmetric  $V_{TH}$ , excellent short channel characteristics with minimal drain induced barrier lowering (DIBL) and subthreshold swing SS have been seen.

In [77], Pedram Razavi et al. using two-dimensional (2-D) simulation, the short channel effects of a modified symmetric double-gate MOSFET made of dual material gates and an oxide stack with high-k material on top of a SiO<sub>2</sub> layer were evaluated and compared to those of a standard symmetric double-gate MOSFET. Comparing this

---

structure to the traditional double-gate MOSFET, it has improved current characteristics and decreases short channel effects (SCEs) such as drain-induced barrier lowering (DIBL), the hot electron effect, and threshold voltage roll-off.

In [78], R. S. Saxena et al. presented a new dual-material-gate-trench power MOSFET which shows a notable increase in transconductance and breakdown voltage without suffering any on-resistance deterioration. The gate of a typical trench MOSFET is divided into two pieces, in this arrangement for work-function engineering. The inversion charge in the channel is shared between the two gates. The device performance was demonstrated using 2-D numerical simulation by changing the lengths of the two gates to permit an equal proportion of the inversion charge. The peak transconductance and breakdown voltage of the novel device improved by around 44% and 20%, respectively, in comparison to the traditional trench MOSFET, respectively, by employing N+ poly-Si as a lower gate material and P+ poly-Si as an upper gate material.

In [79], the advantages of double-gate and dual-material-gate architectures are combined and proposed a dual-material double-gate (DMDG) silicon-on-insulator (SOI) metal-oxide-semiconductor field-effect transistor (MOSFET) for sub-100 nm devices. The alignment of the top and bottom gates, which has a significant impact on the performance of the DMDG-MOSFET, is one of the main problems. In this, the consequences of gate misalignment in the DMDG SOI n-MOSFET were examined. The impacts of gate misalignment on device performance, such as surface potential, electric field, threshold voltage, subthreshold slope, drain-induced barrier lowering, drain current, and transconductance, have been examined in this respect through analytical modelling and in-depth simulations. Both source and drain side misalignments have been considered since gate misalignment can happen on any side of the gate.

In [80], for the advanced nanoscale technology, a novel device configuration known as the dual-material gate SOI MOSFET (DMG SOI MOSFET) is proposed to prevent drain-induced barrier lowering (DIBL) and the short-channel effects (SCEs). Analyzing the electrical properties, the analytical threshold voltage model of the innovative structural device is proposed. Compared to the traditional SOI MOSFET, the DMG SOI MOSFET with high-k dielectric performs better in suppressing DIBL and improving carrier transport efficiency. The DIBL decreases as the dielectric constant rises. The

---

analytical threshold voltage model and the two-dimensional device simulations have a fair level of agreement.

In [81], explore in 16nm MOSFET devices, the dual material gate (DMG) and inverse DMG devices are used to reduce characteristics variation brought on by random dopant fluctuation (RDF). Researchers have looked at and examined the physical mechanisms used by DMG devices to inhibit RDF. DMG has improved by 28%, 12.3%, and 59% for controlling the RDF-induced  $V_{TH}$ ,  $I_{ON}$ , and  $I_{OFF}$  fluctuation, respectively. In [82], examines four common instances of how to reduce short-channel effects using dual-material gate MOSFETs. The double doping gate (DDG) Lightly-doped-Drain (LDD) MOSFET is then introduced as a unique device construction. This new gate design makes use of the material work function. A 2-D device simulator called MEDICI is used to mimic the model. The simulation's outcome demonstrates that by varying the polysilicon's doping concentration, a suitable threshold voltage may be obtained. In the meanwhile, the driving capability has been significantly increased over that of a normal MOSFET. The construction procedure is not difficult and is currently readily accomplished.

In [39], It is suggested to use a dual-material-gate junctionless nanowire transistor (DMG-JNT). Using 3-D numerical simulations, its characteristics are shown and contrasted with a typical single-material-gate JNT. The findings demonstrate that the DMG-JNT has several advantageous characteristics, including a high ON-state current, a high  $I_{ON}/I_{OFF}$  current ratio, improved transconductance  $g_m$ , a high unity-gain frequency  $f_T$ , a high maximum oscillation frequency  $f_{max}$ , and a reduced drain-induced barrier lowering. The consequences of various work-function disparities between the two gates and various control gate ratios are investigated. Finally, the work-function difference optimization for the DMG-JNT is shown.

In [83], the superiority of silicon-on-nothing (SON) over silicon-on-insulator MOSFET is established analytically due to SON's greater resistance to various short-channel effects and enhanced current driving capacity. Additionally, it has been demonstrated that the analytical model accords with a variety of simulation findings from MEDICI, ATLAS 2-D, and other sources. Classical models are insufficient to effectively predict the potential profile, threshold voltage, or charge inversion events for dual-material double-gate (DMDG) SON MOSFETs due to the ultrathin device structure. Under the dual-material

front gate, the 2-D Poisson and 1-D Schrodinger equations have been solved to determine the overall potential and inversion charge profile. Calculated and combined with the classical threshold voltage to produce its quantum equivalent is the quantum threshold voltage's variation from the classical one. Additionally, the suggested model has been examined using the numerical device simulator ATLAS 2-D.

In [84], performed a simulation investigation of the performance characteristics of an analogue circuit for a symmetric double-gate junctionless transistor (DGJLT) employing a dual-material gate and high-k spacer dielectric (DMG-SP) on both sides of the device's gate oxides. The parameters are illustrated and contrasted with single-material (conventional) gate (SMG) and DMG DGJLT. In comparison to the SMG DGJLT, the DMG DGJLT offers better intrinsic gain ( $G_m/R_o$ ), early voltage ( $V_{EA}$ ), and transconductance ( $g_m$ ). The high-k spacer boosts the fringing electric fields through the spacer, significantly enhancing the values for DMG-SP DGJLT.

In [85], It is suggested to use a bulk-FinFET with a dual material gate, or DMG-Bulk-FinFET. Using 3-D simulations, its features are contrasted with those of the typical bulk-FinFET. It is shown that the novel structure possesses characteristics that inhibit short channel effects, enhance transconductance, and increase carrier transport effectiveness. Additionally, the work function differential and gate length ratio may be engineered to enhance these aspects. This paper proposes an optimization plan for the DMG structure and demonstrates how the DMG-Bulk-FinFET performs better than its predecessor with a single material gate.

In [86], presented the asymmetric dual material (DM) junctionless double gate transistor 2-D drain current model. Transconductance and its higher order derivatives are computed based on channel potential and validated using the output of the ATLAS 3-D device simulator. The created model may be used to examine how well the device performs digitally in terms of the nMOS inverter circuit's voltage transfer characteristics. Analog performance and the length of the control gate studied. Through thorough circuit modelling, the results further demonstrate the benefit of the DM gate over the single material gate for digital and analogue applications employing CMOS inverters and common source amplifiers.

In [87], in the subthreshold region of operation, the analogue performance of 100

nm dual-material gate complementary metal oxide semiconductor (DMG CMOS) devices is presented. With the aid of thorough device simulations, the analogue performance parameters for the DMG nMOS (metal oxide semiconductor) devices transconductance  $g_m$ , transconductance generation factor  $g_m / I_D$ , Early voltage  $V_{EA}$ , output resistance  $R_o$ , and intrinsic gain as well as  $V_{EA}$  and  $R_o$  for the DMG pMOS devices are systematically investigated. Study is also done on how various capacitances affect the unity-gain frequency  $f_T$ . It is discovered that the DMG CMOS devices perform noticeably better than their single-material gate (SMG) equivalents. When DMG is utilized for both the n- and p-channel devices, a voltage gain enhancement of more than 70% is shown for the CMOS amplifier.

In [88], It is suggested to use a dual material gate silicon on insulator junctionless transistor (DMG SOI JLT). Using simulation tools from EDA, its properties are shown and contrasted with those of a single Material gate Silicon-On-Insulator Junctionless Transistor (SMG SOI JLT). The outcome demonstrates that the single Material Gate Silicon on Insulator Junctionless Transistor cannot drive as much current as the DMG-SOI JLT. The transition of two gates is abruptly altered by the potential distribution of DMG SOI JLT, which also strengthens the electric field in the channel. In comparison to SMG SOI JLT, when the channel length reduces, DIBL and sub threshold slope change is less in DMG SOI JLT. SMG SOI JLT transconductance is 0.25mS for a channel length of 20nm.