**DEVELOPMENT OF QUASI Z-SOURCE BASED

MULTILEVEL INVERTERS FOR PHOTOVOLTAIC

APPLICATIONS WITH LOW LEAKAGE CURRENT**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**Doctor of Philosophy**

in

**Electrical Engineering**

**By**

**Chinmay Kumar Das**

**(Roll no. 719033)**

**Supervisor**

**Dr. A. Kirubakaran**

**Associate Professor**

**Department of Electrical Engineering

National Institute of Technology Warangal

Warangal, Telangana, India – 506004

October – 2022**

## **APPROVAL SHEET**

This Dissertation Work entitled **Development of Quasi Z-Source based Multilevel Inverters for Photovoltaic Applications with Low Leakage Current** by **Chinmay Kumar Das** is approved for the degree of Doctor of Philosophy.

### **Examiners**

---

---

---

### **Supervisor**

**Dr. A. Kirubakaran**

Associate Professor

EED, NIT Warangal

### **Chairman**

**Dr. N. Vishwanathan**

Professor

EED, NIT Warangal

**Date:** - \_\_\_\_\_

**Department of Electrical Engineering

National Institute of Technology Warangal

Warangal, Telangana, India – 506004

October – 2022**

**CERTIFICATE**

This is to certify that the work presented in the thesis entitled **Development of Quasi Z-Source based Multilevel Inverters for Photovoltaic Applications with Low Leakage Current** which is being submitted by **Chinmay Kumar Das (Roll no. 719033)**, is a bonafide work submitted to National Institute of Technology Warangal in partial fulfilment of the requirement for the award of the degree Doctor of Philosophy in Department of Electrical Engineering. To best of my knowledge the work incorporated in this thesis has not been submitted elsewhere for award of any degree.

**Dr. A. Kirubakaran**

(Supervisor)

Associate Professor

Department of Electrical Engineering

National Institute of Technology

Warangal-506004

Date: -

Place: - NIT, Warangal

## **DECLARATION**

This is to certify that the work presented in the thesis entitled **Development of Quasi Z-Source based Multilevel Inverters for Photovoltaic Applications with Low Leakage Current** is a bonafide work done by me under the supervision of **Dr. A. Kirubakaran**, Associate Professor, Department of Electrical Engineering National Institute of Technology Warangal and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

---

Chinmay Kumar Das

(Roll No. 719033)

Date: -

Place: - Warangal

## **ACKNOWLEDGEMENTS**

The research work and the current thesis are outcomes of constant inspiration and help from a number of persons at various spheres of my association. I would like to convey my most sincere recognition to each and every one for their respective assists.

At the onset, I would like to convey my heartfelt gratitude and deepest regards to my thesis supervisor, **Dr. A. Kirubakaran**, Associate Professor, Department of Electrical Engineering for their valuable guidance, advice, encouragement and warm support at every step of my doctoral program. I do consider myself very lucky for working under such helpful gentle person.

I am very thankful to **Prof. M. Sailaja Kumari** Head, Department of Electrical Engineering for her constant support and encouragement.

I take this immense pleasure to thank all my Doctoral Scrutiny Committee Members **Dr. N. Viswanathan**, Chairman and Professor, Department of Electrical Engineering, **Dr. V.T. Somasekhar**, Professor, Department of Electrical Engineering, **Dr. A.V. Giridhar**, Associate Professor, Department of Electrical Engineering and **Dr. P. Muthu**, Associate Professor, Department of Mathematics for their detailed review, constructive suggestions and excellent advice during this research work.

I wish to express the gratitude to SERB for utilizing facilitates to carry out a part of research work under EMR project grant 2016/007811.

I wish to express my sincere thanks to **Prof. N.V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

I am grateful to my contemporary research scholars Dr. Jammy Ramesh Rahul, Dr. T. Abhilash, Dr. K. Sateesh Kumar, Mr. Hemasundar, Mr. S. Madhu Babu, Mr. Sumon Dhara, Mr. P. Hemakumar, Mr. P. Manoj, Mr. Ajit Kumar Mohanty, Mr. C.R. Arun Kumar, Mr. V. Vijay, Mr. K. Ashok Kumar, Mr. M.F. Baba, Mrs. Pavathy M. L., Mr. Sandip Khobragade, Dr. Pritam Das, Mr. Abhishek Kumar, Mr. A. Dinesh Kumar, Mr. P. Rajnikant, Mr. Debanjan Pathak and Mrs. Soumyashree Dixit Pathak for their constant support during my journey.

I acknowledge special thanks to my friends Miss Nikita Seth, Mr. Aniket Mohanty, Mrs. Priyanka Choudhury, Mr. Avinash Ashish, Mrs. Debashrita Nayak Mr. Ankit

Panda, Mr. Ram Shankar Mohapatro, Mr. Rupak Mahapatra, Mr. Bramheswar Das, Mr. Swarup Sampad Rout, Mr. Raj Kumar Upadhyaya, and Mr. Anmol Mohanty for rendering constant encouragement and moral support throughout my life, without which research work would not have been possible. I heartily acknowledge their love and affection towards me.

My parents **Shri. Chandi Tridev Prasana Kumar Das** and **Smt. Sibashri Das**, my grandparents **Late Shri. Gopinath Das**, **Late Smt. Hiramani Das**, **Late Shri. Rabindra Nath Mohanty** and **Smt. Nihar Nalini Mohanty**, my uncle **Mr. Sibasish Mohanty** and aunt **Smt. Samhitashree Mohanty** deserve special mention for their inseparable support and prayers. They are the persons who show me the joy of intellectual pursuit ever since I was a child. I thank them for sincerely bringing up me with care and love. I would like to thank my sister **Miss Tanmayee Das**, **Miss Swayamshree Mohanty** and relatives for their unconditional love, patience and support during my study.

Above all it is the blessings of the **Almighty** to have rendered the much-needed knowledge and strength which helped me to complete this mammoth work on time.

**Chinmay Kumar Das**

**GD**

## ABSTRACT

---

---

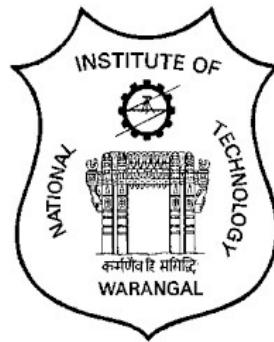

Contemporary research is directed towards the promotion of Renewable Energy Sources (RES) to counter the harmful effects of fossil fuels. Solar Photovoltaic (PV), Wind, and Fuel cell are some of the popular RESs to generate clean power. PV power has seen a huge growth in terms of installation capacity in the last decade due to availability and decreasing production cost. With a worldwide installed capacity of 710GW and having a growth rate of 24% in 2021, it is poised to become the major source of energy in the foreseeable future. However, the main drawback of PV systems is that they produce DC power, requiring a power conversion system to convert it into AC form, either to be consumed in standalone networks or to inject generated power into the grid. Therefore, development of power electronic interface plays a vital role for standalone/grid connected photovoltaic operations.

This is achieved by traditional two-level inverters either with direct DC/AC single-stage operation or in combination of front-end DC/DC boost converter cascaded with DC/AC inverter i.e., two-stage operations for PV applications. Contemporary, multilevel inverters (MLIs) have often accomplished this objective in the past few decades due to (1) operability of high DC input voltages with power semiconductor switching devices of low-voltage ratings, (2) low total harmonic distortion in the output voltage, (3) low filter requirements for grid interfacing, and (4) lower electromagnetic interference. Numerous topologies have been reported in the literature pertaining to MLIs of which generic topologies of MLI's are mainly divided into three categories, namely: (a) neutral point clamped (NPC-MLI), (b) flying capacitor (FC-MLI), and (c) cascaded H-bridge (CHB-MLI); the rest of the topologies are derived from three basic configurations. All of these inverters have a common drawback in that, they all belong to the "buck" category. Consequently, they require a large number of PV panels to be connected in series and parallel to obtain the required power at the required voltage level. In the past, two-stage topologies have been suggested to circumvent this problem. These systems display a good maximum power point tracking (MPPT) capability due the availability of an additional DC/DC boost converter. The other attractive features of the two-stage systems include reactive power capability, lower leakage current, constant common mode voltage (CMV) and unity power factor (UPF) grid current control. However, the demerits of these systems are low reliability, less efficiency and increased complexity.

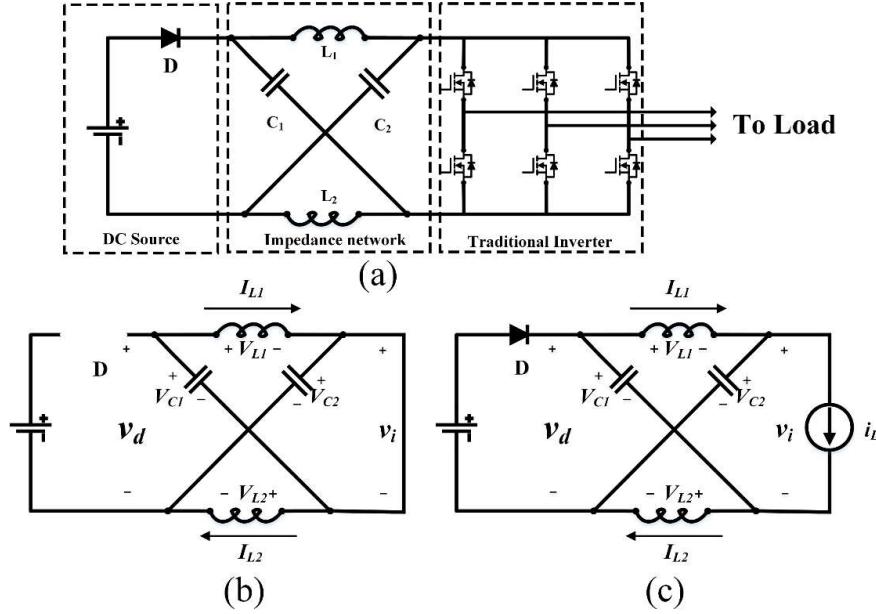

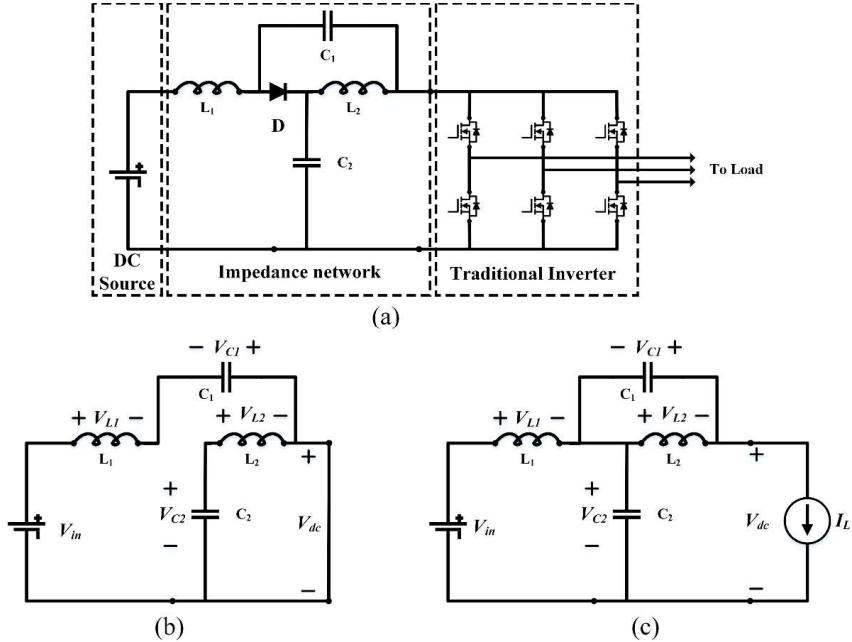

To address the above-said issue, single-stage boosting and inverting (SSBI) system are becoming popular in PV power systems. A Z-source inverter acts as an SSBI that performs boosting and inverting in a single stage. A Z-source (ZS) is an impedance network, which is constituted by the combination of inductors and capacitors. Conventional Z-sources are not suitable for PV applications as they suffer from the problem of discontinuous input current. A quasi-Z source (qZS) network is an improved version of the Z-source network, which provides an inductor after the input source, resulting in continuous input current, ease of integration of RES and low component ratings. Therefore, one might expect they inherit both the merits of qZSs and MLIs for PV applications.

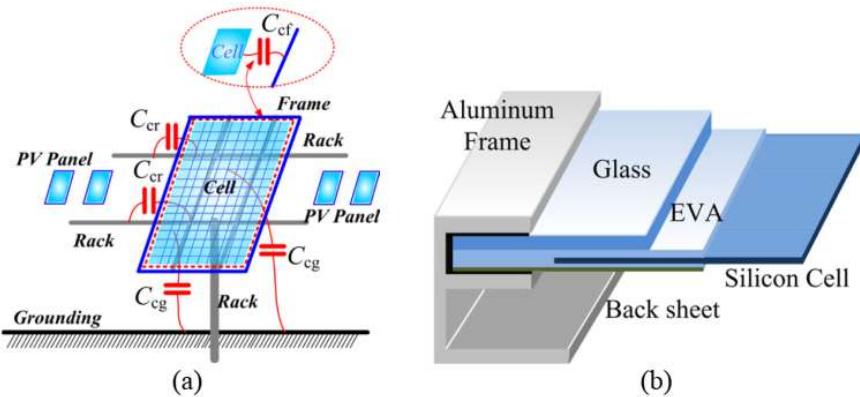

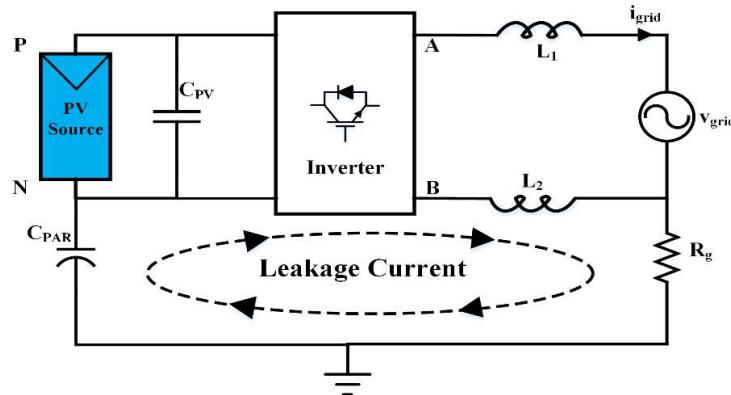

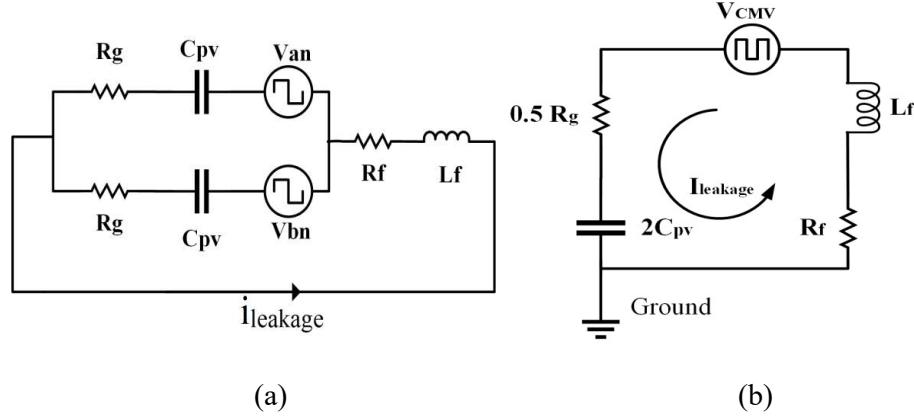

Suppression of the leakage current is one of the important requirements while connecting an RES to the grid. The leakage current is principally caused by the time-variant nature of the CMV across the load terminals with respect to source ground. The conventional approach to avoid the leakage current is to provide galvanic isolation (by using a transformer either on the low-frequency side or on the high-frequency side) between the RES and the grid. Placing an isolation transformer on the AC-side would invite drawbacks of increased cost, increased volume, and reduced efficiency. This short coming may be addressed by designing a system, which places a high frequency transformer (HFT) on the DC-side. Even though PV systems with DC-side HFTs achieve lower volumes, they still demand improvements in aspects of efficiency and cost.

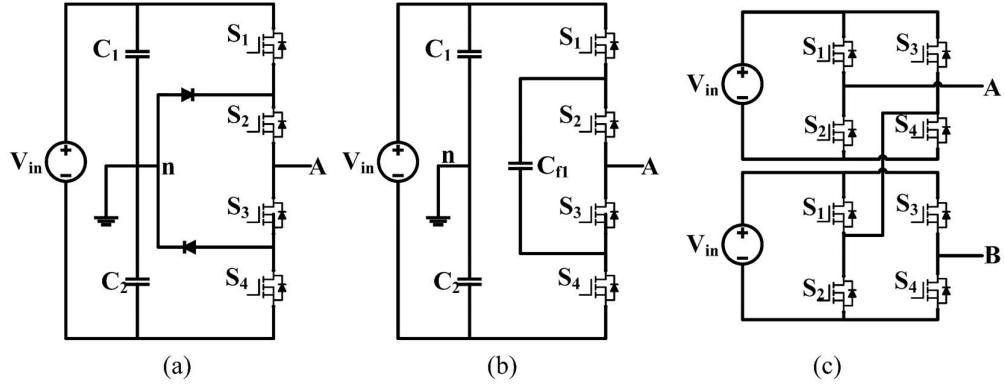

Thus, this situation encourages pushing research towards the development of transformerless PV inverters, which aims to reduce size, cost, and leakage current while improving efficiency. However, the removal of transformer causes direct contact between PV panels and grid. A resonant circuit is formed due to parasitic capacitance of PV panels, filter inductors and grid impedances. The aforesaid fluctuation in CMV excites the resonant circuit and cause flow of leakage current from the grid to PV panels via parasitic capacitances. This is achieved by 1) separation of AC and DC sides, 2) connecting the grid neutral to negative terminal of the input, and 3) connecting the midpoint of the DC-link to the grid neutral. These methods were used either to make the CMV constant or allow only a slow (i.e., low frequency) variation in it to reduce the leakage current. The non galvanic isolation techniques are primarily categorized based on 1) the carrier, 2) topology, and 3) modulation technique. Moreover, considerable research works has been carried out in the area of transformerless inverters for single-phase PV applications.

Several new circuit topologies and modulation schemes have been explored to suppress leakage current. However, most of the PV systems described are two-stage systems, which are complex and loss incurring.

Hence, there is wide scope for further research in the area of transformerless single phase quasi Z-Source based Multilevel Inverters for PV applications. Moreover, to address the aforesaid issues, namely (a) operability with a single source, (b) single-stage boosting and inverting, (c) reduced switch count, (d) improved efficiency, (e) reactive power capability and (f) reduced leakage current, this research focuses on the development of single-phase qZS based MLI topologies for stand-alone/grid-connected PV applications. In this context, three new configurations have been proposed in this thesis.

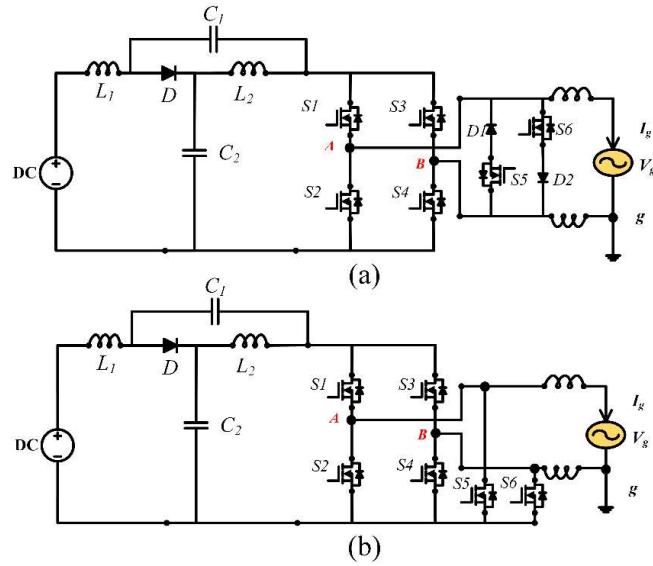

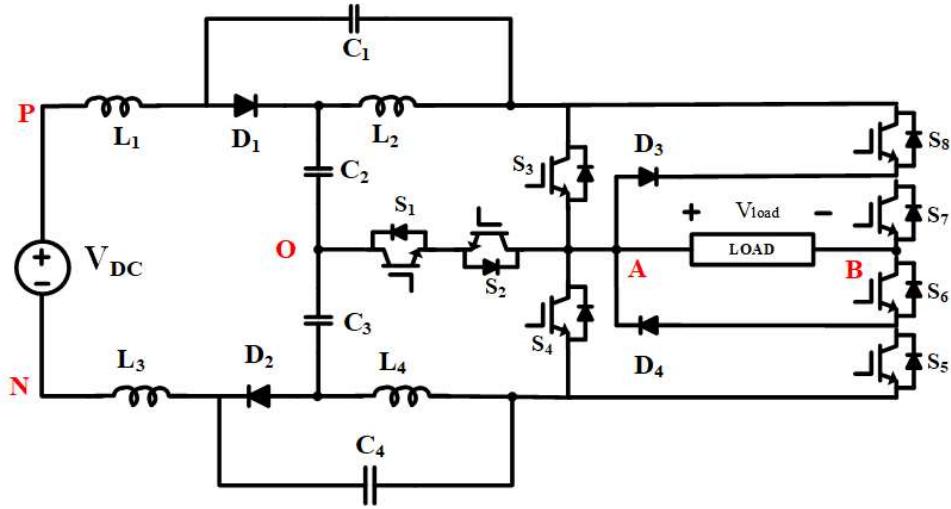

In the first proposal, a quasi Z-source NPC based T-type inverter (Fig. 3.1) was proposed for both stand-alone and grid-connected mode. The proposed improved modulation scheme enables the converter to handle wide input voltage variations, supply reactive power and provide a single stage boosting with inversion. The filter structure and mid-point clamp technique used eliminates high frequency variations across the parasitic capacitor. The proposed converter was tested in MATLAB for various steady-state and dynamic behaviour and further justified with experimental prototype. Moreover, the performance characteristics of the proposed inverter were compared with existing topologies to highlight its merits.

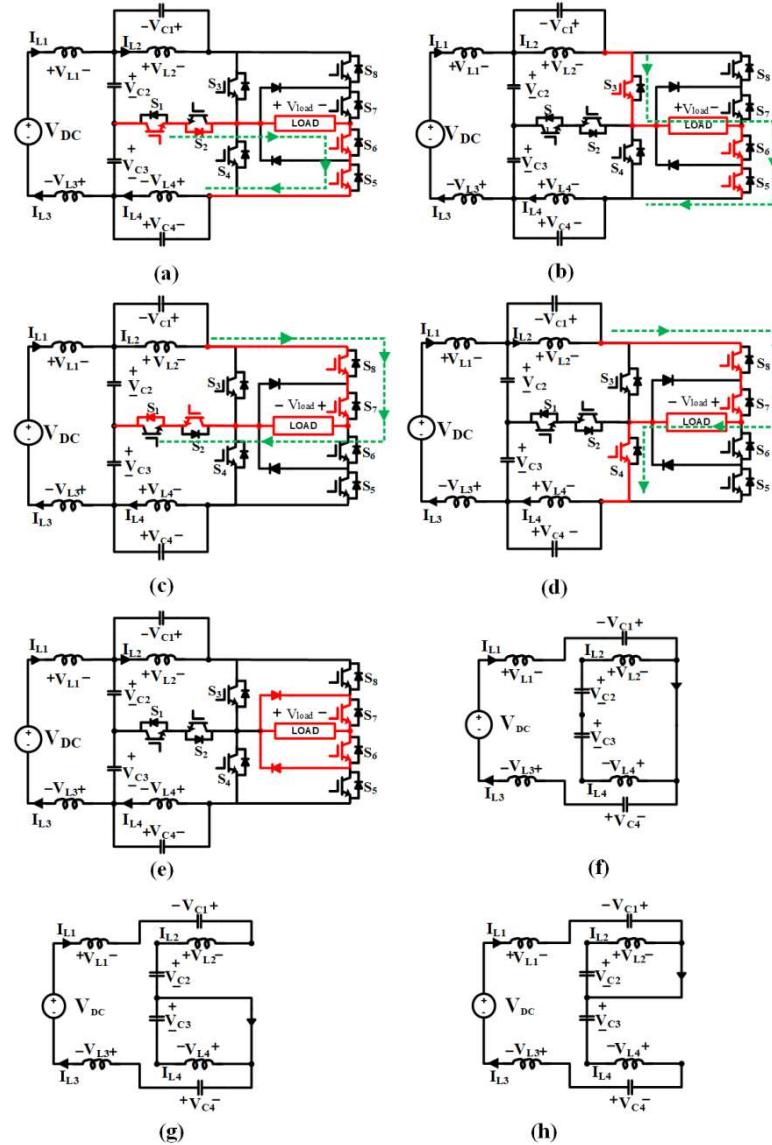

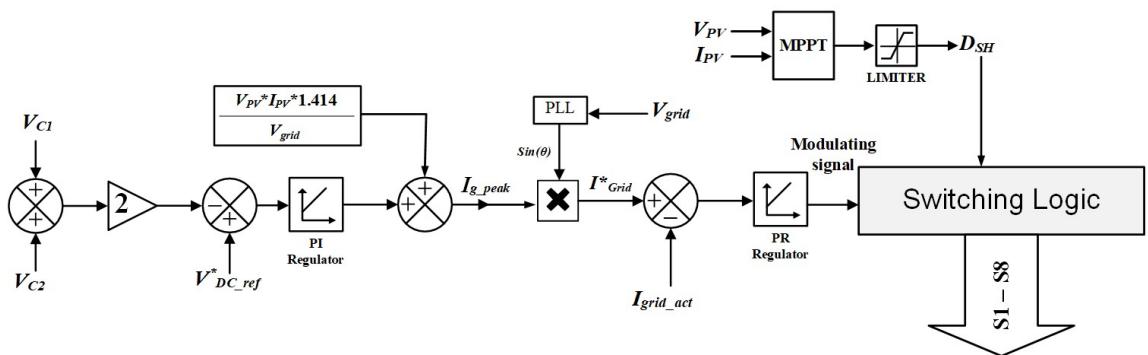

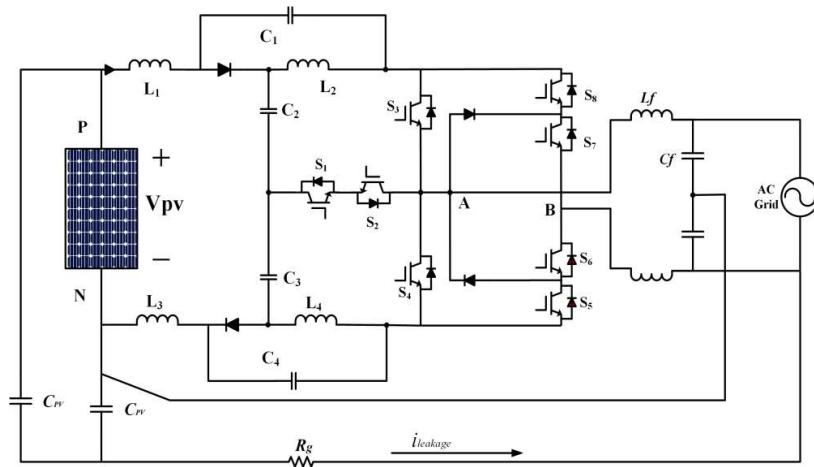

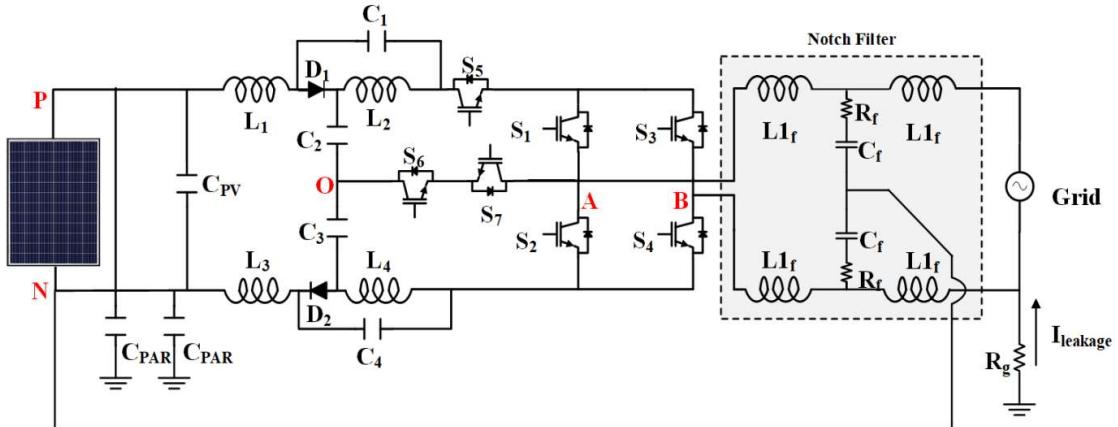

In the second proposal, a single-stage inverter with the amalgamation of dual qZS network and improved T-Type H5 inverter (Fig. 4.1) with the benefits of a single-stage boost, reactive power capability and reduced leakage current was introduced for a PV system. A hybrid method of DC decoupling and Mid-point voltage clamping was utilized for the reduction in leakage current. Furthermore, this converter employs minimum number of switches to operate at any mode, i.e., active, zero and shoot through mode of operation compared to existing inverter topologies.

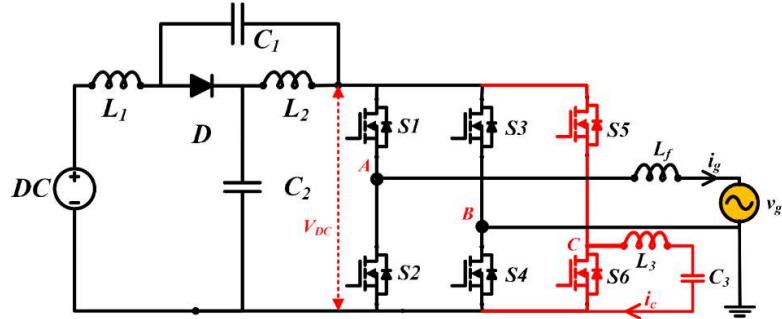

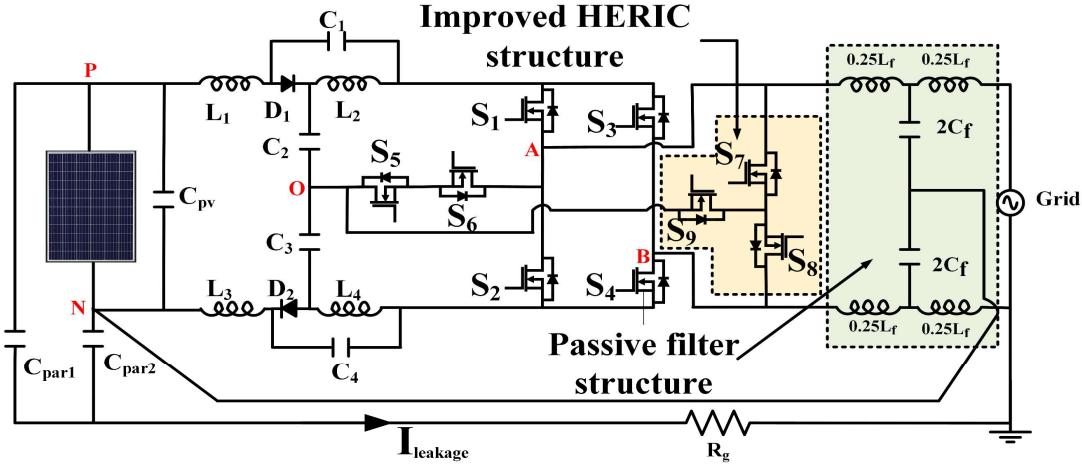

In the third proposal, a seamless structure of qZS network, T-type inverter and improved Highly Efficient and Reliable Inverter Configuration (HERIC) structure (Fig. 5.1) was integrated and proposed for grid-connected PV system. Further, the modulation scheme was modified to incorporate various active, zero and shoot-through states and enable reactive power support. The shoot-through states were chosen in such a way that

voltage stress was reduced. Both Mid-point clamping technique and AC based decoupling were used to reduce leakage current under the standards dictated by *VDE-0126-1-1*.

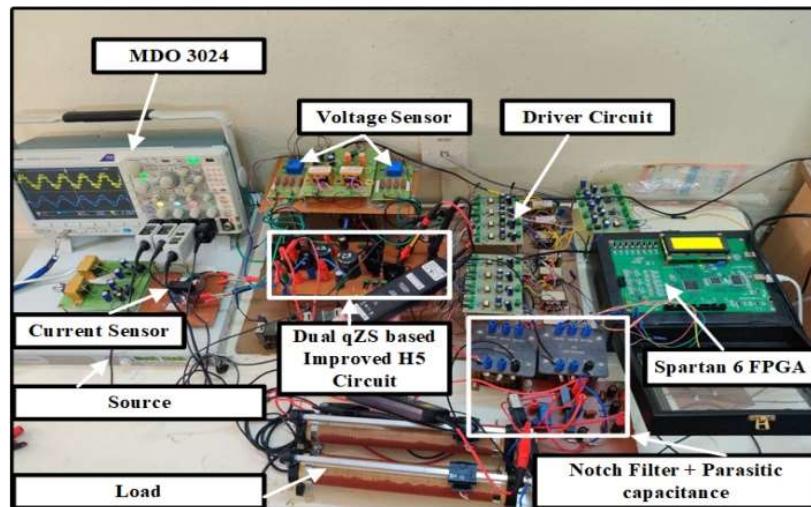

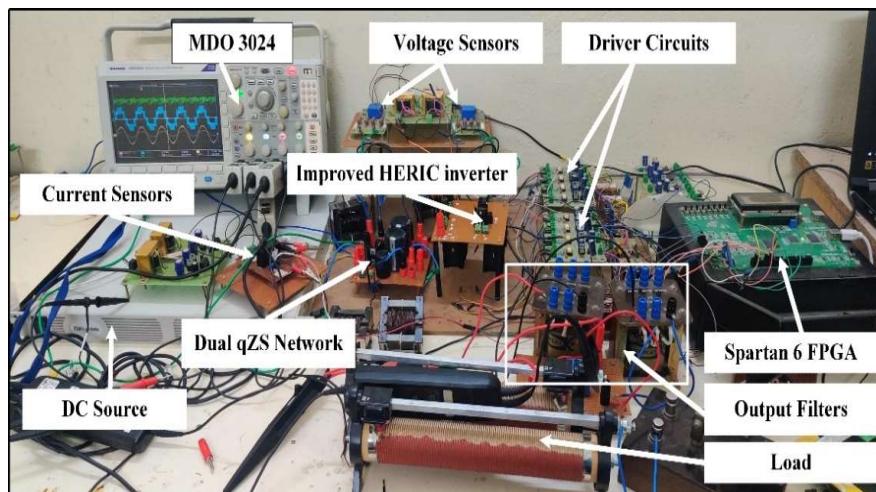

In order to evaluate both steady-state and dynamic performance of the proposed topologies, simulations were performed in MATLAB/Simulink environment and then validated through experimental prototype. The experimental setup was built using IRFP460 MOSFET switches, MURS1560 diodes, TLP250 opto-coupler driver ICs and programmable DC supply. The control algorithm was implemented in Xilinx Spartan 6 platform and Real-time studies were performed using Opal-RT 4500 module for all three proposed topologies. Moreover, in this study, an exhaustive comparison of various five-level qZs based MLIs was done to highlight the merits of the proposed topologies. Finally, the performance of inverters was evaluated using PSIM thermal module which records a maximum efficiency of 92-95%. Thus, the proposed topologies are ideal for standalone/grid connected PV applications.

## TABLE OF CONTENTS

---

---

|                                                              |              |

|--------------------------------------------------------------|--------------|

| <b>Acknowledgements.....</b>                                 | <b>ii</b>    |

| <b>Abstract.....</b>                                         | <b>iv</b>    |

| <b>Table of Contents.....</b>                                | <b>viii</b>  |

| <b>List of Figures.....</b>                                  | <b>xi</b>    |

| <b>List of Tables.....</b>                                   | <b>xviii</b> |

| <b>Abbreviations.....</b>                                    | <b>xix</b>   |

| <b>List of Symbols.....</b>                                  | <b>xxi</b>   |

| <b>CHAPTER 1 INTRODUCTION.....</b>                           | <b>1</b>     |

| 1.1. Background.....                                         | 2            |

| 1.2. Photovoltaic Technology.....                            | 3            |

| 1.2.1. AC Module Inverters.....                              | 3            |

| 1.2.2. String Inverters.....                                 | 4            |

| 1.2.3. Multistring Inverters.....                            | 4            |

| 1.2.4. Central Inverters.....                                | 4            |

| 1.3. Power Electronic Interface.....                         | 4            |

| 1.3.1. Double Stage Inverters.....                           | 4            |

| 1.3.2. Single Stage Inverters.....                           | 5            |

| 1.3.2.1. Isolated Topologies.....                            | 6            |

| 1.3.2.2. Non-Isolated Topologies.....                        | 6            |

| 1.4. Impedance Source Inverters.....                         | 7            |

| 1.5. Multilevel Inverters.....                               | 10           |

| 1.6. Analysis of Leakage Current.....                        | 11           |

| 1.7. Grid Standards.....                                     | 13           |

| 1.8. Summary.....                                            | 13           |

| <b>CHAPTER 2 LITERATURE SURVEY.....</b>                      | <b>14</b>    |

| 2.1. Introduction.....                                       | 15           |

| 2.2. Overview of Impedance Source Networks.....              | 16           |

| 2.3. Overview of Single-Phase Transformerless Inverters..... | 21           |

| 2.3.1. DC Decoupling-Based Topologies.....                   | 21           |

| 2.3.2. AC Decoupling-Based Topologies.....                   | 22           |

| 2.3.3. Mid-Point Clamped Based Topologies.....               | 23           |

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| 2.4. Overview of qZS/ZS Based Single-Phase Transformerless Topologies..... | 27        |

| 2.5. Overview of qZS Based Five-Level Inverters.....                       | 29        |

| 2.6. Problem Formulation.....                                              | 32        |

| 2.7. Objective of the Thesis.....                                          | 33        |

| 2.8. Organisation of Thesis.....                                           | 34        |

| <b>CHAPTER 3 QUASI Z-SOURCE BASED NPC T-TYPE INVERTER.....</b>             | <b>36</b> |

| 3.1. Introduction.....                                                     | 37        |

| 3.2. Operation of proposed qZS based NPC T-type inverter.....              | 37        |

| 3.2.1.    Proposed Topology.....                                           | 37        |

| 3.2.2.    Working Principle.....                                           | 38        |

| 3.2.3.    Modulation Scheme.....                                           | 41        |

| 3.3. Passive Component Selection.....                                      | 42        |

| 3.4. Control Structure.....                                                | 42        |

| 3.4.1.    Stand-Alone System.....                                          | 43        |

| 3.4.2.    Grid-Connected System.....                                       | 44        |

| 3.5. Leakage Current Analysis.....                                         | 45        |

| 3.6. Results and Discussions.....                                          | 46        |

| 3.6.1.    Simulation Results.....                                          | 46        |

| 3.6.2.    Experimental Results.....                                        | 53        |

| 3.6.3.    Efficiency Curve.....                                            | 57        |

| 3.7. Comparison with Existing Topologies .....                             | 58        |

| 3.8. Summary.....                                                          | 59        |

| <b>CHAPTER 4 DUAL QUASI Z-SOURCE BASED IMPROVED H5 INVERTER.....</b>       | <b>61</b> |

| 4.1. Introduction.....                                                     | 62        |

| 4.2. Dual Quasi-Z Source Improved H5 Inverter.....                         | 62        |

| 4.3. Operating Modes and Modified Modulation Scheme.....                   | 63        |

| 4.4. Passive Component Selection.....                                      | 67        |

| 4.5. Control Scheme.....                                                   | 68        |

| 4.6. Leakage Current Analysis.....                                         | 68        |

| 4.7. Results and Discussions.....                                          | 70        |

| 4.7.1.    Simulation Results .....                                         | 70        |

| 4.7.2.    Experimental Results.....                                        | 74        |

|                                  |                                                                                     |            |

|----------------------------------|-------------------------------------------------------------------------------------|------------|

| 4.7.3.                           | Efficiency and Loss Analysis.....                                                   | 77         |

| 4.8.                             | Comparison with Existing Topologies.....                                            | 79         |

| 4.9.                             | Summary.....                                                                        | 81         |

| <b>CHAPTER 5</b>                 | <b>DUAL QUASI Z-SOURCE BASED T-TYPE INVERTER WITH IMPROVED HERIC STRUCTURE.....</b> | <b>82</b>  |

| 5.1.                             | Introduction.....                                                                   | 83         |

| 5.2.                             | System Description.....                                                             | 83         |

| 5.2.1.                           | Proposed Topology.....                                                              | 83         |

| 5.2.2.                           | Operating Modes.....                                                                | 84         |

| 5.2.3.                           | Modified Modulation Scheme.....                                                     | 86         |

| 5.3.                             | Passive Component Selection.....                                                    | 87         |

| 5.3.1.                           | qZS Passive Component Selection.....                                                | 87         |

| 5.3.2.                           | Input Filter Calculation .....                                                      | 88         |

| 5.3.3.                           | Output Filter Calculation.....                                                      | 88         |

| 5.4.                             | Control Scheme for Proposed Topology.....                                           | 89         |

| 5.4.1.                           | Stand-Alone Mode.....                                                               | 89         |

| 5.4.2.                           | Grid-Connected Mode .....                                                           | 90         |

| 5.5.                             | Leakage Current Analysis.....                                                       | 90         |

| 5.6.                             | Results and Discussions.....                                                        | 92         |

| 5.6.1.                           | Simulation Results.....                                                             | 92         |

| 5.6.2.                           | Experimental Results.....                                                           | 95         |

| 5.6.3.                           | Efficiency and Loss Analysis.....                                                   | 100        |

| 5.7.                             | Comparison with Existing Topologies .....                                           | 101        |

| 5.8.                             | Summary .....                                                                       | 104        |

| <b>CHAPTER 6</b>                 | <b>COMPARATIVE ASSESSMENT.....</b>                                                  | <b>105</b> |

| <b>CHAPTER 7</b>                 | <b>CONCLUSION AND FUTURE SCOPE.....</b>                                             | <b>108</b> |

| 7.1.                             | Conclusion.....                                                                     | 109        |

| 7.2.                             | Future Scope .....                                                                  | 111        |

| <b>References.....</b>           |                                                                                     | <b>112</b> |

| <b>List of Publications.....</b> |                                                                                     | <b>121</b> |

| <b>Appendix.....</b>             |                                                                                     | <b>122</b> |

| <b>Bio data .....</b>            |                                                                                     | <b>128</b> |

## LIST OF FIGURES

---

---

|           |                                                                                                                                                                                                                                                              |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.1  | Solar PV trends. (a) Increasing trend of PV installation, (b) percentage change in solar energy with respect to 2020.                                                                                                                                        | 3  |

| Fig. 1.2. | Basic Power Electronics Interface.                                                                                                                                                                                                                           | 3  |

| Fig. 1.3  | PV configurations based on module arrangement and power handling capability.                                                                                                                                                                                 | 5  |

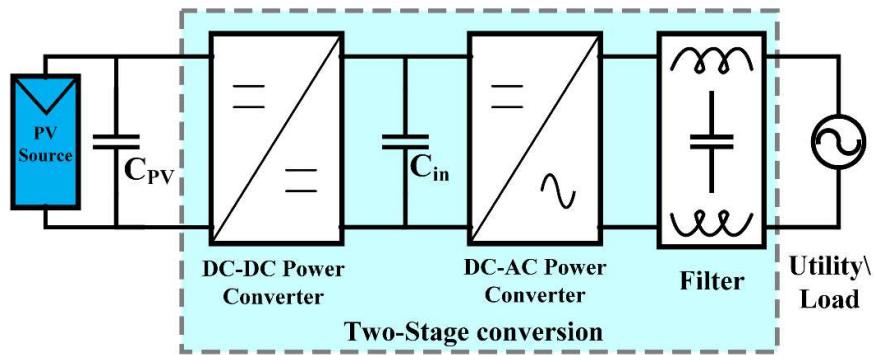

| Fig. 1.4  | Typical Two-Stage Power Converter Topology.                                                                                                                                                                                                                  | 5  |

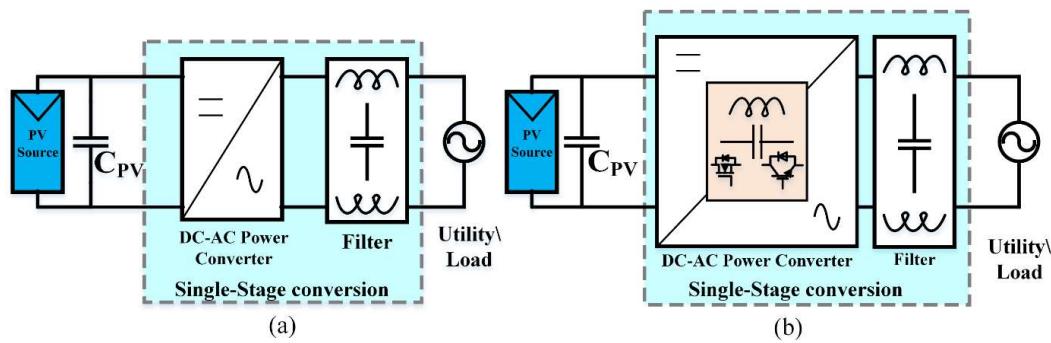

| Fig. 1.5  | Single stage topologies; (a) Buck type single stage topology, (b) Single stage boosting type topology.                                                                                                                                                       | 6  |

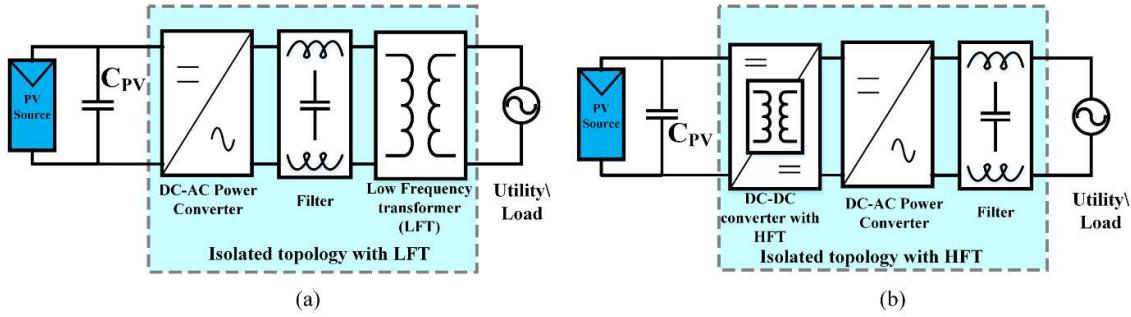

| Fig. 1.6  | Typical scheme for Isolated based topologies; (a) Isolated topologies with LFT, (b) Isolated topologies with HFT.                                                                                                                                            | 7  |

| Fig. 1.7  | Z-Source Inverter; (a) ZSI, (b) Shoot-through Mode, (c) Non-Shoot-Through Mode.                                                                                                                                                                              | 8  |

| Fig. 1.8  | Quasi-Z-Source Inverter; (a) 3-Phase qZSI, (b) STM, (c) NSTM                                                                                                                                                                                                 | 10 |

| Fig. 1.9  | Traditional MLI. (a) Diode-Clamped Topology, (b) Flying Capacitor (FC) Topology and (c) Cascaded H-Bridge (CHB) Topology.                                                                                                                                    | 11 |

| Fig. 1.10 | PV panels with various parasitic (a) Parasitic capacitance across various PV elements, (b) Internal structure of PV panel.                                                                                                                                   | 11 |

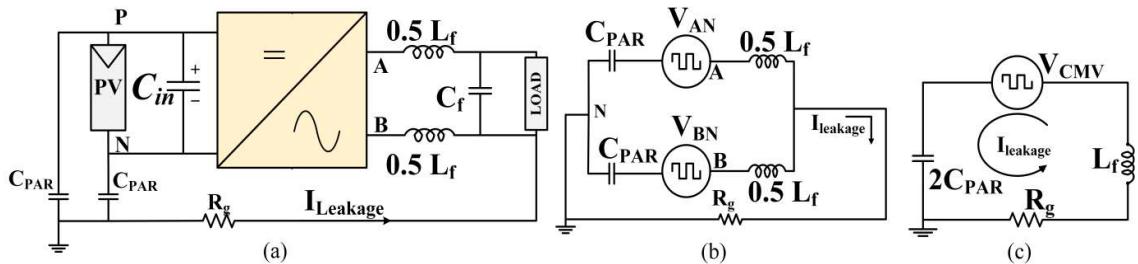

| Fig. 1.11 | Leakage current path for PV integrated system.                                                                                                                                                                                                               | 12 |

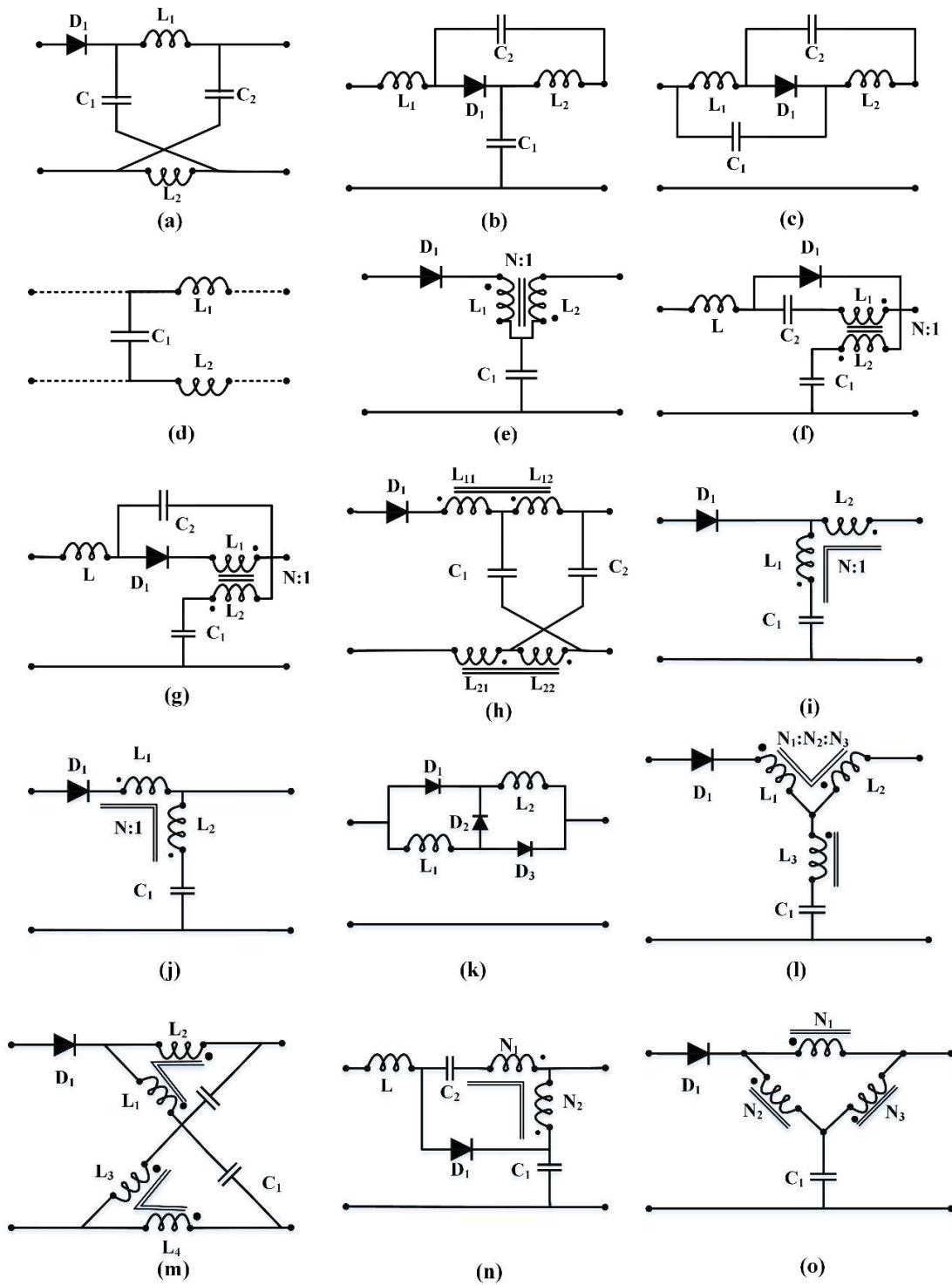

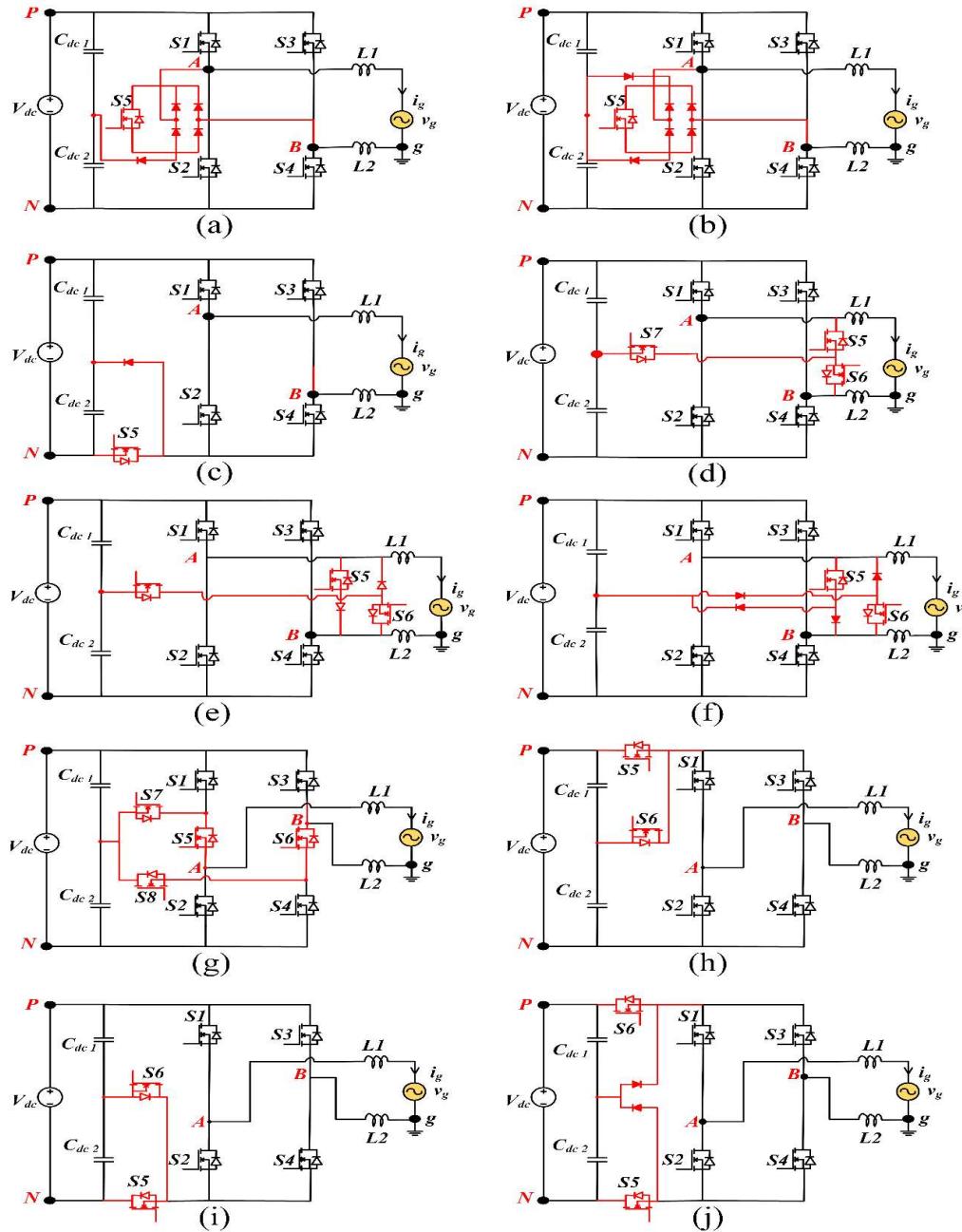

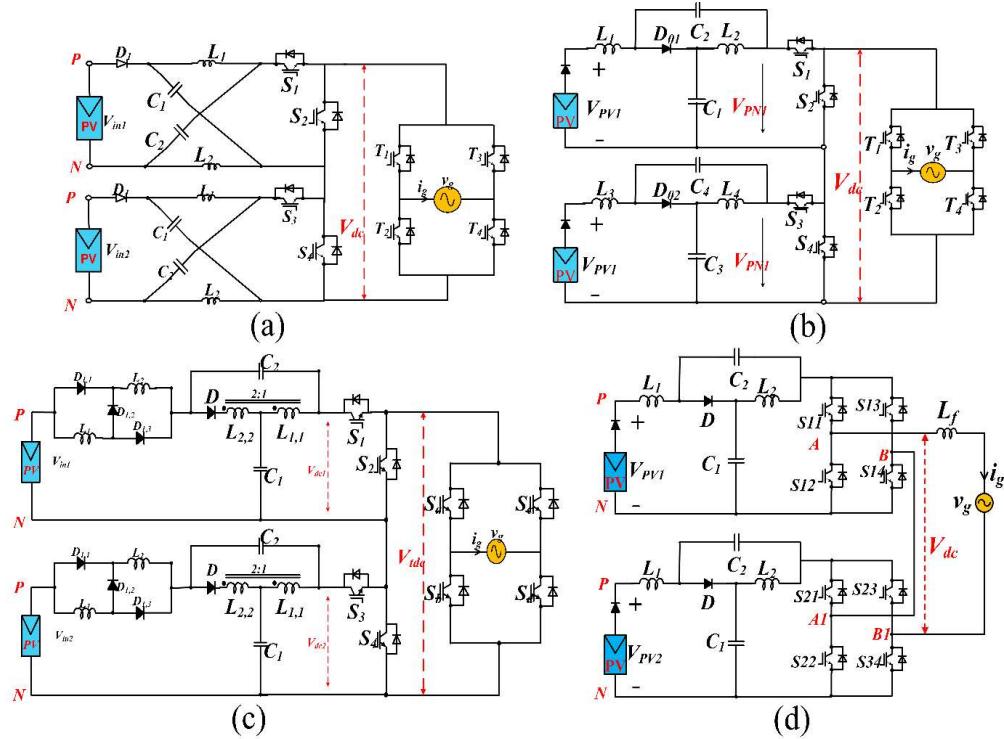

| Fig. 2.1  | Figure 2.1 Basic impedance source networks. (a) ZSN, (b) QZSN, (c) d-QZSN, (d) DZSN, (e) Trans-ZSN (or) TSN, (f) LCCT-ZSN, (g) QLCCT-ZSN, (h) TZSN, (i) $\Gamma$ -SN, (j) $FF\Gamma$ -SN, (k) LSN, (l) YSN, (m) $\Sigma$ -SN, (n) ASN, and (o) $\Delta$ -SN. | 17 |

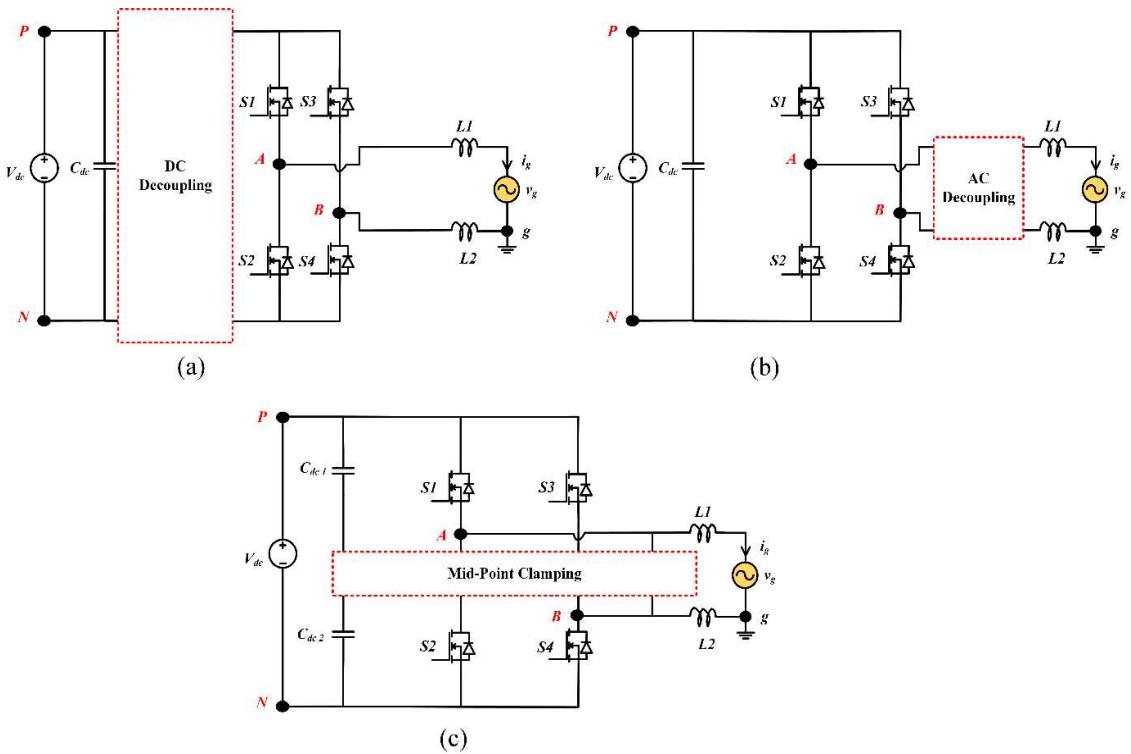

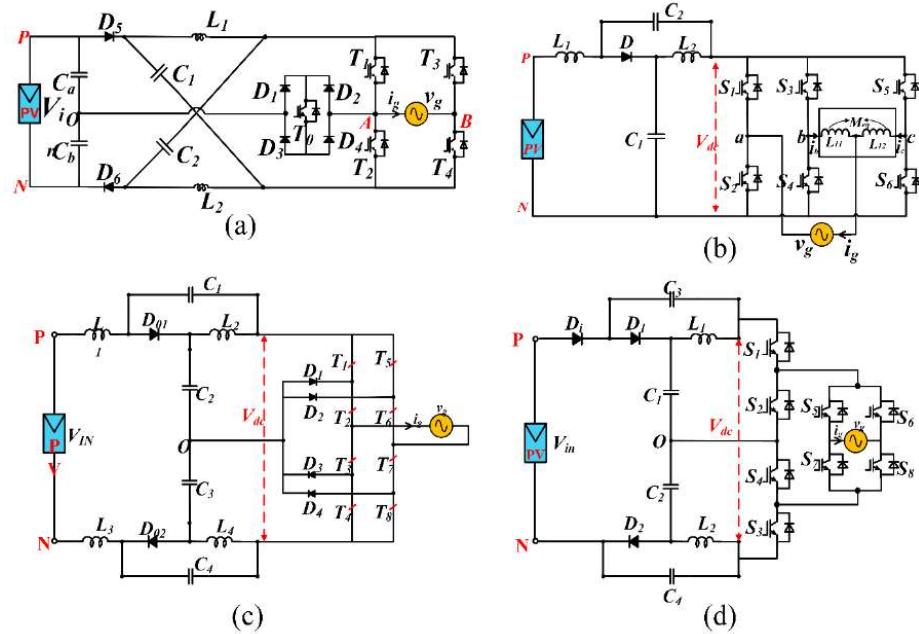

| Fig. 2.2  | Basic classification of transformerless inverters. (a) DC decoupling based, (b) AC decoupling based and (c) Mid-point clamping based.                                                                                                                        | 21 |

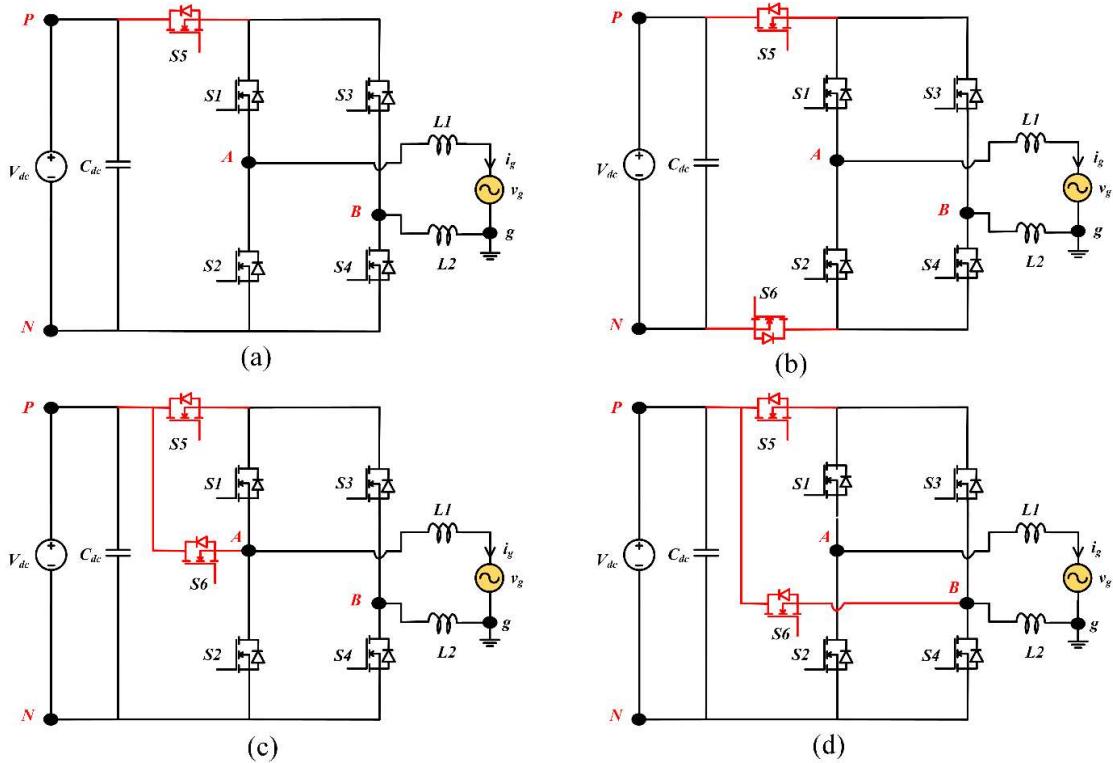

| Fig. 2.3  | DC decoupling-based circuits. (a) H5 inverter, (b) H6 inverter, (c) H6-dc-side-1 topology and (d) H6-dc-side-2 topology.                                                                                                                                     | 23 |

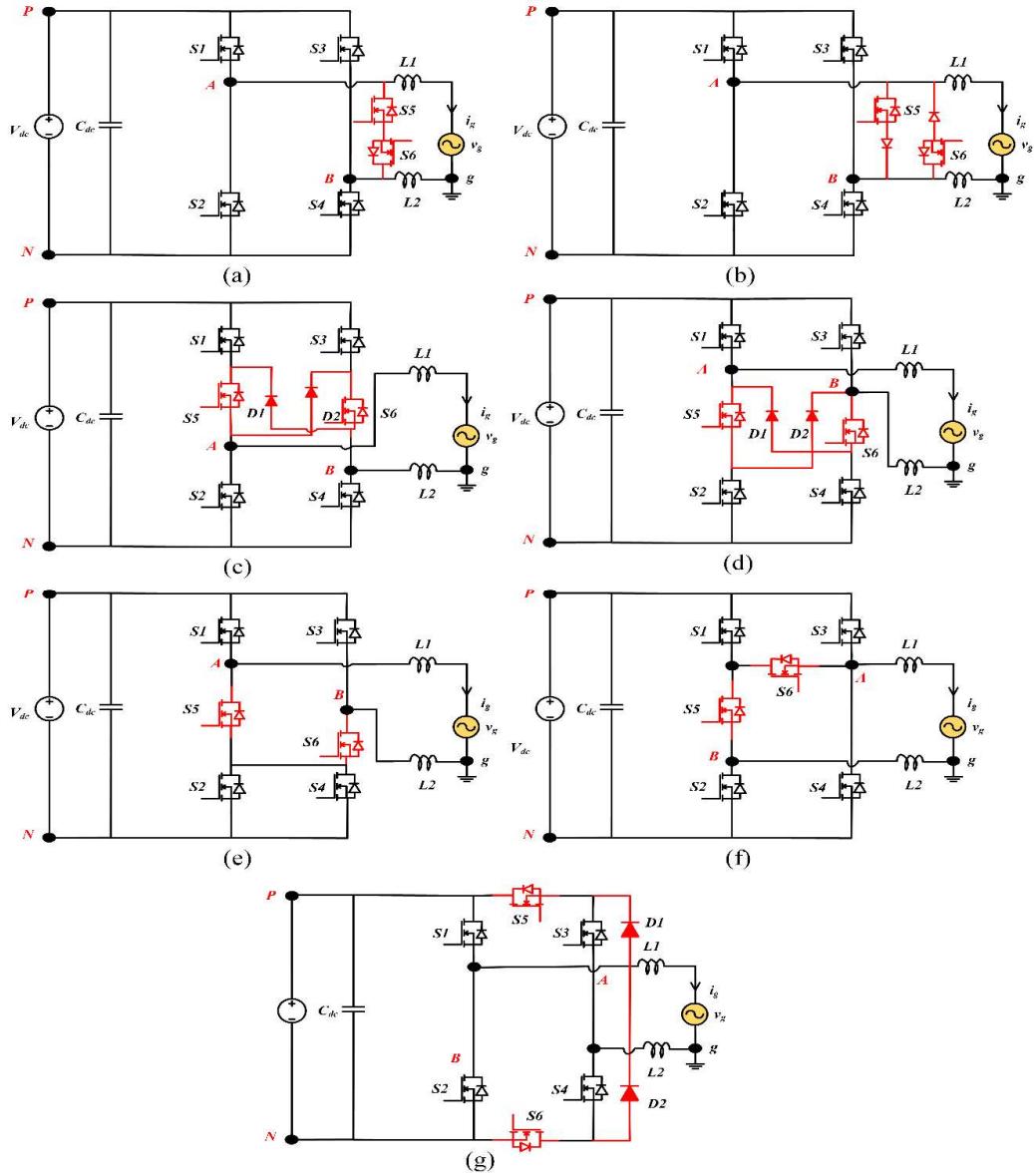

| Fig. 2.4  | AC decoupling-based topologies. (a) HERIC structure, (b) HERIC ac-based structure, (c) H6 with diodes-1 inverter, (d) H6 with diodes-2 inverter, (e) H6-1 inverter, (f) H6 with mid-                                                                         | 25 |

|                                                                                  |                                                                                                                                                                                                                                                             |    |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| switch inverter and (g) Full-bridge inverter with mid-point switches and diodes. |                                                                                                                                                                                                                                                             |    |

| Fig. 2.5                                                                         | Mid-point clamped topologies. (a)HB-ZVR topology, (b) HB-ZVR-D topology, (c) H5-D topology, (d) HERIC-Active-1 topology, (e) HERIC-Active-2 topology, (f)HERIC-Active-3 topology, (g) PN-NPC topology, (h) ih5/oh5 topology, (i) oh5-1 and oh5-2 circuitry. | 26 |

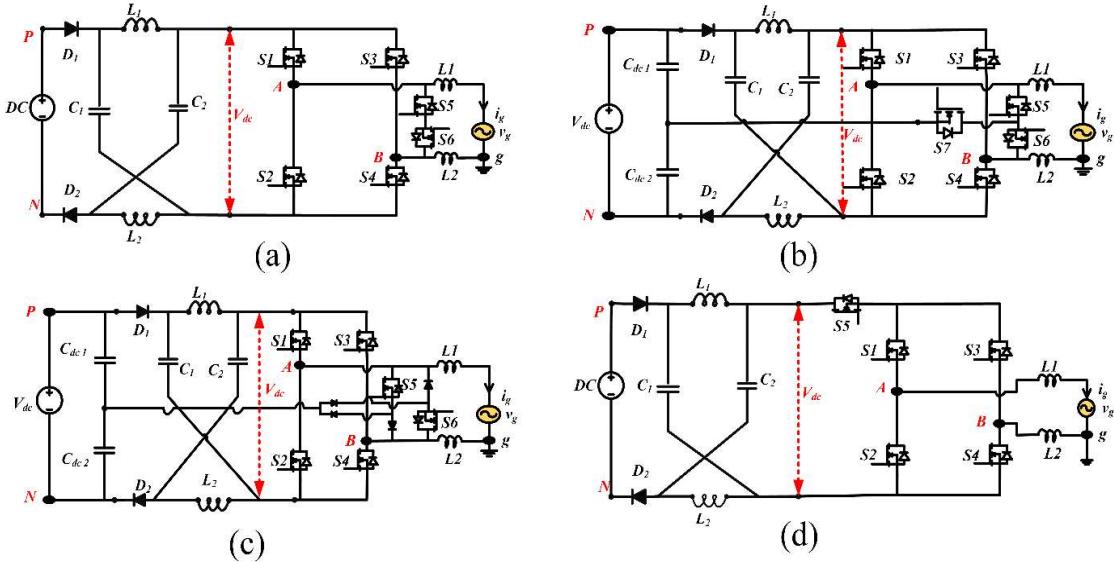

| Fig. 2.6                                                                         | Z-source based transformerless inverters. (a) ZS-HERIC topology, (b) ZS-Active clamping HERIC, (c) ZS- Passive clamping HERIC and (d) ZS-H5 topology.                                                                                                       | 28 |

| Fig. 2.7                                                                         | QZS based Transformerless topologies. (a) qZS based HERIC and (b) qZS based HERIC-1 topology                                                                                                                                                                | 29 |

| Fig. 2.8                                                                         | APF based qZSI topology.                                                                                                                                                                                                                                    | 29 |

| Fig. 2.9                                                                         | Cascaded based qZSI. (a) ZS-HBI topology, (b) qZS-HBI topology, (c) SL-qZS based HBI topology and (d) qZS-CMI topology.                                                                                                                                     | 30 |

| Fig. 2.10                                                                        | Single source based qZS-MLI (a) ZS with T-type inverter, (b) qZS with coupled inductor topology, (c) qZS-NPC topology and (d) MqZS topology.                                                                                                                | 30 |

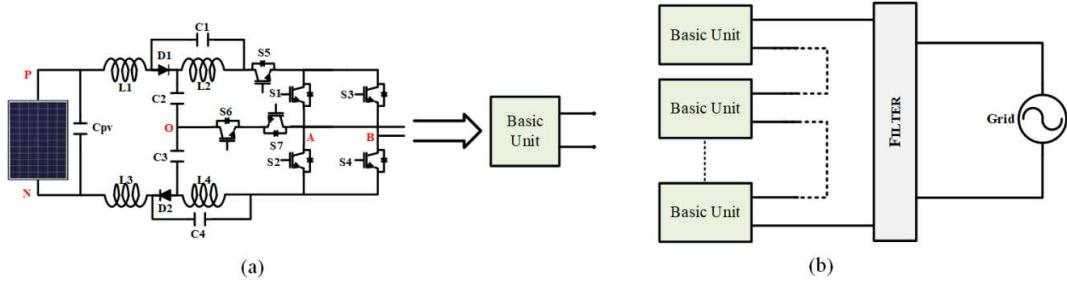

| Fig. 3.1                                                                         | Proposed qZS based NPC inverter.                                                                                                                                                                                                                            | 38 |

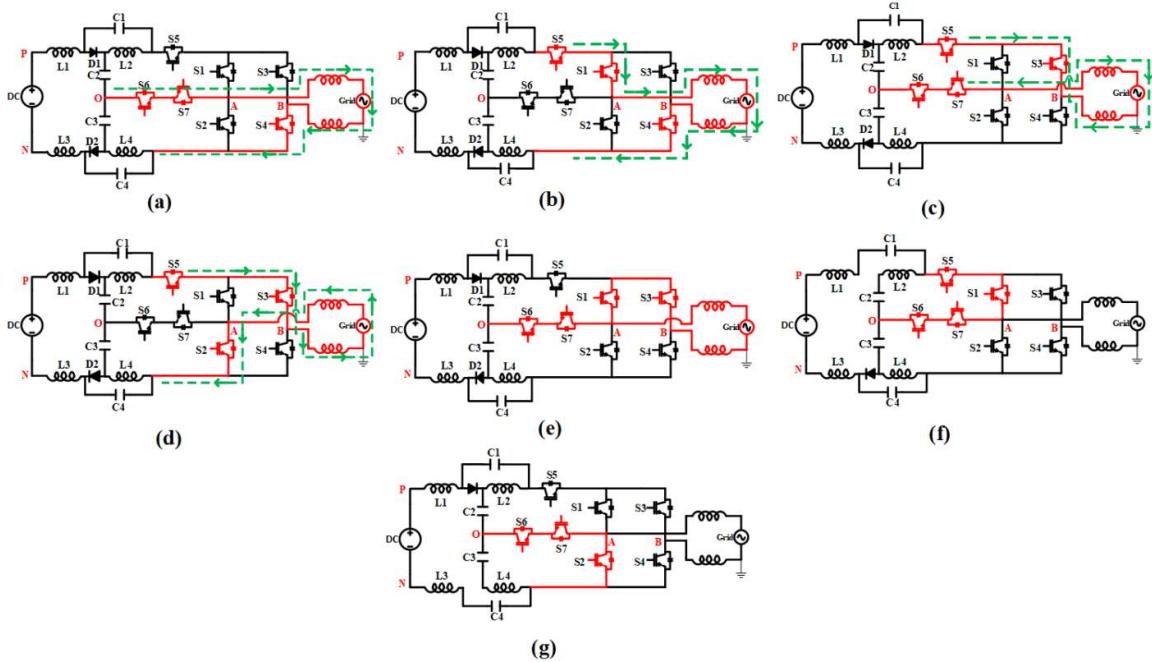

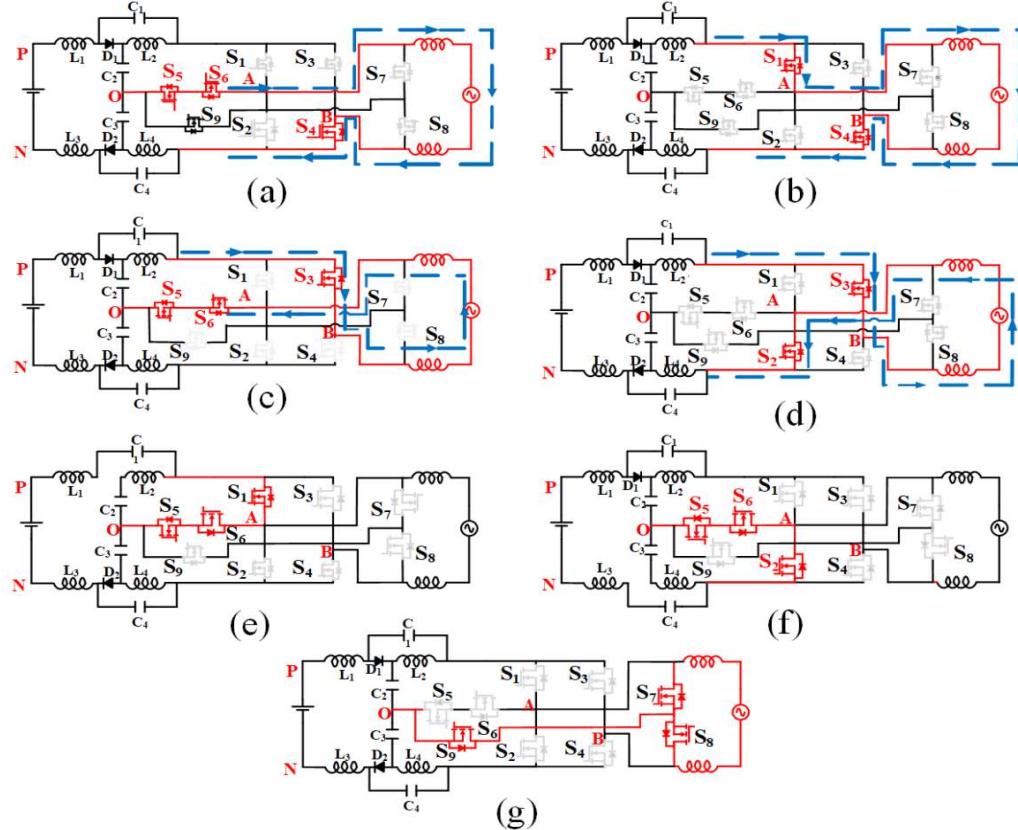

| Fig. 3.2                                                                         | Various operating modes of the proposed converter, Fig (a)-(d) active modes, Fig (e) freewheeling mode and Fig (f)-(h) various shoot through modes.                                                                                                         | 40 |

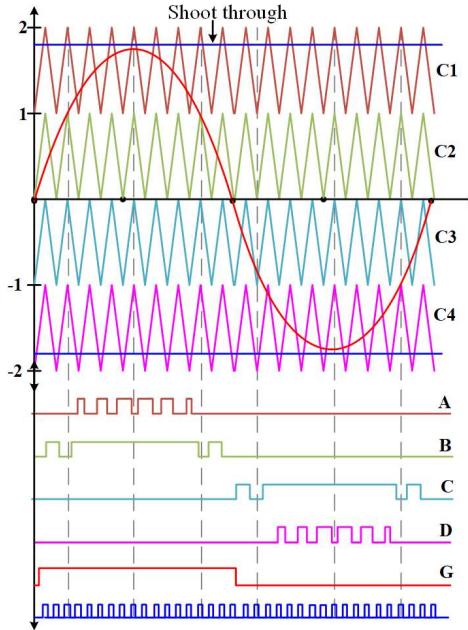

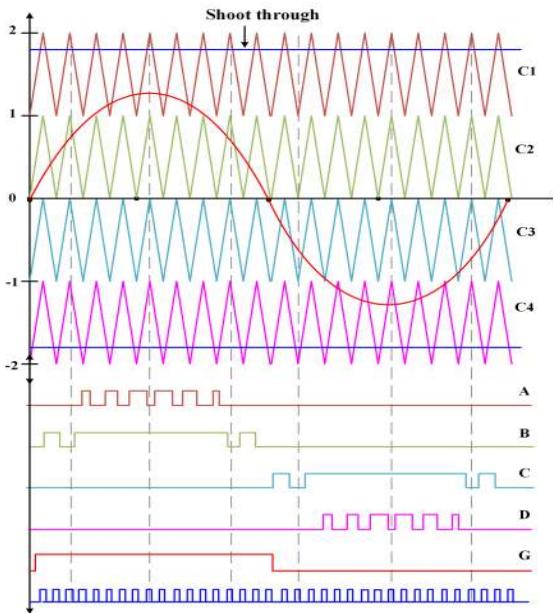

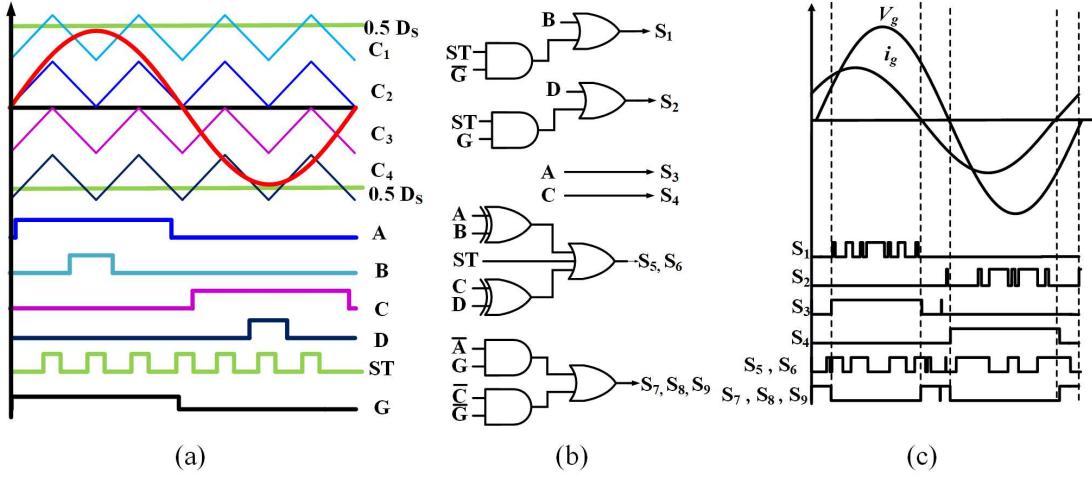

| Fig. 3.3                                                                         | LSPWM and corresponding signals.                                                                                                                                                                                                                            | 41 |

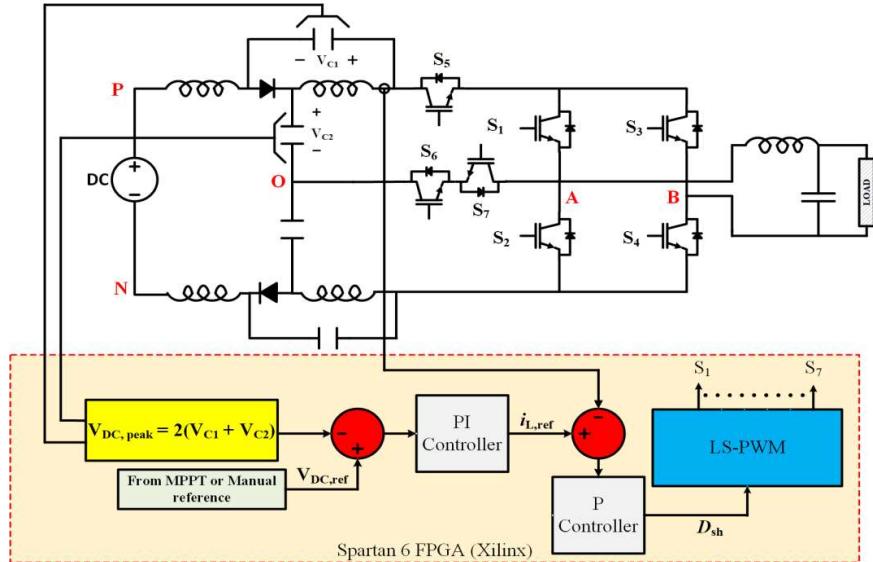

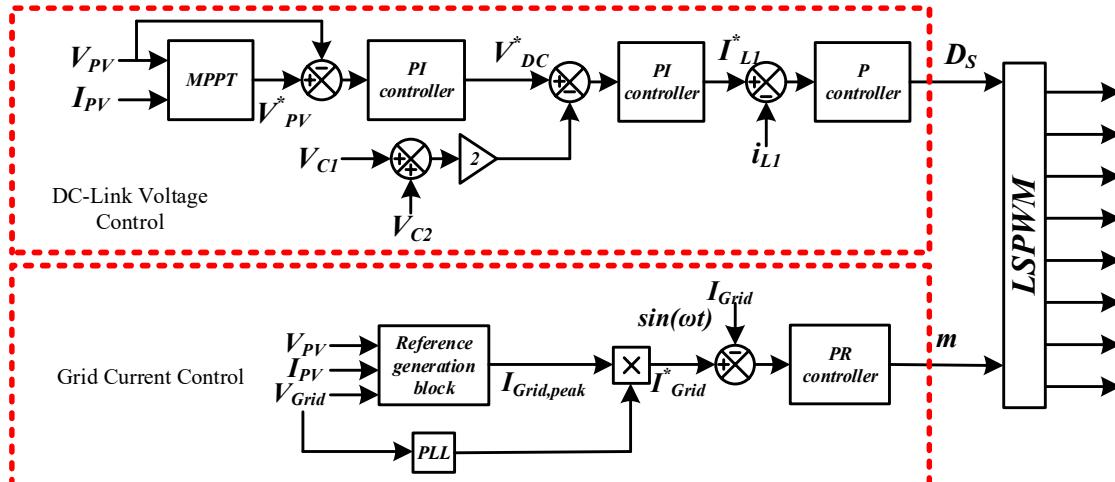

| Fig. 3.4                                                                         | Closed loop control scheme for standalone system.                                                                                                                                                                                                           | 43 |

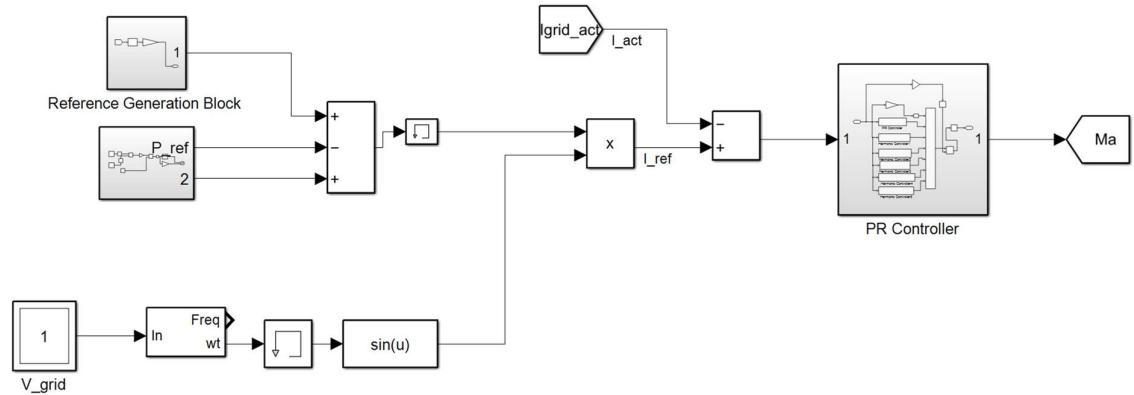

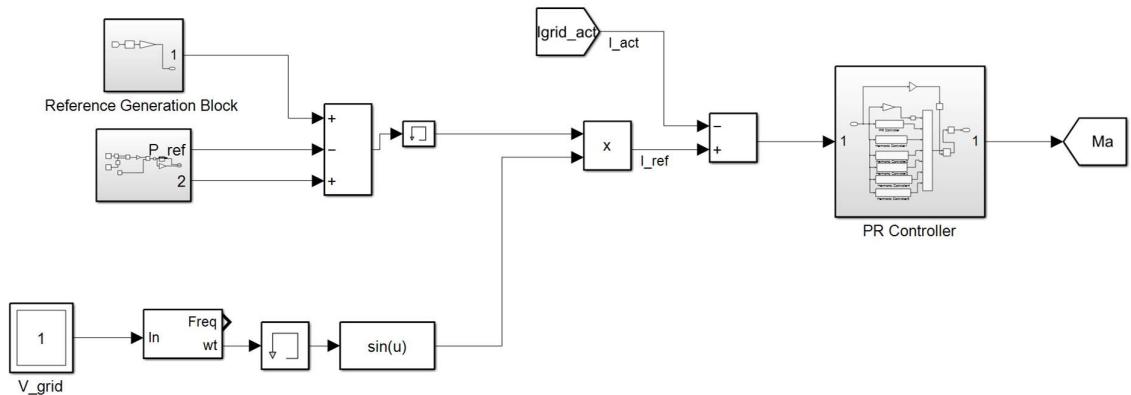

| Fig. 3.5                                                                         | Closed loop control scheme for PV-grid connected system.                                                                                                                                                                                                    | 44 |

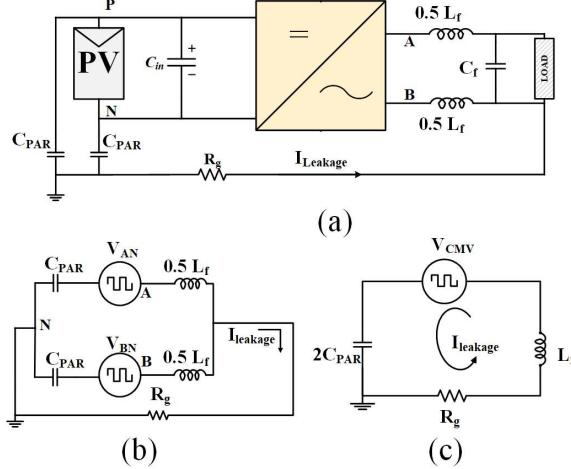

| Fig. 3.6                                                                         | Common Mode circuit representation of the inverter, (a) Equivalent circuit, (b) Exact equivalent circuit.                                                                                                                                                   | 46 |

| Fig. 3.7                                                                         | Proposed topology with split LCL filters to reduce high frequency variation in CMV.                                                                                                                                                                         | 46 |

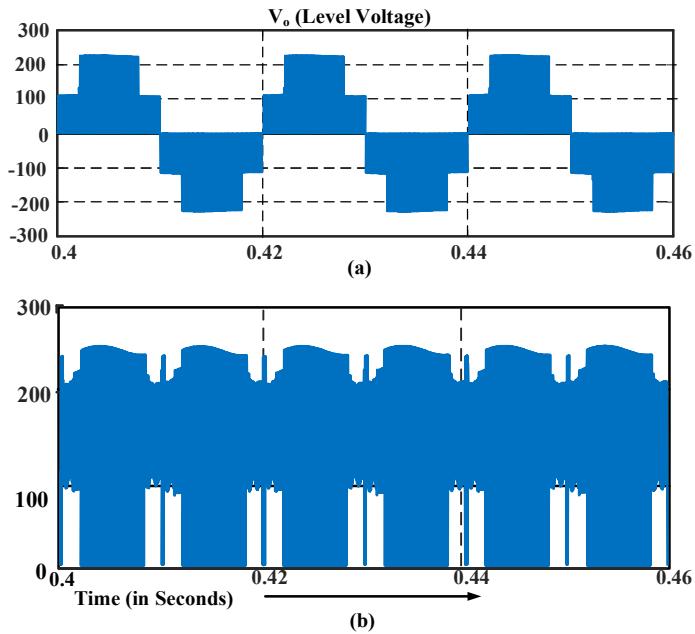

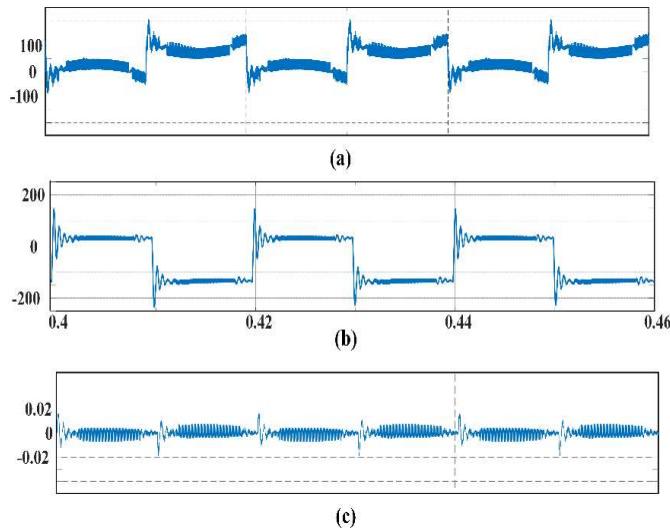

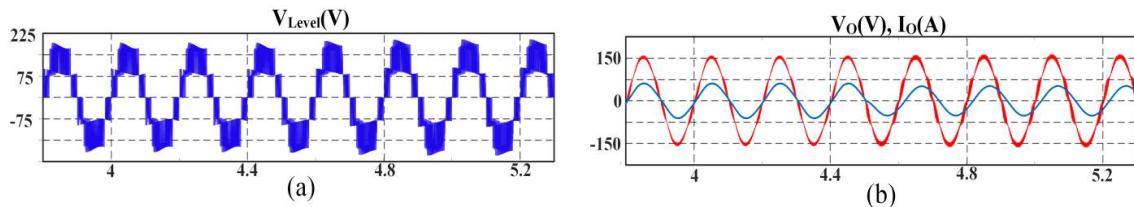

| Fig. 3.8                                                                         | Simulation results for proposed inverter. (a) Output level voltage; (b) DC link voltage.                                                                                                                                                                    | 47 |

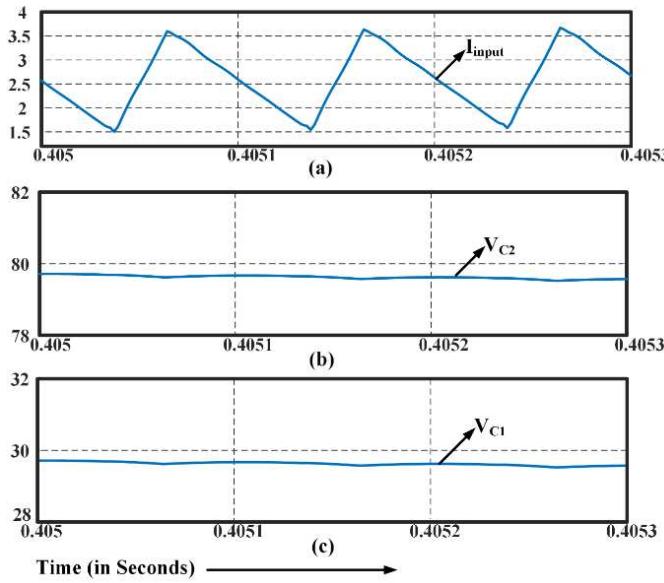

| Fig. 3.9                                                                         | Dynamics of passive components. (a) Inductor current for $L_1$ . (b) Voltage across capacitor $C_2$ . (c) Voltage across capacitor $C_1$ .                                                                                                                  | 48 |

|           |                                                                                                                                                                                                                                             |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

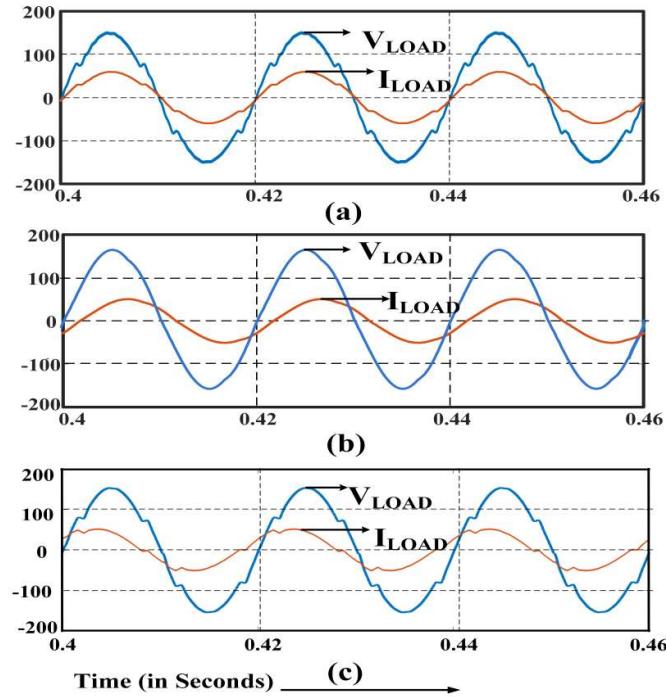

| Fig. 3.10 | Reactive power capability of converter. Output of converter for various load pf (a) UPF; (b) 0.8 Lagging PF and (c) 0.8 Leading PF.                                                                                                         | 50 |

| Fig. 3.11 | Common mode parameters of the inverter (a) CMV; (b) Voltage across parasitic capacitor and (c) Leakage current.                                                                                                                             | 50 |

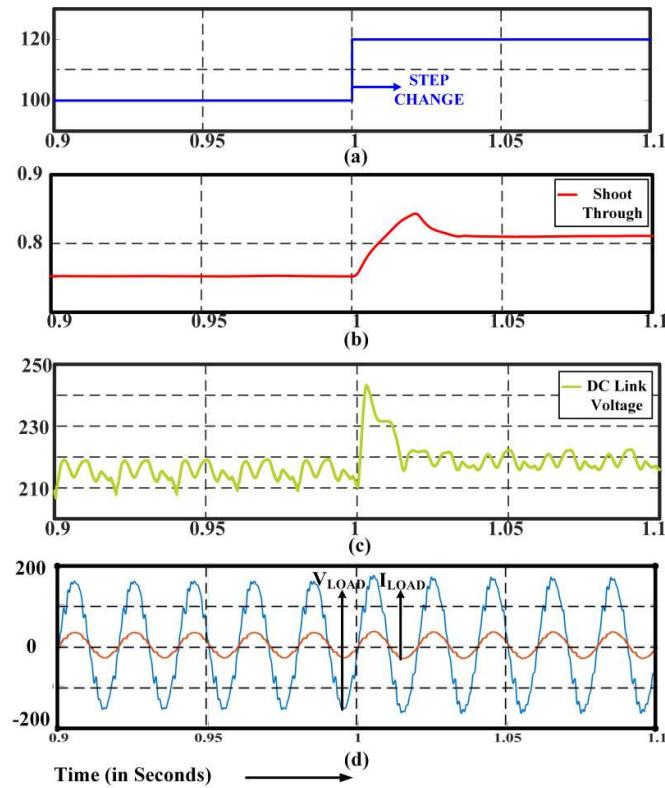

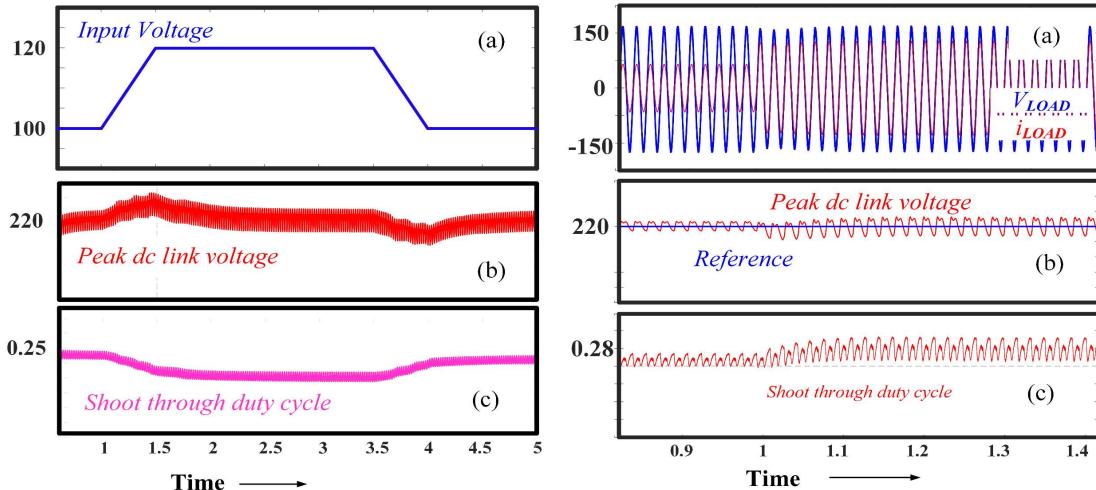

| Fig. 3.12 | Transient response of system for disturbances on source side. (a) Step change in input voltage; (b) Change in shoot through duty cycle; (c) Peak DC link voltage and (d) Output voltage and current.                                        | 51 |

| Fig. 3.13 | Transient performance of the system for step change in load. (a) DC link voltage; (b) Shoot through duty cycle and (c) Output voltage and current.                                                                                          | 51 |

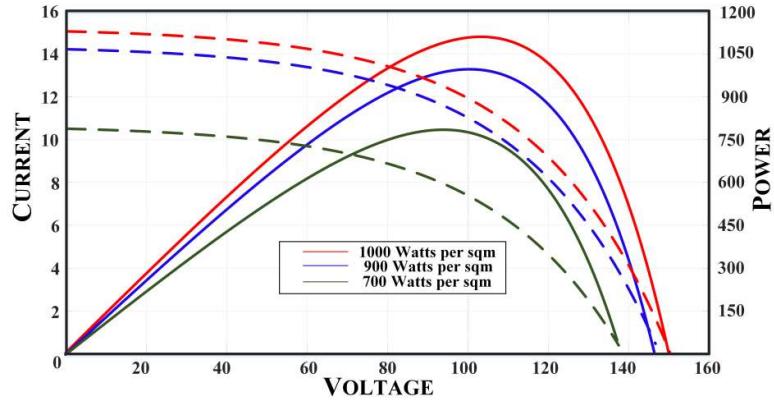

| Fig. 3.14 | P-V and I-V curve of the PV array.                                                                                                                                                                                                          | 52 |

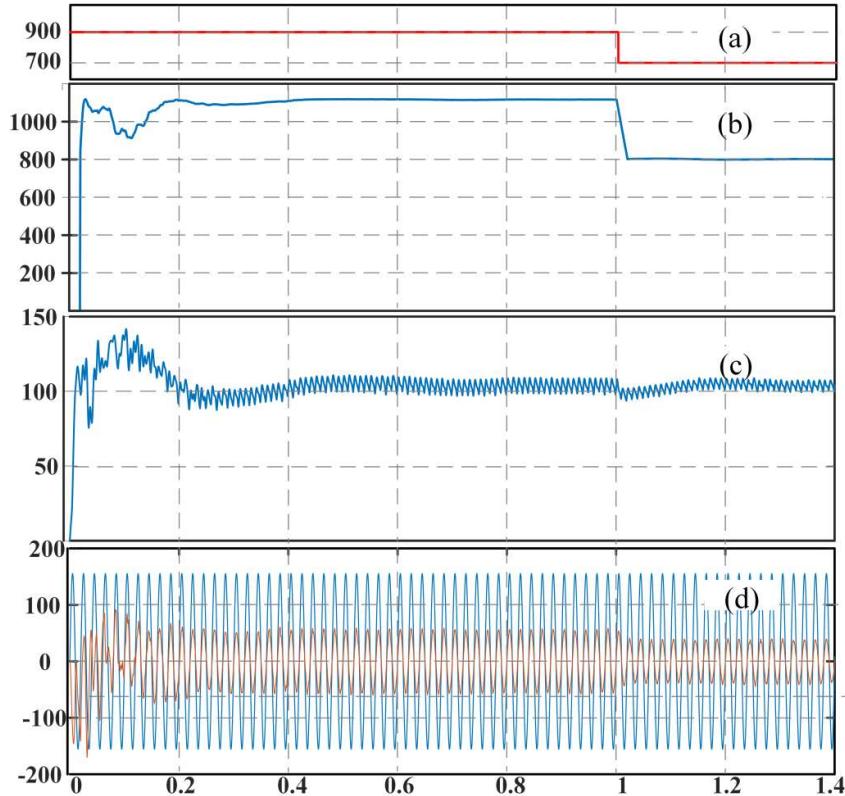

| Fig. 3.15 | Grid based simulation for step change in irradiance (a) Change in irradiance; (b) Change in PV array's power level; (c) PV voltage and (d) Grid voltage and current.                                                                        | 52 |

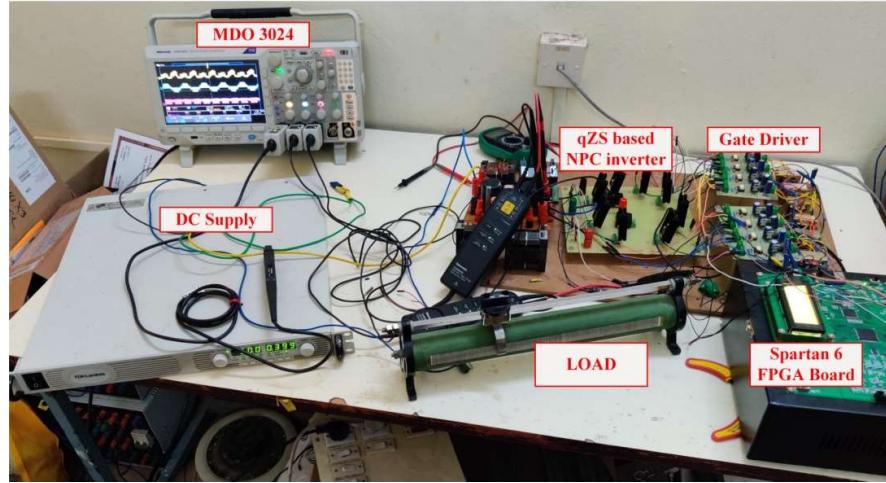

| Fig. 3.16 | Hardware setup of the proposed inverter.                                                                                                                                                                                                    | 54 |

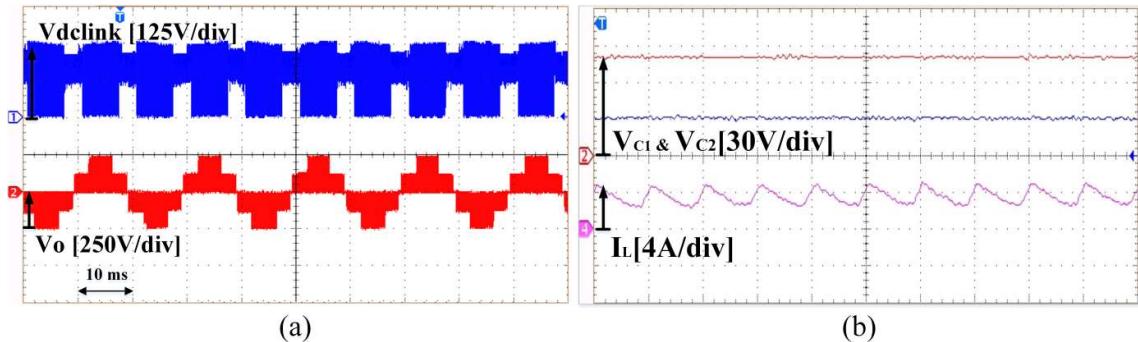

| Fig. 3.17 | Experimental results for proposed system in steady state. (a) DC link Voltage and Output level voltage; (b) Capacitor voltages and inductor current.                                                                                        | 54 |

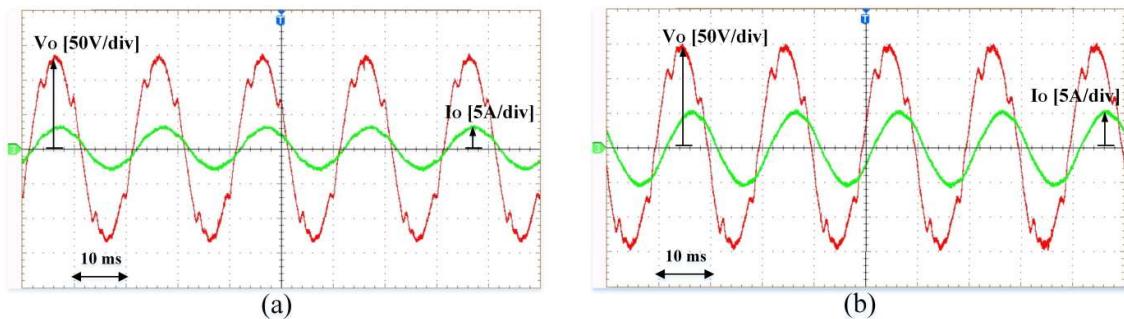

| Fig. 3.18 | Experimental waveform demonstrating reactive power capability of the inverter (a) UPF; (b) 0.8 Lagging PF.                                                                                                                                  | 54 |

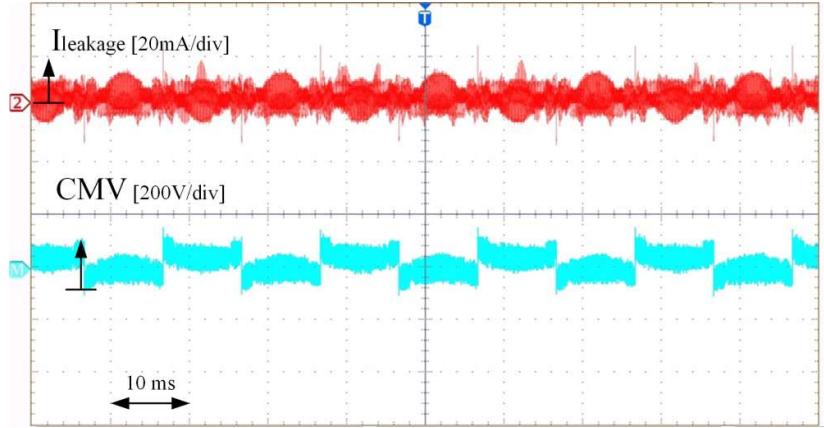

| Fig. 3.19 | Experimental results for leakage current and common mode voltage.                                                                                                                                                                           | 55 |

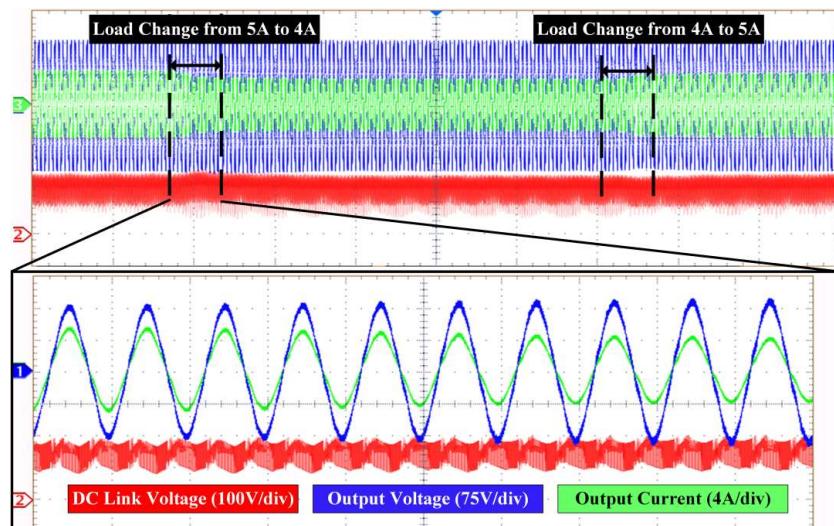

| Fig. 3.20 | Experimental results for transient response of system for step change in load.                                                                                                                                                              | 55 |

| Fig. 3.21 | Experimental result demonstrating transient response of system for change in source voltage.                                                                                                                                                | 56 |

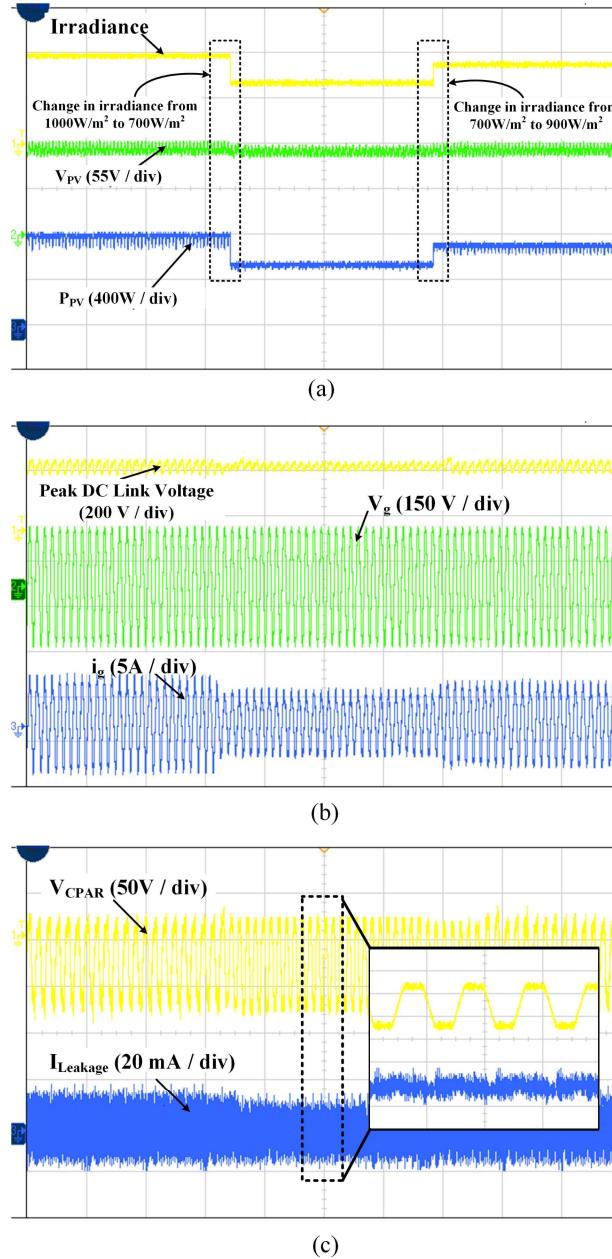

| Fig. 3.22 | Results for the grid connected PV system. (a) Dynamics of input side parameters irradiance, PV array power and Voltage across PV array; (b) Dynamics of output side parameters peak dc link voltage, grid voltage and current respectively. | 56 |

| Fig. 3.23 | Results for common mode properties during grid connected mode.                                                                                                                                                                              | 57 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

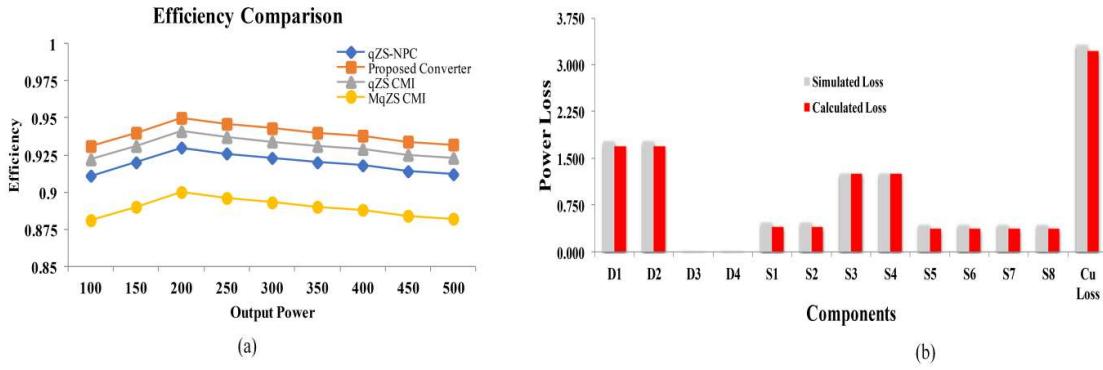

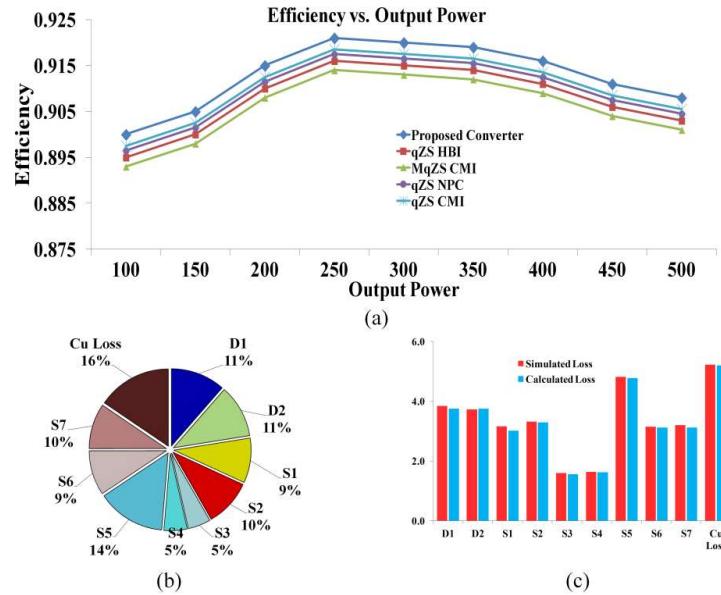

| Fig. 3.24 | Efficiency comparisons of various qZS based inverters.<br>(a) Efficiency vs. Power output for various converter;<br>(b) Comparison graph between calculated loss and simulated loss.                                                                                                                                                                                                                    | 58 |

| Fig. 4.1  | Proposed dual qZS based improved H5 inverter.                                                                                                                                                                                                                                                                                                                                                           | 63 |

| Fig. 4.2  | Generalised form (a) Basic unit; (b) Generalized structure for N-level inverter.                                                                                                                                                                                                                                                                                                                        | 64 |

| Fig. 4.3  | Level shift pulse width modulation scheme.                                                                                                                                                                                                                                                                                                                                                              | 64 |

| Fig. 4.4  | Working modes of the proposed inverter: (a) active switches for generating $+V_{dc}/2$ ; (b) active switches for generating $+V_{dc}$ ; (c), active switches for generating $-V_{dc}/2$ ; (d) active switches for generating $+V_{dc}$ ; (e) active switches for generating zero state; (f) active switches for generating upper shoot through; (g) active switches for generating lower shoot through. | 65 |

| Fig. 4.5  | Closed loop scheme.                                                                                                                                                                                                                                                                                                                                                                                     | 68 |

| Fig. 4.6  | Common mode circuit (a) Overall system representing parasitic elements and leakage current. (b) Total circuit for leakage current flow; (c) Equivalent circuit form source to load side.                                                                                                                                                                                                                | 69 |

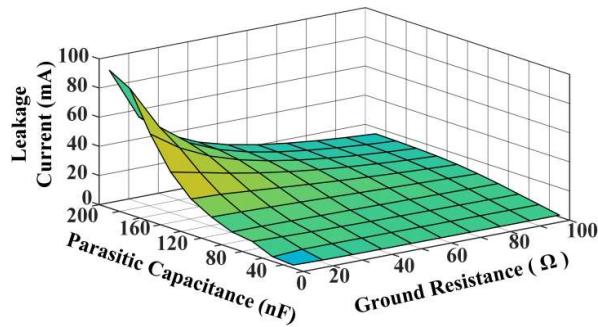

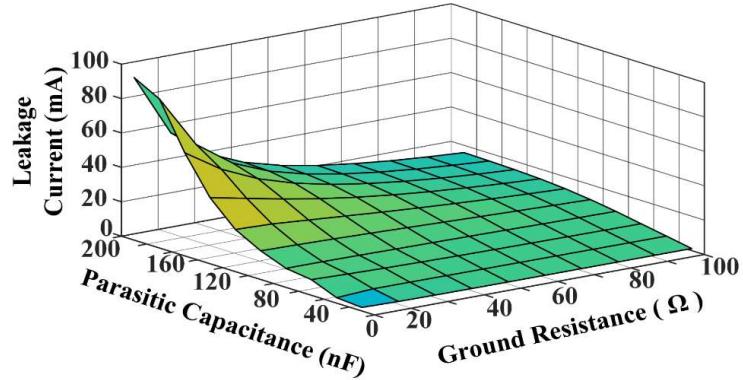

| Fig. 4.7  | Variation of leakage current with respect to ground resistance and parasitic capacitance (CMV=50V).                                                                                                                                                                                                                                                                                                     | 69 |

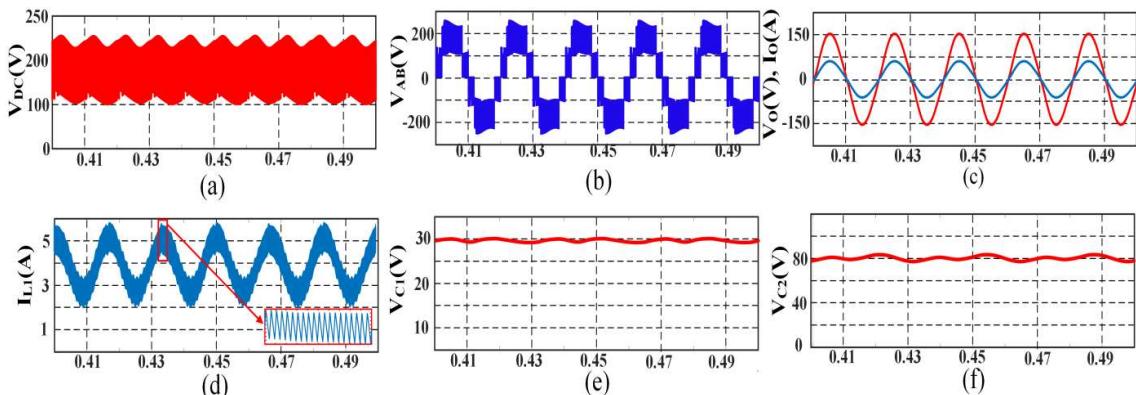

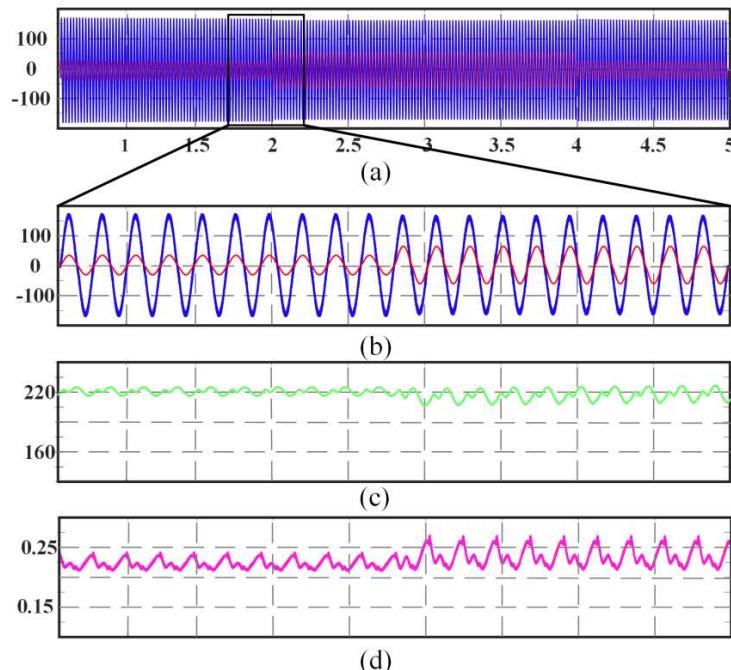

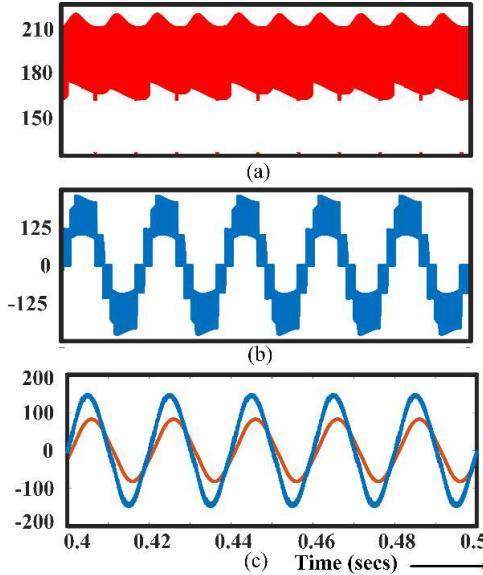

| Fig. 4.8  | Simulation results (a) Boosted DC link voltage; (b) Inverter terminal level voltage; (c) Output Voltage and Current; (d) Inductor current for $L_I$ ; (e) $V_{CI}$ ; (f) $V_{C2}$ .                                                                                                                                                                                                                     | 71 |

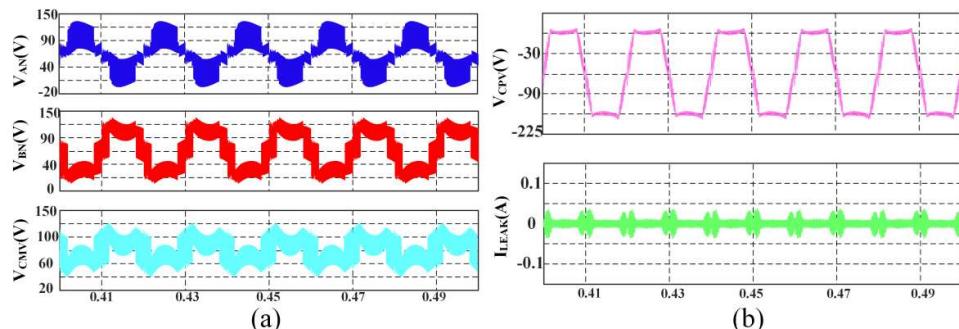

| Fig. 4.9  | Simulation results (a) Common Mode Characteristics $V_{AN}$ , $V_{BN}$ and $V_{CMV}$ respectively; (b) Voltage across parasitic capacitor and Leakage current.                                                                                                                                                                                                                                          | 71 |

| Fig. 4.10 | Reactive power capability of the converter (a) Inverter terminal voltage during load change from UPF to 0.9 Lag PF; (b) Output Voltage and Current.                                                                                                                                                                                                                                                     | 73 |

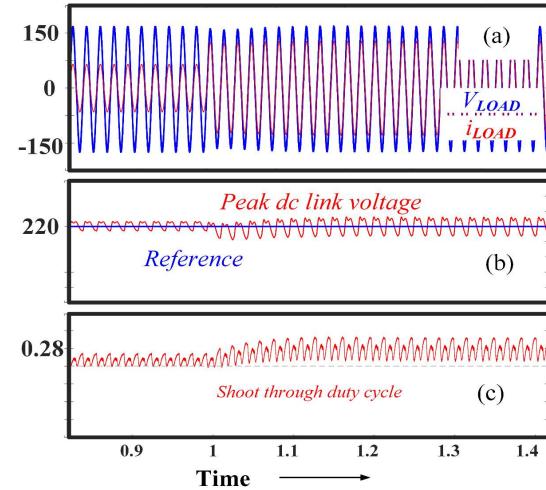

| Fig. 4.11 | Simulation results for closed loop control during change in load : (a) Complete simulation results with output voltage and current; (b) Zoomed version of load voltage and current during release of load at $t=2$ secs; (c) Peak DC link voltage; (d) Shoot-through duty cycle.                                                                                                                        | 73 |

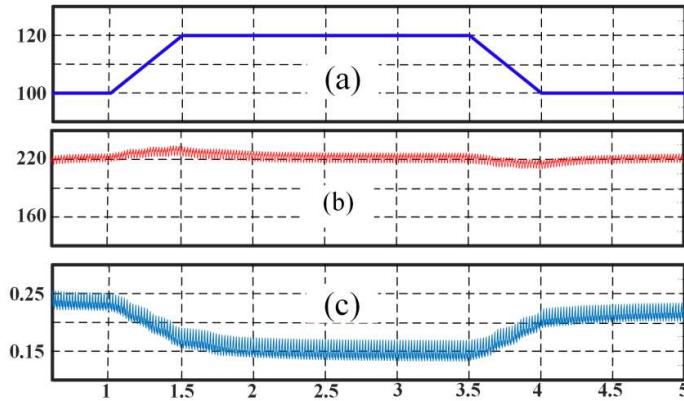

| Fig. 4.12 | Simulation results for closed loop control during change in input voltage: (a) Ramp change in input voltage from 100V to 120V at $t=1$ sec and 120V to 100V at $t=3.5$ secs; (b) Regulated DC link                                                                                                                                                                                                      | 74 |

|           |                                                                                                                                                                                                                                                                                                                           |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | voltage; (c) Change in shoot-through duty cycle.                                                                                                                                                                                                                                                                          |    |

| Fig. 4.13 | Hardware setup of proposed inverter.                                                                                                                                                                                                                                                                                      | 74 |

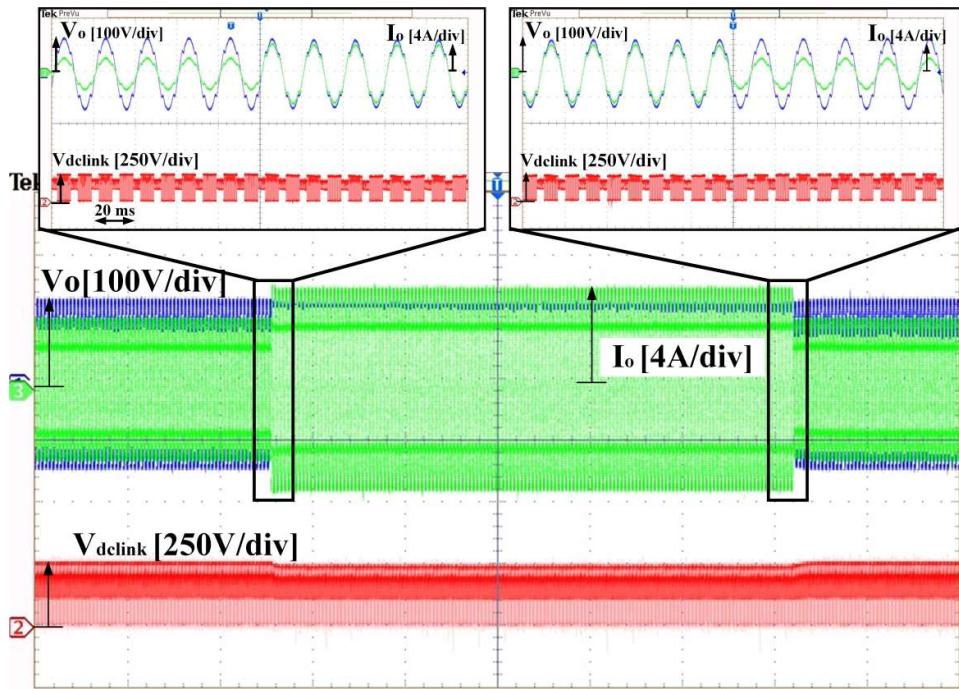

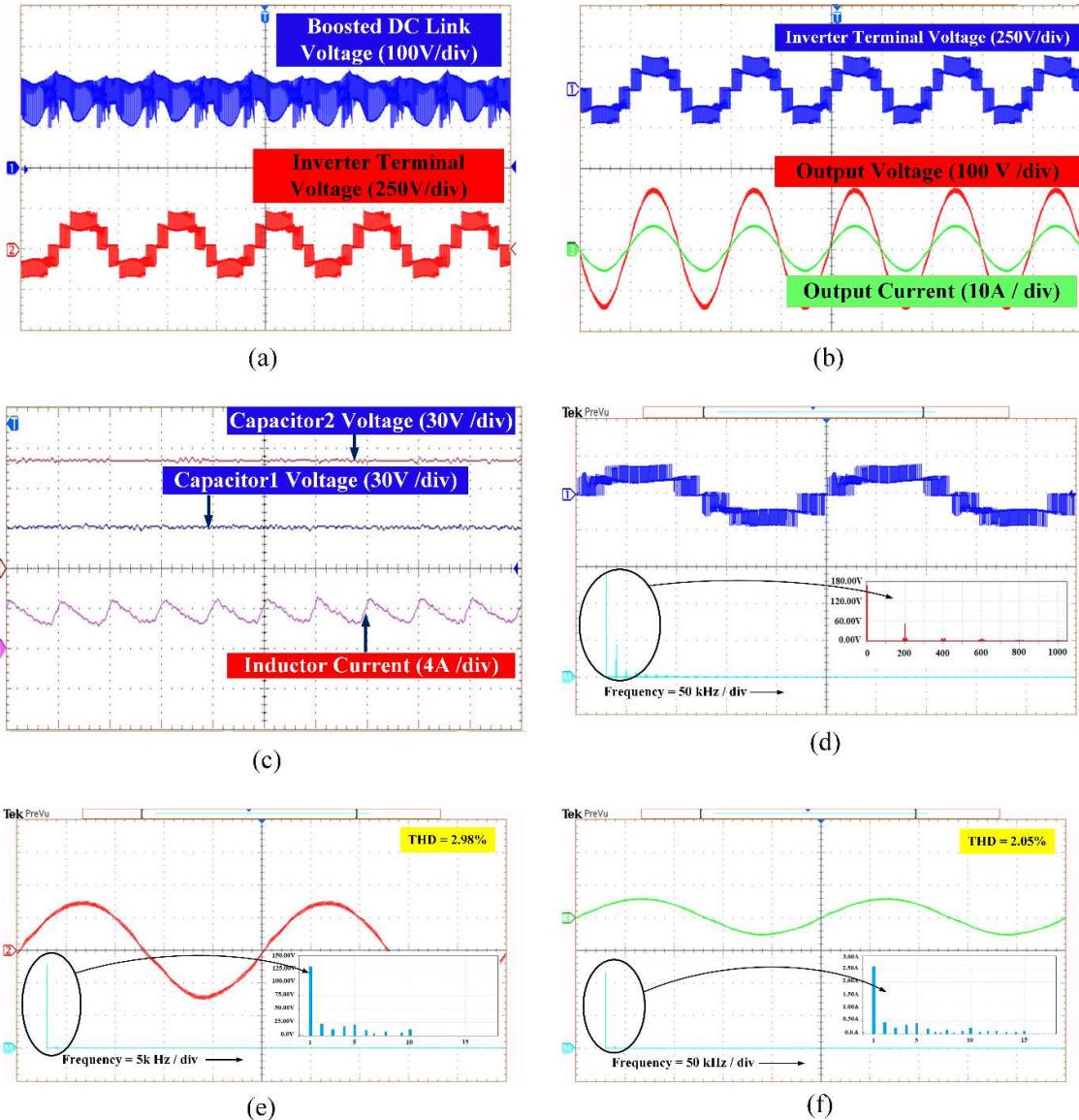

| Fig. 4.14 | Steady State performance of the proposed converter: (a) Boosted dc link voltage, Inverter terminal voltage; (b) Inverter terminal voltage, output voltage and current; (c) $i_{LL}$ , $v_{c1}$ and $v_{c2}$ (d) FFT of inverter terminal voltage; (e) FFT of inverter output voltage; (f) FFT of inverter output current. | 75 |

| Fig. 4.15 | Common mode characteristics of inverter: (a) $V_{AN}$ , $V_{BN}$ and $V_{CMV}$ ; (b) Voltage across parasitic capacitance and leakage current.                                                                                                                                                                            | 76 |

| Fig. 4.16 | Experimental waveform demonstrating the reactive power capability of converter.                                                                                                                                                                                                                                           | 76 |

| Fig. 4.17 | Closed loop results for change in input voltage.                                                                                                                                                                                                                                                                          | 77 |

| Fig. 4.18 | Closed loop results for change in load.                                                                                                                                                                                                                                                                                   | 77 |

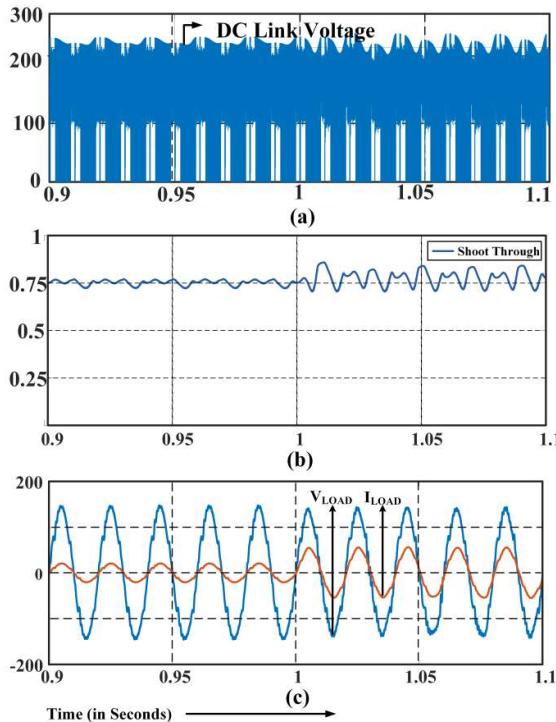

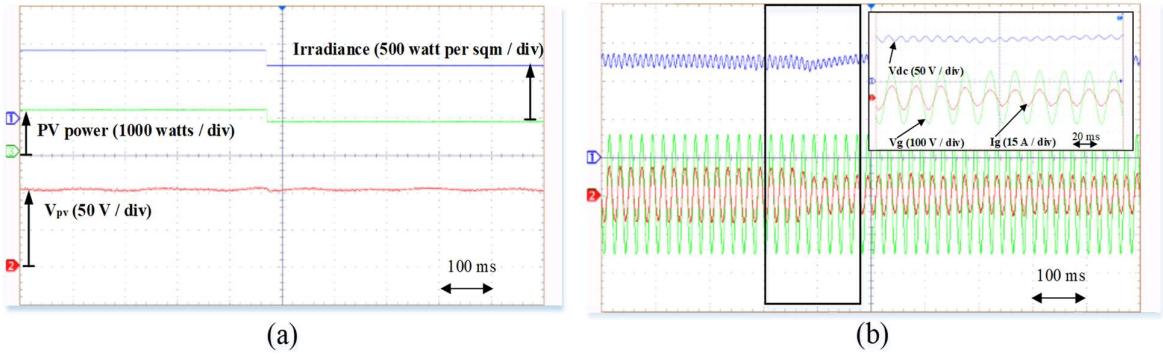

| Fig. 4.19 | Grid-connected mode (a) Variation in input, (b) Variation in output due to change in irradiance.                                                                                                                                                                                                                          | 78 |

| Fig. 4.20 | Efficiency comparison (a) Efficiency of various qzsi, (b) Loss distribution among elements, (c) comparison between calculated and simulated loss.                                                                                                                                                                         | 78 |

| Fig. 5.1  | Dual qZS based improved HERIC structure.                                                                                                                                                                                                                                                                                  | 84 |

| Fig. 5.2  | Operating modes of the proposed inverter that include active states ((a)-(d)), shoot though states ((e)-(f)) and zero state (g).                                                                                                                                                                                          | 86 |

| Fig. 5.3  | Modified PWM Scheme implementation; (a) LSPWM scheme and corresponding signals. (b) Logic for generation of switching signals for $S_1$ - $S_8$ . (c) Switching signals during reactive loads.                                                                                                                            | 87 |

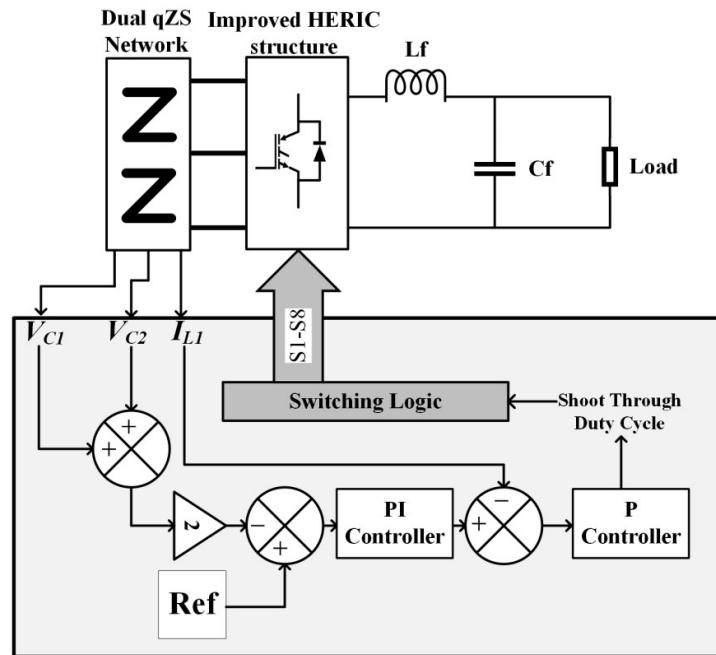

| Fig. 5.4  | Control schematic for the proposed Power converter (DC-link and grid current control).                                                                                                                                                                                                                                    | 90 |

| Fig. 5.5  | Representation of circuit with parasitic elements; (a) Entire system with parasitic elements. (b) Equivalent circuit of the proposed converter in terms of terminal voltage $V_{AN}$ and $V_{BN}$ . (c) Common Mode equivalent circuit.                                                                                   | 91 |

| Fig. 5.6  | Variation of leakage current with respect to ground resistance and parasitic capacitance.                                                                                                                                                                                                                                 | 92 |

| Fig. 5.7  | Simulated waveform of the converter in steady state. (a) Boosted dc-link. (b) Level voltage across output terminals. (c) Output                                                                                                                                                                                           | 93 |

voltage and current.

|           |                                                                                                                                                                                                                                                                                        |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.8  | Simulation results for parasitic elements; (a) Voltages across $V_{AN}$ , $V_{BN}$ and $V_{CMV}$ respectively. (b) Voltage across parasitic capacitance and leakage current.                                                                                                           | 94  |

| Fig. 5.9  | Simulated waveform demonstrating reactive power capability. (a) Level voltage of the converter. (b) Output voltage and current.                                                                                                                                                        | 95  |

| Fig. 5.10 | Dynamic response of the converter for change in source. (a) Change in input voltage. (b) Peak dc-link voltage variation. (c) Change in shoot through duty cycle value.                                                                                                                 | 95  |

| Fig. 5.11 | Figure 5.11. Dynamic response of system subjected to load change. (a) Simulated waveform of load voltage and current during change. (b) Reference and Peak dc-link voltage. (c) Shoot through duty cycle.                                                                              | 95  |

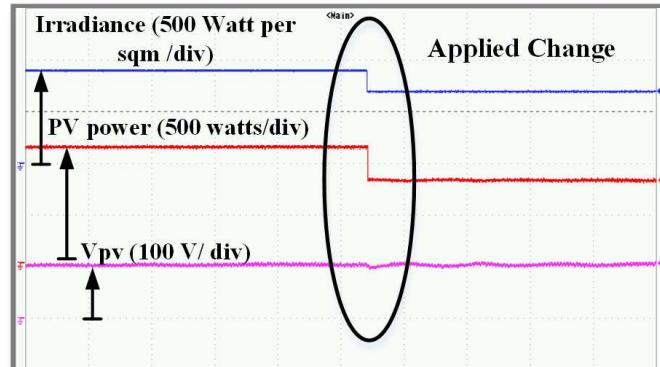

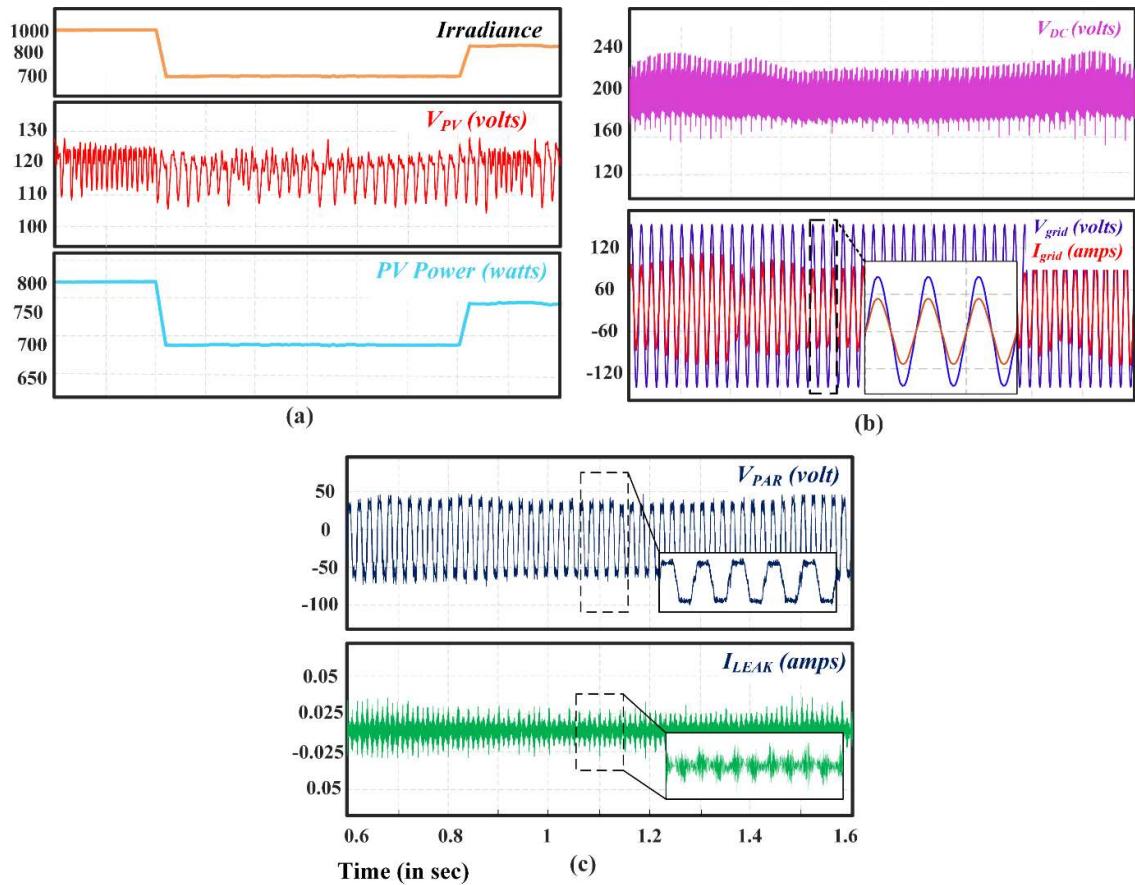

| Fig. 5.12 | Simulation results during grid-tied mode. (a) Solar irradiance, PV Voltage and PV power. (b) Peak dc-link voltage, grid voltage and grid current. (c) Voltage across PV parasitic capacitor and Leakage current.                                                                       | 96  |

| Fig. 5.13 | Experimental prototype of the proposed converter.                                                                                                                                                                                                                                      | 96  |

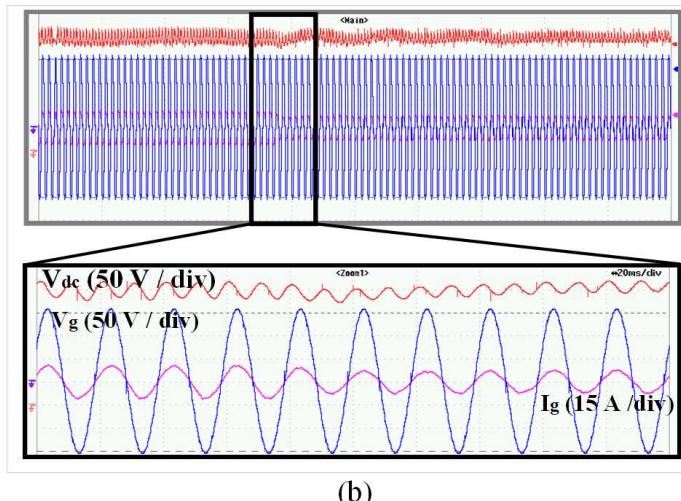

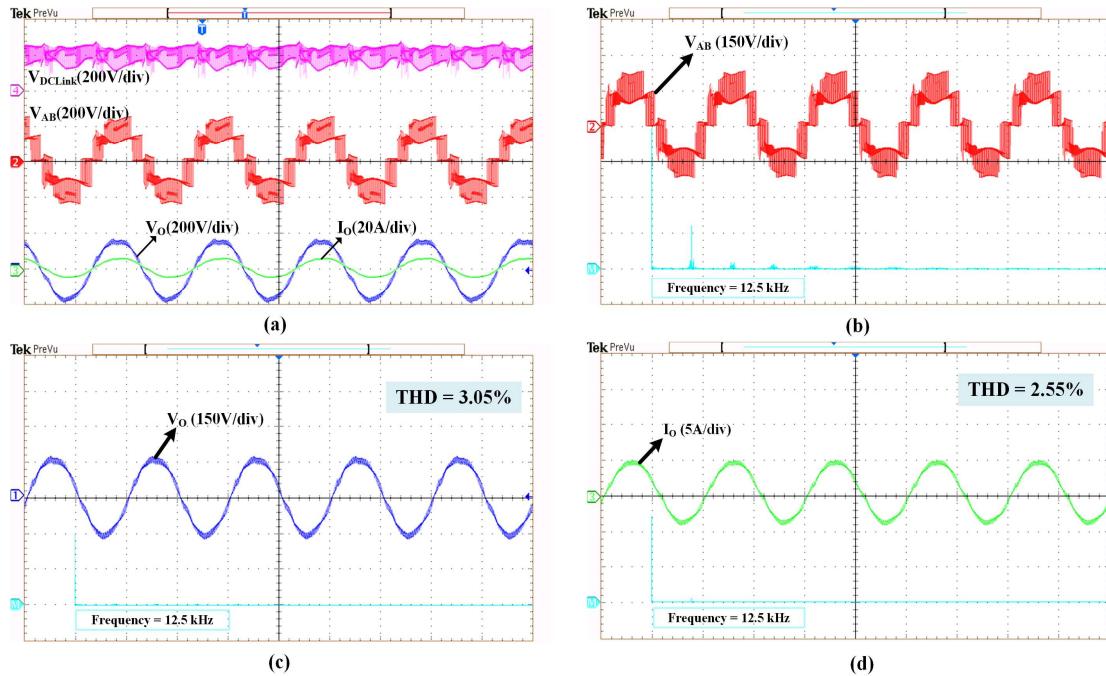

| Fig. 5.14 | Experimental waveform of the proposed converter in steady state (a) Steady state waveform dc-link voltage, level voltage, output voltage and output current. (b) FFT of level voltage ( $V_{AB}$ ). (c) FFT of output filtered voltage ( $V_o$ ). (d) FFT of output current ( $I_o$ ). | 97  |

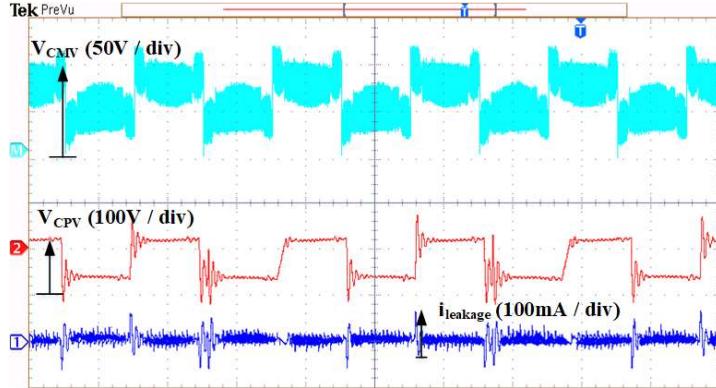

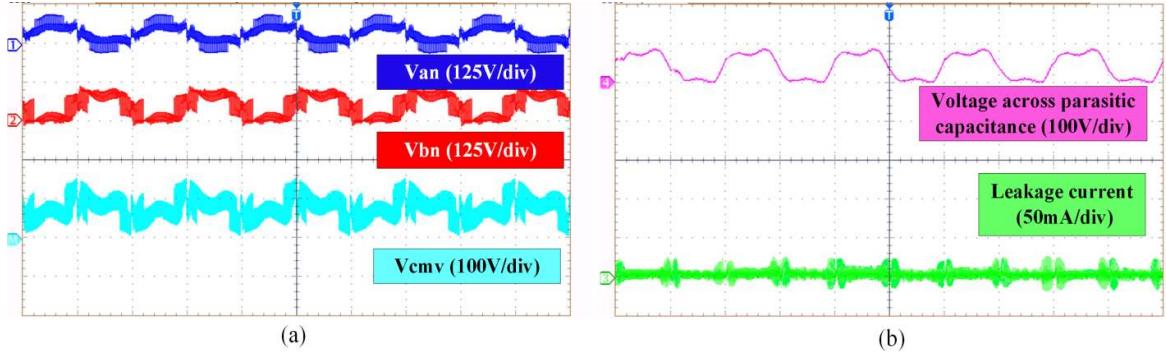

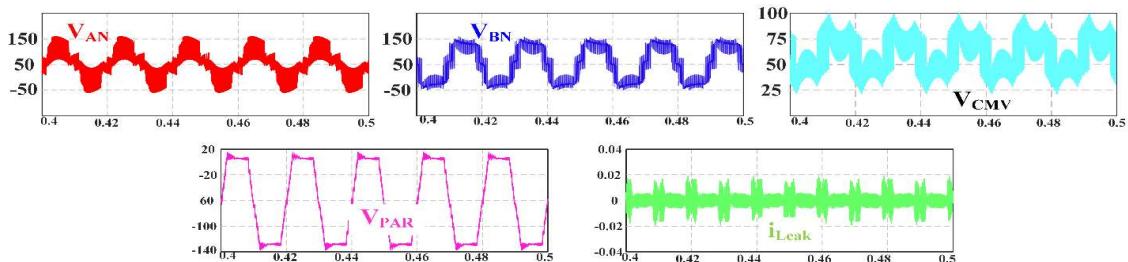

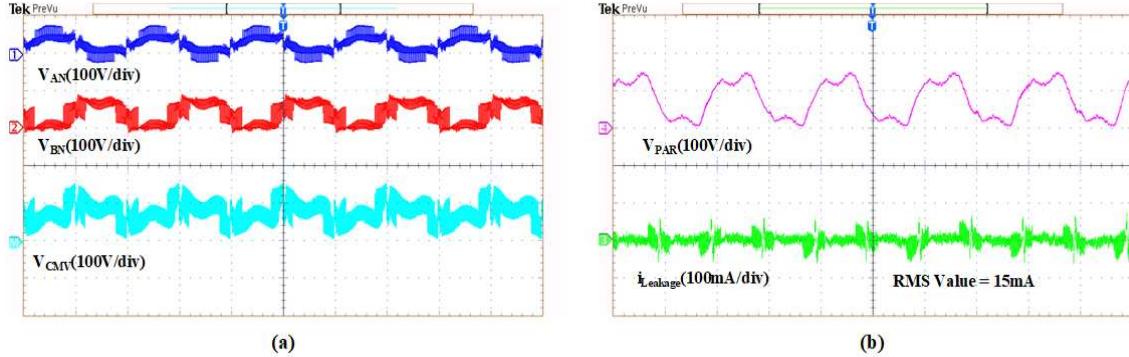

| Fig. 5.15 | Experimental waveform for common mode parameters. (a) Waveform of $V_{AN}$ , $V_{BN}$ and $V_{CMV}$ . (b) Waveforms of voltage across parasitic capacitor ( $V_{PAR}$ ) and leakage current ( $i_{leakage}$ ).                                                                         | 98  |

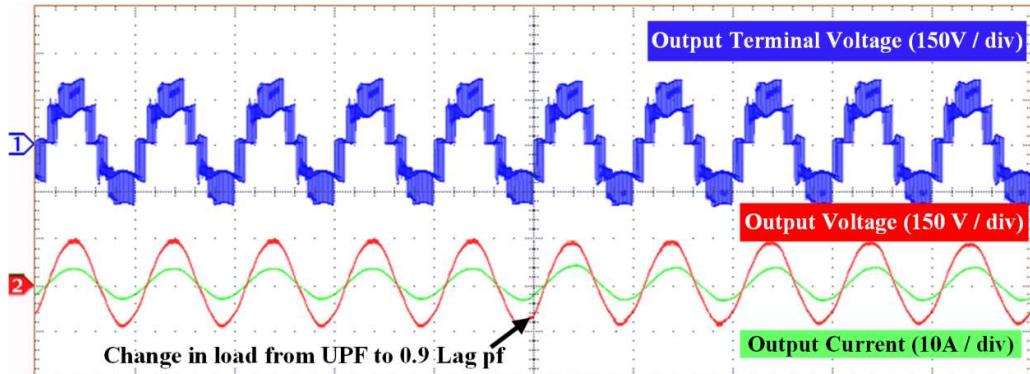

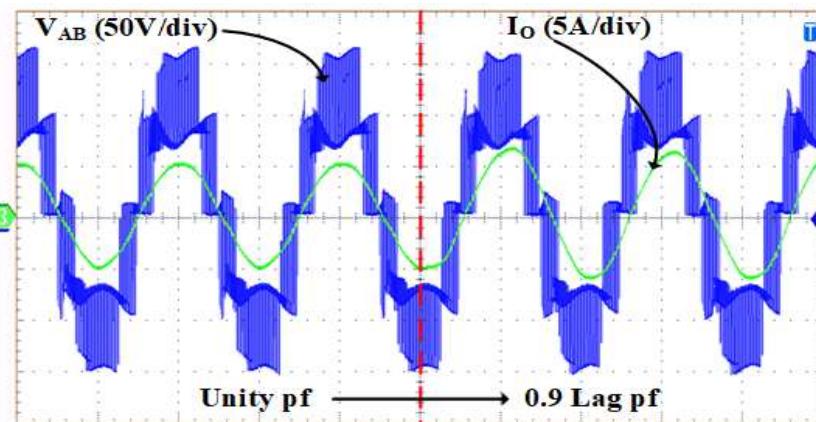

| Fig. 5.16 | Waveform showing reactive power capability of converter.                                                                                                                                                                                                                               | 98  |

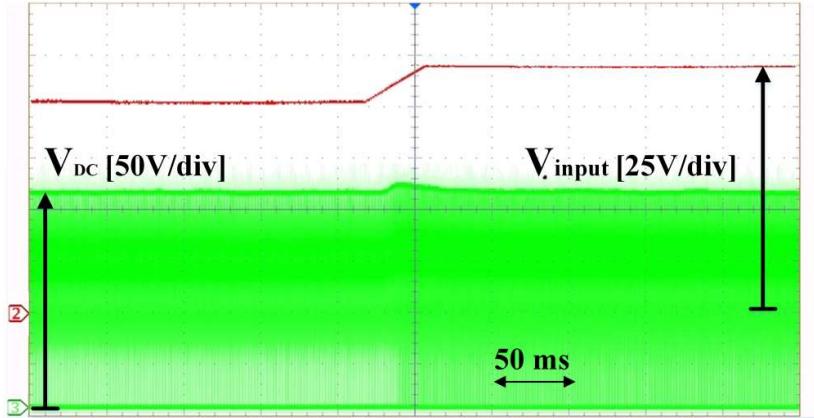

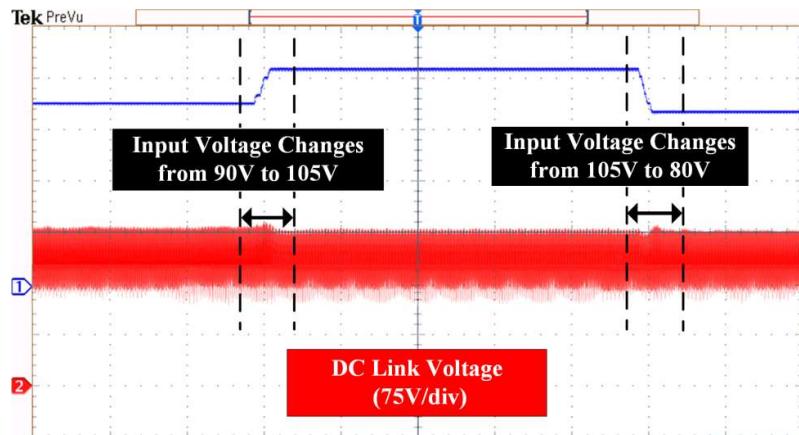

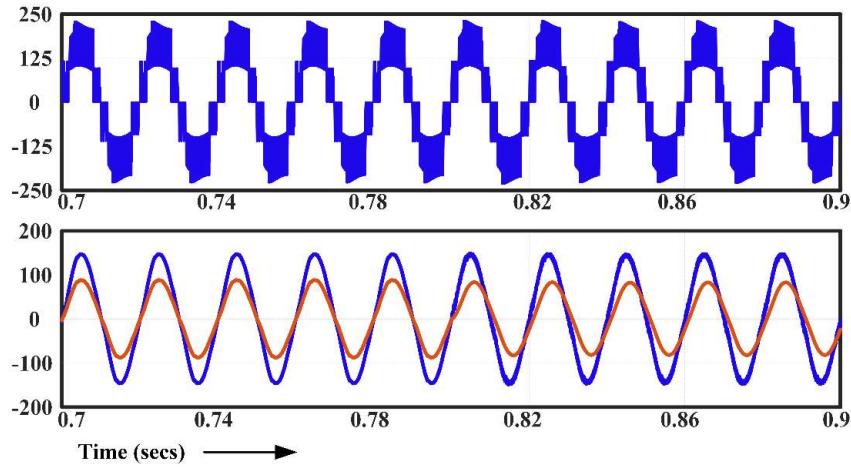

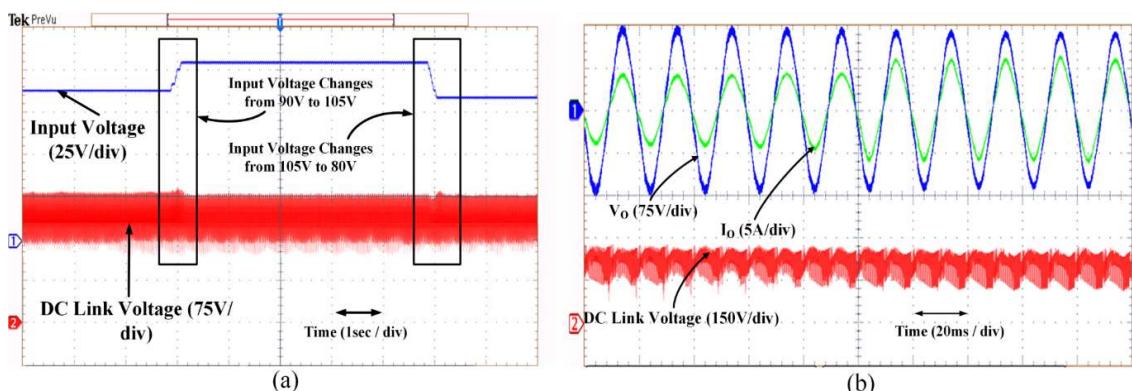

| Fig. 5.17 | Experimental waveform for dynamic performances. (a) Dynamic performance of converter subjected to input voltage change (90V to 105 and 105 to 90V). (b) Dynamic response of the system for load changes from 2.5A to 4A.                                                               | 98  |

| Fig. 5.18 | Results during grid-tied mode. (a) Input side parameters irradiance, PV Voltage, PV power. (b) Output side parameters Peak dc-link voltage, grid voltage and grid current. (c) Voltage across parasitic capacitor and Leakage current.                                                 | 99  |

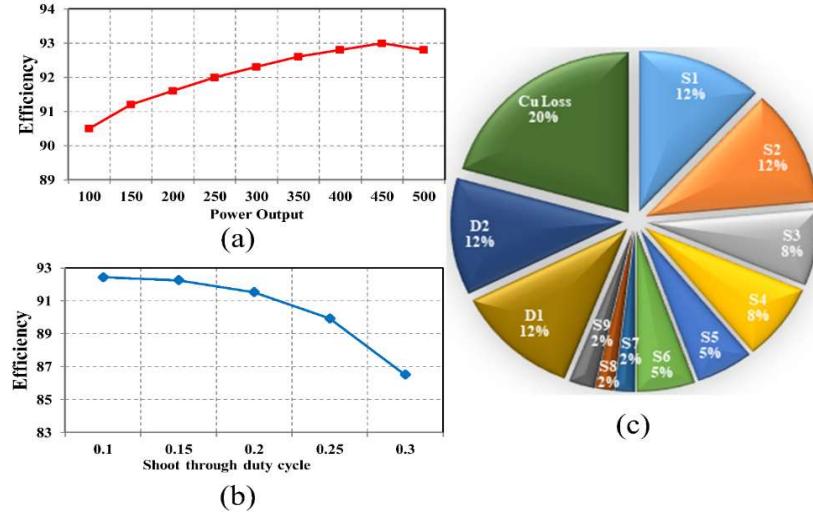

| Fig. 5.19 | Efficiency and loss distribution; (a)Efficiency vs. Output power                                                                                                                                                                                                                       | 101 |

the proposed converter, (b) Efficiency vs. Shoot through duty cycle, (c) Loss distribution among various elements.

|         |                                                            |     |

|---------|------------------------------------------------------------|-----|

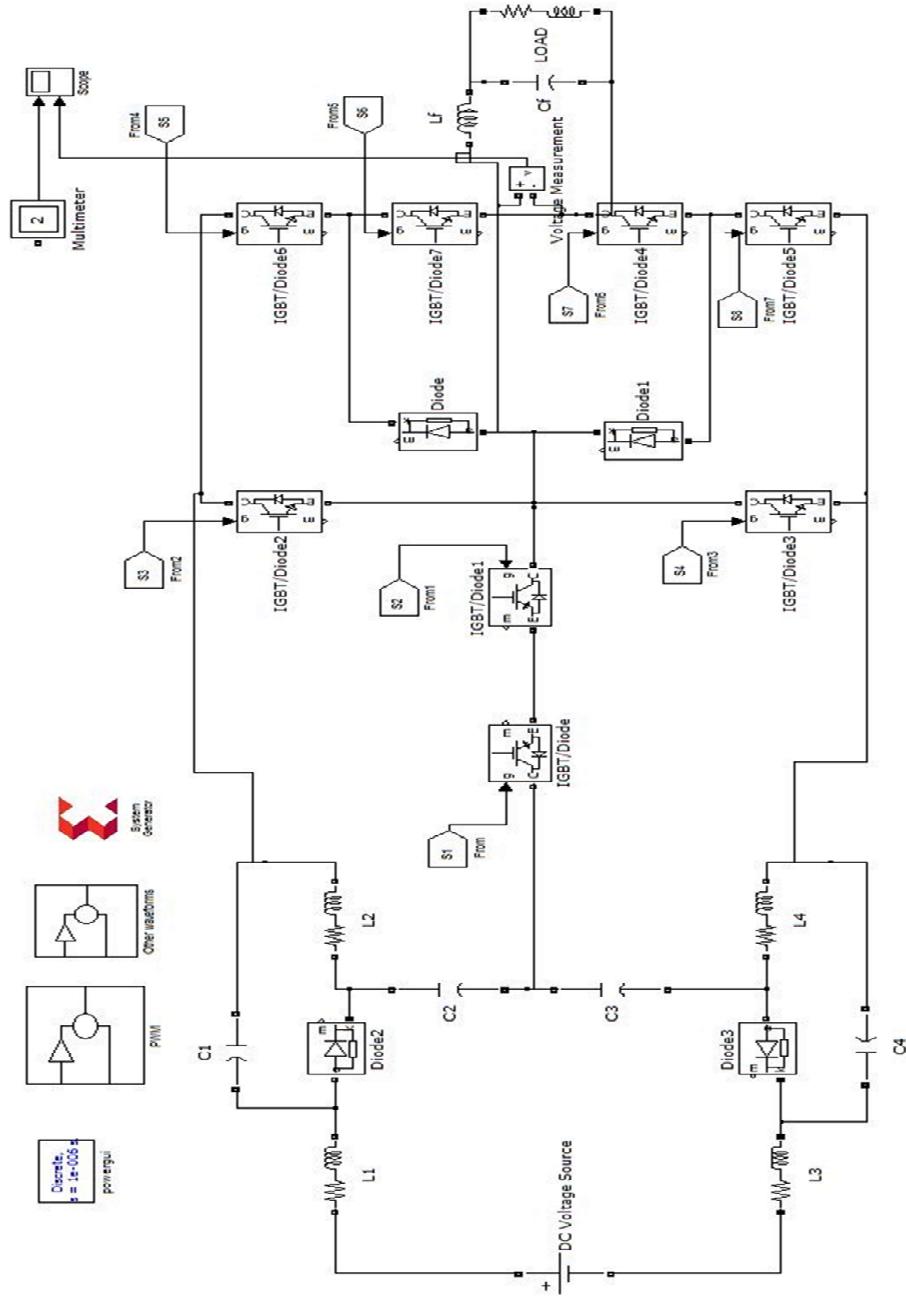

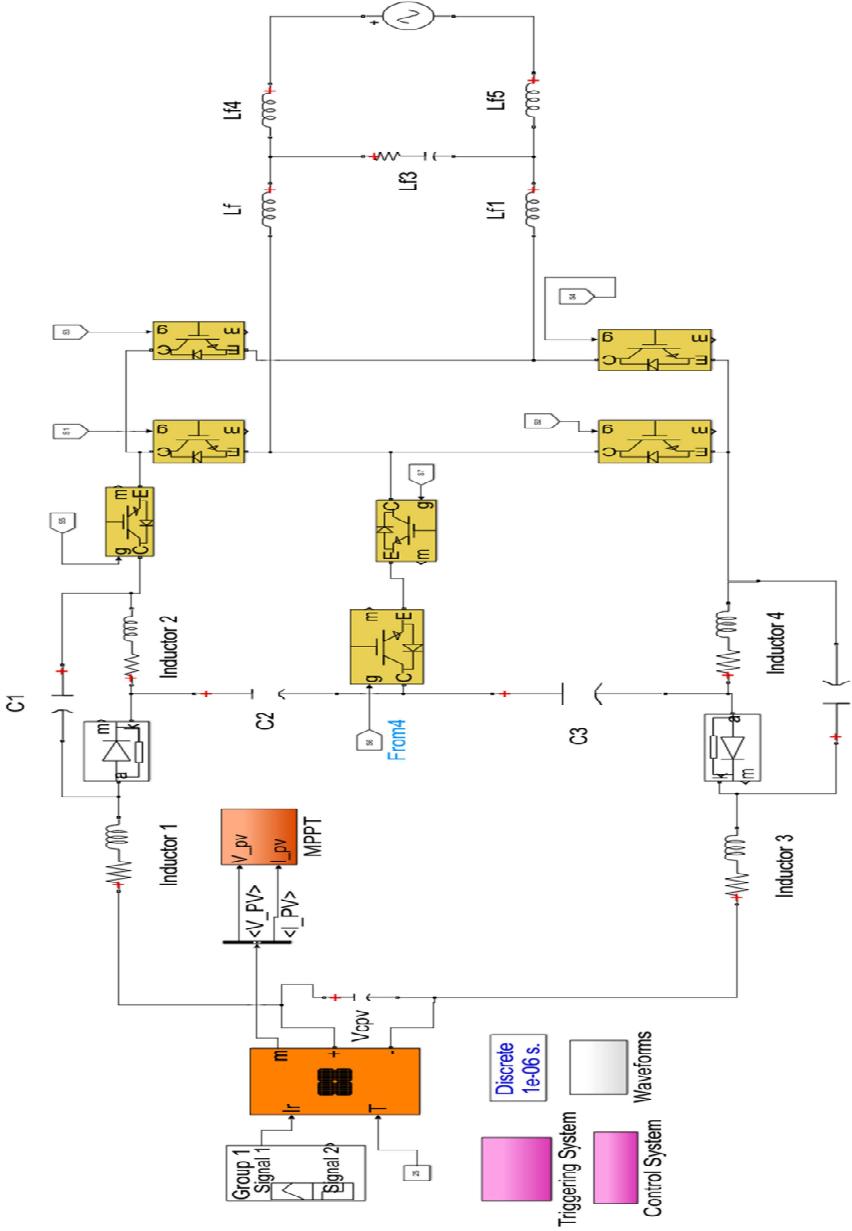

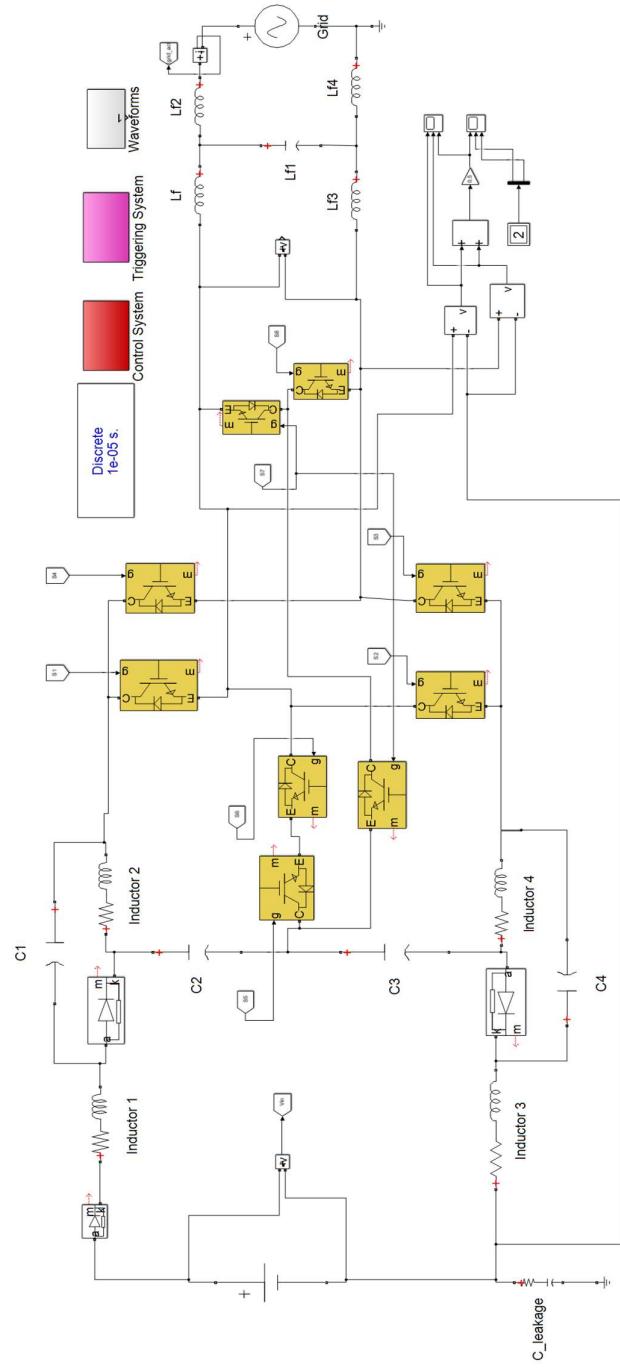

| Fig. A1 | Simulink model for qZS based NPC T-type inverter.          | 119 |

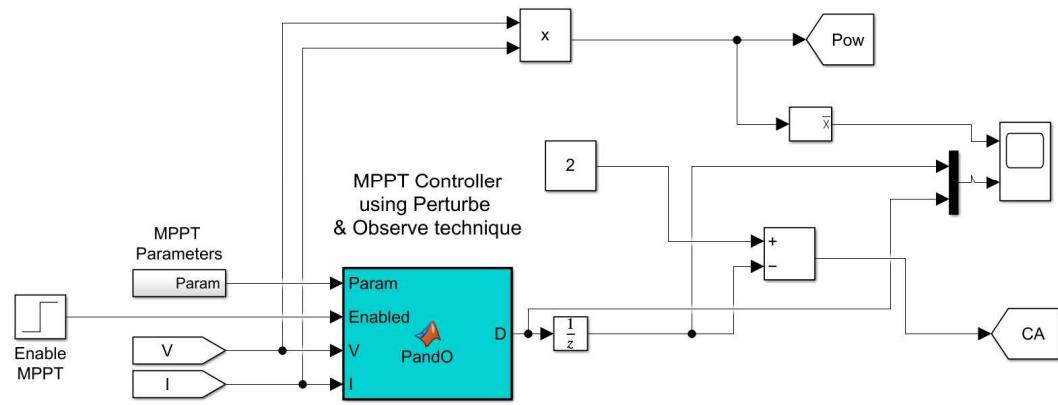

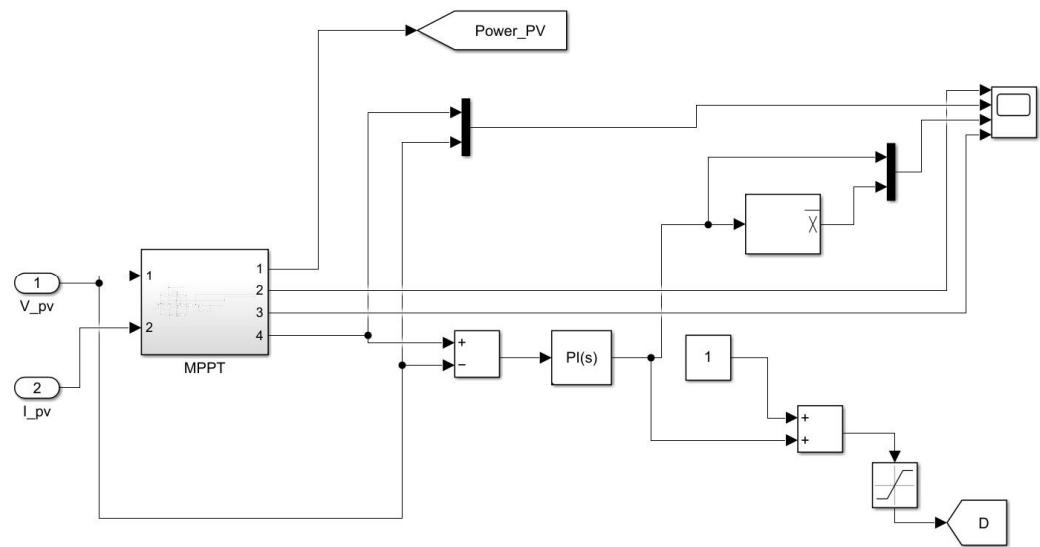

| Fig. A2 | Simulink model of MPPT based DC-link voltage control.      | 120 |

| Fig. A3 | Simulink model of grid current control.                    | 120 |

| Fig. A4 | Simulink model for Dual qZS based improved H5 inverter.    | 121 |

| Fig. A5 | Simulink model of MPPT based DC-link voltage control.      | 122 |

| Fig. A6 | Simulink model of grid current control.                    | 122 |

| Fig. A7 | Simulink model for Dual qZS based improved HERIC inverter. | 123 |

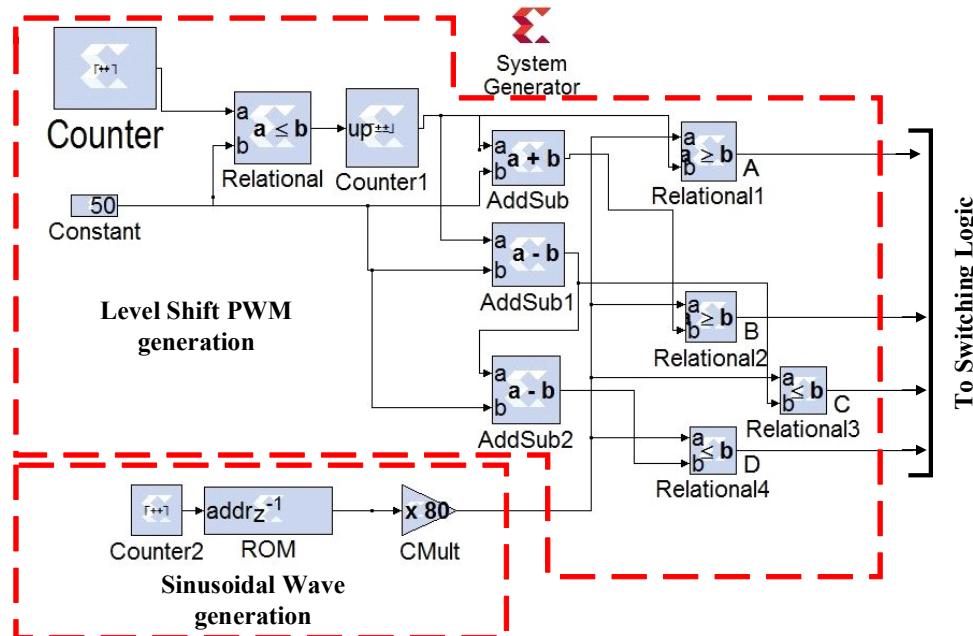

| Fig. B1 | FPGA-Simulink model to generate pulses using LSPWM.        | 124 |

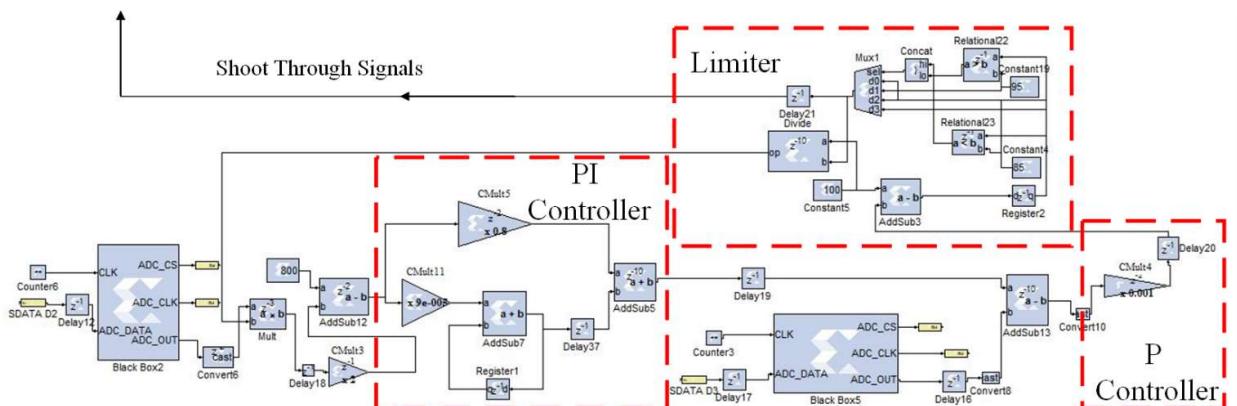

| Fig. B2 | FPGA-Simulink model to control DC-link voltage.            | 124 |

## LIST OF TABLES

---

---

|           |                                                                                           |     |

|-----------|-------------------------------------------------------------------------------------------|-----|

| Table 1.1 | Grid Codes for PV Inverters                                                               | 13  |

| Table 2.1 | Comparison of Various Impedance Source Networks                                           | 19  |

| Table 2.2 | Comparative Assessment of qZS Based Five-Level Topologies                                 | 31  |

| Table 3.1 | Switching States of the qZS-NPC-T <sup>2</sup> I                                          | 42  |

| Table 3.2 | Simulation and Experimental Parameters                                                    | 47  |

| Table 3.3 | Component Comparison of Proposed Topology with Existing Topologies                        | 59  |

| Table 3.4 | Voltage Stress Comparison                                                                 | 59  |

| Table 4.1 | Switching Table for Proposed Converter                                                    | 66  |

| Table 4.2 | Simulation and Experimental Parameters                                                    | 71  |

| Table 4.3 | Complete Comparisons with Existing Topologies                                             | 80  |

| Table 5.1 | Switching Sequence                                                                        | 85  |

| Table 5.2 | Simulation and Experimental Parameters                                                    | 93  |

| Table 5.3 | Complete Comparison of Proposed Topology with Existing Topologies                         | 102 |

| Table 5.4 | Voltage Stress Comparison                                                                 | 103 |

| Table 6.1 | Comparative Analysis of Proposed Topologies with Existing qZS based Five-Level Topologies | 107 |

## ABBREVIATIONS

---

---

|         |                                                      |

|---------|------------------------------------------------------|

| AC      | Alternating Current                                  |

| ADC     | Analog to Digital Converter                          |

| CCM     | Continuous Conduction Mode                           |

| CHB     | Cascaded H Bridge                                    |

| CMV     | Common Mode Voltage                                  |

| CMF     | Common Mode Filter                                   |

| CMI     | Cascaded Multilevel Inverter                         |

| CST     | Complete Shoot Through                               |

| DCM     | Discontinuous Conduction Mode                        |

| DC      | Direct Current                                       |

| EMI     | Electro Magnetic Interference                        |

| FC      | Flying Capacitor                                     |

| FFT     | Fast Fourier Transform                               |

| FPGA    | Field Programmable Gate Array                        |

| FB-NPC  | Full Bridge Neutral Point Clamped                    |

| HFT     | High Frequency Transformer                           |

| HERIC   | Highly Efficient and Reliable Inverter Configuration |

| HBZVR   | Half Bridge Zero Voltage Rectifier                   |

| HBZVR-D | Half Bridge Zero Voltage Rectifier with Diode        |

| IS      | Impedance Source                                     |

| IRENA   | International Renewable Energy Agency                |

| IEEE    | Institute of Electrical and Electronics Engineers    |

| IEC     | International Electro technical Commission           |

| LCCT    | Inductor-Capacitor-Capacitor-Transformer             |

| LSPWM   | Level Shifted Pulse Width Modulation                 |

| LFT     | Low Frequency Transformer                            |

| LST     | Lower Shoot Through                                  |

| MPPT    | Maximum Power Point Tracking                         |

| MLI     | Multilevel Inverter                                  |

| NPC     | Neutral Point Clamped                                |

| PV      | Photovoltaic                                         |

|       |                                                                       |

|-------|-----------------------------------------------------------------------|

| PF    | Power Factor                                                          |

| PLL   | Phase Locked Loop                                                     |

| P     | Proportional                                                          |

| PI    | Proportional-Integrator                                               |

| PR    | Proportional-Resonant                                                 |

| PWM   | Pulse Width Modulation                                                |

| PSIM  | Power Simulation                                                      |

| PCB   | Printed Circuit Board                                                 |

| P & O | Perturb and Observe Method                                            |

| qZS   | Quasi Z-Source                                                        |

| RES   | Renewable Energy Sources                                              |

| SPWM  | Sinusoidal Pulse Width Modulation                                     |

| ST    | Shoot Through                                                         |

| SVM   | Space Vector Modulation                                               |

| THD   | Total Harmonic Distortion                                             |

| UPF   | Unity Power Factor                                                    |

| UST   | Upper Shoot Through                                                   |

| VSI   | Voltage Source Inverter                                               |

| VDE   | <i>Verband der Elektrotechnik, Elektronik und Informationstechnik</i> |

| ZS    | Z-Source                                                              |

| ZSI   | Z-Source Inverter                                                     |

## LIST OF SYMBOLS

---

---

|                 |                                       |

|-----------------|---------------------------------------|

| $B$             | Boost Factor                          |

| $C_1$           | Capacitor 1 of the Impedance network  |

| $C_2$           | Capacitor 2 of the Impedance network  |

| $C_3$           | Capacitor 3 of the Impedance network  |

| $C_4$           | Capacitor 4 of the Impedance network  |

| $C_f$           | Output Filter Capacitor               |

| $C_{PAR}$       | Parasitic Capacitance of the PV panel |

| $C_{PV}$        | Input capacitor after PV panel        |

| $D_{SH}$        | Shoot-through Duty cycle              |

| $D_1, D_2$      | Diodes of Impedance network           |

| $f_s$           | Switching frequency                   |

| $f_o$           | Output frequency                      |

| $I_O$           | Output current                        |

| $I_{grid\_act}$ | Sensed Grid Current                   |

| $I_{grid}^*$    | Reference grid current                |

| $i_L$           | Inductor current                      |

| $I_{PV}$        | Photovoltaic Current                  |

| $i_{LEAKAGE}$   | Leakage current                       |

| $K_p$           | Proportional constant                 |

| $K_i$           | Integrator constant                   |

| $K_r$           | Resonant constant                     |

| $k_{C1}$        | Ripple factor for capacitor 1 voltage |

| $k_{C2}$        | Ripple factor for capacitor 2 voltage |

| $K_L$           | Ripple factor for inductor current    |

| $L_{I-L_4}$     | Inductances of qZS network            |

| $L_f$           | Filter inductance                     |

| $m$             | Modulation index                      |

| $P_{out}$       | Output Power                          |

| $P_{IN}$        | Input Power                           |

|               |                                                                       |

|---------------|-----------------------------------------------------------------------|

| $R_g$         | Ground Resistance                                                     |

| $V_{pv}$      | Input PV voltage                                                      |

| $V_{AN}$      | Voltage across inverter terminal A and negative terminal of PV source |

| $V_{BN}$      | Voltage across inverter terminal B and negative terminal of PV source |

| $V_{CMV}$     | Common mode voltage                                                   |

| $V_g$         | Grid Voltage                                                          |

| $V_{out}$     | Output Voltage                                                        |

| $V_L$         | Voltage across inductor of impedance source                           |

| $V_C$         | Voltage across capacitor of impedance source                          |

| $V_{DC}$      | DC-Link Voltage                                                       |

| $V_{DC\_act}$ | Sensed DC-link Voltage                                                |

| $V_{DC}^*$    | Reference DC-Link Voltage                                             |

| $V_{CPV}$     | Voltage across parasitic capacitance                                  |

# Chapter 1

## INTRODUCTION

# Chapter 1

## Introduction

---

---

### 1.1. Background

Renewable energy sources are steadily establishing themselves as promising energy sources to substitute fossil fuels over the last few decades. They have the potential to counter the harmful effects produced by fossil fuels by providing cleaner energy. Non-conventional energy sources like solar, wind and fuel cell are emerging as alternate power generating systems, which could reduce the dependence on conventional energy sources. Of these, solar photovoltaic (SPV) systems are poised to be the most dominant sources due to their abundance, zero-carbon emission, reducing cost of panels, absence of moving parts and advancements in power semiconductor switching device technology and inverter topologies. According to international agencies like IRENA, PV power system holds 24.3% amongst all non-conventional energy sources installed across the globe. With a worldwide installed capacity of 709GW [1] (Fig. 1.1) and an unprecedented growth rate of 24%, solar photovoltaic systems are poised to become a major source of energy generation in the foreseeable future.

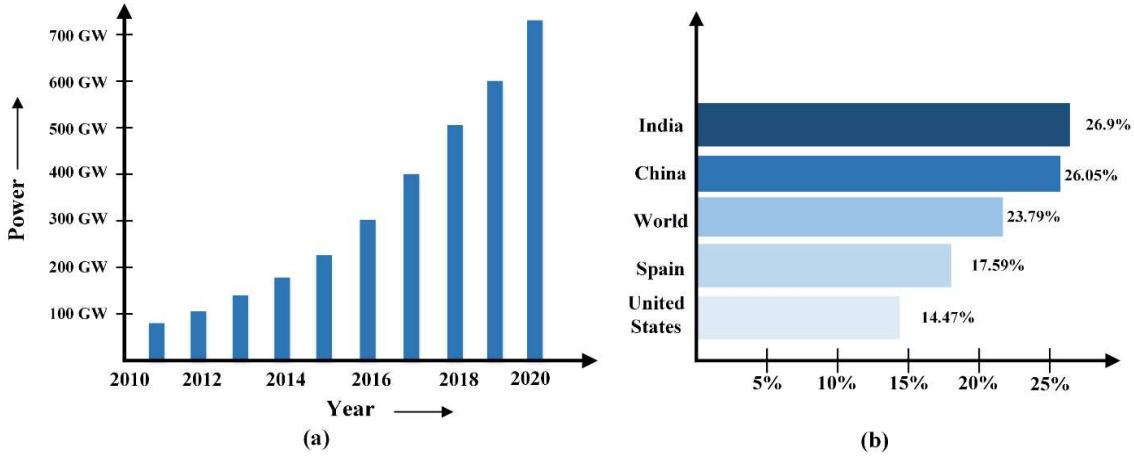

In general, PV sources produce DC power and need to be interfaced with the utility/load. The development of power electronic interface is quite an important part in PV power system as shown in Fig. 1.2. The operation of PV systems can be classified in to 2 modes (i) Stand-alone mode, (ii) Grid connected mode [2]. In stand-alone mode of operation, the power processed from the PV source is directly fed to load and stored in batteries for further use. This operating mode is most effective in providing electricity to remote areas where both forms of power (AC and DC) could be utilised. Batteries are the primal source of energy storage in this mode of operation which increases the overall control complexity of the system. Whereas, in grid-connected mode of operation, the power is injected to utility and residential loads based on the requirement[3]. These systems do not need energy storage devices and hence, are a more popular form of PV power generation. More than 90% of worlds PV systems are grid connected due to advantages like low cost, limited storage requirement and negligible maintenance[4]. However, variations in PV output, improved efficiency, reduced count of power semiconductor devices, improved control structure, common mode voltage (CMV) and leakage current due to parasitic capacitance have impelled

the researchers for further development of new Power Conditioners for PV applications in the present scenario.

Figure 1.1 Solar PV trends. (a) Increasing trend of PV installation, (b) percentage change in solar energy with respect to 2020

Figure 1.2 Basic Power Electronics interface

## 1.2. Photovoltaic Technology

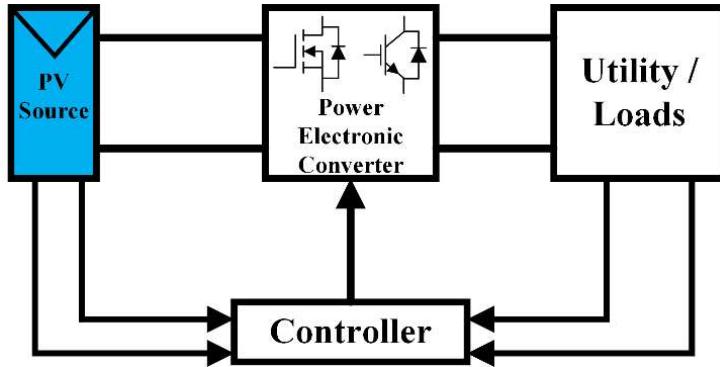

In general, PV cells produce an open cell voltage of 0.6V. Therefore, many cells are needed in series and parallel combinations for the desired output voltage. Further, photovoltaic technology can be classified into four categories *viz.* module, string, multi-string, and central inverters based on their output power rating and PV module arrangement. A brief discussion of the types of inverter configuration is provided below[5]–[7].

### 1.2.1. AC Module Inverters

They are formed with an amalgamation of micro inverter and PV panels as shown in Fig. 1.3(a). They are the ‘plug-and-play’ type and typically output low power as they are connected to single PV panels. Module inverters are best known for accurately tracking maximum power point (MPPT) in mismatch conditions (partial shading). These kinds of

inverter may have additional DC-DC converter stage and transformer to provide galvanic isolation.

### **1.2.2. String Inverters**

The string inverter depicted in Fig. 1.3(b) shows the string configuration where the inverter is fed from a series of PV panels. The total number of strings connected depends on the load requirement and thus, a DC-DC converter can also be interfaced. String inverters have lower efficiency in achieving MPPT during partial shading conditions than modular inverters. These are typically used in residential applications due to medium output power level and they lack galvanic isolation.

### **1.2.3. Multi-String Inverters**

The multi-string concept is an expanded form of the string inverter to improve power level and flexibility. As shown in Fig. 1.3(c), each PV string is provided with its own DC-DC converter which functions as an MPPT tracker, voltage booster and feed power to DC bus bar. An inverter processes this power from the DC bus bar to utility/load. This concept makes the system more reliable and efficient during partial shading conditions. These are used for medium and large power applications like residential or commercial purposes.

### **1.2.4. Central Inverters**

Central inverter configuration depicted in Fig. 1.3(d) shows how power from the PV array is fed to utility through a single inverter system. In this configuration, PV panels are connected in series and parallel to obtain large power output. The strings are connected in a parallel manner through diodes to avoid reverse current flow. These inverters are highly reliable and have maximum operating life compared to all other configurations but they suffer from lowest energy extraction (MPPT) and are inefficient to overcome mismatch problems. Central inverters are typically used for large power commercial applications.

## **1.3. Power Electronics Interfaces**

Based on power processing stages, the PV inverters can be divided into 2 types: double-stage inverters and single-stage stage inverters[5], [7], [8].

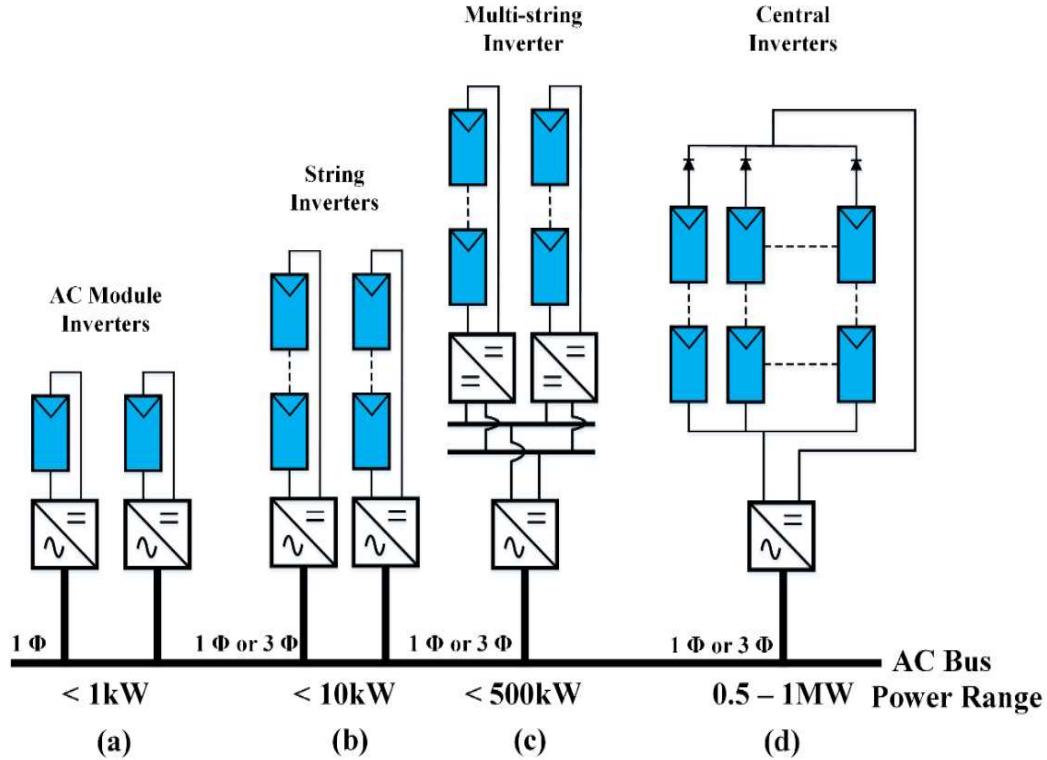

### **1.3.1. Double-Stage Inverters**

Most of the PV modules generate low output voltage hence, it becomes essential to boost input voltage based on requirement. Fig. 1.4 shows the basic configuration of double-stage inverters where the configuration consists of 2 power processing stages, the first of which is voltage boosting and the second is voltage inversion. Voltage boosting is achieved

by a DC-DC converter which operates at high frequency, and then boosted DC voltage goes through inversion to feed the load. Due to additional boosting stage, they require lesser number of PV panels than single stage inverters and also provide excellent MPPT during partial shading conditions. However, the additional power processing stage and requirement of higher components increases the size, cost and deteriorates its efficiency.

Figure 1.3 PV configurations based on module arrangement and power handling capability

Figure 1.4 Typical Two-Stage Power Converter Topology

### 1.3.2. Single-Stage Inverters

The power is processed in a single-stage in such types of inverters. They don't require additional boosting stage and can be further classified into two types, namely, simple single-

stage inverters (Fig. 1.5(a)) and SSBI (Fig. 1.5(b)). Simple single-stage inverters are just like multi-string inverters or central inverter where inverters are fed directly from PV panels. They have low efficiency in extracting maximum power and require a larger number of PV panels. However, SSBI integrate boosting and inverting stage to a single seamless configuration and incorporate advantages like good MPP tracking, high efficiency, low component requirement and high reliability. Furthermore, these systems need to interface with the grid in order to supply into excess power to grid. Based on the type of connection with grid, they can be further classified in to two sub categories which are isolated and non-isolated connections.

### 1.3.2.1 Isolated Topologies

Isolated topologies provide galvanic isolation between the PV source and the utility. Mostly, galvanic isolation is provided by the presence of transformer in the system which eliminates leakage current and DC current injection into utility. The placement of transformer can be done in 2 ways: (i) placing the transformer between inverter and utility (Fig. 1.6(a)), (ii) placing the transformer between source and inverter (Fig. 1.6(b)). The former one is a low frequency transformer (50/60 Hz) and the latter one is high frequency transformer and, in both the cases it degrades the system efficiency, increases the cost and makes it bulky.

### 1.3.2.2 Non-Isolated Topologies

Non-isolated topologies alternatively known as transformerless topologies, are shown in Fig. 1.5, these are topologies which do not provide galvanic isolation between source and utility. Though the system becomes lighter and more efficient, absence of galvanic isolation creates a resonant path that triggers leakage current. The prime motive of the topologies is to suppress the leakage current flowing from utility to PV source with various modulation techniques and power semiconductor device rearrangement.

Figure 1.5 Single stage topologies; (a) Buck type single stage topology, (b) Single stage boost type topology

Figure 1.6 Typical scheme for Isolated based topologies; (a) Isolated topologies with LFT, (b) Isolated topologies with HFT.

## 1.4 The Impedance Source Inverter

From the above discussion, it is clear that the inverter configuration can be classified into various categories based on power levels, power processing stages and interconnection with grid. However, for medium and large power applications, multi-string and central inverters are suitable, and these can be further connected in either two-stage or single-stage system. Due to the presence of additional DC-DC converter, two-stage systems provide good maximum power extraction and require fewer PV panels in series. Further, the presence of additional active and passive components makes the two-stage system bulky, less efficient and less reliable. Hence, single-stage systems which are capable of achieving boosting and inverting are best suited for PV generating system.