# **Investigation on Single-Phase Step-Up Multilevel Inverters for Photovoltaic Standalone Applications**

Thesis

Submitted in partial fulfillment of the requirements

for the award of the degree of

**Doctor of Philosophy

in

Electrical Engineering**

By

**Sambhani Madhu Babu**

**(Roll No. 717013)**

**Supervisor**

**Dr. B.L. Narasimharaju**

Associate Professor

**Department of Electrical Engineering**

**National Institute of Technology Warangal**

(An Institute of National Importance)

**Warangal-506004, Telangana, India**

**July - 2022**

Dedicated to

**My beloved Mother**

## APPROVAL SHEET

This thesis entitled "**Investigation on Single-Phase Step-Up Multilevel Inverters for Photovoltaic Standalone Applications**" by **Mr. Sambhani Madhu Babu** is approved for the degree of Doctor of Philosophy.

### Examiners

.....

.....

.....

### Supervisor

**Dr. B.L. Narasimharaju**

Associate Professor

Department of Electrical Engineering, NIT Warangal.

### Chairman

**Dr. D.M. Vinod Kumar**

Professor

Department of Electrical Engineering, NIT Warangal.

Date:.....

Department of Electrical Engineering

National Institute of Technology Warangal

Warangal - 506004, Telangana State, India.

DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

WARANGAL-506004

## **CERTIFICATE**

This is to certify that the thesis entitled "**Investigation on Single-Phase Step-Up Multilevel Inverters for Photovoltaic Standalone Applications**", which is being submitted by **Mr. Sambhani Madhu Babu** (Roll No: 717013), is a bonafide work submitted to National Institute of Technology Warangal in partial fulfillment of the requirements for the award of the degree of **Doctor of Philosophy** in Department of Electrical Engineering. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

Date: July 2022

Place: NIT-Warangal

**Dr. B.L. Narasimharaju**

(Supervisor)

Associate Professor

Department of Electrical Engineering

National Institute of Technology Warangal

Warangal - 506004

## DECLARATION

This is to certify that the work presented in the thesis entitled "**Investigation on Single-Phase Step-Up Multilevel Inverters for Photovoltaic Standalone Applications**" is bonafide work done by me under the supervision of **Dr.B.L.Narasimharaju**, Associate Professor, Department of Electrical Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

Date: July 2022

Place: NIT-Warangal

**Sambhani Madhu Babu**

**(Roll no: 717013)**

## ACKNOWLEDGMENTS

It gives me immense pleasure to express my deep sense of gratitude and thanks to my supervisor **Dr. B.L. Narasimharaju**, Associate Professor, Department of Electrical Engineering, National Institute of Technology Warangal, for his invaluable guidance, support, and suggestions. His knowledge, suggestions, and discussions helped me become a capable researcher. He has shown me the imaginative side of this wonderful and potential research area. His encouragement helped me to overcome the difficulties encountered in research as well in my life. I am extremely thankful to him to make me part of SPARC project, SERB-IMPRINT project and other collaborative research activities.

I am grateful to the **institute and other government agencies (SERB-DST, IMPRINT, SPARC and MoE, GoI)** for providing a great research facility, which immensely helped me to carry out the experimentation for my research work.

I wish to express my sincere thanks to **Prof. N. V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

I am very much thankful to **Prof. M. Sailaja Kumari**, Head, Department of Electrical Engineering for her constant encouragement, support and cooperation.

I also express my sincere thanks to **Prof. V.T. Somasekhar** and **Prof. S. Srinivasa Rao**, former heads, Department of Electrical Engineering for their valuable suggestions, support and cooperation.

I take this opportunity to thank all my Doctoral Scrutiny Committee members, **Prof. D. M. Vinod Kumar**, Department of Electrical Engineering, **Prof. S. Srinivasa Rao**, Department of Electrical Engineering, **Dr. P. Selvi**, Assistant Professor, Department of Electrical Engineering and **Dr. P. Muthu**, Associate Professor and Head, Department of Mathematics for their detailed review, constructive suggestions and excellent advice during the progress of this research work.

I am grateful to **Prof. V.T. Somasekhar**, **Prof. S. Srinivasa Rao**, **Dr. A. Kirubakaran**, Assistant Professor, **Dr. A.V. Giridhar**, Assistant Professor, **Dr. Ch. Ramulu**, Assistant Professor, **Dr. G. Siva Kumar**, Assistant Professor, **Dr. Vinay Kumar T.**, Assistant Professor, for sharing the hardware equipment for my research work.

I also appreciate the encouragement from teaching and non-teaching members of Department of Electrical Engineering. They have always been encouraging and supportive.

I am indebted to Dr. Ratna Rahul Tupakula, Dr. Venu Sonti, Dr. V.V.K. Satyakar, Mr. Dharmesh Y., Mr. K. Hemasundar Rao, Dr. P Srinivas, Dr. K. Narendar Reddy, Mr. P Hemakumar, Mr. K. Ashok Kumar, Mr. M.F. Baba and Mr. Sumon Dhara for their brotherly care and unconditional support throughout my PhD journey.

I convey my special thanks to contemporary research scholars Dr. Vijaybabu K, Dr. U. Ramanjaneyulu, Dr. Ch. Kasi Ramakrishna Reddy, Dr. Hareesh M., Dr. Suresh L., Dr. K. V. Praveen Kumar, Dr. M. Santosh, Dr. A Pranay Kumar Mr. S. Ramkumar, Dr. K. Sateesh Kumar, Dr. Bhaskar Gupta, Dr. Dileep Krishna, Dr. B Laxman, Dr. K. Eswar, Mr. P Manoj, Mr. M. Kalyan Chakravarthi, Mr. Ch. Madhu Kishore, Dr. P Mounica, Dr. Rambabu M, Mr. K Srinivas, Mr. G. Ramesh, Mr. D. Ramesh, Mr. D. Satish Reddy, Mr. Chinmay Kumar Das, Dr. Vijay Vardhan Reddy and Mr. Sagar Petkar for being with me during my research journey.

I heartily thankful to institute health center staff and especially to **Dr. Srivastava** and **Dr. Anchoori Karthik** for being compassionate during my health emergencies.

I acknowledge my gratitude to all my teachers and colleagues at various places for supporting and co-operating with me to complete the work. I gratefully acknowledge my friends and extended family members **Jafar Sadik, K. Sriram, B. Swamy, D. Siva Kumar, K. Venkata Reddy, Y.V. Prashant** for continuous support and encouragement throughout my life.

I express my deep sense of gratitude and reverence to my beloved mother **Smt. S. Gangamma**, my grandmother **Smt. B. Dalamma**, my younger brother **S. Venu Babu** and other family members for their blessings, constant encouragement, shouldering the responsibilities and moral support rendered to me throughout my life, without which my research work would not have been possible.

## ABSTRACT

In recent times, every nation is determined towards the increased use of renewable energy sources like solar, wind etc., to combat with the adverse environmental changes caused by the burning of conventional fossil fuels. Out of these, Photovoltaic (PV) technology is extremely evolved and accessible to all starting from house roof-top generation to large power plants in rural, urban and remote locations. The AC module configuration is a viable solution for low power PV application and helps to harvest maximum energy from PV either with or without grid facility. The desired features of inverter are voltage gain, compactness, low output voltage THD (Total Harmonic Distortion), efficient conversion and low cost. The conventional step-up inverters either with low frequency or high frequency transformer provide the required voltage gain. However, at low power operation the percentage of core losses are relatively high and results in reduced overall efficiency. Moreover, the presence of transformer leads to increased size and cost of the inverter. The conventional transformerless step-up inverters with front-end boost converter provide reduced size and cost, however the voltage gain is limited to 3. Moreover, the front-end boost converter process the rated power and a bulky DC-link capacitor is required to maintain the DC-link voltage. The step-up inverters with front-end DC-DC converter with floating DC-link is presented to reduce the capacitor size, however the voltage gain is limited to 3. Recent times, switched capacitor (SC) based step-up inverters are popular due to their improved voltage gain, multilevel output with lesser THD and better efficiency at low output power. However, the parallel charging and series discharging technique in SC based inverters demand a bulky capacitors for low frequency and high power applications to avoid voltage drooping issues. Further, these inverters with higher voltage levels require more number of capacitors and switching components, which results in increased system size. Additionally, the SC based inverters draw impulse current during capacitor charging intervals, which demands high current rated devices. To address the impulse charging current issue, a bulky inductor is used in the charging path of the quasi resonant switched capacitor (QRSC) based inverters. The impedance offered by the resonant inductor will reduce the peak of the charging current. However, the other merits and demerits of SC based inverters and the QRSC based inverters are similar. Hence, there is a requirement of step-up inverter, which provides reduced

capacitor charging current, improved voltage gain and higher voltage levels while utilizing less components and small size capacitors.

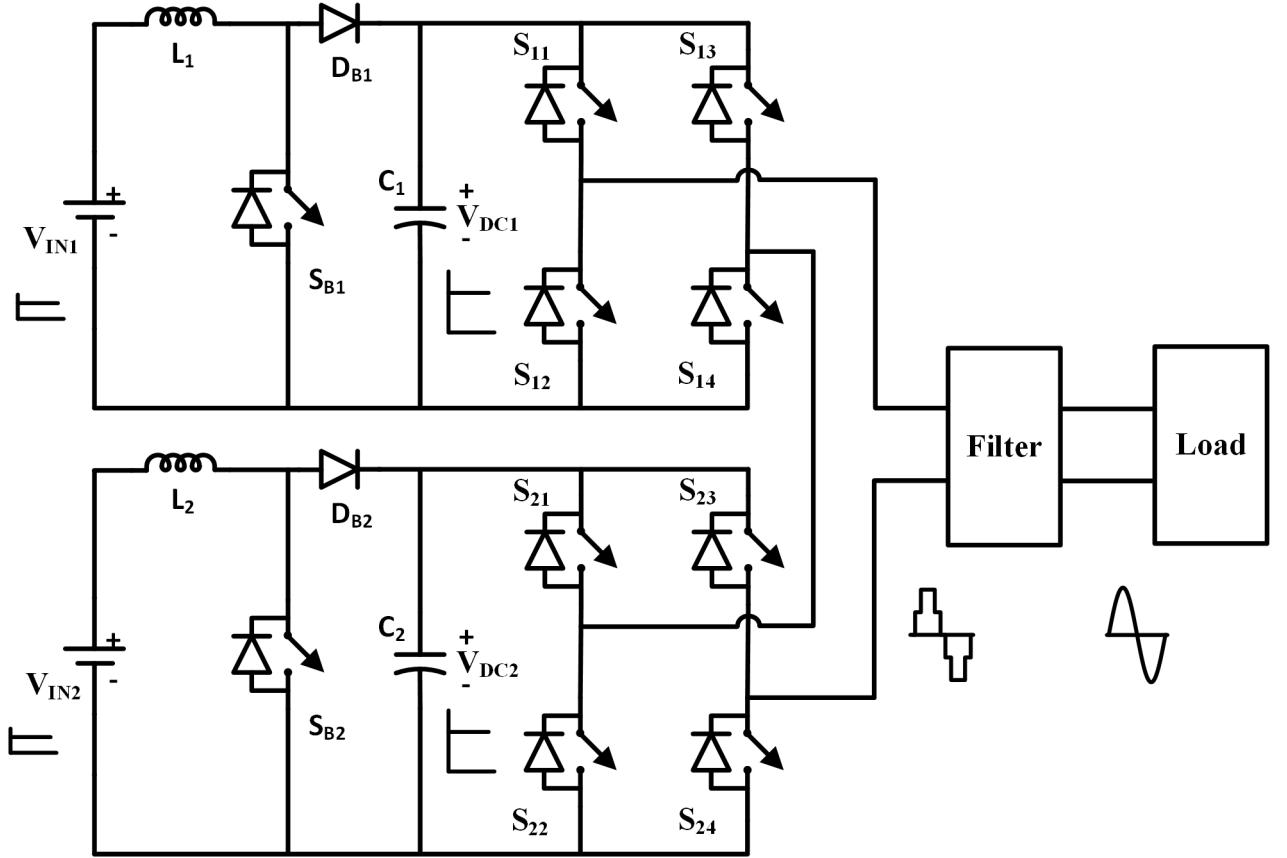

To meet the above objectives, a new boost DC-link integrated multilevel inverter (MLI) is realized by the integration of two two-level boost DC-link converters with a hybrid H-bridge inverter using two symmetrical voltage sources. The proposed topology with proper selection of capacitor voltage levels can produce 9-, 11- and 13-level outputs and provides a maximum voltage gain of 3.

To further improve the voltage gain and number of voltage levels, a MLI with four level boost DC-link basic unit is proposed. With two basic units and two symmetrical voltage sources it can produce 17-level output voltage and provide a voltage gain of 4. In asymmetrical mode of operation, the same configuration is able to produce 31-level output.

The proposed 13-level and 17-level MLIs are required to power from two sources. However, for PV AC module applications the step-up inverter configurations that utilize single source and provide higher voltage gain are essential. Hence, an improved buck-boost integrated MLIs with single-source is proposed. By choosing the appropriate voltage ratios of capacitor voltages with respect to the source voltage, one of the proposed converter can produce an 11-level output voltage with a voltage gain of 5 and other converter produce a 13-level output voltage with a voltage gain of 2 respectively.

The buck-boost converters presented in the proposed inverters are only process fractional part of total energy. All of the proposed MLIs utilize nearest level stair case modulation, thus produce a low frequency common mode voltage, which results in reduced leakage currents. The capacitors presented in the proposed step-up inverters are being charged at high switching frequency to the desired voltage values. Thus, provide reduced component count, capacitor size, charging current and eliminate voltage drooping issue. Therefore, the developed step-up inverters are suitable for standalone PV applications.

# Contents

|                                                                        |             |

|------------------------------------------------------------------------|-------------|

| <b>ACKNOWLEDGMENTS</b>                                                 | <b>i</b>    |

| <b>ABSTRACT</b>                                                        | <b>iii</b>  |

| <b>List of Figures</b>                                                 | <b>viii</b> |

| <b>List of Tables</b>                                                  | <b>xiv</b>  |

| <b>Abbreviations &amp; Symbols</b>                                     | <b>xvi</b>  |

| <b>1 Introduction</b>                                                  | <b>2</b>    |

| 1.1 General introduction . . . . .                                     | 2           |

| 1.2 PV systems . . . . .                                               | 2           |

| 1.2.1 Grid connected PV systems . . . . .                              | 4           |

| 1.2.2 Off-grid PV systems . . . . .                                    | 4           |

| 1.3 Single phase step-up inverters . . . . .                           | 5           |

| 1.3.1 Step-up inverters with transformer . . . . .                     | 6           |

| 1.3.2 Step-up inverters without transformer . . . . .                  | 7           |

| <b>2 Literature Review on Single-phase Transformerless Inverters</b>   | <b>9</b>    |

| 2.1 Introduction . . . . .                                             | 9           |

| 2.2 Two-level inverter with front-end boost converter . . . . .        | 9           |

| 2.3 Step-up inverter with improved front-end boost converter . . . . . | 10          |

| 2.4 Multilevel inverter with front-end boost converter . . . . .       | 11          |

| 2.5 Single-stage differential boost inverters . . . . .                | 12          |

| 2.5.1 Conventional DBIs . . . . .                                      | 12          |

| 2.5.2 Clamped DBIs: . . . . .                                          | 13          |

|          |                                                                                 |           |

|----------|---------------------------------------------------------------------------------|-----------|

| 2.5.3    | Cascaded DBIs: . . . . .                                                        | 17        |

| 2.6      | Switched capacitor multilevel inverters . . . . .                               | 19        |

| 2.7      | Quasi-resonant switched capacitor multilevel inverters . . . . .                | 21        |

| 2.8      | Research gaps & Motivation . . . . .                                            | 23        |

| 2.9      | Thesis objectives . . . . .                                                     | 25        |

| 2.10     | Thesis contributions . . . . .                                                  | 25        |

| 2.11     | Thesis organization . . . . .                                                   | 26        |

| 2.12     | Summary . . . . .                                                               | 27        |

| <b>3</b> | <b>Boost DC-link Integrated Cascaded Multilevel Inverter</b>                    | <b>29</b> |

| 3.1      | Introduction . . . . .                                                          | 29        |

| 3.2      | Working and operating principle of the proposed BDIMLI . . . . .                | 31        |

| 3.3      | Comparative analysis . . . . .                                                  | 42        |

| 3.4      | Experimental Results . . . . .                                                  | 46        |

| 3.5      | Summary . . . . .                                                               | 50        |

| <b>4</b> | <b>Improved Boost DC-link Integrated Cascaded Multilevel Inverter</b>           | <b>52</b> |

| 4.1      | Introduction . . . . .                                                          | 52        |

| 4.2      | Working and operating principle of the proposed IBDIMLI . . . . .               | 52        |

| 4.3      | Comparative Analysis . . . . .                                                  | 59        |

| 4.4      | Experimental Results . . . . .                                                  | 63        |

| 4.5      | Summary . . . . .                                                               | 70        |

| <b>5</b> | <b>Single-source Buck-boost Integrated 13-level Inverter</b>                    | <b>72</b> |

| 5.1      | Introduction . . . . .                                                          | 72        |

| 5.2      | Working and operating principle of the proposed SBMLI . . . . .                 | 72        |

| 5.3      | Comparative analysis . . . . .                                                  | 80        |

| 5.4      | Experimental Results . . . . .                                                  | 82        |

| 5.5      | Summary . . . . .                                                               | 84        |

| <b>6</b> | <b>Improved Single-source Buck-boost Integrated High gain 11-level Inverter</b> | <b>86</b> |

| 6.1      | Introduction . . . . .                                                          | 86        |

|                             |                                                                  |            |

|-----------------------------|------------------------------------------------------------------|------------|

| 6.2                         | Working and operating principle of the proposed ISBMLI . . . . . | 86         |

| 6.3                         | Comparative analysis . . . . .                                   | 93         |

| 6.4                         | Experimental Results . . . . .                                   | 94         |

| 6.5                         | Summary . . . . .                                                | 100        |

| <b>7</b>                    | <b>Conclusions and future Scope of research</b>                  | <b>102</b> |

| 7.1                         | Conclusions . . . . .                                            | 102        |

| 7.2                         | Future scope of research work . . . . .                          | 104        |

| <b>Bibliography</b>         |                                                                  | <b>106</b> |

| <b>List of publications</b> |                                                                  | <b>116</b> |

# List of Figures

|     |                                                                                                                                                                                                      |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Block diagram of grid connected PV system during (a) the presence of sunlight<br>(b) the absence of sunlight; and off-grid PV system during (c) the presence of sunlight (d) the absence of sunlight | 3  |

| 1.2 | Different grid connected PV configurations.                                                                                                                                                          | 3  |

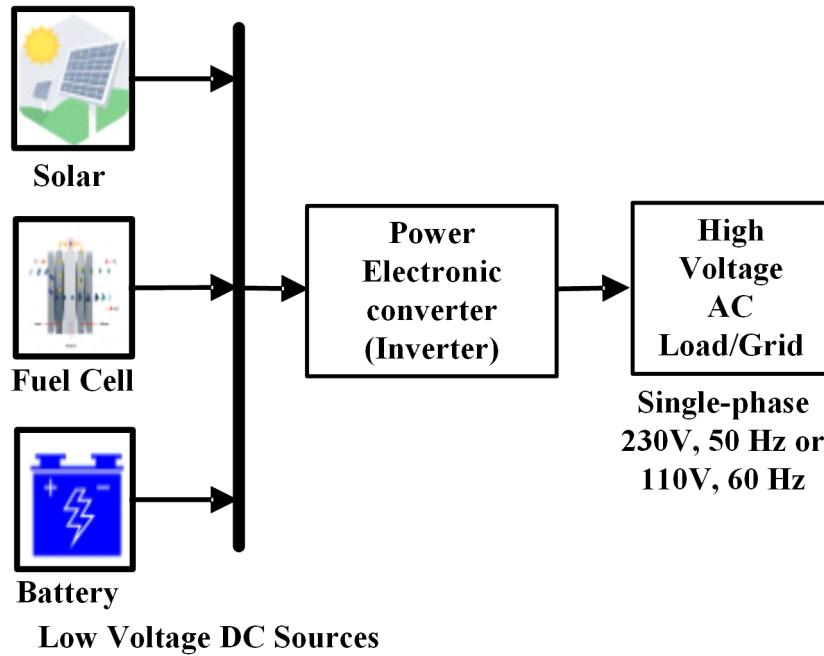

| 1.3 | Block diagram of inverter for renewable applications.                                                                                                                                                | 5  |

| 1.4 | Block diagram of single phase step-up inverters: (a) with low-frequency transformer (b) with high-frequency transformer (c) two-stage transformerless (d) single-stage transformerless               | 6  |

| 2.1 | Circuit diagram of two stage two-level step-up inverter with front-end boost converter                                                                                                               | 10 |

| 2.2 | Circuit diagram of improved time sharing two stage two-level step-up inverter with front-end boost converter                                                                                         | 11 |

| 2.3 | Circuit diagram of two stage multilevel step-up inverter with front-end boost converter                                                                                                              | 12 |

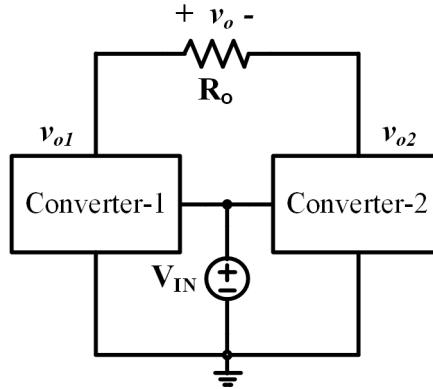

| 2.4 | Block diagram of conventional DBIs                                                                                                                                                                   | 13 |

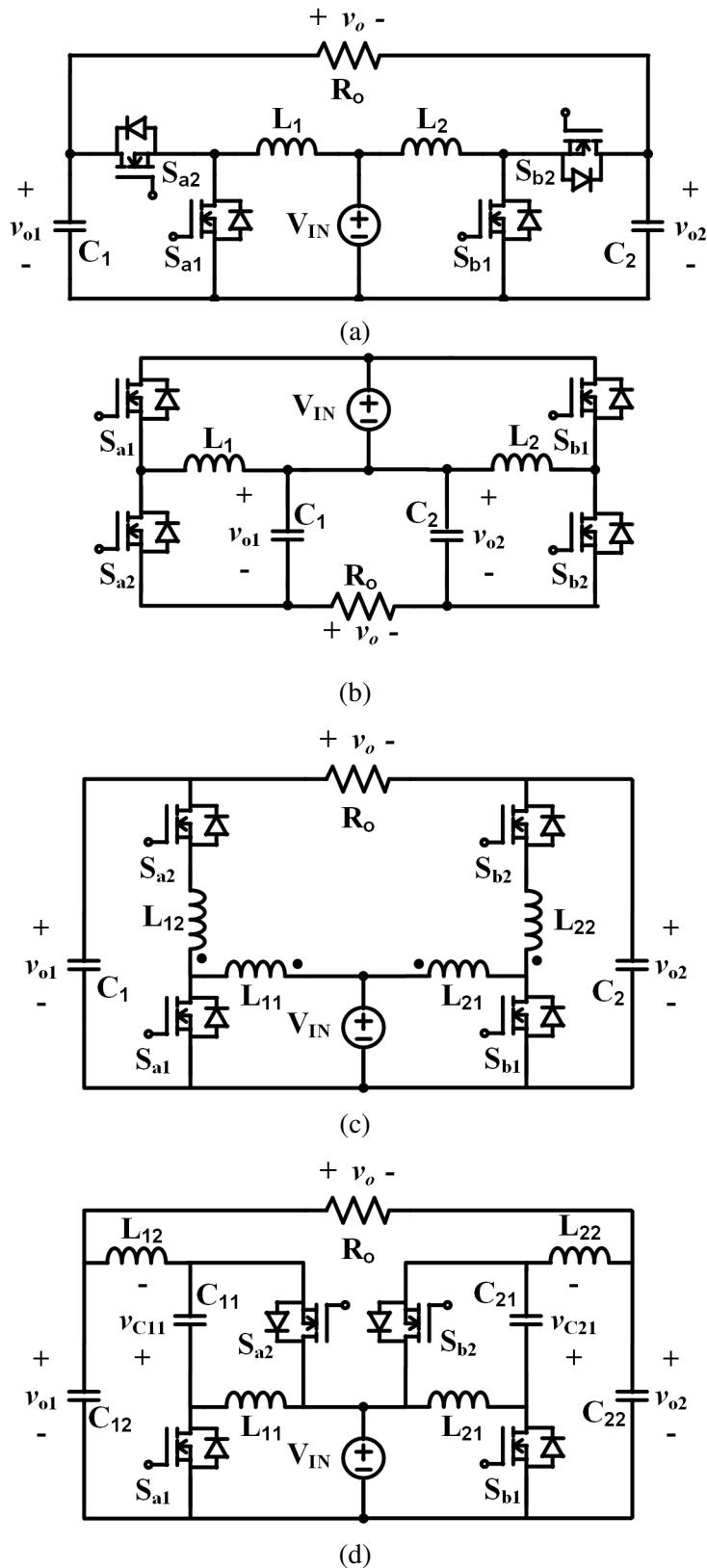

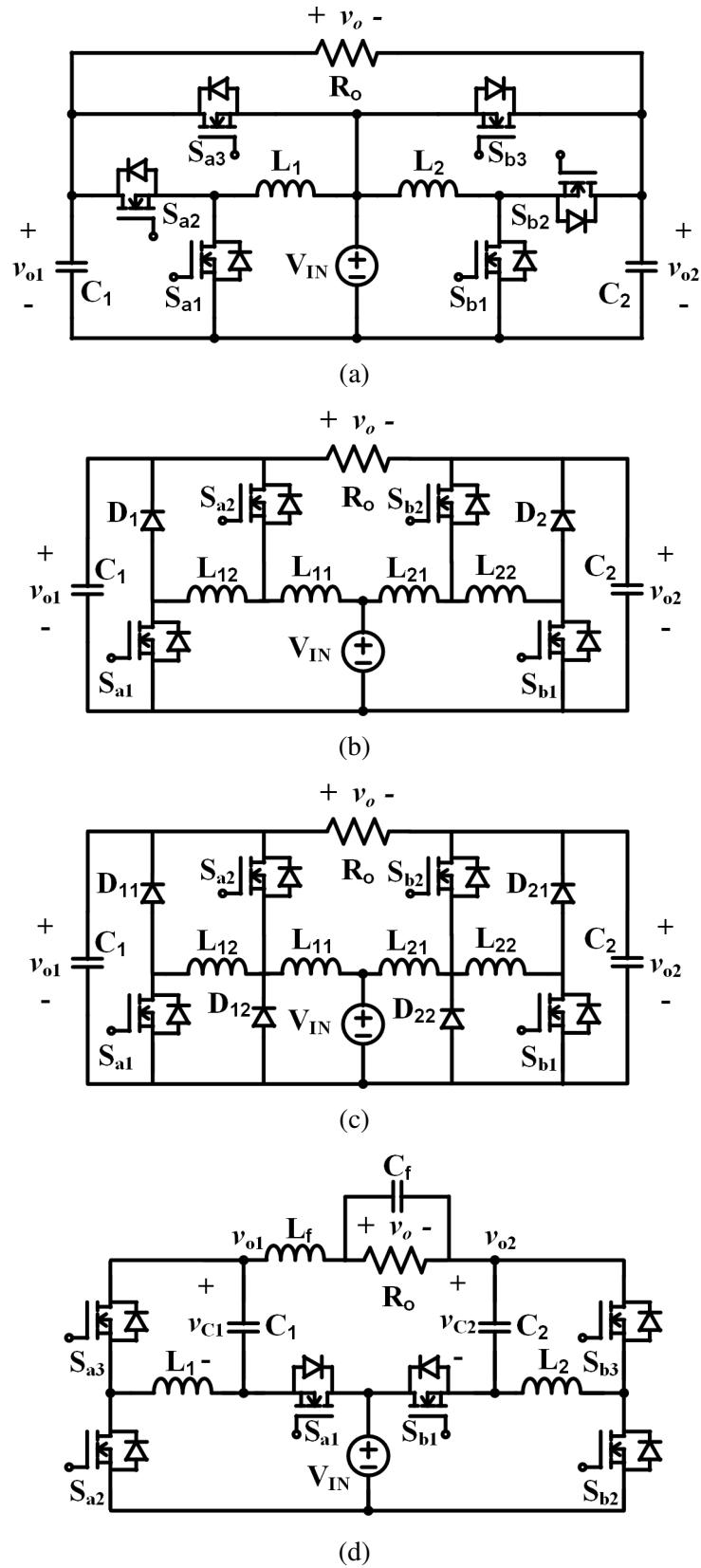

| 2.5 | Circuit diagrams of simple DBI topologies developed using a) boost b) buck-boost c) couple boost d) SC converters as basic units                                                                     | 14 |

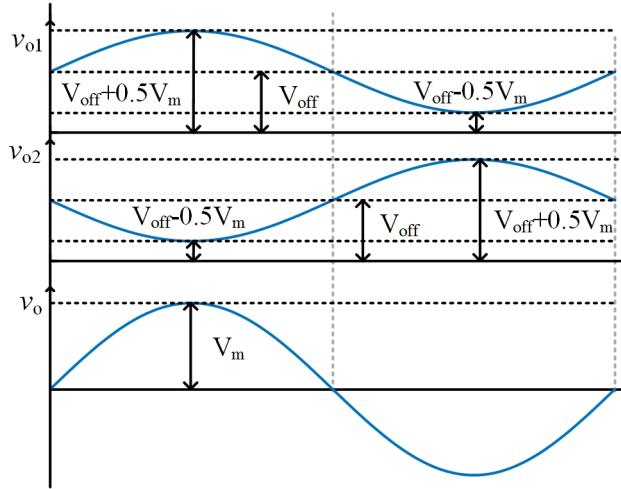

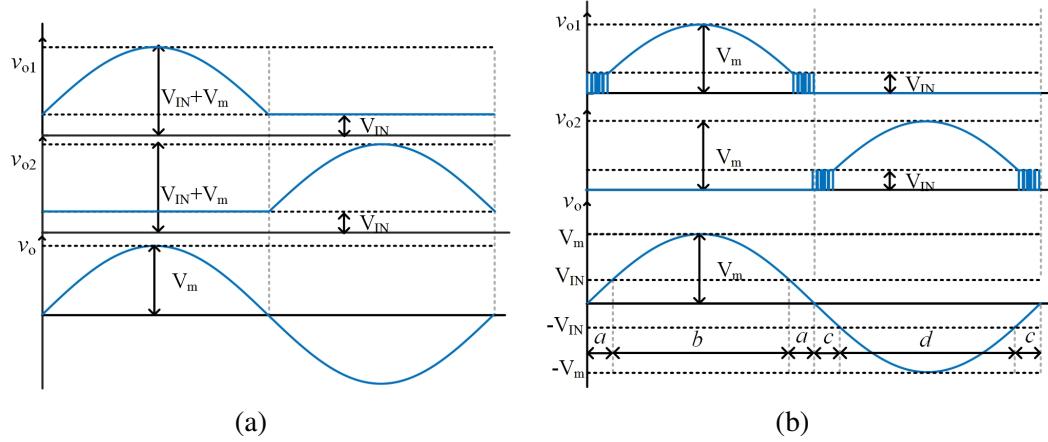

| 2.6 | Model waveforms of type DBIs with decoupled full cycle modulation                                                                                                                                    | 15 |

| 2.7 | Circuit diagrams of DBIs with by-pass switches: a) Improved boost DBI b) split inductor DBI-I c) split inductor DBI-II d) Improved buck-boost                                                        | 16 |

| 2.8 | Model waveforms of type: DBIs with (a) decoupled half cycle modulation [?]<br>(b) decoupled dual mode half cycle modulation [?]                                                                      | 17 |

| 2.9 | Circuit diagram of type: C DBIs formed by cascade connection of (a) boost & quasi Z source (b) boost & buck-boost                                                                                    | 18 |

|      |                                                                                                                                                                                                                                                                                                                                                      |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.10 | Model waveforms of type C DBIs with integrated full cycle modulation . . . . .                                                                                                                                                                                                                                                                       | 18 |

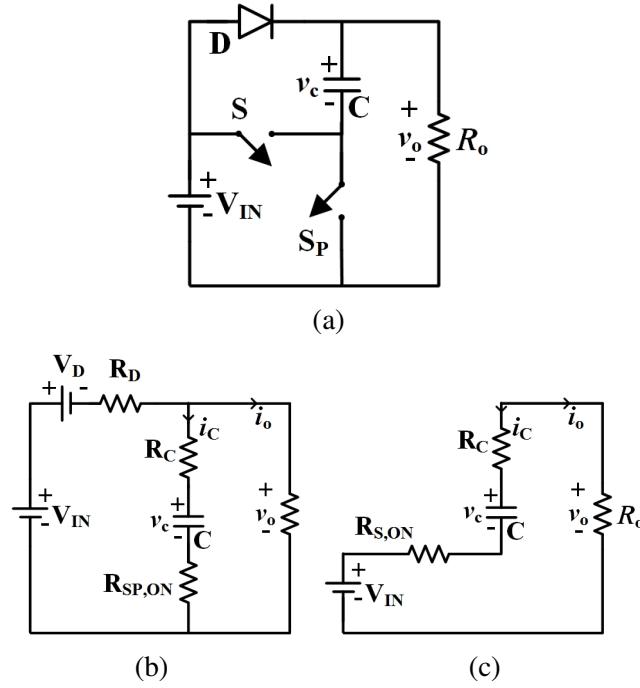

| 2.11 | Circuit diagram of SC (a) basic unit (b) basic unit when capacitor is getting charged (c) basic unit when capacitor is getting discharged . . . . .                                                                                                                                                                                                  | 19 |

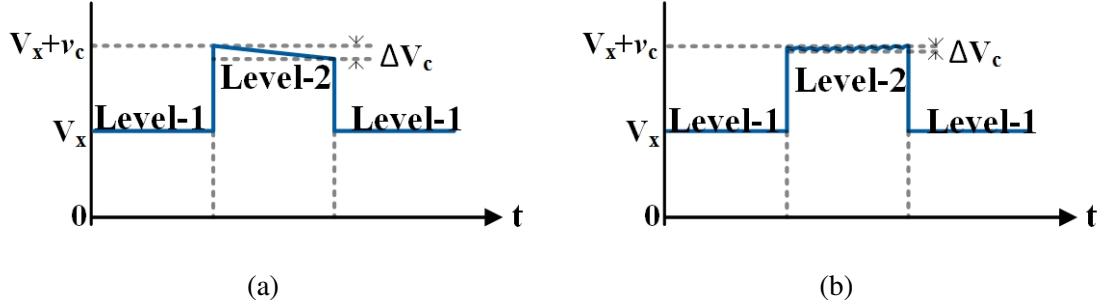

| 2.12 | Model waveforms of basic unit of switched capacitor based inverters: (a) when $R_o$ is high and duration of level-2 is short, (b) when $R_o$ is low and duration of level-2 is short, (c) when $R_o$ is high and duration of level-2 is long . . . . .                                                                                               | 20 |

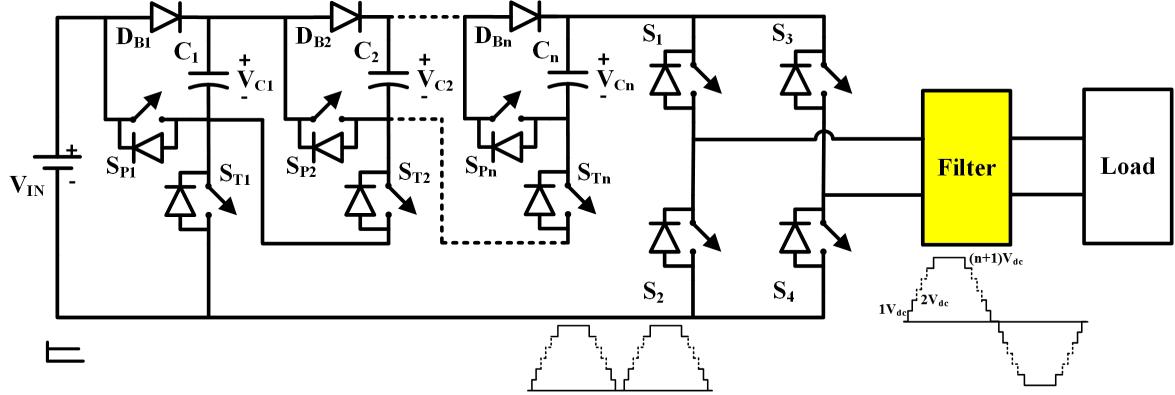

| 2.13 | Extended high step-up switched capacitor multilevel inverter . . . . .                                                                                                                                                                                                                                                                               | 21 |

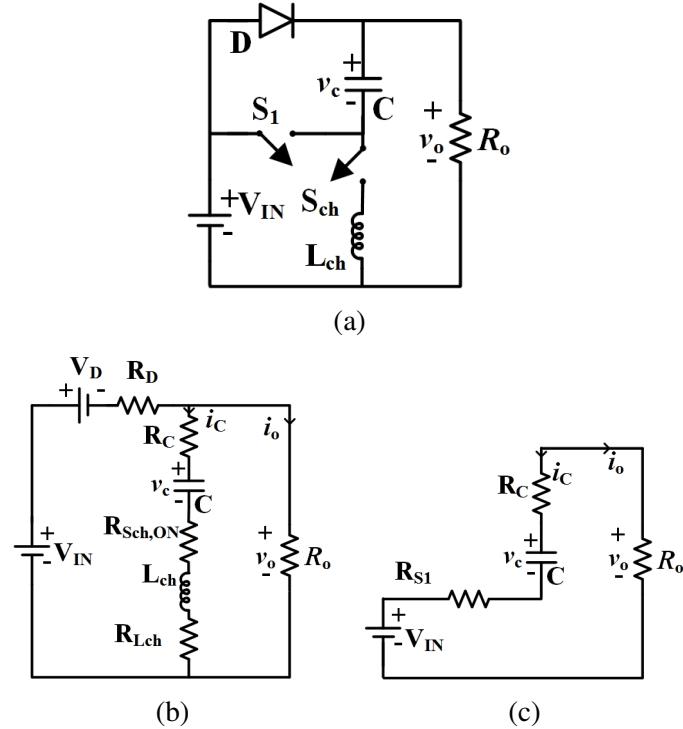

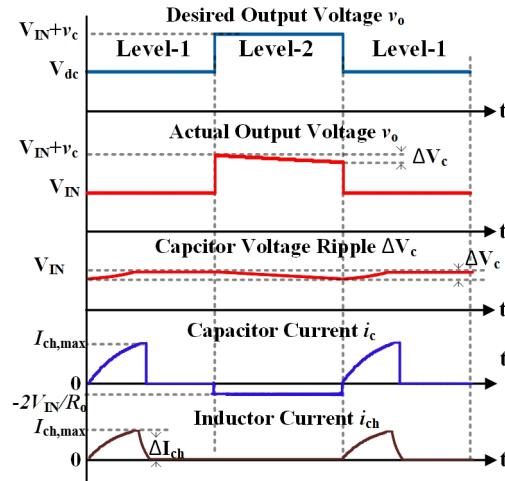

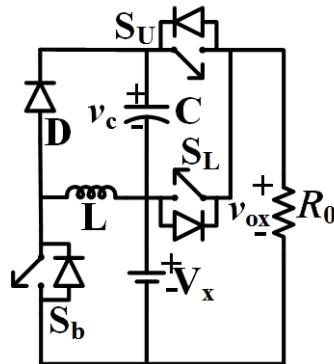

| 2.14 | Circuit diagram of quasi resonant SC (a) basic unit (b) basic unit when capacitor is getting charged (c) basic unit when capacitor is getting discharged . . . . .                                                                                                                                                                                   | 22 |

| 2.15 | Model waveforms of basic unit of quasi resonant SC based inverters . . . . .                                                                                                                                                                                                                                                                         | 22 |

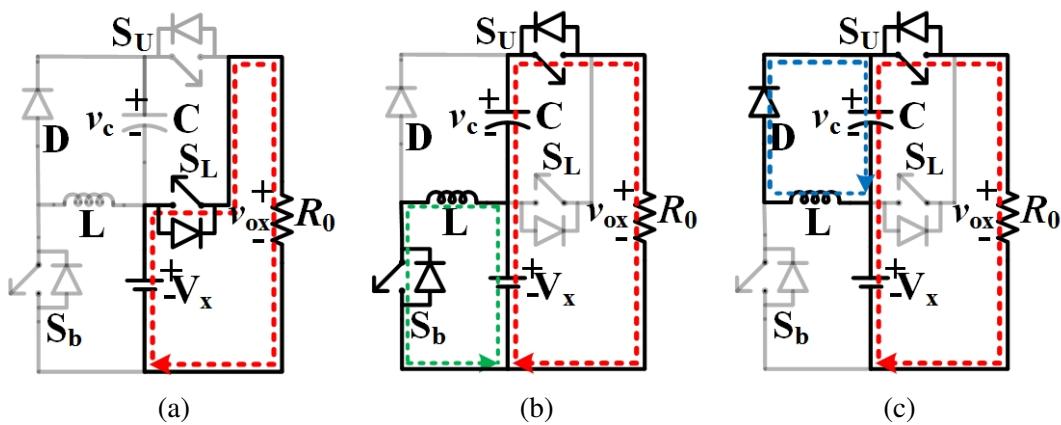

| 3.1  | Two-level Boost DC-link Converter Unit. . . . .                                                                                                                                                                                                                                                                                                      | 30 |

| 3.2  | Equivalent circuit of TBDC during (a) level-1 (b) level-2 while inductor charging (c) level-2 while inductor discharging . . . . .                                                                                                                                                                                                                   | 30 |

| 3.3  | TBDC model waveforms: output voltage, switch gate pulses, capacitor voltage and inductor current during level-1 and level-2 operations. . . . .                                                                                                                                                                                                      | 30 |

| 3.4  | Typical output voltage waveform of (a) SCMLI basic cell (b) TBDC . . . . .                                                                                                                                                                                                                                                                           | 31 |

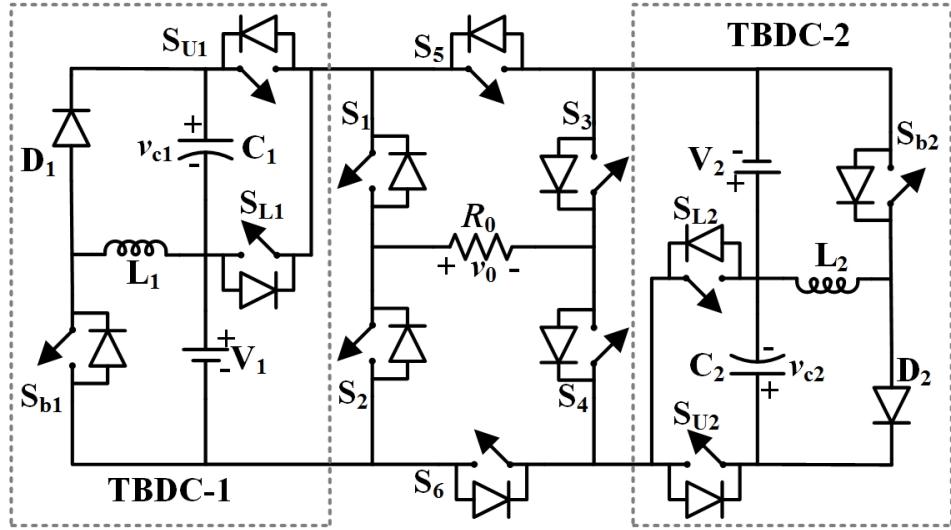

| 3.5  | Schematic diagram of the proposed Boost DC-link Integrated Cascaded MLI. .                                                                                                                                                                                                                                                                           | 33 |

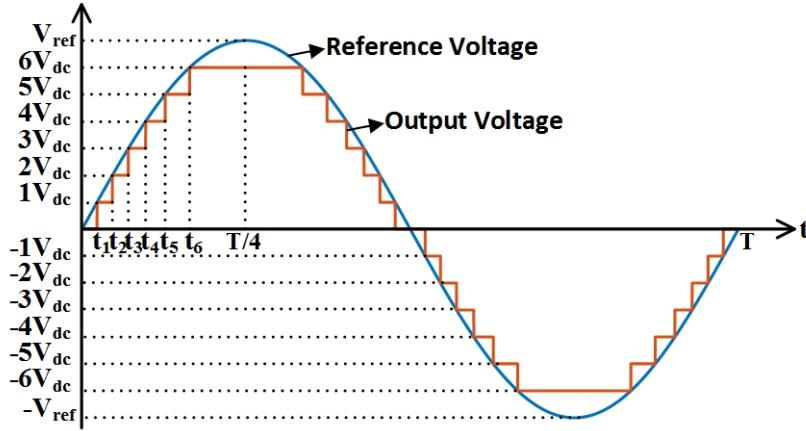

| 3.6  | Model waveform of the 13-level output voltage. . . . .                                                                                                                                                                                                                                                                                               | 34 |

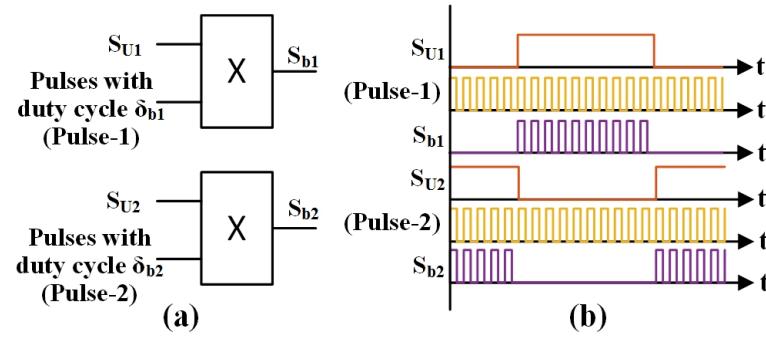

| 3.7  | $S_{b1}$ & $S_{b2}$ gate pulses:(a) logic diagram, (b) model waveforms. . . . .                                                                                                                                                                                                                                                                      | 34 |

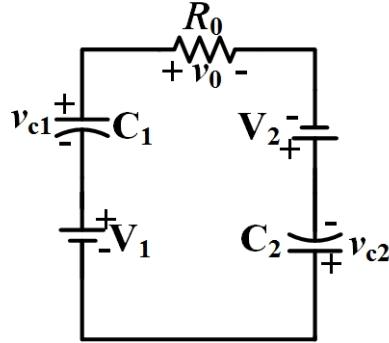

| 3.8  | Equivalent circuit of BDIMLI for peak output voltage. . . . .                                                                                                                                                                                                                                                                                        | 35 |

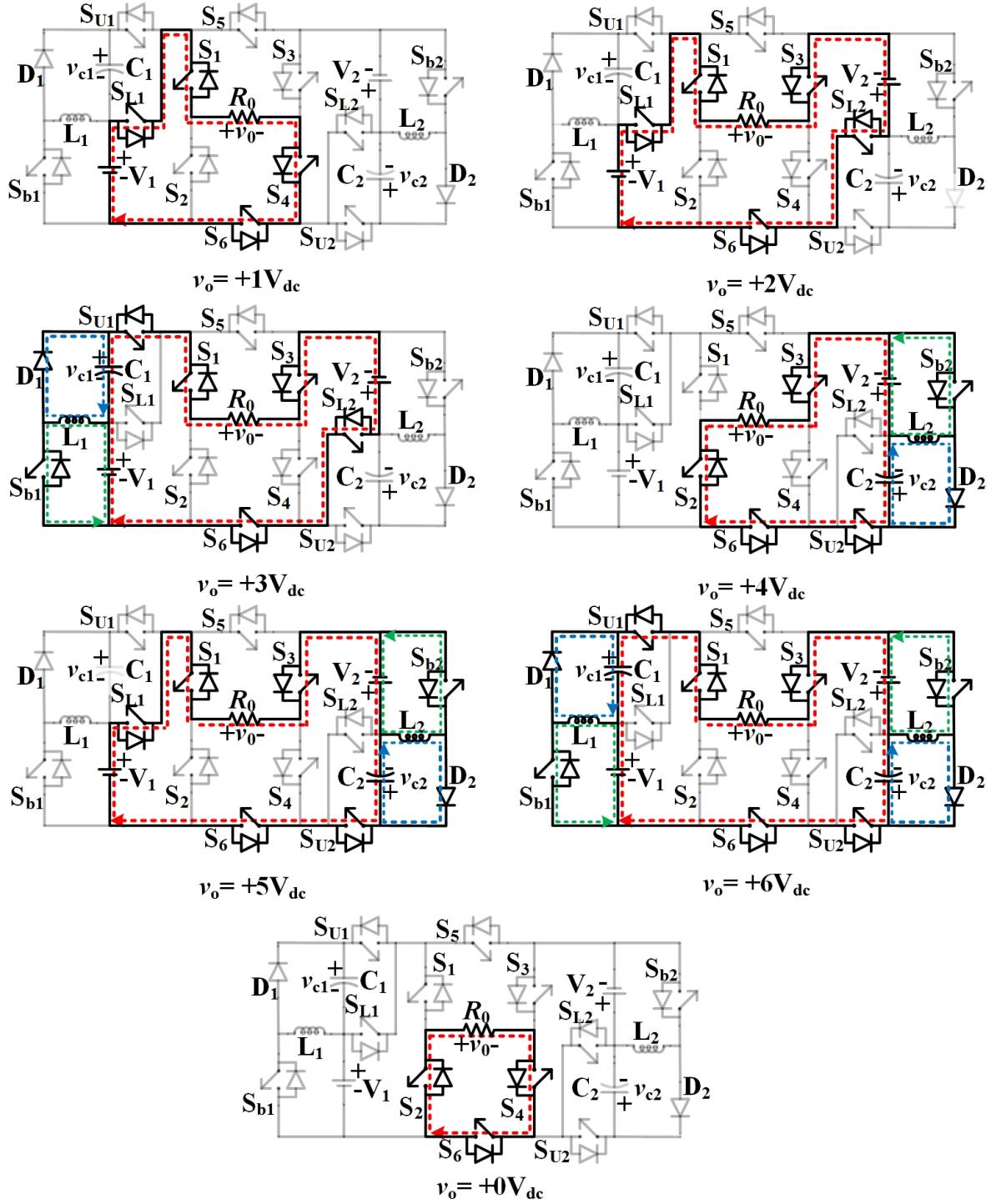

| 3.9  | Different modes of operation of the proposed BDIMLI for 13-level operation from $+0V_{dc}$ to $+6V_{dc}$ . . . . .                                                                                                                                                                                                                                   | 36 |

| 3.10 | Different modes of operation of the proposed BDIMLI for 13-level operation from $-0V_{dc}$ to $-6V_{dc}$ . . . . .                                                                                                                                                                                                                                   | 37 |

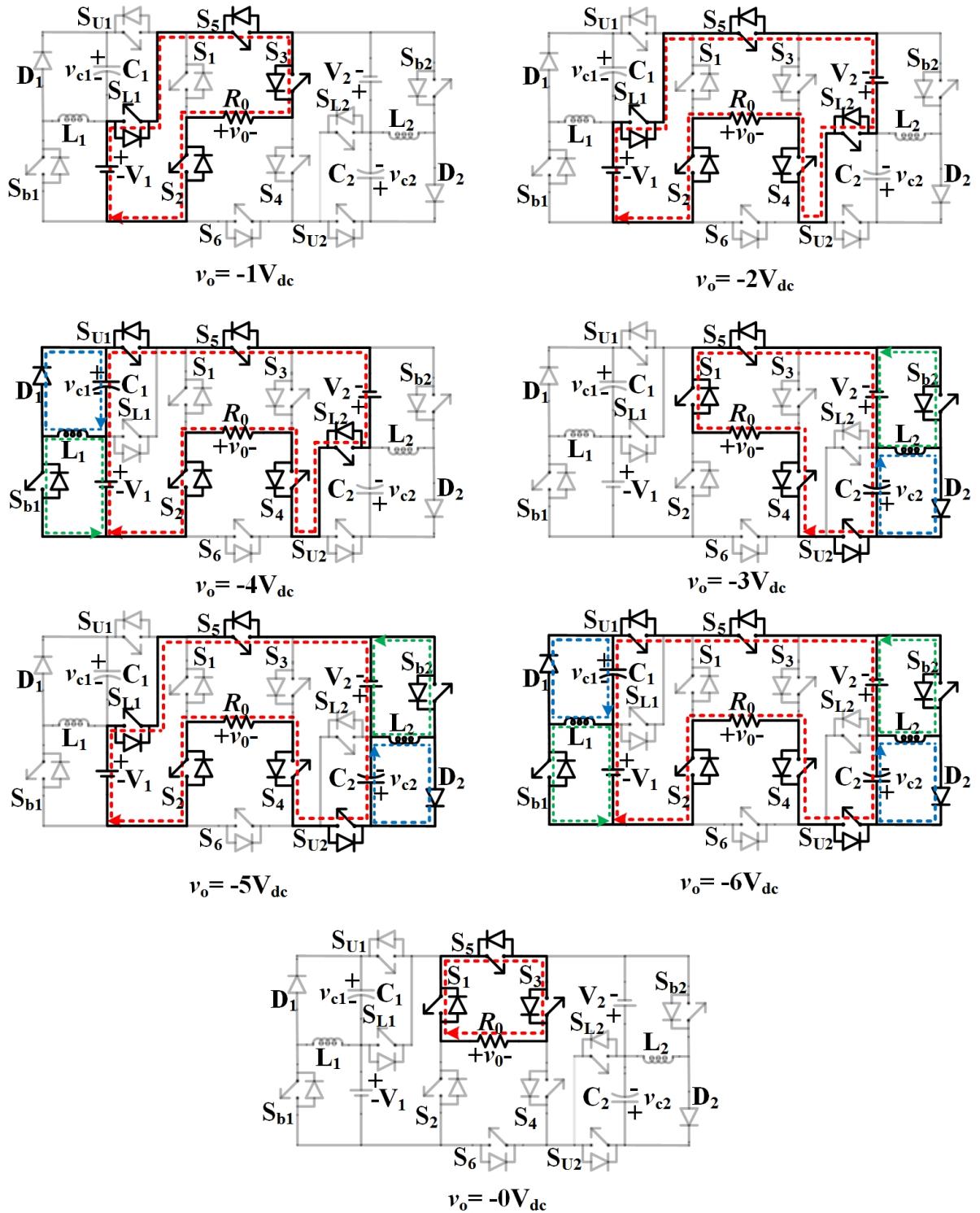

| 3.11 | Design characteristics for 9-level operation: (a) $L_{B1}$ & $L_{B2}$ versus $R_o$ at $f_s = 10\text{kHz}$ , $30\text{kHz}$ & $50\text{kHz}$ (b) $C_{1,min}$ & $C_{2,min}$ versus $R_o$ at $f_s = 10\text{kHz}$ for different ripple voltages and (c) $C_{1,min}$ & $C_{2,min}$ versus $P_{max}$ with $f_s = 10\text{kHz}$ and $V_1=50\text{V}$ . .  | 41 |

| 3.12 | Design characteristics for 13-level operation: (a) $L_{B1}$ & $L_{B2}$ versus $R_o$ at $f_s = 10\text{kHz}$ , $30\text{kHz}$ & $50\text{kHz}$ (b) $C_{1,min}$ & $C_{2,min}$ versus $R_o$ at $f_s = 10\text{kHz}$ for different ripple voltages and (c) $C_{1,min}$ & $C_{2,min}$ versus $P_{max}$ with $f_s = 10\text{kHz}$ and $V_1=50\text{V}$ . . | 42 |

|      |                                                                                                                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

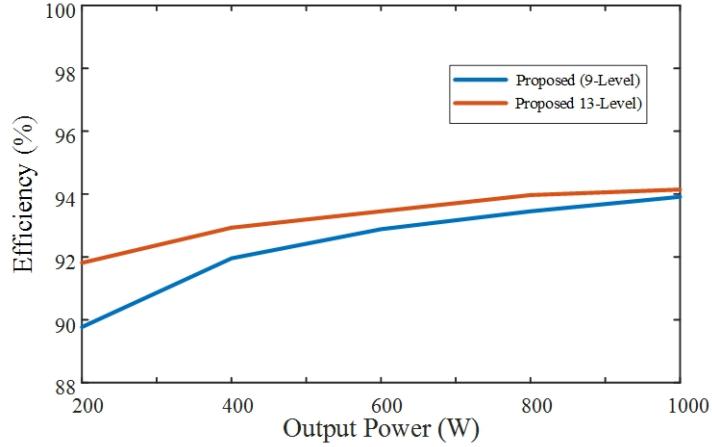

| 3.13 | Efficiency curves of proposed BDIMLI. . . . .                                                                                                                                                                                                                                                     | 45 |

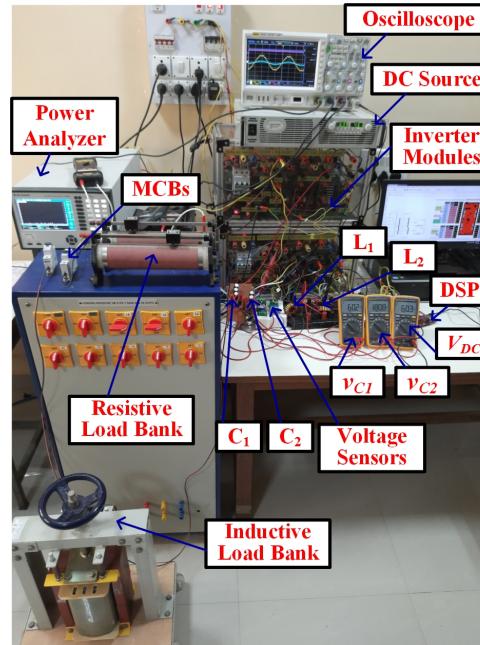

| 3.14 | Experimental prototype of proposed BDIMLI. . . . .                                                                                                                                                                                                                                                | 46 |

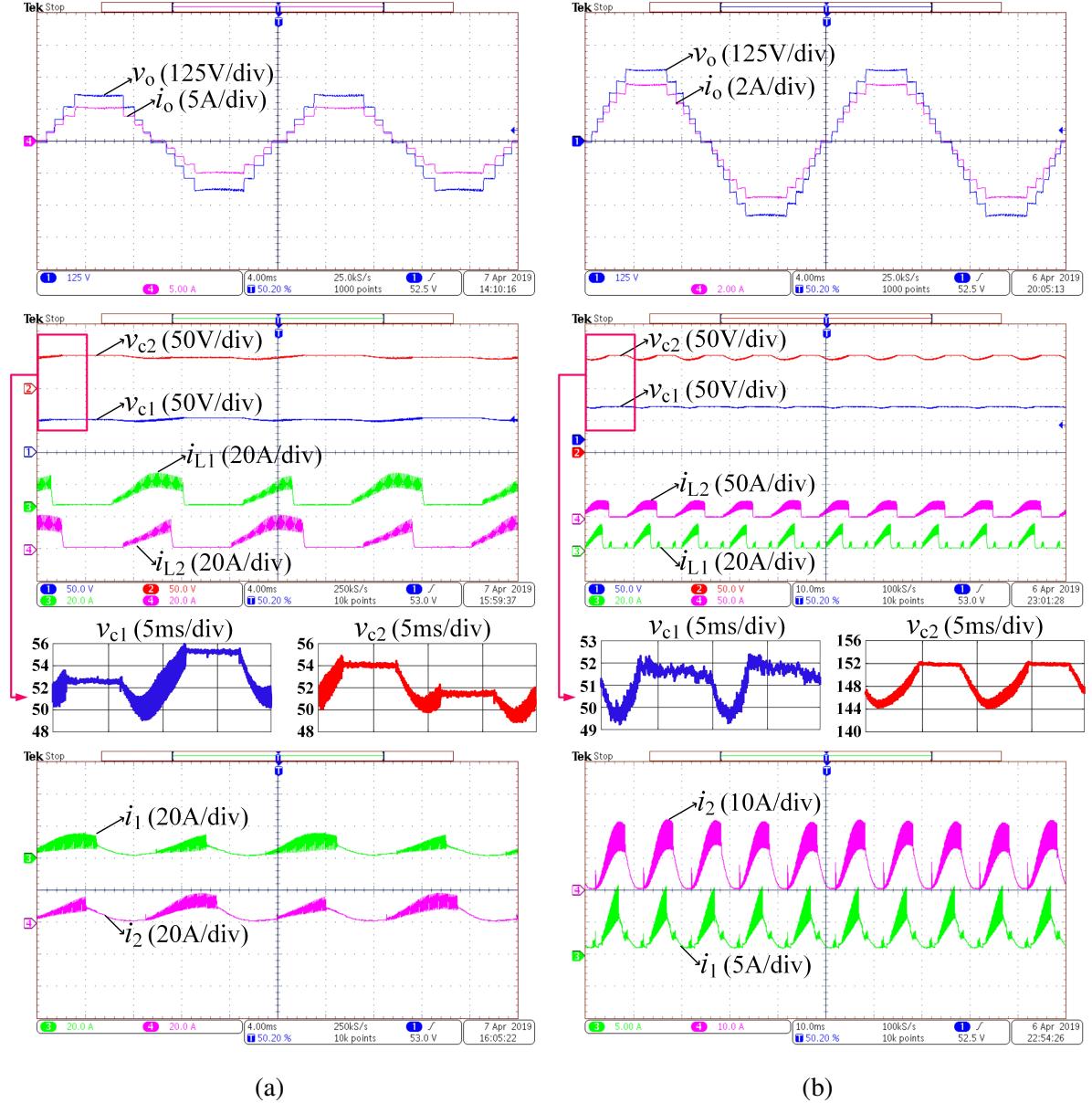

| 3.15 | Experimental waveforms of load voltage $v_o$ , load current $i_o$ , inductors $L_1, L_2$ currents ( $i_{L1}, i_{L2}$ ), capacitors $C_1, C_2$ voltages ( $v_{c1}$ and $v_{c2}$ ) and dc voltage source currents ( $i_1$ and $i_2$ ) for (a) 9-level operation and (b) 13-level operation. . . . . | 47 |

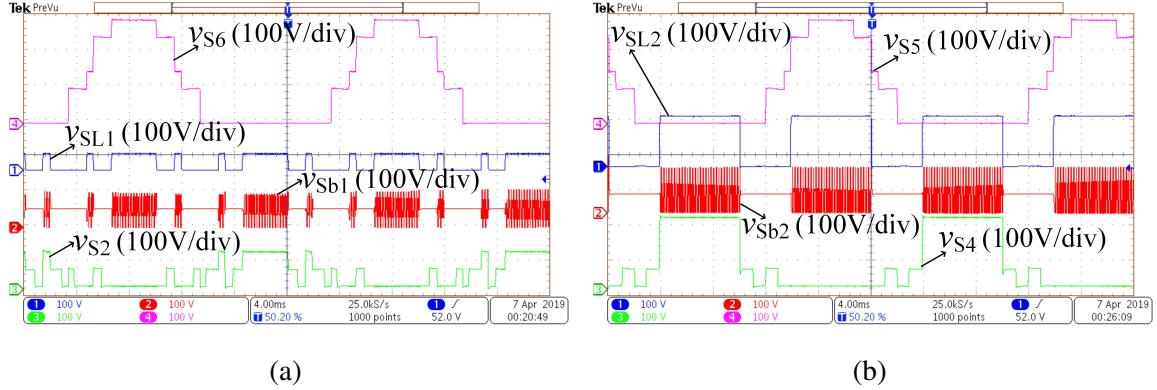

| 3.16 | Experimental waveforms of 13-level operation: (a) PIV of $S_2, S_6, S_{L1}, S_{b1}$ (b) PIV of $S_4, S_5, S_{L2}, S_{b2}$ . . . . .                                                                                                                                                               | 48 |

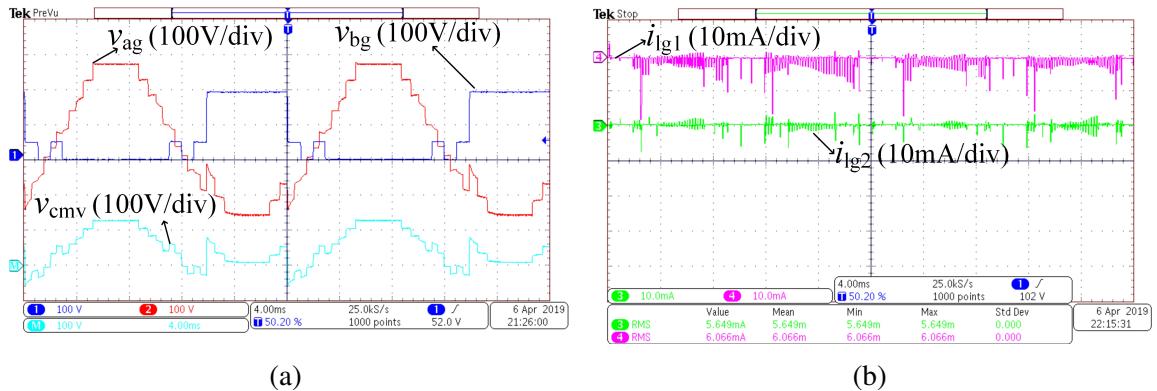

| 3.17 | Experimental waveforms of 13-level operation: (a) CMV (b) DC source leakage currents $i_{lg1}$ and $i_{lg2}$ . . . . .                                                                                                                                                                            | 48 |

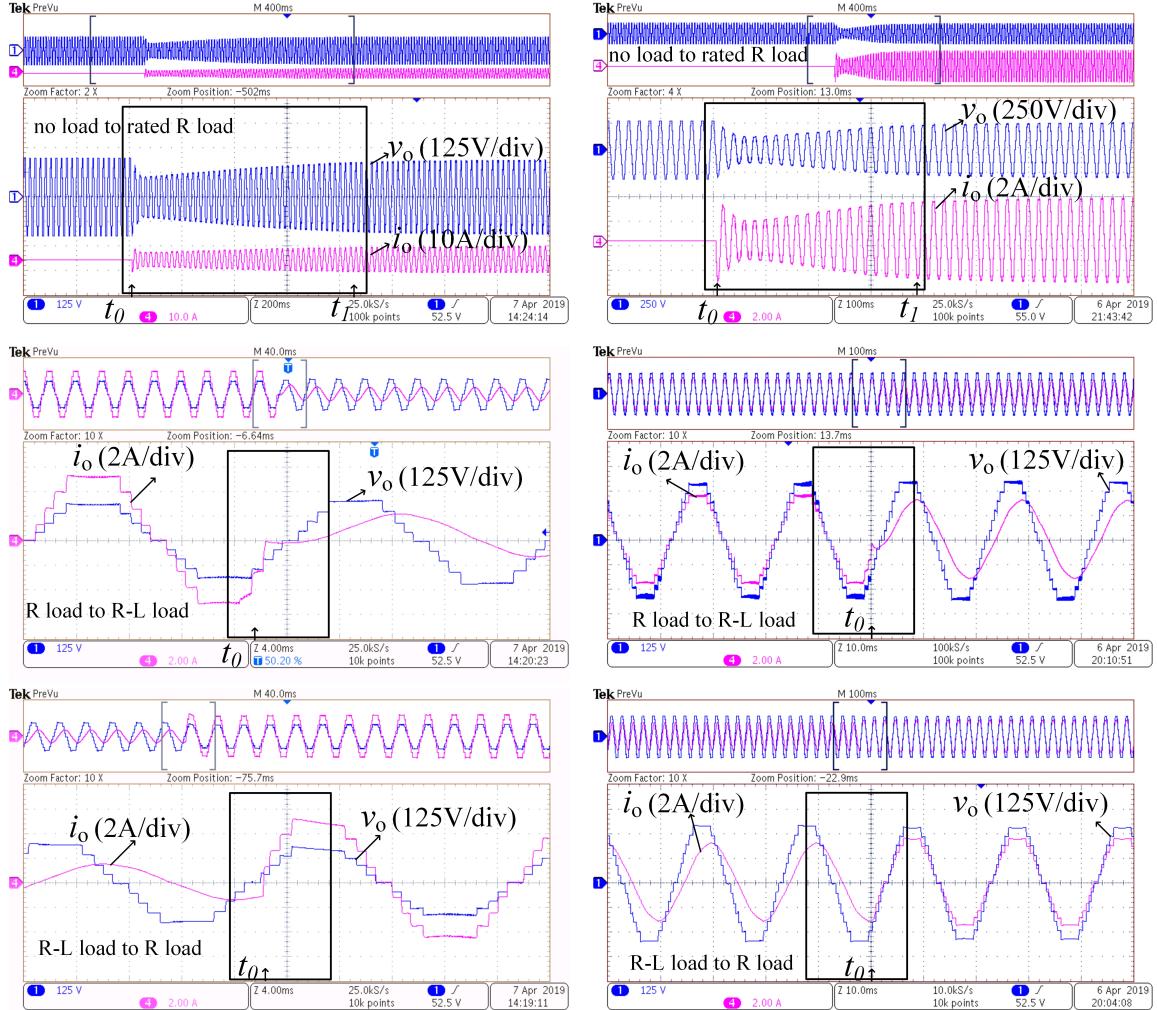

| 3.18 | Dynamic behavior of the proposed BDIMLI with step change in load conditions: no-load to rated R load, R load to R-L load, and R-L load to R load for (a) 9-level operation and (b) 13-level operation. . . . .                                                                                    | 49 |

| 3.19 | Harmonic spectrum of load voltage $v_o$ for (a) 9-level operation and (b) 13-level operation. . . . .                                                                                                                                                                                             | 49 |

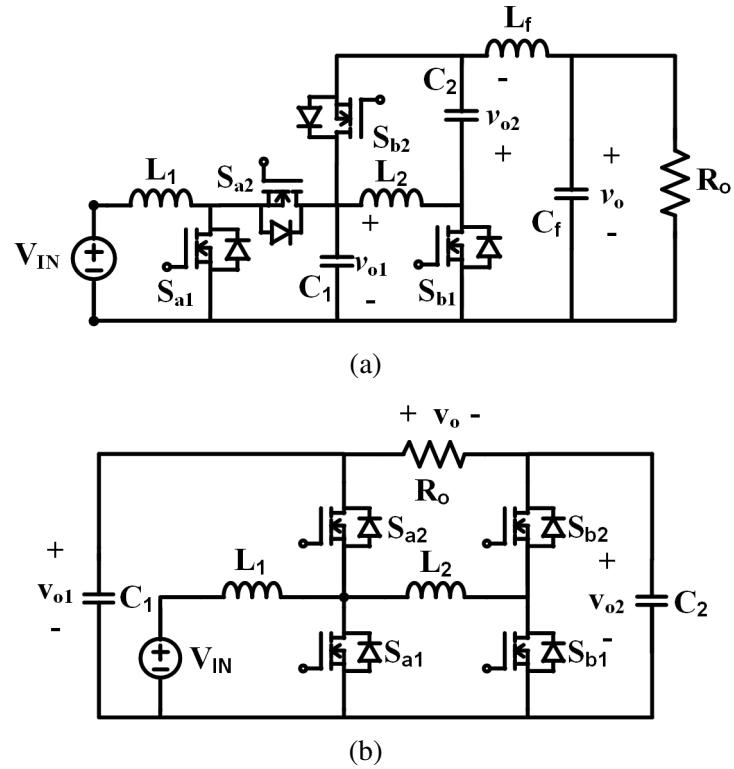

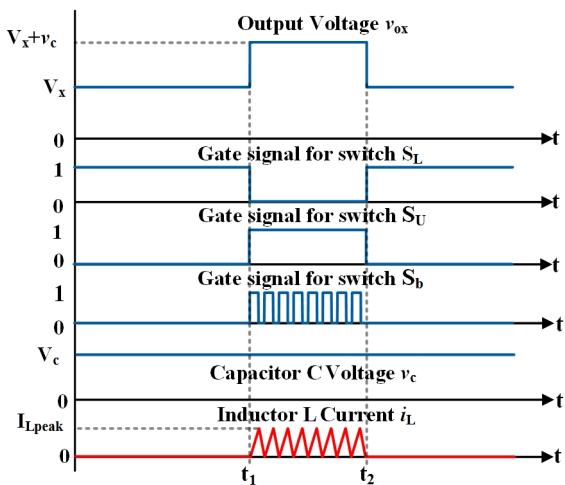

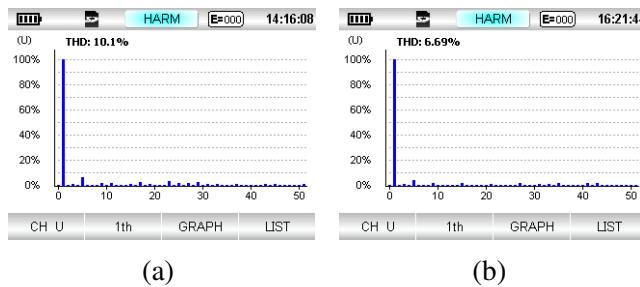

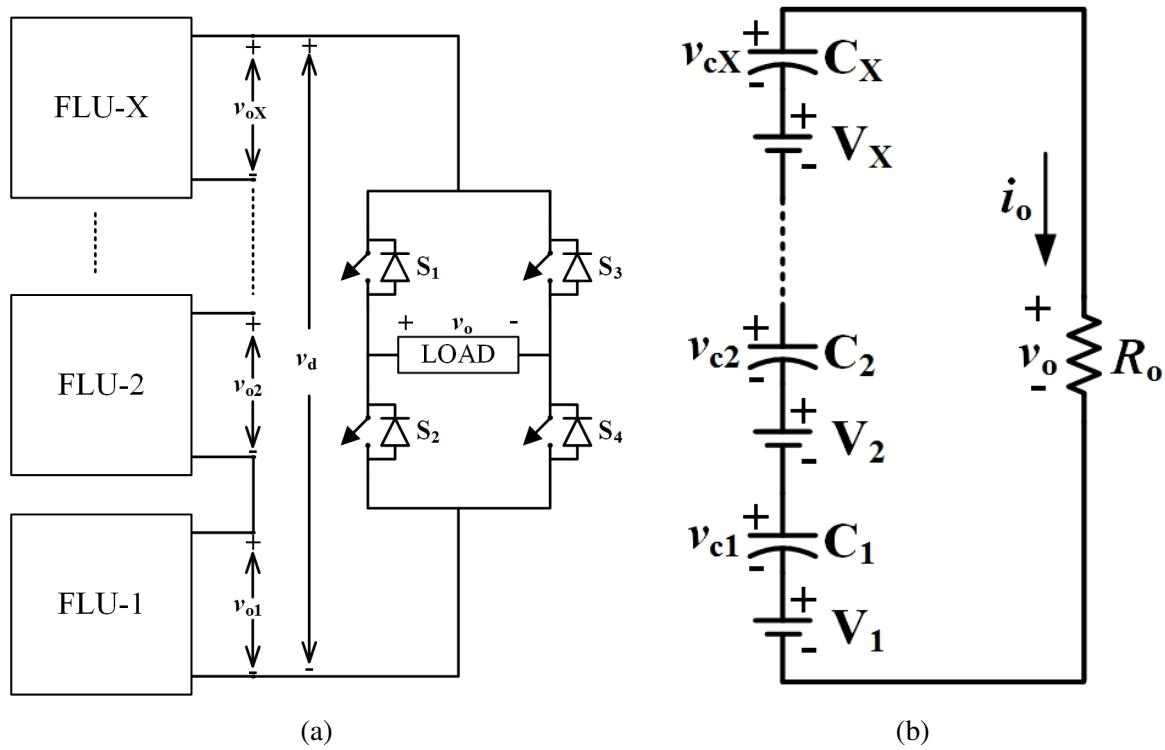

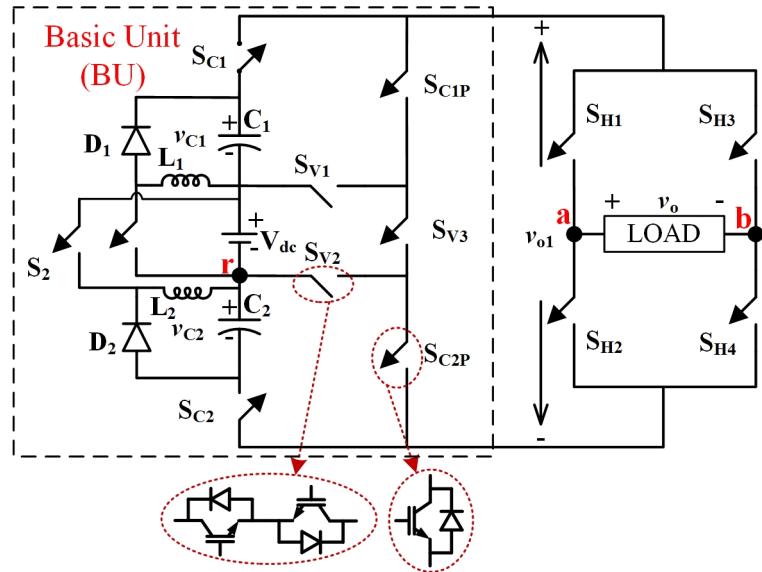

| 4.1  | Proposed basic four-level unit: (a) circuit diagram (b) equivalent block diagram                                                                                                                                                                                                                  | 53 |

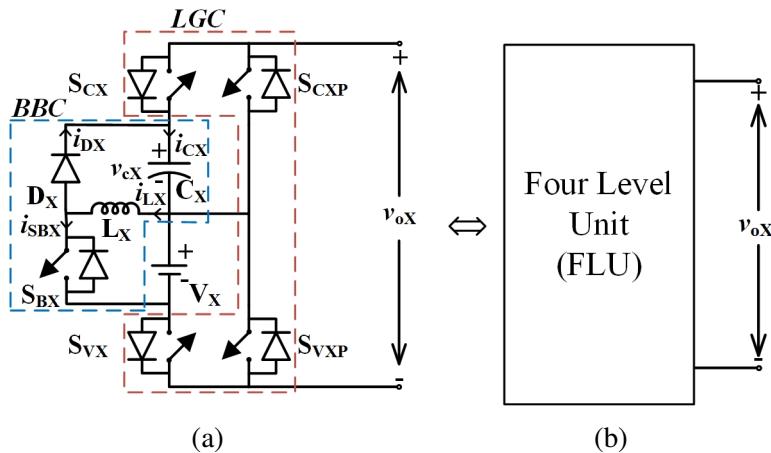

| 4.2  | Equivalent circuit of FLU: (a) 0 level (b) $V_x$ (c) $v_{cx}$ (d) $V_x + v_{cx}$ . (Blue and green lines represents the inductor charging and discharging paths) . . . . .                                                                                                                        | 54 |

| 4.3  | Generalized structure of the IBDIMLI: (a) block diagram (b) equivalent circuit for peak voltage level . . . . .                                                                                                                                                                                   | 57 |

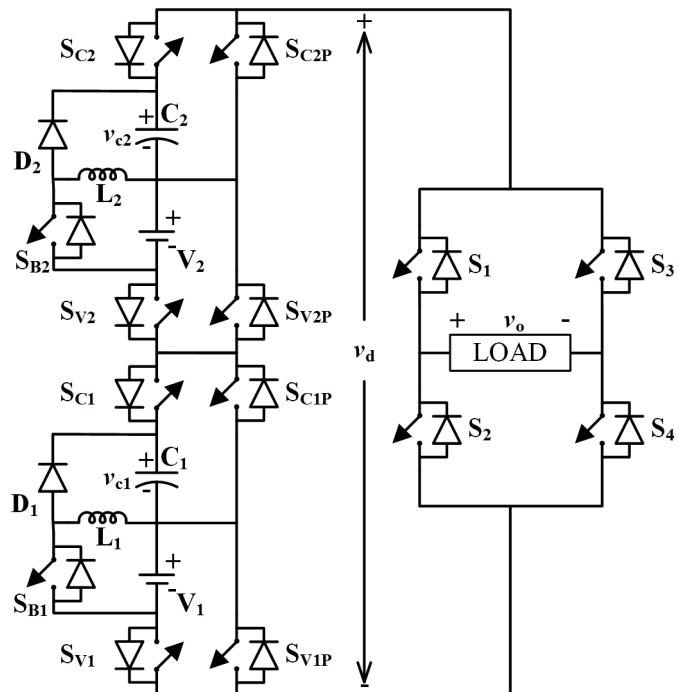

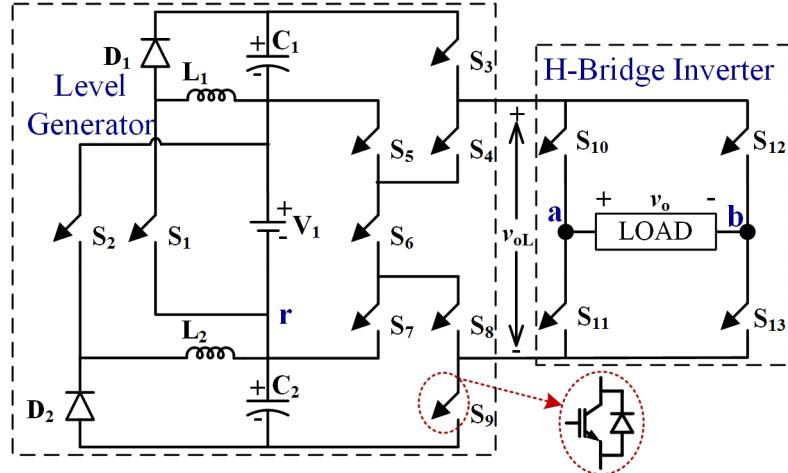

| 4.4  | Proposed IBDIMLI circuit for $x=2$ . . . . .                                                                                                                                                                                                                                                      | 57 |

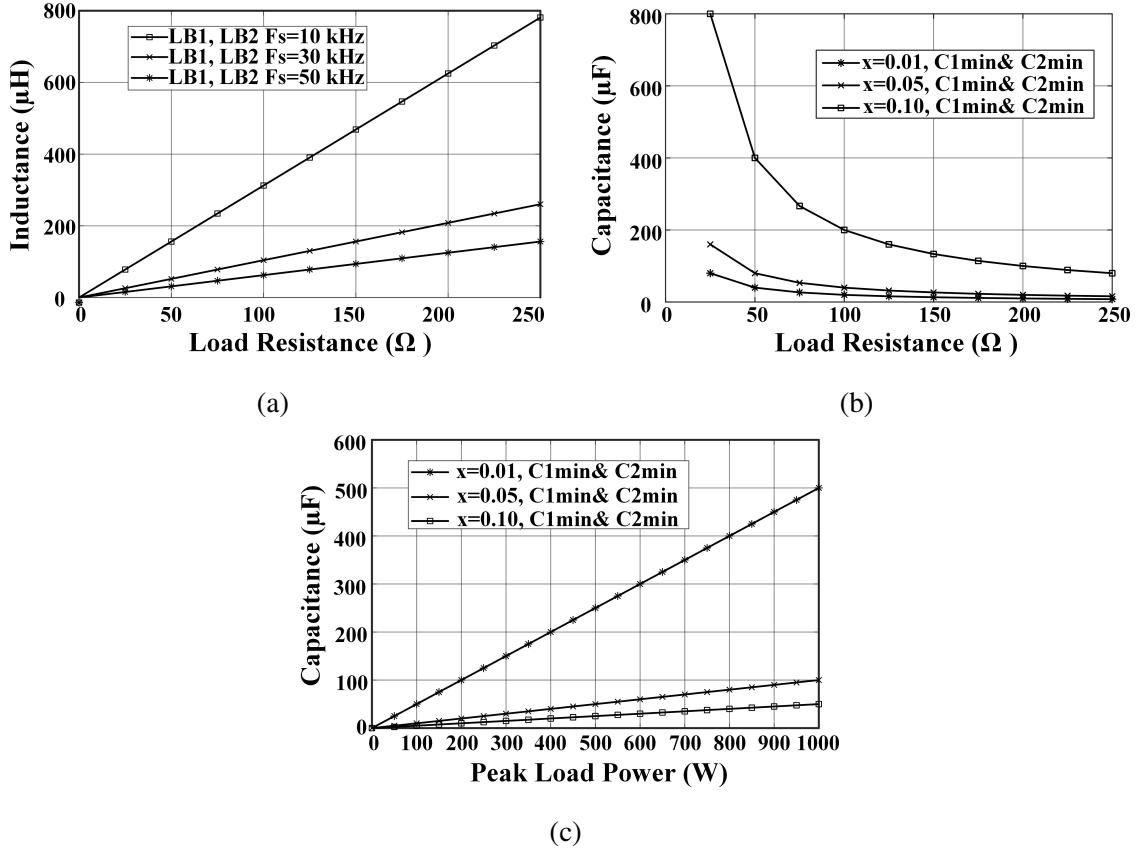

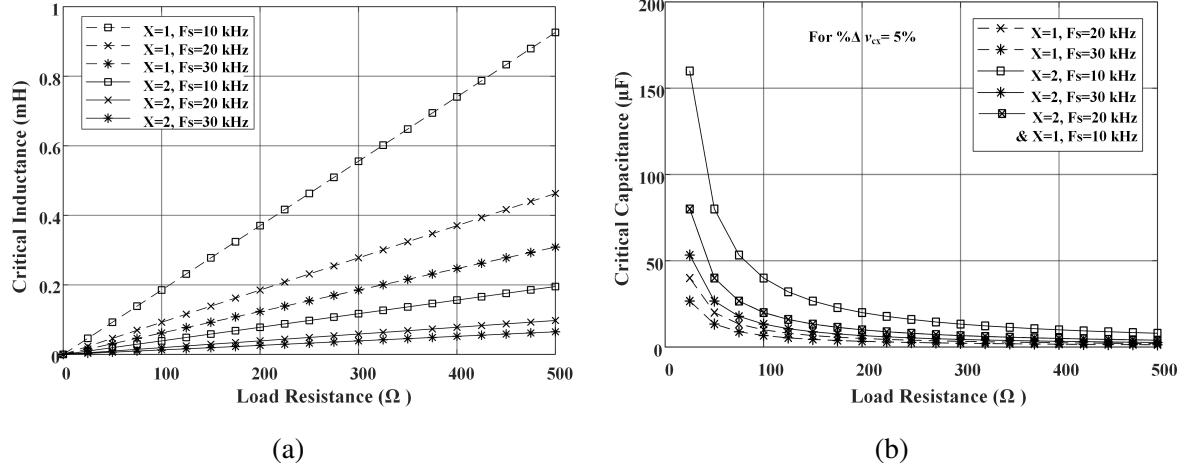

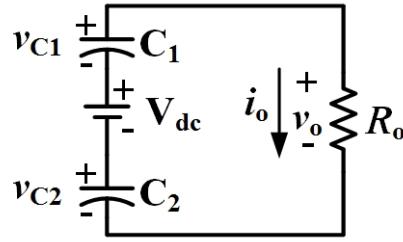

| 4.5  | Variation of critical inductance and capacitance with respect to load resistance for symmetrical operation of the IBDIMLI at different switching frequencies . . . . .                                                                                                                            | 58 |

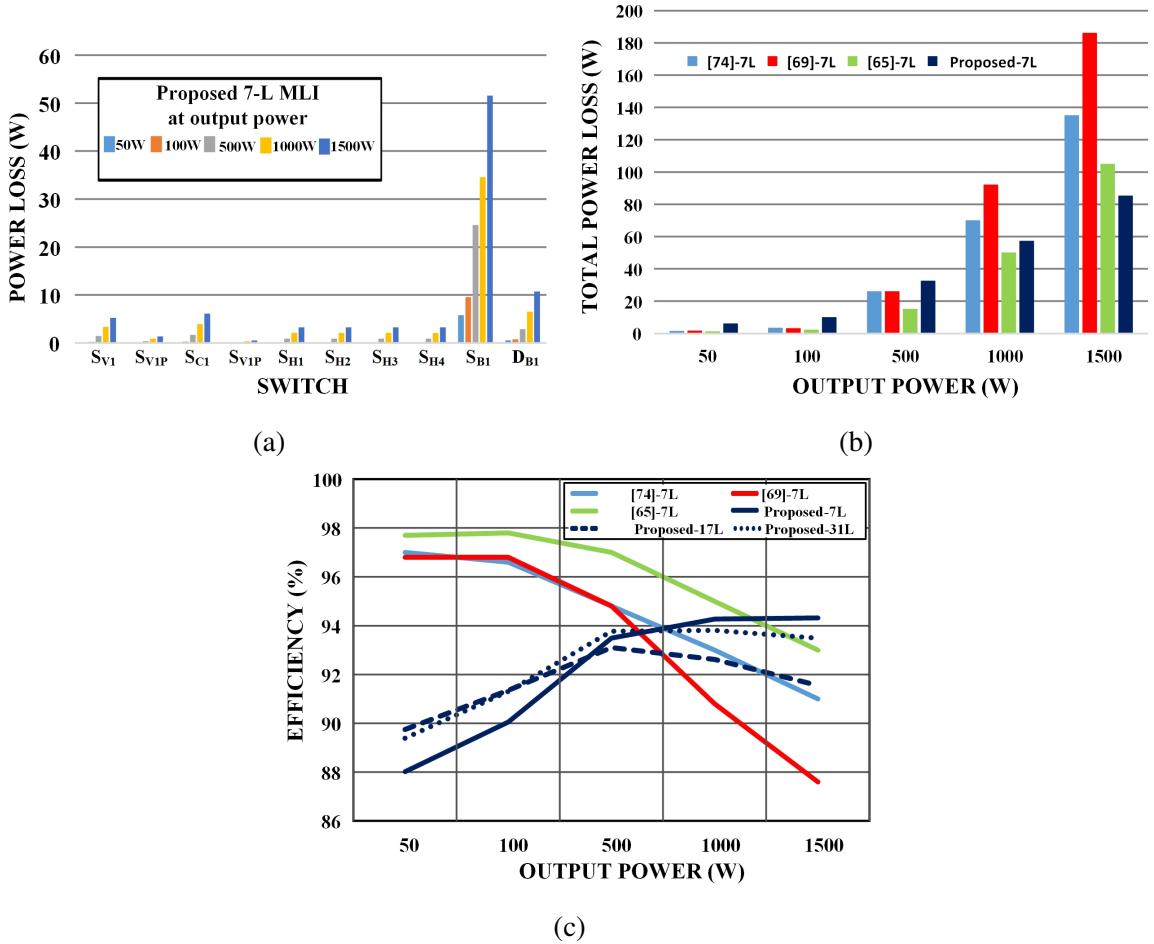

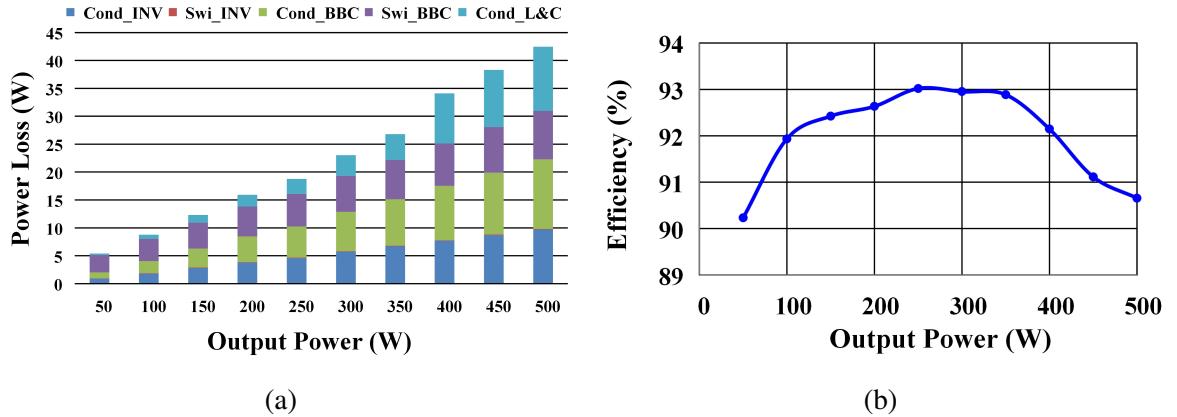

| 4.6  | Comparison of (a) power loss of switches of IBDIMLI (b) total power loss distribution and (c) efficiency characteristics of proposed MLI with recent boost MLIs at different output powers. . . . .                                                                                               | 62 |

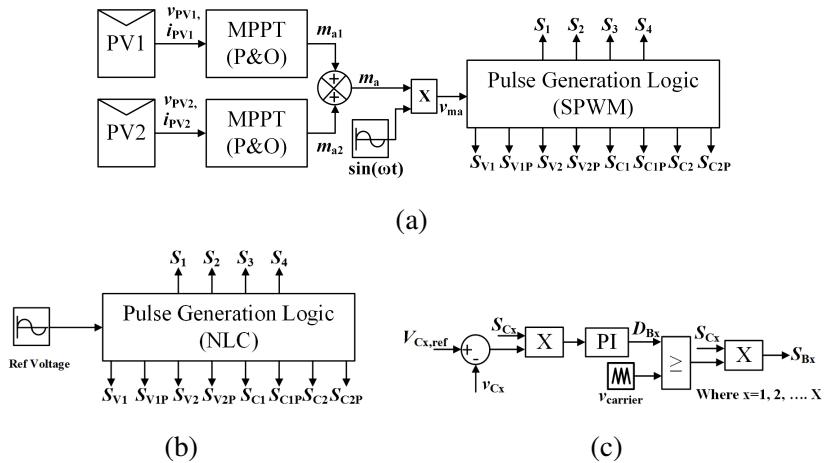

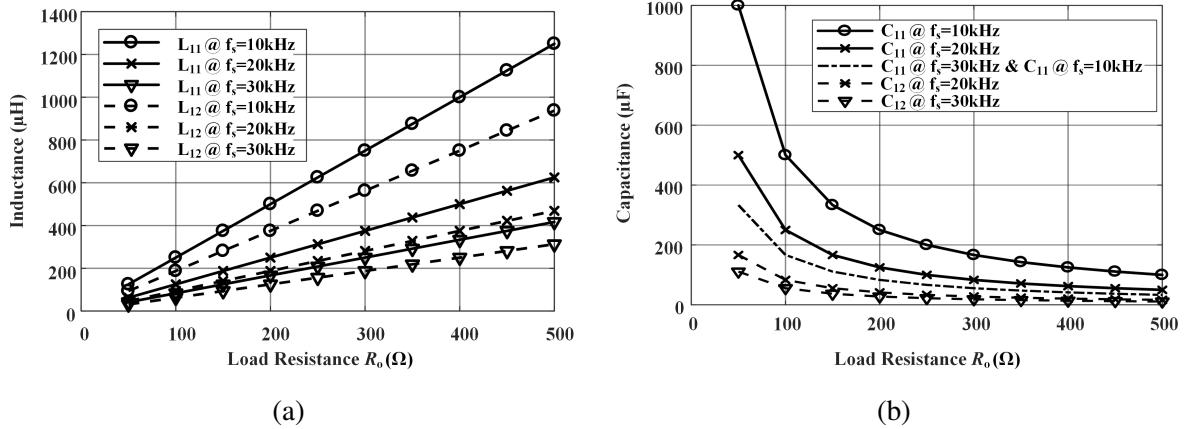

| 4.7  | Block diagram of control logic: (a) SPWM control (b) NLC (c) closed-loop PI controller for capacitor voltage $V_{Cx}$ . . . . .                                                                                                                                                                   | 63 |

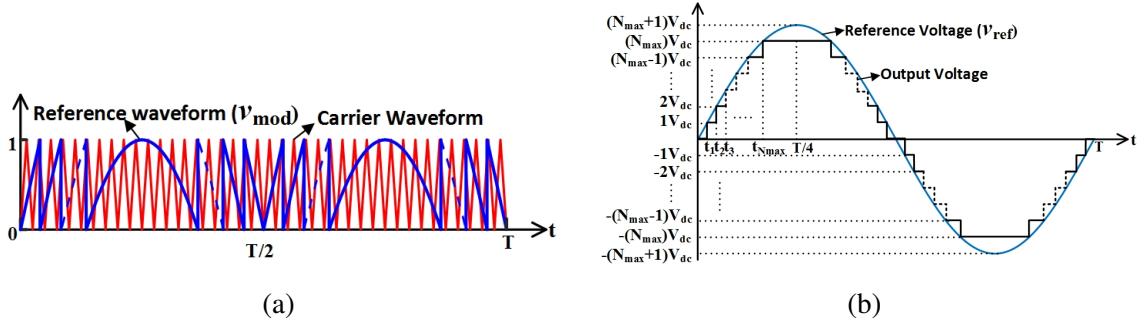

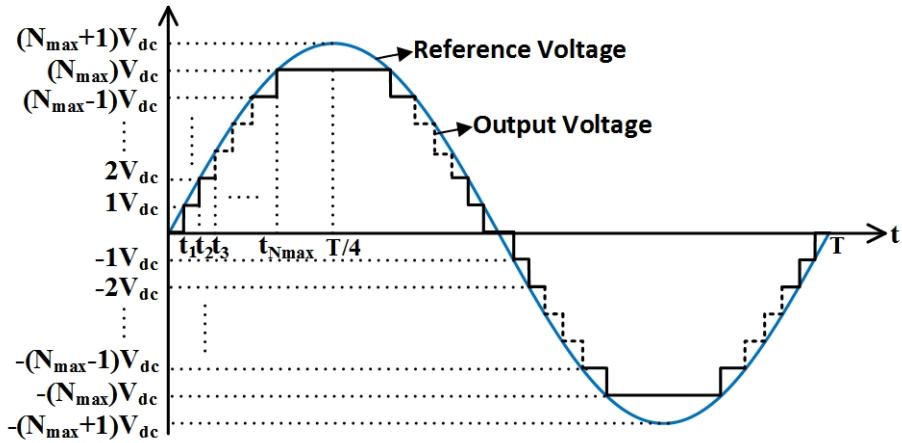

| 4.8  | Modulation scheme of the proposed MLI for (a) SPWM control (b) NLC control                                                                                                                                                                                                                        | 64 |

| 4.9  | Experimental prototype of the proposed IBDIMLI. . . . .                                                                                                                                                                                                                                           | 65 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

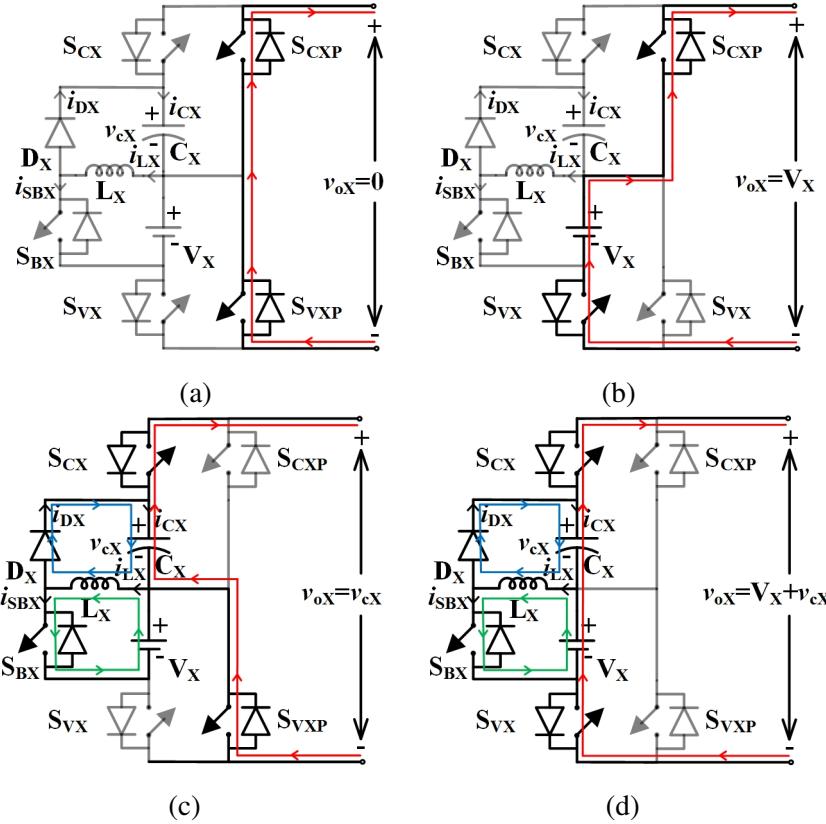

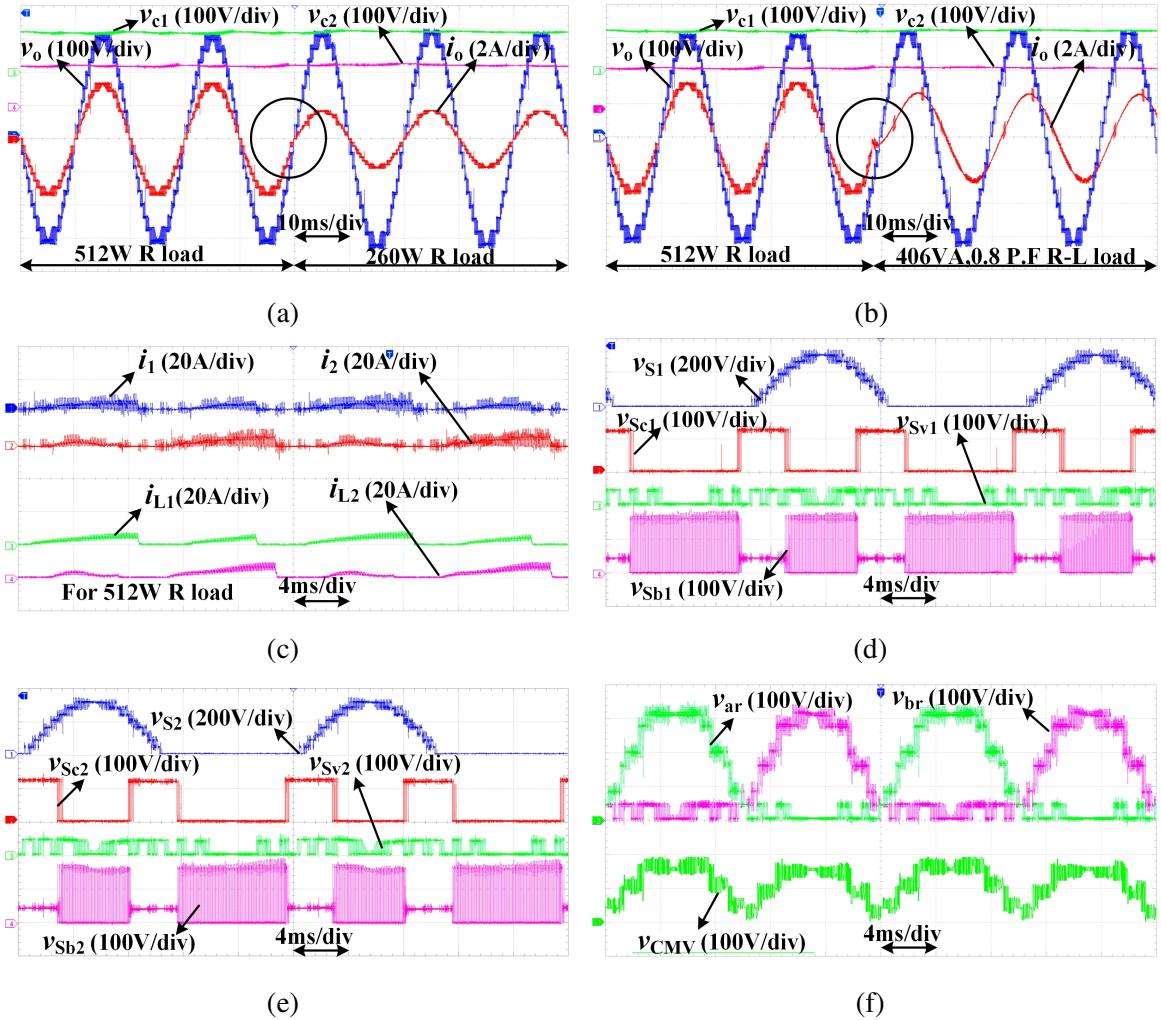

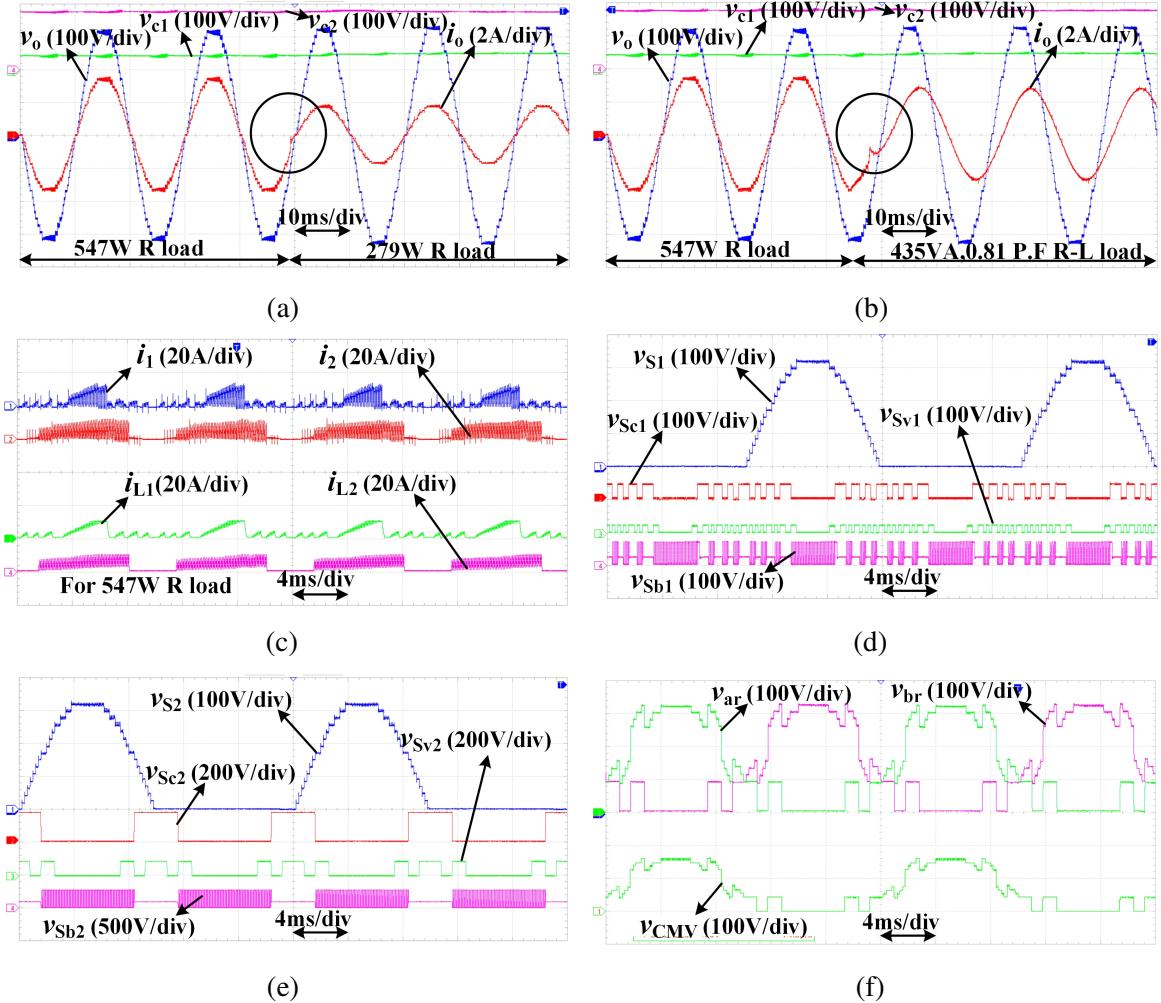

| 4.10 Experimental waveforms of 17-level operation with SPWM: (a) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in R load (b) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in load i.e., R-load to R-L load (c) $i_1$ , $i_2$ , $i_{L1}$ & $i_{L2}$ (d) voltage of switches $S_1$ , $S_{C1}$ , $S_{V1}$ & $S_{B1}$ (e) voltage of switches $S_2$ , $S_{C2}$ , $S_{V2}$ & $S_{B2}$ (f) $v_{ar}$ , $v_{br}$ & $v_{CMV}$ . . . . . | 66 |

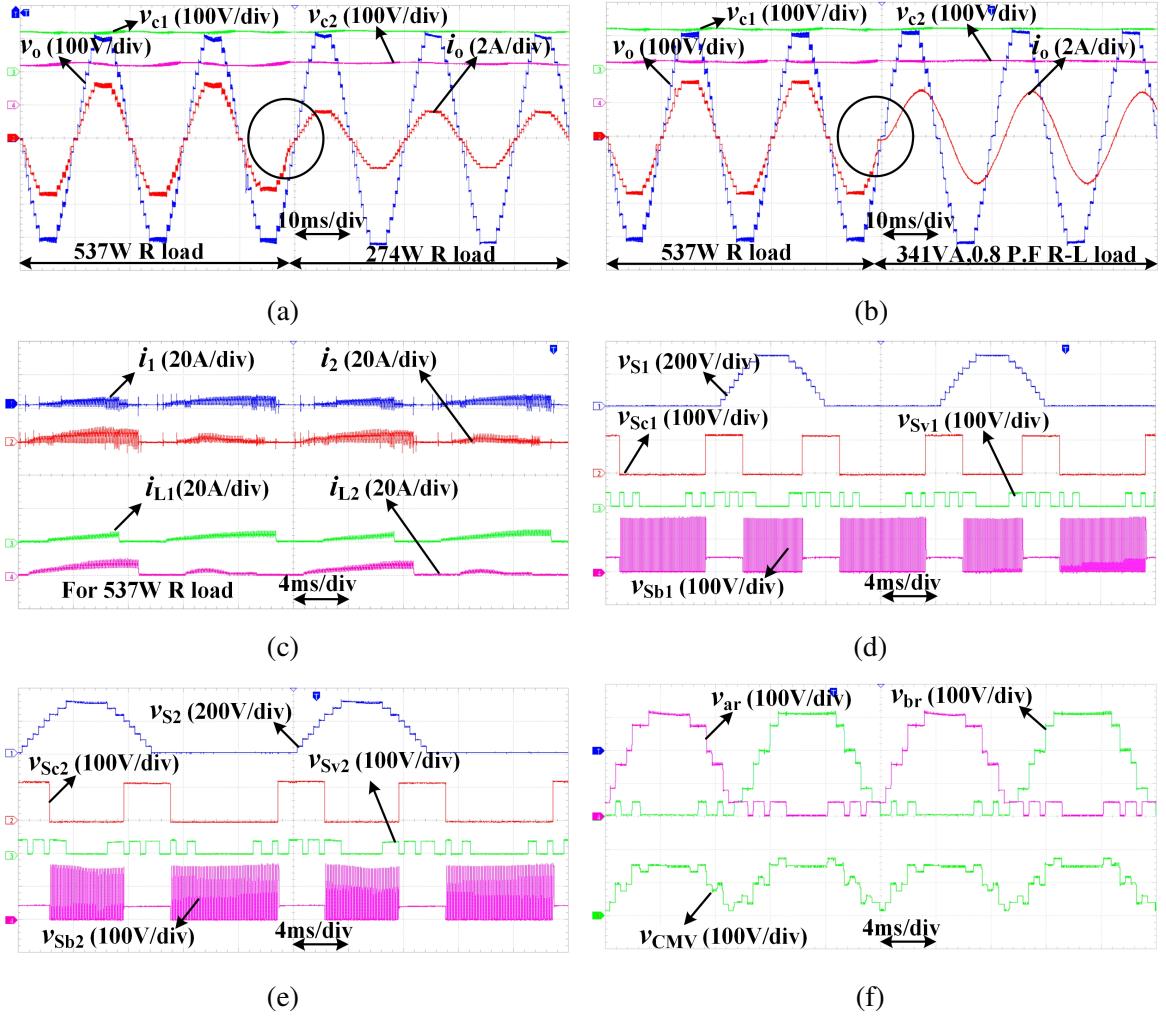

| 4.11 Experimental waveforms of 17-level operation with NLC: (a) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in R load (b) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in load i.e., R-load to R-L load (c) $i_1$ , $i_2$ , $i_{L1}$ & $i_{L2}$ (d) voltage of switches $S_1$ , $S_{C1}$ , $S_{V1}$ & $S_{B1}$ (e) voltage of switches $S_2$ , $S_{C2}$ , $S_{V2}$ & $S_{B2}$ (f) $v_{ar}$ , $v_{br}$ & $v_{CMV}$ . . . . .  | 67 |

| 4.12 Experimental waveforms of 31-level operation with NLC: (a) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in R load (b) $v_o$ , $i_o$ , $v_{c1}$ & $v_{c2}$ for a step change in load i.e., R-load to R-L load (c) $i_1$ , $i_2$ , $i_{L1}$ & $i_{L2}$ (d) voltage of switches $S_1$ , $S_{C1}$ , $S_{V1}$ & $S_{B1}$ (e) voltage of switches $S_2$ , $S_{C2}$ , $S_{V2}$ & $S_{B2}$ (f) $v_{ar}$ , $v_{br}$ & $v_{CMV}$ . . . . .  | 68 |

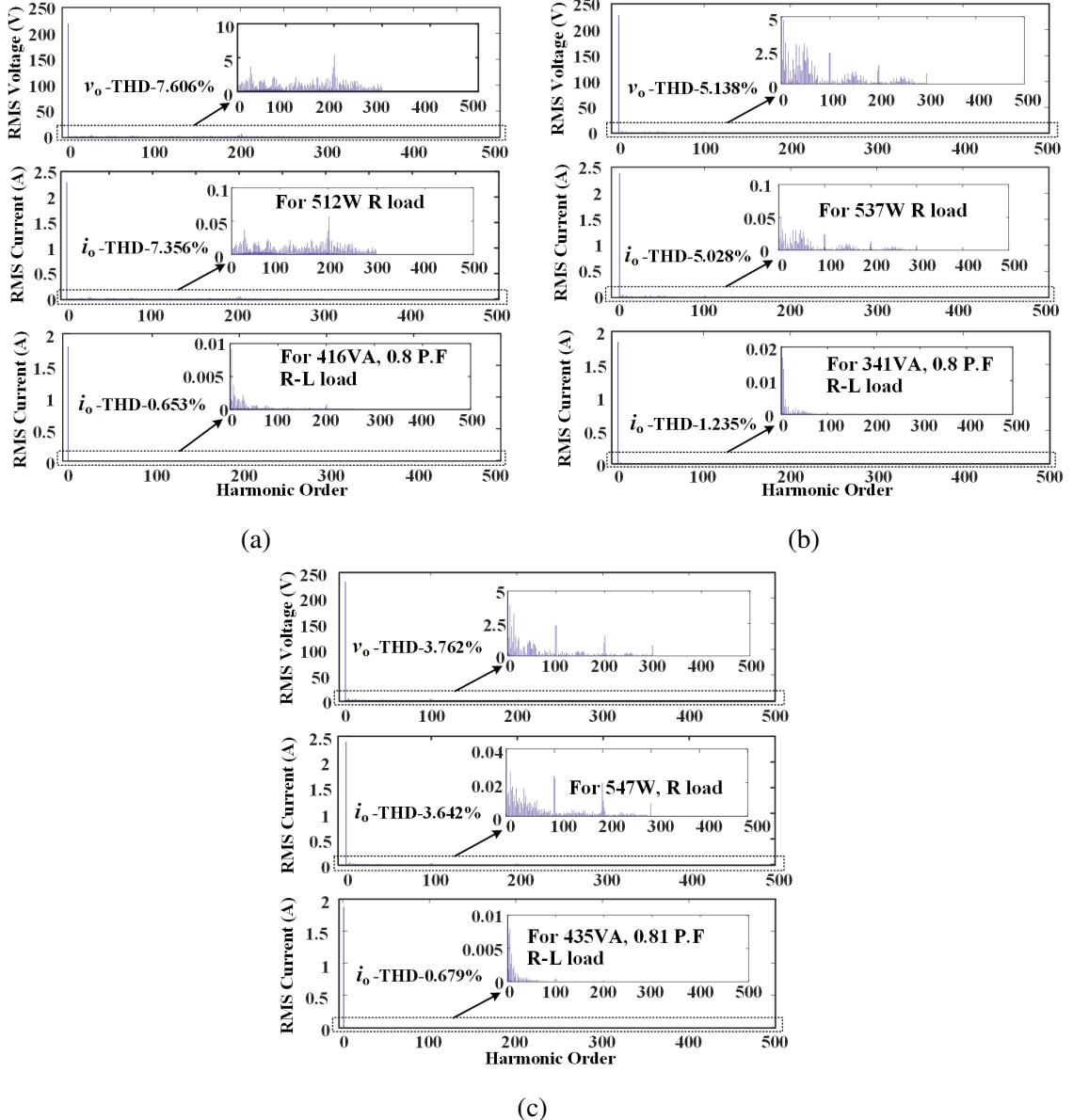

| 4.13 Experimental waveforms of harmonic spectrum of load voltage and load current with R load and R-L load for (a) 17-level operation with SPWM (b) 17-level operation with NLC (c) 31-level operation with NLC . . . . .                                                                                                                                                                                                                       | 69 |

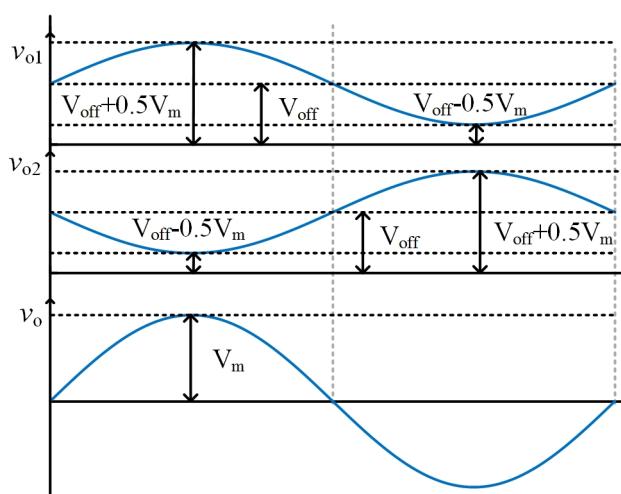

| 5.1 Proposed 13-level MLI . . . . .                                                                                                                                                                                                                                                                                                                                                                                                             | 73 |

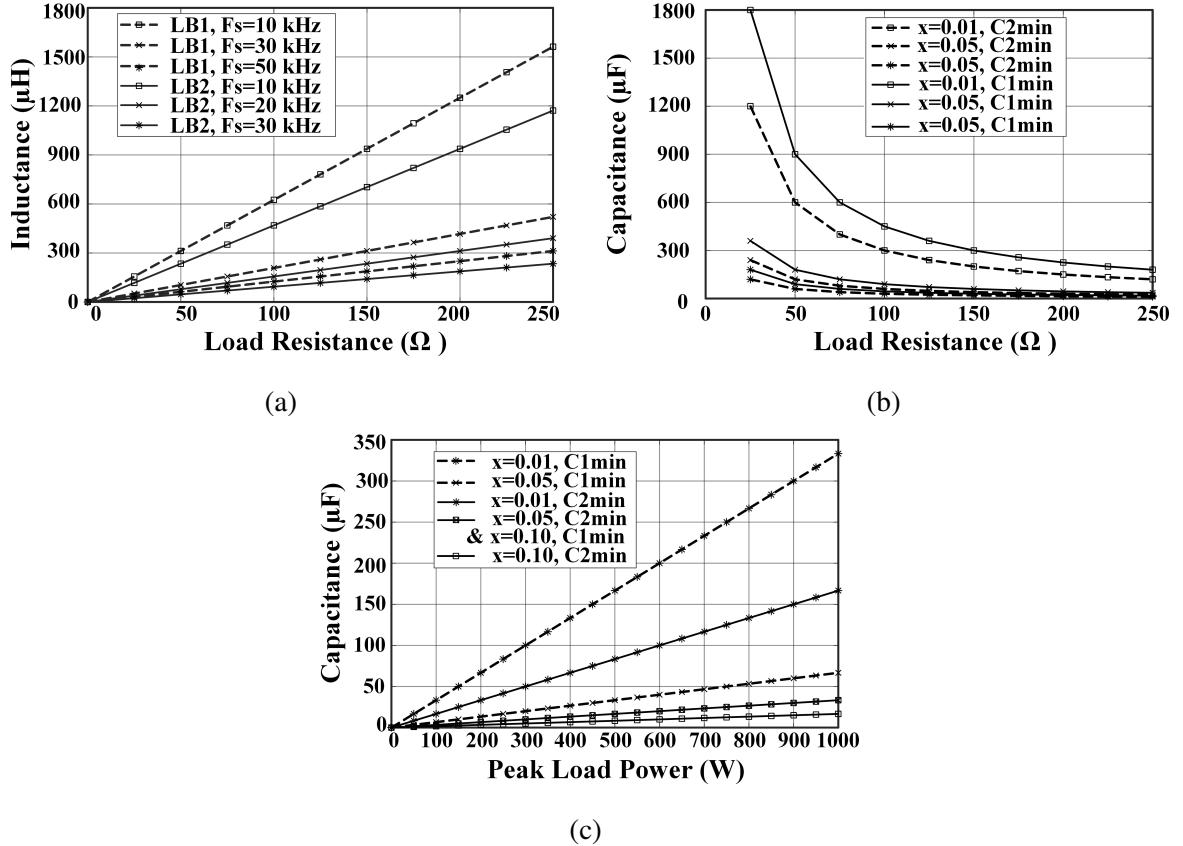

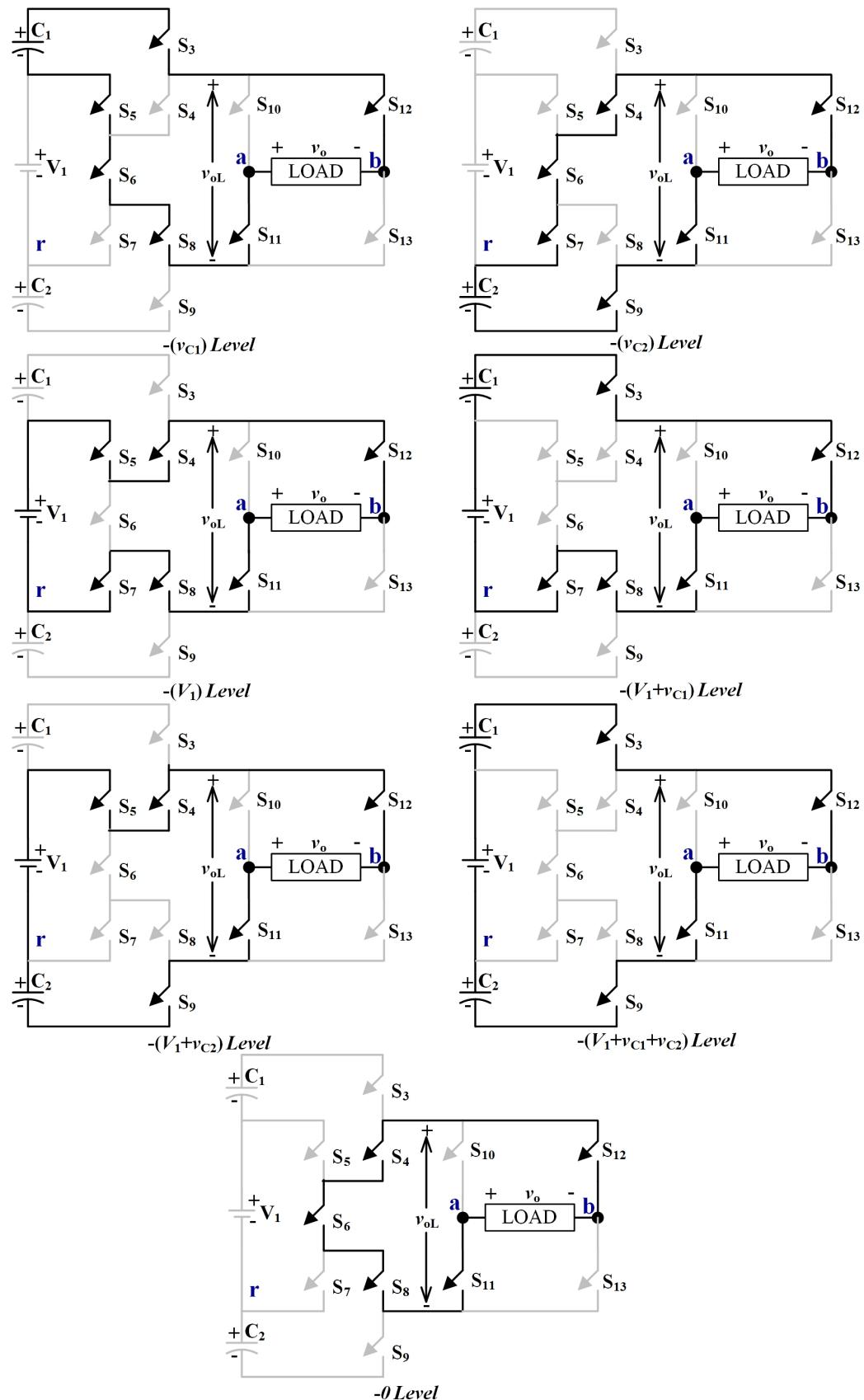

| 5.2 Equivalent circuits of SBMLI from $+0 V_{dc}$ to $+6 V_{dc}$ . . . . .                                                                                                                                                                                                                                                                                                                                                                      | 74 |

| 5.3 Equivalent circuits of SBMLI from $-0 V_{dc}$ to $-6 V_{dc}$ . . . . .                                                                                                                                                                                                                                                                                                                                                                      | 75 |

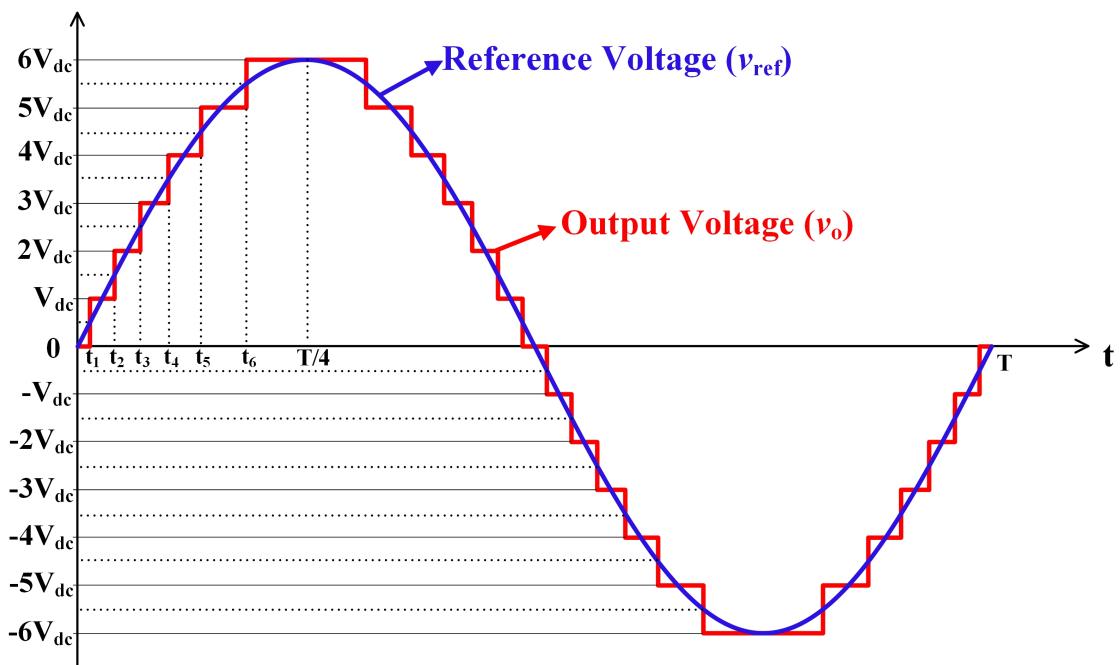

| 5.4 Proposed MLI model waveform . . . . .                                                                                                                                                                                                                                                                                                                                                                                                       | 76 |

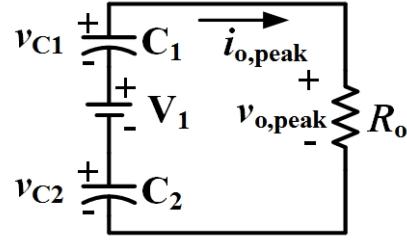

| 5.5 Equivalent circuit of the proposed MLI at $+6 V_{dc}$ / $-6 V_{dc}$ . . . . .                                                                                                                                                                                                                                                                                                                                                               | 77 |

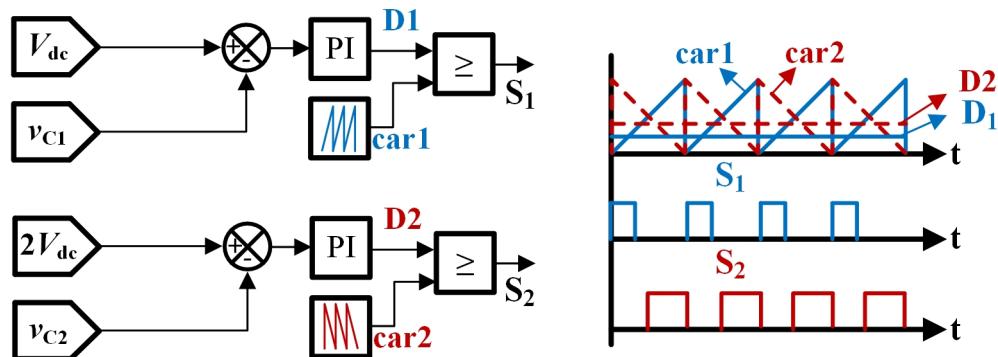

| 5.6 Block diagram of closed loop control and pulse generation of BBCs . . . . .                                                                                                                                                                                                                                                                                                                                                                 | 78 |

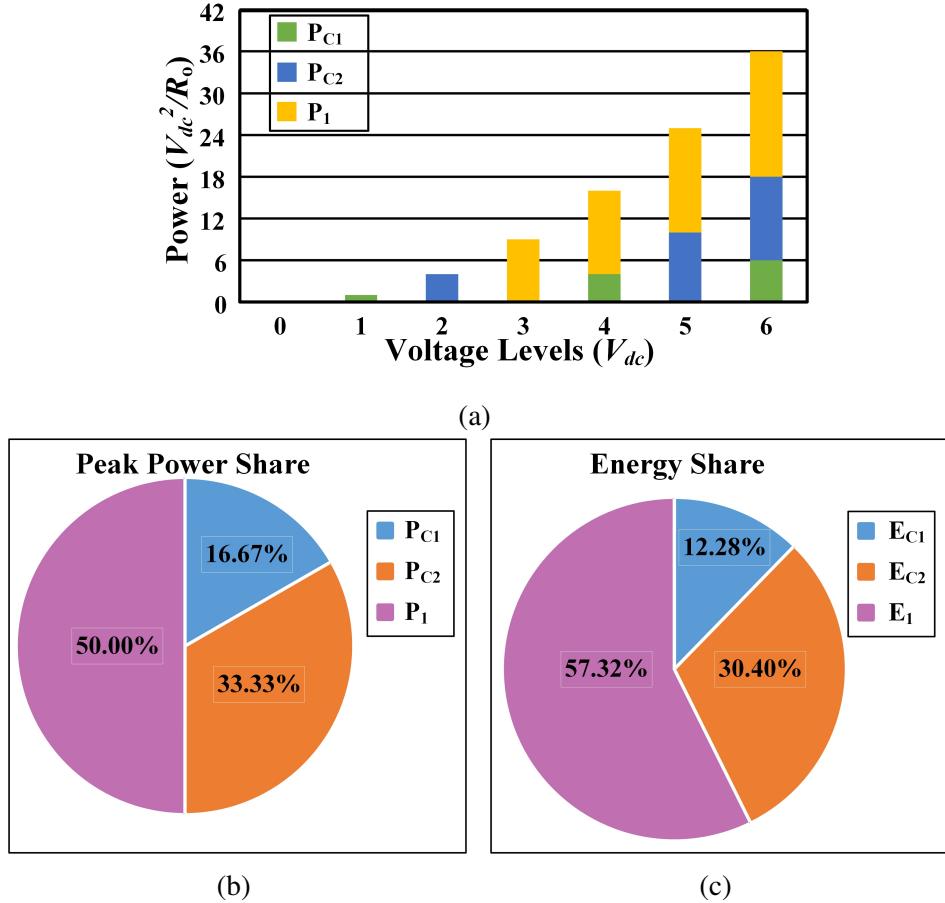

| 5.7 Comparison of source and BBCs: (a) power share at each level (b) power share at peak level (c) total energy share. . . . .                                                                                                                                                                                                                                                                                                                  | 80 |

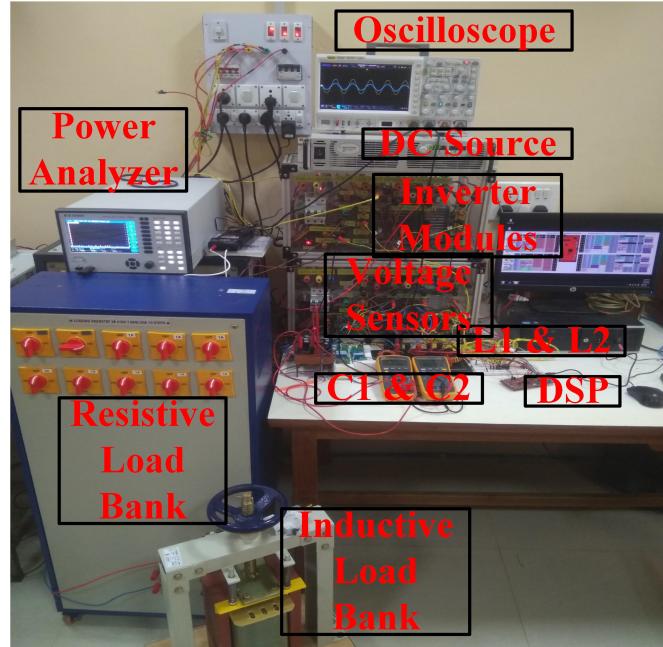

| 5.8 Experimental setup of the SBMLI . . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 82 |

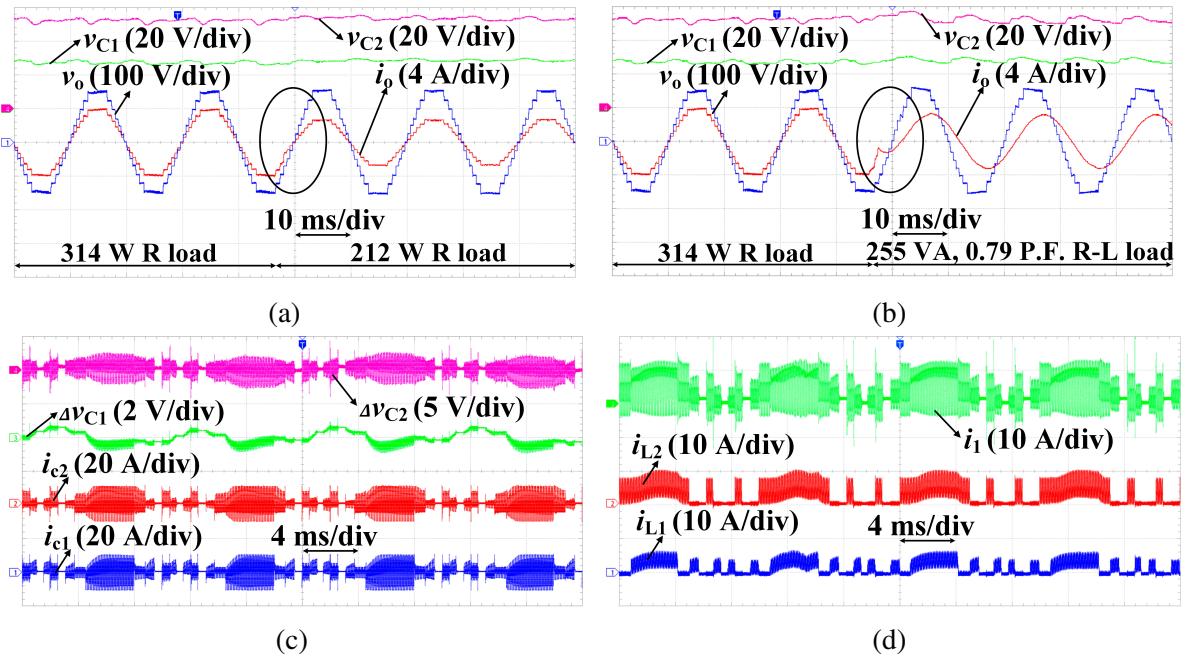

| 5.9 SBMLI's experimental results: (a) $v_o$ , $i_o$ , $v_{C1}$ and $v_{C2}$ for sudden variation in R load (i.e., 314 W to 212 W) (b) $v_o$ , $i_o$ , $v_{C1}$ and $v_{C2}$ for sudden variation in load type (i.e., 314 W to 255 VA, 0.79 power) (c) capacitors $C_1$ & $C_2$ currents and ripple voltages (d) $i_1$ , $i_{L1}$ and $i_{L2}$ . . . . .                                                                                         | 82 |

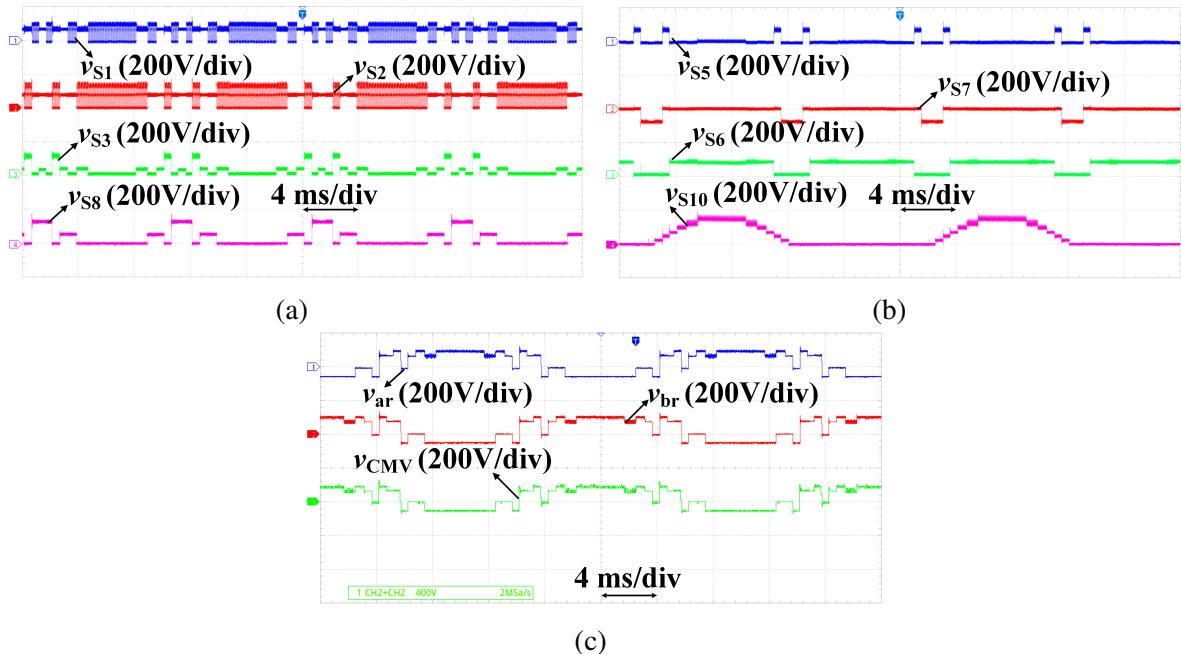

| 5.10 SBMLI's voltage waveforms of: (a) $S_1$ , $S_2$ , $S_3$ and $S_8$ (b) $S_5$ , $S_6$ , $S_7$ and $S_{10}$ (c) $v_{ar}$ , $v_{br}$ and CMV. . . . .                                                                                                                                                                                                                                                                                          | 83 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

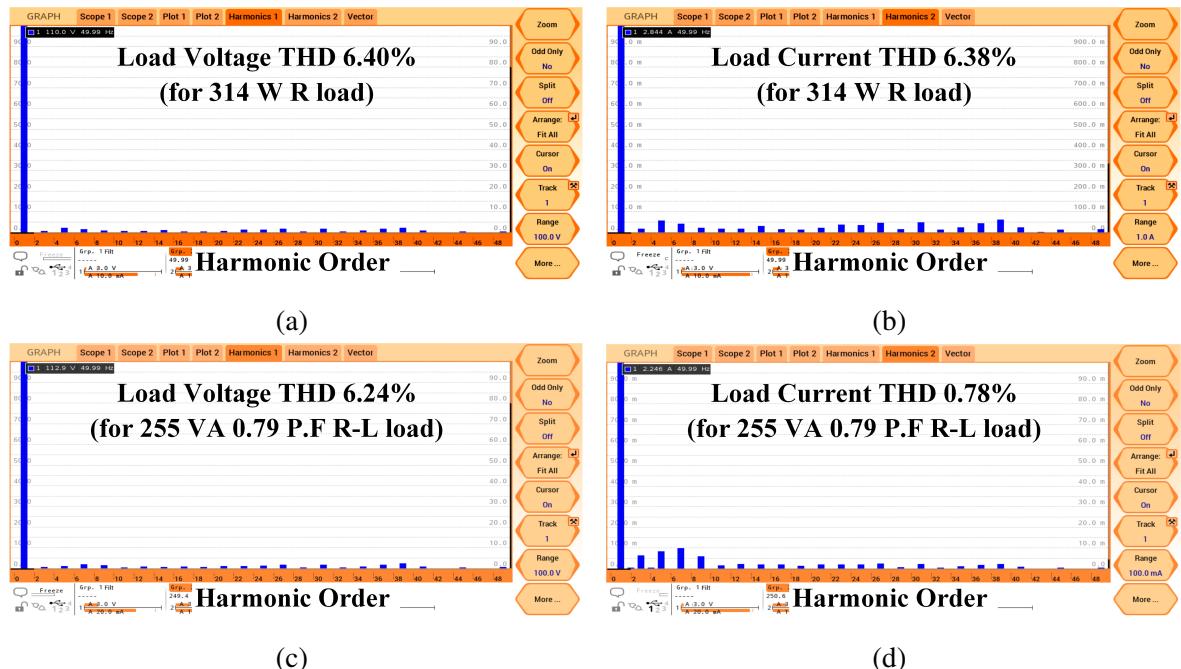

| 5.11 THD of $v_o$ and $i_o$ for (a) & (b) 314 W R load (c) & (d) 255 VA, 0.79 power factor R-L load . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83 |

| 6.1 Equivalent circuit of the ISBMLI for the peak output voltage level . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |

| 6.2 Model waveform of ISBMLIs with nearest level control . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88 |

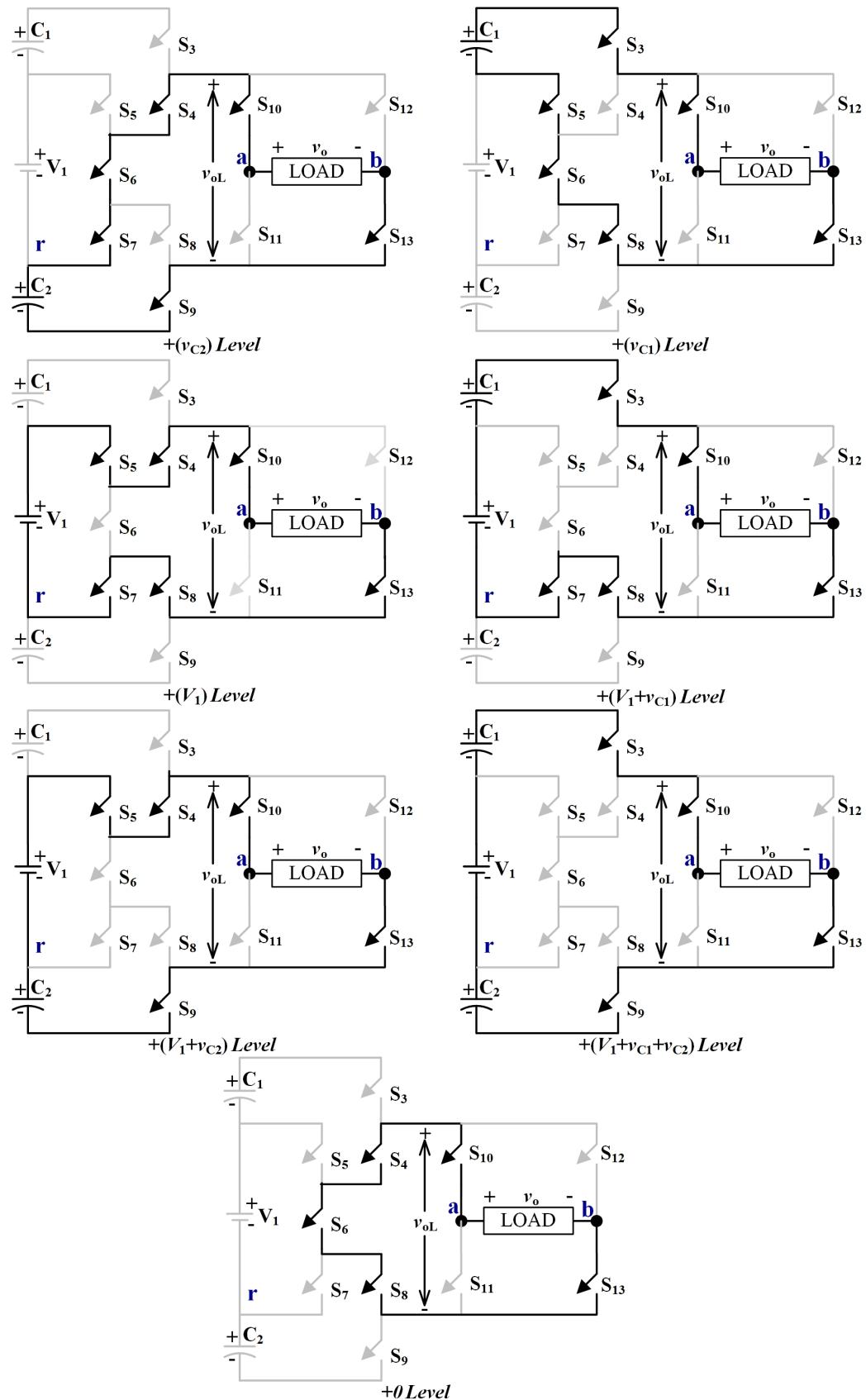

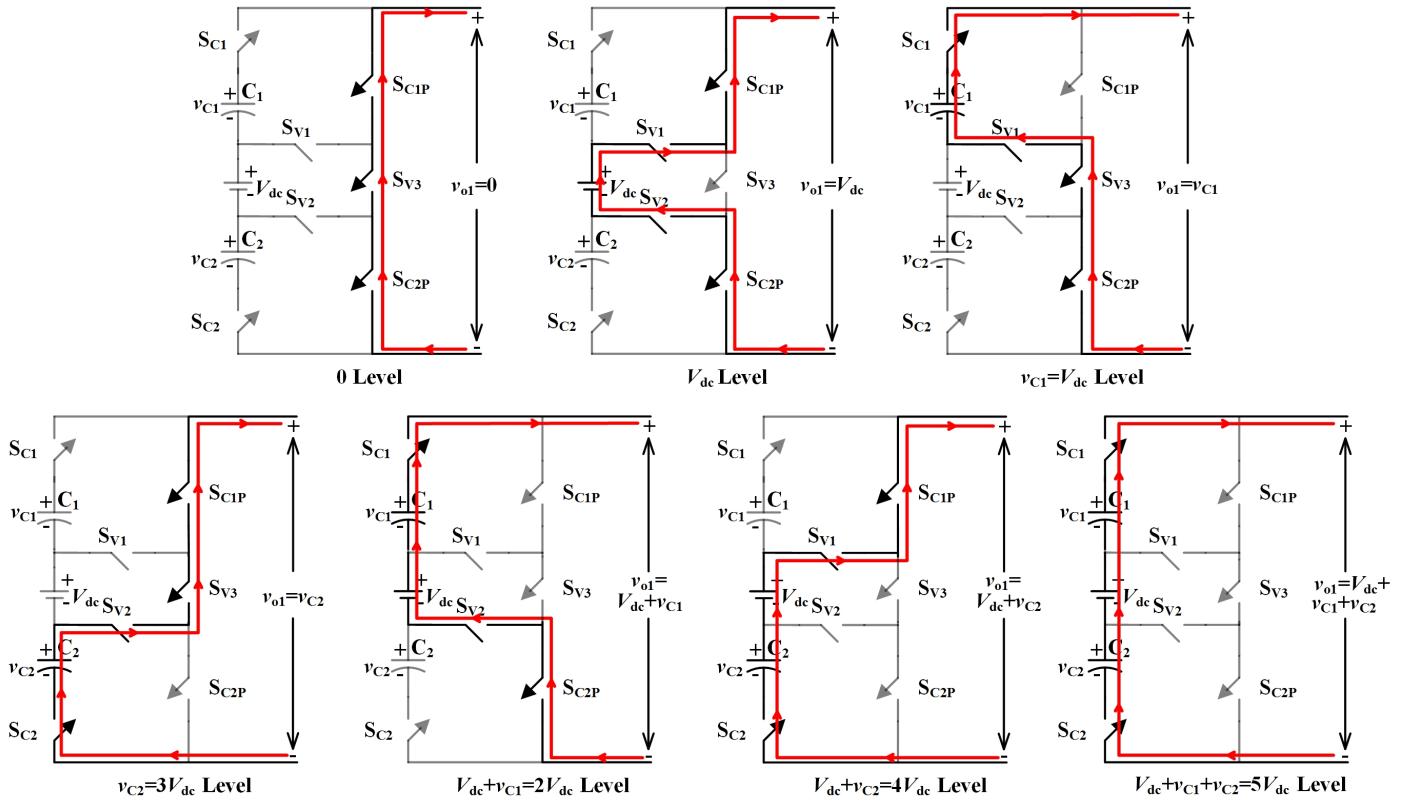

| 6.3 Equivalent circuits of ISBMLI basic unit from 0 $V_{dc}$ to 5 $V_{dc}$ levels. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 89 |

| 6.4 Equivalent circuit of the ISBMLI for the peak output voltage level . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90 |

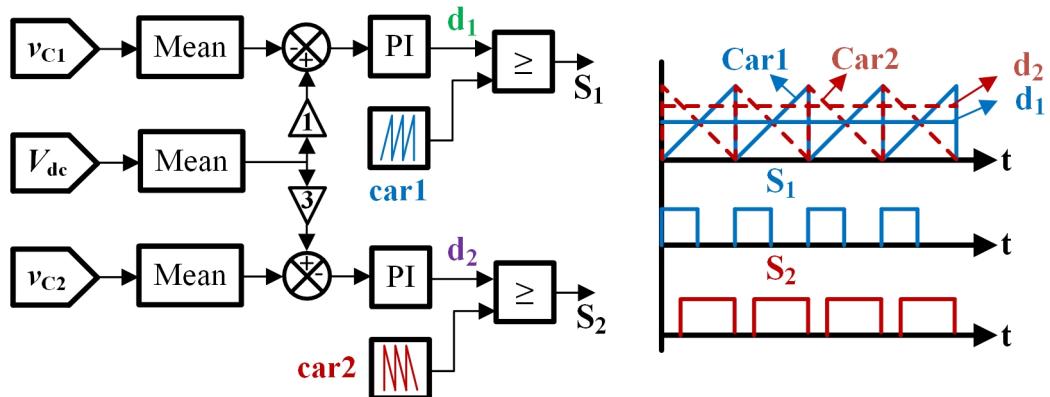

| 6.5 Design characteristics of (a) critical inductances $L_{B1}$ and $L_{B2}$ (b) minimum capacitances $C_{1,min}$ and $C_{2,min}$ for 5% ripple voltage with respect load current at different switching frequencies . . . . .                                                                                                                                                                                                                                                                                                                                                  | 90 |

| 6.6 Block diagram of closed loop control and pulse generation of BBCs . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91 |

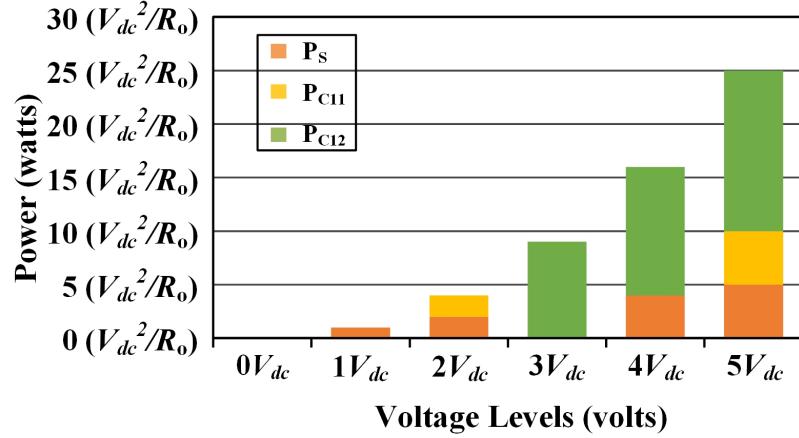

| 6.7 Power processed by DC source and BBCs at different operating voltage levels .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92 |

| 6.8 Experimental setup of the ISBMLI . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95 |

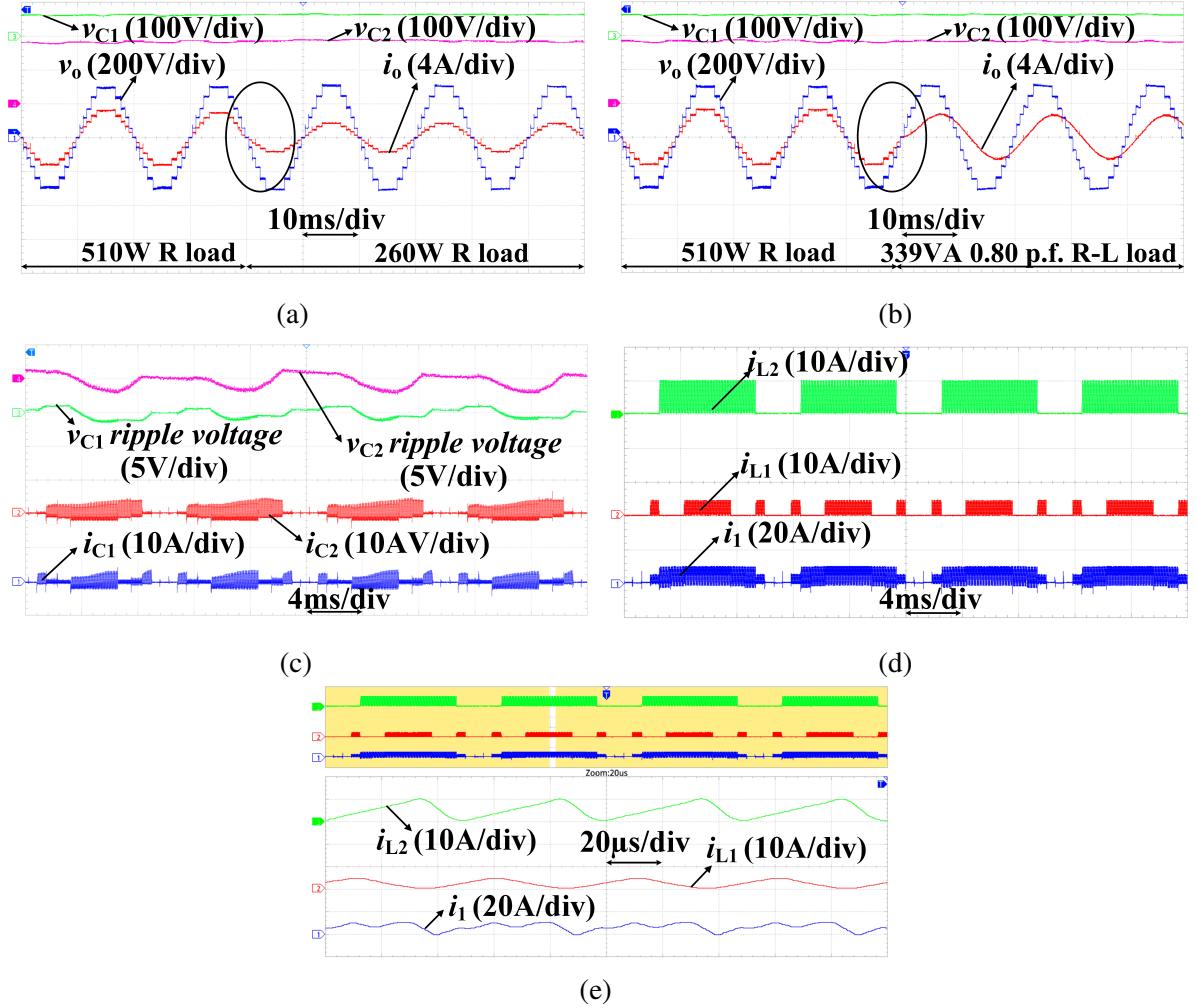

| 6.9 Experimental waveforms of the ISBMLI: (a) load voltage ( $v_o$ ), load current ( $i_o$ ) and capacitor voltages ( $v_{C1}$ and $v_{C2}$ ) during step change in R load for (i.e., 510 W R load to 260 W R load) (b) $v_o$ , $i_o$ , $v_{C1}$ and $v_{C2}$ during step change in load type (i.e., 510 W R load to 339 VA, 0.8 power factor R-L load) (c) capacitors $C_1$ & $C_2$ currents and ripple voltages (d) source current $i_1$ , inductor currents $i_{L1}$ and $i_{L2}$ (e) zoomed version of source current $i_1$ , inductor currents $i_{L1}$ and $i_{L2}$ . . . | 96 |

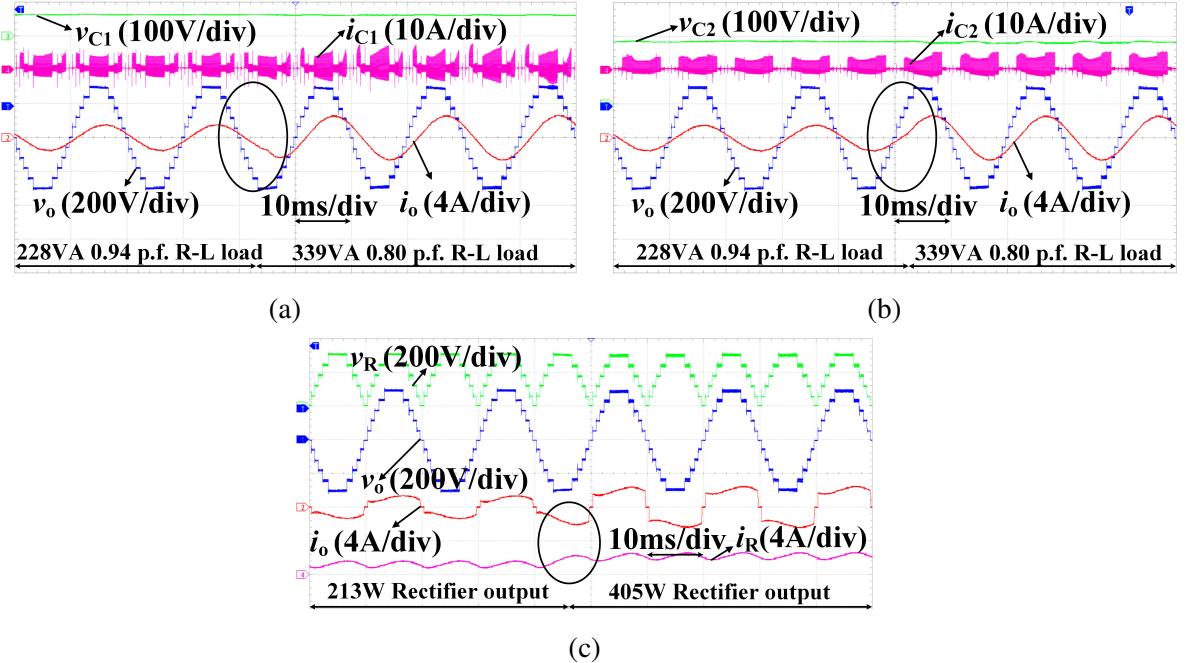

| 6.10 Experimental waveforms of the ISBMLI: (a) $v_o$ , $i_o$ , $v_{C1}$ and $i_{C1}$ during step change in RL load (i.e., 228 VA, 0.94 power factor RL load to 339 VA, 0.8 power factor R-L load) (b) $v_o$ , $i_o$ , $v_{C2}$ and $i_{C2}$ during step change in RL load (i.e., 228 VA, 0.94 power factor RL load to 339 VA, 0.8 power factor R-L load) (c) $v_o$ , $i_o$ , rectifier output voltage and output currents $v_R$ and $i_R$ during step change in non-linear load (i.e., 213 W to 405 W) . . . . .                                                                | 97 |

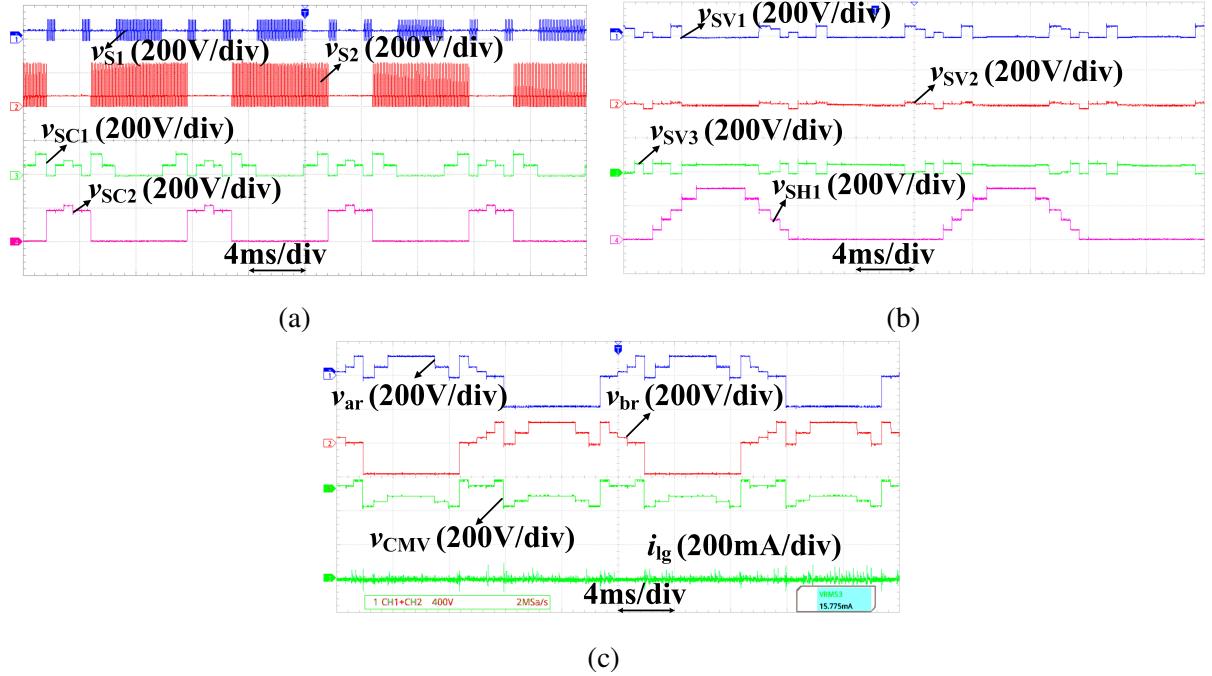

| 6.11 Experimental waveforms of the ISBMLI: (a) voltages of switches $S_1$ , $S_2$ , $S_{C1}$ and $S_{C2}$ (b) voltages of switches $S_{V1}$ , $S_{V2}$ , $S_{V3}$ and $S_{H1}$ (c) pole voltages $v_{ar}$ , $v_{br}$ , CMV and leakage current $i_{lg}$ . . . . .                                                                                                                                                                                                                                                                                                               | 98 |

| 6.12 ISBMLI: (a) Power loss distribution and (b) efficiency characteristics for 11-level operation at different output power conditions. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                | 98 |

|                                                                                                                                                                                                                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

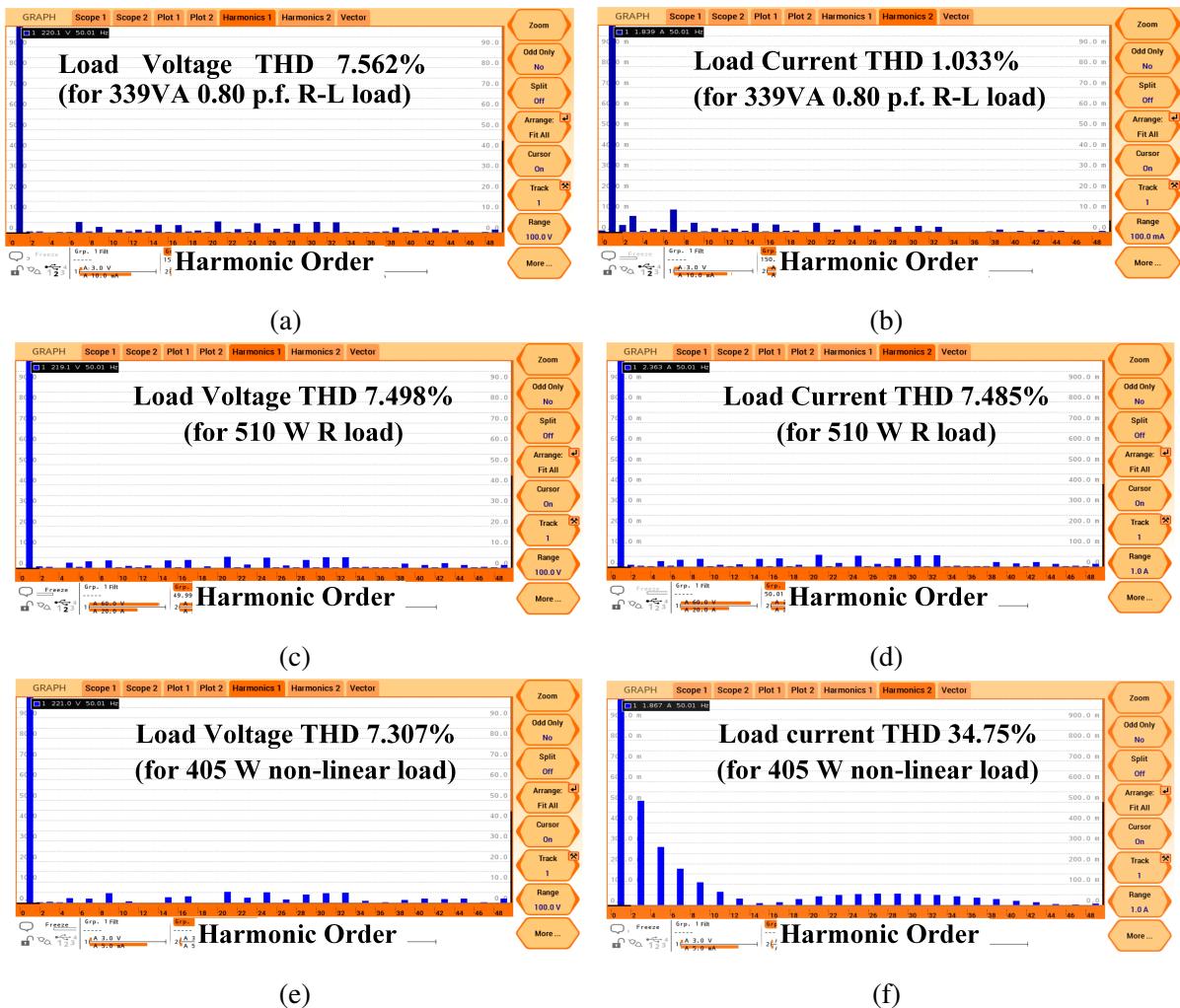

| 6.13 Experimental waveforms of the ISBMLI: (a) & (b) harmonic spectrum of $v_o$ and $i_o$ for 339 VA, 0.8 power factor R-L load respectively (c) & (d) harmonic spectrum of $v_o$ and $i_o$ for 510W R load respectively (e) & (f) harmonic spectrum of $v_o$ and $i_o$ for 405 W non-linear load respectively . . . . . | 99 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

# List of Tables

|      |                                                                                                                                                                    |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Summary of single-phase transformerless step-up inverters . . . . .                                                                                                | 24 |

| 3.1  | Capacitor voltages, and step-up ratios for 9, 11 & 13-level operation of BDIMLI with $V_1 = V_2 = V_{dc}$ . . . . .                                                | 34 |

| 3.2  | Switching States of the proposed BDIMLI for 9-evel operation . . . . .                                                                                             | 38 |

| 3.3  | Switching States of the proposed BDIMLI for 11-level Output . . . . .                                                                                              | 39 |

| 3.4  | Switching States of the proposed BDIMLI for 13-level operation . . . . .                                                                                           | 40 |

| 3.5  | Comparison of Proposed BDIMLI with Existing MLI Topologies with symmetrical DC sources for 9-level output ( $P_o = 1000W$ , $V_{o,max} = 200V$ and $f_o = 50Hz$ )  | 43 |

| 3.6  | Comparison of Proposed BDIMLI with Existing MLI Topologies with symmetrical DC sources for 13-level output ( $P_o = 1000W$ , $V_{o,max} = 300V$ and $f_o = 50Hz$ ) | 43 |

| 3.7  | Cost comparison of the proposed BDIMLI with other step-up MLI topologies for 13-level operation at $P_o = 1000W$ . . . . .                                         | 44 |

| 3.8  | Loss analysis of the Proposed BDIMLI for 9 and 13-level operation using PSIM                                                                                       | 45 |

| 3.9  | Specification & Design Parameters of BDIMLI . . . . .                                                                                                              | 46 |

| 3.10 | Comparison of experimental THD of the proposed BDIMLI with the MLI presented in [1] . . . . .                                                                      | 50 |

| 4.1  | Switching States of Basic FLU . . . . .                                                                                                                            | 54 |

| 4.2  | Switching States of proposed IBDIMLI for 17 Level operation . . . . .                                                                                              | 56 |

| 4.3  | Comparison of IBDIMLI with existing MLI topologies . . . . .                                                                                                       | 59 |

| 4.4  | Cost comparison of IBDIMLI with existing 7-level boost inverter topologies . .                                                                                     | 61 |

| 4.5  | Specification & Design Parameters of the IBDIMLI for experimental study . .                                                                                        | 65 |

| 5.1  | Look-up table of SBMLI for 13-level operation with $V_1 = 3 V_{dc}$ , $V_{c1} = V_{dc}$ and $V_{c2} = 2 V_{dc}$ . . . . .                                          | 76 |

|     |                                                                                 |    |

|-----|---------------------------------------------------------------------------------|----|

| 5.2 | Comparison of the SBMLI and recent 13-level MLIs . . . . .                      | 81 |

| 5.3 | Specifications of the proposed 13-level MLI . . . . .                           | 81 |

| 6.1 | Switching States of basic unit of ISBMLI . . . . .                              | 88 |

| 6.2 | Comparative study of the ISBMLI with the recent 11-level SCMLIs . . . . .       | 93 |

| 6.3 | Comparative study of the ISBMLI and the recent SCMLIs in generalized operation  | 94 |

| 6.4 | Specifications and Design Parameters of ISBMLI for 11-level operation . . . . . | 95 |

| 6.5 | Power loss distribution of ISBMLI at different power ratings . . . . .          | 97 |

## Abbreviations & Symbols

|                 |                                                  |

|-----------------|--------------------------------------------------|

| $\%P_{c1}$      | Percentage of peak power processed by each BBC-1 |

| $\%P_{c2}$      | Percentage of peak power processed by each BBC-2 |

| $\%P_{S,max}$   | Percentage of peak power processed by source     |

| $\Delta v_C$    | Ripple voltage of capacitor $C$                  |

| $\Delta V_{c1}$ | Ripple voltage of capacitor $C_1$                |

| $\Delta V_{c2}$ | Ripple voltage of capacitor $C_2$                |

| $\Delta V_{cx}$ | Ripple voltage of capacitor $C_x$                |

| $\delta$        | Duty cycle of BBC                                |

| $\delta_x$      | Duty cycle of BBC x                              |

| $\delta_1$      | Duty cycle of BBC-1                              |

| $\delta_2$      | Duty cycle of BBC-2                              |

| $\omega_{ch}$   | Natural frequency of the charging circuit        |

| $C_p$           | Parasitic capacitance of PV panel                |

| $C_{1,min}$     | Minimum capacitance of capacitor $C_1$           |

| $C_{2,min}$     | Minimum capacitance of capacitor $C_2$           |

| $C_{min,SC}$    | Minimum capacitance of capacitor $C$ in SC unit  |

| $C_{min}$       | Minimum capacitance of capacitor $C$             |

| $C_{xmin}$      | Minimum capacitance of capacitor $C_x$           |

|               |                                                 |

|---------------|-------------------------------------------------|

| $car1$        | Carrier voltage 1                               |

| $car2$        | Carrier voltage 2                               |

| $E_C$         | Energy transferred to the capacitor $C$         |

| $E_L$         | Energy stored in the inductor $L$               |

| $E_S$         | Energy processed by the source                  |

| $E_{c1}$      | Energy processed by BBC-1                       |

| $E_{c2}$      | Energy processed by BBC-2                       |

| $E_{Total}$   | Total energy delivered to load in quarter cycle |

| $f_o$         | Frequency of the output voltage                 |

| $f_s$         | Switching frequency of BBCs                     |

| $f_{tri}$     | Frequency of carrier voltage                    |

| $i_C$         | Instantaneous current through capacitor $C$     |

| $i_L$         | Instantaneous current through inductor $L$      |

| $I_o$         | Average output current                          |

| $I_{C,peak}$  | Peak current the capacitor $C$                  |

| $I_{CP,QRSC}$ | Peak current the capacitor $C$ in QRSC cell     |

| $I_{CP,SC}$   | Peak current the capacitor $C$ in SC cell       |

| $i_D$         | Instantaneous current through switch $D$        |

| $I_{LB,peak}$ | Peak current of inductor $L$ in BCM             |

| $i_{lg1}$     | Leakage current 1                               |

| $i_{lg2}$     | Leakage current 2                               |

|             |                                            |

|-------------|--------------------------------------------|

| $I_{Lpeak}$ | Peak current of the inductor $L$           |

| $I_{o,max}$ | Peak Value of output current               |

| $i_o$       | Instantaneous output current               |

| $i_{Sb}$    | Instantaneous current through switch $S_b$ |

| $k$         | Voltage level                              |

| $L_B$       | Critical inductance of inductor $L$        |

| $L_{B1}$    | Critical inductance of inductor $L_1$      |

| $L_{B2}$    | Critical inductance of inductor $L_2$      |

| $L_{ch}$    | Inductor in QRSC cell                      |

| $L_{xB}$    | Critical inductance of inductor $L_x$      |

| $m_{a1}$    | Amplitude modulation index 1               |

| $m_{a2}$    | Amplitude modulation index 2               |

| $n$         | Step-up ratio BBC                          |

| $n_x$       | Step-up ratio of BBC-x                     |

| $n_1$       | Step-up ratio of BBC-1                     |

| $n_2$       | Step-up ratio of BBC-2                     |

| $N_{cap}$   | Number of capacitors                       |

| $N_{dc}$    | Number of DC sources                       |

| $N_{dio}$   | Number of diodes                           |

| $N_{dri}$   | Number of drivers                          |

| $N_{ind}$   | Number of inductors                        |

|                 |                                                          |

|-----------------|----------------------------------------------------------|

| $N_{lev}$       | Number of levels                                         |

| $N_{max,asymm}$ | Number of voltage levels in asymmetric mode of operation |

| $N_{max,symm}$  | Number of voltage levels in symmetric mode of operation  |

| $N_{swi}$       | Number of switches                                       |

| $P_o$           | Average output power                                     |

| $P_{1,avg}$     | Average voltage of source 1                              |

| $P_{2,avg}$     | Average voltage of source 2                              |

| $P_{c1}$        | Maximum power delivered by capacitor $C_1$               |

| $P_{c2}$        | Maximum power delivered by capacitor $C_2$               |

| $P_{cond}$      | Total conduction losses                                  |

| $P_{cx}$        | Maximum power shared by capacitor $C_x$                  |

| $P_{lc}$        | Total passive component power losses                     |

| $P_{o,max}$     | Maximum value of output power                            |

| $P_{S,max}$     | Peak power of source                                     |

| $P_{swi}$       | Total switching Losses                                   |

| $R_o$           | Output resistance                                        |

| $R_p$           | Parasitic resistance of PV panel                         |

| $R_{c1}$        | Effective resistance of BBC-1                            |

| $R_{c2}$        | Effective resistance of BBC-2                            |

| $R_{cx}$        | Effective resistance of BBC-x                            |

| $R_C$           | ESR of the capacitor $C$                                 |

|             |                                          |

|-------------|------------------------------------------|

| $R_D$       | ON state resistance of diode $D$         |

| $R_{S,ON}$  | ON state resistance of switch $S$        |

| $R_{SP,ON}$ | ON state resistance of switch $S_P$      |

| $T$         | Timeperiod of the output voltage         |

| $T_S$       | Time period of the inductor $L$ current  |

| $Tk$        | Duration of $k^{th}$ level               |

| $V_1$       | Source 1 voltage                         |

| $V_2$       | Source 2 voltage                         |

| $v_d$       | DC-link voltage                          |

| $V_o$       | RMS value of output voltage              |

| $V_x$       | Voltage magnitude of source x            |

| $v_{ar}$    | Pole a voltage                           |

| $v_{br}$    | Pole b voltage                           |

| $V_{c1}$    | Average voltage of capacitor $C_1$       |

| $v_{c1}$    | Instantaneous voltage of capacitor $C_1$ |

| $V_{c2}$    | Average voltage of capacitor $C_2$       |

| $v_{c2}$    | Instantaneous voltage of capacitor $C_2$ |

| $v_{CMV}$   | CMV of the MLI                           |

| $v_{cx}$    | Instantaneous voltage of capacitor $C_x$ |

| $V_c$       | Average voltage of capacitor $C$         |

| $V_D$       | Forward voltage drop of diode $D$        |

|              |                                               |

|--------------|-----------------------------------------------|

| $V_{IN}$     | Source voltage                                |

| $v_L$        | Instantaneous voltage across the inductor $L$ |

| $v_{mod}$    | Modulation voltage                            |

| $V_{o,peak}$ | Peak value of output voltage                  |

| $v_{o1}$     | Basic unit-1 output voltage                   |

| $v_{o2}$     | Basic unit-2 output voltage                   |

| $v_{ox}$     | Instantaneous output voltage of basic unit x  |

| $v_o$        | Instantaneous output voltage                  |

| $v_{ref}$    | Reference voltage                             |

| $v_{tri}$    | Carrier voltage                               |

| $x$          | Number of basic units cascaded                |

| AC           | Alternating current                           |

| asym         | symmetrical voltage sources                   |

| BBC          | Buck-boost converter                          |

| BCM          | Boundary conduction mode                      |

| BDIMLI       | boost DC-link integrated multilevel inverter  |

| CCM          | Continuous conduction mode                    |

| CMV          | Common mode voltage                           |

| Conv-1       | Basic unit-1                                  |

| Conv-2       | Basic unit-2                                  |

| CSDC         | Current Spikes During Charging                |

|         |                                                                  |

|---------|------------------------------------------------------------------|

| CVD     | Capacitor voltage drooping                                       |

| DBI     | Differential boost inverter                                      |

| DC      | Direct current                                                   |

| DCM     | Discrete conduction mode                                         |

| ESR     | Equivalent series resistance                                     |

| FLU     | Four level unit                                                  |

| IBDIMLI | improved boost DC-link integrated cascaded multilevel inverter   |

| ISBMLI  | Improved single-source buck-boost integrated multilevel inverter |

| LGC     | Level generation circuit                                         |

| MLI     | Multilevel inverter                                              |

| NLC     | Nearest level control                                            |

| PV      | Photovoltaic                                                     |

| QRSC    | Quasi-resonant switched capacitor                                |

| RMS     | Root mean square                                                 |

| SBMLI   | single-source buck-boost integrated multilevel inverter          |

| SC      | Switched capacitor                                               |

| SCMLI   | Switched capacitor multilevel inverter                           |

| SPWM    | Sinusoidal pulse width modulation                                |

| sym     | symmetrical voltage sources                                      |

| TBDC    | Two-level boost DC-link converters                               |

| TBDC-1  | Two-level boost DC-link converter-1                              |

TBDC-2 Two-level boost DC-link converter-2

THD Total harmonic distortion

TSV Total switch voltage

# **Chapter 1**

## **Introduction**

# Chapter 1

## Introduction

### 1.1 General introduction

The global trend of urbanization and population growth compelling every country towards more energy generation and handling of the consequences. Majority of the world's energy is generated from burning fossil fuels like coal, diesel and petrol [2]. Power generation from conventional sources is polluting air, water bodies and causing serious global warming issues. The prices of these sources are dependent on atmosphere and political factors hence, highly unpredictable. In recent times the awareness on environmental problems forcing every nation towards the increased use of renewable energy sources like solar, wind, geothermal and tidal etc. Out of these, wind and solar energy sources are available everywhere and occupied the majority of renewable energy generation [3, 4]. The overall installation and maintenance cost of the wind energy system is high compared to solar energy systems [3]. The Photovoltaic (PV) technology is extremely evolved and accessible to all starting from house roof-top generation to large power plants in rural, urban and remote locations. Hence, the PV based power generation is an attractive solution to electrify the remote locations, where the installation of transmission lines or transport of conventional fuels are expensive.

### 1.2 PV systems

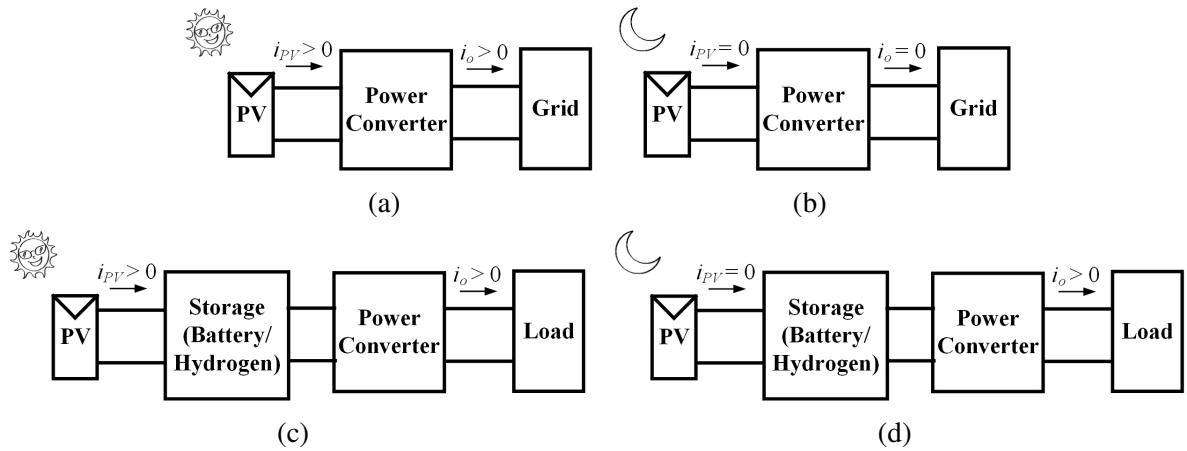

The PV power generation is highly variable and intermittent [5, 6] due to the dependence upon the climate conditions such as, irradiance of the sunlight, temperature and season etc., which results in unreliable power supply to the connected electrical loads. To harvest the maximum available energy from PV panels and also, to provide reliable power supply to the connected loads, there are two types [7, 8] of PV systems are in practice, namely

1. Grid connected PV systems

2. Off-grid PV systems

Figure 1.1: Block diagram of grid connected PV system during (a) the presence of sunlight (b) the absence of sunlight; and off-grid PV system during (c) the presence of sunlight (d) the absence of sunlight

Figure 1.2: Different grid connected PV configurations.

The block diagrams of grid connected and off-grid PV systems are depicted in Figure 1.1, during the presence and absence of sunlight.

### 1.2.1 Grid connected PV systems

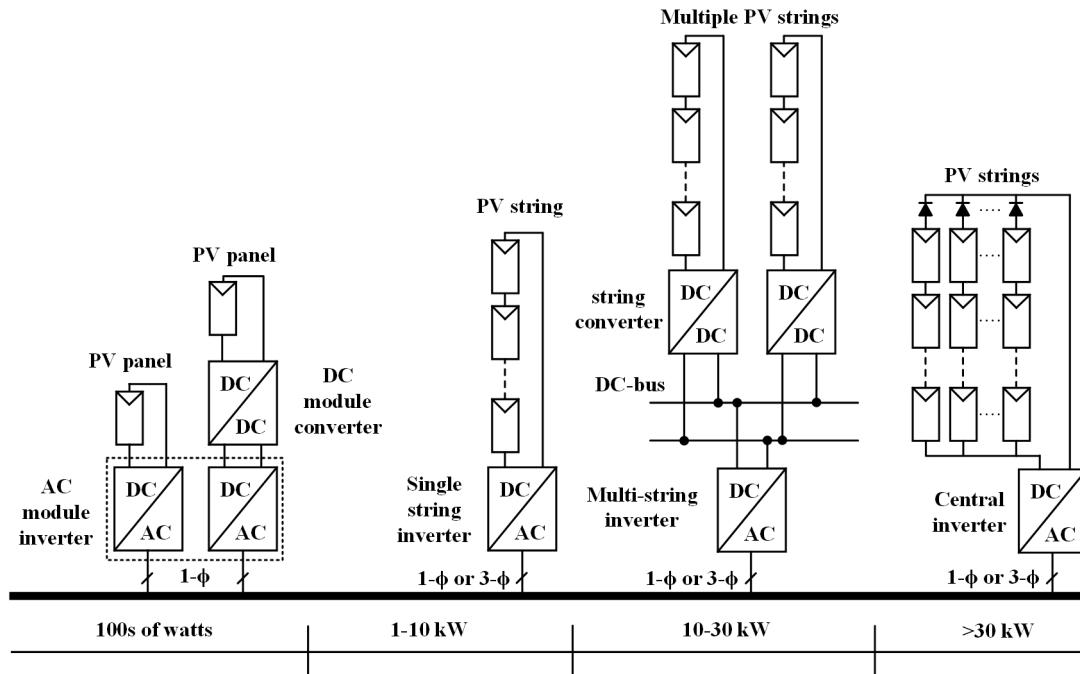

The grid connected operation of the PV shown in Figures 1.1a and 1.1b will improve the reliability and harvest the maximum energy from the PV panels to the grid. The operating power range of grid connected PV systems can be varied from hundreds of watts to tens of kilo-watts and the different grid connected PV configurations [9] are shown in Figure 1.2. They are broadly classified as central inverters, multi-string inverters [10, 11], single string inverters [12, 13] and module inverters [14–17]. The central and multi-string PV systems are used to process the PV energy at a large scale in industrial and PV power-plant applications. The single string and module structures are widely used for commercial and residential roof top applications. The partial shading conditions of PV array will affect the maximum power to be extracted in central and string based inverters. In contrast to the string inverters, the module inverters are immune to partial shading issues and provide high modularity, thus provides scope for further research.

### 1.2.2 Off-grid PV systems

The power generation from conventional energy sources is difficult and non-economical in remote locations such as rural, forest and islands with no grid facility [3,4]. Hence, the power generation from PV is a cost effective alternative and also, helps to preserve the sensitive eco system of the remote places. However, the absence of the grid and intermittent nature of the PV source affects the reliability of the power supply to the connected electrical appliances. To address this issue, PV with storage elements such as battery and hydrogen gas can be used to improve the reliability as shown in Figures 1.1c and 1.1d. The stored hydrogen gas can be converted to electrical energy by using fuel cell and power electronic converter. The surplus power from PV source will be stored in the storage devices and the stored energy will be delivered to the loads when power from PV is either absent or insufficient. Usually, the terminal voltage of PV, batteries and fuel cells are at low magnitude and the majority of the loads operates at high magnitude AC (alternate current) voltages. As the power rating of the off-grid PV systems are less than 1 kW, the module converters are the key structure to provide modularity and efficient conversion [18–20]. Hence, a high gain inverter is essential to convert low voltage DC (either from PV or from battery or fuel cell) to high voltage AC and the block diagram of inverters for

Figure 1.3: Block diagram of inverter for renewable applications.

renewable PV applications is depicted in Figure 1.3.

### 1.3 Single phase step-up inverters

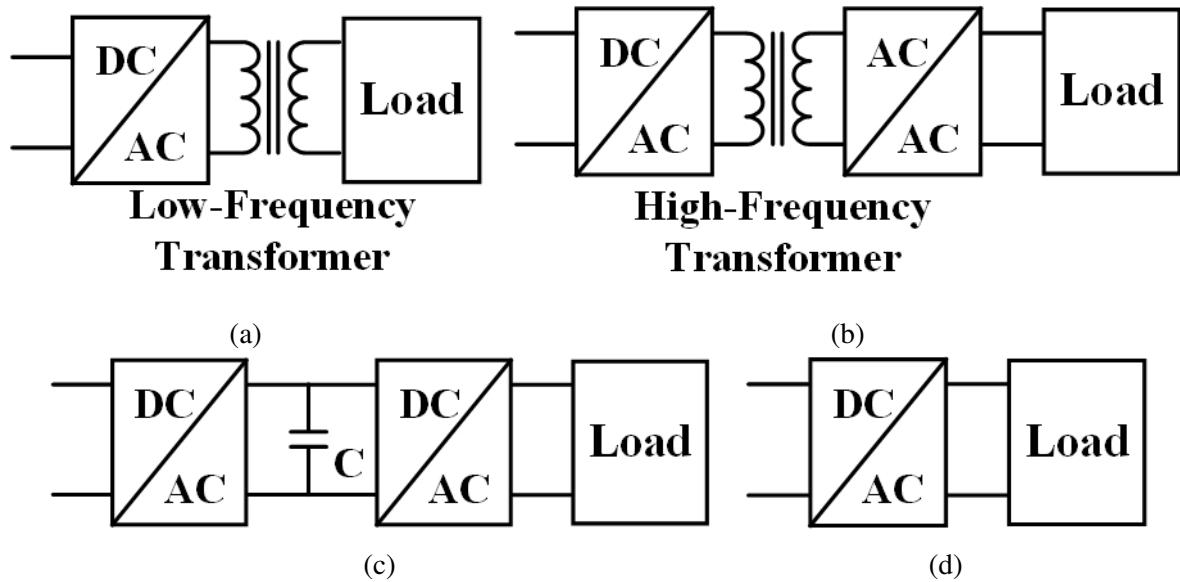

The voltage step-up can be achieved by using various techniques such as, step-up transformer and front DC-DC converters etc. Based on the usage of transformer, the step-up inverters used for PV applications can be categorized as follows [20–25] and the respective block diagrams are depicted in Figure 1.4.

1. Step-up inverters with transformer

- (a) Step-up inverter with low or power frequency transformer

- (b) Step-up inverter with high frequency transformer

2. Step-up inverters without transformer

- (a) Two-stage transformerless step-up inverters

- (b) Single-stage transformerless step-up inverters

Figure 1.4: Block diagram of single phase step-up inverters: (a) with low-frequency transformer (b) with high-frequency transformer (c) two-stage transformerless (d) single-stage transformerless

### 1.3.1 Step-up inverters with transformer

The step-up inverters with transformer utilize a step-up transformer to step up the voltage and the transformer can be either low-frequency or high-frequency.

#### 1.3.1.1 Step-up inverters with line-frequency transformer

The block diagram of the step-up inverter with line-frequency transformer is depicted in Figure 1.4a. Here, the inverter converts the low-magnitude DC voltage into low-magnitude low-frequency AC and then the step-up transformer will convert the low-magnitude low-frequency AC into high-magnitude low-frequency AC. With simple operation, it provides required voltage gain and galvanic isolation, however it requires a bulky line frequency transformer which results in increased cost and volume of the inverter.

#### 1.3.1.2 Step-up inverters with high-frequency transformer

The block diagram of the step-up inverter with high-frequency transformer [26–35] is depicted in Figure 1.4b. Here, the inverter in the first stage converts the low-magnitude DC voltage into low-magnitude high-frequency AC and then the high frequency step-up transformer will

converts the low-magnitude high-frequency AC into high-magnitude high-frequency AC. The second stage converter converts high-magnitude high-frequency AC in to high-magnitude low-frequency AC. Though, the inverter process the energy in multiple stages, the utilization of high frequency transformer relatively reduces the cost and volume of the inverter compared to the inverter with low frequency transformer.

For low power applications, the percentage core losses of transformers presented in step-up inverters with transformer are relatively high, which results in reduced overall efficiency.

### 1.3.2 Step-up inverters without transformer

The step-up inverters without transformer, use a non isolated boost network to achieve required voltage gain. Based on the number of power conversion stages, which are further classified as two stage and single-stage transformerless inverters.

#### 1.3.2.1 Two stage transformer less inverter

The block diagram of the two stage transformerless inverter [36–39] is depicted in Figure 1.4c. The first stage of this inverter converts the low-magnitude DC voltage into high-magnitude DC and second stage converts the high-magnitude DC into high-magnitude low-frequency AC. The operation of this inverter is simple, however the front end DC-DC converter has to process the rated power. Hence, the cascade operation of two converters decreases the overall efficiency.

#### 1.3.2.2 Single stage transformer less inverter

The block diagram of the single stage transformerless inverter [21, 40–45] is depicted in Figure 1.4d. The inverter directly converts the low-magnitude DC voltage into high-magnitude low-frequency AC in single stage. Thus, results in improved efficiency compared to the two stage transformerless inverters.

In summary, the transformerless step-up inverters do not provide galvanic isolation, however they provide better efficiency, reduced cost and size compared to the step-up inverters with transformer [20]. Thus, the research is mainly focused on transformerless step-up inverters for PV stand alone applications.

## **Chapter 2**

# **Literature Review on Single-phase Transformerless Inverters**

# Chapter 2

## Literature Review on Single-phase Transformerless Inverters

### 2.1 Introduction

This chapter presents a comprehensive review of various single-phase transformerless step-up inverters suitable for PV standalone applications. The output voltage of PV panel, fuel-cell and battery are of low magnitude DC voltage (less than 60 V). Usually, the majority loads work with high magnitude AC voltage (110 V/60 Hz or 230 V/50 Hz). To transfer the energy from the low voltage DC sources to the loads operating at high voltage AC, the inverter should possess the following features

- High Voltage gain

- Compactness

- Low output voltage THD (Total harmonic distortion)

- Efficient conversion

- Low cost

### 2.2 Two-level inverter with front-end boost converter

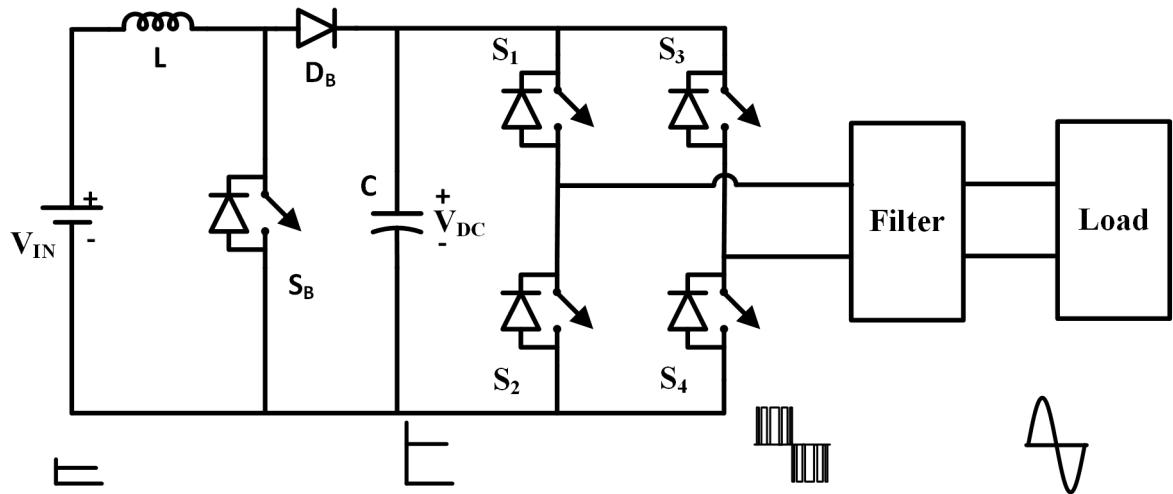

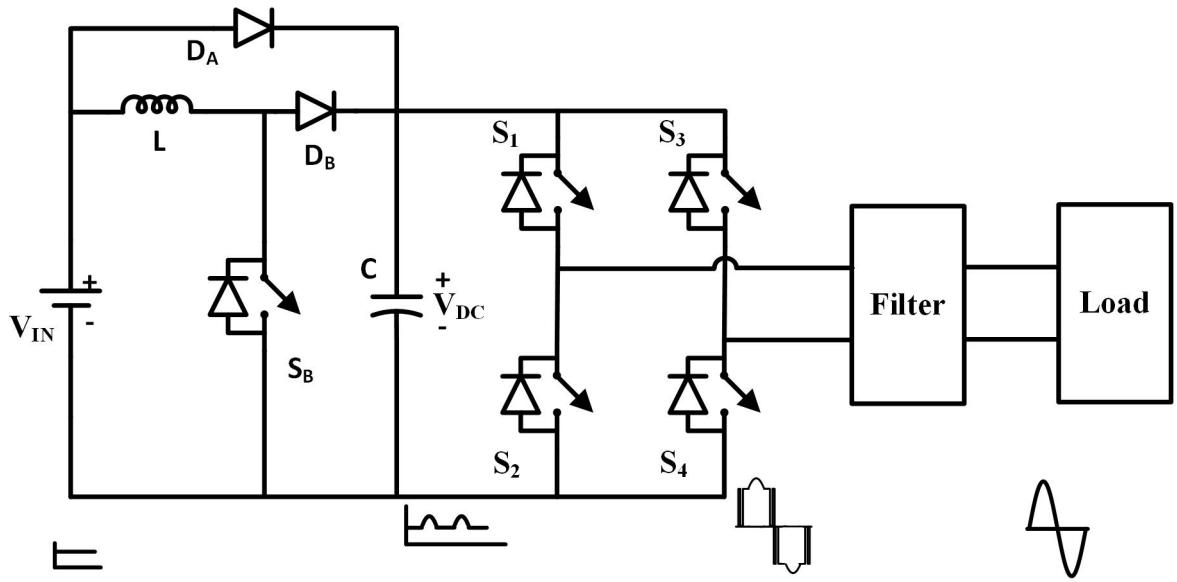

The circuit diagram of the two stage two-level step-up inverter with front-end boost converter [46–49] is depicted in Figure 2.1. The front-end boost converter increases the DC voltage magnitude and the second stage H-bridge network converts the high-magnitude DC into high-magnitude low-frequency AC. The front-end boost converter needs to process the rated power and a bulk capacitor is required to maintain a stiff DC-link voltage. The H-bridge inverter presented in the second stage produce two-level output, which result in high output voltage THD. Hence, requires a large filter to suppress the harmonic content of the inverter

Figure 2.1: Circuit diagram of two stage two-level step-up inverter with front-end boost converter