# **Design and Analysis of Modified GAA Nanosheet FET Based Circuits for High Frequency Applications**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**Doctor of Philosophy**

by

**N. Aruna Kumari**

(Roll No. 720060)

Supervisor

**Dr. P. Prithvi**

Assistant Professor, Dept. of ECE

**Department of Electronics & Communication Engineering**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL – 506004, T.S, INDIA**

**December-2022**

## APPROVAL SHEET

This thesis entitled "**Design and Analysis of Modified GAA Nanosheet FET Based Circuits for High Frequency Applications**" by **Ms N. Aruna Kumari** is approved for the degree of **Doctor of Philosophy**.

### Examiners

---

---

### Supervisor

---

**Dr. P. Prithvi**

Assistant Professor, Electronics and Communication Engineering Department,

NIT WARANGAL

### Chairman

---

**Prof. P. Sreehari Rao**

Head, Electronics and Communication Engineering Department,

NIT WARANGAL

**Date:**

**Place:**

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Design and Analysis of Modified GAA Nanosheet FET Based Circuits for High Frequency Applications**" is a bonafide work done by me under the supervision of **Dr. P. Prithvi**, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**N. Aruna Kumari**

**Roll No: 720060**

**Date:**

**Place: Warangal**

**Department of Electronics and Communication Engineering

National Institute of Technology

Warangal – 506 004, Telangana, India**

**CERTIFICATE**

This is to certify that the dissertation work entitled "**Design and Analysis of Modified GAA Nanosheet FET Based Circuits for High Frequency Applications**", which is being submitted by Ms. N. Aruna Kumari (Roll No.720060), is a bonafide work submitted to National Institute of Technology Warangal in partial fulfilment of the requirement for the award of the degree of **Doctor of Philosophy in Electronics and Communication Engineering**.

To the best of our knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. P. Prithvi**

Supervisor

Department of ECE

National Institute of Technology

Warangal – 506004

**Dedicated to My

Parents, Gurus, & Friends**

# CONTENTS

|                                                                                                                         |             |

|-------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>Abstract.....</b>                                                                                                    | <b>viii</b> |

| <b>List of Figures.....</b>                                                                                             | <b>x</b>    |

| <b>List of Tables .....</b>                                                                                             | <b>xv</b>   |

| <b>Nomenclature.....</b>                                                                                                | <b>xvi</b>  |

| <b><u>1</u> <u>Introduction</u>.....</b>                                                                                | <b>1</b>    |

| 1.1    Introduction .....                                                                                               | 1           |

| 1.2    CMOS Technology Scaling .....                                                                                    | 4           |

| 1.3    Conventional MOSFET.....                                                                                         | 6           |

| 1.4    Short Channel Efects.....                                                                                        | 7           |

| 1.5    Multigate Architectures.....                                                                                     | 15          |

| 1.6    Motivation .....                                                                                                 | 17          |

| 1.7    Novelty of Overall Proposed Work .....                                                                           | 17          |

| 1.8    Device Simulation.....                                                                                           | 18          |

| 1.9    Workflow .....                                                                                                   | 19          |

| 1.10    Research Specifications .....                                                                                   | 20          |

| 1.11    Research Objectives.....                                                                                        | 21          |

| 1.12    Thesis organization.....                                                                                        | 21          |

| <b><u>2</u> <u>Literature Review</u>.....</b>                                                                           | <b>22</b>   |

| 2.1    Literature Survey.....                                                                                           | 25          |

| 2.2    Research Gaps Identified .....                                                                                   | 30          |

| 2.3    Conclusion.....                                                                                                  | 30          |

| <b><u>3</u> <u>Performance Evaluation of GAA Nanosheet FET with Varied Geometrical and Process Parameters</u> .....</b> | <b>31</b>   |

| 3.1    Introduction .....                                                                                               | 31          |

| 3.2    Device Structure and Simulation Framework .....                                                                  | 32          |

| 3.3    Results and Conclusions .....                                                                                    | 35          |

| 3.3.1    Impact on DC Performance of NSFET with Geometric Variations .....                                              | 35          |

| 3.3.2    Impact on DC Performance of NSFET with Scaling .....                                                           | 38          |

|          |                                                                                                                      |           |

|----------|----------------------------------------------------------------------------------------------------------------------|-----------|

| 3.3.3    | Impact of Temperature and workfunction variations on NSFET .....                                                     | 40        |

| 3.4      | Conclusions .....                                                                                                    | 44        |

| <b>4</b> | <b>Device and Circuit-Level Performance Comparison of GAA Nanosheet FET With Varied Geometrical Parameters .....</b> | <b>45</b> |

| 4.1      | Introduction .....                                                                                                   | 45        |

| 4.2      | Device structure and Simulation Methodology .....                                                                    | 46        |

| 4.3      | Results and Conclusions.....                                                                                         | 47        |

| 4.3.1.   | Geometry Dependence on DC Metrics of NSFET .....                                                                     | 47        |

| 4.3.2.   | Geometry Influence on Analog/RF Response of GAA NSFET .....                                                          | 51        |

| 4.3.3.   | Geometry Influence on Circuit Applications of GAA NSFET .....                                                        | 59        |

| 4.4      | Conclusion.....                                                                                                      | 64        |

| <b>5</b> | <b>Temperature Assessment of Nanosheet FET for CMOS Circuit Applications .....</b>                                   | <b>65</b> |

| 5.1      | Introduction .....                                                                                                   | 65        |

| 5.2      | Device structure and Simulation Methodology .....                                                                    | 65        |

| 5.3      | Result and Discussions.....                                                                                          | 66        |

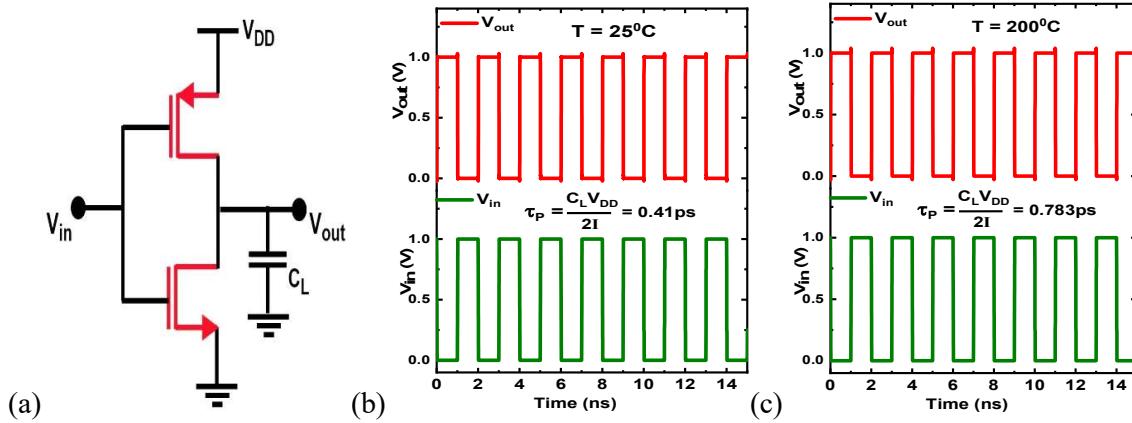

| 5.3.1    | Impact of Temperature on DC and analg/RF Metrics of NSFET.....                                                       | 66        |

| 5.3.2    | Impact of Temperature on Circuit Applications.....                                                                   | 71        |

| 5.4      | Conclusion.....                                                                                                      | 74        |

| <b>6</b> | <b>A Comprehensive Analysis and Performance Comparison of CombFET and NSFET for CMOS Circuit Applications .....</b>  | <b>75</b> |

| 6.1      | Introduction .....                                                                                                   | 75        |

| 6.2      | Device structure and Simulation Parameters.....                                                                      | 75        |

| 6.3      | Results and Conclusions.....                                                                                         | 77        |

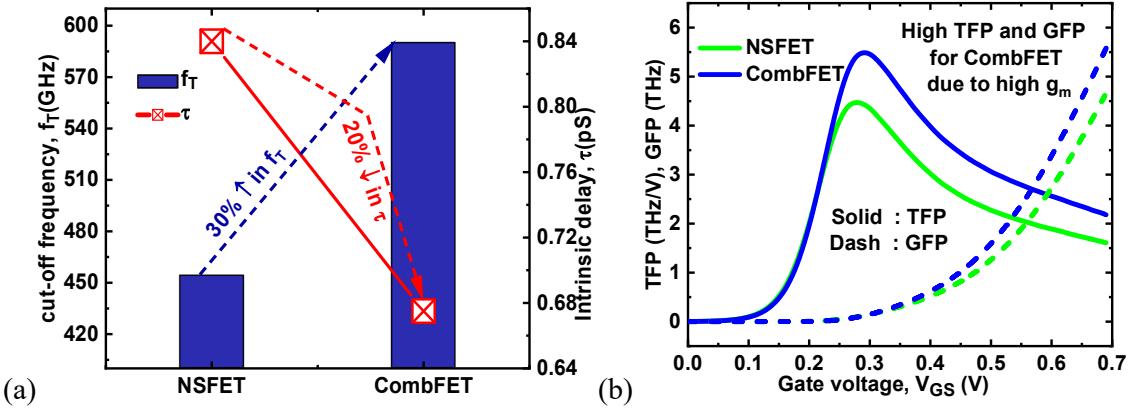

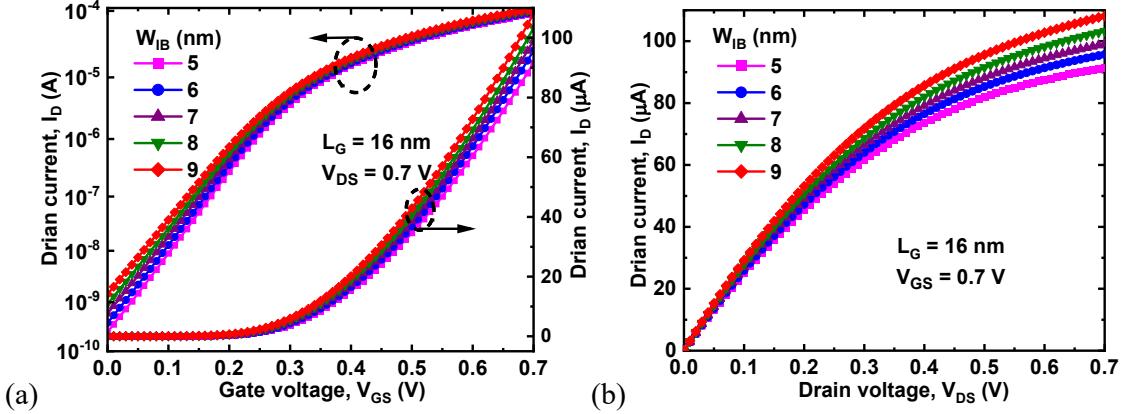

| 6.3.1    | DC and analog/RF FOMs Analysis of both NSFET and CombFET .....                                                       | 77        |

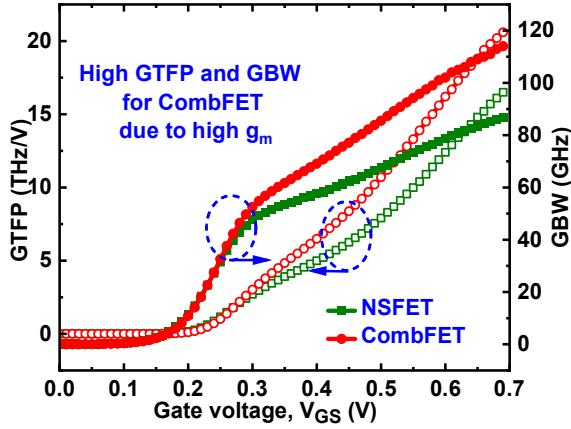

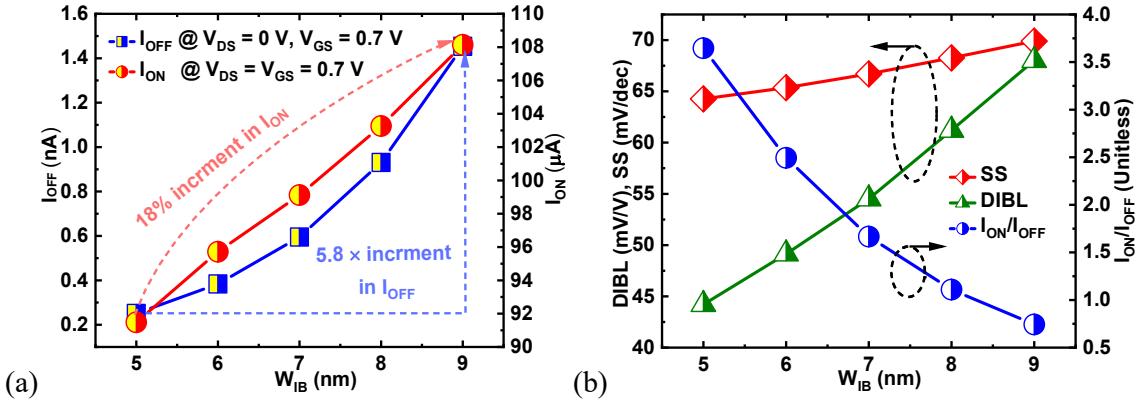

| 6.3.2    | Impact of Interbridge Width ( $W_{IB}$ ) on the Performance of CombFET .....                                         | 82        |

| 6.3.3    | Impact of Interbridge Height ( $H_{IB}$ ) on the Performance of CombFET .....                                        | 83        |

| 6.3.4    | Performance Comparison of NSFET and CombFET for Circuit Applications.....                                            | 85        |

| 6.4      | Conclusion.....                                                                                                      | 88        |

|                                                                 |            |

|-----------------------------------------------------------------|------------|

| <b>7_Results, Conclusions and Future Scope of the Work.....</b> | <b>89</b>  |

| 7.1    Results and Overall Conclusions.....                     | 89         |

| 7.2    Future Scope of the Work .....                           | 91         |

| <b>Appendix A .....</b>                                         | <b>92</b>  |

| Visual TCAD Input File for Nanosheet FET.....                   | 92         |

| Visual TCAD Input File for CombFET .....                        | 96         |

| Look-up Table Based Verilog-A Code .....                        | 102        |

| <b>List of Publications.....</b>                                | <b>104</b> |

| <b>Acknowledgements.....</b>                                    | <b>105</b> |

| <b>Bibliography .....</b>                                       | <b>107</b> |

## ABSTRACT

Semiconductor devices transformed the human lives from the past few decades. The major technological breakthrough in semiconductor devices is the invention of Complementary Metal Oxide Semiconductor (CMOS) technology. Also, the heart of CMOS technology is Metal Oxide Semiconductor Field Effect Transistor (MOSFET). CMOS scaling is the driving mechanism for technological applications. However, in addition to the advantages, disadvantageous short channel effects (SCEs) also came into the picture with scaling. Thus, to get around the CMOS scaling limitations, some possible alternatives, such as multigate semiconductor devices are proposed. The multi-gate (MuG) based MOSFETs play a significant role in downscaling the MOSFET dimension, allowing for better control over the device carriers. Moreover, to enhance gate's electrostatic integrity and to achieve the SS close to the Boltzmann tyranny of 60 mV/decade, multi-gate (MuG) architectures such as double gate, trigate, Fin-shaped FET (FinFET), gate-all-around (GAA) nanowires (NW), and nanosheets (NS) can be used. The GAA nanosheet FET (NSFET) is proven to be a potential candidate to continue the scaling for sub-5-nm nodes.

In GAA NSFETs, the gate surrounds the channel in all directions. Wrapping the channel on all sides by the gate leads to greater gate control, lower power, minimized drain effect on channel electrostatics and reduced leakage in GAA NS transistors. For the same physical channel area as a FinFET, the GAA channel reduces SCEs and improves the effective area of the channel and hence boosting the drive current. Thus reduced SCEs with GAA FETs drive towards optimal performance and ensures continued scaling for future technology nodes. Increasing the number of stacked nanosheets is a viable option to increase the drive current. However, as the number of nanosheets increases, the parasitic capacitances also increase, which increases the delay of the device.

Therefore, in this thesis, the NSFET with two vertically stacked nanosheets is designed. Moreover, the geometry of the nanosheet plays a crucial role in the device's performance. Thus, it is highly essential to analyse the performance at different geometry of the nanosheet. Though some works addressed the geometrical impact at the device level, the geometry impact at high frequency circuit applications needs to be explored. The influence of geometry on DC metrics, Analog/RF metrics and circuit applications is analysed in detail by varying the geometry of the nanosheet.

Further, semiconductor devices are very much sensitive to variations in temperature. The impact of temperature on the multigate FETs is addressed by some researchers. However, none has addressed the impact of temperature on NSFET in high frequency circuit applications. Thus, in this work, the impact of temperature at both device and circuit levels is analysed for NSFET based high frequency circuit applications.

To continue the scaling, the effective area ( $W_{eff}$ ) per footprint (FP) ( $W_{eff}/FP$ ), needs to be reduced, which affects the performance of the device with scaling. Thus, it is essential to improve the on current without increasing the FP by using device engineering such as structural engineering and high- $k$  gate stack engineering. Thus, to increase the  $W_{eff}$  under the same FP, the Fin-like interbridge is combined with nanosheets to form Comb-like-channel structure along with high- $k$  gate stack is proposed. The proposed structure enhances the on current and switching ratios of the device significantly. Moreover, the device's behaviour in circuit applications such as ring oscillators is addressed and compared with traditional NSFET under the same FP. The analysis reveals that by using the proposed device, the performance of the device can be increased and is capable of scaling for sub-5-nm nodes.

## LIST OF FIGURES

|                                                                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.1. Showing the number of transistors per integrated circuit for various process technology nodes from the year of invention of transistor by intel microprocessor ..... | 2  |

| Fig. 1.2. (a) Various power consumption, (b) gate length scaling with respect to time .....                                                                                    | 5  |

| Fig. 1.3. Schematic view of conventional metal oxide semiconductor field effect transistor (MOSFET) .....                                                                      | 6  |

| Fig. 1.4. The effect of DIBL on (a) Long channel (b) Short channel MOSFET.....                                                                                                 | 7  |

| Fig. 1.5. Channel length modulation illustration in MOSFET.....                                                                                                                | 8  |

| Fig. 1.6. Leakage current through gate oxide in MOSFET.....                                                                                                                    | 9  |

| Fig. 1.7. Velocity saturation in MOSFET.....                                                                                                                                   | 10 |

| Fig. 1.8. Surface scattering effect in MOSFET.....                                                                                                                             | 11 |

| Fig. 1.9. (a) The GIDL effect in the MOSFET (b) Electron tunneling phenomena by GIDL effect.....                                                                               | 11 |

| Fig. 1.10. Ballistic transport mechanism in the MOSFET.....                                                                                                                    | 12 |

| Fig. 1.11. Various leakage current mechanisms in the MOSFET MOSFET.....                                                                                                        | 13 |

| Fig. 1.12. Schematic of hot carrier effect of MOSFET.....                                                                                                                      | 14 |

| Fig. 1.13. Effect of the punch through in the MOSFET.....                                                                                                                      | 14 |

| Fig. 1.14. Various Multigate FET architectures .....                                                                                                                           | 15 |

| Fig. 1.15. GAA Nanosheet FET.....                                                                                                                                              | 16 |

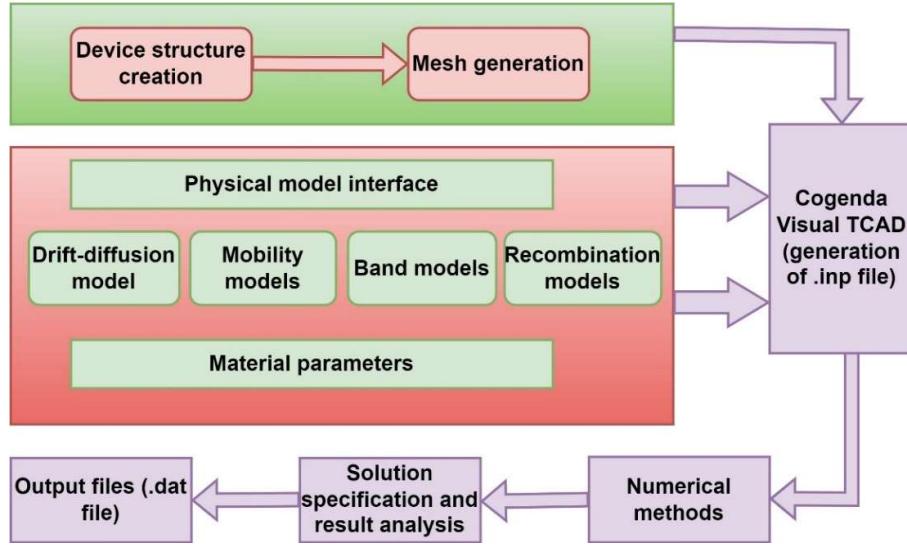

| Fig. 1.16. Simulation process from device generation to outputs extraction.....                                                                                                | 19 |

| Fig. 1.17. Workflow along with contributions (C1-C4).....                                                                                                                      | 20 |

| Fig. 2.1. (a) OFF state leakage current (b) Intrinsic delay (c) Power dissipation.....                                                                                         | 23 |

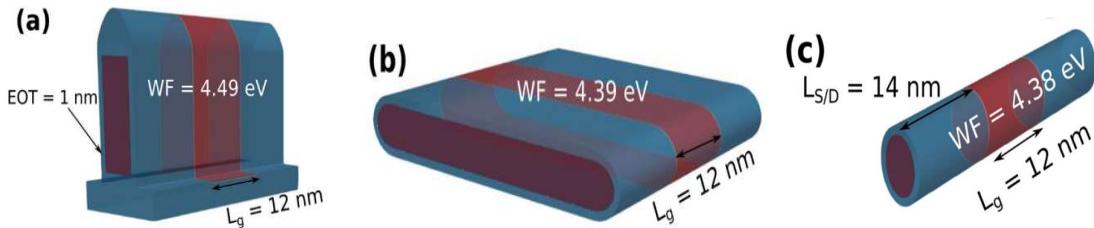

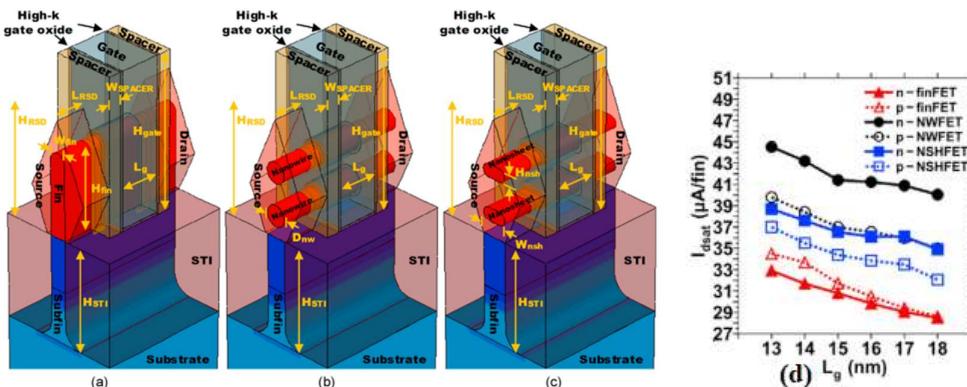

| Fig. 2.2. Device structures of (a) FinFET, (b) GAA NSFET and (c) GAA NWFET .....                                                                                               | 23 |

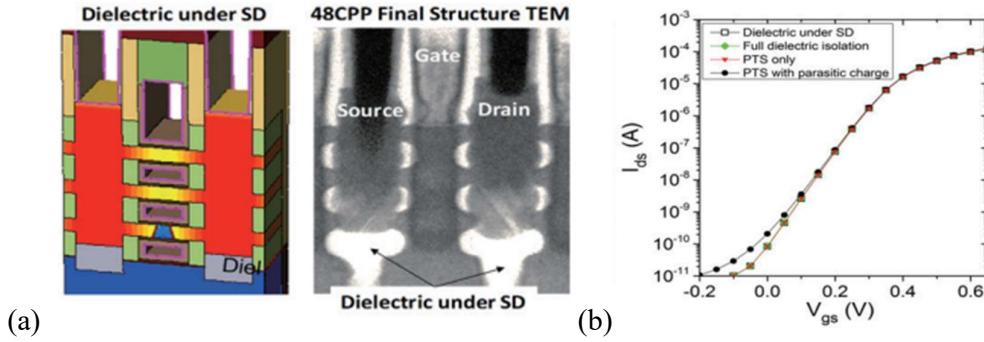

| Fig. 2.3. Device structures of (a) NSFET and its TEM image (b) transfer characteristics of NSFET .....                                                                         | 24 |

| Fig. 2.4. Simulated structures of (a) FinFET (b) GAA NSFET (c) GAA NWFET (d) drain current ( $I_{dsat}$ ).....                                                                 | 24 |

|                                                                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

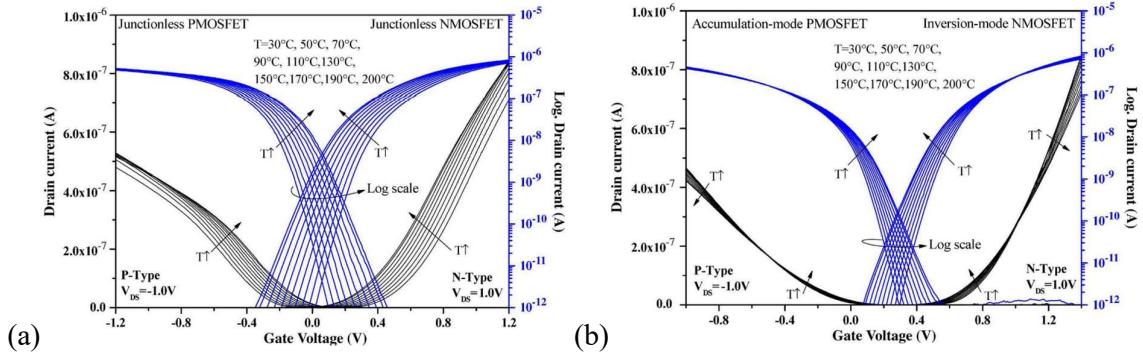

| Fig. 2.5. Simulated $I_D$ - $V_{GS}$ characteristics of NW FET with (a) JL mode (b) accumulation and inversion mode at elevated temperatures.....                                      | 25 |

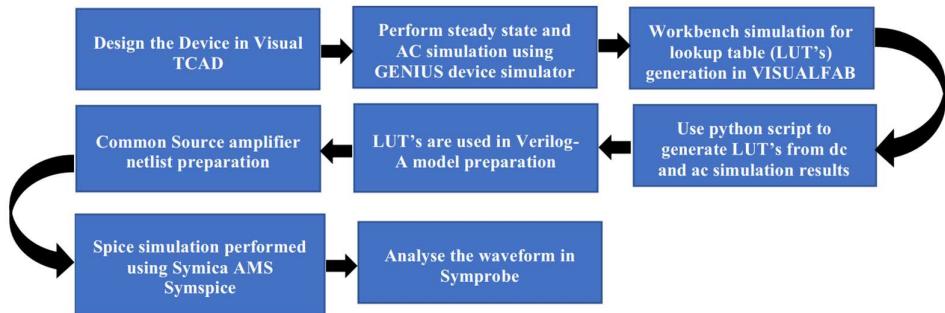

| Fig. 2.6. Flowchart of the process followed to design the circuit using look up table-based Verilog-A model .....                                                                      | 26 |

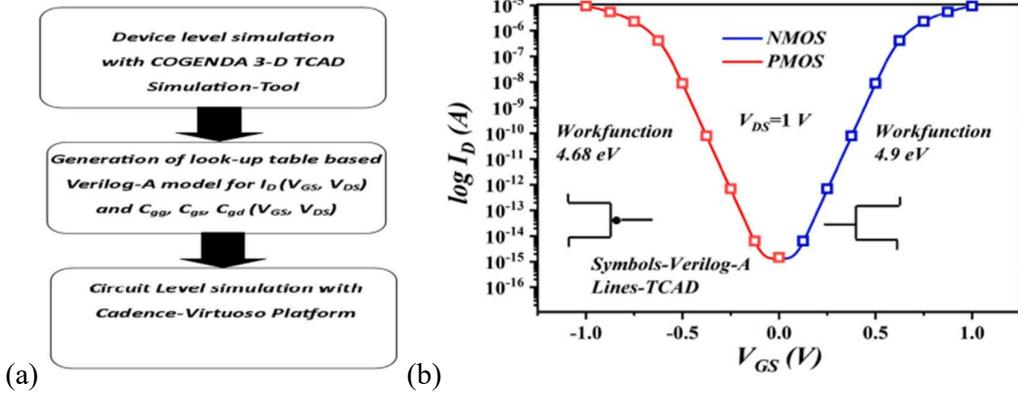

| Fig. 2.7. (a) Process flow from TCAD to circuit simulations and (b) Verilog-A model calibration with TCAD .....                                                                        | 27 |

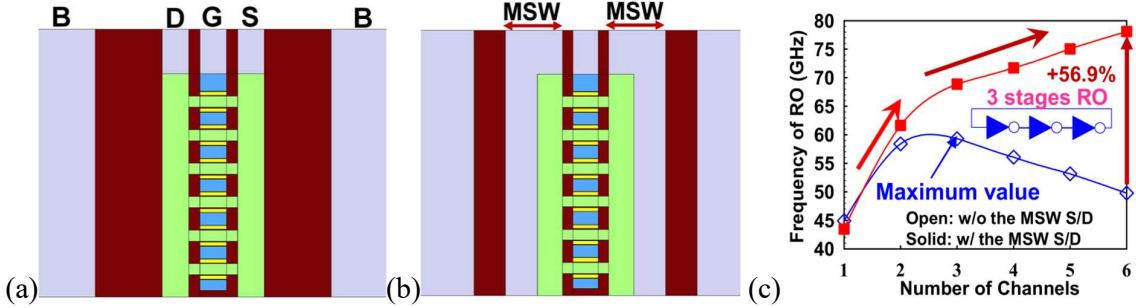

| Fig. 2.8. Nanosheet FET (a) without MSW contact (b) with MSW contact and (c) variations in the frequency of oscillations as a function of the number of channels .....                 | 28 |

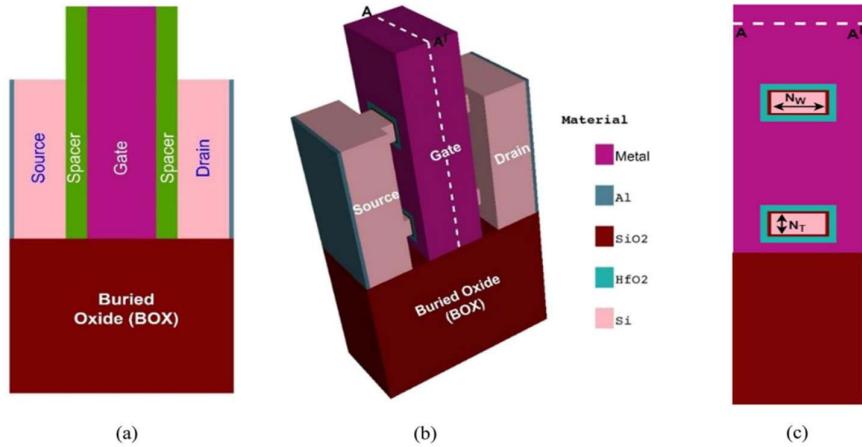

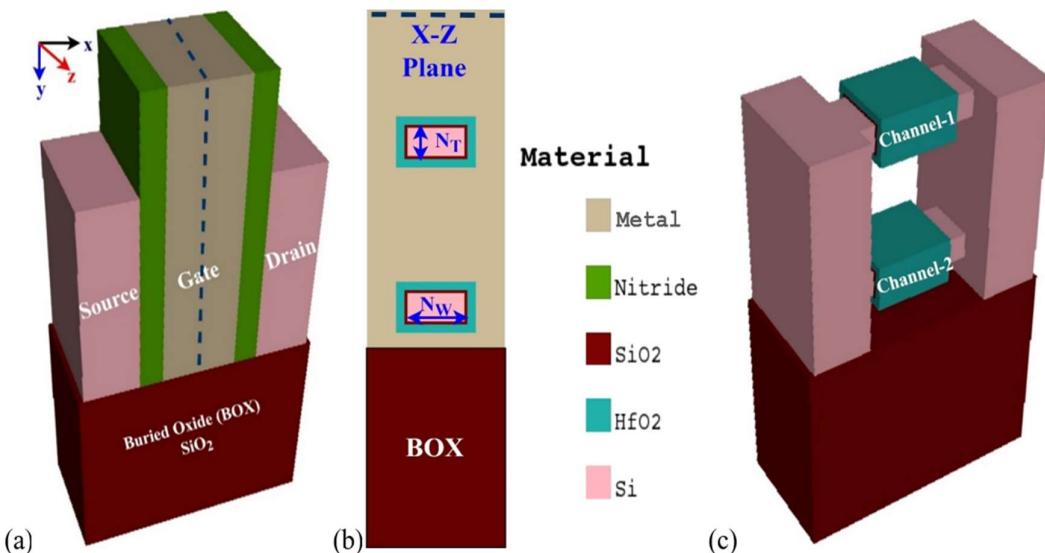

| Fig. 3.1. (a) 2-D view of NSFET with nitride spacer, (b) 3-D schematic view of NSFET and (c) 2-D cross sectional view of NSFET.....                                                    | 33 |

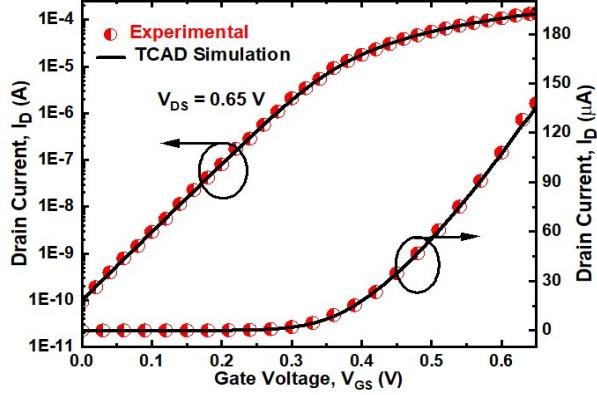

| Fig. 3.2. Calibration of simulation models with that of experimental results .....                                                                                                     | 34 |

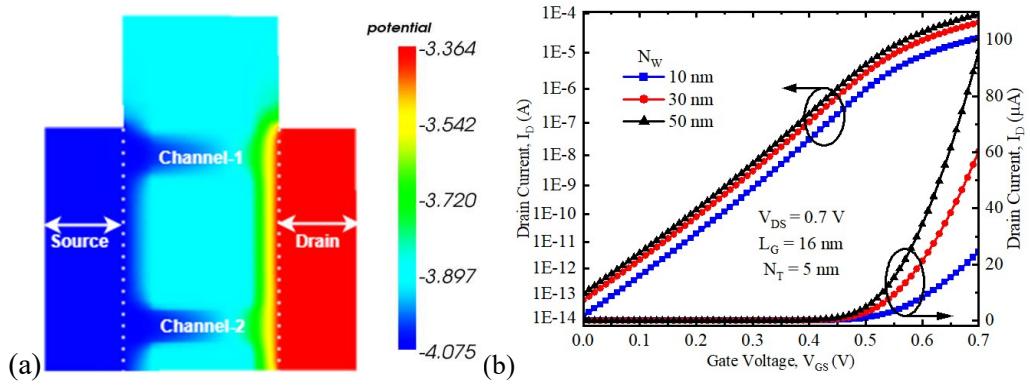

| Fig. 3.3. (a) Contour plot of the potential distribution of NSFET in ON state (b) Transfer characteristics of NSFET in linear and log scale for $V_{DS} = 0.7$ V .....                 | 35 |

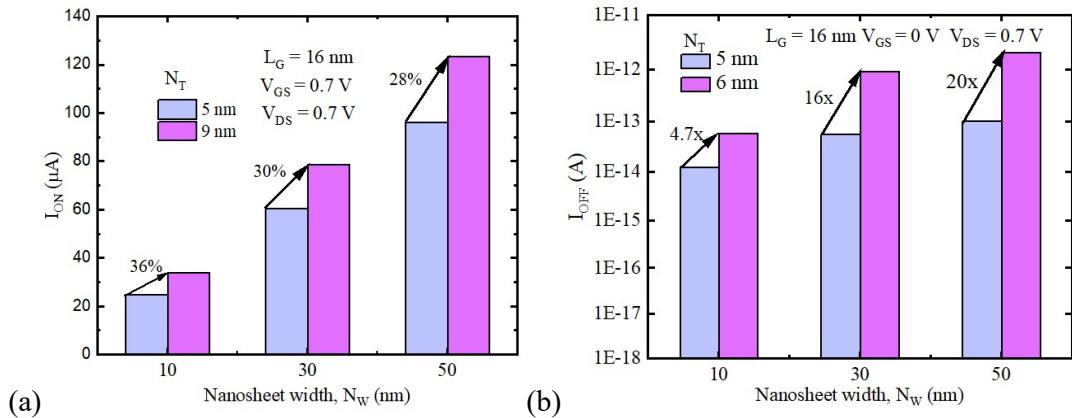

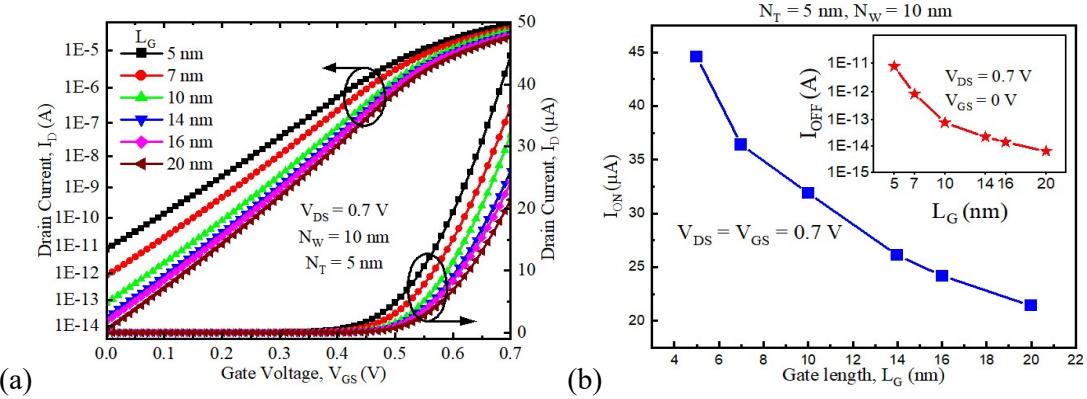

| Fig. 3.4. (a) $I_{ON}$ and (b) $I_{OFF}$ as a function of $N_w$ for various $N_T$ values .....                                                                                         | 35 |

| Fig. 3.5. (a) $I_{ON}/I_{OFF}$ and SS (b) DIBL and $V_{th}$ as a function of $N_w$ for various $N_T$ values .....                                                                      | 36 |

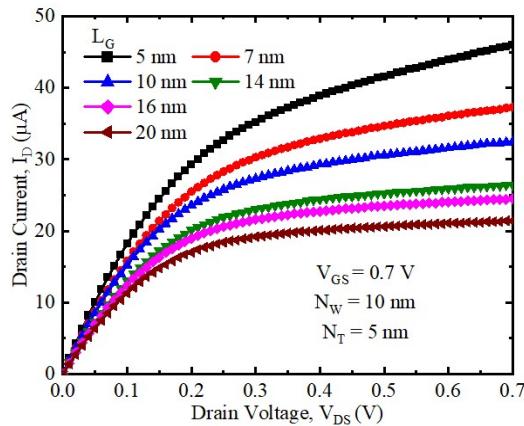

| Fig. 3.6. Output characteristics for various $N_w$ values as a function of drain voltage .....                                                                                         | 38 |

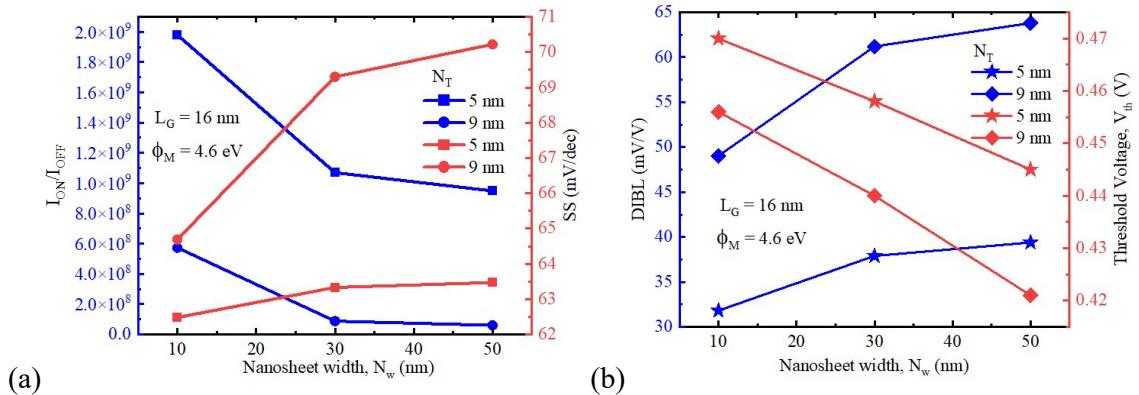

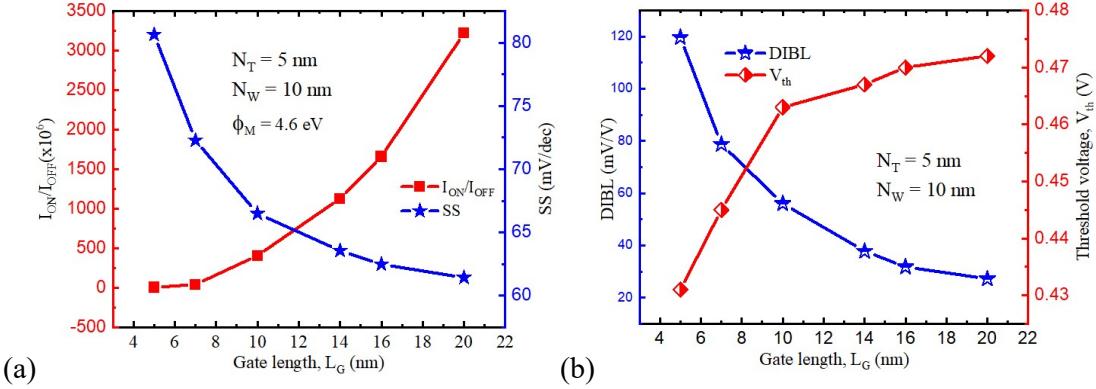

| Fig. 3.7. Transfer characteristics for various $L_G$ values and (b) $I_{ON}$ and $I_{OFF}$ (inset) as a function of $L_G$ .....                                                        | 38 |

| Fig. 3.8. (a) $I_{ON}/I_{OFF}$ and SS (b) DIBL and $V_{th}$ as a function of $L_G$ .....                                                                                               | 39 |

| Fig. 3.9. Output characteristics for various $L_G$ values as a function of drain voltage .....                                                                                         | 40 |

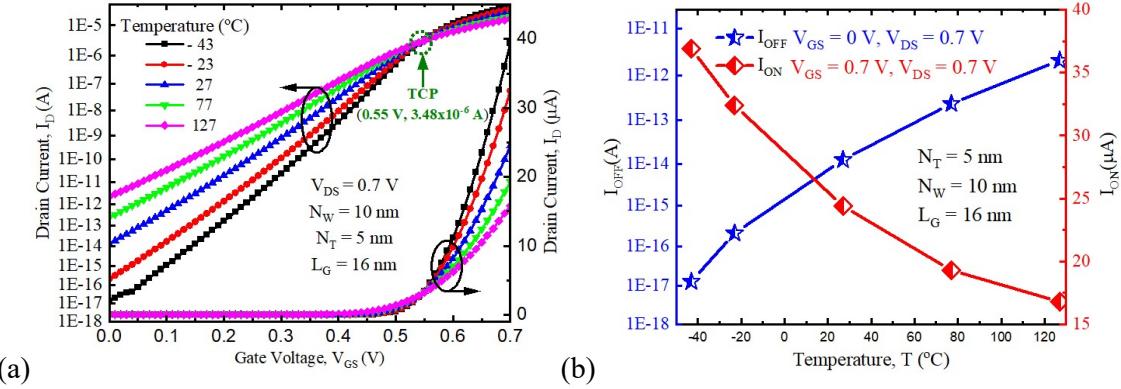

| Fig. 3.10. (a) Temperature variations (b) $I_{ON}$ and $I_{OFF}$ variations as a function of $V_{GS}$ .....                                                                            | 40 |

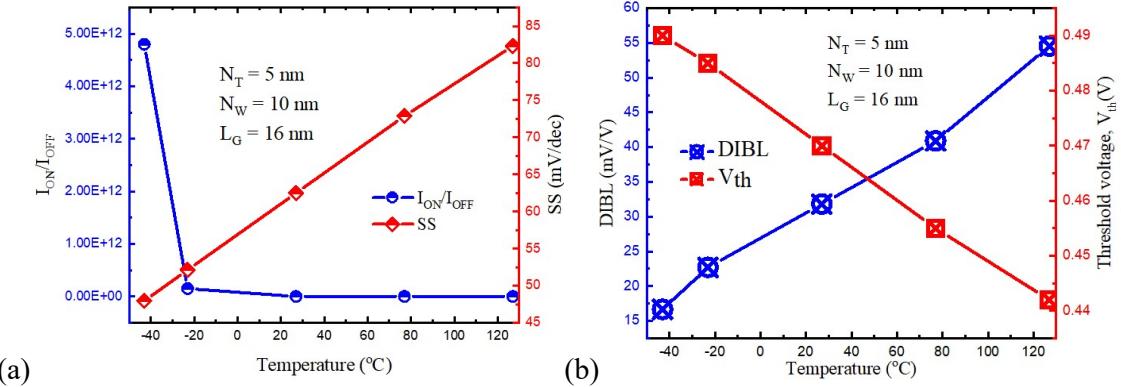

| Fig. 3.11. (a) $I_{ON}/I_{OFF}$ and SS (b) DIBL and $V_{th}$ variations as a function of temperature .....                                                                             | 41 |

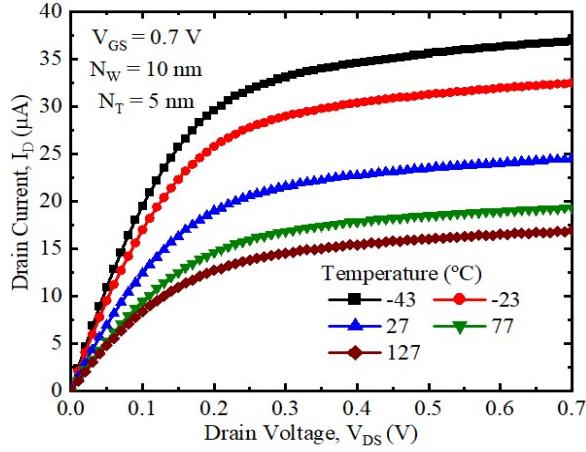

| Fig. 3.12. Output characteristics for various temperature values as a function of drain voltage .....                                                                                  | 41 |

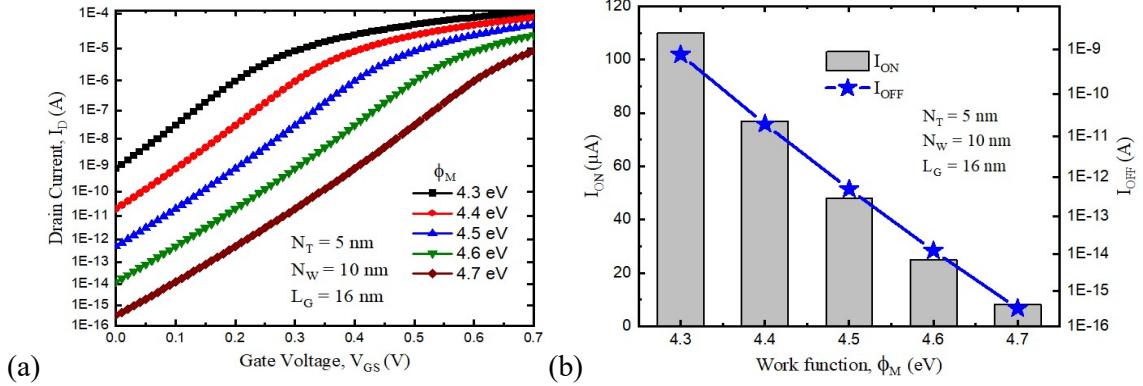

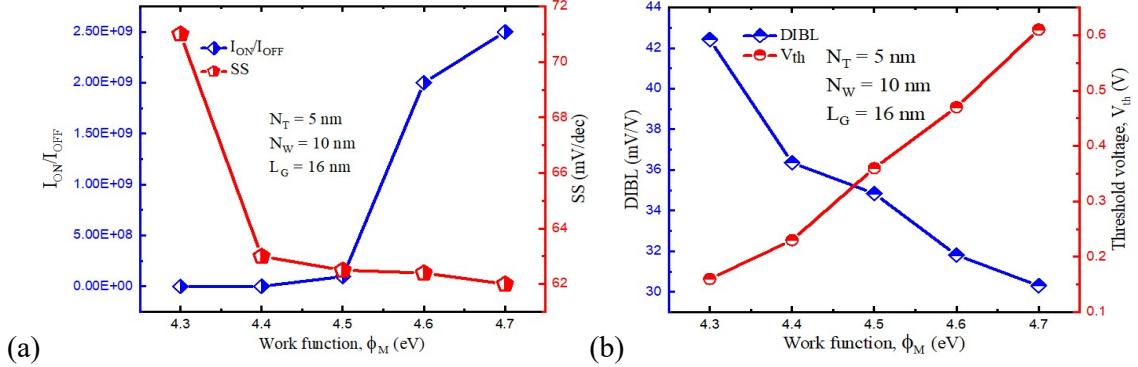

| Fig. 3.13. (a) Drain current variations with work function (b) $I_{ON}$ and $I_{OFF}$ variations as a function of work function .....                                                  | 42 |

| Fig. 3.14. (a) $I_{ON}/I_{OFF}$ and SS (b) DIBL and $V_{th}$ variations as a function of work function .....                                                                           | 42 |

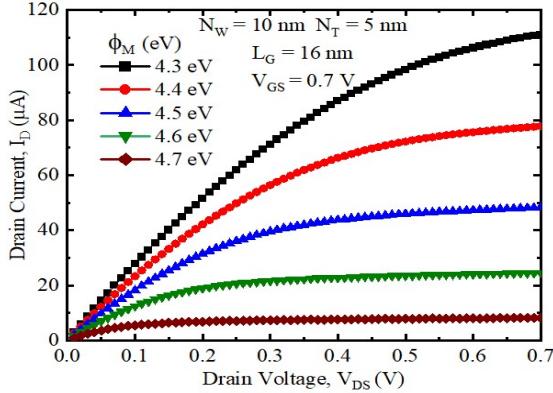

| Fig. 3.15. Output characteristics for various work function values as a function of drain voltage.....                                                                                 | 43 |

| Fig. 4.1. (a) Three-dimensional view of NSFET with Nitride spacer, (b) Cross sectional view of NSFET with $N_T$ and $N_w$ and (c) Three-dimensional view of NSFET with nanosheet ..... | 46 |

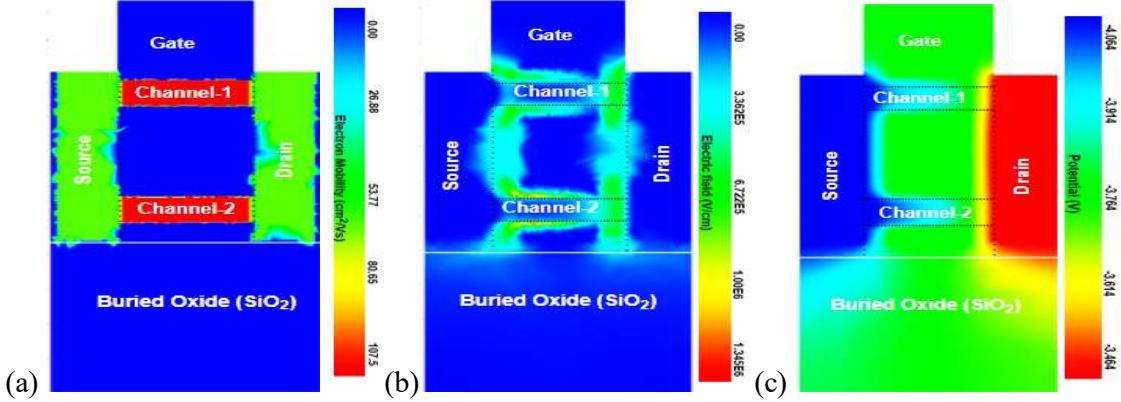

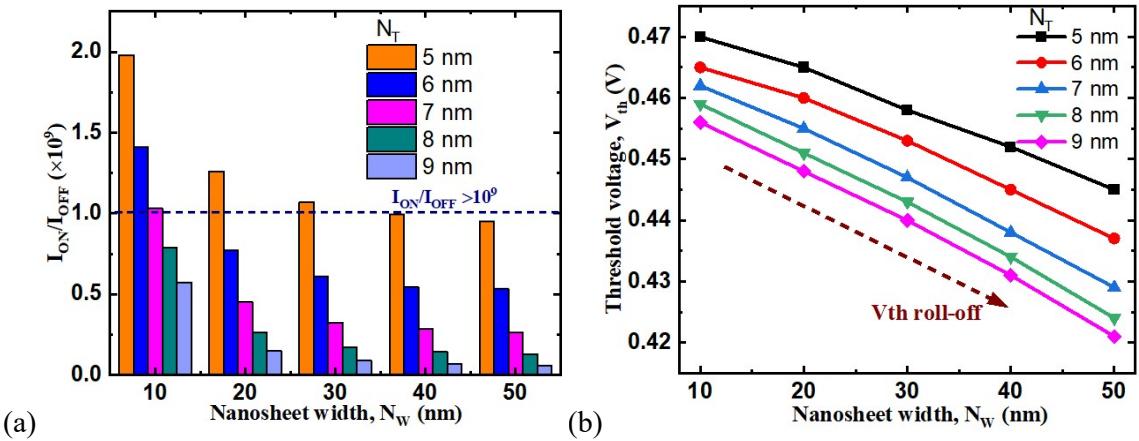

| Fig. 4.2. (a) Electron mobility (b) Electric field distribution (c) Potential of NSFET.....                                                                                            | 48 |

|                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

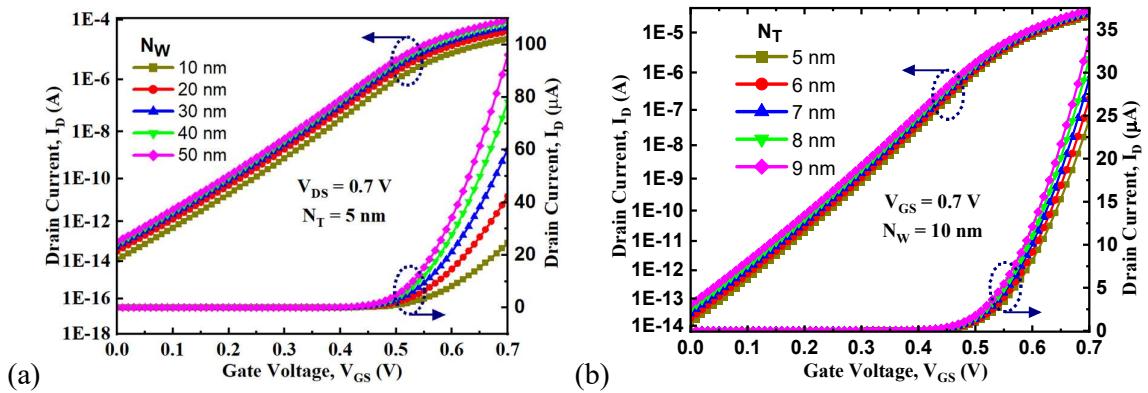

| Fig. 4.3. Fig. 4.3: Transfer characteristics of NSFET in linear and log scale for various (a) $N_W$ values and (a) $N_T$ values.....                  | 48 |

| Fig. 4.4. (a) $I_{ON}$ and (b) $I_{OFF}$ as a function of $N_W$ for various $N_T$ values.....                                                         | 49 |

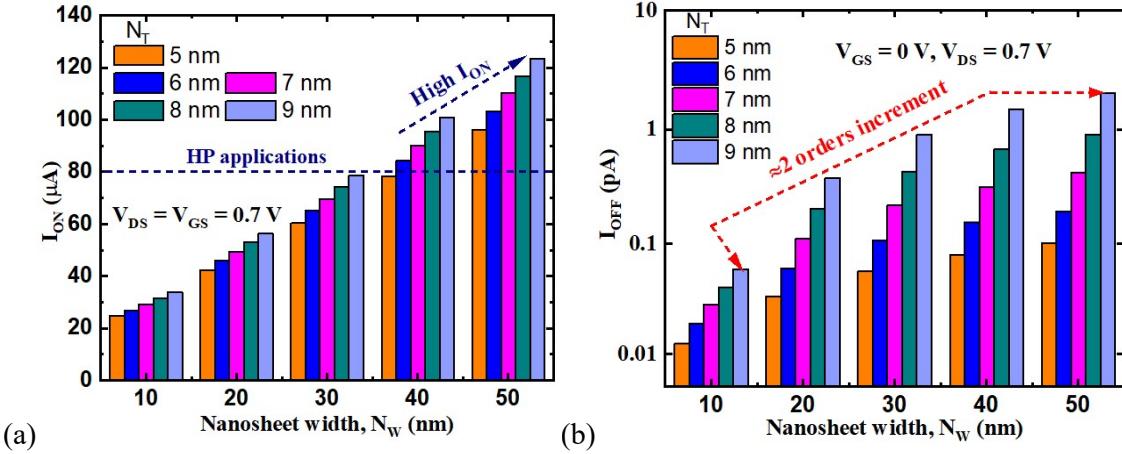

| Fig. 4.5. (a) Switching ratio and (b) Threshold voltage ( $V_{th}$ ) variations as a function of $N_W$ for various $N_T$ values .....                 | 50 |

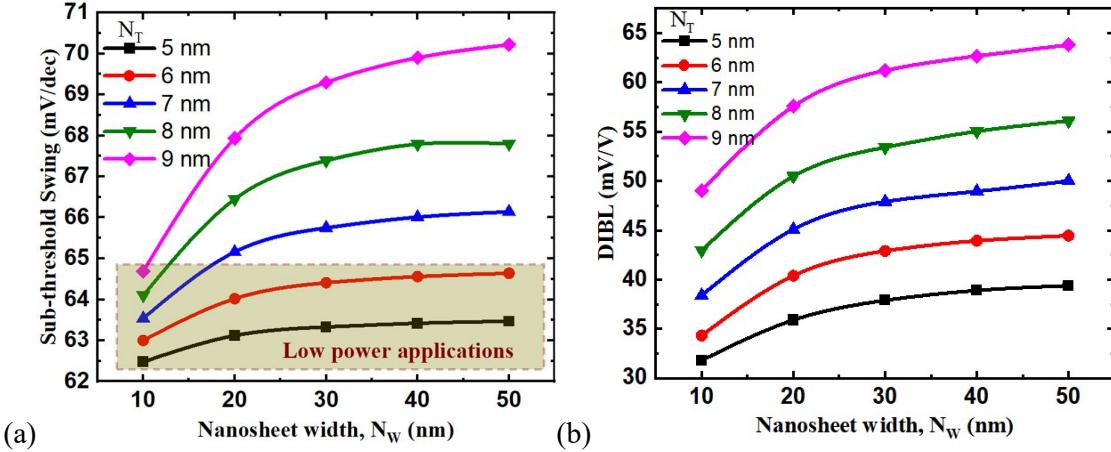

| Fig. 4.6. (a) SS and (b) DIBL as a function of $N_W$ for various $N_T$ values.....                                                                    | 51 |

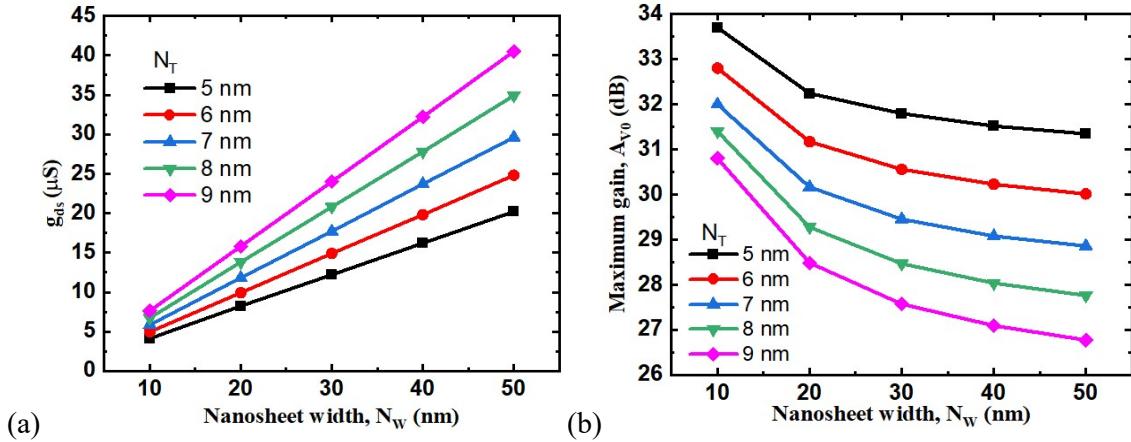

| Fig. 4.7. (a) Transconductance ( $g_m$ ) and (b) Transconductance generation factor (TGF) values as a function of $N_W$ for various $N_T$ values..... | 52 |

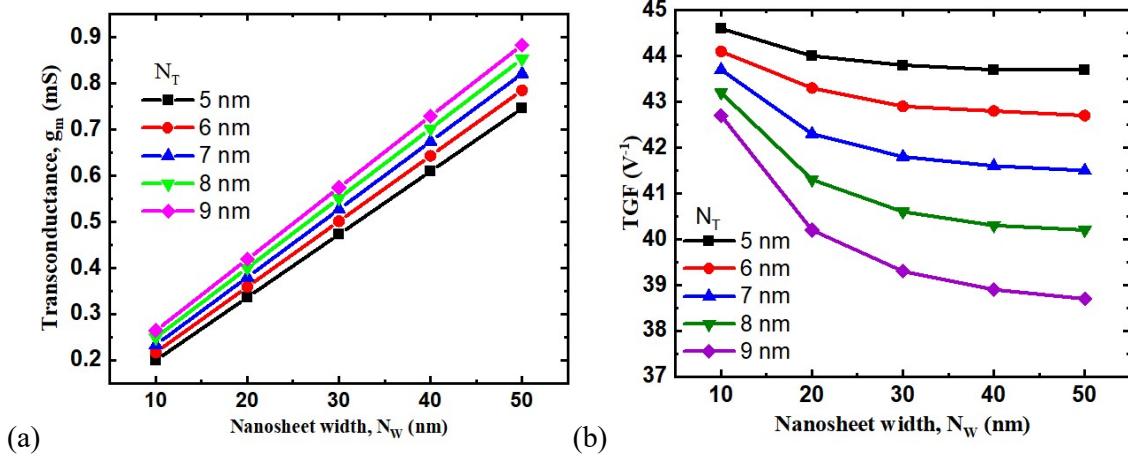

| Fig. 4.8. (a) $g_{ds}$ and (b) Maximum gain, $A_{V0}$ values as a function of $N_W$ for various $N_T$ values .....                                    | 53 |

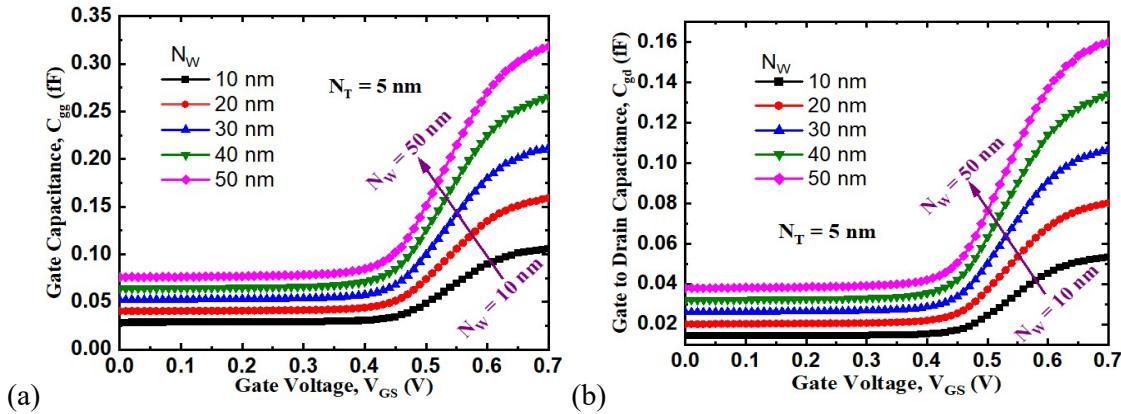

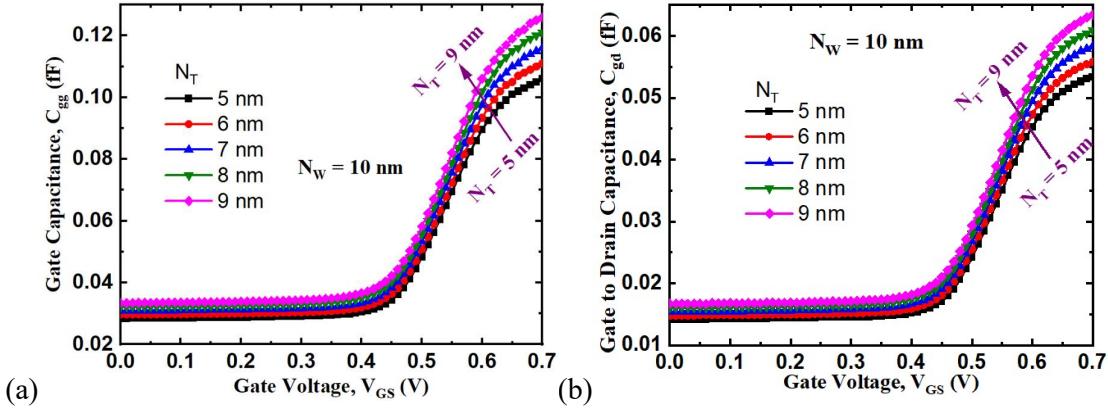

| Fig. 4.9. (a) $C_{gg}$ and (b) $C_{gd}$ versus $V_{GS}$ for various $N_W$ values for constant $N_T$ of 5 nm .....                                     | 54 |

| Fig. 4.10. (a) $C_{gg}$ and (b) $C_{gd}$ values as a function of $V_{GS}$ for various $N_T$ values for constant $N_W$ of 10 nm .....                  | 55 |

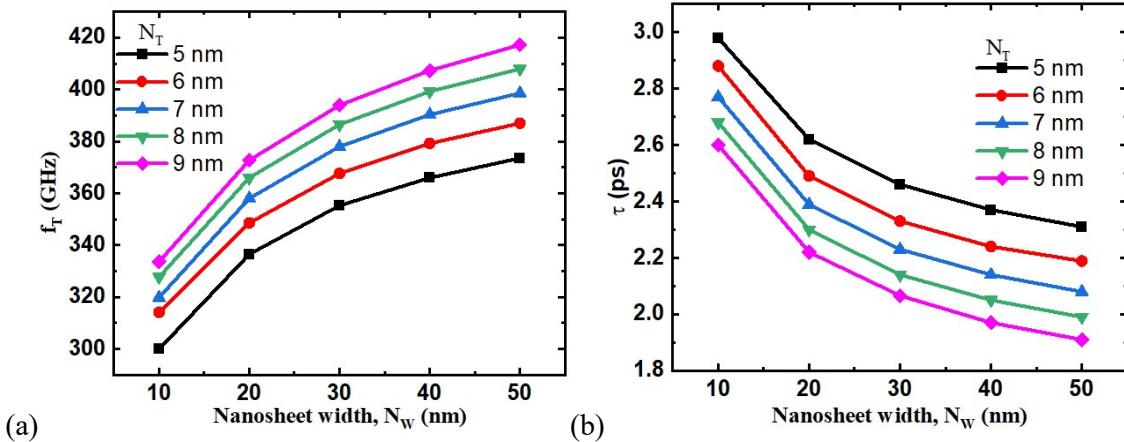

| Fig. 4.11. (a) $f_T$ (b) Intrinsic delay, $\tau$ values with respect to $N_W$ for different $N_T$ values .....                                        | 55 |

| Fig. 4.12. (a) TFP and (b) GFP values as a function of $N_W$ for various $N_T$ values .....                                                           | 57 |

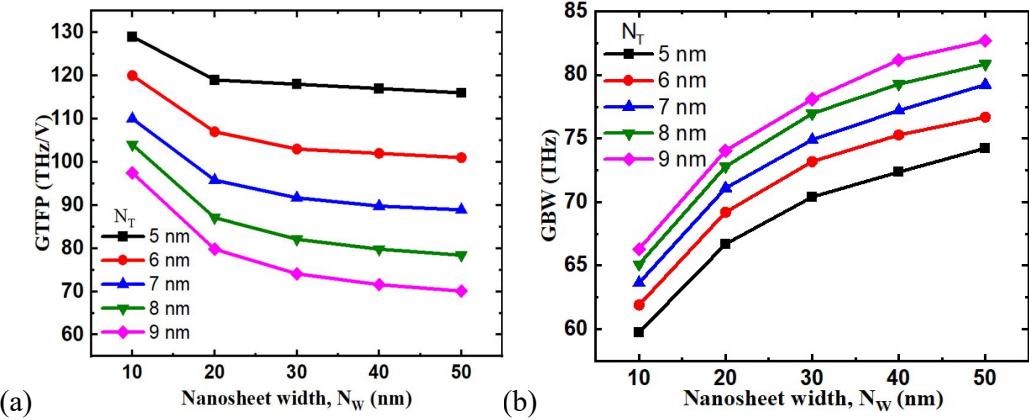

| Fig. 4.13. (a) GTFP and (b) GBW values as a function of $N_W$ for various $N_T$ values .....                                                          | 58 |

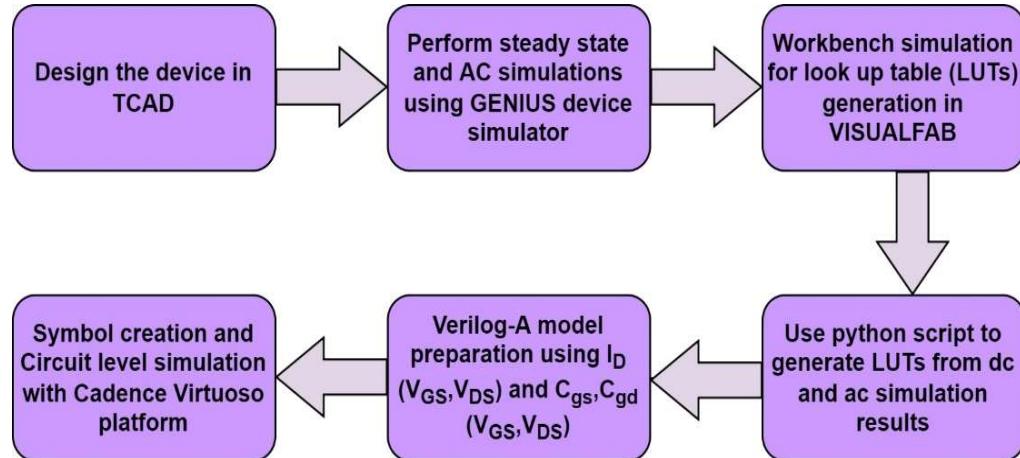

| Fig. 4.14. Flow chart of Verilog-A model creation and SPICE simulation .....                                                                          | 59 |

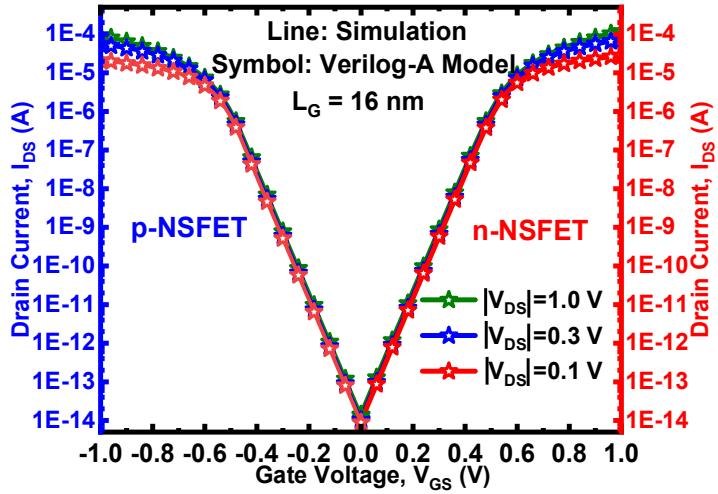

| Fig. 4.15. Calibration of TCAD data with Verilog-A model .....                                                                                        | 60 |

| Fig. 4.16. Look up table format (left) and Verilog-A code for symbol creation (right).....                                                            | 60 |

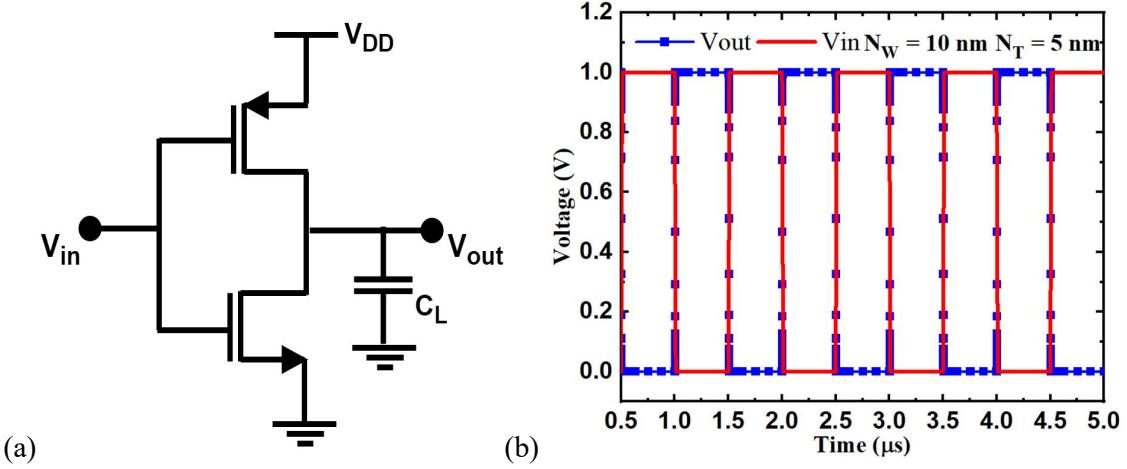

| Fig. 4.17. (a) Inverter schematic diagram (b) transient response of inverter for $N_W = 10$ nm and $N_T = 5$ nm.....                                  | 61 |

| Fig. 4.18. (a) Propagation delay ( $\tau_p$ ), EDP and (b) Switching current of inverter for different $N_W$ at constant $N_T$ of 5 nm .....          | 61 |

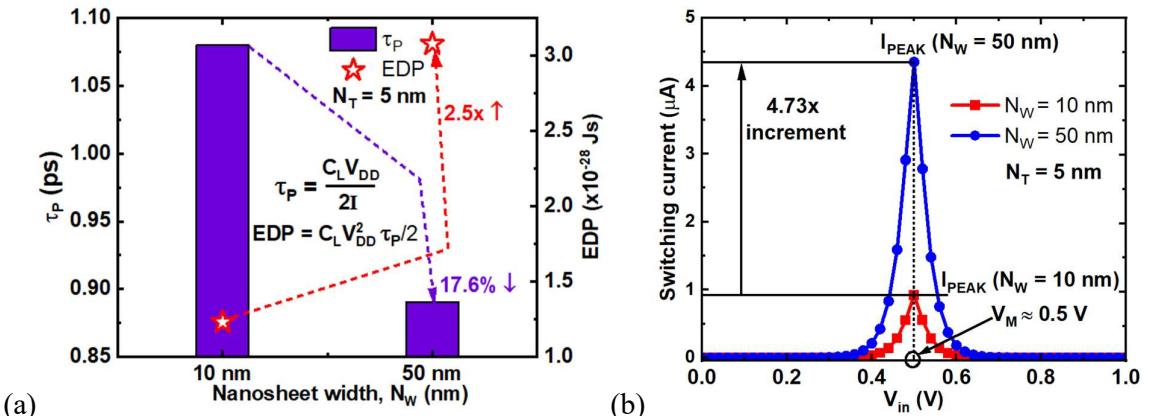

| Fig. 4.19. (a) Transfer characteristics of inverter for various $V_{DD}$ values (b) NM as a function of $N_W$ at $V_{DD} = 1$ V .....                 | 62 |

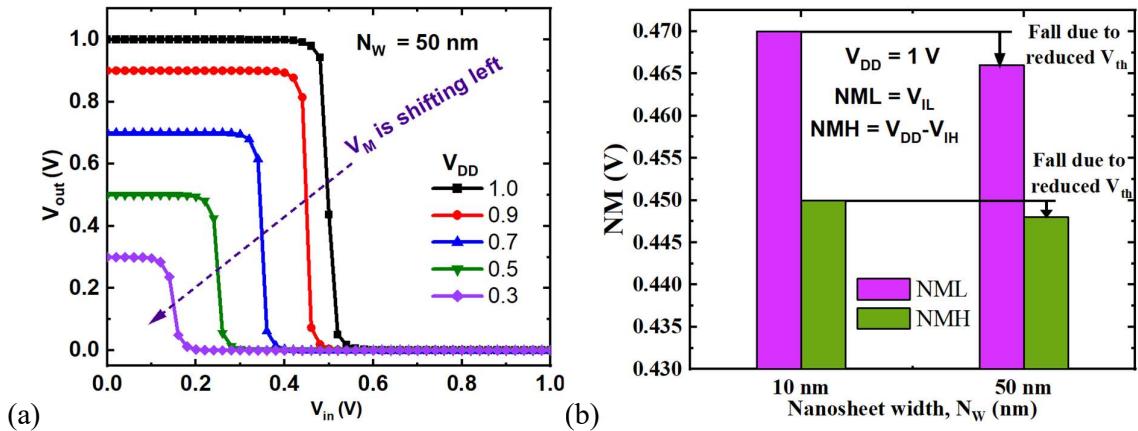

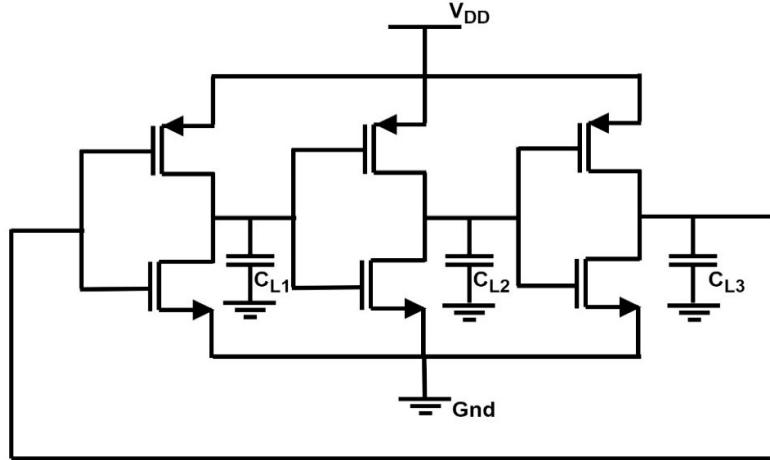

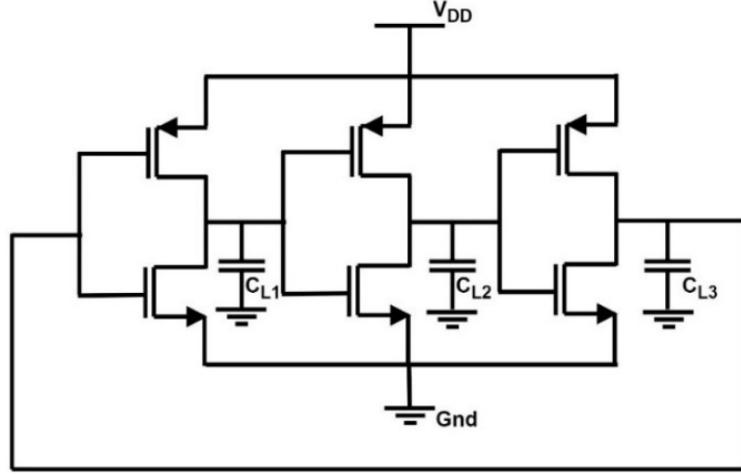

| Fig. 4.20. 3- stage ring oscillator (RO) .....                                                                                                        | 63 |

| Fig. 4.21. 3- stage ring oscillator transient response for (a) $N_W$ of 10 nm and (b) $N_W$ of 50 nm.....                                             | 63 |

|                                                                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

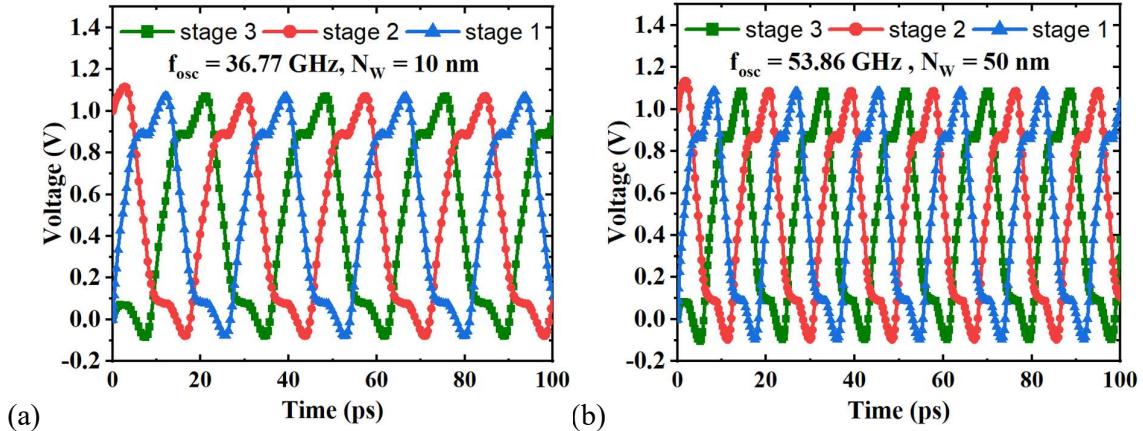

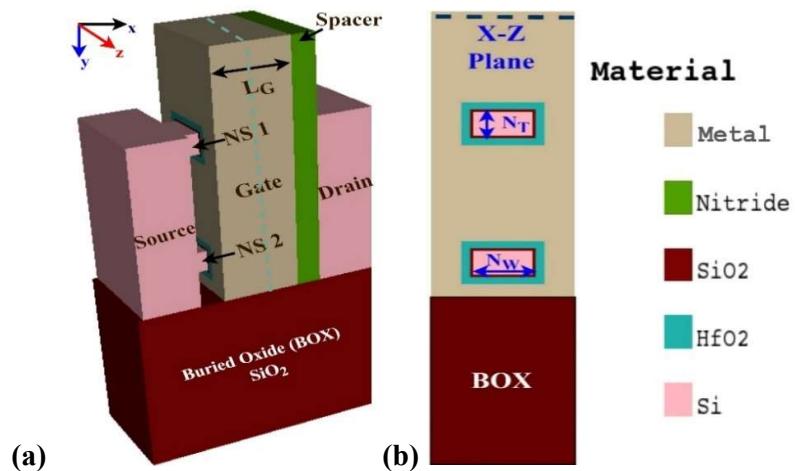

| Fig 5.1. (a) 3-D view of NSFET representing stacked nanosheets, (b) 2-D cross-section view of NSFET .....                                                   | 65 |

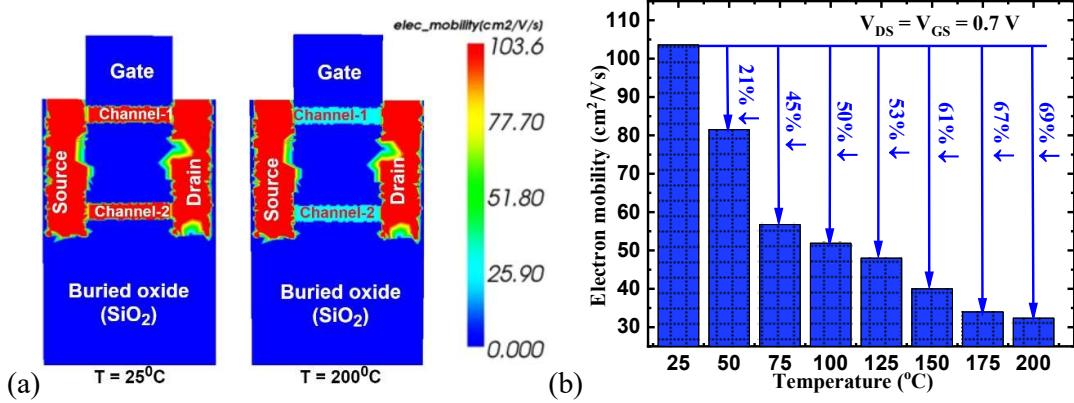

| Fig. 5.2. Contour plot for electron mobility of NSFET at 25 <sup>0</sup> C and 200 <sup>0</sup> C and (b) electron mobility at different temperatures ..... | 67 |

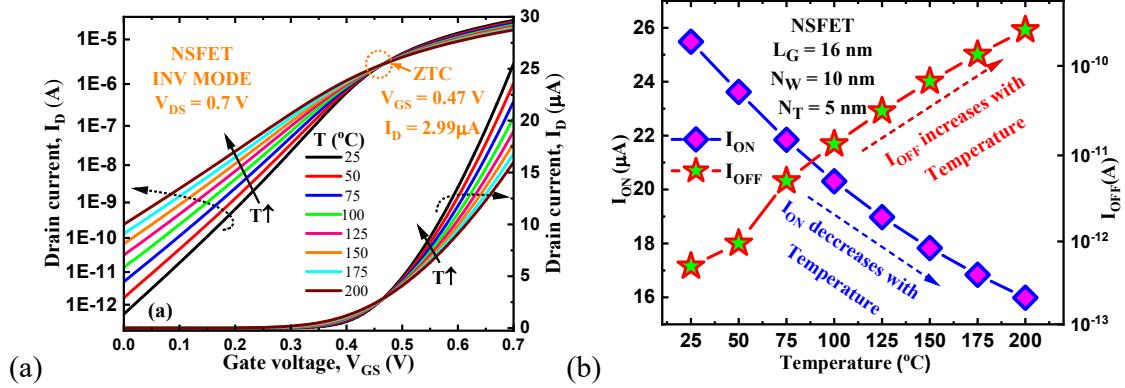

| Fig. 5.3. (a) Transfer characteristics and (b) $I_{ON}$ and $I_{OFF}$ of NSFET at different temperatures .....                                              | 67 |

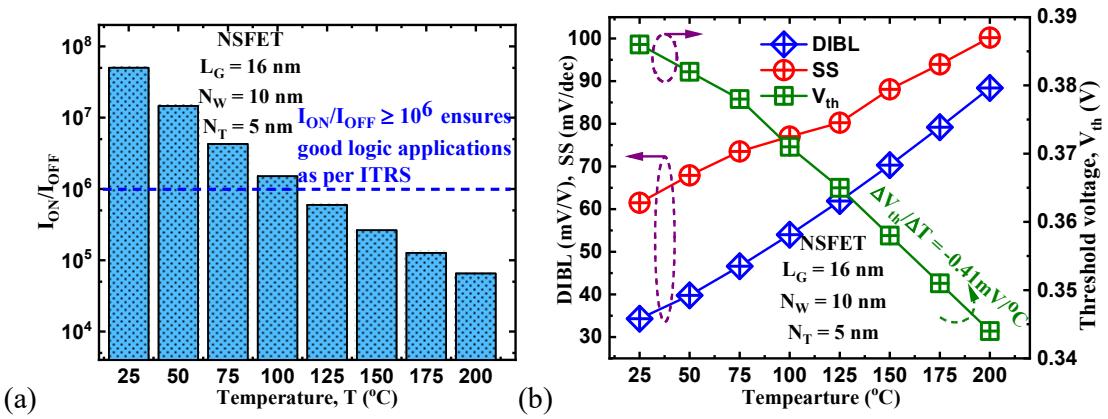

| Fig. 5.4. (a) $I_{ON}/I_{OFF}$ (b) SS, DIBL and $V_{th}$ of NSFET at different temperatures .....                                                           | 68 |

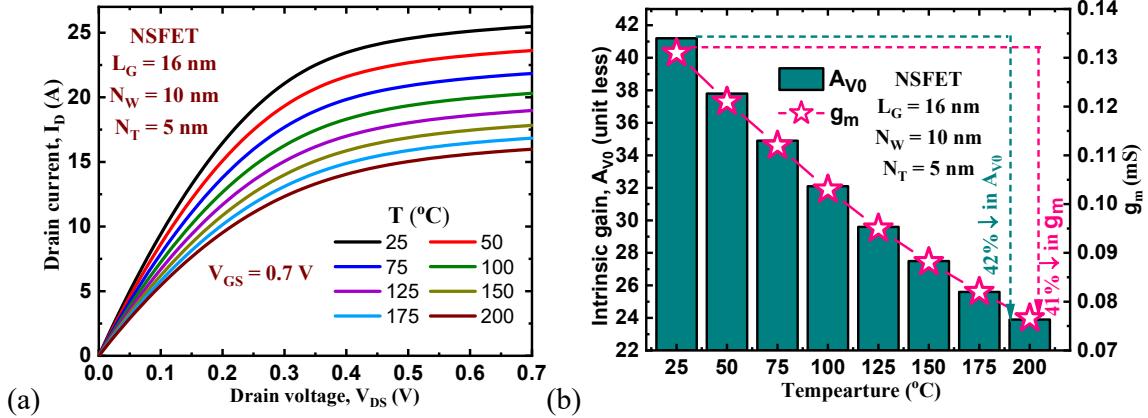

| Fig. 5.5. (a) Output characteristics and (b) $A_{v0}$ and $g_m$ of NSFET with temperature .....                                                             | 69 |

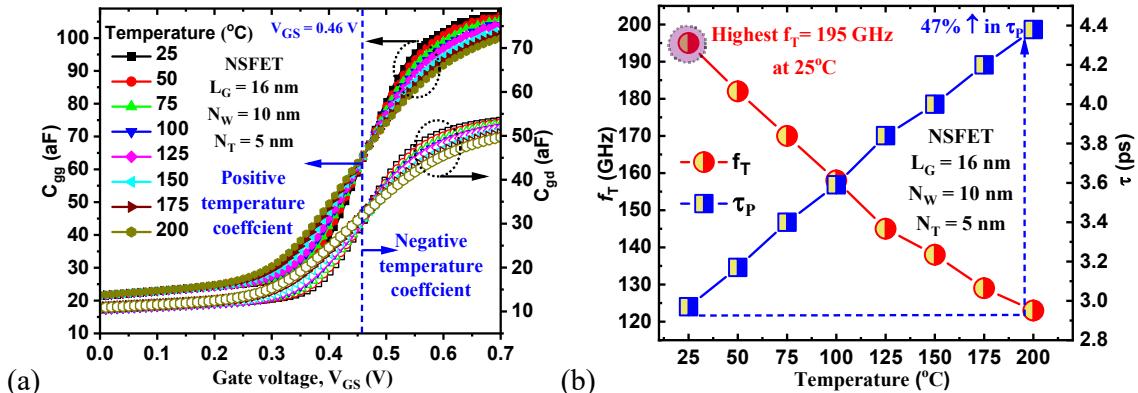

| Fig. 5.6. (a) $C_{gg}$ , $C_{gd}$ (b) cut-off frequency ( $f_T$ ), intrinsic delay ( $\tau$ ) of NSFET at various temperatures .....                        | 69 |

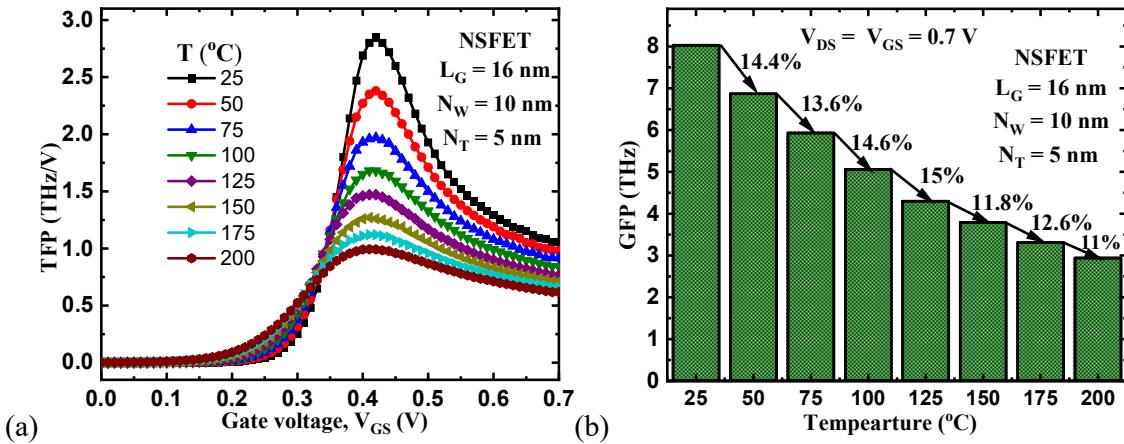

| Fig. 5.7. (a) TFP and (b) GFP of NSFET at various temperatures .....                                                                                        | 70 |

| Fig. 5.8. (a) GTFP and (b) GBW of NSFET at various temperatures .....                                                                                       | 71 |

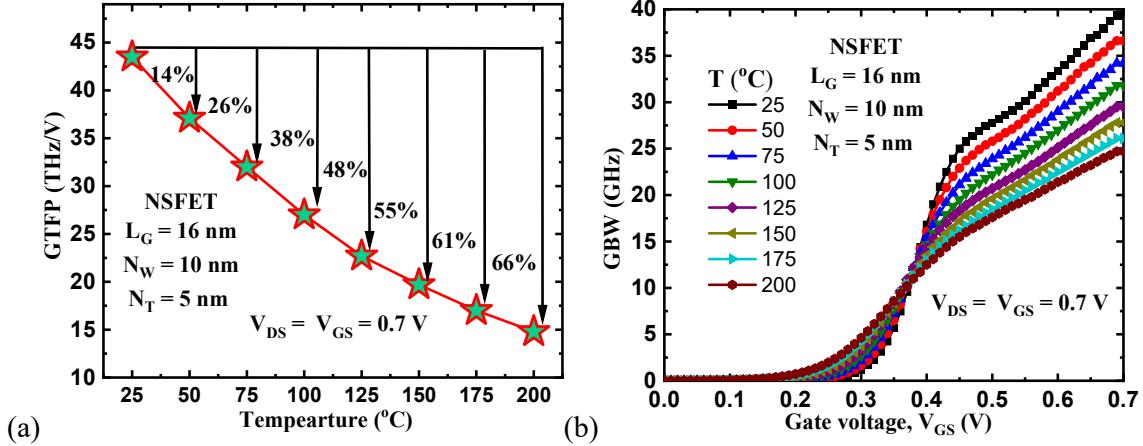

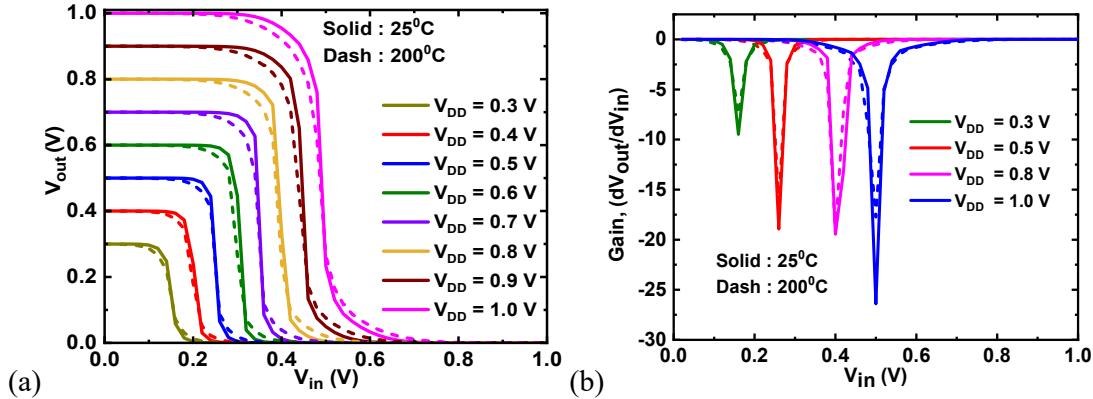

| Fig. 5.9. (a) Schematic of the inverter, transient response of inverter at (b) T = 25 <sup>0</sup> C and (c) T = 200 <sup>0</sup> C .....                   | 72 |

| Fig. 5.10. (a) Output characteristics of inverter at different temperatures and (b) Gain of the inverter at 25 <sup>0</sup> C and 200 <sup>0</sup> C .....  | 72 |

| Fig. 5.11. Schematic of the 3-stage ring oscillator .....                                                                                                   | 73 |

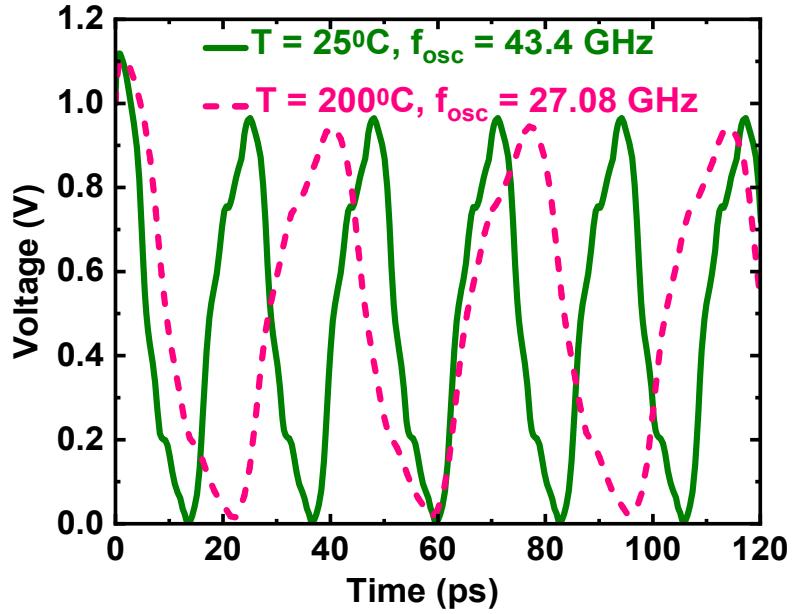

| Fig. 5.12. Transient response of RO at 25 <sup>0</sup> C and 200 <sup>0</sup> C .....                                                                       | 73 |

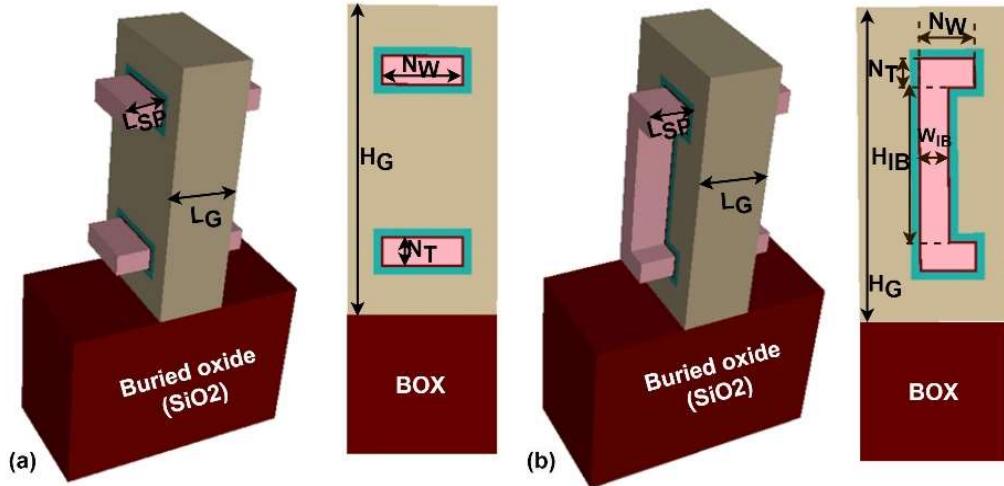

| Fig. 6.1. 3-D and 2-D cross-sectional views of (a) NSFET and (b) CombFET .....                                                                              | 76 |

| Fig. 6.2. Process flow of CombFET .....                                                                                                                     | 76 |

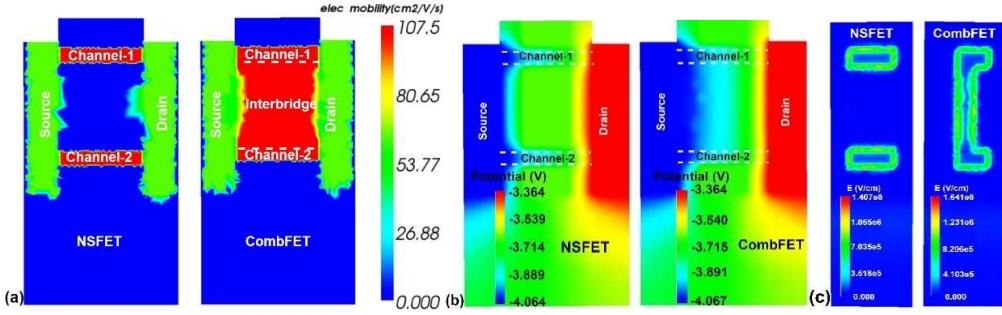

| Fig. 6.3. Contour plots of both NSFET and CombFET for (a) electron mobility, (b) potential, and (c) electric field in ON state .....                        | 78 |

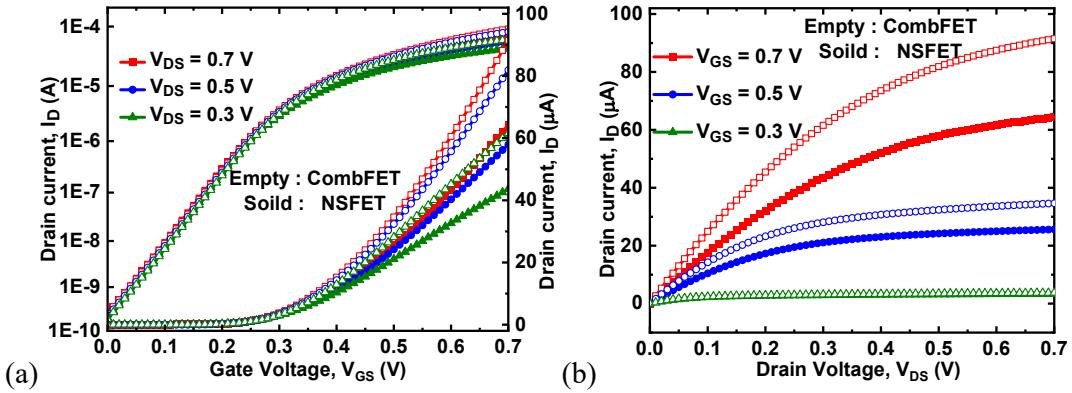

| Fig. 6.4. (a) $I_D-V_{GS}$ and (b) $I_D-V_{DS}$ for both NSFET and CombFET at different voltages .....                                                      | 78 |

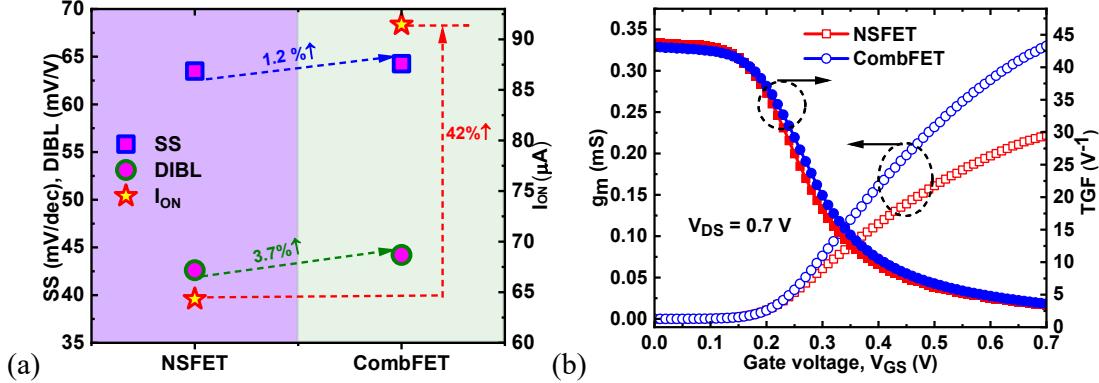

| Fig. 6.5. (a) SS, DIBL and $I_{ON}$ , (b) $g_m$ and TGF for both NSFET and CombFET .....                                                                    | 79 |

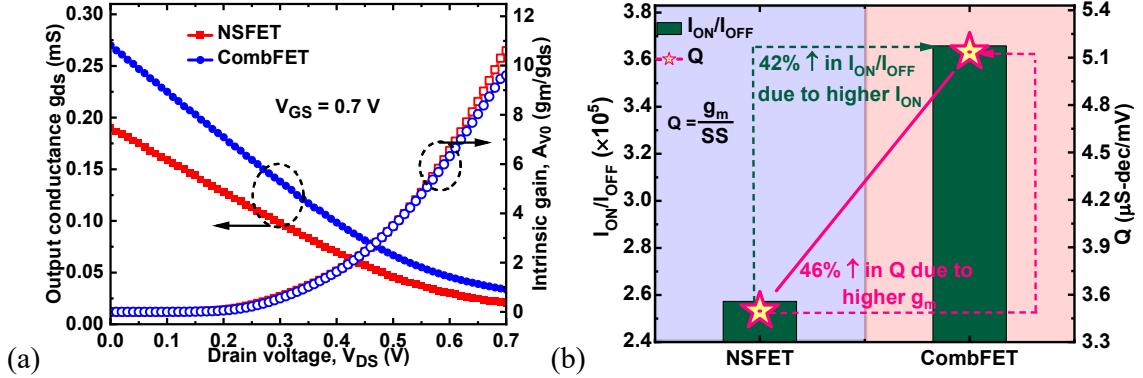

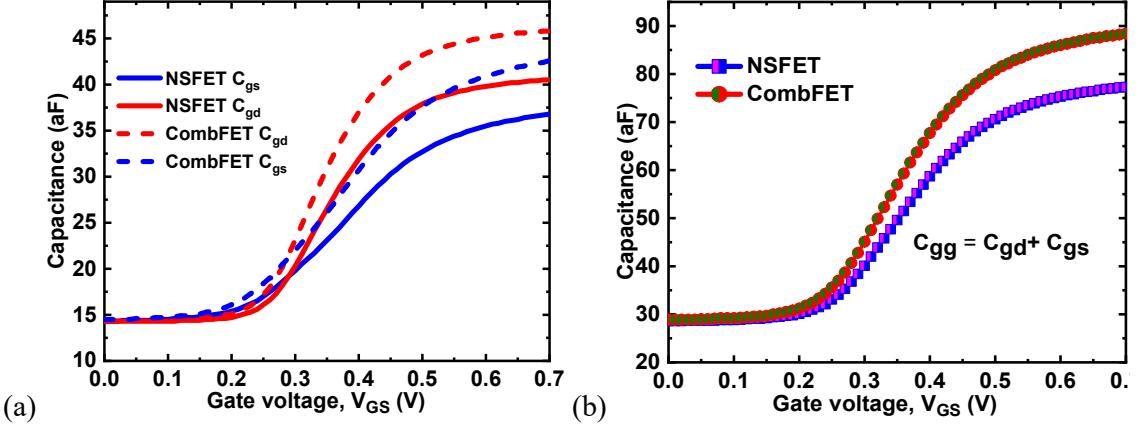

| Fig. 6.6. (a) Output conductance ( $g_{ds}$ ) and intrinsic gain ( $A_{v0}$ ) (b) $I_{ON}/I_{OFF}$ and Q for both NSFET and CombFET .....                   | 80 |

| Fig. 6.7. (a) $C_{gs}$ , $C_{gd}$ and (b) $C_{gg}$ for both NSFET and CombFET .....                                                                         | 81 |

| Fig. 6.8. (a) $f_T$ and $\tau$ , and (b) TFP and GFP for both NSFET and CombFET .....                                                                       | 81 |

|                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Fig. 6.9. GTFP and GBW for both NSFET and CombFET .....                                                   | 82 |

| Fig. 6.10. (a) $I_D$ - $V_{GS}$ and (b) $I_D$ - $V_{DS}$ for various $W_{IB}$ values .....                | 83 |

| Fig. 6.11. (a) $I_{ON}$ and $I_{OFF}$ (b) SS, DIBL and $I_{ON}/I_{OFF}$ for various $W_{IB}$ values ..... | 83 |

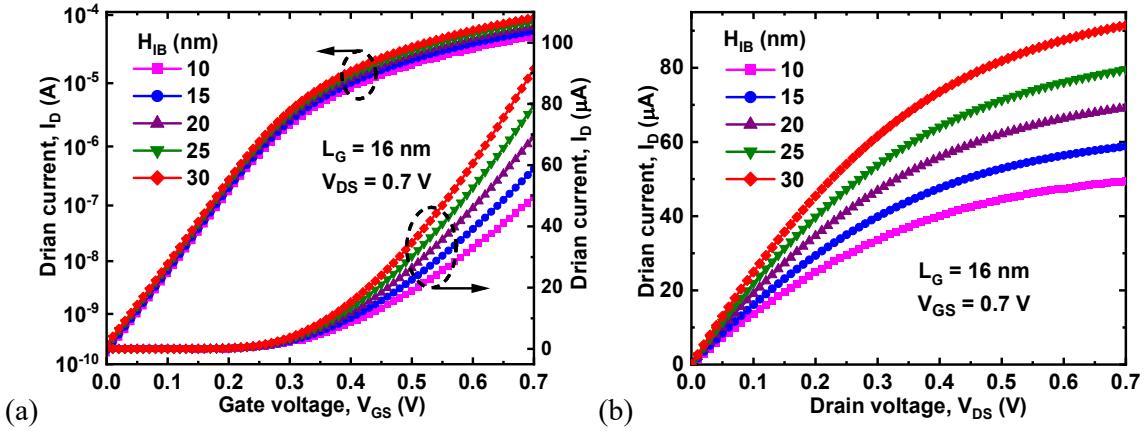

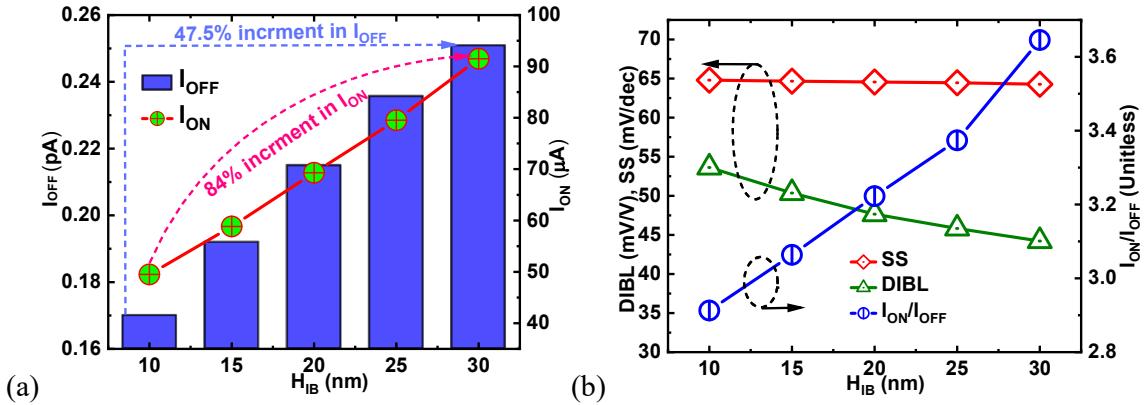

| Fig. 6.12. (a) $I_D$ - $V_{GS}$ and (b) $I_D$ - $V_{DS}$ for various $H_{IB}$ values .....                | 84 |

| Fig. 6.13. (a) $I_{ON}$ and $I_{OFF}$ (b) SS, DIBL and $I_{ON}/I_{OFF}$ for various $H_{IB}$ values ..... | 84 |

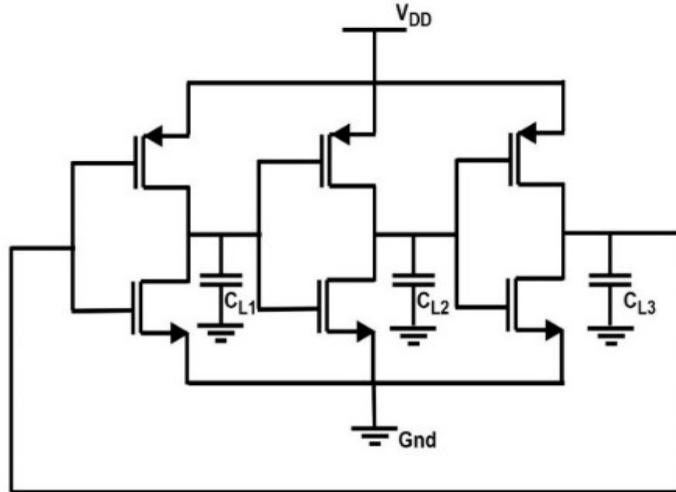

| Fig. 6.14. Schematic diagram of the 3-stage ring oscillator (RO) .....                                    | 85 |

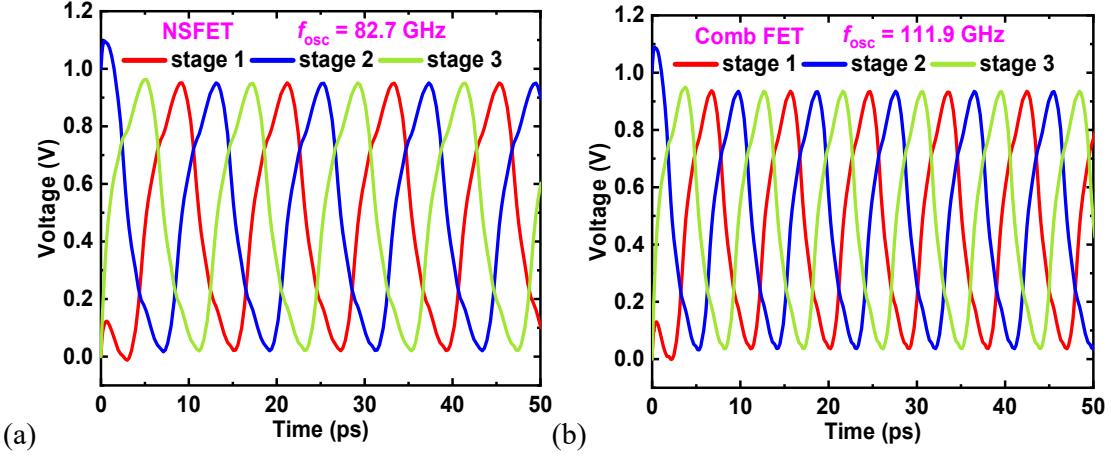

| Fig. 6.15. The transient response for (a) NSFET based RO and (b) CombFET based RO .....                   | 86 |

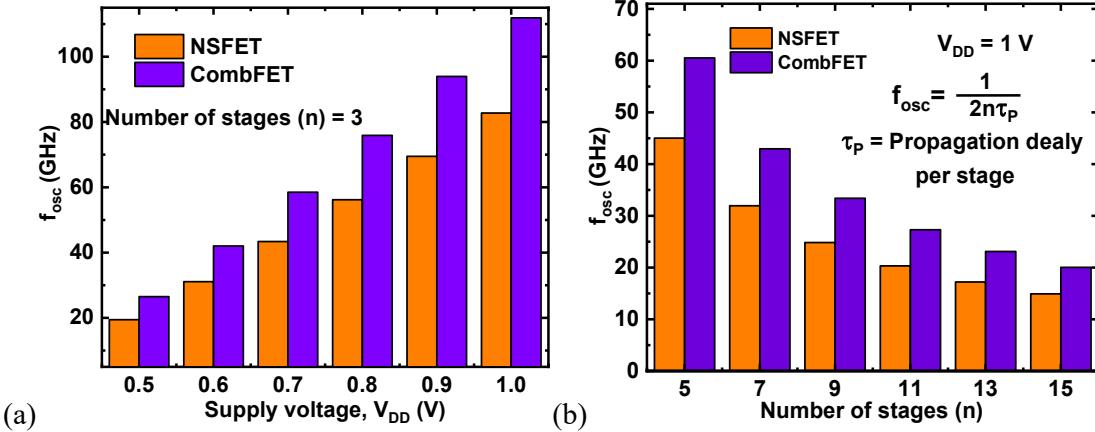

| Fig. 6.16. Variations in $f_{OSC}$ with (a) supply voltage and (b) number of stages .....                 | 86 |

## LIST OF TABLES

|                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.1. Area, designer, production year (2000 onwards), process node count of transistors, and fabrication technology for various processors..... | 4  |

| Table 2.1. Comparison of performance of Multigate FETs reported in the literature.....                                                               | 29 |

| Table 3.1. Device parameters used in simulation .....                                                                                                | 34 |

| Table 4.1. Simulation parameters.....                                                                                                                | 47 |

| Table 4.2. Comparison of DC and analog/RF metrics with existing literature .....                                                                     | 59 |

| Table 4.3. Comparison of $f_{osc}$ with existing literature.....                                                                                     | 64 |

| Table 5.1. Design parameters for NSFET .....                                                                                                         | 66 |

| Table 6.1. Device parameters of NSFET and CombFET .....                                                                                              | 77 |

| Table 6.2. Comparison with existing literature .....                                                                                                 | 87 |

## NOMENCLATURE

|           |                                                   |

|-----------|---------------------------------------------------|

| IC        | Integrated chip                                   |

| IoT       | Internet of things                                |

| BTBT      | Band to band to tunneling                         |

| DIBL      | Drain induced barrier lowering                    |

| $I_{OFF}$ | OFF-state leakage current                         |

| $I_{ON}$  | ON current                                        |

| $V_{DD}$  | Supply Voltage                                    |

| $k$       | Dielectric constant                               |

| EOT       | Equivalent oxide thickness                        |

| JL FET    | Junctionless field effect transistor              |

| $f_T$     | Cut-off frequency                                 |

| SOI       | Silicon on insulator                              |

| MOSFET    | Metal oxide semiconductor field effect transistor |

| CMOS      | Complementary metal oxide semiconductor           |

| SCEs      | Short channel effects                             |

| $V_{th}$  | Threshold voltage                                 |

| RDF       | Random dopant fluctuations                        |

| GAA       | Gate all around                                   |

| HP        | High performance                                  |

| AC        | Accumulation                                      |

| DG        | Double gate                                       |

| $t_{ox}$  | Gate oxide thickness                              |

| TG        | Trigate                                           |

| BOX       | Buried oxide                                      |

| SS        | Subthreshold swing                                |

| TGF       | Transaction generation factor                     |

| $C_{gd}$  | Miller Capacitance                                |

| $C_{gg}$  | Gate capacitance                                  |

| $C_{ox}$  | Gate oxide capacitance                            |

| GBW       | Gain band width product                           |

|                  |                                                     |

|------------------|-----------------------------------------------------|

| $L_G$            | Gate length                                         |

| $N_w$            | Nanosheet width                                     |

| $N_t$            | Nanosheet thickness                                 |

| $\tau$           | Intrinsic delay                                     |

| ITRS             | International technology roadmap for semiconductors |

| IRDS             | International roadmap for devices and systems       |

| $Q$              | ON-OFF performance metric                           |

| $L_{eff}$        | Effective channel length                            |

| INV              | Inversion mode                                      |

| TFP              | Transconductance frequency product                  |

| GFP              | Gain frequency product                              |

| GTFP             | Gain transconductance frequency product             |

| EDP              | Energy delay product                                |

| PDP              | Power delay product                                 |

| $V_{EA}$         | Early voltage                                       |

| WF               | Work function                                       |

| $G_m$            | Transconductance                                    |

| $L_s$            | Source side spacer length                           |

| $L_d$            | Drain side spacer length                            |

| $I_{ON}/I_{OFF}$ | ON-OFF current ratio                                |

| $V_{GS}$         | Gate voltage                                        |

| $V_{DS}$         | Drain voltage                                       |

| $I_D$            | Drain current                                       |

| $f_{osc}$        | Frequency of oscillations                           |

| $T$              | Temperature                                         |

| $I_{SC}$         | Switching current                                   |

| NM               | Noise margin                                        |

| NML              | Noise margin low                                    |

| NMH              | Noise margin high                                   |

| $V_M$            | Switching threshold                                 |

# Chapter-1

## Introduction

### 1.1 Introduction

Due to the ever-increasing demand for low-power, high-speed, and smaller-size electronic equipment, electronic gadgets have gotten a lot of attention in recent decades [1]. The device technology boosted the performance of various fields. From hand-held calculators, radios, walkmans, and CD/DVD players in the past to today's smart devices such as electronic wrist watches, smartphones, displays, cameras, sensors, smart driver-less cars, bipedal robots, and medical devices such as heart-beat measurement devices, pacemakers, and oximeters, as well as the internet of things (IoTs) are advanced by the continuous growth of semiconductor industry. Nanoelectronic devices with ultra-low power consumption are being explored extensively around the world in order to enable the aforementioned technological applications. The tremendous increment in functionality and substantial downsizing of integrated circuits is achieved by Complementary Metal Oxide Semiconductor (CMOS) scaling and which enabled the growth of IoT and the big data era [2], [3]. Mobile phones, which are equal to early supercomputers, are now a part of every household because of superb CMOS technology. MOSFETs (Metal Oxide Semiconductor Field-Effect Transistors) are the building blocks of CMOS circuitry, and they can be used as switches in integrated circuits. Usually, in the OFF-state, the switch should not consume any power, and the switching from the OFF-condition to the ON-condition should be seamless. However, MOSFET's subthreshold swing (SS) is restricted to the Boltzmann tyranny of 60 mV/decade due to the intrinsic thermionic injection method of conduction [4]. As a result, the supply voltage required to produce a reasonable switching ratio ( $I_{ON}/I_{OFF}$ ) is strictly limited [5].

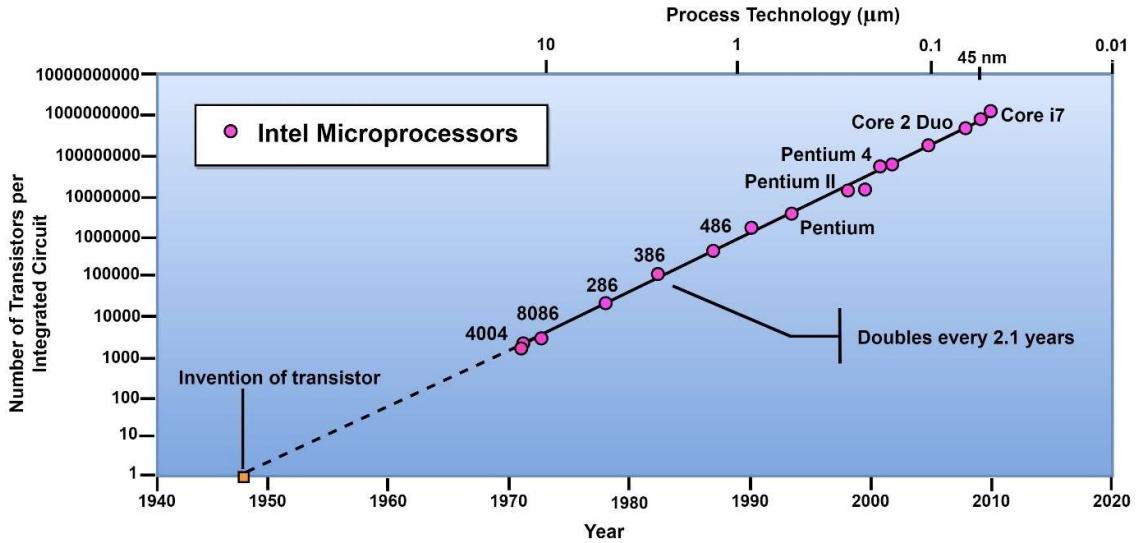

To enable applications that go beyond technological constraints, active research is being conducted all around the world on ultra-low power nano electronic devices. Since the first transistor invention in 1948 by Bardeen, Brattain, and Shockley at Bell Labs [6], [7] and the evolution of the Integrated Circuit (IC) in 1958 by Jack Kilby at IBM, the packing density of transistors in IC has been steadily improving over the time, following the well-known Moore's law trend [8], [9]. Then comes the development of the MOSFET, the most widely manufactured electronic device, sometimes known as the "workhorse" of the electronics industry. The

following Fig. 1.1 shows the number of transistors per integrated circuit with respect to process technology node from the year of the invention of the transistor by intel microprocessor.

Fig. 1.1: Number of transistors per integrated circuit for various process technology nodes from the year of the invention of transistor by intel microprocessor [10].

The CMOS scaling created revolutions in human life. Microelectronics, a branch of electronics studies about miniature electronic components and designs, has grown substantially from MOSFET scaling over the past three decades. In addition to the enhancement in performance, the CMOS technology offered more benefits in terms of smaller physical device manufacturing with scaling. The higher package density and enhanced efficiency demonstrated the superiority of reduced physical size. Due to the decreased parasitic capacitances and supply voltages, this continual growth resulted in significant power savings per node, which increased Integrated Circuit performance [10].

Table 1.1 demonstrates various crucial parameters like processor name, number of transistors, area, process node, and fabrication techniques used for various CPUs built since the year 2000, explaining the trend of scaling. SCEs and greater gate leakage currents, which become much more prevalent at smaller dimensions, limit device performance in terms of microprocessor speed, and power consumption with MOSFET scaling [11]. With scaling, the disadvantages like poor gate electrostatic integrity, increased leakage currents, performance/power ratio and reliability of the device. Gate induced drain leakage (GIDL), DIBL, SS, gate oxide tunnelling of carriers, and source/drain direct tunnelling are examples of SCEs that degrade device

performance and consequently alter subthreshold characteristics. In section 1.4, these adverse effects are discussed in detail.

| Processor                          | Process | Year | Area | Transistors        | Designer   | Fabrication technology     |

|------------------------------------|---------|------|------|--------------------|------------|----------------------------|

| <b>Pentium 4 Willamette</b>        | 180 nm  | 2000 | 217  | $4.20 \times 10^7$ | Intel      | -                          |

| <b>Pentium III Tualatin</b>        | 130 nm  | 2001 | 81   | $4.50 \times 10^7$ | Intel      | -                          |

| <b>Itanium 2 McKinley</b>          | 180 nm  | 2002 | 421  | $2.20 \times 10^8$ | Intel      | Bulk CMOS process          |

| <b>Itanium 2 Madison 6M</b>        | 130 nm  | 2003 | 374  | $4.10 \times 10^8$ | Intel      | -                          |

| <b>Pentium 4 Prescott</b>          | 90 nm   | 2004 | 110  | $1.12 \times 10^8$ | Intel      | -                          |

| <b>Pentium D Smithfield</b>        | 90 nm   | 2005 | 206  | $2.28 \times 10^8$ | Intel      | -                          |

| <b>Core 2 Duo Conroe</b>           | 65 nm   | 2006 | 143  | $2.91 \times 10^8$ | Intel      | -                          |

| <b>Pentium 4 Cedar Mill</b>        | 65 nm   | 2006 | 90   | $1.84 \times 10^8$ | Intel      | -                          |

| <b>POWER6</b>                      | 65 nm   | 2007 | 341  | $7.89 \times 10^8$ | IBM        | Partially depleted SOI     |

| <b>Core 2 Duo Wolfdale</b>         | 45 nm   | 2007 | 107  | $4.11 \times 10^8$ | Intel      | -                          |

| <b>AMD K10 quad-core 6M L3</b>     | 45 nm   | 2008 | 258  | $7.58 \times 10^8$ | AMD        | SOI Technology             |

| <b>Six-core Xeon 7400</b>          | 45 nm   | 2008 | 503  | $1.90 \times 10^9$ | Intel      | High- <i>k</i> process     |

| <b>Six-core Opteron 2400</b>       | 45 nm   | 2009 | 346  | $9.04 \times 10^9$ | AMD        | SOI technology             |

| <b>8-core POWER7 32M L3</b>        | 45 nm   | 2010 | 567  | $1.20 \times 10^9$ | IBM        | -                          |

| <b>16-core SPARC T3</b>            | 40 nm   | 2010 | 377  | $1.00 \times 10^9$ | Sun/Oracle | -                          |

| <b>Six-core Core i7 (Gulftown)</b> | 32 nm   | 2010 | 240  | $1.17 \times 10^9$ | Intel      | -                          |

| <b>10-core Xeon Westmere-EX</b>    | 32 nm   | 2011 | 512  | $2.60 \times 10^9$ | Intel      | High- <i>k</i> /Metal Gate |

| <b>Atom "Medfield"</b>             | 32 nm   | 2012 | 64   | $4.32 \times 10^9$ | Intel      | High- <i>k</i> /Metal Gate |

| <b>61-core Xeon Phi</b>            | 22 nm   | 2012 | 720  | $5.00 \times 10^9$ | Intel      | Trigate                    |

|                                      |       |      |       |                         |           |                                   |

|--------------------------------------|-------|------|-------|-------------------------|-----------|-----------------------------------|

| <b>Quad+GPU Core i7 Ivy Bridge</b>   | 22 nm | 2012 | 160   | 1.40 x 10 <sup>9</sup>  | Intel     | FinFET Tri Gate transistors       |

| <b>Six-core Core i7 Ivy Bridge E</b> | 22 nm | 2013 | 256   | 1.86 x 10 <sup>9</sup>  | Intel     | FinFET Tri gate transistors       |

| <b>A7 (dual-core ARM64)</b>          | 28 nm | 2013 | 102   | 1.00 x 10 <sup>9</sup>  | Apple     | High- <i>k</i> metal gate process |

| <b>18-c Xeon Haswell-E5</b>          | 22 nm | 2014 | 661   | 5.56 x 10 <sup>9</sup>  | Intel     | -                                 |

| <b>A8</b>                            | 20 nm | 2014 | 89    | 2.00 x 10 <sup>9</sup>  | Apple     | -                                 |

| <b>A8X</b>                           | 20 nm | 2014 | 128   | 3.00 x 10 <sup>9</sup>  | Apple     | -                                 |

| <b>A9</b>                            | 14 nm | 2015 | 96    | 2.00 x 10 <sup>9</sup>  | Apple     | FinFET process                    |

| <b>A9X (dual-core ARM64)</b>         | 16 nm | 2015 | 143.9 | 3.00 x 10 <sup>9</sup>  | Apple     | FinFET+ Process                   |

| <b>Xeon Broadwell-E5</b>             | 14 nm | 2016 | 456   | 7.20 x 10 <sup>9</sup>  | Intel     | Trigate FinFET                    |

| <b>Snapdragon 835</b>                | 10 nm | 2016 | 72.3  | 3.00 x 10 <sup>9</sup>  | Qualcomm  | FinFET Process                    |

| <b>A11 Bionic</b>                    | 10 nm | 2017 | 89.23 | 4.30 x 10 <sup>9</sup>  | Apple     | FinFET process                    |

| <b>Snapdragon 850</b>                | 10 nm | 2017 | 94    | 5.30 x 10 <sup>9</sup>  | Qualcomm  | FinFET Process                    |

| <b>Tegra Xavier SoC</b>              | 12 nm | 2018 | 350   | 9.00 x 10 <sup>9</sup>  | Nvidia    | FinFET process                    |

| <b>GC2 IPU</b>                       | 16 nm | 2018 | 825   | 2.36 x 10 <sup>10</sup> | Graphcore | FinFET process                    |

| <b>Snapdragon 8cx</b>                | 7 nm  | 2018 | 112   | 8.50 x 10 <sup>9</sup>  | Qualcomm  | FinFET Process                    |

| <b>A12X Bionic</b>                   | 7 nm  | 2018 | 122   | 1.00 x 10 <sup>10</sup> | Apple     | FinFET Process                    |

| <b>A12 Bionic</b>                    | 7 nm  | 2018 | 83.27 | 6.90 x 10 <sup>9</sup>  | Apple     | FinFET process                    |

Table 1.1: Area, designer, production year (2000 onwards), process node count of transistors, and fabrication technology for various processors [12].

## 1.2 CMOS Technology Scaling

Power consumption is an important consideration in the design of modern integrated circuits. Users want a portable hand-held device with a longer battery life in general. CMOS circuits should therefore be designed in such a way that they dissipate less power. In CMOS circuits, power consumption is majorly classified into two categories. Those are (a) dynamic power

consumption, which is due to the charging and discharging of the load capacitor while switching, and (b) static power consumption, which is the leakage power consumed by the device in idle condition.

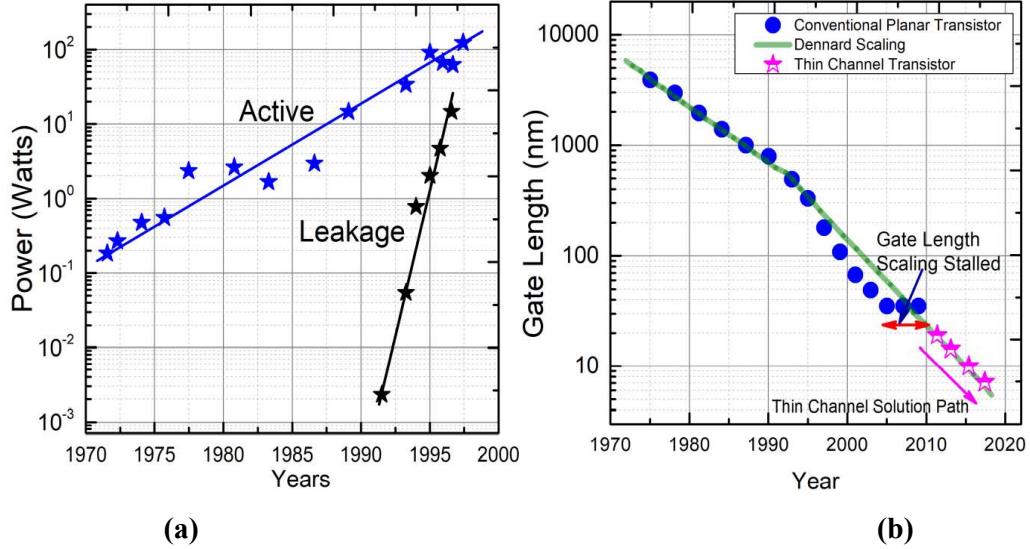

Fig. 1.2: (a) Various power consumptions [4], (b) gate length scaling with respect to time [8].

When the size of MOSFETs is scaled down, the dynamic power dissipation decreases due to a decrease in gate capacitance. However, at the beginning of the 1990's, dynamic power started dominating overall consumption [4], [13]. Furthermore, as demonstrated in Fig. 1.2(a), the active and leakage power increases dramatically every year [8]. In order to increase the packing density of transistors in ICs, the transistor size is reduced by scaling down the channel length and other device parameters. The electrostatic integrity of silicon CMOS devices began to deteriorate due to leakage through scaled ultra-thin gate oxide and different device characteristics, resulting in the introduction of unfavourable SCEs such as DIBL, gate leakage, and threshold voltage roll-off [14]. The high- $k$  metal gate (HKMG) is suggested as a way to avoid leakage through ultra-thin oxide [15], [16]. Despite HKMG solutions, rising leakage power reached active power levels around the year 2000, arresting scaling patterns Fig. 1.2 (b).

However, further downscaling the conventional MOSFET is cumbersome due to various adverse SCEs which limit the processor efficiency and power dissipation aspects. To prevent leakage power dissipation and improve gate controllability, Multiple gate FETs like FinFET (Fin Field Effect Transistor), ultra-thin body and box (UTBB) fully depleted silicon-on-insulator (SOI) are proposed [17]. These options laid the groundwork for keeping Moore's law alive for future scaling.

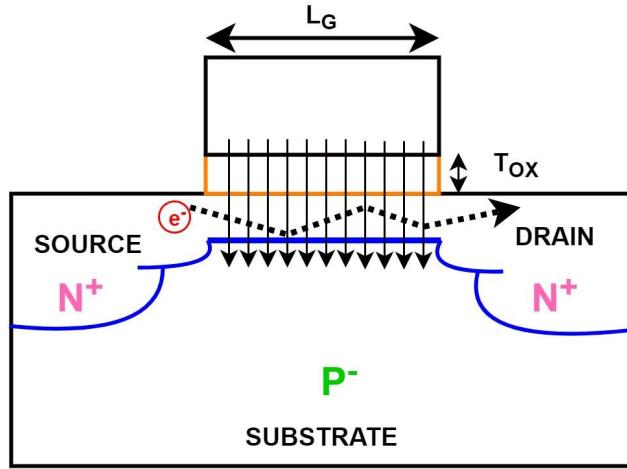

### 1.3 Conventional MOSFET

Usually, the conventional MOSFET contains four terminals called source, drain, gate, and body. The schematic of conventional n-type MOSFET is shown in Fig. 1.3. As it is well known, the n-type MOSFET's channel and body are doped with p-type impurities, whereas, the source/drain are doped with n-type impurities.

Fig. 1.3: Schematic view of conventional MOSFET [18].

However, for p-type MOSFET, the source/drain terminals are doped with p-type doping, and the channel is doped with n-type impurities.

The body of a MOSFET is often connected to the source, resulting in a three-terminal device known as a field-effect transistor (FET). The voltage applied at the gate terminal controls the channel that exists beneath the gate region. Insulating oxide ( $\text{SiO}_2$ ) separates the gate terminal from the silicon material, resulting in a strong interface between the gate and channel. In n-channel operation, the drain is biased at a higher potential than the source. When the applied voltage is zero at the gate terminal, the current between the source and drain is comparatively low due to the large potential barrier for electrons between the source and channel; this is referred to as the transistor's OFF state. The minority carriers in the substrate are drawn to the channel surface when a positive bias is applied to the gate terminal owing to the electric field created across the gate dielectric (hence, the field effect). Inversion mode refers to the accumulation of minority carriers in the channel, which inverts the type of free carriers present at the channel's surface. The inverted channel acts as a conducting layer between the source and drain terminals. As a result, a substantial current flow exists in the device, indicating that the device is in the ON state. By utilizing these ON and OFF mechanisms, the MOSFET can be used as a switch. The switch should be turned OFF when the voltage provided to the control gate is less than a predetermined threshold voltage ( $V_{th}$ ). The device should be ON with a limited

amount of current (indicated as  $I_{ON}$ ) between the source and drain once the control gate voltage is above  $V_{th}$ . The MOSFET, on the other hand, is unable to attain optimal switching behaviour. The gate is normally operated in the positive voltage regime for n-channel operation. The subthreshold region is defined as the range of gate to source voltages ( $V_{GS}$ ) between 0 V and  $V_{th}$ , where the current grows exponentially with gate voltage. Depending on the bias applied for above  $V_{th}$  the MOSFET can be operated in either linear or saturation regions [18].

## 1.4 Short Channel Effects

Short channel length devices are more prone to SCEs due to the merging of depletion zones below the gate between the source and drain junctions. As a result, the electrostatics of the channel area of short channel MOSFETs are influenced by the gate voltage, as well as the source and drain voltages. The threshold voltage is reduced as a result of the significant sharing of channel depletion charges by the depletion zones of the source/channel and drain/channel junctions. Reduced gate length in nanoscale MOSFETs has a number of negative consequences, including reduced  $V_T$ , increased  $I_{OFF}$ , higher SS, increased power dissipation, deteriorated DIBL, hot carrier effects, minimised effective channel length (channel length modulation), increased GIDL, increased gate-oxide tunnelling leakage current, direct source to drain quantum tunnelling (ballistic transport), surface scattering, and impact ionisation. In MOSFET scaling theory, these effects are referred to as short-channel effects (SCEs). Some important SCEs are discussed as follows:

### 1.4.1 Drain Induced Barrier Lowering (DIBL):

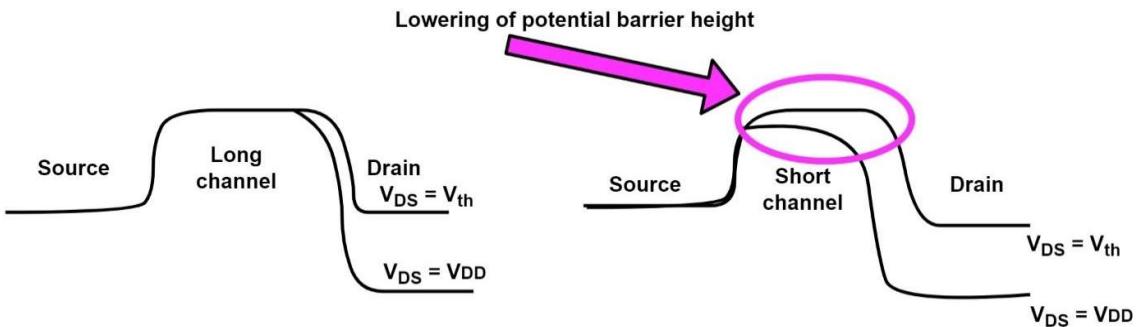

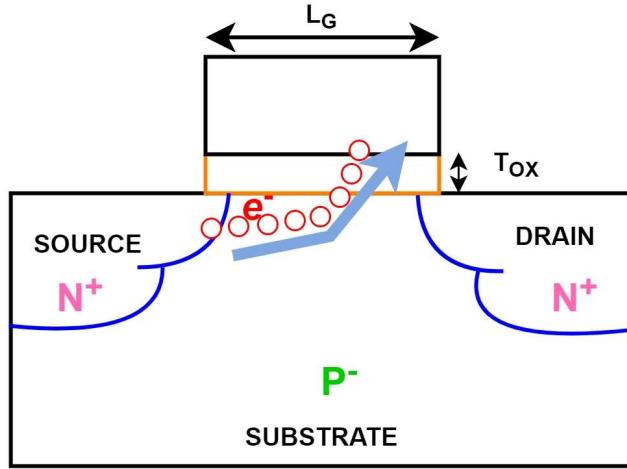

Fig. 1.4: The effect of DIBL on (a) Long channel (b) Short channel MOSFET [18], [19].

In conventional MOSFETs, the gate alone controls the flow of current through the channel. However, when channel length decreases, the drain begins to act as a second gate, i.e., the drain current,  $I_D$  is controlled by both gate and drain voltages. Usually, for long channel devices, with

the rise in  $V_{DS}$ , the drain side bands only affect. However, as the gate length shortens, rise in the  $V_{DS}$  leads to the lowering of the source to channel barrier (which the gate should be able to regulate) also. This phenomenon is often referred to as drain induced barrier lowering [18], [19] which is shown in Fig. 1.4.

### 1.4.2 Subthreshold Swing (SS):

Sub-threshold swing (SS) is an important metric for device application in logic circuits. The SS is defined as the change in the gate voltage needed to get a decade change in current. For a MOSFET SS can be given by the equation shown [20]:

$$SS = \left( \frac{KT}{q} \right) * \ln(10) * (1 + (C_D/C_{ox})) \quad (1.1)$$

Here, T is the temperature in kelvin, q is the electron charge,  $C_D$  is the depletion capacitance, and  $C_{ox}$  is the gate oxide capacitance. The term  $(1+C_D/C_{ox}) \geq 1$  denotes the coupling efficiency of the gate voltage to the channel potential. Even the second term is ignored since it is less than 1. The first term limits SS to 60 mV/Decade. Thus, for MOSFET, the SS is limited to 60 mV/dec, which is the thermodynamic limit, also called as Boltzmann limit. The SS value tends to rise with short channel lengths.

### 1.4.3 Channel Length Modulation:

Fig. 1.5: Channel length modulation illustration in MOSFET [18].

When the drain voltage,  $V_{DS}$  exceeds the gate overdrive voltage, pinch off occurs at the drain end by a length of  $\Delta L_G$  [21], [22] as shown in Fig. 1.5.

The relation between  $I_D$  and  $\Delta L_G$  can be expressed as [22]:

$$I_D = I_{Dsat} / (1 - \Delta L_G / L_G) \quad (1.2)$$

Here,  $\Delta L_G$  is more critical parameter and is a function of  $V_{DS}$  in the short channel device. The device exhibits non-saturation behaviour and lowering  $V_{th}$  due to the channel length modulation. For shorter channel lengths, the  $V_{th}$  is a strong function of  $L_G$ , and it falls drastically for shorter channel lengths [23]. It is also known as  $V_{th}$  - roll off with  $L_G$  scaling.

The drain current ( $I_D$ ) becomes relatively constant with respect to the drain voltage when  $V_{DS} \geq V_{GS} - V_{th}$ , and the device is considered to be in the saturation regime. The inversion charge  $Q_{I(x)}$  approaches zero when  $V(x)$  approaches  $V_{GS} - V_{th}$ . Where  $V(x)$  is the channel potential, the inversion charge density  $Q_{I(x)}$  is proportional to  $V_{GS} - V(x) - V_{th}$  [24]. As a result, the creation of the channel inversion area is limited to the region  $0 \leq x \leq L'$  channel length ( $L$ ) below the gate for  $V_{DS} > V_{GS} - V_{th}$  and the MOSFET is said to be in the pinch-off situation. Further, increase in  $V_{DS}$ , the effective channel length ( $L'$ ) reduces. Thus, the channel length modulation refers to  $L$ 's dependence on the drain voltage [18], [25]. In the saturation region, this effect lowers channel resistance and raises drain current ( $I_D$ ). In other words, while the device is in its saturation mode of operation, the slope of the  $I_D - V_{DS}$  curve becomes slightly positive and alters from the ideal zero value.

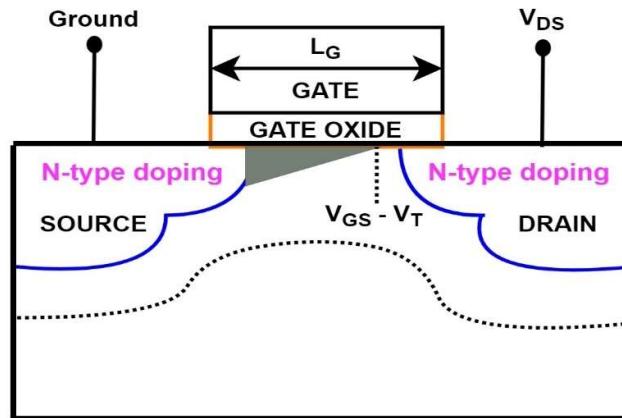

#### 1.4.4 Gate Oxide Leakage:

Fig. 1.6: Leakage current through gate oxide in MOSFET [18].

In the MOSFET structures, the  $\text{SiO}_2$  is a suitable contender and an excellent insulator. With scaling, it is inevitable to scale gate oxide thickness. However, when the oxide thickness reaches scaling of less than 3 nm, the carriers tunneling probability rises, resulting in gate oxide leakage

current [18], [26]. As a solution for this, a high- $k$  dielectric material is utilised to avoid gate oxide tunneling. The direct tunneling of carriers is reduced with high- $k$  dielectric oxide.

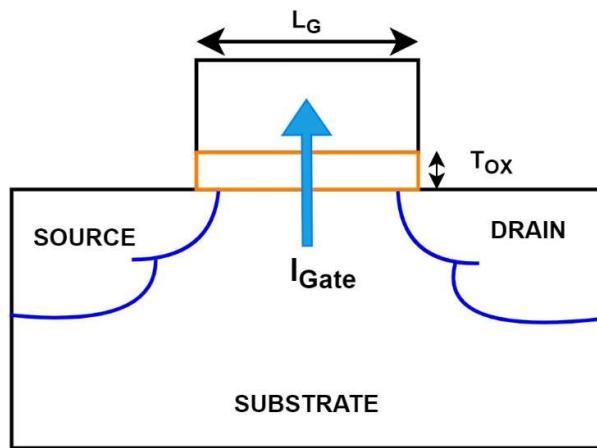

#### 1.4.5 Velocity Saturation:

Fig. 1.7: Velocity saturation in MOSFET [18].

The carriers' velocity tends to saturate at higher electric fields due to mobility saturation. Constant field scaling helps to sustain the equal electric fields and can be advantageous. However, constant field scaling is not always preferred by the semiconductor industry [27]. For example, compared to supply voltage scaling, oxide thickness scaling is more at particular technology node. As a result, in nano-scale MOSFETs, higher electric fields are present and tend to be the saturation of carriers. There will be no adverse effect if saturation is attained at drain voltages larger than the overdrive voltage. However, at the nanoscale regime, this phenomenon can be observed at lower drain voltages and offers less ON current. From Fig. 1.7, it is noticed that for lower electric fields the velocity increases linearly, whereas, for higher electric fields, it tends to saturate at  $10^7$  cm/s around  $E_c=10^5$  V/cm at room temperature [19].

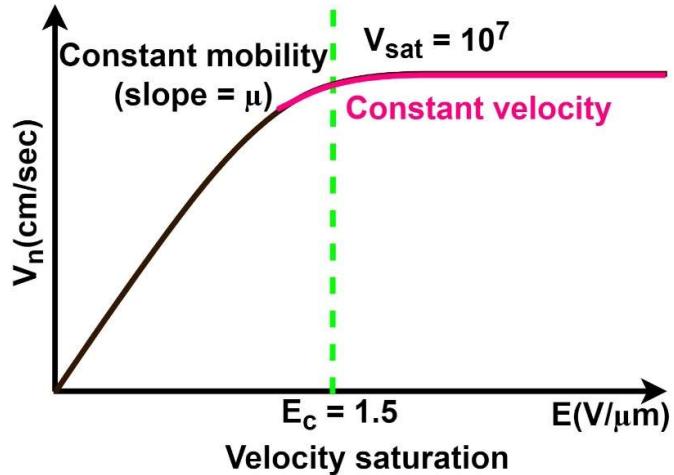

#### 1.4.6 Surface Scattering:

As the depletion layer extends laterally into the channel area with scaling, the lateral electric field tends to rise, due to which the surface mobility is affected by electric field. The surface scattering mechanism in the thin inversion layer of MOSFET tends to reduce the mobility under the influence of vertical electric field. Thus, travelling parallel to the surface is difficult for the carriers [28], as shown in Fig 1.8.

Fig. 1.8: Surface scattering effect in MOSFET [28].

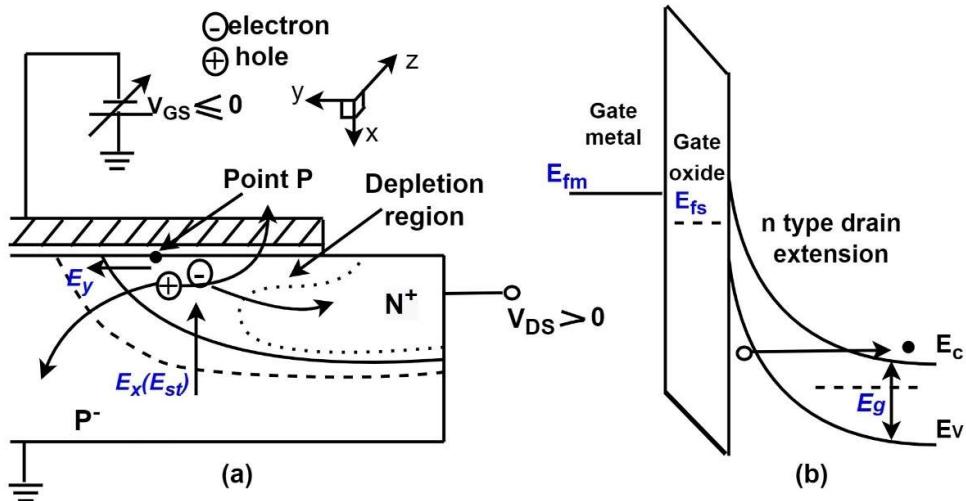

#### 1.4.7 Gate Induced Drain Leakage (GIDL):

Fig. 1.9: (a) The GIDL effect in the MOSFET (b) Electron tunneling phenomena by GIDL effect [31].

Usually, the electric field between the gate-end of the channel and the drain/channel junction is quite strong when a high drain bias voltage with low or negative gate bias voltage is applied to MOSFETs. Tunneling of electrons from the channel valence band to empty states in the drain region is likely to happen [29], which is shown in Fig 1.9(a) and (b). In OFF-state, this band-to-band tunnelling (BTBT) exacerbates the drain leakage current in MOSFETs and leads to more static power dissipation.

#### 1.4.8 Random Dopant Fluctuations (RDFs):

In nanoelectronics devices, random doping fluctuations (RDFs) are a severe concern, resulting in the loss of different performance metrics like effective carrier mobility and threshold voltage ( $V_{th}$ ). As the doping in nano electronic devices cannot be accurately controlled, minimising these effects becomes more difficult. Initially, this problem is addressed by Meng-Hsueh Chiang [30]. He stated that extremely scaled nano electronic devices are more prone to RDFs. Ultra-short nano scale devices having gate length around 12 nm have the highest RDF impact. This may be attributed to the fact that maintaining ultra-sharp doping gradients near S/D junctions is highly difficult at this level. A few orders of change in doping concentration at both channel and source/drain is required while moving from source to channel and then channel to drain within a few nanometres, which further raises the thermal budget requirements substantially. The researchers explored many methods to overcome this issue. According to Tetsu Ohtou et al., SOI-based nano electronic devices are more resistant to RDF and process variations when the substrate impurity concentration is higher than that of the channel [31]. Electrostatic doping (ED) has lately emerged as a potential technique for doping nanoscale electronics, in contrast to the regularly used ion-implantation strategy. In summary, we may conclude that addressing the issue of uniform doping at the nanoscale is fundamental.

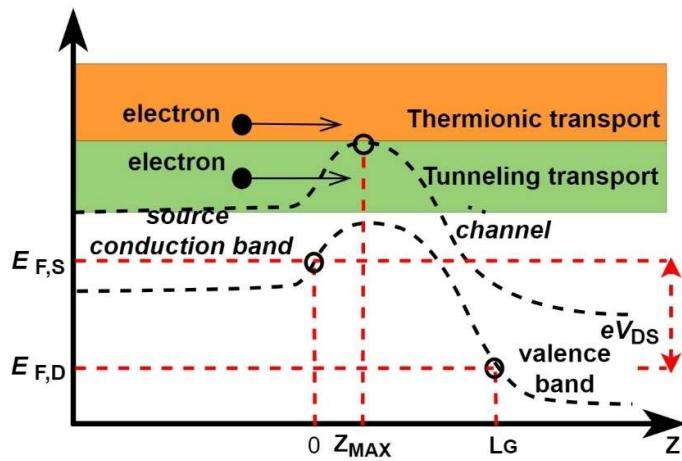

#### 1.4.9 Direct Source to Drain Quantum Tunneling:

Fig. 1.10: Ballistic transport mechanism in the MOSFET [18].

As the channel length shrinks, the lateral electric field in the channel grows. The likelihood of carriers tunneling directly from the source to the drain through the incredibly narrow channel between them increases in the presence of a strong electric field in the channel. This ballistic

transport phenomenon must be considered for calculating the device parameters of MOS transistors with channel lengths below 30–40 nm. The ballistic transport for nearly less than 10 nm channel length contributes to a leakage current in addition to the thermionic current [32] and is shown in Fig. 1.10.

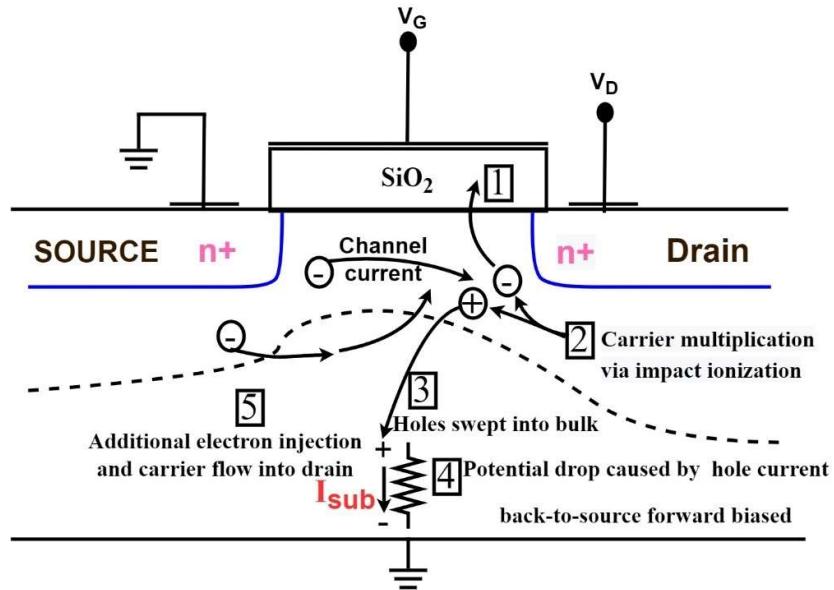

#### 1.4.10 Impact Ionization

Due to the high electron velocity in the channel of a short-channel MOSFET in the presence of a strong electric field, the impact ionisation process can produce electron-hole pairs in the depletion zone of the channel/drain junction. Gate leakage current, GIDL, and substrate leakage current are all unwanted for the device if the generated carriers travel toward the gate, drain, and substrate [33]. Any remaining holes collect in the bulk substrate as the electrons travel in the direction of the drain. Fig. 1.11 depicts the various contributions to the unwanted substrate leakage current in MOSFETs by forming the p-type base of an n-p-n parasitic BJT [34].

Fig. 1.11: Various leakage current mechanisms in the MOSFET [18].

#### 1.4.11 Hot Carrier Effects

There is a strong electric field at the drain side of the MOSFET with high  $V_{DS}$  and low  $V_{GS}$ . The increasing lateral field may induce the carriers to accelerate at the channel-drain junction. Certain carriers may thereby accumulate sufficient kinetic energy to pass through the gate oxide dielectric region, damaging the channel/oxide contact as shown in Fig. 1.12.

Fig. 1.12: Schematic of hot carrier effect of MOSFET [18].

This might change the oxide interface charges, which would disrupt the device's usual electrical behaviour. At higher fields, hot carriers could harm the oxide interface and affect the device's operation [30].

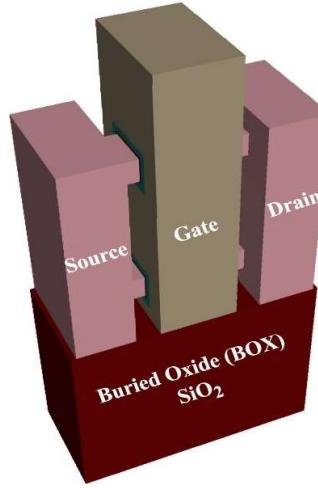

#### 1.4.12 Punch Through Effect

Fig. 1.13: Effect of the punch through in the MOSFET [18].

The punch through effect happens in a MOSFET when the depletion areas between the source/channel and the channel/drain unite to form a single depletion zone, as shown in Fig. 1.13. In this situation, the drain current is not controlled by the gate voltage, and it rapidly rises with the drain voltage. Punch through effect can be lessened by increasing substrate doping, using thinner oxides, and using junctions with shallower depths [35].

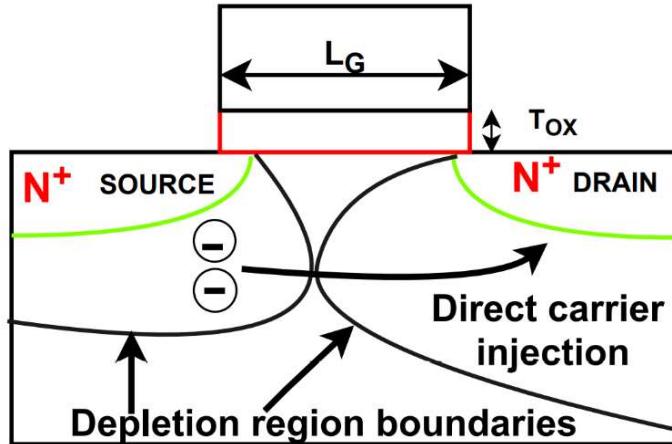

## 1.5 Multigate Architectures

In order to further reduce the MOSFET size and improve control over the channel, multi-gate (MuG) based MOSFETs are crucial. Moreover, to obtain the SS close to the Boltzmann tyranny of 60 mV/decade, multi-gate (MuG) architectures are proposed. Double gate [36], [37], trigate [38], and gate-all-around FETs [39]–[42] are some examples of MuG FETs and are shown in Fig 1.14. In double gate, the gate covers the channel in top and bottom directions. The gate covers both sides and the top of the channel in trigate structures. In gate all around (GAA) structures, the gate wraps around the channel on all sides. For scaling feasibility, the GAA topologies are the most promising for ultimate MOSFET scalability. The GAA structures offer the best controllability over the gate as the gate wraps around the channel in all directions. SCEs such as SS, DIBL,  $V_{th}$  roll-off, etc., are thereby greatly diminished in GAA nanowire (NW)/nanosheet (NS) MOSFETs, bringing SS closer to the desired 60 mV/decade limit.

Fig. 1.14: Various Multigate FET architectures [36].

### 1.5.1 Fin Field Effect Transistor (FinFET):

Intel was the first significant semiconductor company to commercialise 14 nm FinFET technology in 2014. On a silicon-on-insulator (SOI) or bulk silicon wafer, a Fin shape channel is etched and patterned to create a FinFET. Unlike MOSFETs, where the channel is solely controlled by one gate, FinFETs use gate structures which regulate the channel in three directions. As a result, thin fin can be regulated by the gate more effectively than planar MOSFETs. FinFETs have far better gate control than planar MOSFETs, which significantly

reduces leakage current. In FinFETs, the effective area of the channel is increased, resulting in greater drive current compared to the planar MOSFET [37], [43]. As a result, FinFET enables a large packing density of ICs [44]. Moreover, technology giants like TSMC announced the manufacturing of FinFET at advanced (7 nm) technology nodes [45]. However, at these lower nodes, disadvantageous SCEs like threshold voltage roll-off, SS degradation, DIBL, increased power consumption, and higher parasitic capacitances are raised. Moreover, scaling of FinFET became difficult for sub-5-nm nodes as it possesses fabrication difficulties and reliability issues.

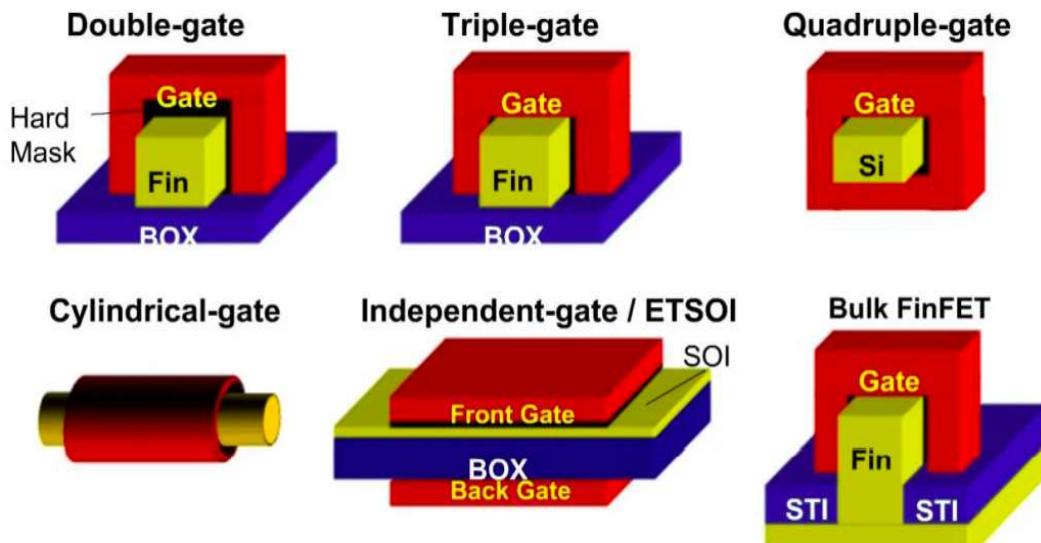

### 1.5.2 GAA Nanosheet FETs

Advanced multi-gate architectures such as GAA nanosheet FET (NSFET) transistors are proposed (Fig. 1.15) to continue the scaling for sub-5-nm nodes [39]. The GAA FETs received a lot of attention in recent years owing to their superior electrical performance. Interest in NS architectures has increased as a result of Intel, IBM, Global Foundry, and IMEC's announcement that they are going to adapt the GAA FETs into their IC fabrication [46]. As the gate covers the channel in all directions, superior gate control, lower power, minimizing the effect of drain effect on channel electrostatics and reduced leakage in GAA NS transistors can be achieved by using GAA FETs [47], [48]. Under the same footprint (FP), compared to FinFET, the GAA NSFET can reduce SCEs and improve device performance [49].

Fig. 1.15: GAA Nanosheet FET.

As a result, the GAA FETs promote optimal performance and ensure the scaling of the transistor for future technology nodes to manifest Moore's law.

## 1.6 Motivation

Multi-gate structures are proposed in the literature to improve device performance. Fin-shaped Field Effect Transistor (FinFET) was ideal for sub-22-nm technology nodes. However, it is shown that for sub-7-nm node technologies, the scaling feasibility of FinFET is questionable and more prone to SCEs. As a result, researchers came up with a solution for the gate all around (GAA) structures such as Nanosheet FETs. Major industry giants announced that Nanosheet FETs are going to be adopted by their fabrication units.

The GAA Nanosheet FET is proven to be capable of continuing Moore's law for sub-5-nm technology nodes. Though various literature is available on Nanosheet FET [49]–[53], the impact of device geometry on Nanosheet FET and its circuit applications needs to be addressed in detail. Further, semiconductor devices are meant to be used at various temperatures [54]. As the nanoscale devices are very much sensitive to temperature, the effect of temperature at both device and circuit levels needs to be addressed to estimate the robustness of Nanosheet FET towards thermal variations.

Furthermore, while adding more sheets in NSFET might enhance drive current in GAA devices, but taller fin devices complicate the manufacturing process and add parasitic capacitances. Also, despite having greater gate electrostatic control, GAA FETs must minimize the channel width per layout footprint ( $W_{eff}/FP$ ) while scaling. So, to obtain enhanced performance under the same FP, the different device engineering techniques, like structural engineering along with high-k gate stack, need to be explored on Nanosheet FET to further optimize the performance. Also, it is highly essential to study circuit behaviour in high-frequency applications with optimized Nanosheet FET by incorporating various device engineering at the device level.

## 1.7 Novelty of Overall Proposed Work

1. The geometry of the nanosheet plays a crucial role on the performance of the device. It is highly essential to address the impact of geometry and process parameters on Nanosheet FET (NSFET). Thus, GAA Nanosheet FET, according to the N5 [65] criteria, is designed and analysed its performance variations towards varied geometrical and process parameters.

2. Further, Analysis of analog/RF performance of the device is essential to estimate the device's suitability for analog/RF circuit applications. Also, the impact of geometry in high frequency circuit applications needs to be explored. To address the gap in the existing literature, which

mainly focuses on device level analysis, the circuit-level performance analysis of GAA nanosheet FET is carried out with varied geometrical parameters.

3. Moreover, semiconductor devices are sensitive to variations in temperature. The impact of temperature on the multigate FETs is addressed by some researchers. However, none has addressed the impact of temperature on NSFET in high frequency circuit applications. Thus, the impact of temperature on nanosheet FET for CMOS circuit applications is demonstrated at elevated temperatures.

4. To continue the scaling of NSFETs, the effective area ( $W_{eff}$ ) per footprint (FP) ( $W_{eff}/FP$ ), needs to be reduced, which affects the performance of the device with scaling. Thus, there is a need to improve the device's on current without increasing the FP by using device engineering such as structural engineering and high-k gate stack engineering. To increase the  $W_{eff}$  under the same FP, the CombFET is designed by combining Fin-like interbridge with nanosheets. Moreover, the performance is compared for both CombFET and NSFET devices for CMOS Circuit Applications.

## 1.8 Device Simulation

The 3-D Cogenda Visual Technology Computer Aided Design (TCAD) device simulator [55] is utilised in this thesis study to generate and simulate various device architectures. The TCAD are used in VLSI technology to model the electrical, thermal, optical, and electronic aspects of semiconductor devices.

These simulations are quite useful for figuring out how the device functions by solving physics-based equations. Particularly, simulators are a group of TCAD tools. It helps process and device engineers to comprehend semiconductor devices' manufacturing and reliability. It supports 2-D and 3-D simulation flows, as well as a variety of materials, including silicon and III-V compound semiconductor devices. Industries are constrained by time and financial constraints. Therefore, producers must create new process nodes quickly. Because of this, simulation tools make it easier to design process flows and optimise devices before wafer processing and manufacture. Without having to construct the devices, the physics, operation, and performance of the device may be immediately investigated using TCAD tools, thus saving time and money during the research and development process.

Fig. 1.16: Simulation process from device generation to outputs extraction.

The fully coupled Poisson and continuity equations are systematically solved by the Cogenda Visual TCAD device simulator to determine the various physical quantities required to undertake DC, AC, and transient analysis on the semiconductor device under consideration. The scheme command file is used to send all structural parameters, including dimensions, doping, and others, into the simulator, as illustrated in Fig.1.16. Without needing to manufacture the device, these simulation techniques can be used to estimate the device's realistic performance and the impact of process variation. These simulation tools significantly reduced the cost of designing, increasing the efficiency and speed of the production process. In order to effectively estimate the performance of the device, appropriate physical models must be included.

## 1.9 Workflow

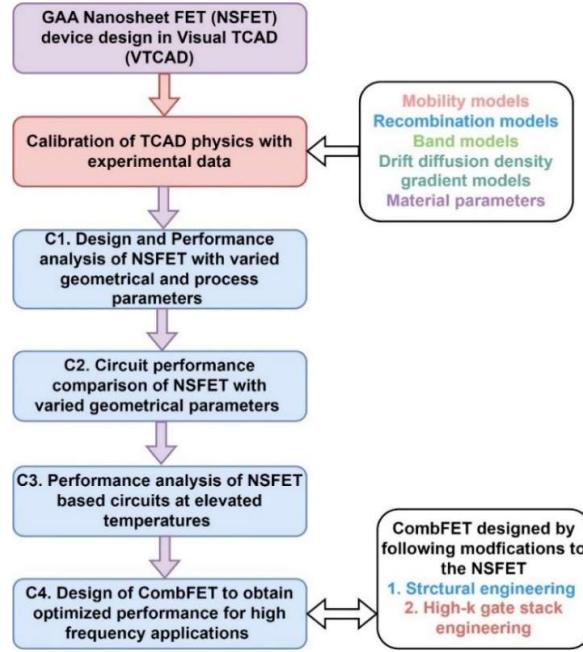

The workflow of overall research is depicted in Fig. 1.17. Initially, the GAA nanosheet FET is designed in Visual TCAD and calibrated the device physics with experimental data. The calibrated physics is incorporated into the device physics to carryout the subsequent device simulations. For all the analysis, the Silicon (Si) material is considered. For circuit level analysis, lookup table based Verilog-A model is used to generate the symbols of the device and circuit simulations are performed in the Cadence tool. The contributions (C1-C4) are given in Fig. 1.17.

Fig. 1.17: Workflow along with contributions (C1-C4).

## 1.10 Research Specifications

The specifications of the research are as follows:

- All the device design and simulations are carried out using 3-D Cogenda Visual Technology Computer Aided Design (TCAD) device simulator [55].

- The device is designed according to IRDS standards [65], [134]. The parameters are listed below.

- Length of the gate - 16 nm

- Source/Drain doping ( $\text{cm}^{-3}$ ) -  $10^{20} (\text{cm}^{-3})$

- Doping of the channel ( $\text{cm}^{-3}$ ) -  $10^{15} (\text{cm}^{-3})$

- EOT ( $T_{\text{SiO}_2} + (\epsilon_{\text{SiO}_2}/\epsilon_{\text{HfO}_2}) \times T_{\text{HfO}_2}$ ) - 0.78 nm

- Length of Drain/Source (nm) - 12 nm

- Height of the gate - 60 nm

- For all the circuit simulations are carried out in Cadence tool [120] through lookup table based Verilog - A models.

## 1.11 Research Objectives

The objectives of the research are as follows:

1. To design and analyze the performance variations of GAA Nanosheet FET with Varied Geometrical and Process Parameters at 5-nm technology node.

2. To analyze the circuit-level performance of GAA Nanosheet FET with varied geometrical parameters.

3. To evaluate the robustness of Nanosheet FET based circuits at elevated temperatures as the nanoscale devices' behaviour is very sensitive to temperature fluctuations.

4. To optimize the Nanosheet FET using both structural engineering with high-k gate stack to obtain better performance parameters like on current ( $I_{ON}$ ), ON/OFF current ratio ( $I_{ON}/I_{OFF}$ ) and performance assessment of optimized Nanosheet FET in high frequency integrated circuit applications like ring oscillator to get high frequency of oscillations ( $f_{osc}$ ).

## 1.12 Thesis Organization

The thesis presents the Design and Analysis of Modified GAA Nanosheet FET Based Circuits for High Frequency Applications. The thesis is organized into seven chapters. The following section gives a summary of the chapters.

Chapter 1: Presents an introduction to the work, motivation, and problem statement.

Chapter 2: Explores a literature overview of the present state-of-the-art on device engineering such as structural engineering, high-k gate stack, and performance analysis of NSFET and circuit applications. This chapter concludes with a brief outline of the thesis.

Chapter 3: Design and performance evaluation of NSFET with varied geometrical and process parameters.