# **Improvised Space-Vector Pulse Width Modulation Schemes for Four-Level Open-End Winding Induction Motor Drives**

Submitted in partial fulfillment of the requirements

for the award of the degree of

**Doctor of Philosophy**

by

**Suresh Lakhimsetty**

**(Roll No. 715015)**

Supervisor

**Dr. V. T. Somasekhar**

Professor

**Department of Electrical Engineering**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

(An Institute of National Importance)

**Warangal - 506004, Telangana State, India**

**November – 2019**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

WARANGAL-506004**

**CERTIFICATE**

This is to certify that the thesis entitled "**Improvised Space-Vector Pulse Width Modulation Schemes for Four-Level Open-End Winding Induction Motor Drives**", which is being submitted by **Mr. Suresh Lakhimsetty** (Roll No. 715015), is a bonafide work submitted to National Institute of Technology, Warangal in partial fulfilment of the requirement for the award of the degree of *Doctor of Philosophy* in *Department of Electrical Engineering*. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. V. T. Somasekhar**

(Supervisor)

Professor

Department of Electrical Engineering

National Institute of Technology

Warangal – 506004

Date:

Place: Warangal

## **Approval Sheet**

This Thesis entitled "**Improvised Space-Vector Pulse Width Modulation Schemes for Four-Level Open-End Winding Induction Motor Drives**" by **Suresh Lakhimsetty** is approved for the degree of Doctor of Philosophy

### **Examiners**

---

---

---

### **Supervisor**

Dr. V. T. Somasekhar

Professor

### **Chairman**

Dr. S. Srinivasa Rao

Professor & Head,

Department of Electrical Engineering,

NIT Warangal

Date:

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Improvised Space-Vector Pulse Width Modulation Schemes for Four-Level Open-End Winding Induction Motor Drives**" is a bonafide work done by me under the supervision of **Prof. V. T. Somasekhar, Department of Electrical Engineering, National Institute of Technology Warangal** and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission not been taken when needed.

**Suresh Lakhimsetty**

**(Roll No.715015)**

Date:

Place: Warangal

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor **Prof. V. T. Somasekhar**, for his continuous support of my Ph.D work and related research, for his patience, motivation, and immense knowledge. His knowledge, suggestions and discussions helped me to become a capable researcher. His guidance helped me in all the time of my research and writing of this thesis.

I thank **Prof. N. V. Ramana Rao**, Director, National Institute of Technology Warangal and **Prof. S. Srinivasa Rao**, Head, Department of Electrical Engineering for all the support and facilities offered by them.

My sincere thanks to my Doctoral Scrutiny Committee members, **Dr. M. Sailaja Kumari**, Professor, Department of Electrical Engineering, **Dr. Ch. Venkaiah**, Associate Professor, Department of Electrical Engineering and **Dr. C. B. Rama Rao**, Professor, Department of Electronics and Communication Engineering for their advice during the progress of this research work.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal. They have always been encouraging and supportive.

I take this opportunity to convey my special thanks to Dr. B. Venugopal Reddy, Associate Professor, NIT Goa, co-scholars of EED, Dr. K. Ramsha, Dr. M. Vishnu Prasad, Dr. Venu Sonti, Mr. M. Hareesh, Mr. K. Kiran Babu, Dr. T. Ratna Rahul, Dr. K. V. Praveen Kumar, Mr. Sumon Dhara, Mr. P. Hema Kumar, Mr. P. Manoj Kumar, the P.G. students of EED, Mr. S. Nagarjun, Mr. S. V. Siva Prasad, Mr. Rajendra Singh Rathore, and Dr. N. Prasad, Department of ECE for their technical and moral support.

I gratefully acknowledge my wife **Mrs. Durga** for her continuous support and encouragement, towards my fruitful research work and life success.

My special, sincere acknowledge and heartfelt gratitude to my parents **Shri. Byragi & Smt. Ragamma**, my brothers **Mr. Samba Siva Rao, Mr. Venu Gopal Rao**, for their sincere prayers, blessings, constant encouragement and moral support rendered to me throughout my journey, without which my research work would not have been possible. I heartily acknowledge all my relatives for their love and affection towards me.

Finally, I would like to express my sincere thanks to all those who helped me directly or indirectly in the progress and completion of this research work.

**Suresh Lakhimsetty**

## ABSTRACT

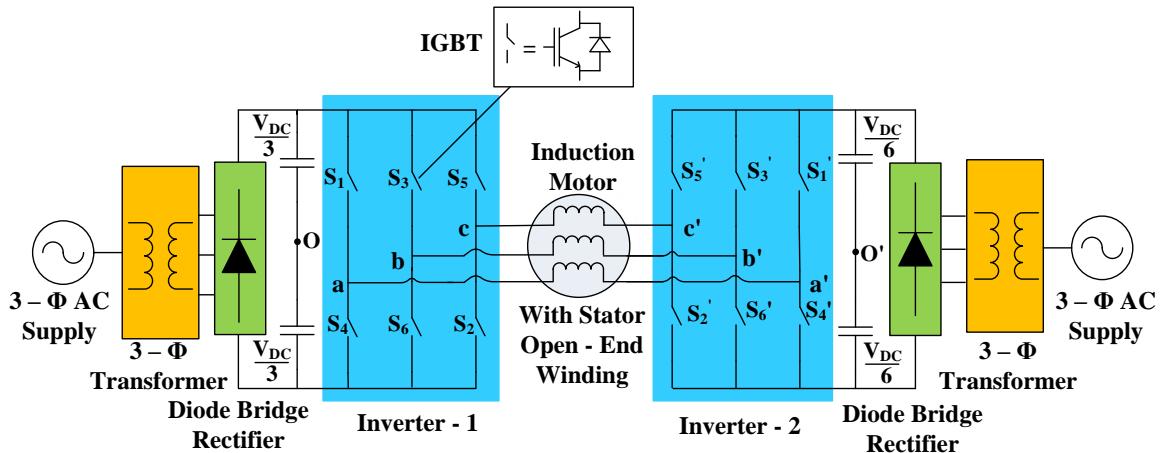

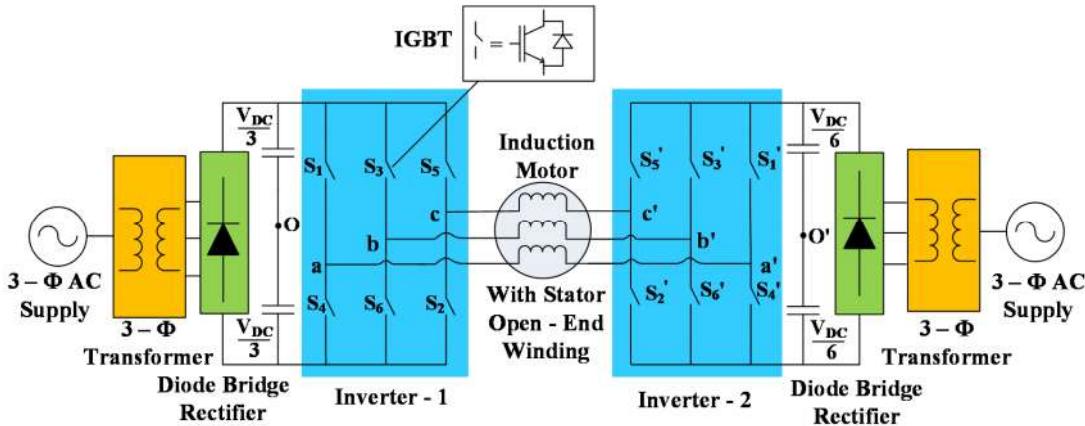

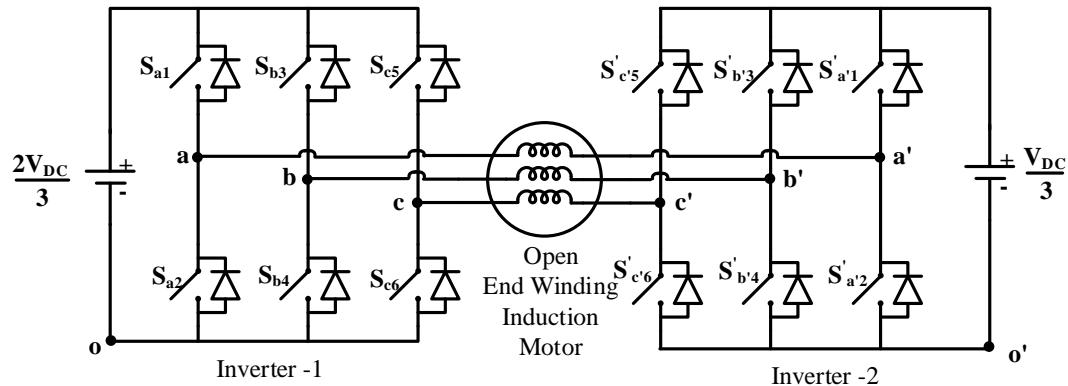

In this thesis, the Open-End Winding Induction Motor (OEWIM) drive is considered for achieving the multilevel operation. The OEWIM drive is realized by removing the star or delta connections of the stator winding of an induction motor and feeding it with two two-level Voltage Source Inverters (VSIs) from either side. In the present thesis, the VSIs are operated with two different DC input voltages, which are in the ratio of 2:1, to achieve four-levels across each motor phase winding. Thus, this drive configuration is named as the four-level Open-End Winding Induction Motor Drive.

The four-level OEWIM drive circuit configuration mainly suffers from two problems. They are: (i) the lower dc-link voltage capacitor is overcharged by its counter-part, i.e. the higher dc-link voltage capacitor (ii) the presence of zero-sequence current (ZSC) in the motor phase windings. However, the ZSC can be avoided by denying a path for the circulation of zero-sequence current by using isolated dc-power supplies.

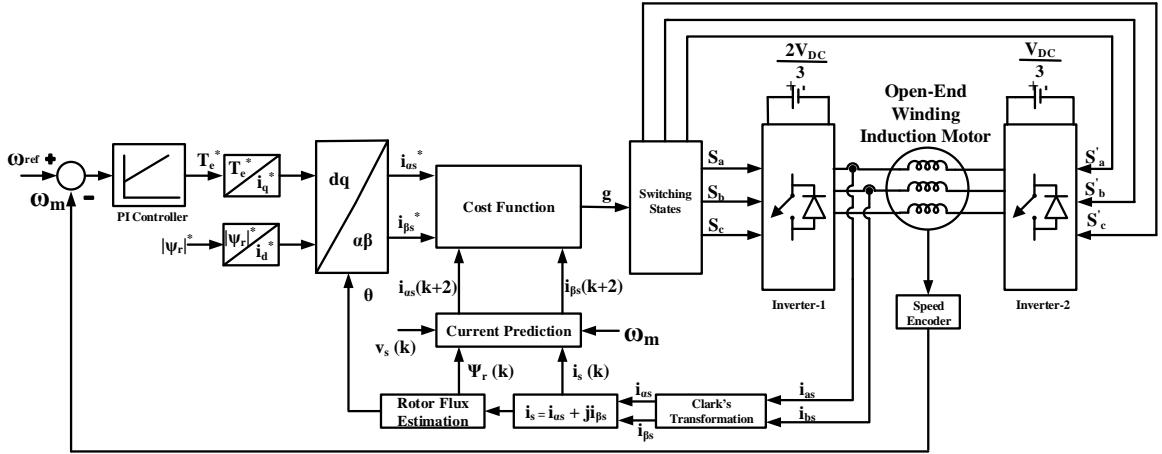

This thesis investigates about the applicability of various Space-Vector Pulse Width Modulation (SVPWM) schemes for two circuit topologies of the four-level OEWIM drive (of which, one circuit is a slightly improvised version of an existing topology). The proposed SVPWM techniques avoid the overcharging of the lower-voltage dc-link capacitor and improve the drive performance. A closed-loop control strategy, based on Model Predictive Control (MPC), is also proposed to improve the performance of the OEWIM drive.

To improve the performance of the four-level OEWIM drive, four variants of *Discontinuous-Decoupled SVPWM (DDSVPWM)* techniques are proposed. It is known that, the Discontinuous-SVPWM techniques reduce the switching power loss in inverters. However, lack of structural symmetry of the power circuit renders it unwieldy to devise these SVPWM schemes. Chapter-2 explores the applicability of the Discontinuous-Decoupled SVPWM techniques for the four-level OEWIMD, without compromising on the waveform symmetries. It is shown that the proposed SVPWM techniques, while avoiding the overcharging

phenomenon of the low-voltage dc-link capacitor, also lower the  $dv/dt$  across the motor phase windings.

Three variants of SVPWM strategies are proposed in Chapter-3 for the four-level OEWIM drive with two isolated dc-power supplies to reduce the switching power loss and to improve the drive performance. In the proposed SVPWM schemes, the inverter, which is operated with the lower dc-link voltage is clamped to the nearest sub-hexagonal centre (NSHC), while the other inverter is switched around it. The proposed SVPWM schemes, apart from avoiding the overcharging phenomenon and achieving all waveform symmetries, reduce power loss in the dual-inverter system (compared to the Discontinuous Decoupled SVPWM schemes available in chapter-2).

A nested rectifier-inverter topology with two dc-power supplies (as against three reported in the earlier literature) is proposed in Chapter-4 to improve the reliability of the four-level OEWIM drive. The unwanted phenomenon of overcharging the low-voltage capacitor is avoided with this power circuit also. To suppress the zero-sequence currents, an SVPWM scheme is proposed and is named as *Nested Inverter Clamped Sample-Averaged Zero-Sequence Elimination (NICSAZE)*. The proposed NICSAZE-PWM scheme eliminates the zero-sequence currents in the average sense and reduces the power loss in the dual-inverter system.

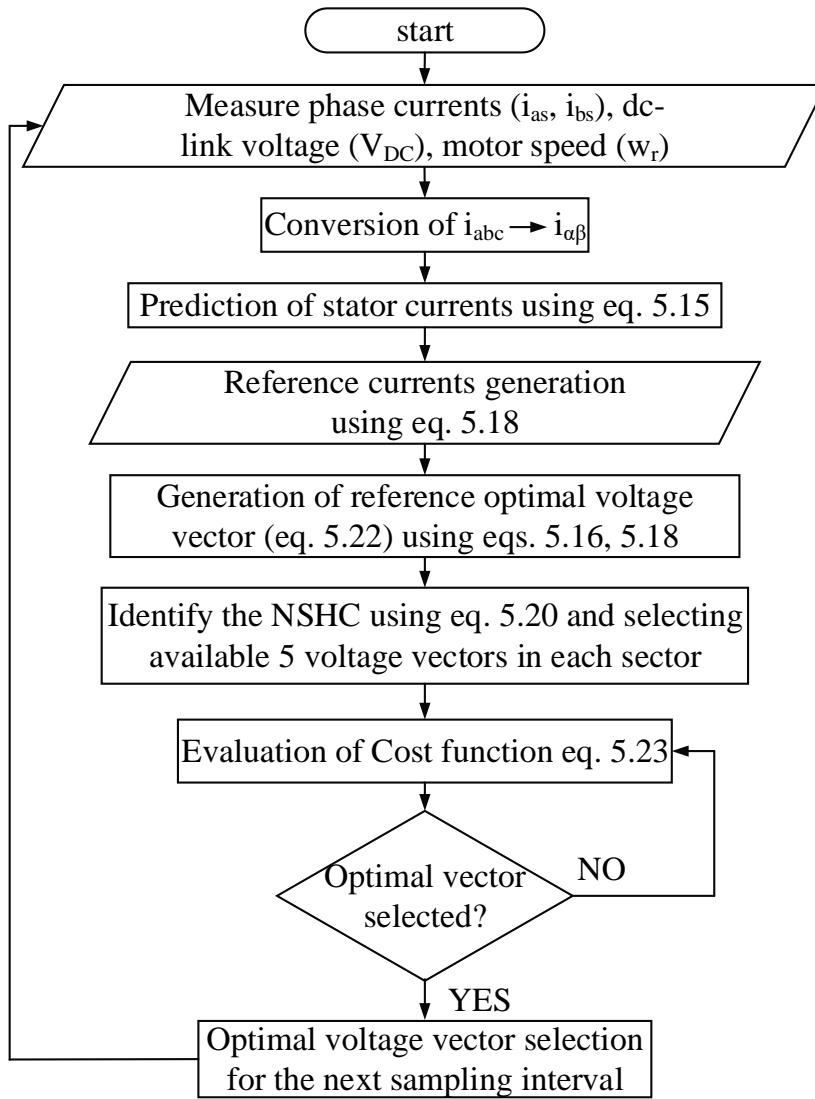

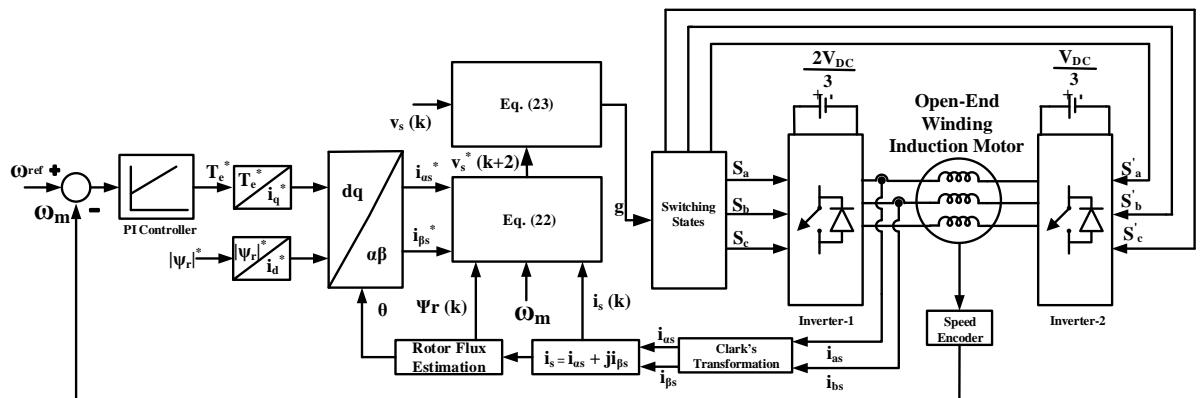

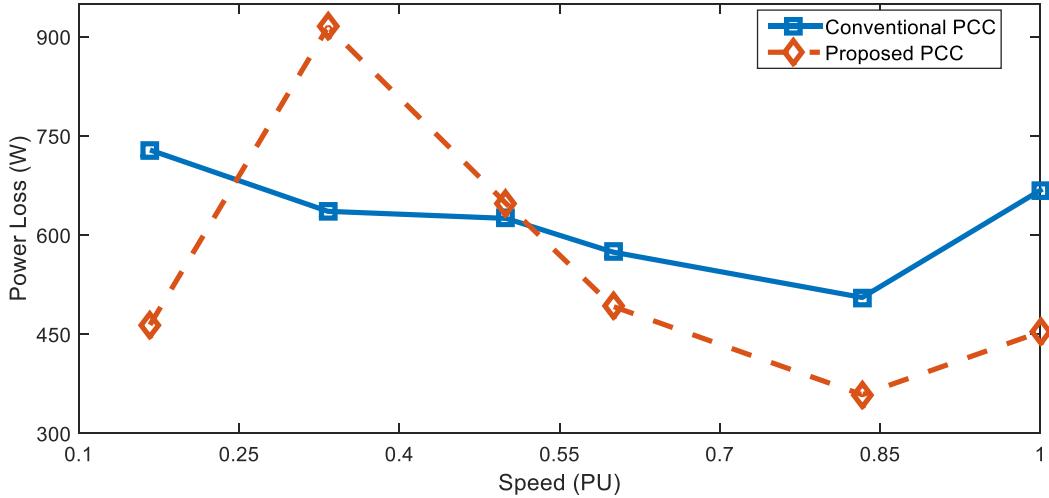

An improvised Predictive Current Control (PCC) algorithm, which belongs to the genre of MPC, is proposed to control the load currents of the four-level OEWIM drive in Chapter-5. The conventional PCC uses all of the available 37 candidate voltage vectors of the dual-inverter system to select the optimal voltage vector. In contrast, the proposed PCC (which utilises the concept of NSHC described in Chapter-3) requires the testing of only 5 candidate voltage vectors for the selection. Thus, the proposed PCC results in a considerable alleviation of the computational burden on the control platform. It is also shown that, compared to the conventional PCC, the proposed PCC technique results in the reduction of power loss incurred in the dual-inverter system for a considerable portion of the operating range of the drive.

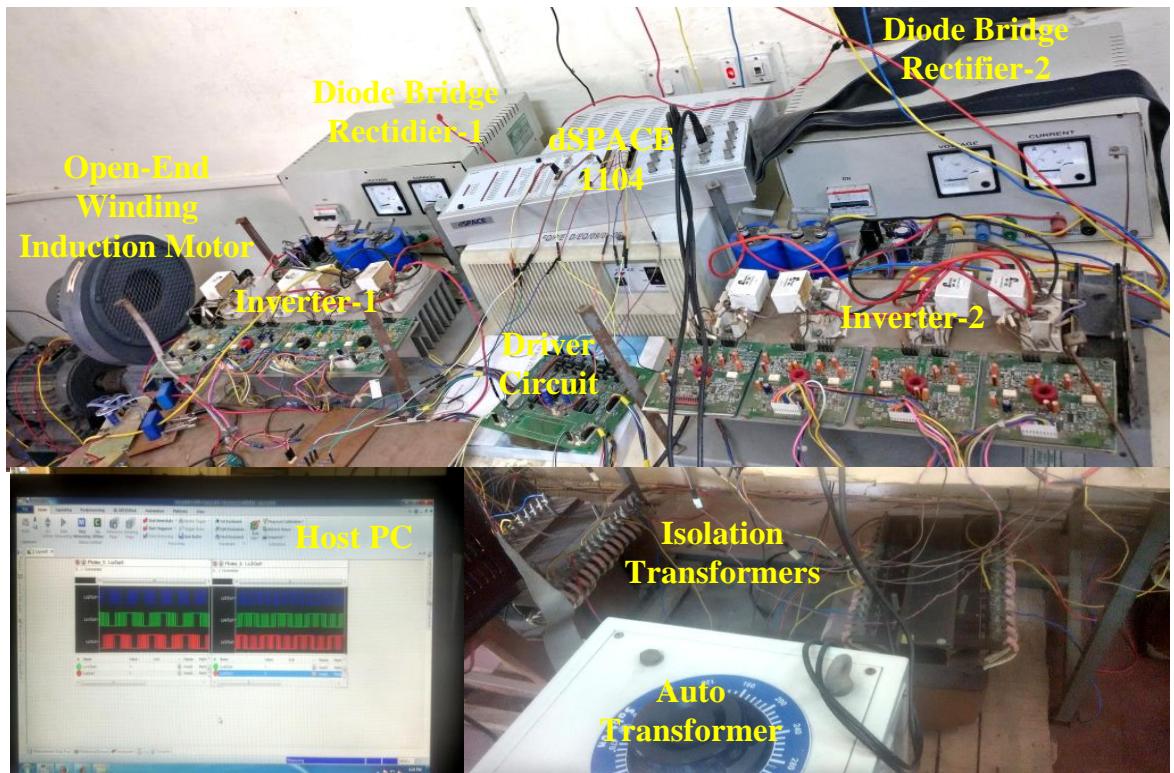

All the PWM schemes, circuit topologies and the closed-loop control strategies proposed in this thesis are first simulated using *MATLAB/SIMULINK* software and the results are then validated by implementing these schemes on a 5-HP, 400 V, 50 Hz, 1445 RPM, three-phase open-end winding induction motor. The experimental work presented in this thesis is carried out using the *dSPACE1104* control platform.

# CONTENT

|                                                                                                                                                |             |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>ACKNOWLEDGEMENTS .....</b>                                                                                                                  | <b>i</b>    |

| <b>ABSTRACT .....</b>                                                                                                                          | <b>iii</b>  |

| <b>CONTENT .....</b>                                                                                                                           | <b>vi</b>   |

| <b>List of Figures .....</b>                                                                                                                   | <b>ix</b>   |

| <b>List of Tables.....</b>                                                                                                                     | <b>xxi</b>  |

| <b>List of Symbols.....</b>                                                                                                                    | <b>xxii</b> |

| <b>List of Abbreviations .....</b>                                                                                                             | <b>xxvi</b> |

| <b>Chapter 1: Introduction.....</b>                                                                                                            | <b>1-1</b>  |

| 1.1    Background.....                                                                                                                         | 1-2         |

| 1.2    Literature Review.....                                                                                                                  | 1-5         |

| 1.2.1    Recent advances in MLIs.....                                                                                                          | 1-11        |

| 1.2.2    Open-End Winding Induction Motor drives.....                                                                                          | 1-13        |

| 1.2.3    Closed loop operation of OEWIMD .....                                                                                                 | 1-21        |

| 1.3    Applications, advantages and disadvantages of dual inverter fed OEWIND.....                                                             | 1-23        |

| 1.4    Motivation.....                                                                                                                         | 1-24        |

| 1.5    Objectives .....                                                                                                                        | 1-25        |

| 1.6    Organization of the thesis.....                                                                                                         | 1-26        |

| 1.7    Summary.....                                                                                                                            | 1-29        |

| <b>Chapter 2: Discontinuous Decoupled SVPWM Schemes for a Four-Level Open-End Winding Induction Motor Drive with Waveform Symmetries .....</b> | <b>2-1</b>  |

| 2.1    Introduction.....                                                                                                                       | 2-2         |

| 2.2    Mathematical Model of a Four-Level OEWIMD .....                                                                                         | 2-3         |

| 2.3    Discontinuous Decoupled SVPWM Strategies for Four-Level OEWIMD with Equal Duty .....                                                    | 2-8         |

| 2.4    Simulation and Experimental Results .....                                                                                               | 2-17        |

| 2.5    Comparative Analysis of DDPWM & CSPWM Strategies.....                                                                                   | 2-29        |

| 2.6    Conclusion .....                                                                                                                        | 2-38        |

| <b>Chapter 3: Single Inverter Switched SVPWM Schemes for a Four-Level Open-End Winding Induction Motor Drive .....</b>                         | <b>3-1</b>  |

| 3.1    Introduction.....                                                                                                                       | 3-2         |

|     |                                                                      |      |

|-----|----------------------------------------------------------------------|------|

| 3.2 | Principle of the Proposed Biasing SVPWM Scheme.....                  | 3-4  |

| 3.3 | Simulation & Experimental Results.....                               | 3-9  |

| 3.4 | Comparative Performance Analysis of Improvised SVPWM techniques..... | 3-21 |

| 3.5 | Conclusion .....                                                     | 3-27 |

**Chapter 4: A Four-Level Open-End Winding Induction Motor Drive with a Nested Rectifier-Inverter Combination with Two DC Power Supplies .....** 4-1

|        |                                                                             |      |

|--------|-----------------------------------------------------------------------------|------|

| 4.1    | Introduction.....                                                           | 4-2  |

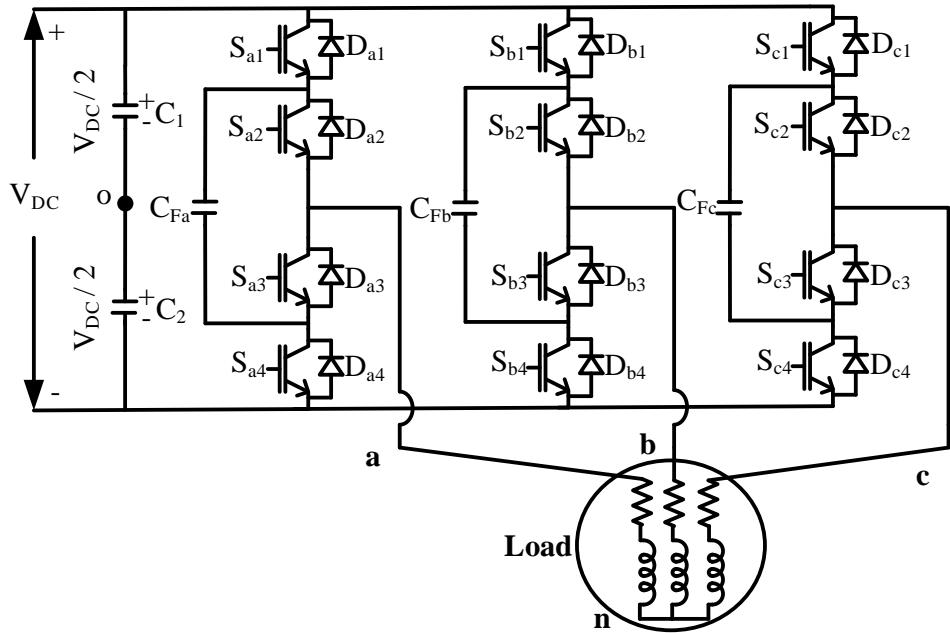

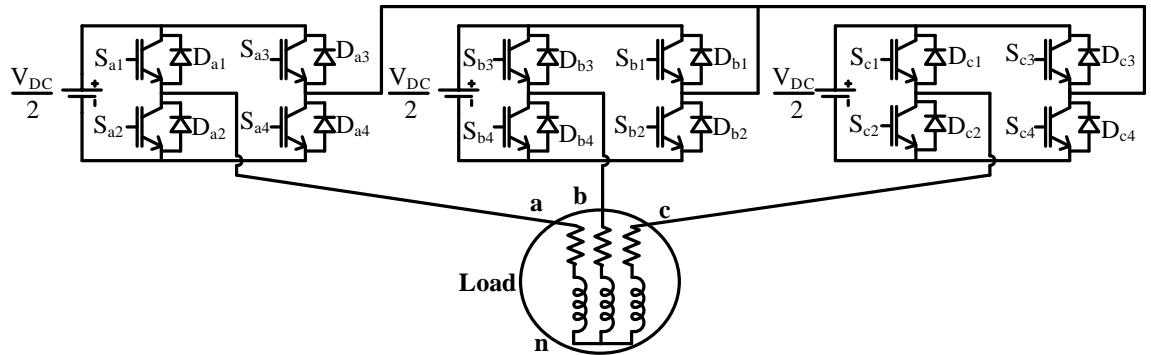

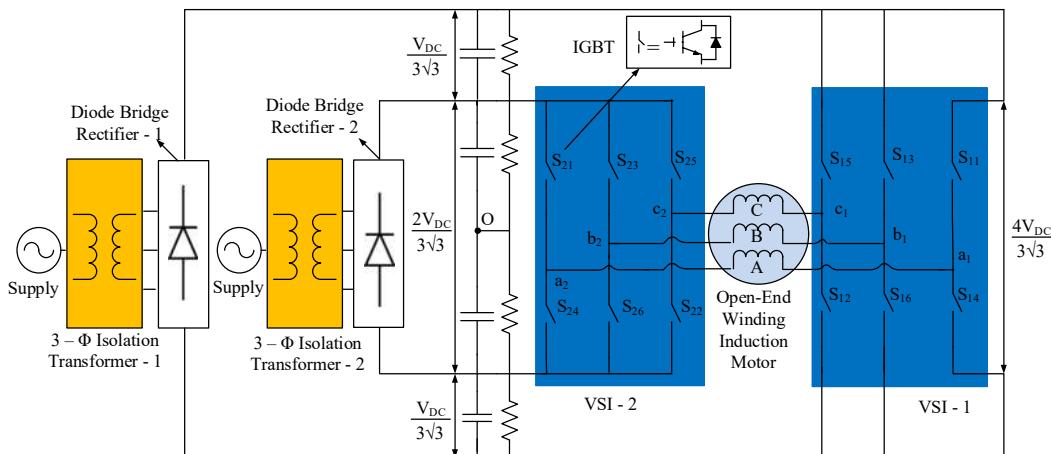

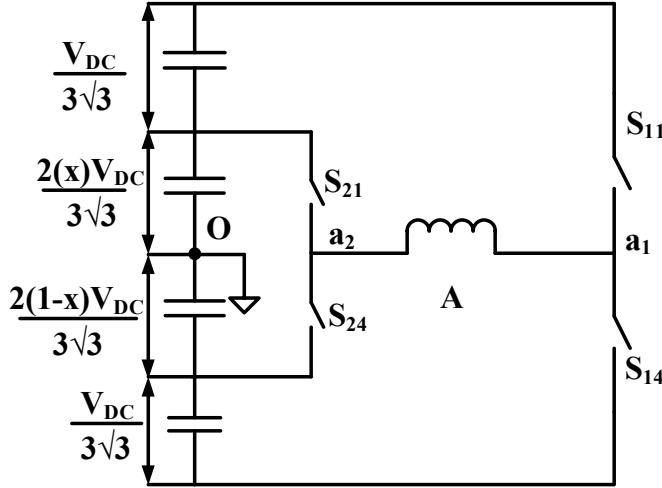

| 4.2    | New Nested Rectifier-Inverter Configuration for four-level OEWIMD.....      | 4-3  |

| 4.2.1. | Description of topology .....                                               | 4-3  |

| 4.2.2. | Avoidance of lower dc-link voltage capacitor overcharging.....              | 4-5  |

| 4.2.3. | Comparison with other 4-L multilevel inverter topologies .....              | 4-7  |

| 4.3    | SVPWM Techniques For The Elimination Of Zero-Sequence Voltages.....         | 4-8  |

| 4.3.1. | DSAZE PWM Technique .....                                                   | 4-10 |

| 4.3.2. | NICSAZE SVPWM Strategy.....                                                 | 4-12 |

| 4.4    | Simulation and Experimental Results .....                                   | 4-16 |

| 4.4.1. | Simulation Results.....                                                     | 4-17 |

| 4.4.2. | Experimental Results.....                                                   | 4-20 |

| 4.4.3. | Fault tolerant capability of the proposed power circuit configuration ..... | 4-25 |

| 4.4.4. | Performance characteristics of the proposed topology .....                  | 4-27 |

| 4.5    | Conclusion .....                                                            | 4-30 |

**Chapter 5: An Efficient Predictive Current Control Strategy for a Four-Level Open-End Winding Induction Drive .....** 5-1

|       |                                                                                                   |      |

|-------|---------------------------------------------------------------------------------------------------|------|

| 5.1   | Introduction.....                                                                                 | 5-2  |

| 5.2   | Modeling of Four-Level OEWIM Drive .....                                                          | 5-3  |

| 5.3   | Conventional Predictive Current Controller for a Four-Level OEWIMD .....                          | 5-6  |

| 5.3.1 | Stator current prediction .....                                                                   | 5-6  |

| 5.3.2 | Generation of Reference Currents .....                                                            | 5-9  |

| 5.3.3 | Cost-function.....                                                                                | 5-9  |

| 5.4   | Predictive Current Controller for a Four-Level OEWIMD based on Nearest Sub-Hexagonal Centers..... | 5-10 |

| 5.4.1 | Selection of optimal voltage vector.....                                                          | 5-10 |

| 5.4.2 | Formulation of the Cost-function based on Voltage References .....                                | 5-13 |

| 5.5   | Simulation and Experimental Results .....                                                         | 5-15 |

|                                                                                       |            |

|---------------------------------------------------------------------------------------|------------|

| 5.6 Conclusion .....                                                                  | 5-25       |

| <b>Chapter 6: Conclusion and Future work of Research.....</b>                         | <b>6-1</b> |

| 6.1 Conclusion .....                                                                  | 6-2        |

| 6.1.1. Major Contributions of the Thesis .....                                        | 6-2        |

| 6.1.2. Minor Contributions of the Thesis .....                                        | 6-4        |

| 6.2 Future scope.....                                                                 | 6-4        |

| 6.2.1. Power Circuit Configurations for Open-End Winding Induction Motor Drives ..... | 6-4        |

| 6.2.2. Control strategies for Open-End Winding Induction Motor Drives .....           | 6-4        |

| <b>Appendix-I: Experimental set-up.....</b>                                           | <b>A-1</b> |

| <b>References.....</b>                                                                | <b>R-1</b> |

| <b>List of Publications.....</b>                                                      | <b>P-1</b> |

# List of Figures

| <b>Figure</b> | <b>Page</b>                                                                                                                                  |      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>No.</b>    | <b>Figure title</b>                                                                                                                          |      |

| Fig. 1.1      | Conventional two-level voltage source inverter                                                                                               | 1-3  |

| Fig. 1.2      | Inverter topologies based on supply techniques (a) Multilevel inverter with single-ended load (b) Dual-inverter with open-ended load         | 1-4  |

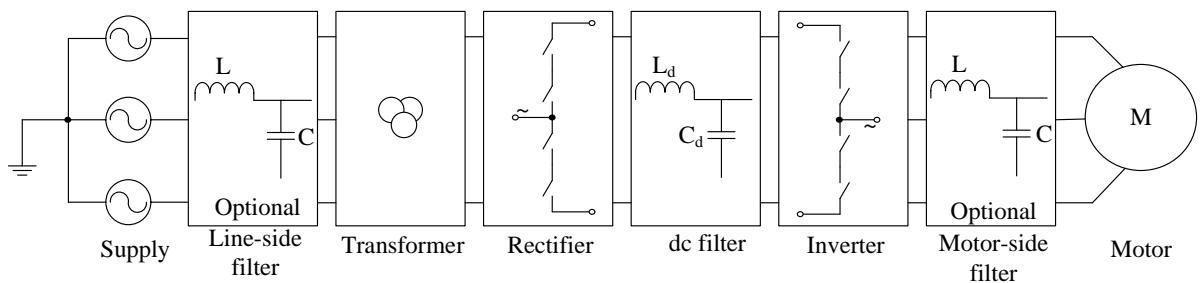

| Fig. 1.3      | General block diagram of industrial MV drive                                                                                                 | 1-6  |

| Fig. 1.4      | Three-level NPC MLI                                                                                                                          | 1-8  |

| Fig. 1.5      | Three-level FC MLI                                                                                                                           | 1-9  |

| Fig. 1.6      | Three-level CHB MLI                                                                                                                          | 1-10 |

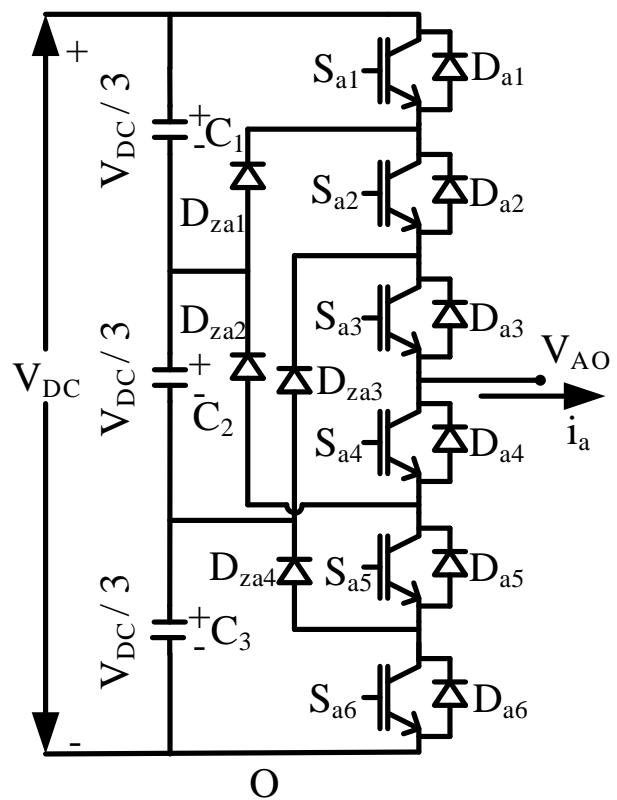

| Fig. 1.7      | Per-phase diagram of a four-level NPC MLI                                                                                                    | 1-10 |

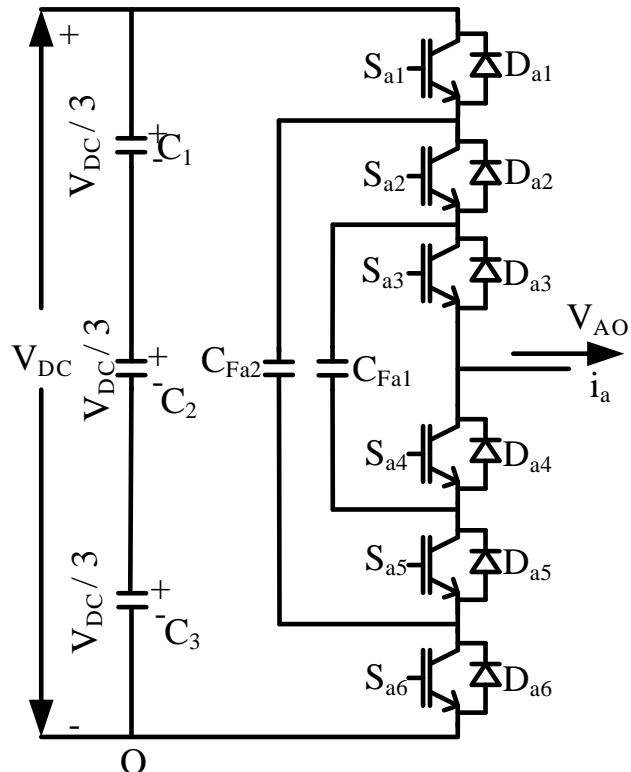

| Fig. 1.8      | Per-phase diagram of a four-level FC MLI                                                                                                     | 1-11 |

| Fig. 1.9      | Open-End Winding topologies for realization of three-level operation with symmetric power supplies. (a) Single dc-link (b) Isolated dc-links | 1-15 |

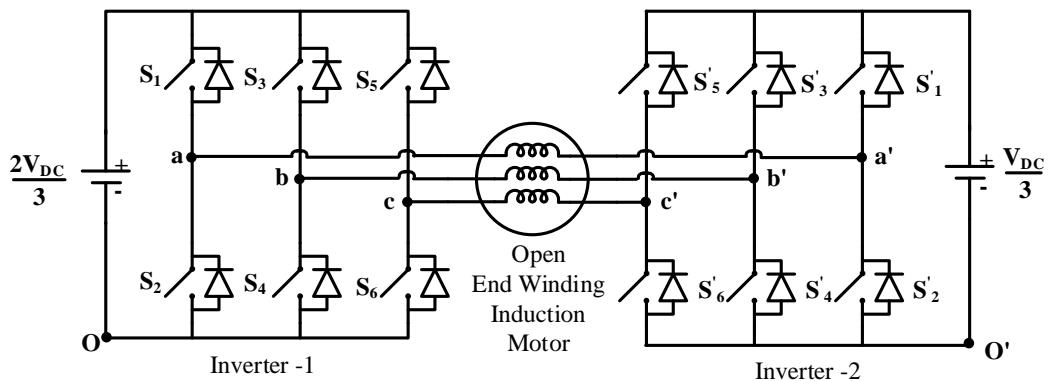

| Fig. 1.10     | Four-level OEWIMD with unequal dc-link voltages                                                                                              | 1-17 |

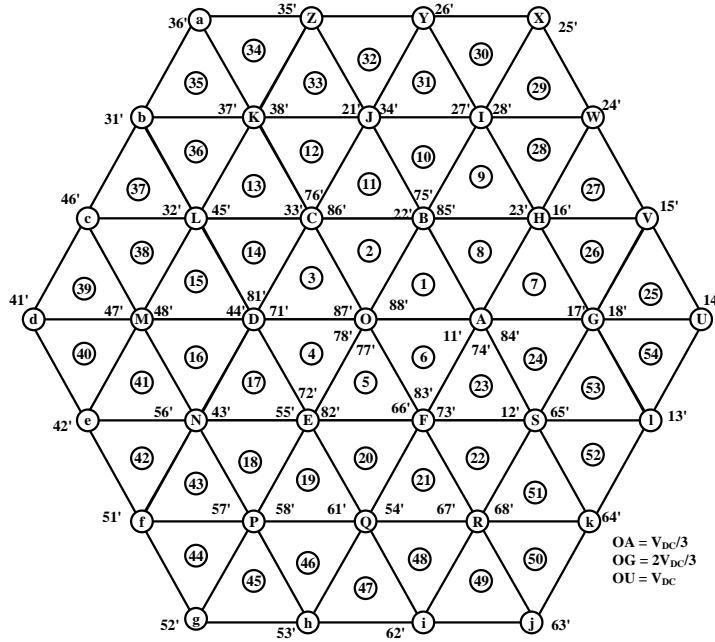

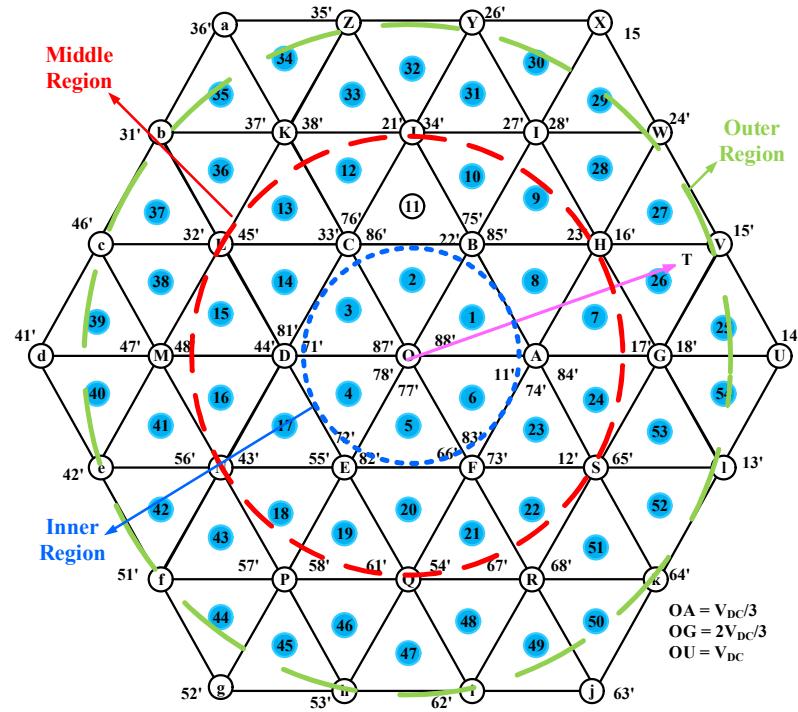

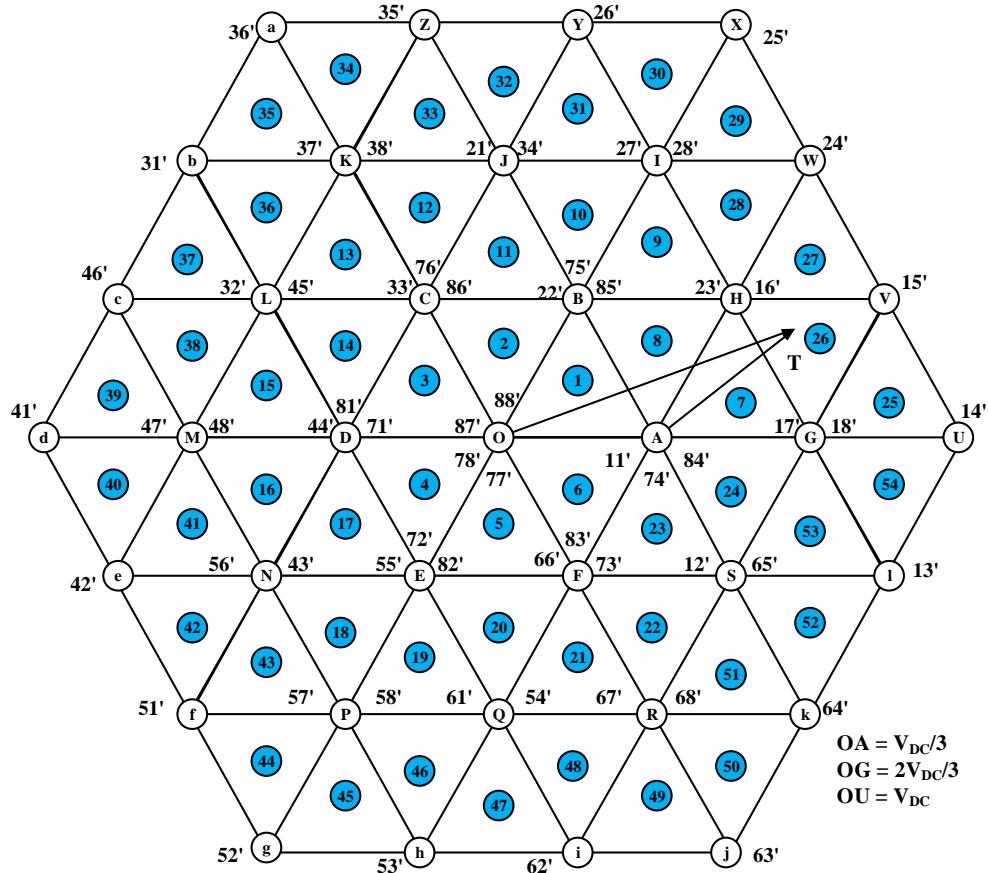

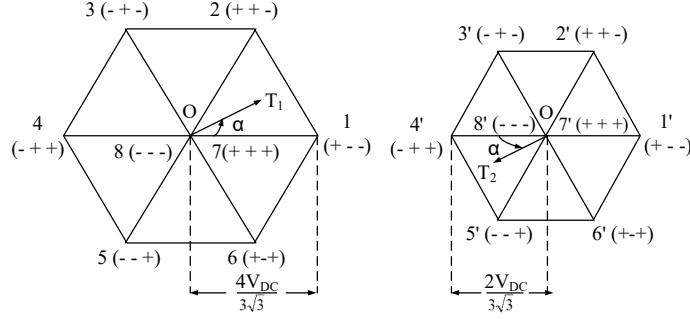

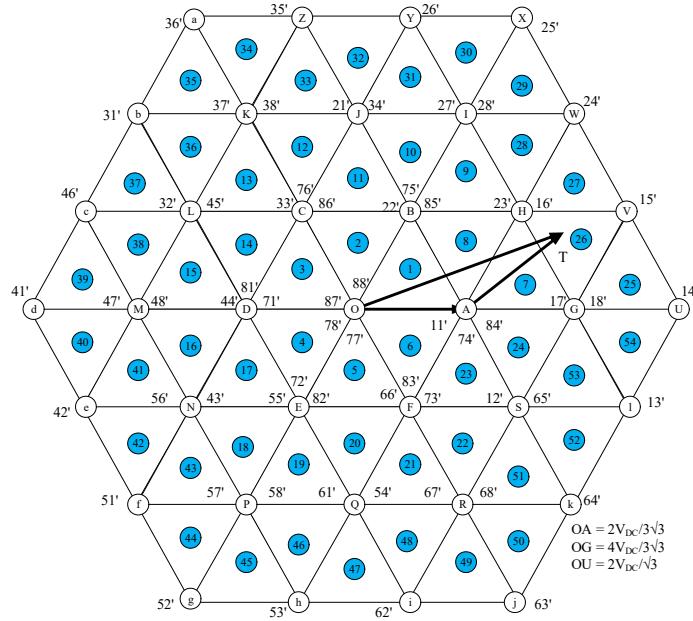

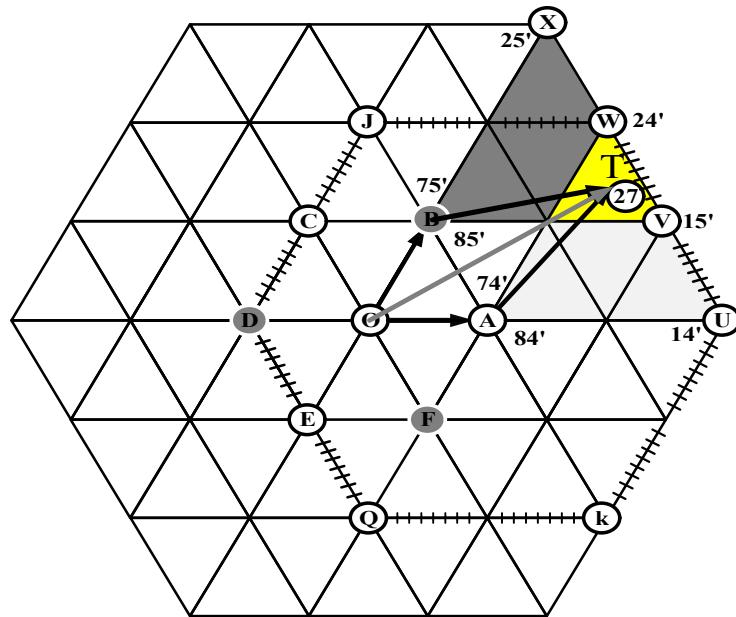

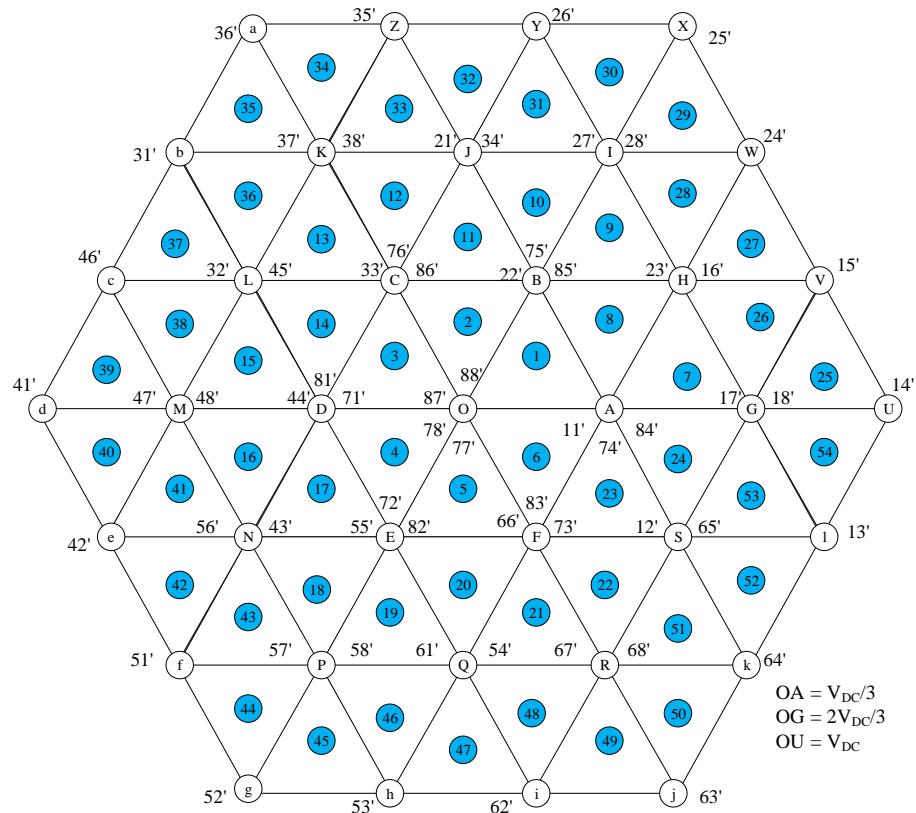

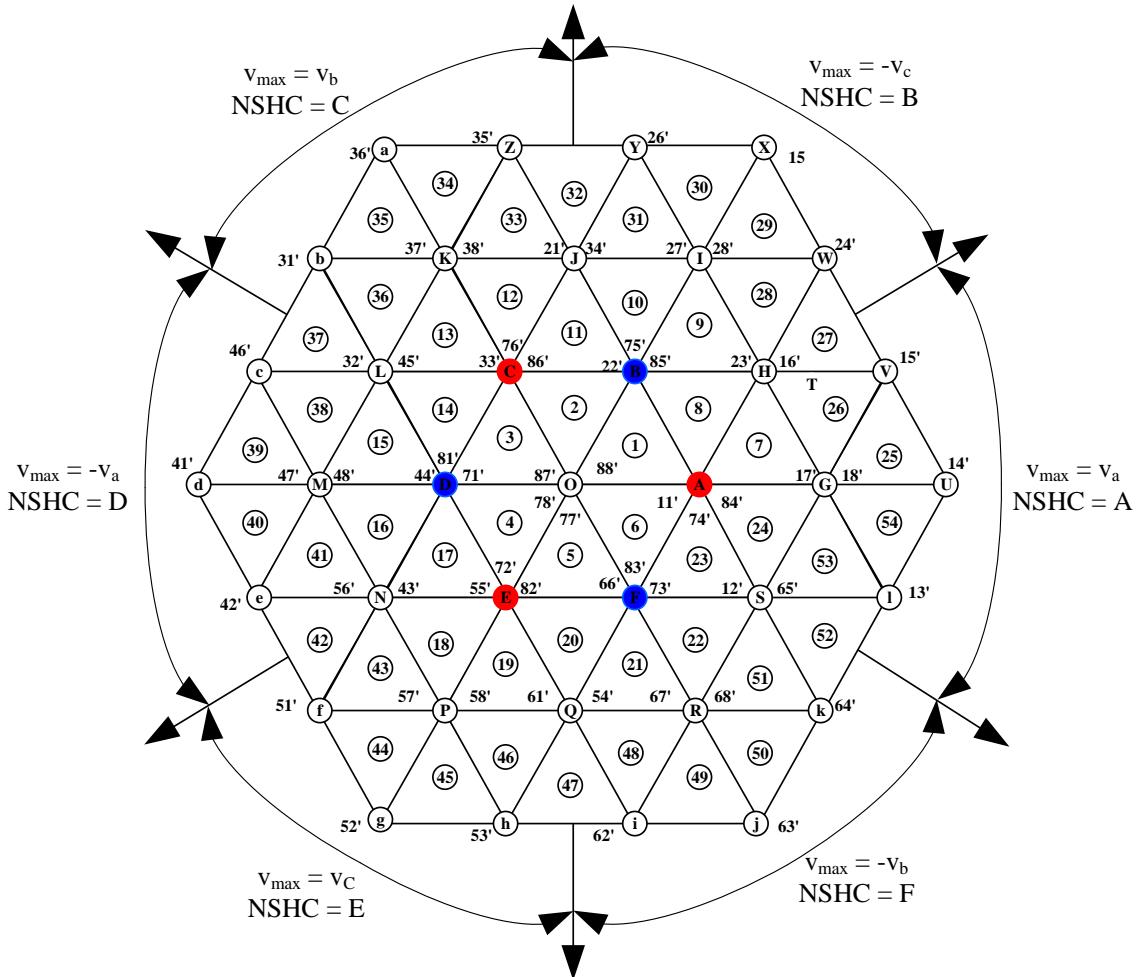

| Fig. 1.11     | Space vector diagram of four-level OEWIMD                                                                                                    | 1-18 |

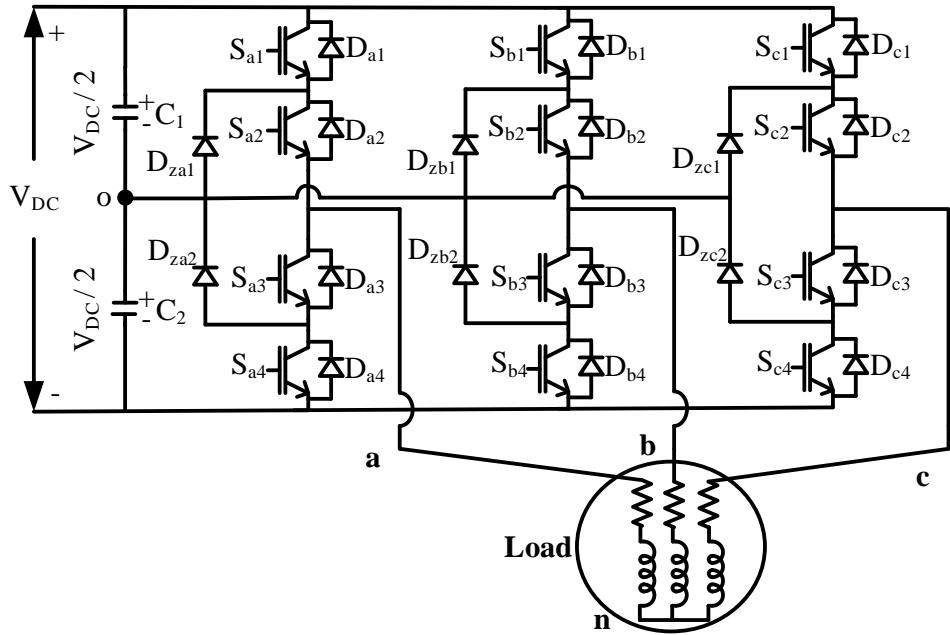

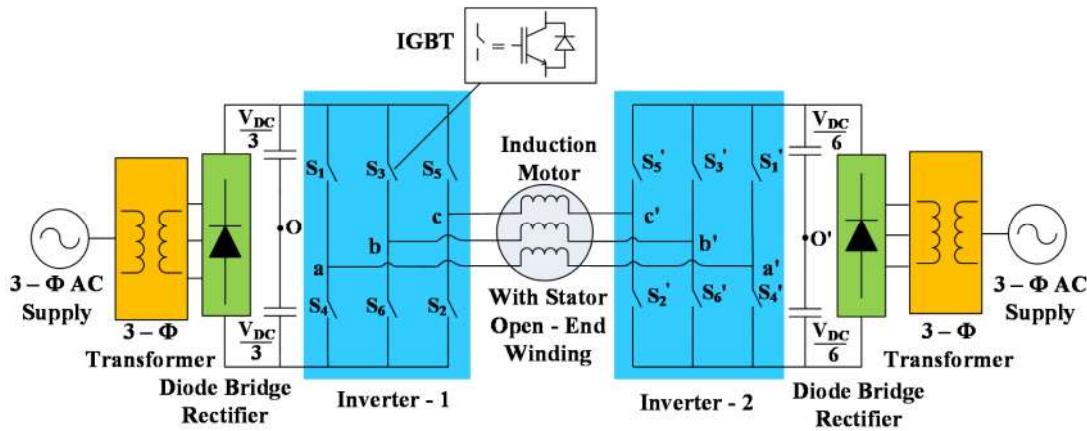

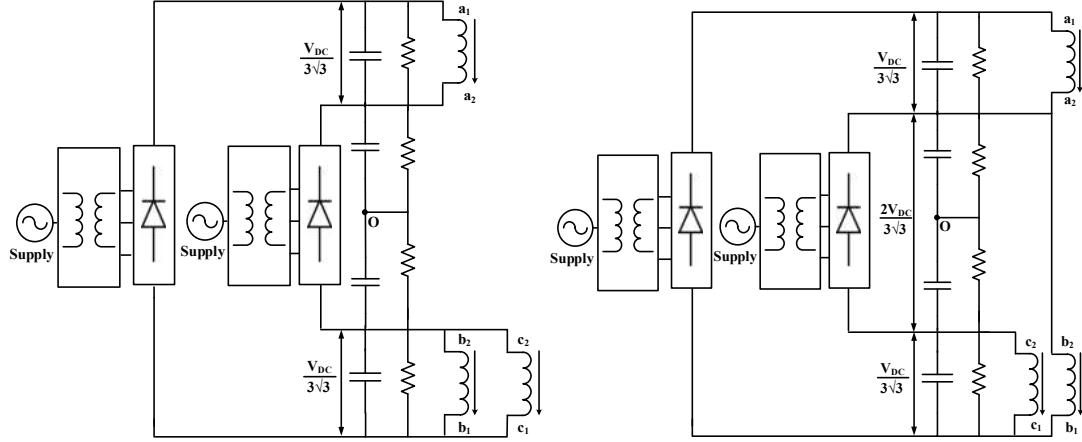

| Fig. 2.1      | Circuit configuration for four-level OEWIMD                                                                                                  | 2-4  |

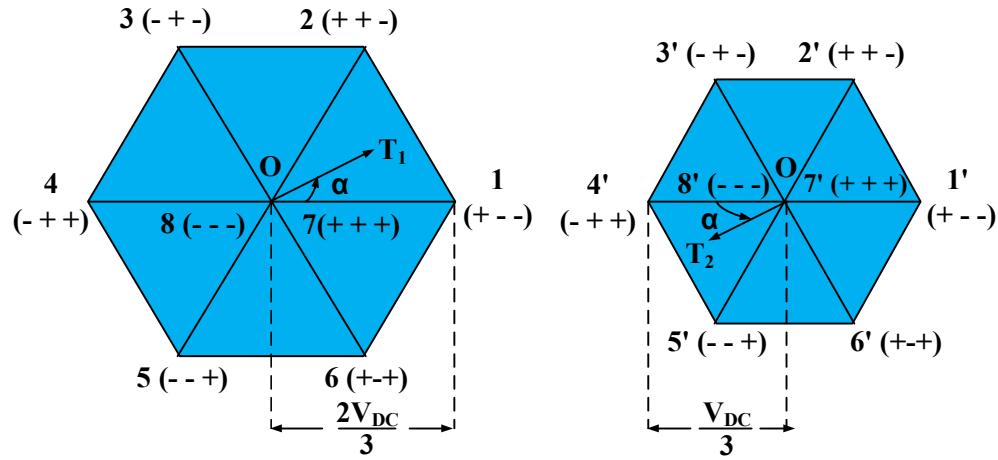

| Fig. 2.2      | Space vector locations of inverter-1 (left) & inverter-2 (right) (not drawn to scale)                                                        | 2-4  |

| Fig. 2.3      | Space vector combinations of dual-inverter system                                                                                            | 2-5  |

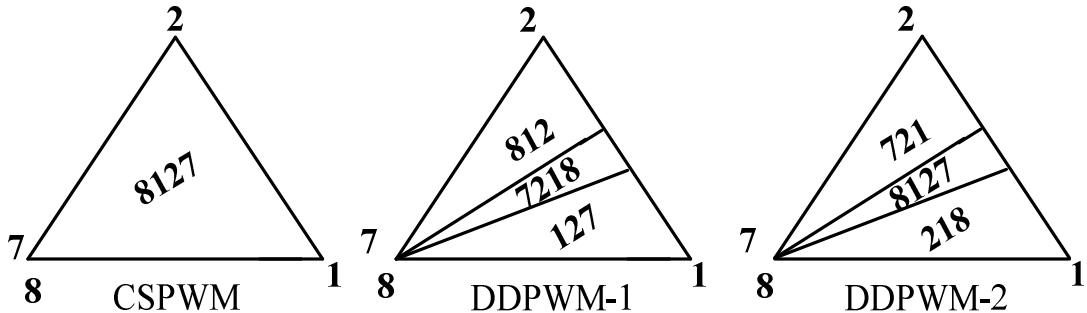

| Fig. 2.4      | Sequence of voltage vectors applied in sector-I for the conventional 2-level VSI for CSPWM (left), DDPWM-1 (middle), DDPWM-2 (right)         | 2-13 |

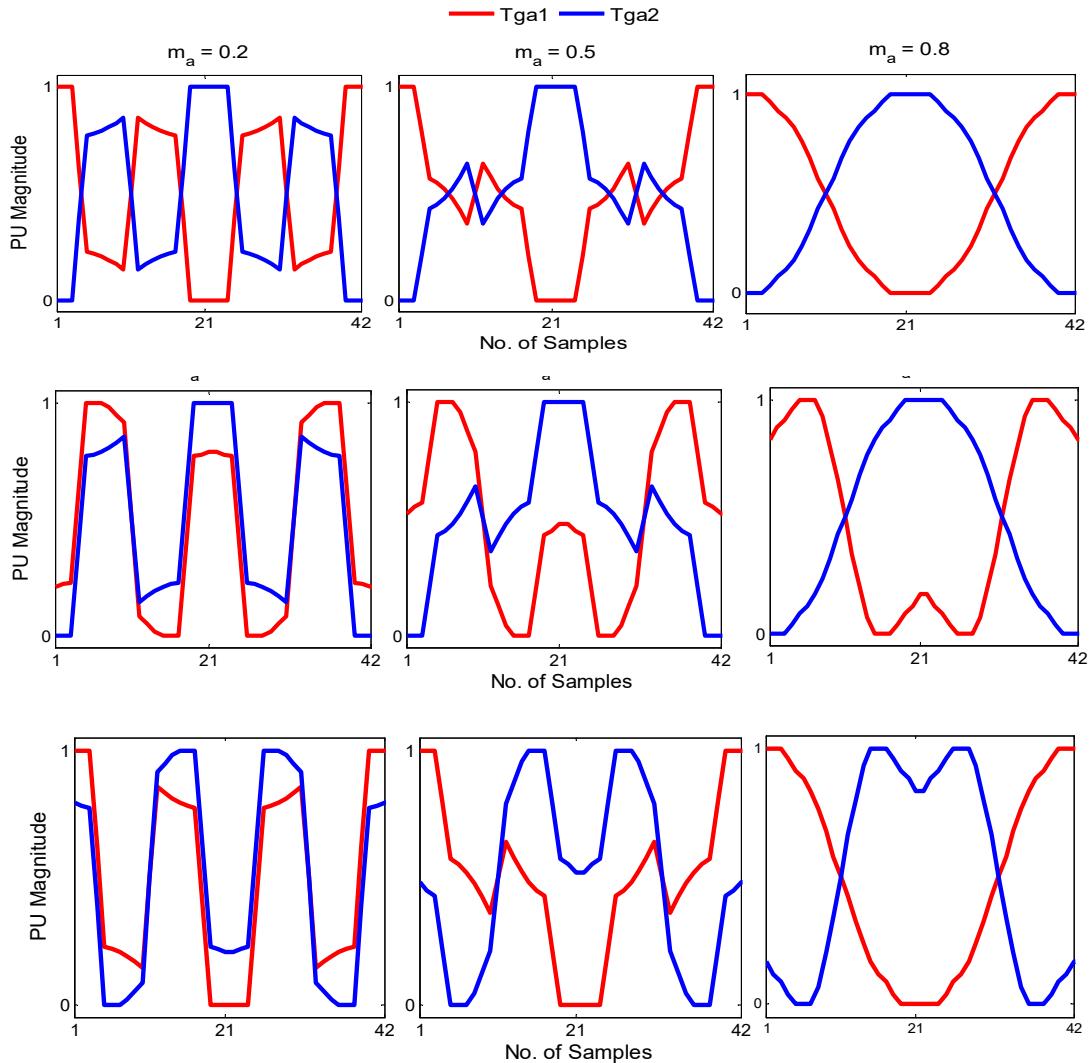

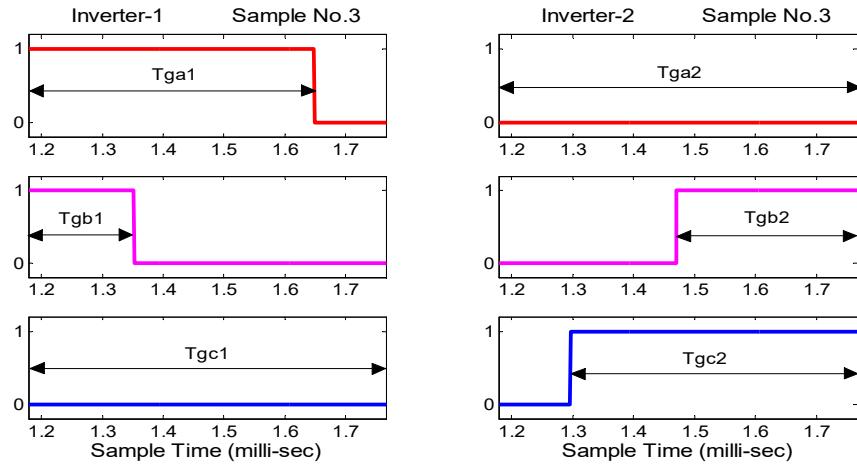

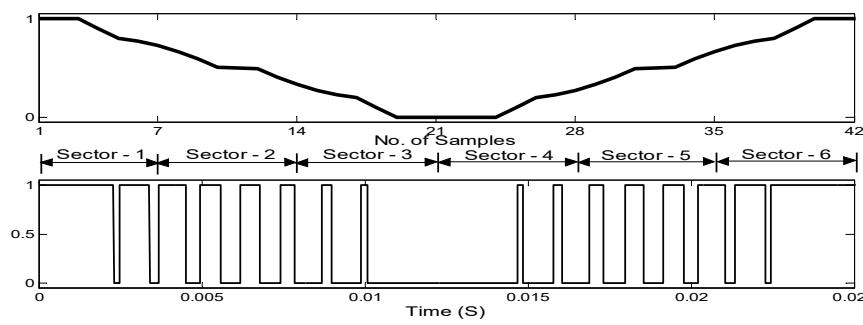

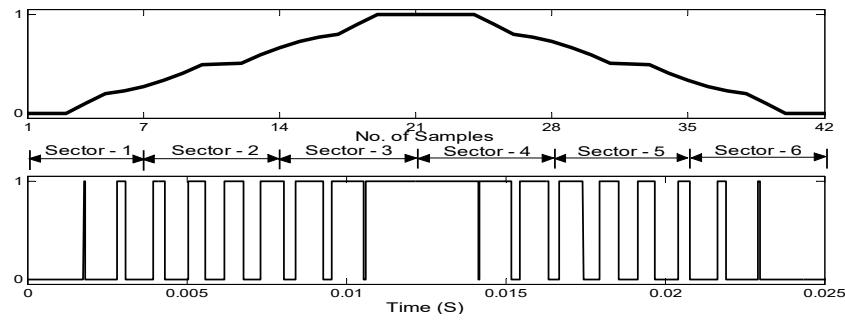

Fig. 2.5 Modulating signals for DDPWM-1 (top), DDPWM-2 (second),

DDPWM-3 (third) and DDPWM-4 (bottom) 2-15

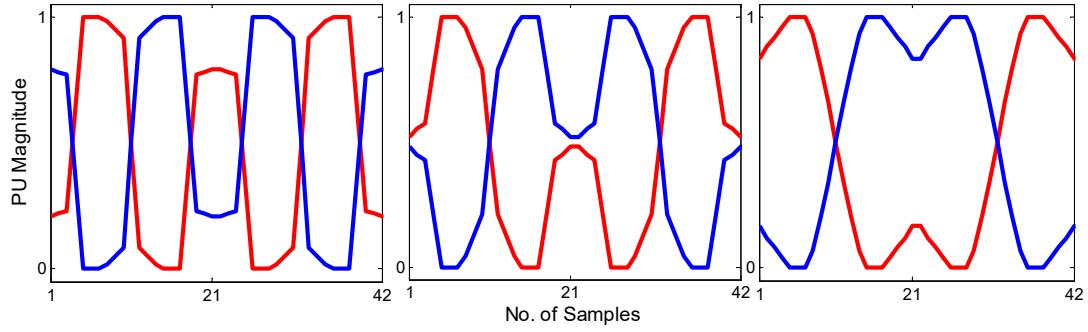

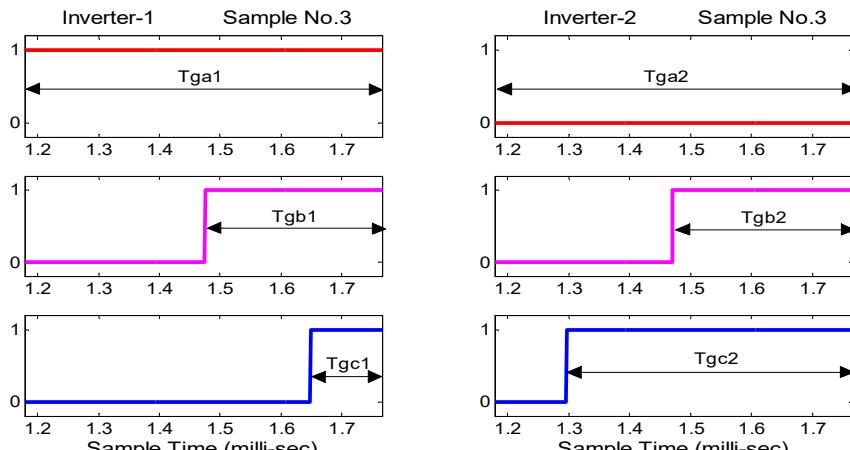

Fig. 2.6 Simulated switching time periods of inverter-1 (left) and inverter-2

(right). (a) DDPWM-1 (b) DDPWM-2 (c) DDPWM-3 (d) DDPWM-4 2-16

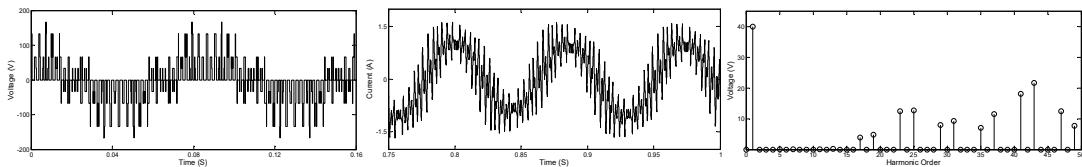

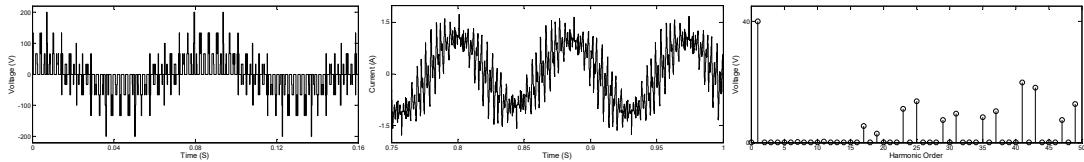

Fig. 2.7 Simulated Phase-A voltage (left), current (middle) and harmonic

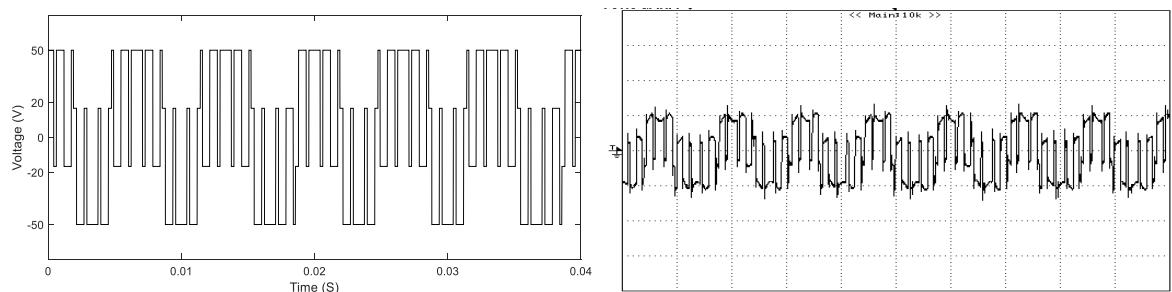

spectrum (right) of DDPWM-1 at  $m_a = 0.2$  2-18

Fig. 2.8 Simulated Phase-A voltage (left), current (middle) and harmonic

spectrum (right) of DDPWM-2 at  $m_a = 0.2$  2-19

Fig. 2.9 Simulated Phase-A voltage (left), current (middle) and harmonic

spectrum (right) of DDPWM-3 at  $m_a = 0.2$  2-19

Fig. 2.10 Simulated Phase-A voltage (left), current (middle) and harmonic

spectrum (right) of DDPWM-4 at  $m_a = 0.2$  2-19

Fig. 2.11 Simulated control signals with modulating waveforms for DDPWM-1 at

$m_a = 0.7$ . (a) inverter-1 (b) inverter-2 2-20

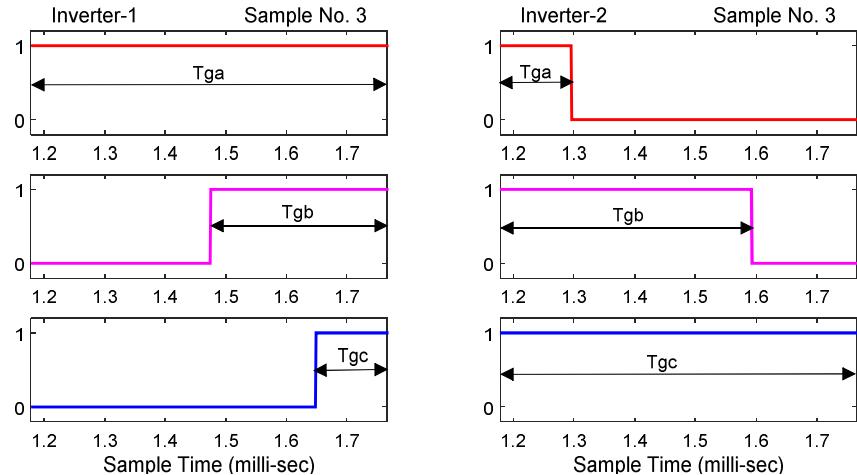

Fig. 2.12 Simulated control signals with modulating waveforms for DDPWM-2 at

$m_a = 0.7$ . (a) inverter-1 (b) inverter-2 2-20

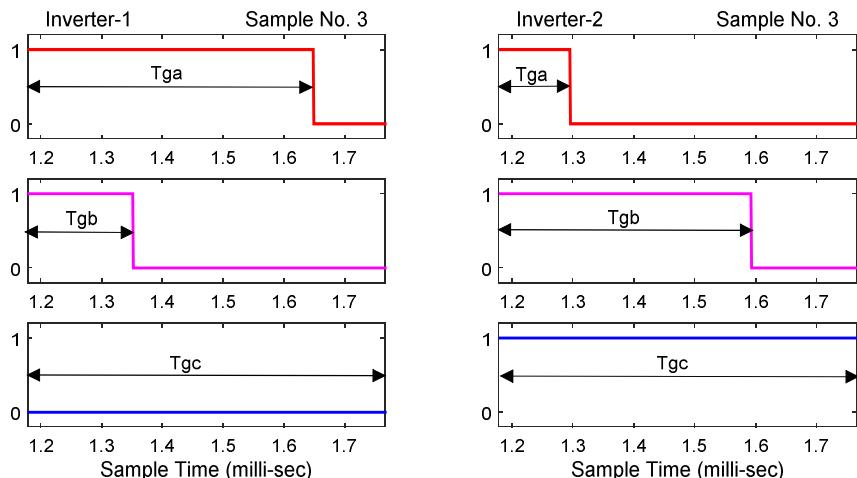

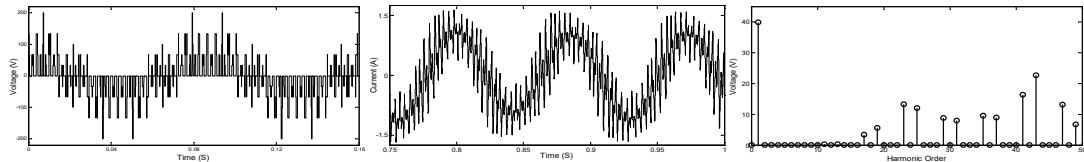

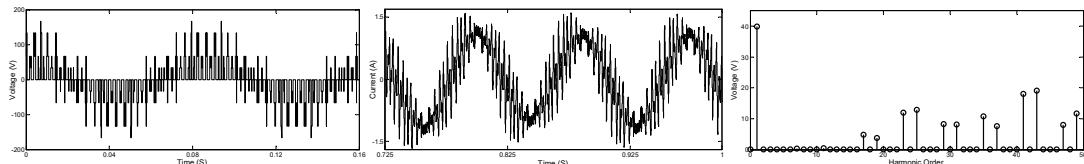

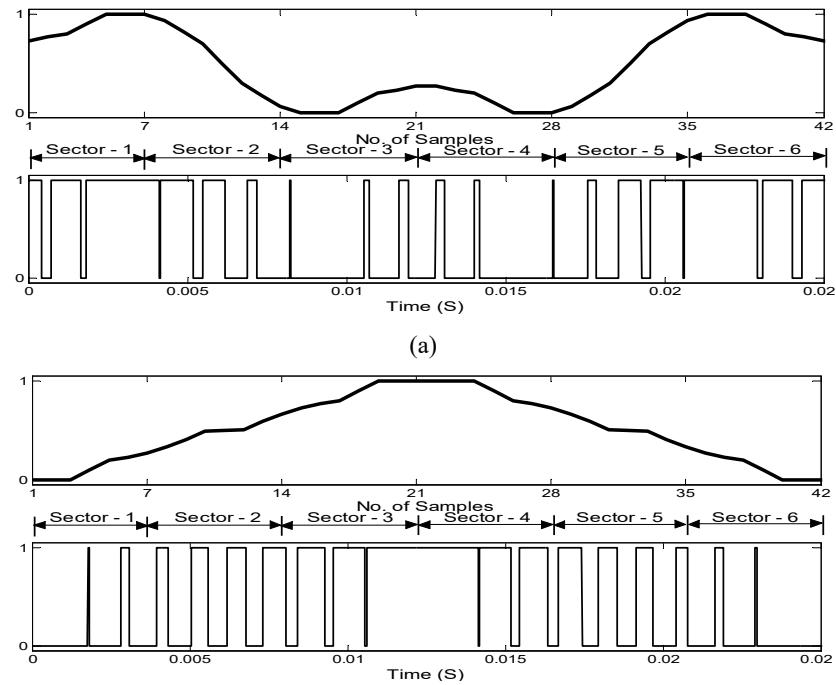

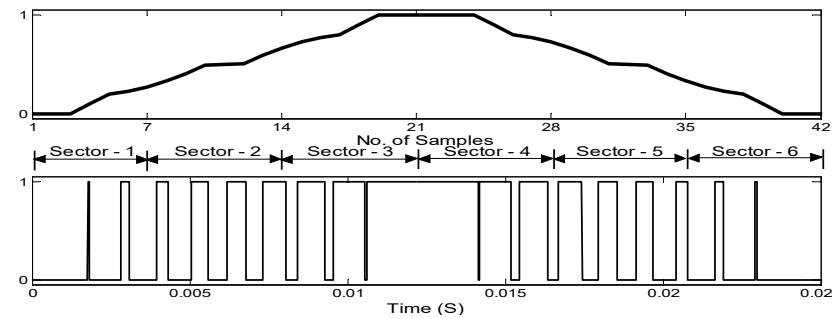

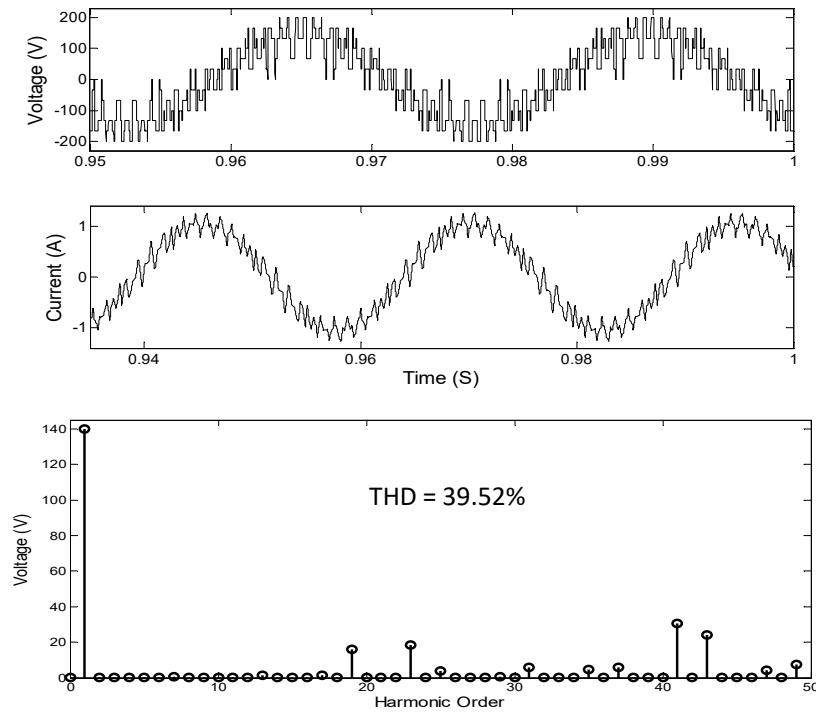

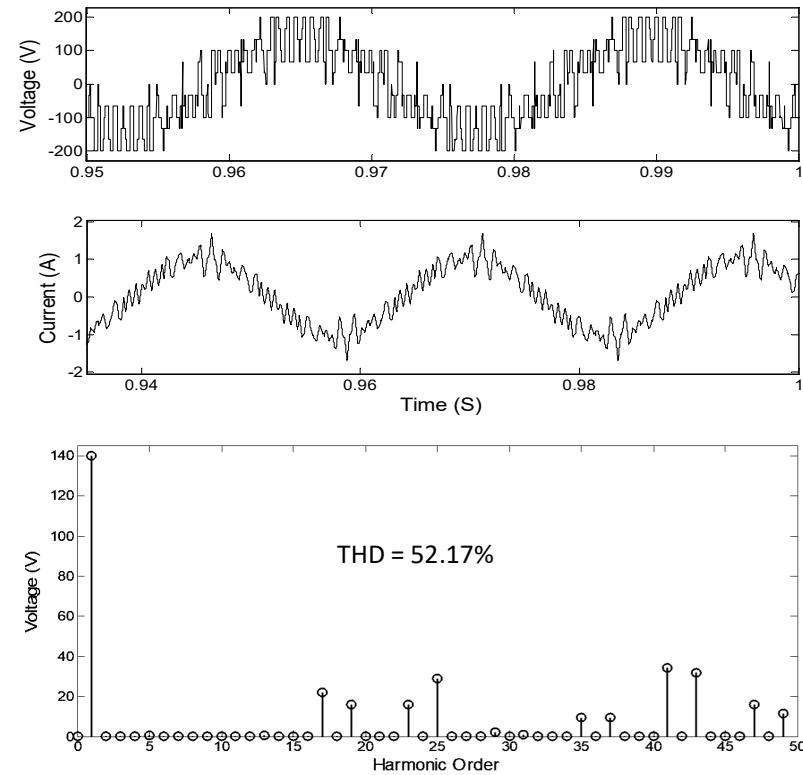

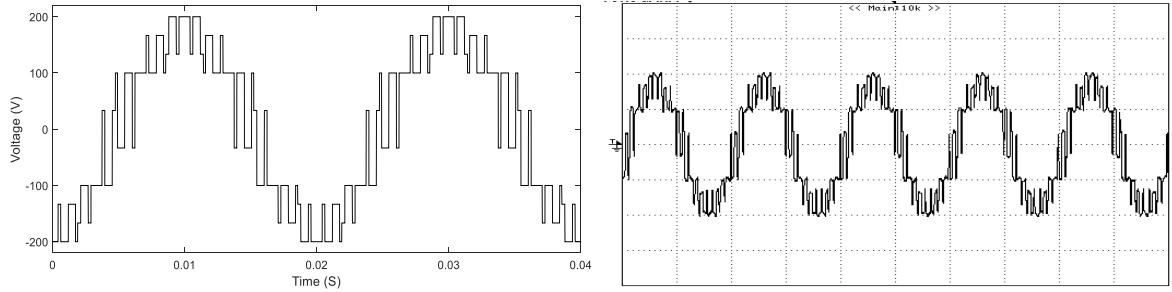

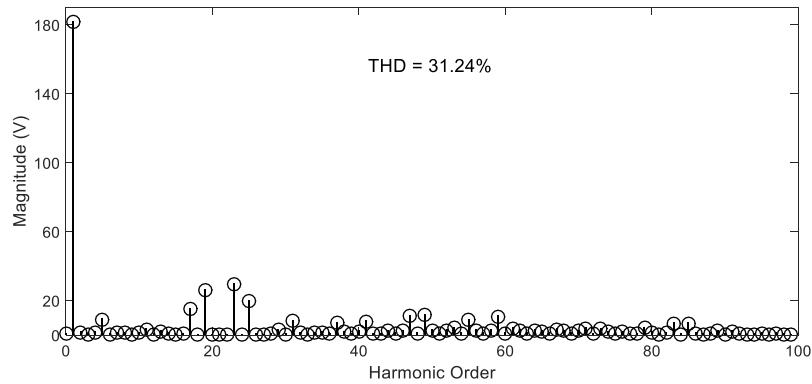

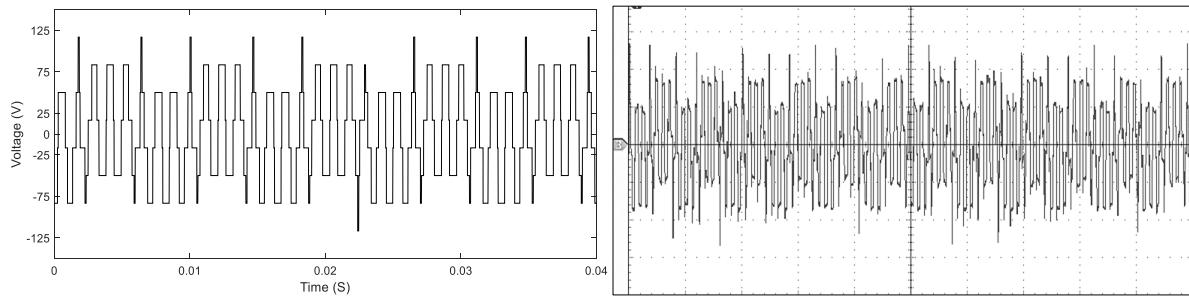

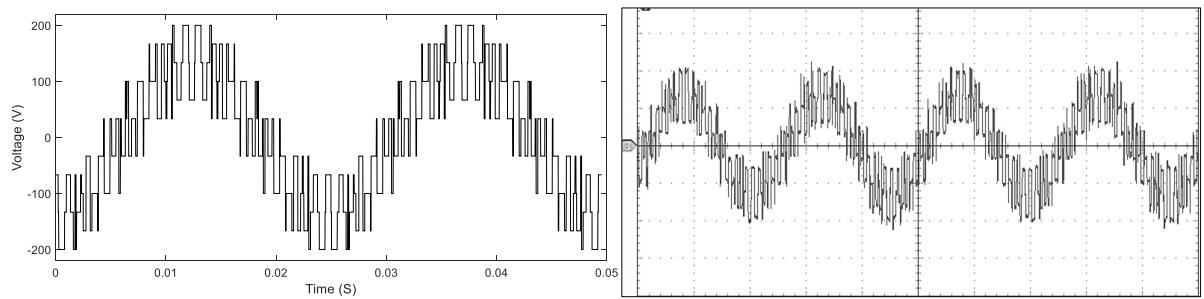

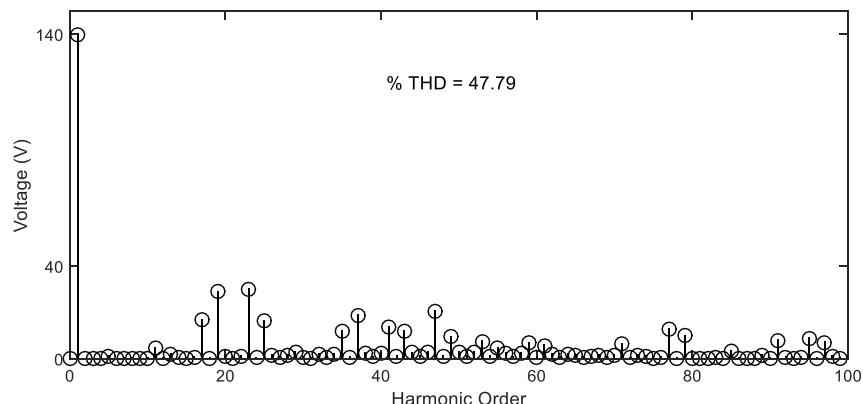

Fig. 2.13 Simulated Phase-A voltage (top), current (middle) waveforms and

harmonic spectrum of phase-A voltage (bottom) of DDPWM-1 at  $m_a =$

0.7 2-21

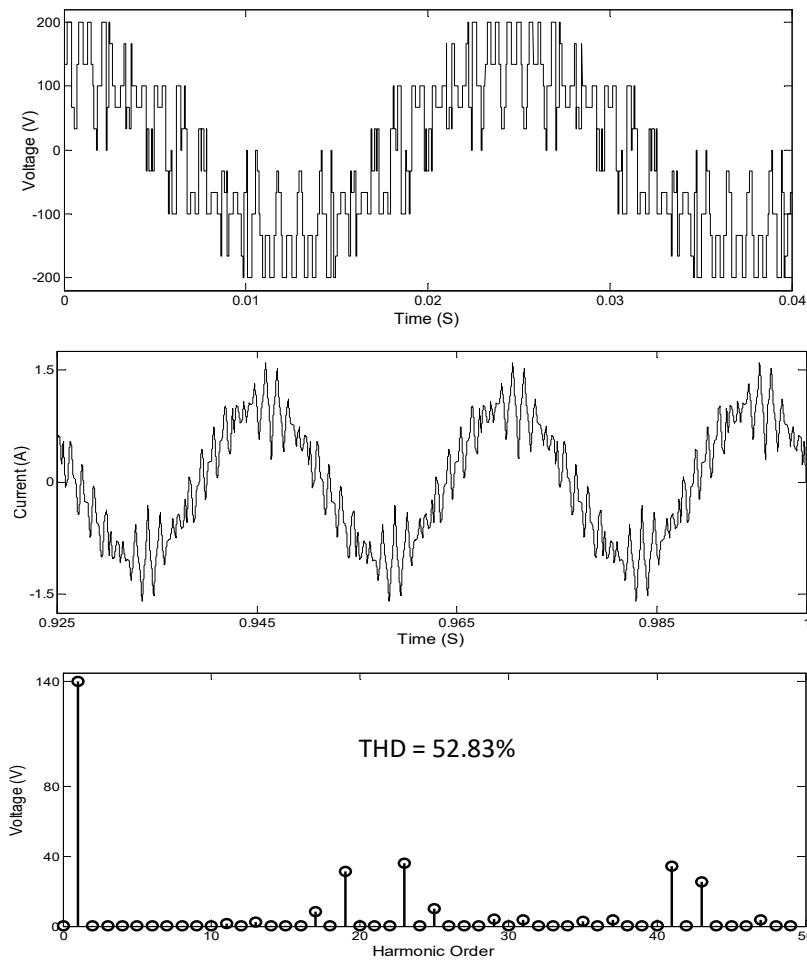

Fig. 2.14 Simulated Phase-A voltage (top), current (middle) waveforms and

harmonic spectrum of phase-A voltage (bottom) of DDPWM-2 at  $m_a =$

0.7 2-21

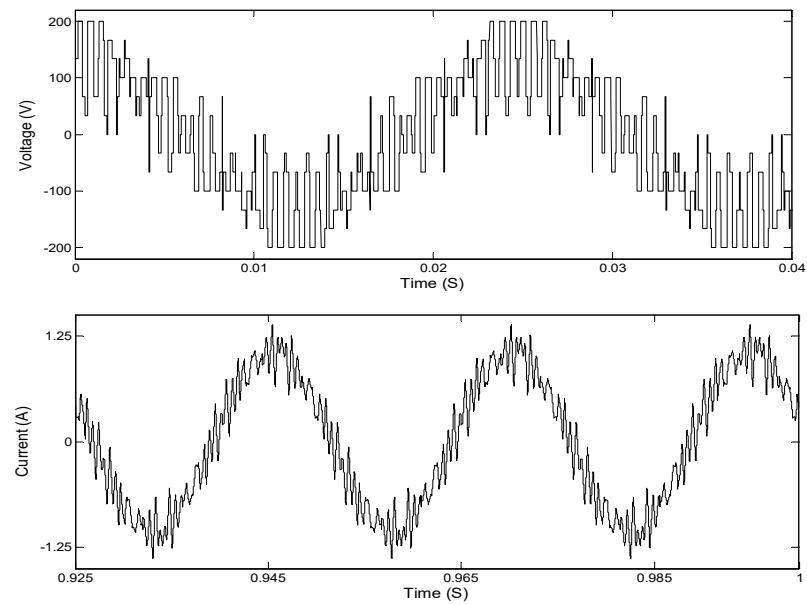

Fig. 2.15 Simulated Phase-A voltage (top), current (middle) waveforms and

harmonic spectrum of phase-A voltage (bottom) of DDPWM-3 at  $m_a =$

0.7 2-22

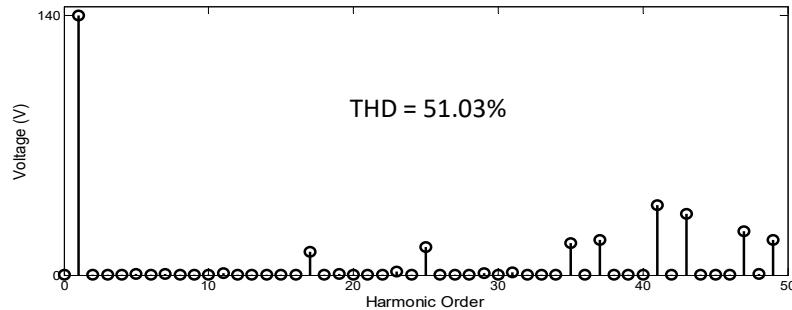

Fig. 2.16 Simulated Phase-A voltage (top), current (middle) waveforms and harmonic spectrum of phase-A voltage (bottom) of DDPWM-4 at  $m_a = 0.7$  2-23

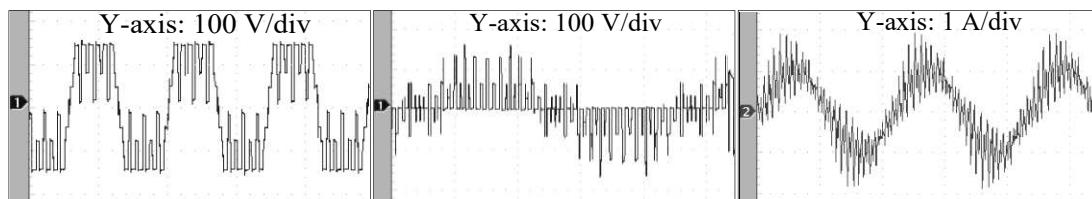

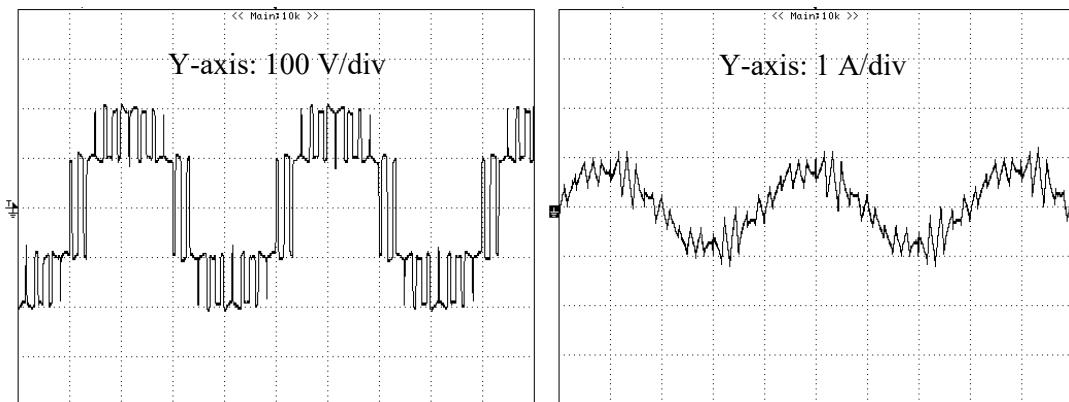

Fig. 2.17 Experimental waveforms of common mode voltage (left), Phase-A voltage (middle) and current (right) at  $m_a = 0.2$  for DDPWM-1 technique (X-axis: 10 ms/div) 2-23

Fig. 2.18 Experimental waveforms of common mode voltage (left), Phase-A voltage (middle) and current (right) at  $m_a = 0.2$  for DDPWM-2 technique (X-axis: 10 ms/div) 2-23

Fig. 2.19 Experimental waveforms of common mode voltage (left), Phase-A voltage (middle) and current (right) at  $m_a = 0.2$  for DDPWM-3 technique (X-axis: 10 ms/div) 2-24

Fig. 2.20 Experimental waveforms of common mode voltage (left), Phase-A voltage (middle) and current (right) at  $m_a = 0.2$  for DDPWM-4 technique (X-axis: 10 ms/div) 2-24

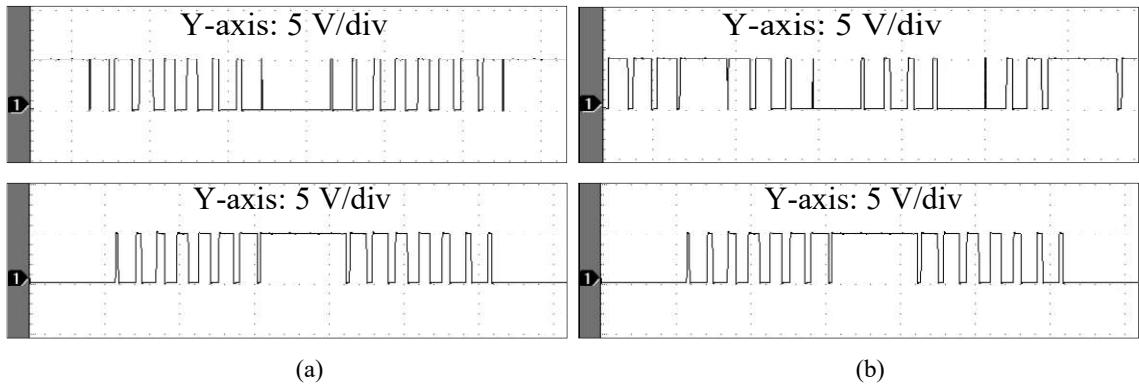

Fig. 2.21 Experimental control signals for Phase-A of dual inverters (inverter-1 (top), inverter-2 (bottom)) at  $m_a = 0.7$  (X-axis: 4 ms/div). (a) DDPWM-1 (b) DDPWM-2 2-24

Fig. 2.22 Experimental Pole voltages of inverter-1(left), inverter-2 (right) at  $m_a = 0.7$  for DDPWM-1 (X-axis: 10 ms/div) 2-25

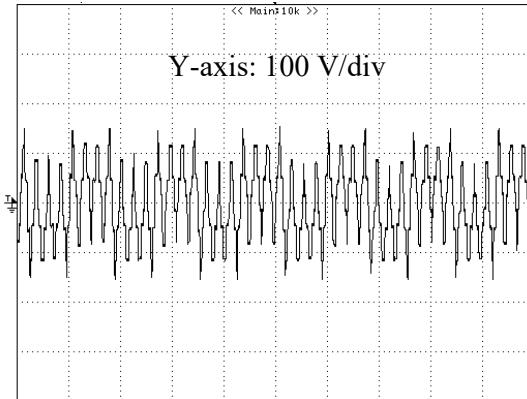

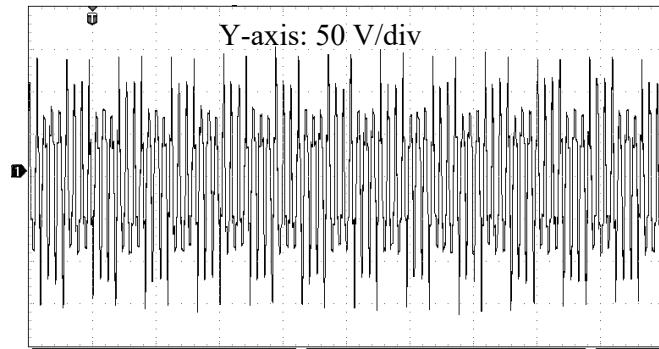

Fig. 2.23 Experimental common mode voltage waveform for DDPWM-1 at  $m_a = 0.7$  (X-axis: 5 ms/div) 2-25

Fig. 2.24 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-1 at  $m_a = 0.7$ . (X-axis: 5 ms/div(left), 10 ms/div (right)) 2-25

Fig. 2.25 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-1 at  $m_a = 1$  (X-axis: 5 ms/div) 2-26

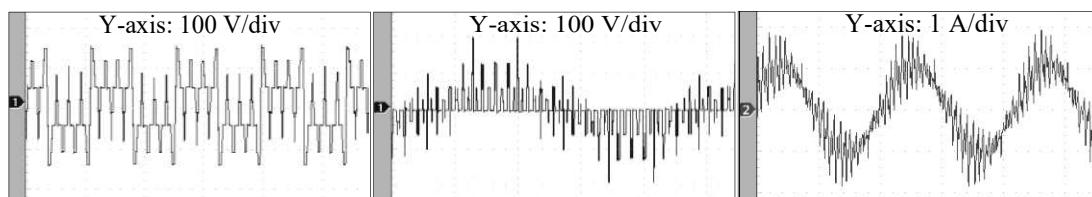

Fig. 2.26 Experimental Pole voltages of inverter-1(left), inverter-2 (right) at  $m_a = 0.7$  for DDPWM-2 (X-axis: 10 ms/div) 2-26

Fig. 2.27 Experimental common mode voltage waveform for DDPWM-2 at  $m_a = 0.7$  (X-axis: 10 ms/div) 2-27

Fig. 2.28 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-2 at  $m_a = 0.7$  (X-axis: 5 ms/div (left), 10 ms/div (right)) 2-27

Fig. 2.29 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-2 at  $m_a = 1$  (X-axis: 5 ms/div) 2-27

Fig. 2.30 Experimental common mode voltage waveform for DDPWM-3 at  $m_a = 0.7$  (X-axis: 10 ms/div) 2-28

Fig. 2.31 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-3 at  $m_a = 0.7$  (X-axis: 10 ms/div) 2-28

Fig. 2.32 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-3 at  $m_a = 1$  (X-axis: 10 ms/div) 2-28

Fig. 2.33 Experimental common mode voltage waveform for DDPWM-4 at  $m_a = 0.7$  (X-axis: 4 ms/div) 2-29

Fig. 2.34 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-4 at  $m_a = 0.7$  (X-axis: 10 ms/div) 2-29

Fig. 2.35 Experimental Phase-A voltage (left) and current (right) waveforms for DDPWM-4 at  $m_a = 1$  (X-axis: 10 ms/div) 2-29

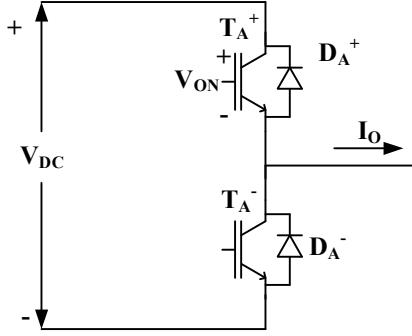

Fig. 2.36 One of the A-Phase leg of dual-inverter topology 2-30

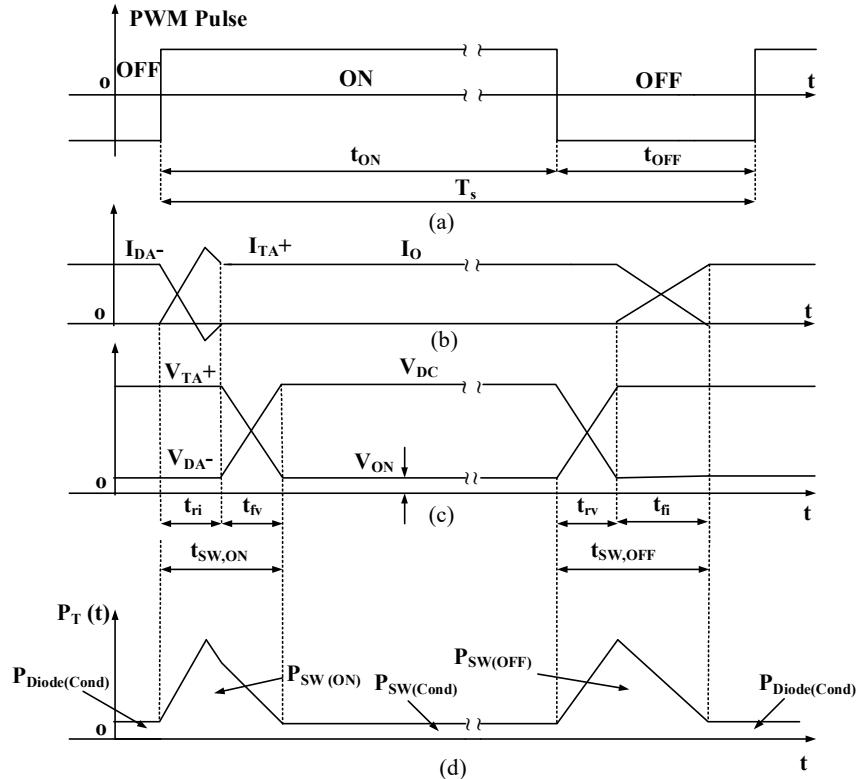

Fig. 2.37 Current through and Voltage across  $T_A^+, D_A^-$  with diode reverse recovery current 2-31

|                                                                                                                                                                                             |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

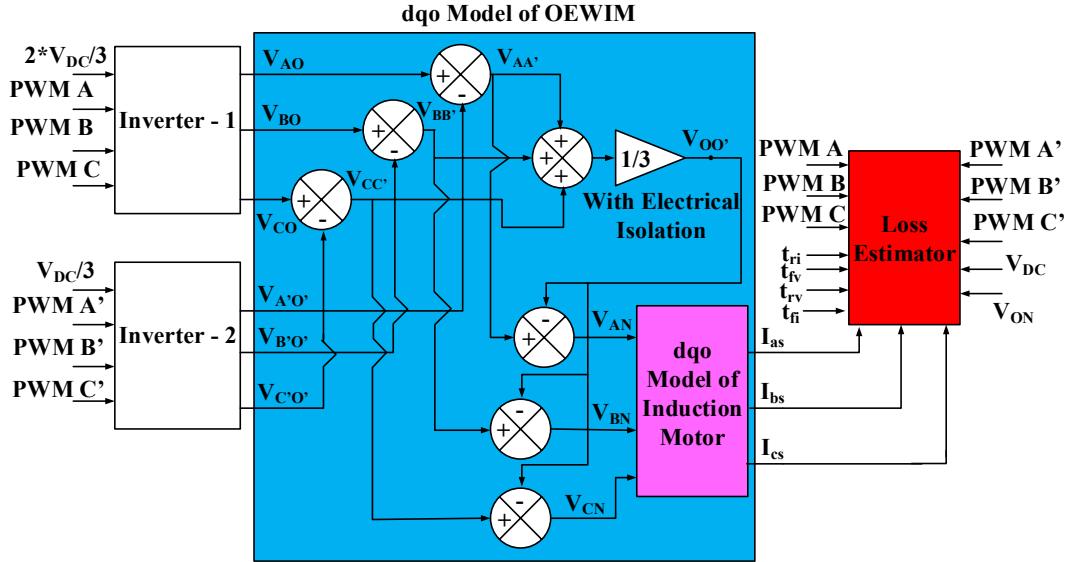

| Fig. 2.38 Improvised loss model for four-level OEWIMD                                                                                                                                       | 2-32 |

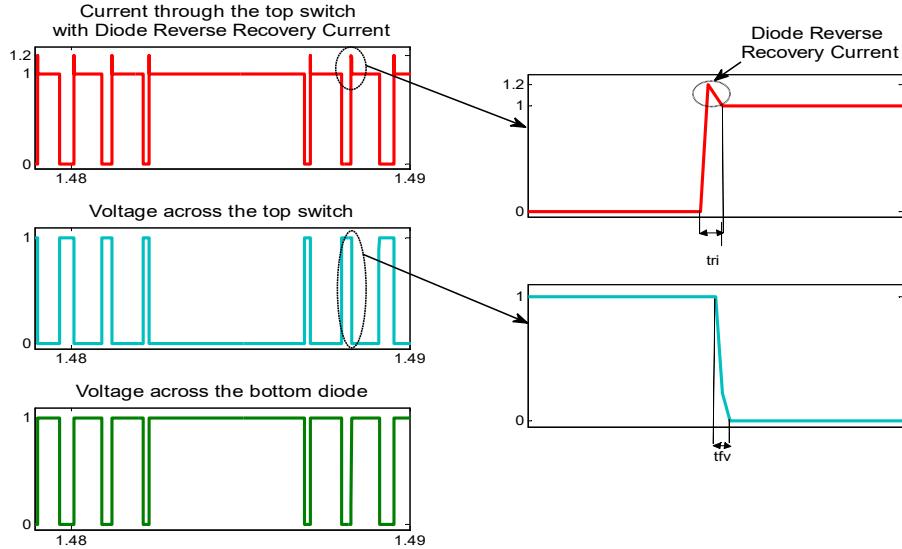

| Fig. 2.39 Simulated current and voltage waveforms of the top switching device with diode reverse recovery current and the bottom diode                                                      | 2-33 |

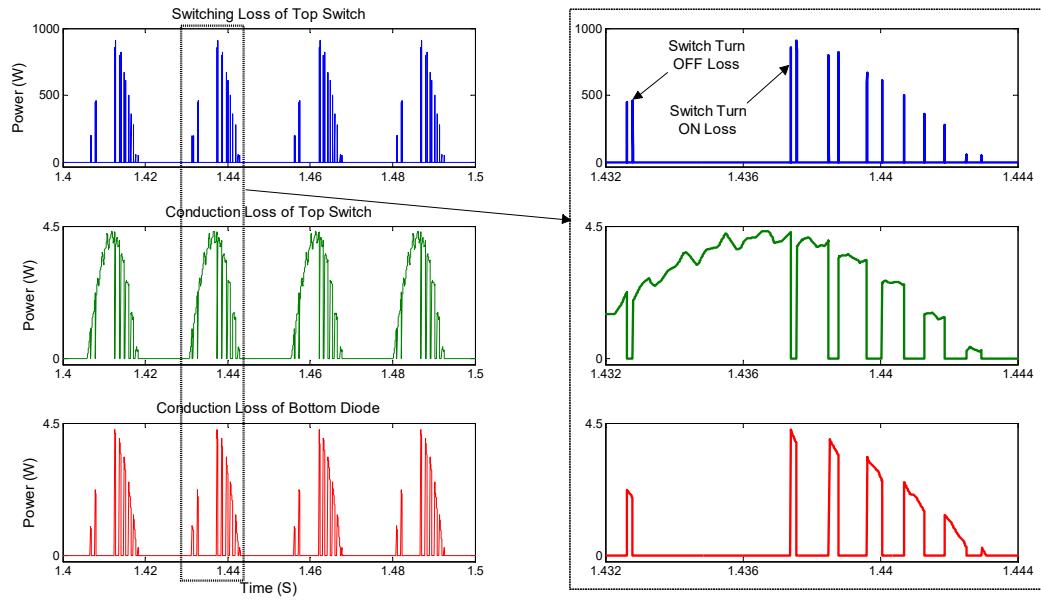

| Fig. 2.40 Simulated loss waveforms of top switching device and bottom anti-parallel diode with zoomed portion                                                                               | 2-34 |

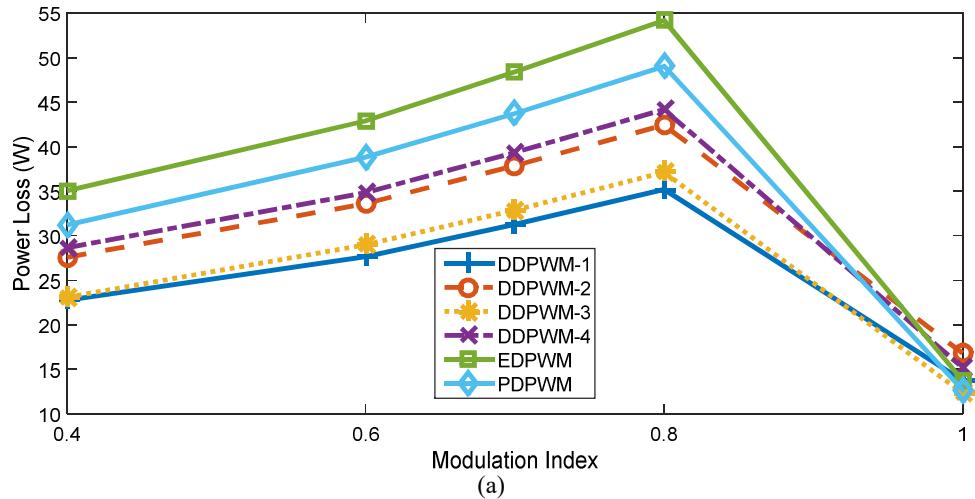

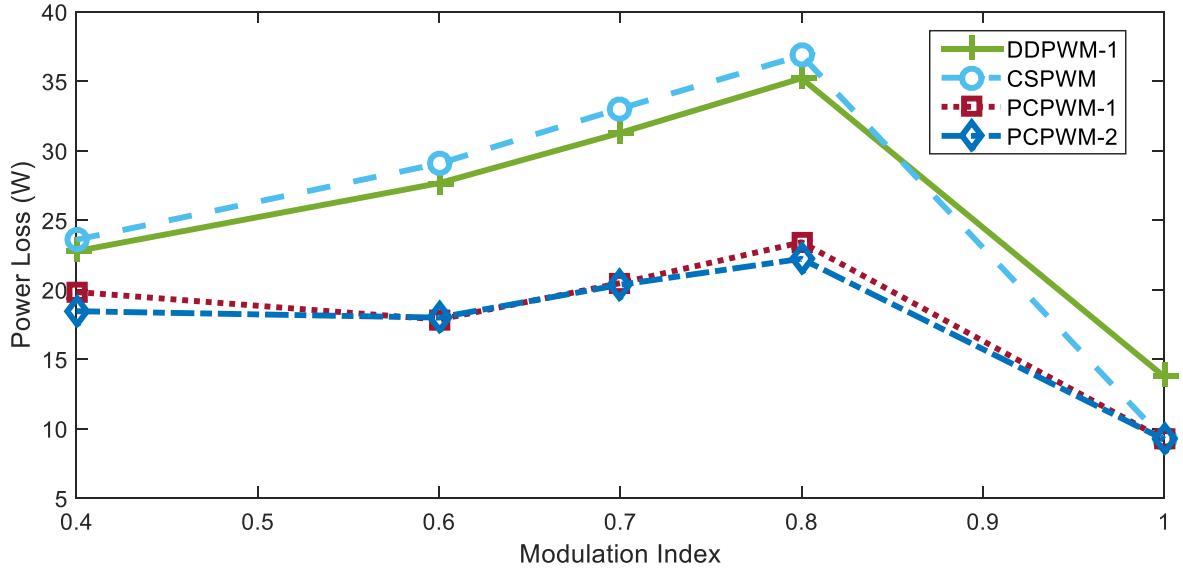

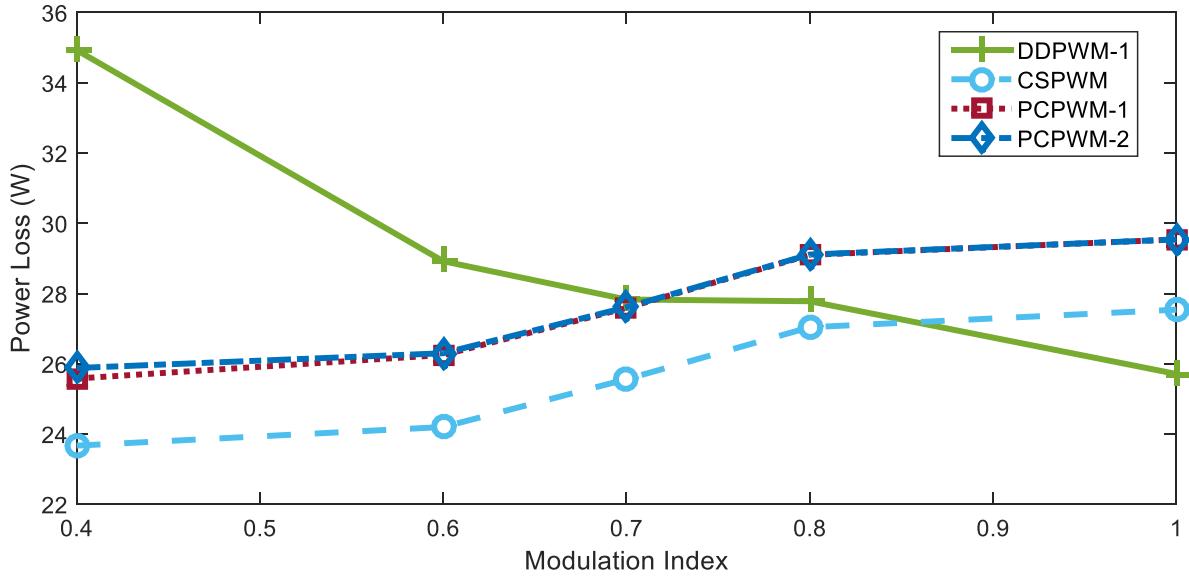

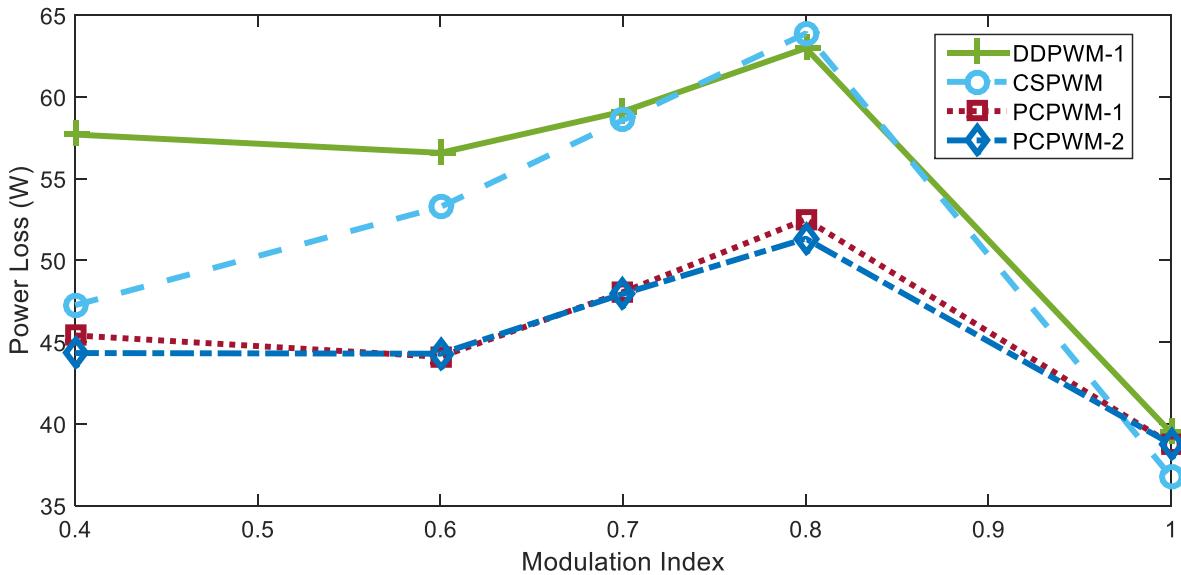

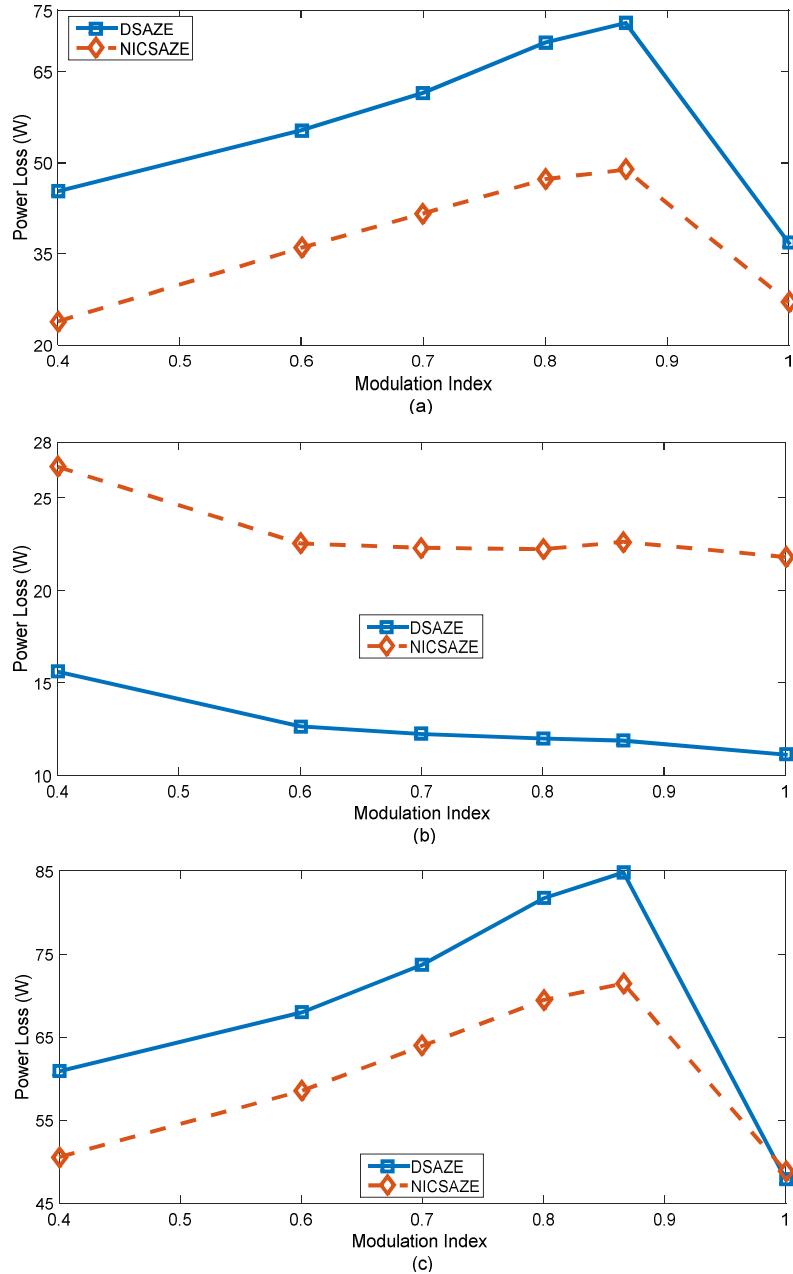

| Fig. 2.41 Loss of dual-inverter fed four-level OEWIM (a) total switching power loss, (b) total conduction power loss, (c) Overall dual-inverter loss                                        | 2-35 |

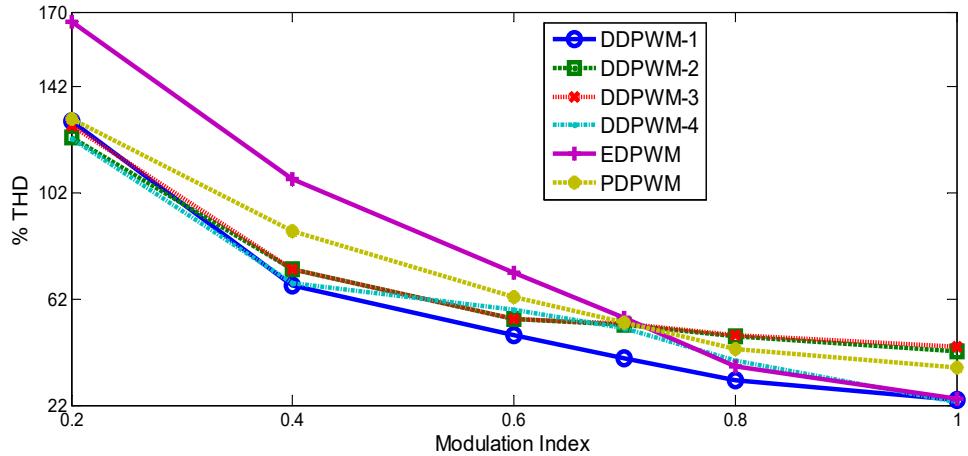

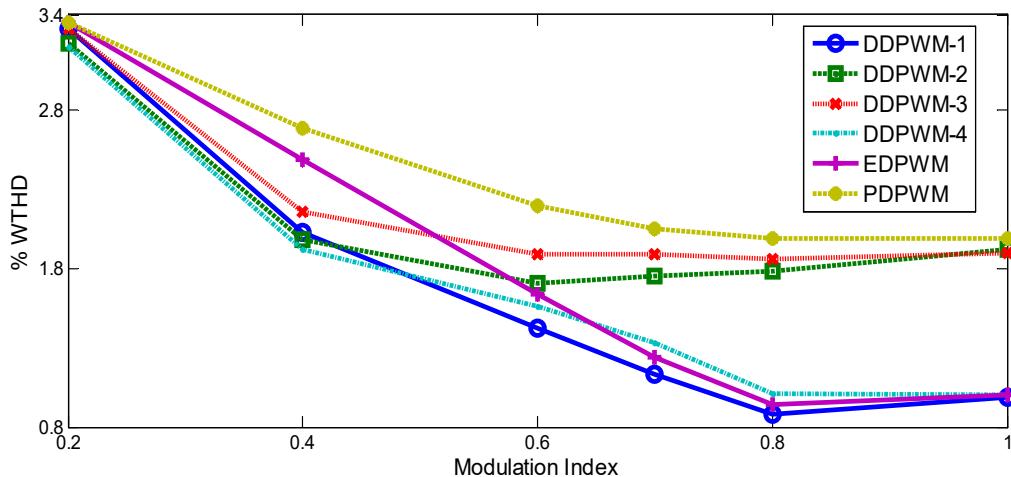

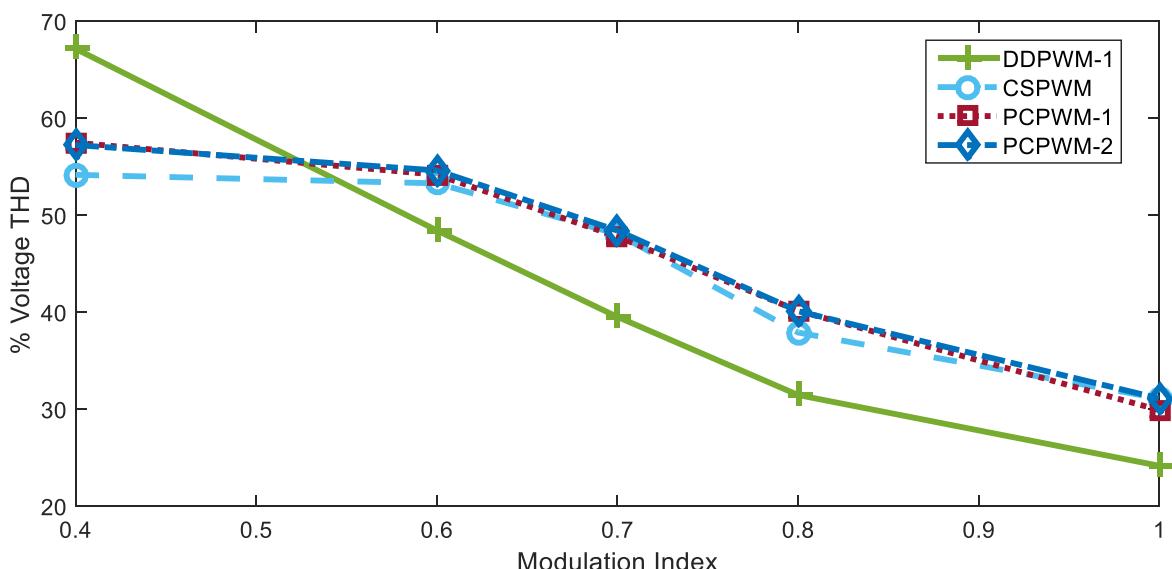

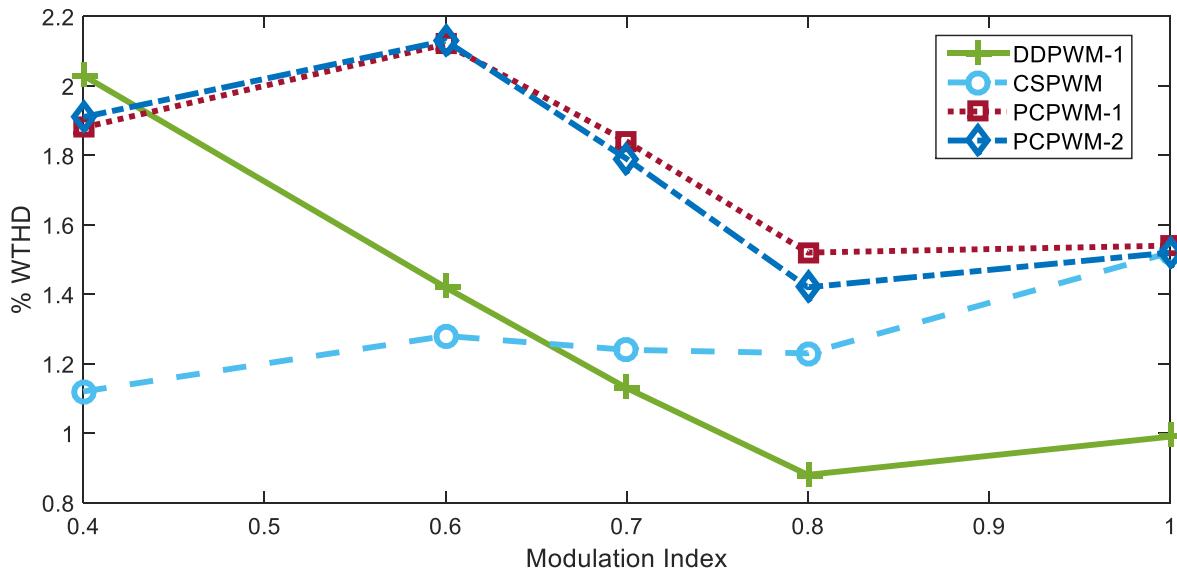

| Fig. 2.42 THD for four-level OEWIMD                                                                                                                                                         | 2-37 |

| Fig. 2.43 WTHD for four-level OEWIMD                                                                                                                                                        | 2-37 |

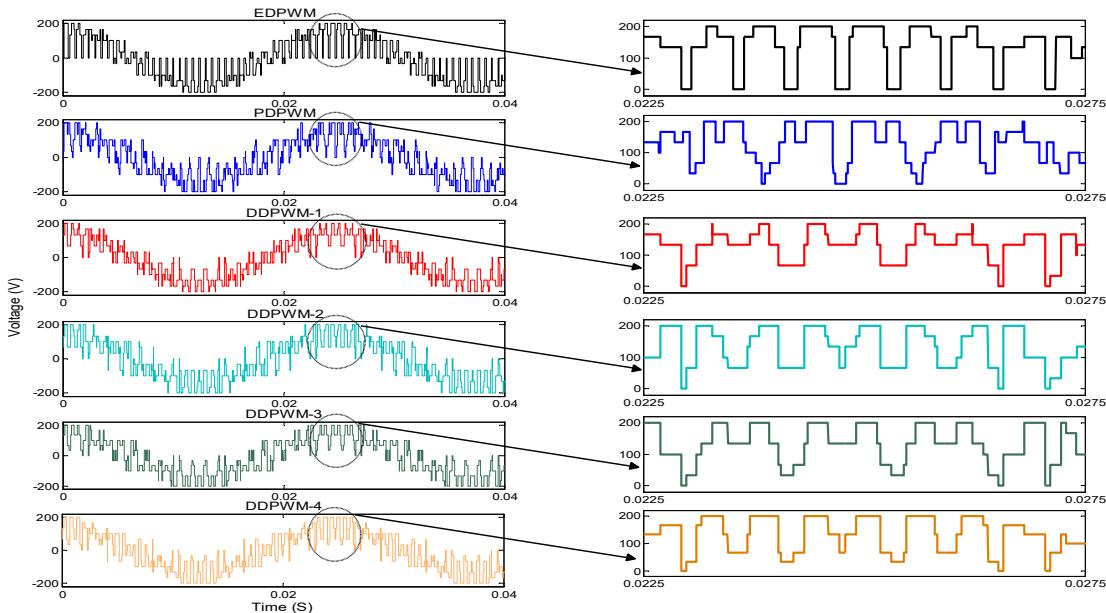

| Fig. 2.44 The voltage pulses appearing across the motor winding with the EDPWM (top), PDPWM (second), DDPWM-1 (third) DDPMW-2 (fourth), DDPWM-3 (fifth) and the DDPWM-4 (bottom) techniques | 2-38 |

| Fig. 3.1 A Four-level OEWIMD with unequal dc-link voltages                                                                                                                                  | 3-2  |

| Fig. 3.2 Space vector combinations of dual-inverter system                                                                                                                                  | 3-3  |

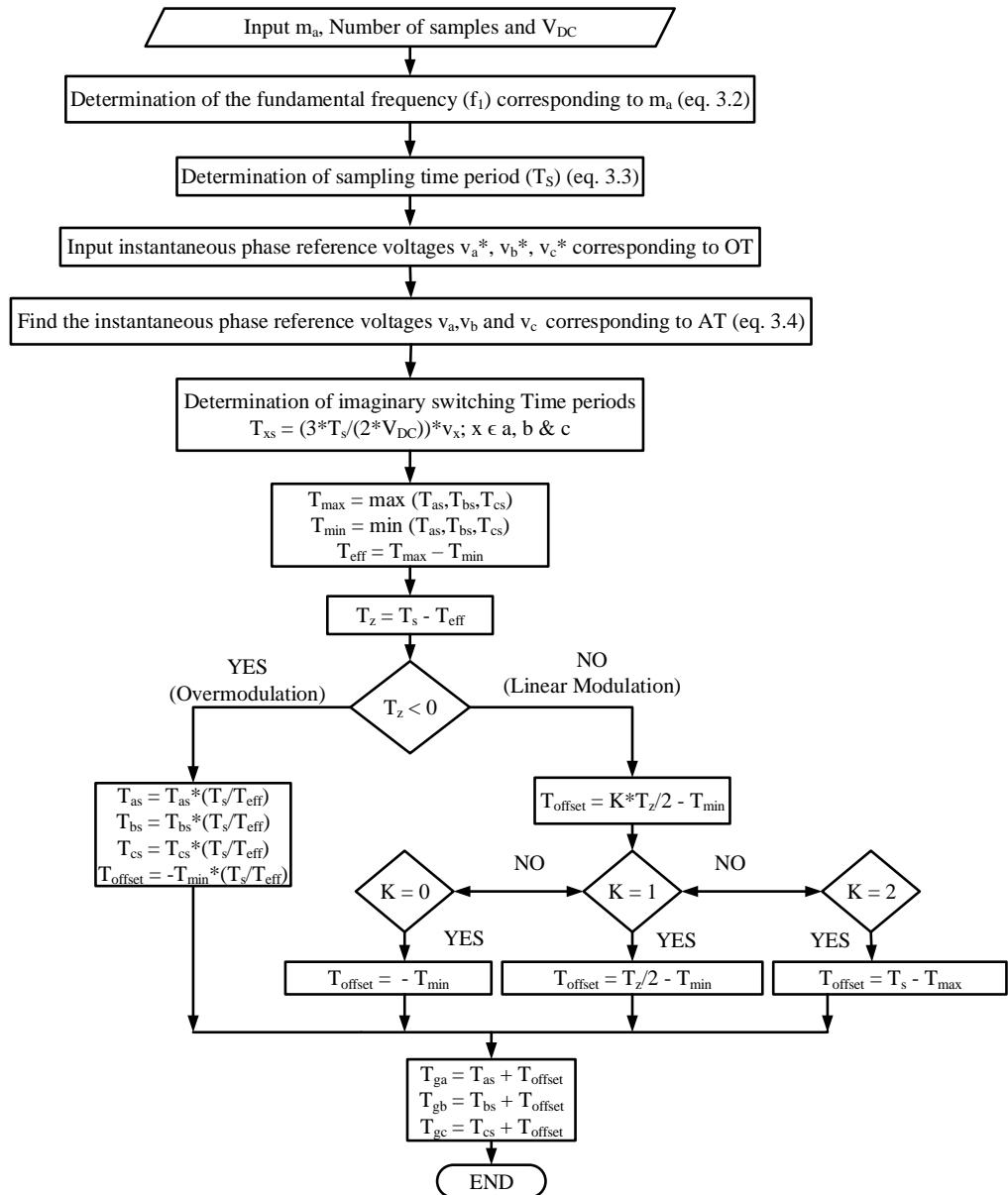

| Fig. 3.3 Flow chart of proposed SVPWM Strategy                                                                                                                                              | 3-7  |

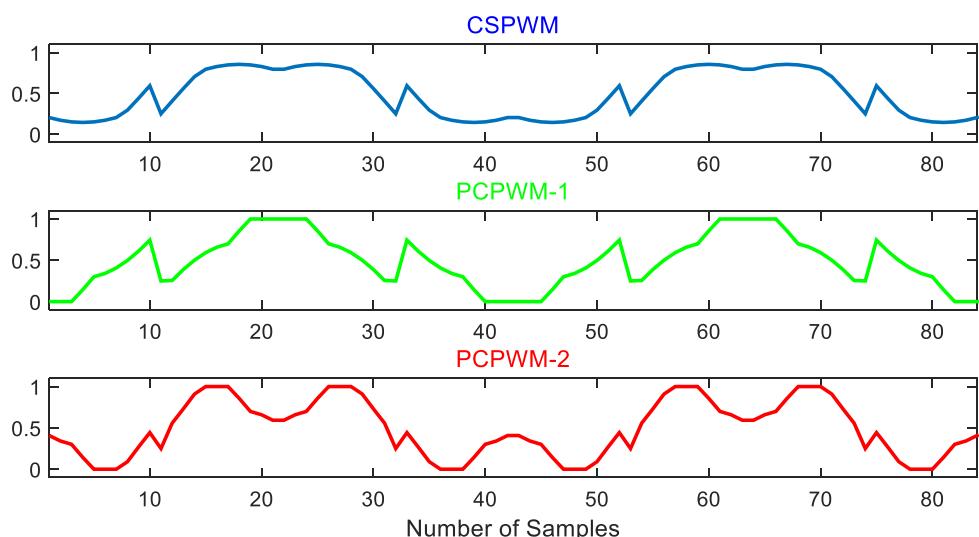

| Fig. 3.4 Modulating signals for CSPWM, PCPWM -1 & PCPWM -2                                                                                                                                  | 3-8  |

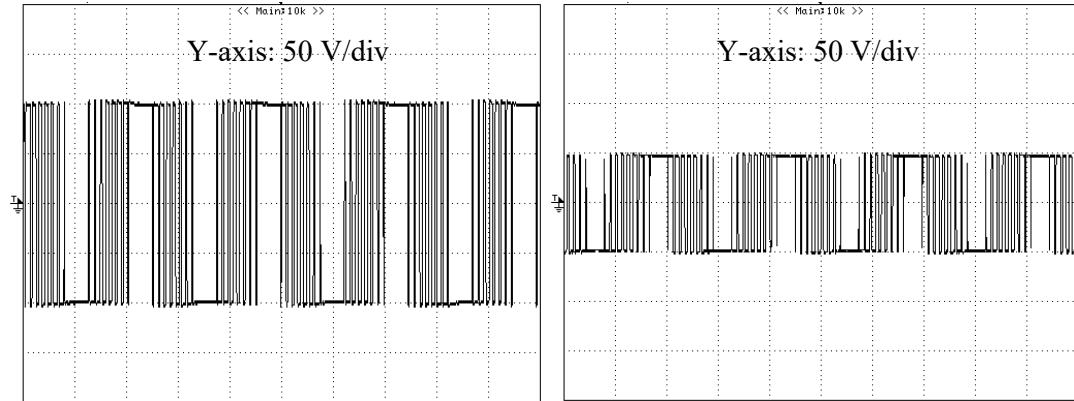

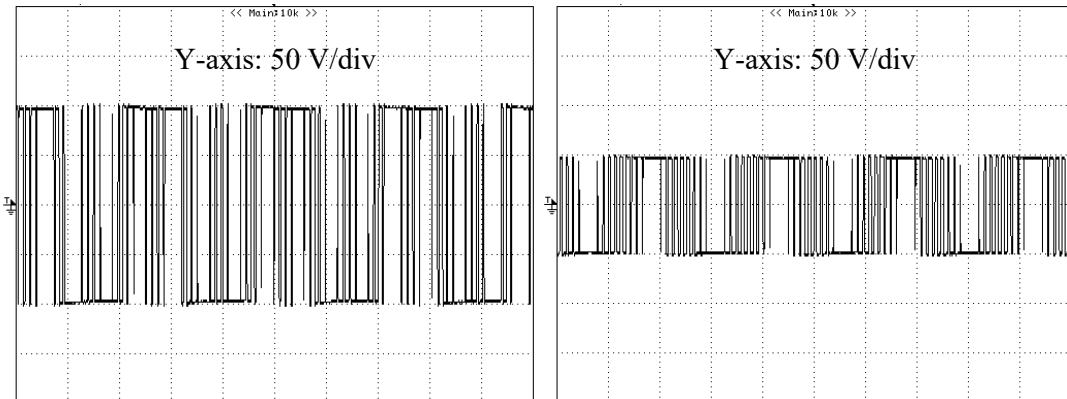

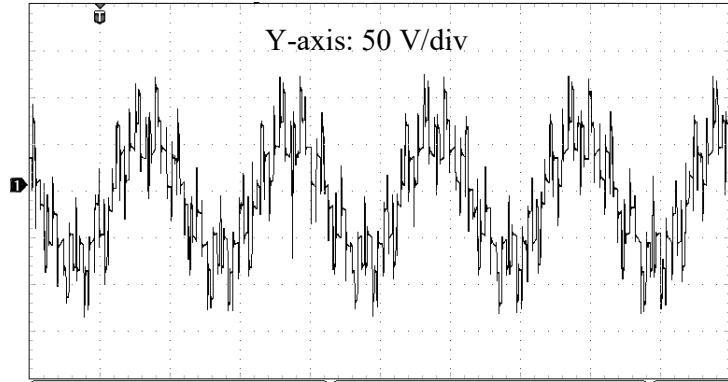

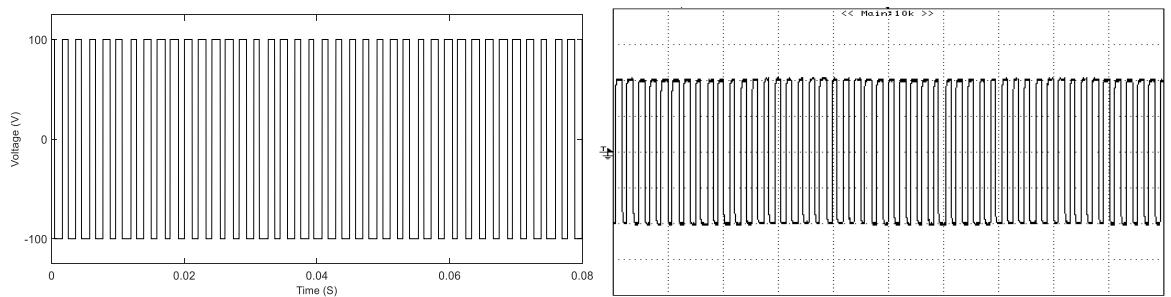

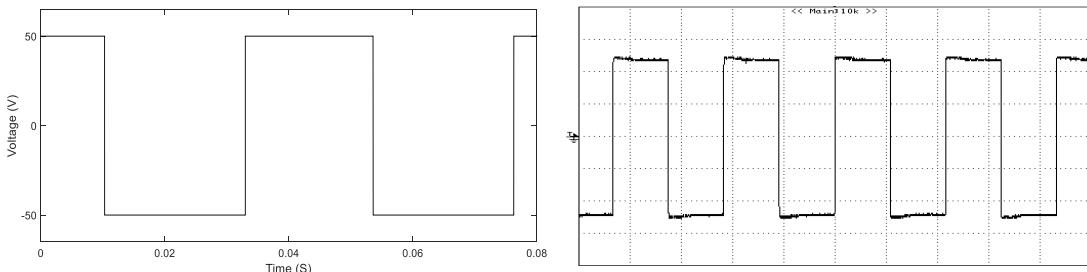

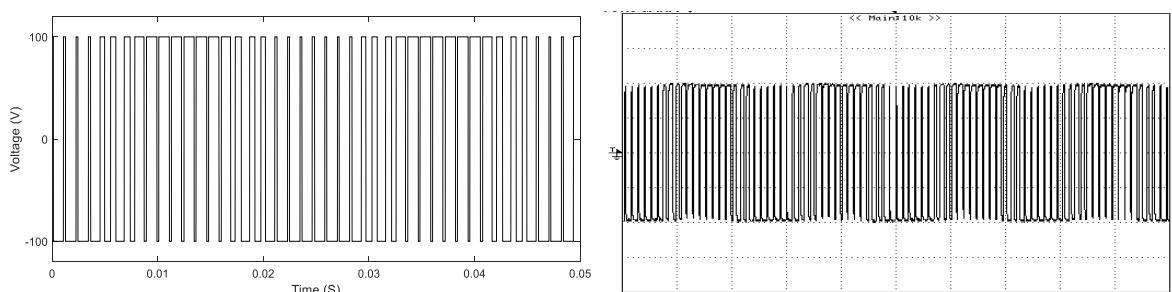

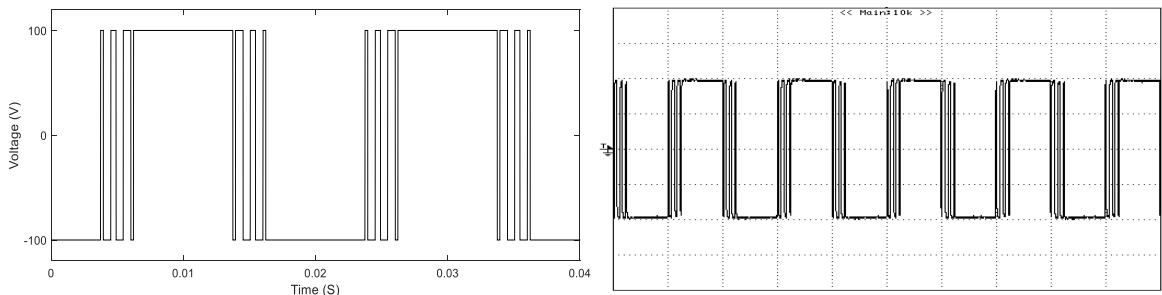

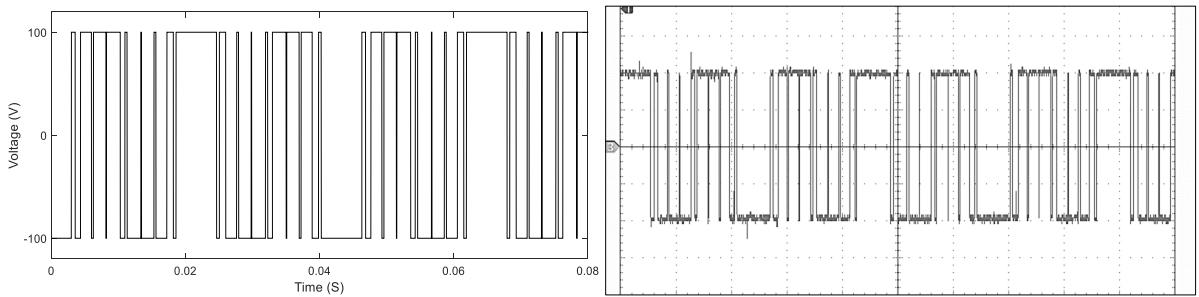

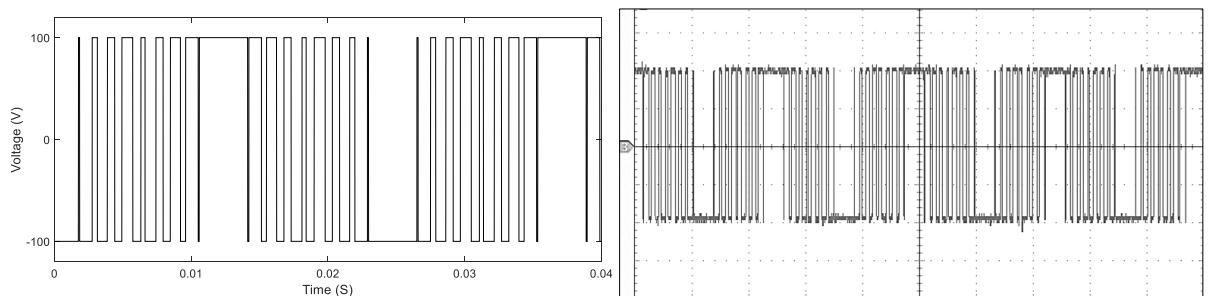

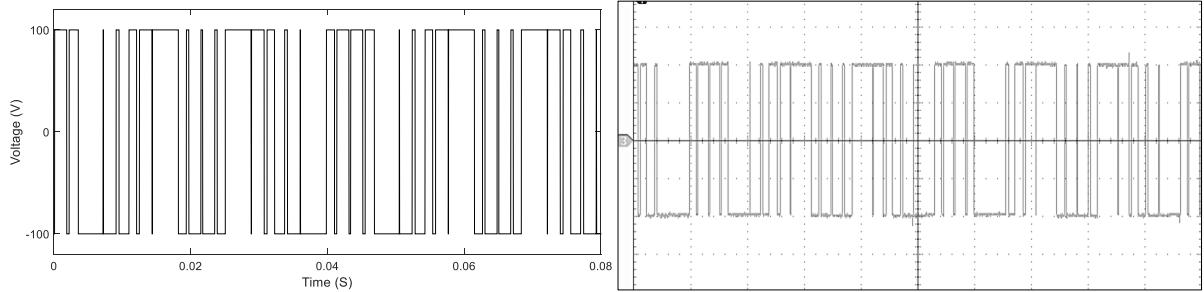

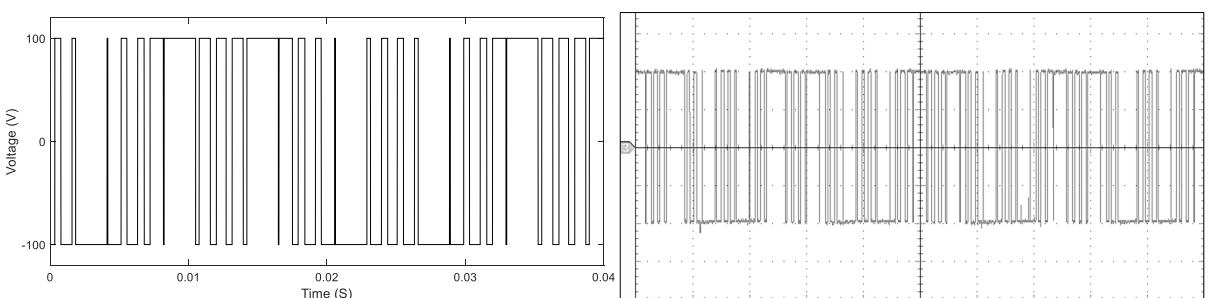

| Fig. 3.5 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at $m_a = 0.4$ for CSPWM, Scale: X-axis: 20 ms/div, Y-axis: 50 V/div                                  | 3-10 |

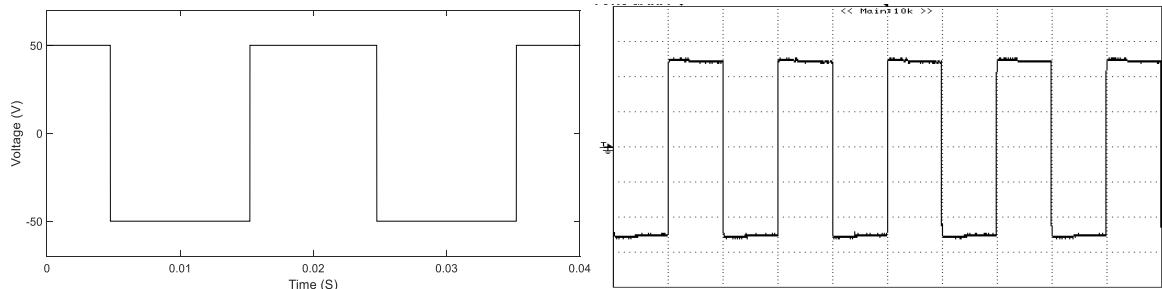

| Fig. 3.6 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at $m_a = 0.4$ for CSPWM, Scale: X-axis: 20 ms/div, Y-axis: 20 V/div                                  | 3-10 |

| Fig. 3.7 Simulated (left) and experimentally (right) obtained common mode voltage at $m_a = 0.4$ for CSPWM, Scale: X-axis: 10 ms/div, Y-axis: 50 V/div                                      | 3-10 |

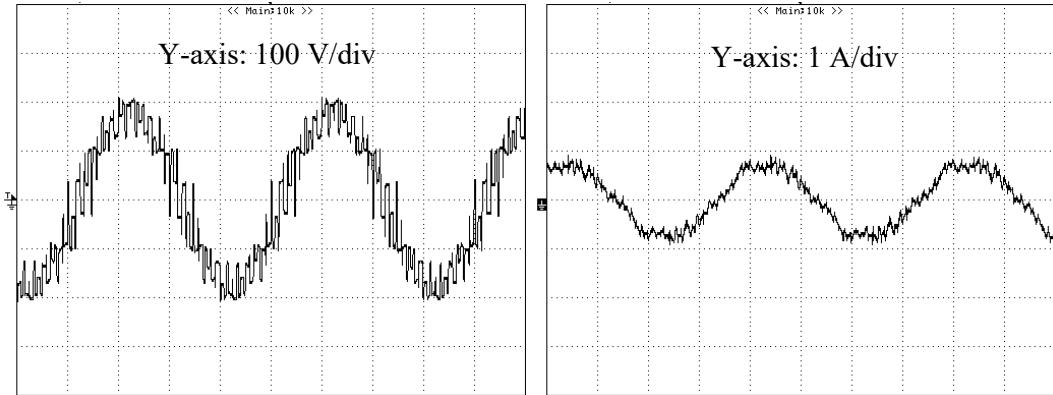

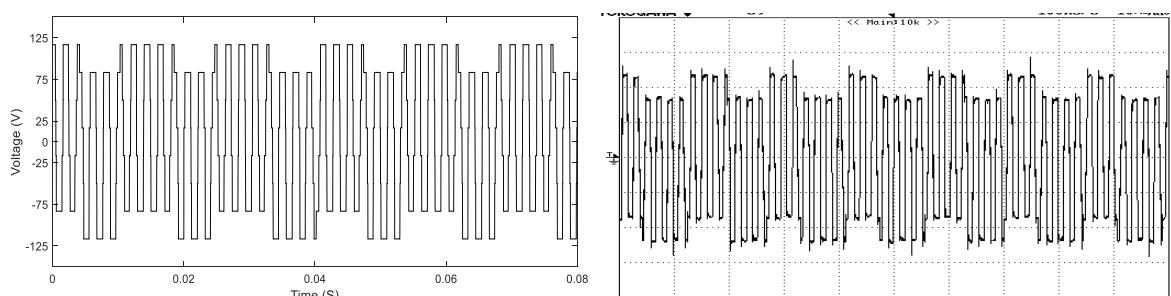

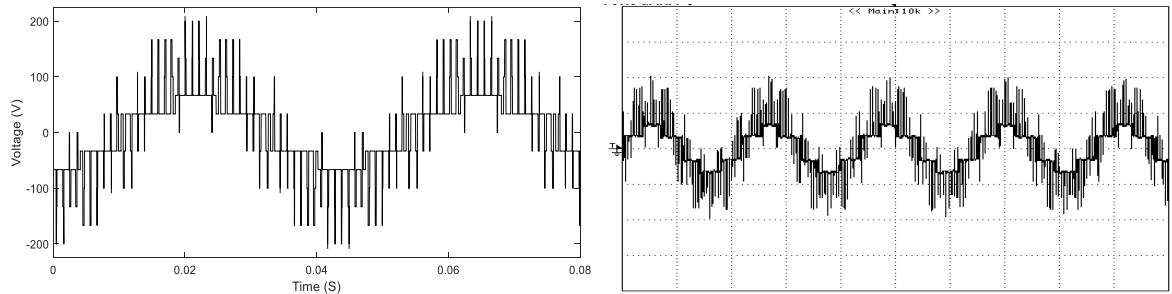

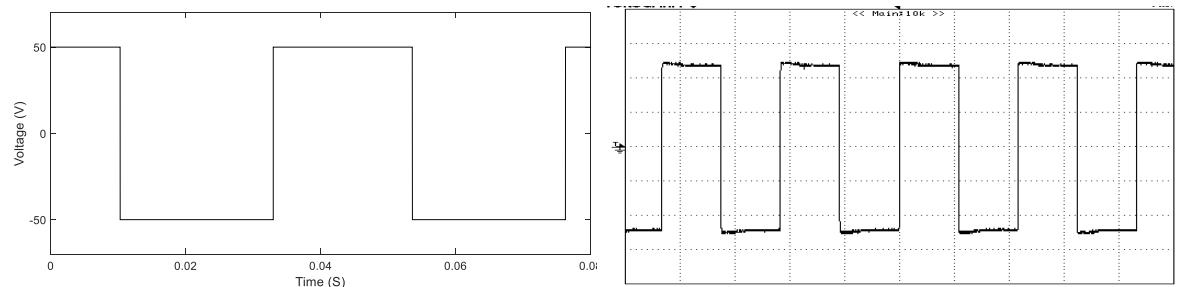

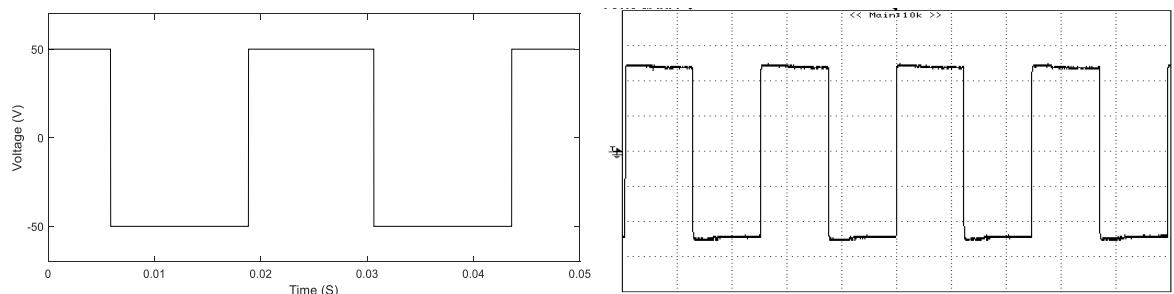

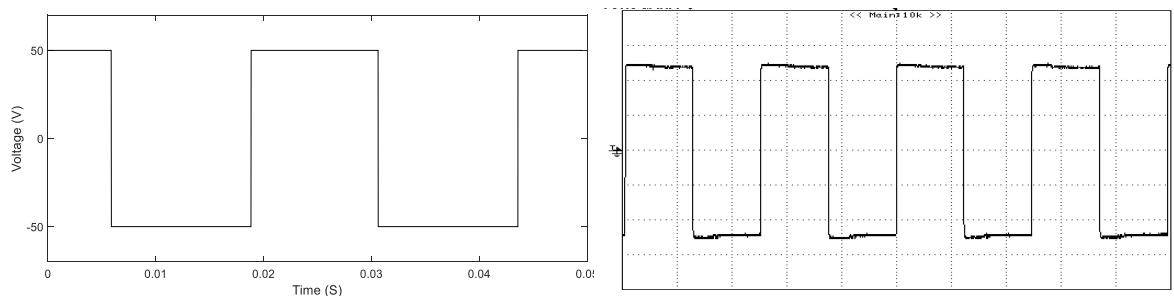

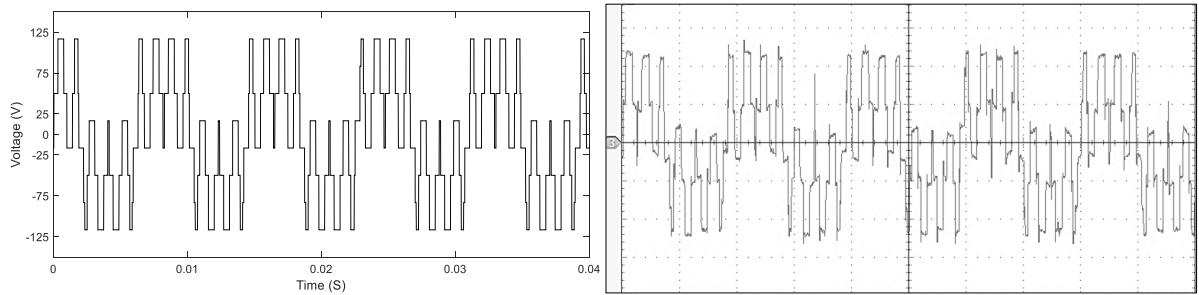

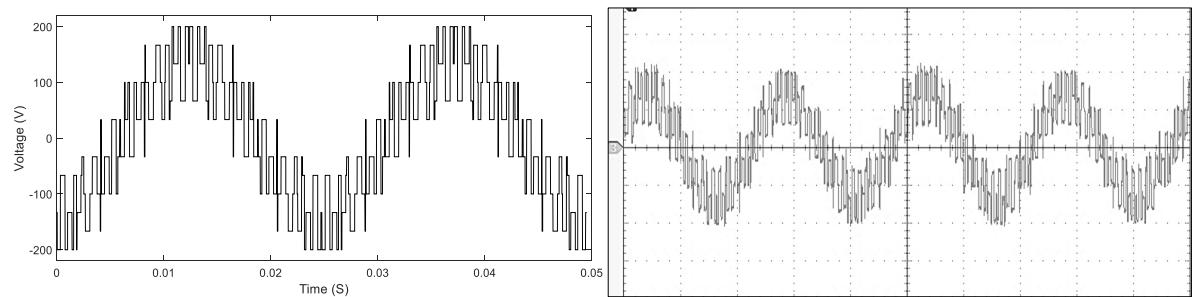

Fig. 3.8 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 0.4$  for CSPWM, Scale: X-axis: 20 ms/div, Y-axis: 100 V/div 3-11

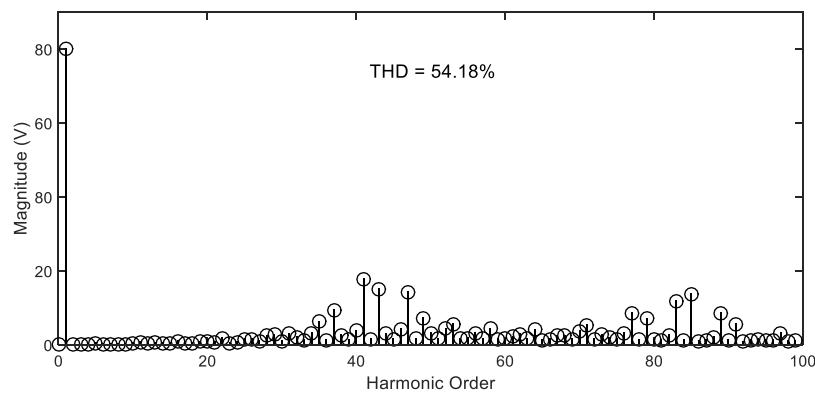

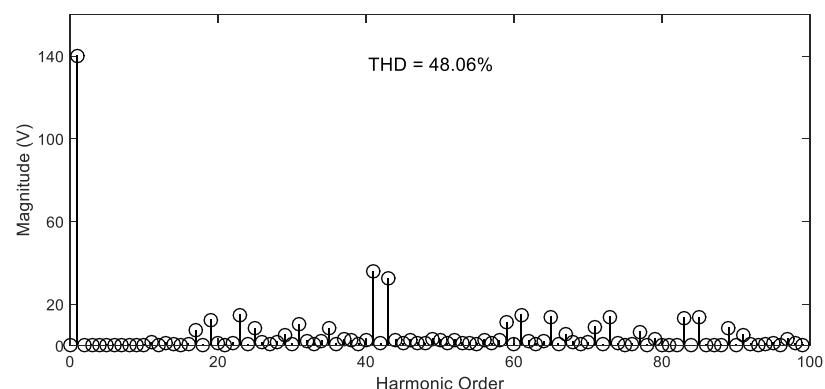

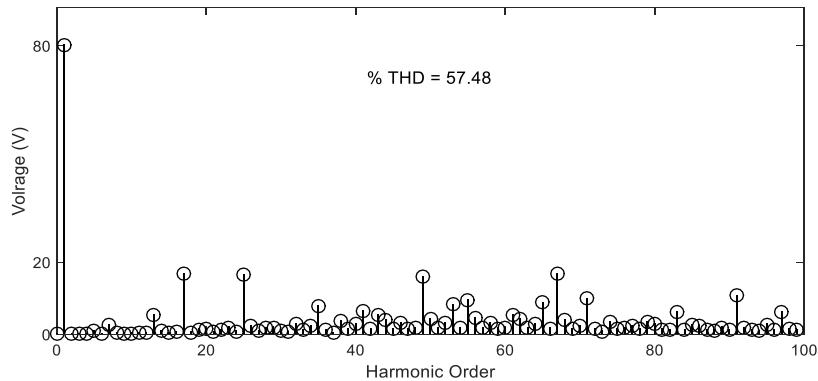

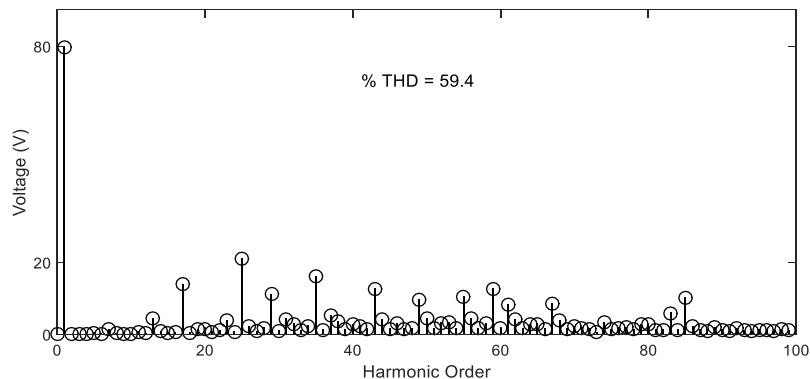

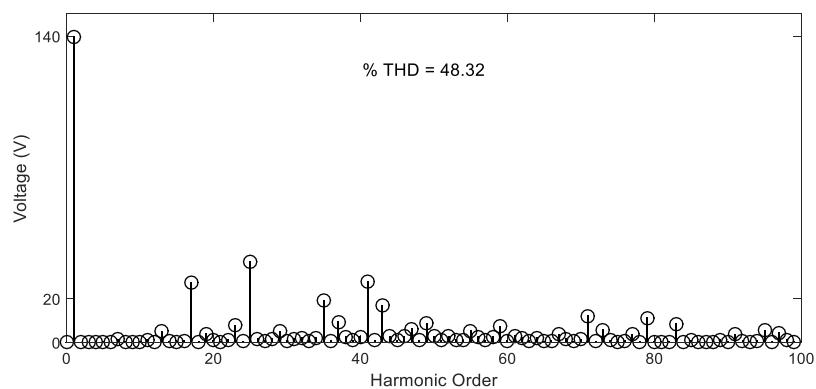

Fig. 3.9 FFT analysis of Phase-A voltage at  $m_a = 0.4$  for CSPWM 3-11

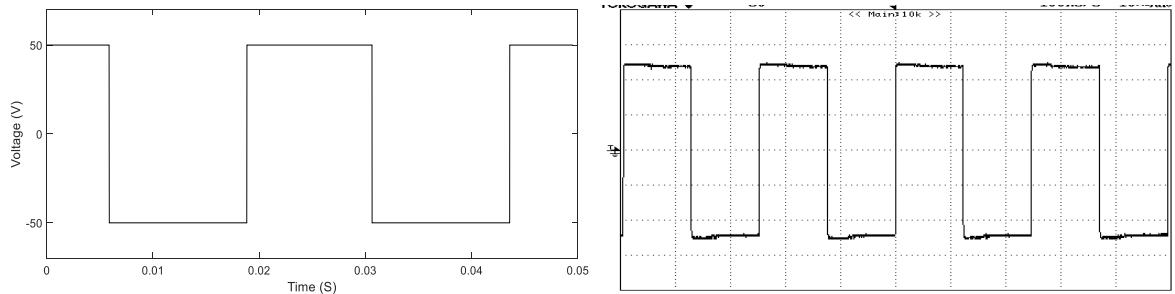

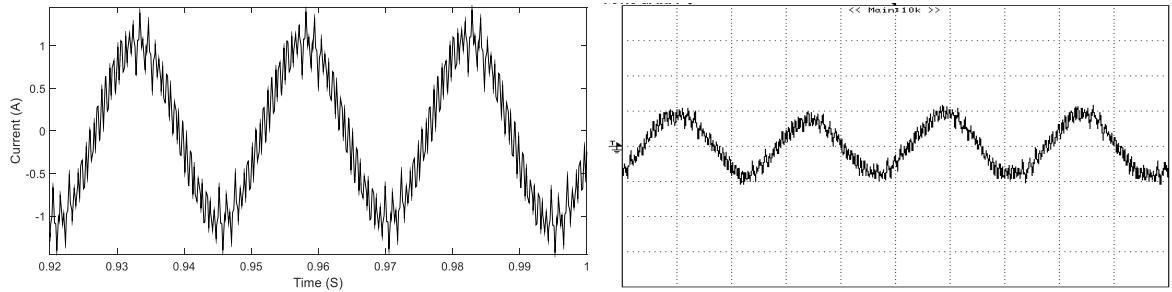

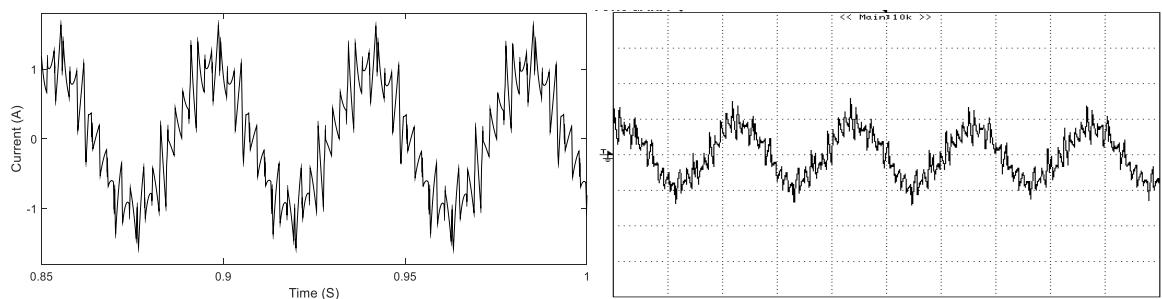

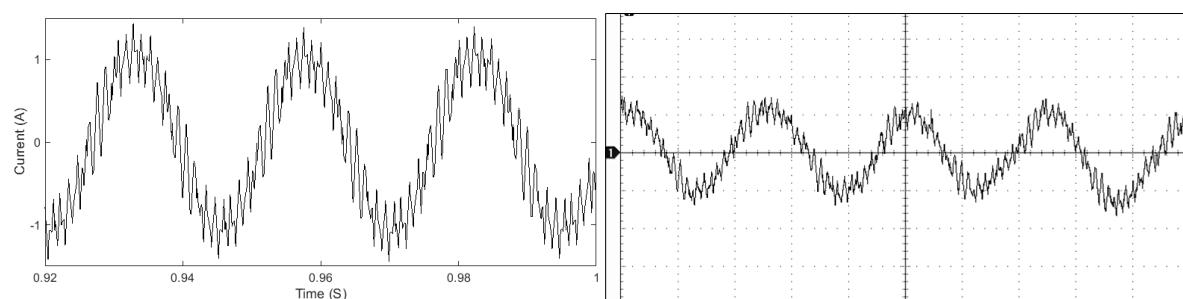

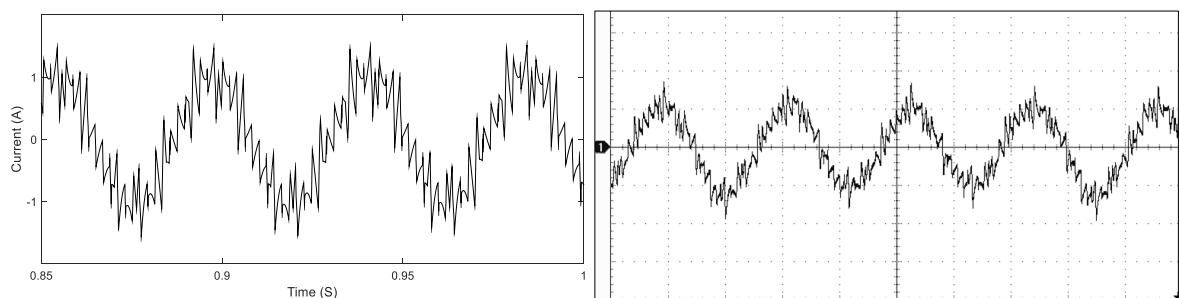

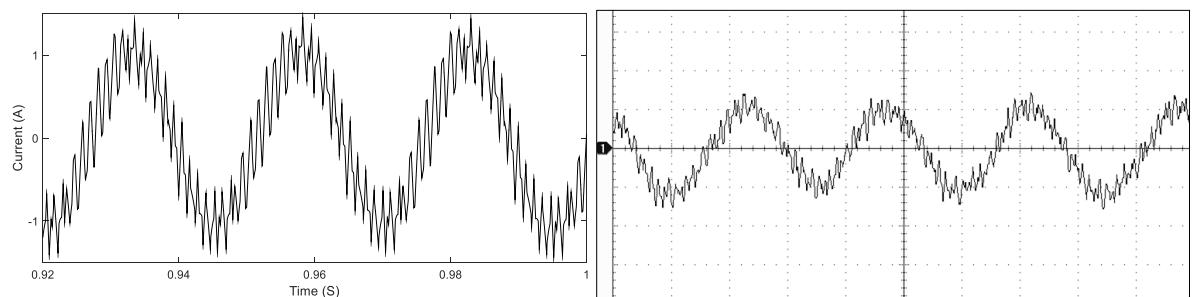

Fig. 3.10 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 0.4$  for CSPWM, Scale: X-axis: 20 ms/div, Y-axis: 1 A/div 3-11

Fig. 3.11 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 0.7$  for CSPWM, Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-11

Fig. 3.12 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at  $m_a = 0.7$  for CSPWM, Scale: X-axis: 10 ms/div, Y-axis: 20 V/div 3-12

Fig. 3.13 Simulated (left) and experimentally (right) obtained common mode voltage at  $m_a = 0.7$  for CSPWM, Scale: X-axis: 5 ms/div, Y-axis: 50 V/div 3-12

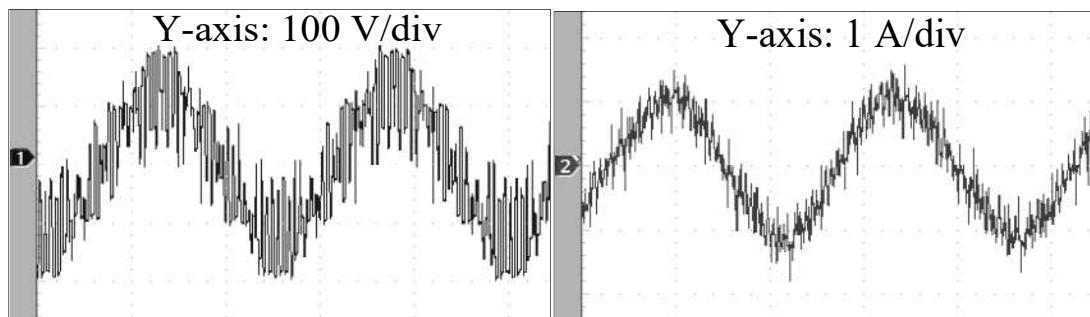

Fig. 3.14 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 0.7$  for CSPWM, Scale: X-axis: 10 ms/div, Y-axis: 100 V/div 3-12

Fig. 3.15 FFT analysis of Phase-A voltage at  $m_a = 0.7$  for CSPWM 3-12

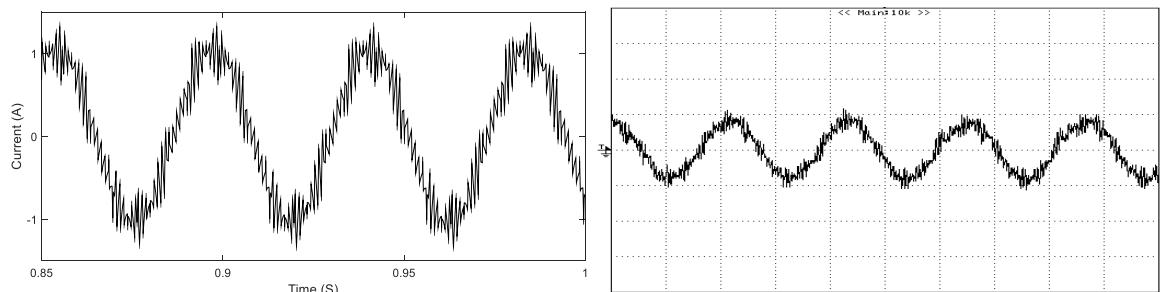

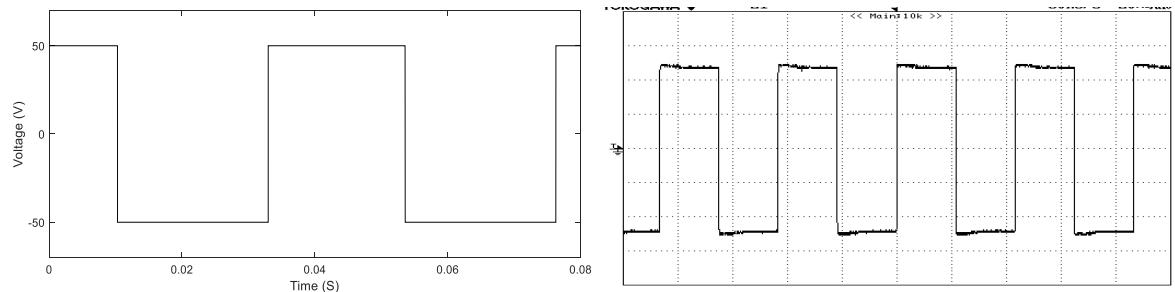

Fig. 3.16 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 0.7$  for CSPWM, Scale: X-axis: 10 ms/div, Y-axis: 1 A/div 3-13

Fig. 3.17 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 1$  for CSPWM. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-13

Fig. 3.18 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at  $m_a = 1$  for CSPWM. Scale: X-axis: 10 ms/div, Y-axis: 20 V/div 3-13

Fig. 3.19 Simulated (left) and experimentally (right) obtained common mode voltage at  $m_a = 1$  for CSPWM. Scale: X-axis: 5 ms/div, Y-axis: 50 V/div 3-13

Fig. 3.20 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 1$  for CSPWM. Scale: X-axis: 10 ms/div, Y-axis: 100 V/div 3-14

Fig. 3.21 FFT analysis of Phase-A voltage at  $m_a = 1$  for CSPWM 3-14

Fig. 3.22 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 1$  for CSPWM. Scale: X-axis: 10 ms/div, Y-axis: 1 A/div 3-14

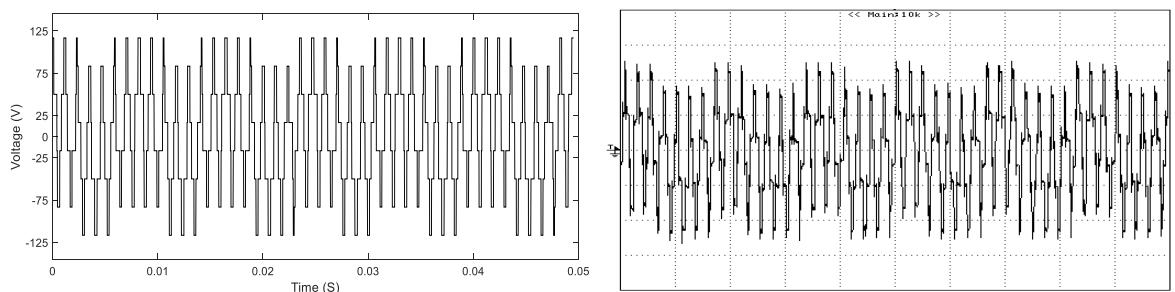

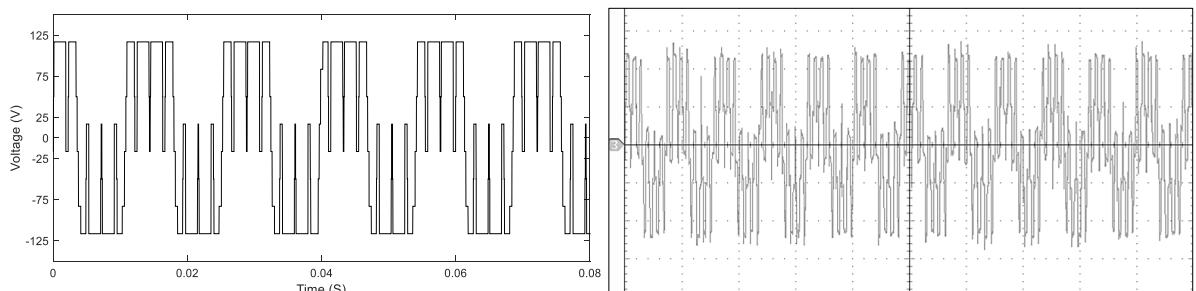

Fig. 3.23 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 0.4$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-15

Fig. 3.24 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at  $m_a = 0.4$  for PCPWM-1. Scale: X-axis: 20 ms/div, Y-axis: 20 V/div 3-15

Fig. 3.25 Simulated (left) and experimentally (right) obtained common mode voltage at  $m_a = 0.4$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-15

Fig. 3.26 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 0.4$  for PCPWM-1. Scale: X-axis: 20 ms/div, Y-axis: 100V/div 3-15

Fig. 3.27 FFT analysis of Phase-A voltage at  $m_a = 0.4$  for PCPWM-1 3-16

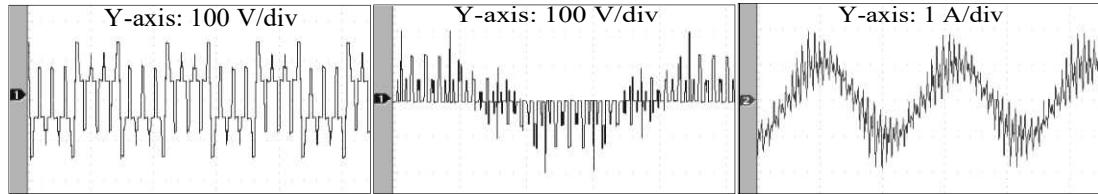

Fig. 3.28 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 0.4$  for PCPWM-1. Scale: X-axis: 20 ms/div, Y-axis: 1 A/div 3-16

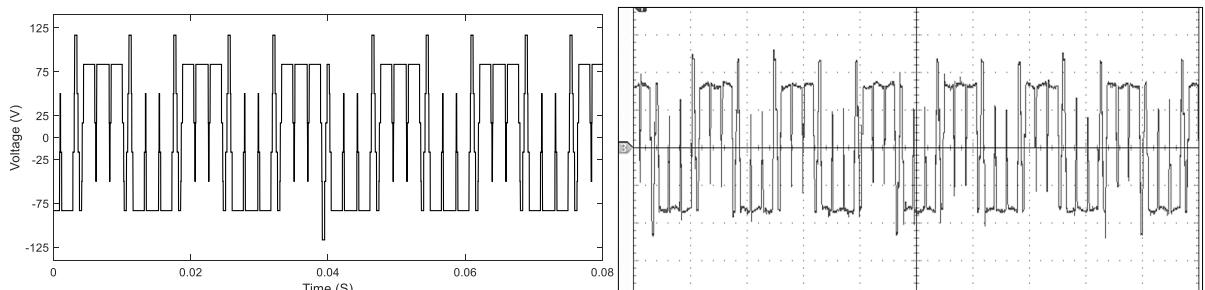

Fig. 3.29 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 0.7$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-16

Fig. 3.30 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at  $m_a = 0.7$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 20 V/div 3-16

Fig. 3.31 Simulated (left) and experimentally (right) obtained common mode voltage at  $m_a = 0.7$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-17

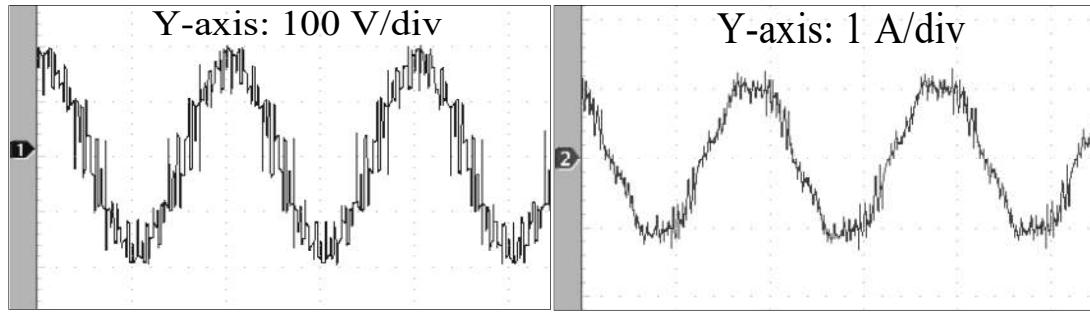

Fig. 3.32 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 0.7$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 100 V/div 3-17

Fig. 3.33 FFT analysis of Phase-A voltage at  $m_a = 0.7$  for PCPWM-1 3-17

Fig. 3.34 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 0.7$  for PCPWM-1. Scale: X-axis: 10 ms/div, Y-axis: 1 A/div 3-17

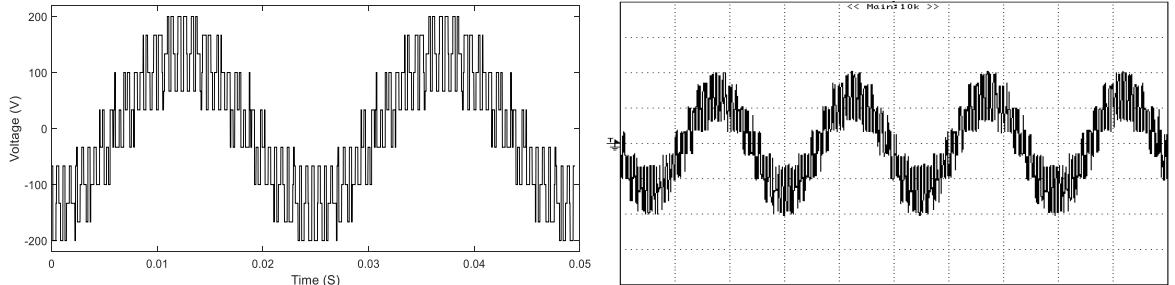

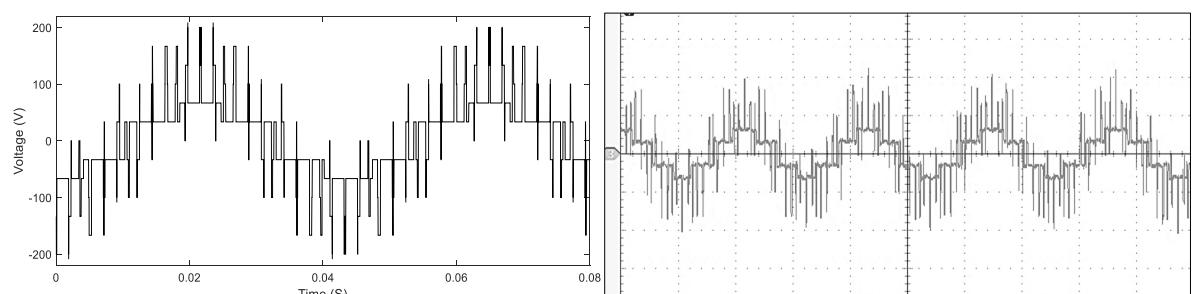

Fig. 3.35 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 0.4$  for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-18

Fig. 3.36 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at  $m_a = 0.4$  for PCPWM-2. Scale: X-axis: 20 ms/div, Y-axis: 20 V/div 3-18

Fig. 3.37 Simulated (left) and experimentally (right) obtained common mode voltage at  $m_a = 0.4$  for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-18

Fig. 3.38 Simulated (left) and experimentally (right) obtained Phase-A voltage at  $m_a = 0.4$  for PCPWM-2. Scale: X-axis: 20 ms/div, Y-axis: 100 V/div 3-18

Fig. 3.39 FFT analysis of Phase-A voltage at  $m_a = 0.4$  for PCPWM-2 3-19

Fig. 3.40 Simulated (left) and experimentally (right) obtained Phase-A Current at  $m_a = 0.4$  for PCPWM-2. Scale: X-axis: 20 ms/div, Y-axis: 1 A/div 3-19

Fig. 3.41 Simulated (left) and experimentally (right) obtained inverter-1 pole voltage at  $m_a = 0.7$  for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 50 V/div 3-19

|                                                                                                                                                               |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3.42 Simulated (left) and experimentally (right) obtained inverter-2 pole voltage at $m_a = 0.7$ for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 20 V/div | 3-19 |

| Fig. 3.43 Simulated (left) and experimentally (right) obtained common mode voltage at $m_a = 0.7$ for PCPWM-2. Scale: X-axis: 5 ms/div, Y-axis: 50 V/div      | 3-20 |

| Fig. 3.44 Simulated (left) and experimentally (right) obtained Phase-A voltage at $m_a = 0.7$ for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 100 V/div        | 3-20 |

| Fig. 3.45 FFT analysis of Phase-A voltage at $m_a = 0.7$ for PCPWM-2                                                                                          | 3-20 |

| Fig. 3.46 Simulated (left) and experimentally (right) obtained Phase-A Current at $m_a = 0.7$ for PCPWM-2. Scale: X-axis: 10 ms/div, Y-axis: 1 A/div          | 3-20 |

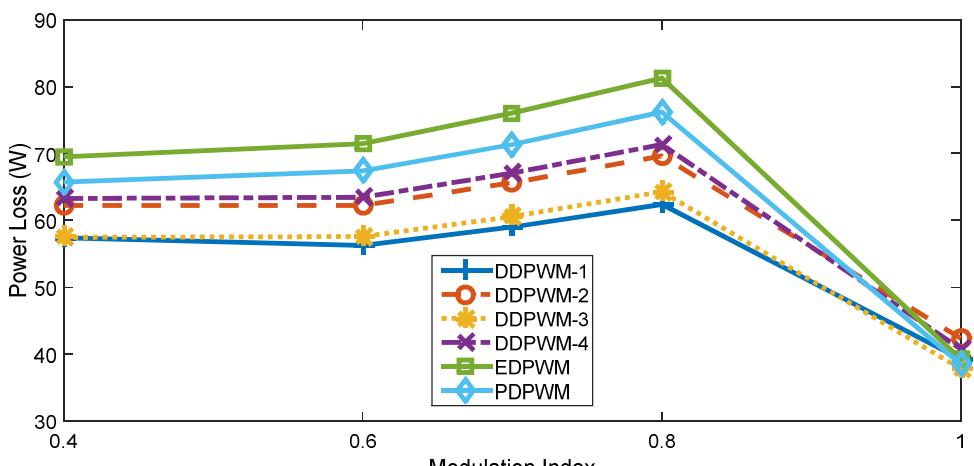

| Fig. 3.47 Dual-inverter switching power loss of four – level OEWIMD                                                                                           | 3-23 |

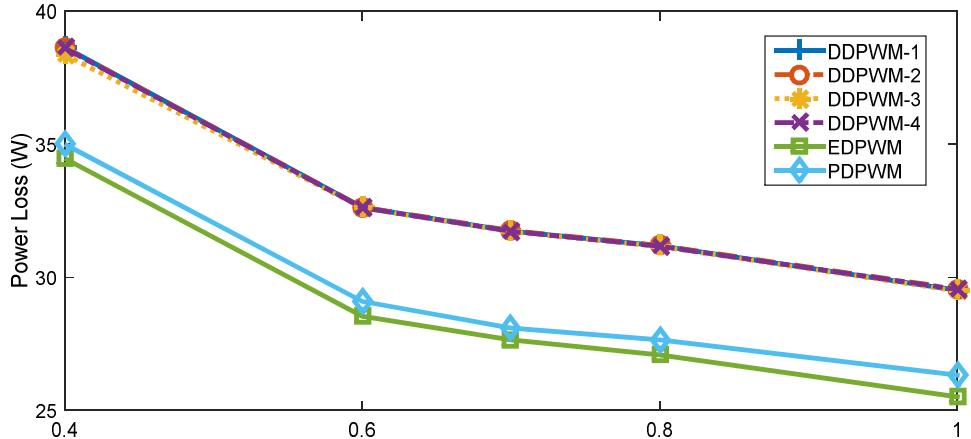

| Fig. 3.48 Dual-inverter conduction power loss of four – level OEWIMD                                                                                          | 3-24 |

| Fig. 3.49 Dual-inverter power loss of four – level OEWIMD                                                                                                     | 3-24 |

| Fig. 3.50 Modulation index vs Phase Voltage THD of four PWM Techniques                                                                                        | 3-25 |

| Fig. 3.51 Modulation Index vs WTHD of four PWM Techniques                                                                                                     | 3-26 |

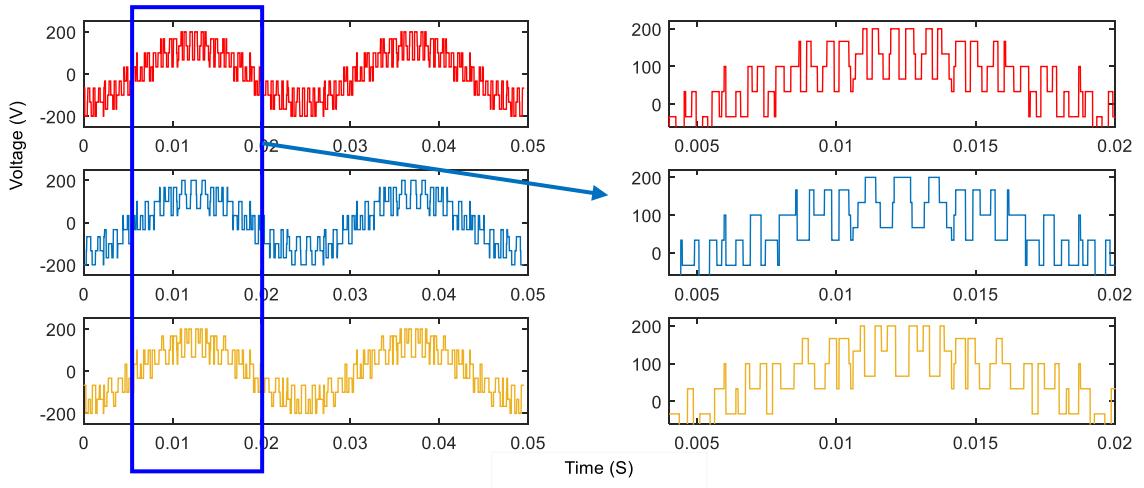

| Fig. 3.52 Phase voltage waveforms with waveform symmetries CSPWM (top), PCPWM-1 (middle) and PCPWM-2 (bottom)                                                 | 3-27 |

| Fig. 4.1 Four-level OEWIM with isolated dc-power supplies                                                                                                     | 4-2  |

| Fig. 4.2 Proposed topology for 4-L OEWIMD                                                                                                                     | 4-3  |

| Fig. 4.3 Individual space vector locations of VSIs-1 (left) and 2 (right) (not drawn to scale)                                                                | 4-4  |

| Fig. 4.4 Resultant space vector diagram of proposed 4-L OEWIMD                                                                                                | 4-4  |

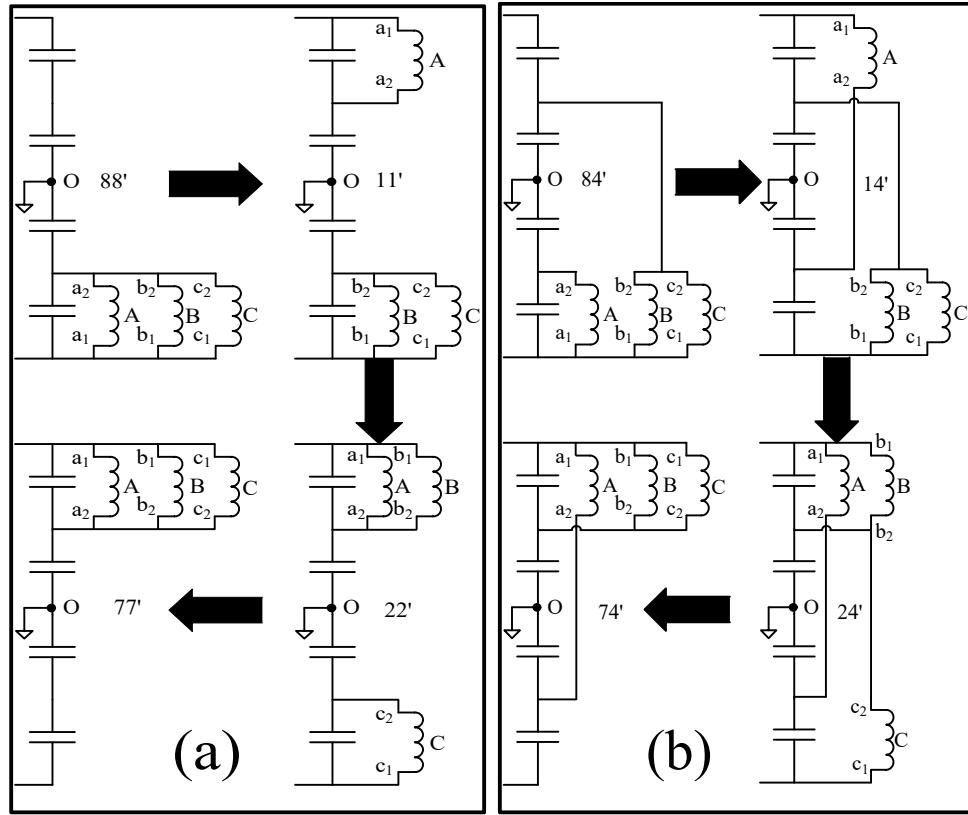

| Fig. 4.5 OEWIM winding connections for the switching combination 11' (left), 12' (right)                                                                      | 4-6  |

|           |                                                                                                                                                                                                |      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 4.6  | OEWIM phase connections during mode-by-mode transition: (a) two-level operation (b) four-level operation                                                                                       | 4-7  |

| Fig. 4.7  | Principle operation of NICSAZE SVPWM technique                                                                                                                                                 | 4-12 |

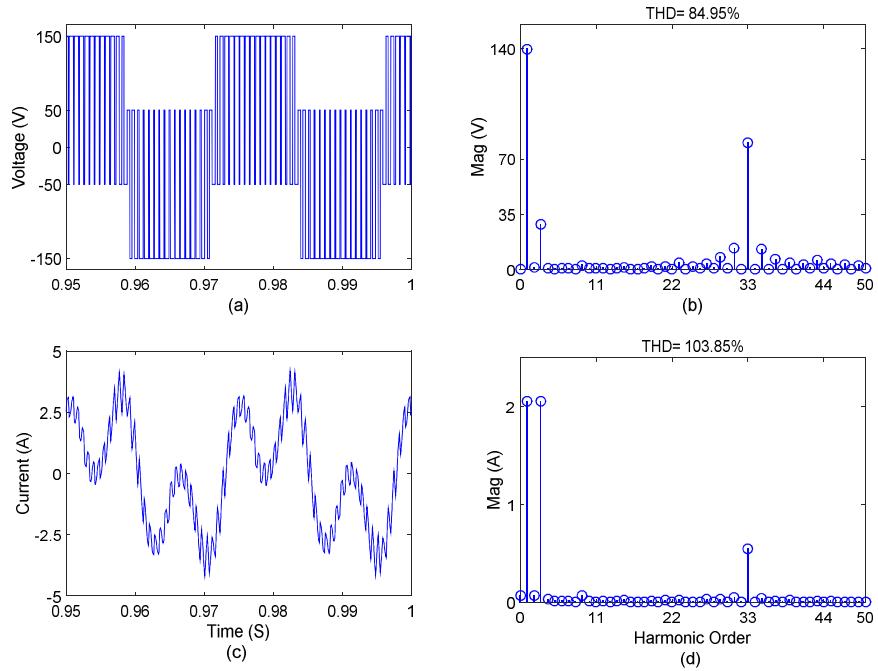

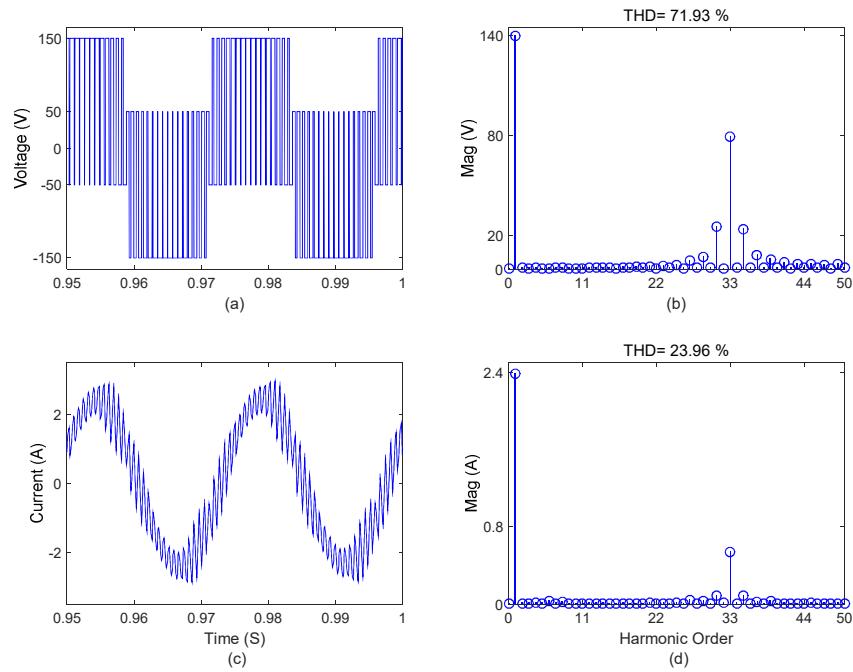

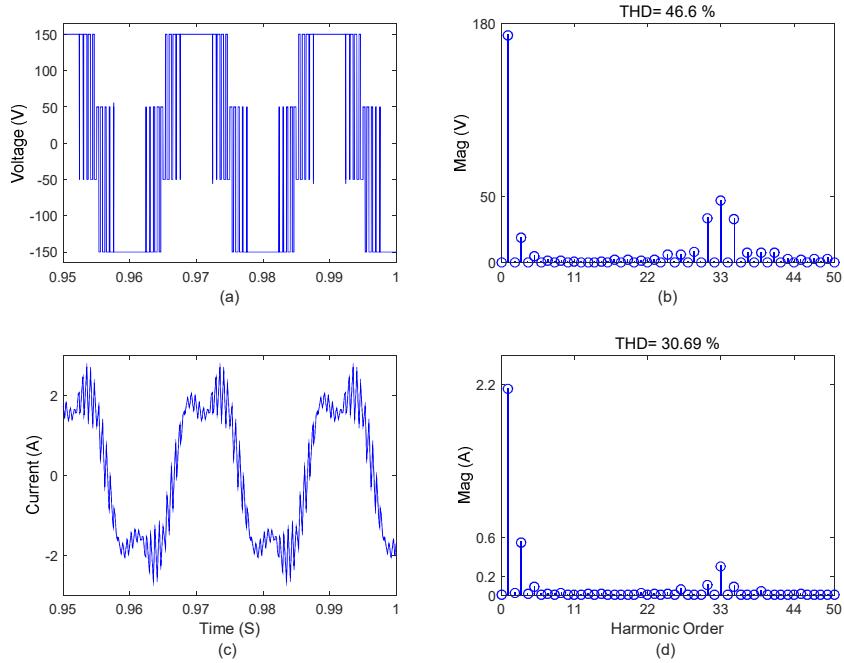

| Fig. 4.8  | Simulation results for center spaced SVPWM technique at $m_a = 0.7$ : (a) $v_{a_1a_2}$ (b) $v_{a_1a_2}$ FFT analysis (c) $i_a$ and (d) $i_a$ FFT analysis                                      | 4-18 |

| Fig. 4.9  | Simulation results for DSAZE PWM technique at $m_a = 0.7$ : (a) $v_{a_1a_2}$ (b) $v_{a_1a_2}$ FFT analysis (c) $i_a$ and (d) $i_a$ FFT analysis                                                | 4-18 |

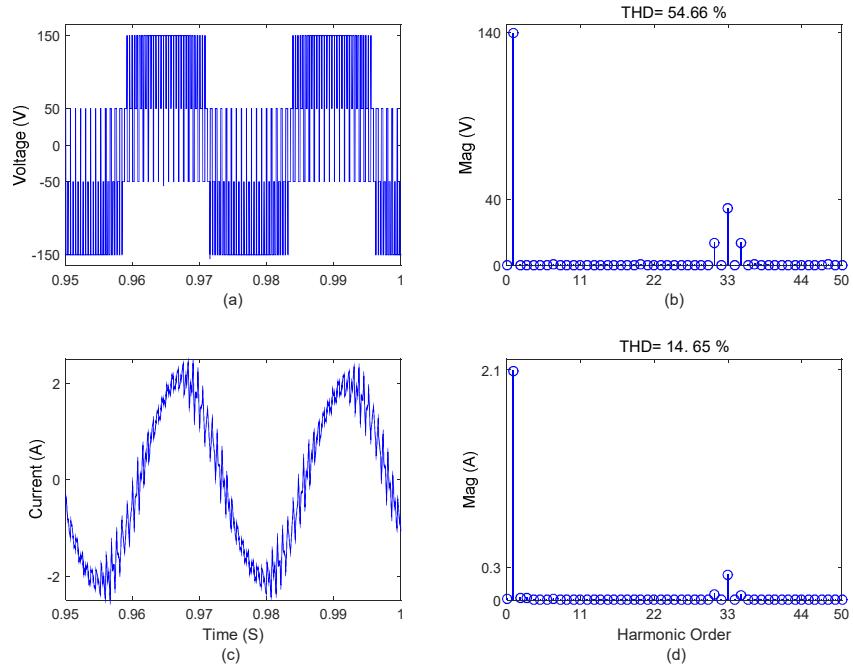

| Fig. 4.10 | Simulation results for DSAZE PWM technique at $m_a = 1$ : (a) $v_{a_1a_2}$ (b) $v_{a_1a_2}$ FFT analysis (c) $i_a$ and (d) $i_a$ FFT analysis                                                  | 4-19 |

| Fig. 4.11 | Simulation results for NICSAZE PWM technique at $m_a = 0.7$ : (a) $v_{a_1a_2}$ (b) $v_{a_1a_2}$ FFT analysis (c) $i_a$ and (d) $i_a$ FFT analysis                                              | 4-19 |

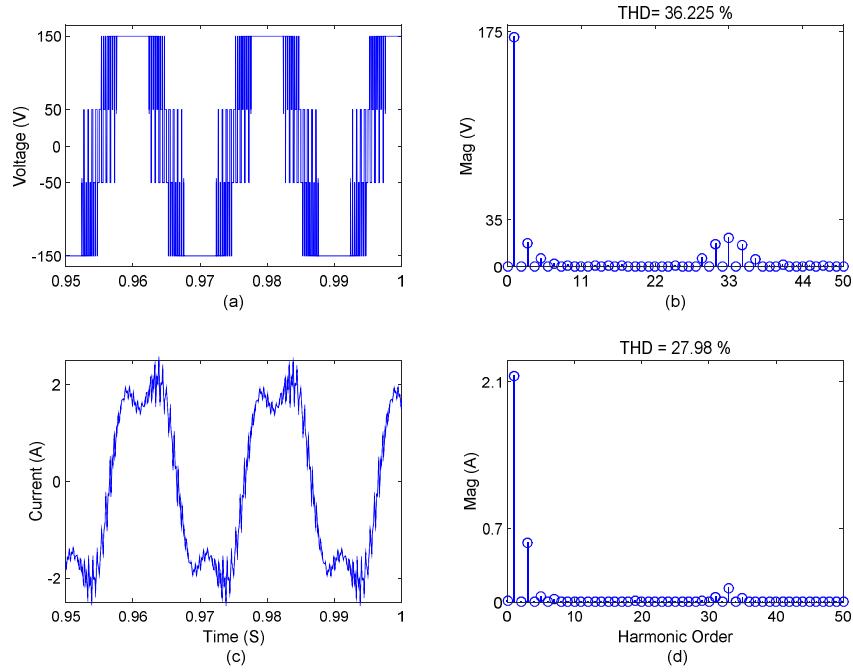

| Fig. 4.12 | Simulation results for NICSAZE PWM technique at $m_a = 1$ : (a) $v_{a_1a_2}$ (b) $v_{a_1a_2}$ FFT analysis (c) $i_a$ and (d) $i_a$ FFT analysis                                                | 4-20 |

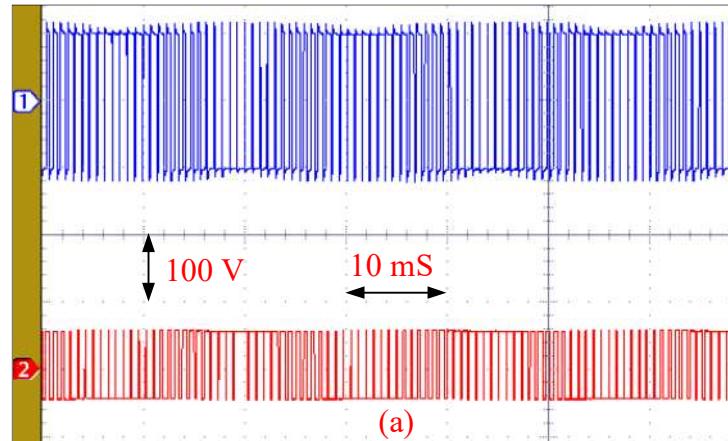

| Fig. 4.13 | Experimental results for Center-Spaced SVPWM technique at $m_a = 0.7$ : (a) $v_{a_1a_2}$ (top) and $i_a$ (bottom)                                                                              | 4-21 |

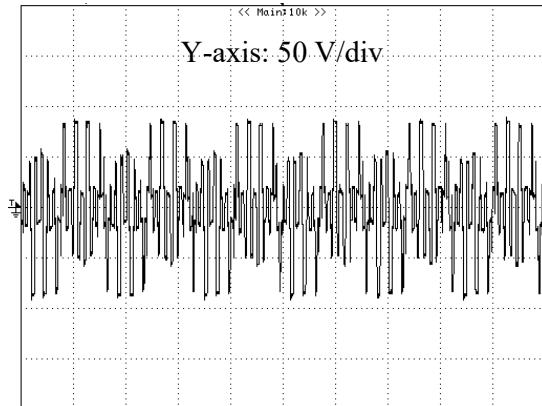

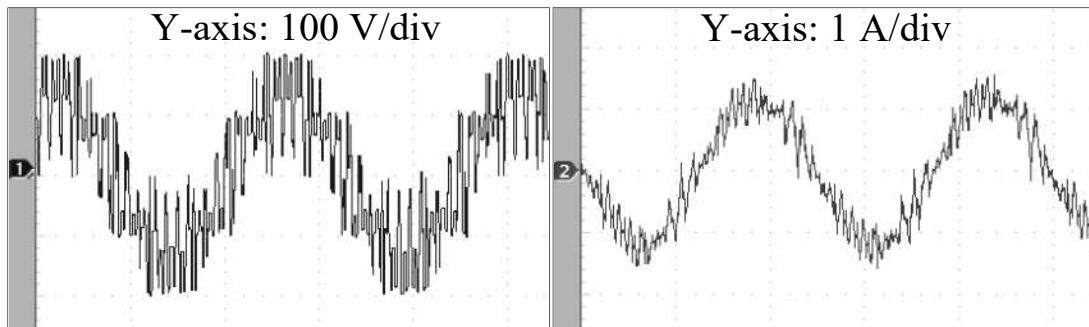

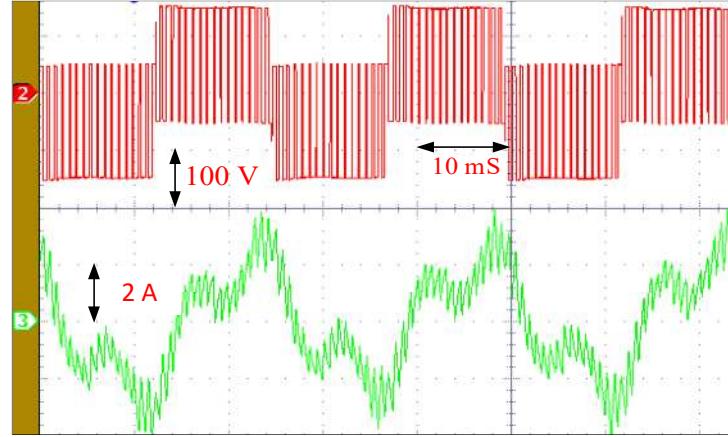

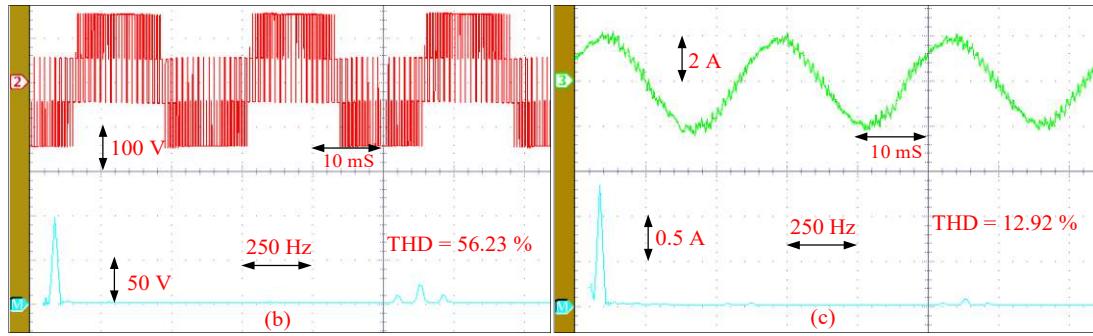

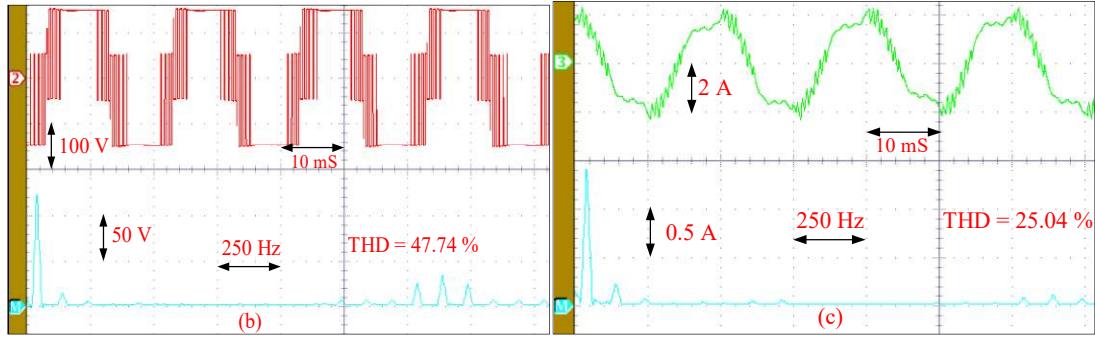

| Fig. 4.14 | Experimental results for DSAZE PWM technique at $m_a = 0.7$ : (a) Pole voltage of VSI-1 (top) and 2 (bottom), (b) $v_{a_1a_2}$ and its harmonic spectrum (c) $i_a$ and its harmonic spectrum   | 4-22 |

| Fig. 4.15 | Experimental results for DSAZE PWM technique at $m_a = 1$ : (a) Pole voltage of VSI-1 (top) and 2 (bottom), (b) $v_{a_1a_2}$ and its harmonic spectrum (c) $i_a$ and its harmonic spectrum     | 4-22 |

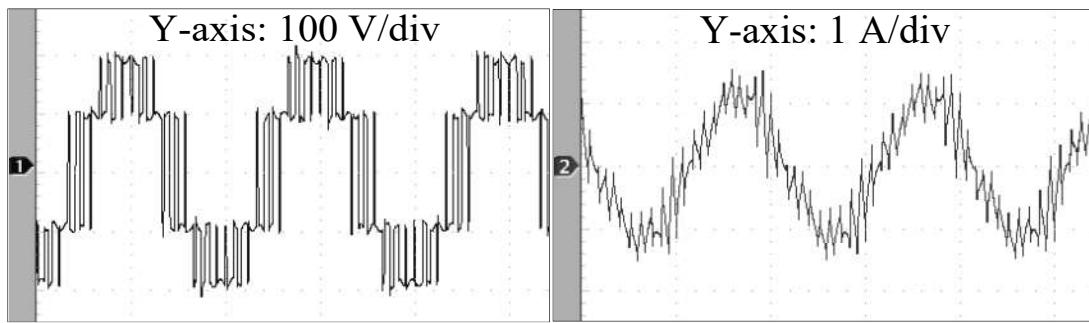

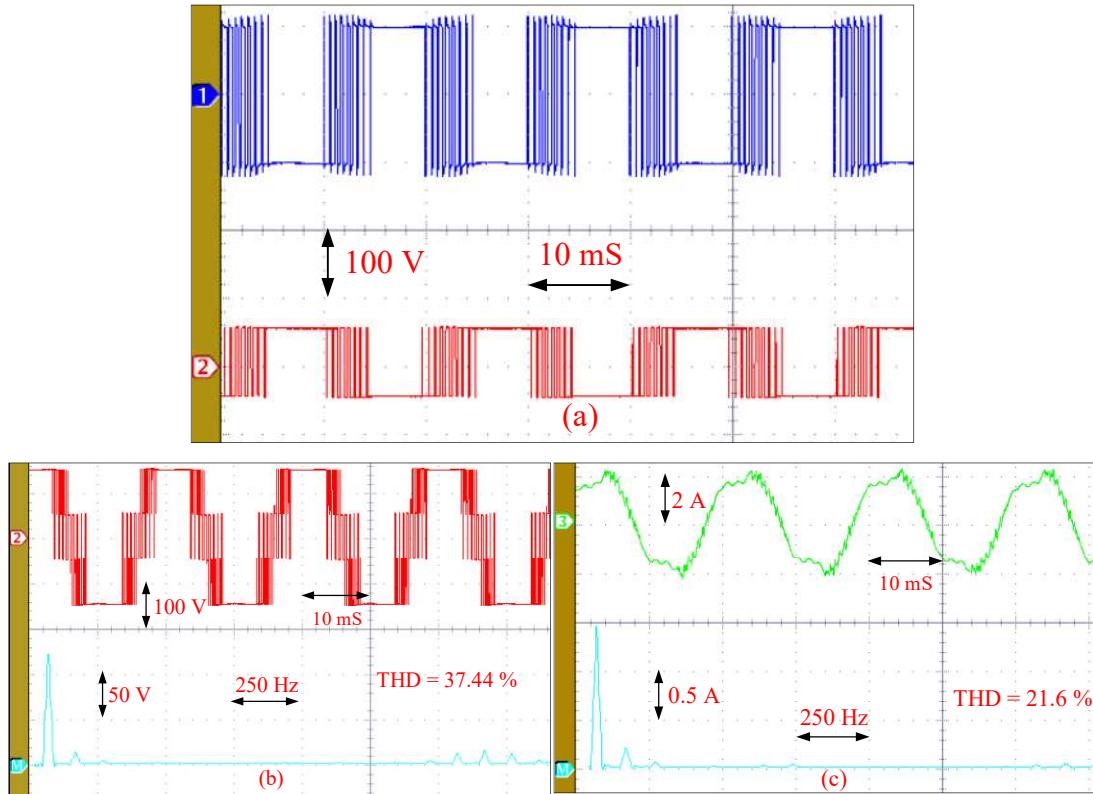

| Fig. 4.16 | Experimental results for NICSAZE PWM technique at $m_a = 0.7$ : (a) Pole voltage of VSI-1 (top) and 2 (bottom), (b) $v_{a_1a_2}$ and its harmonic spectrum (c) $i_a$ and its harmonic spectrum | 4-23 |

|                                                                                                                                                                                                        |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 4.17 Experimental results for NICSAZE PWM technique at $m_a = 1$ : (a) Pole voltage of VSI-1 (top) and 2 (bottom), (b) $v_{a_1a_2}$ and its harmonic spectrum (c) $i_a$ and its harmonic spectrum | 4-24 |

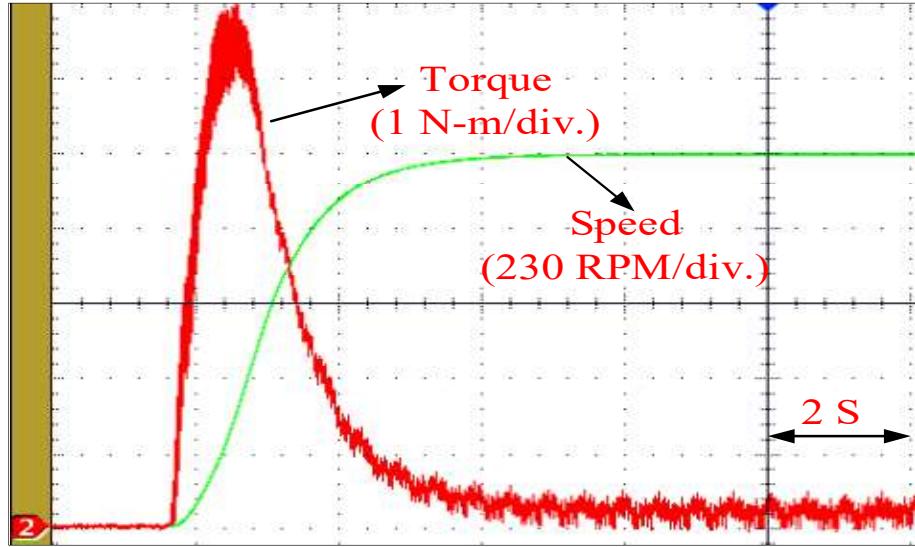

| Fig. 4.18 Experimental torque and speed waveforms of OEWIMD with NICSAZE PWM technique at $m_a = 0.7$                                                                                                  | 4-25 |

| Fig. 4.19 Distribution of dc-link voltages for the proposed topology with unbalance                                                                                                                    | 4-26 |

| Fig. 4.20 (a) Unbalanced pole voltages of VSI-I (top), VSI-II (bottom), (b) balanced phase voltage and (c) OEWIMD phase current in loaded conditions at $m_a = 0.6$ with lower dc-link voltage         | 4-27 |

| Fig. 4.21 Simulation results: (a) $P_{sw}$ versus $m_a$ (b) $P_{Con}$ versus $m_a$ (c) $P_{DI}$ versus $m_a$                                                                                           | 4-29 |

| Fig. 5.1 Circuit diagram of four-level OEWIMD                                                                                                                                                          | 5-3  |

| Fig. 5.2 Dual-inverter system overall space vector diagram                                                                                                                                             | 5-4  |

| Fig. 5.3 Block diagram of PCC                                                                                                                                                                          | 5-7  |

| Fig. 5.4 Voltage vector selection using NSHC for OEWIMD                                                                                                                                                | 5-12 |

| Fig. 5.5 Flow chart for the proposed PCC strategy                                                                                                                                                      | 5-14 |

| Fig. 5.6 Block diagram of proposed PCC for a four-level OEWIMD                                                                                                                                         | 5-14 |

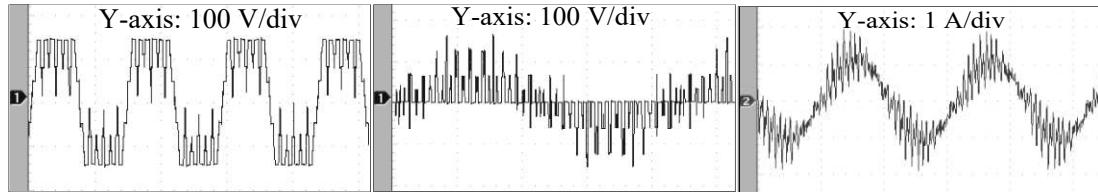

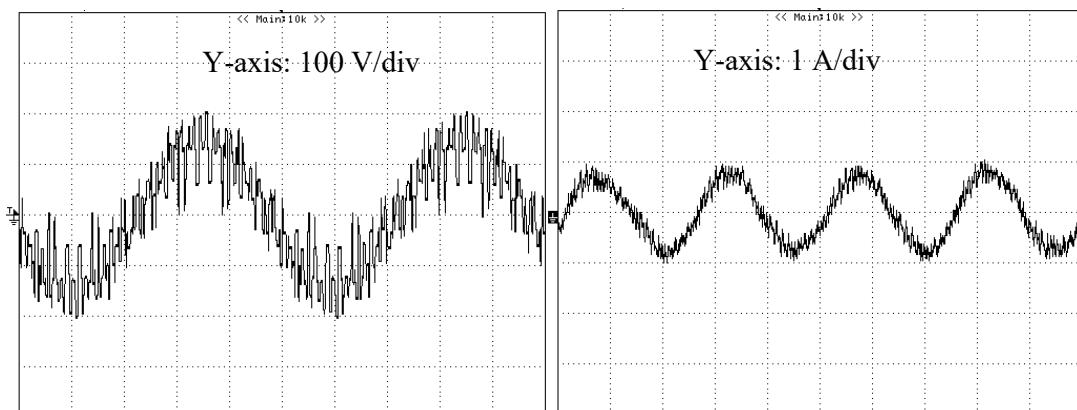

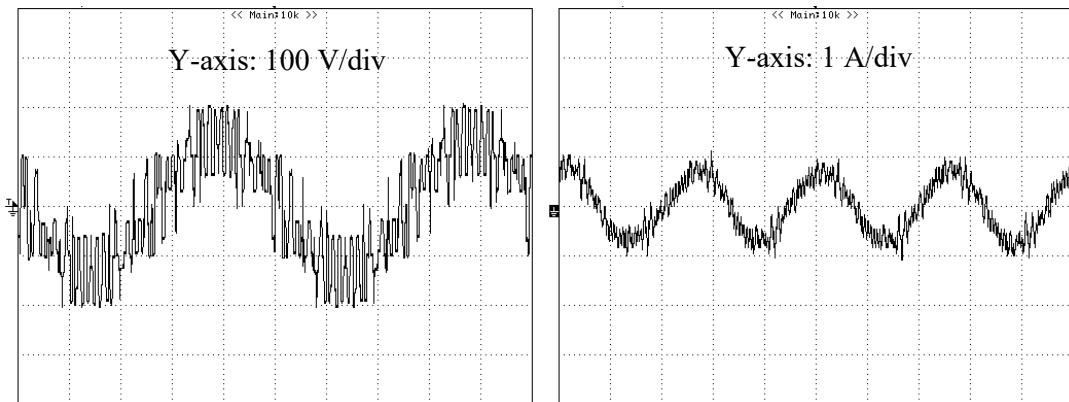

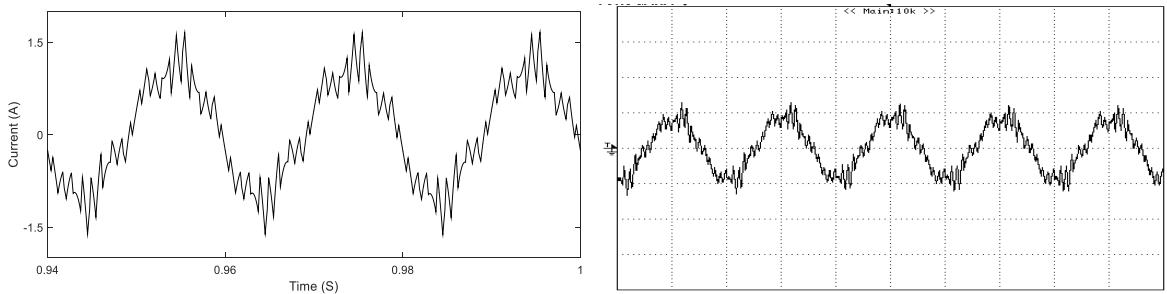

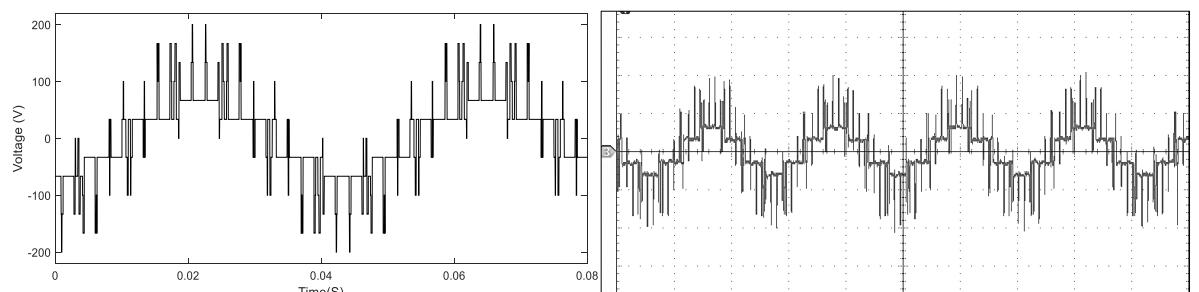

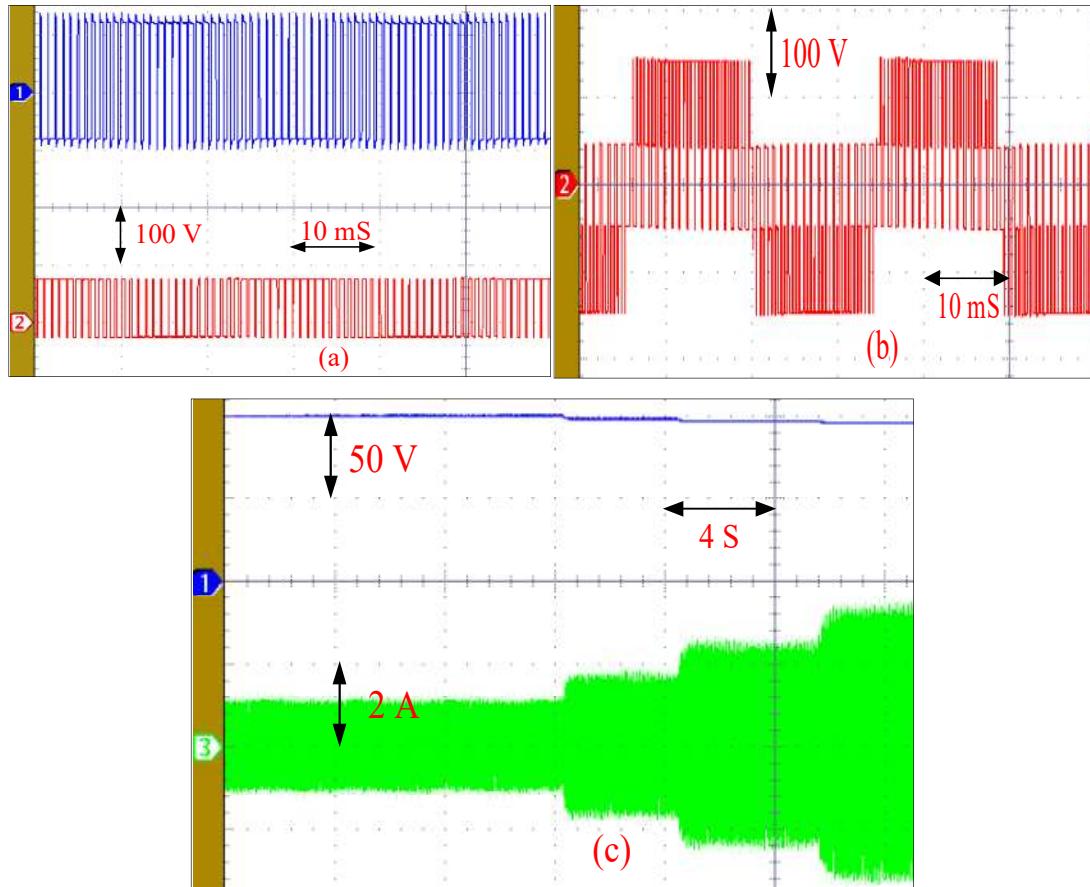

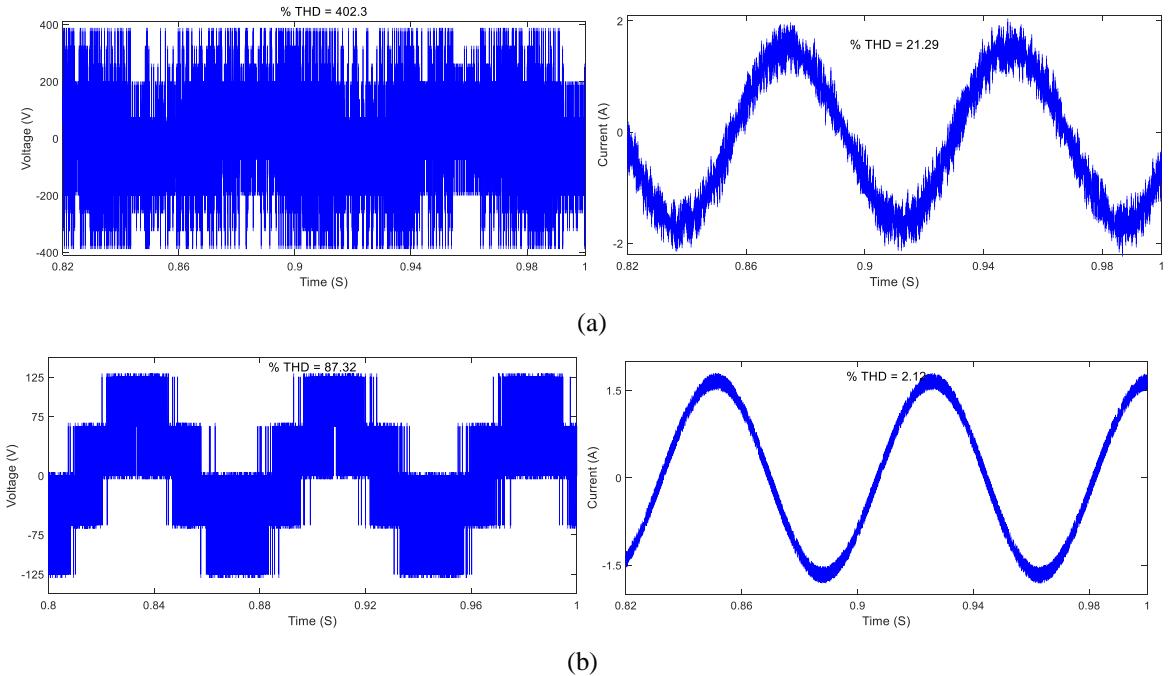

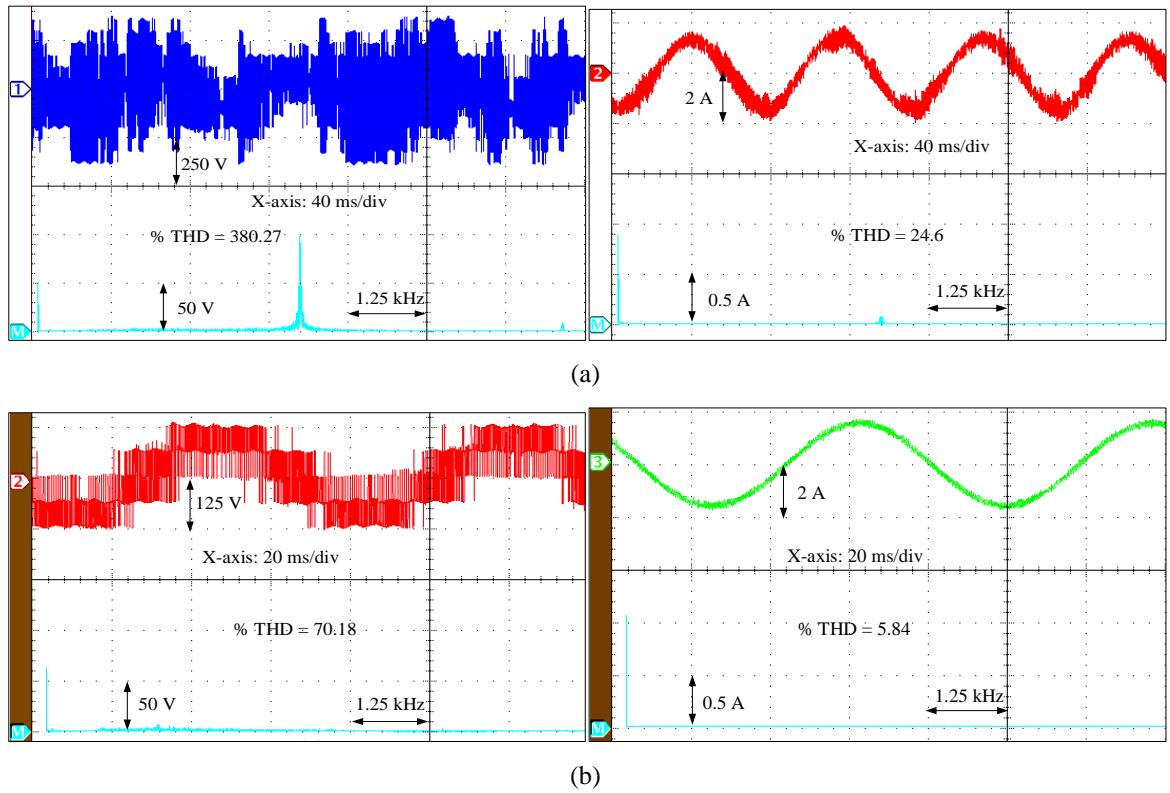

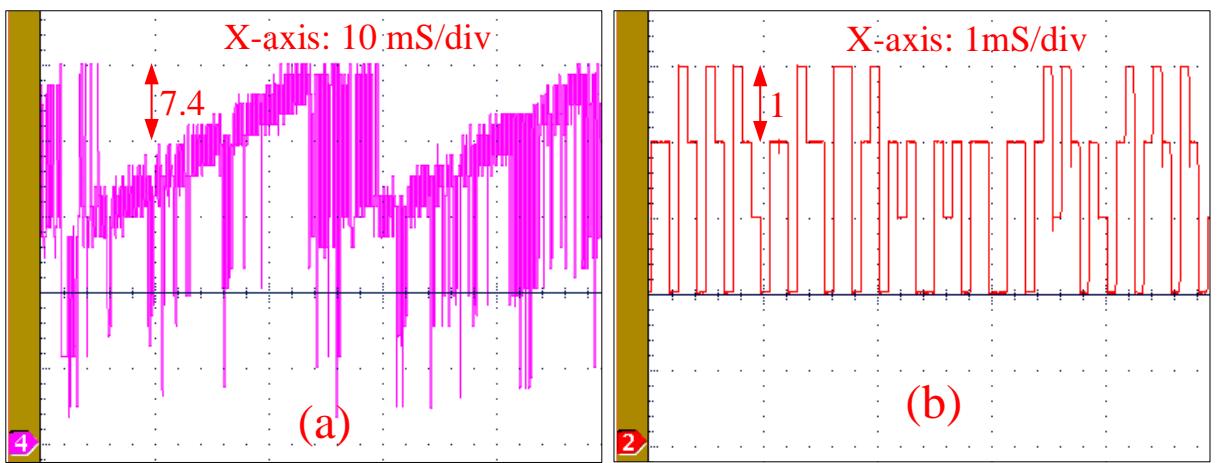

| Fig. 5.7 Simulation results of phase voltage (left) and current (right) at speed of 400 RPM. (a) Conventional PCC (b) Proposed PCC                                                                     | 5-16 |

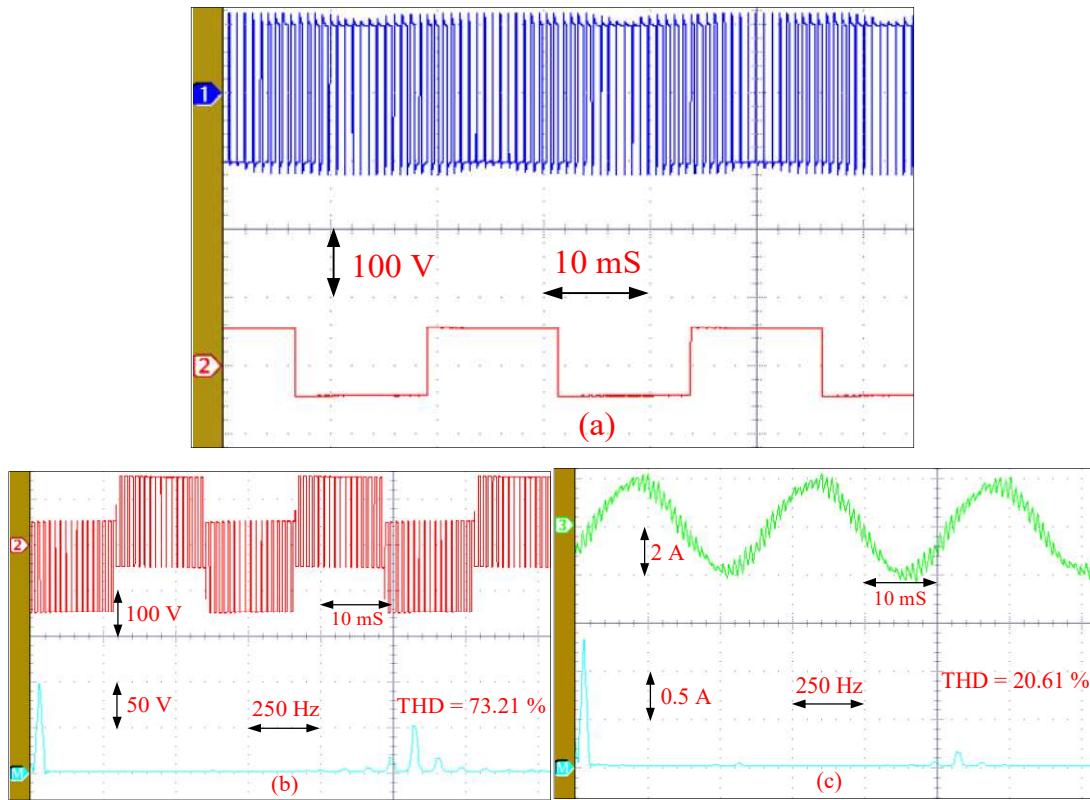

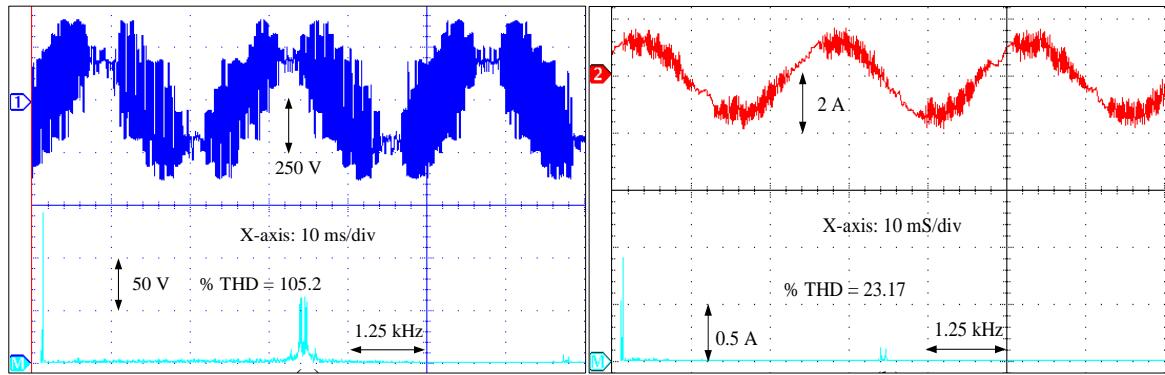

| Fig. 5.8 Experimental phase voltage (left) and current (right) with FFT analysis at speed of 400 RPM. (a) Conventional PCC (b) Proposed PCC                                                            | 5-17 |

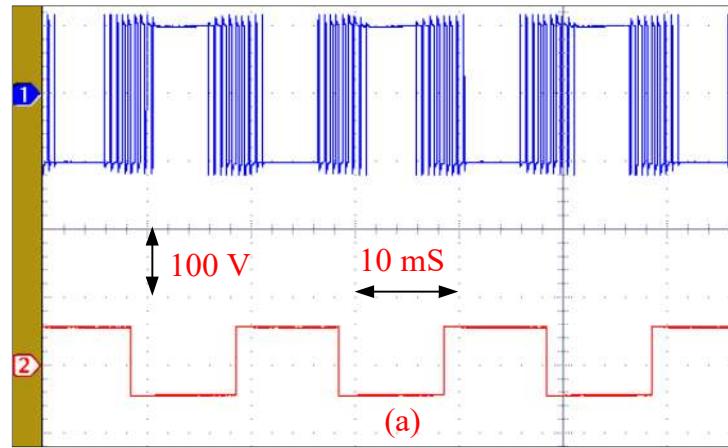

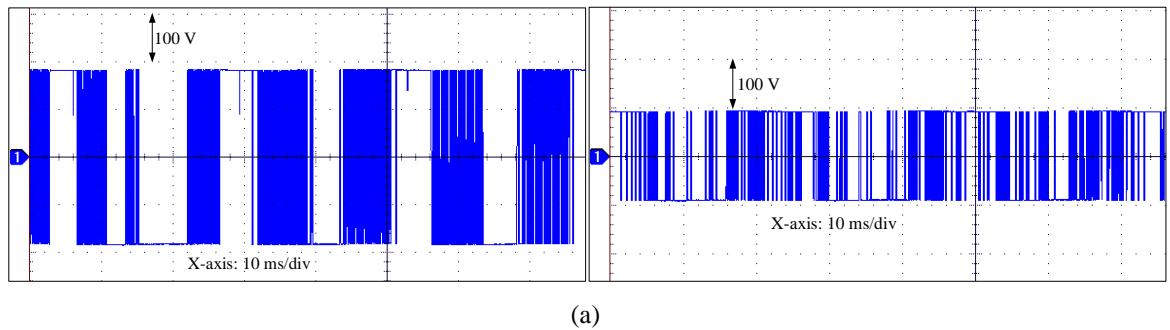

| Fig. 5.9 Experimentally obtained pole voltage of inverter-1 (left) and inverter-2 (right). (a) Conventional PCC (b) proposed PCC                                                                       | 5-18 |

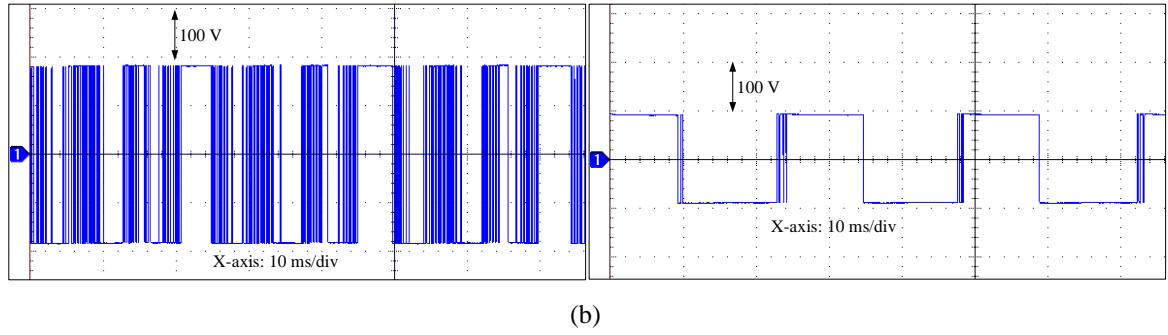

| Fig. 5.10 Simulation results of $v_{aa'}$ (left) and $i_{aa'}$ (right) at a speed of 1200 RPM. (a) Conventional PCC, (b) Proposed PCC                                                                  | 5-18 |

Fig. 5.11 Experimental phase voltage (left) and current (right) waveforms with FFT analysis at a speed of 1200 RPM. (a) Conventional PCC, (b) Proposed PCC

5-19

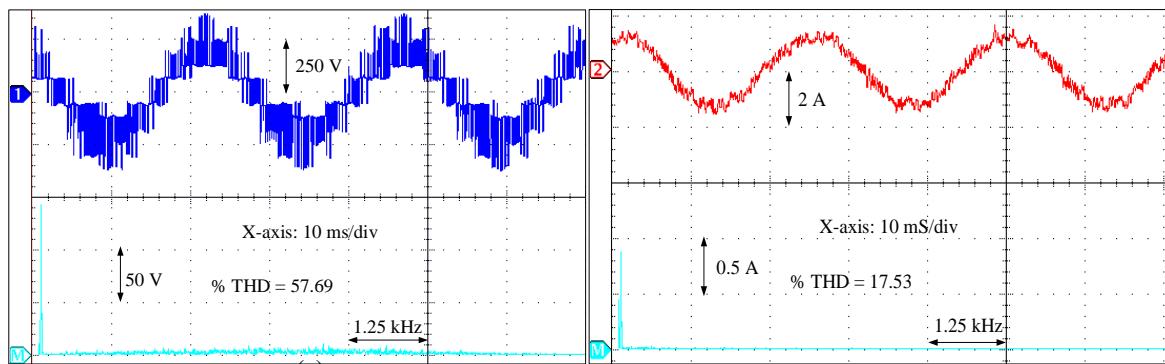

Fig. 5.12 Experimental steady state torque of OEWIMD: (a) Conventional PCC (b) Proposed PCC at a speed of 1200 RPM

5-19

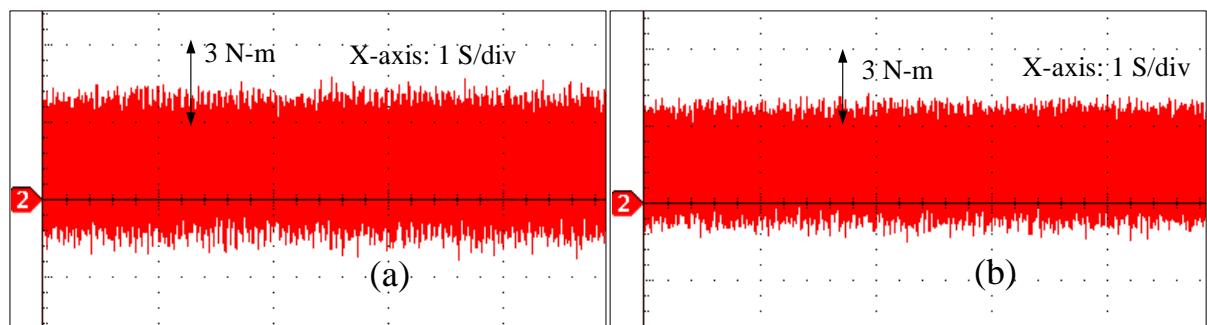

Fig. 5.13 Experimental cost function value at a speed of 1200 RPM: (a) Conventional PCC (b) Proposed PCC

5-20

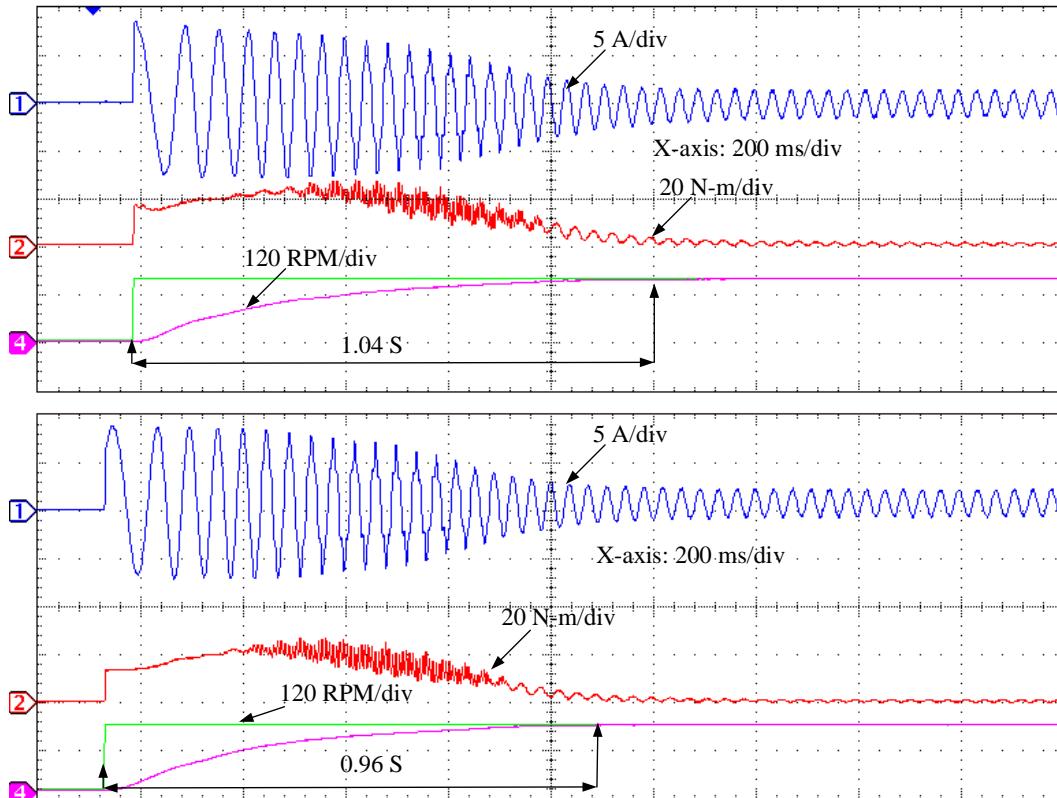

Fig. 5.14 Experimental result of stator current, torque and speed of four-level OEWIMD during acceleration: conventional PCC (top), proposed PCC (bottom)

5-21

Fig. 5.15 Experimental result of stator current, torque and speed of four-level OEWIMD during speed-reversal: conventional PCC (top), proposed PCC (bottom)

5-22

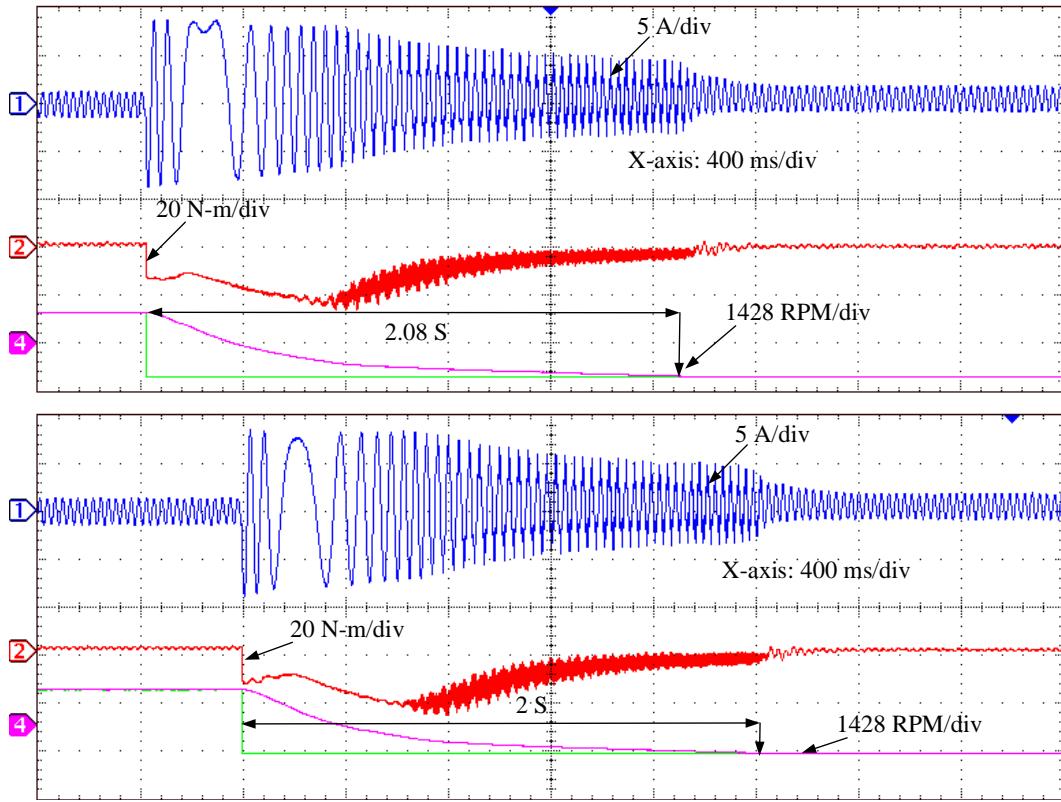

Fig. 5.16 Experimental torque response of OEWIMD: (a) Conventional PCC (b) Proposed PCC

5-23

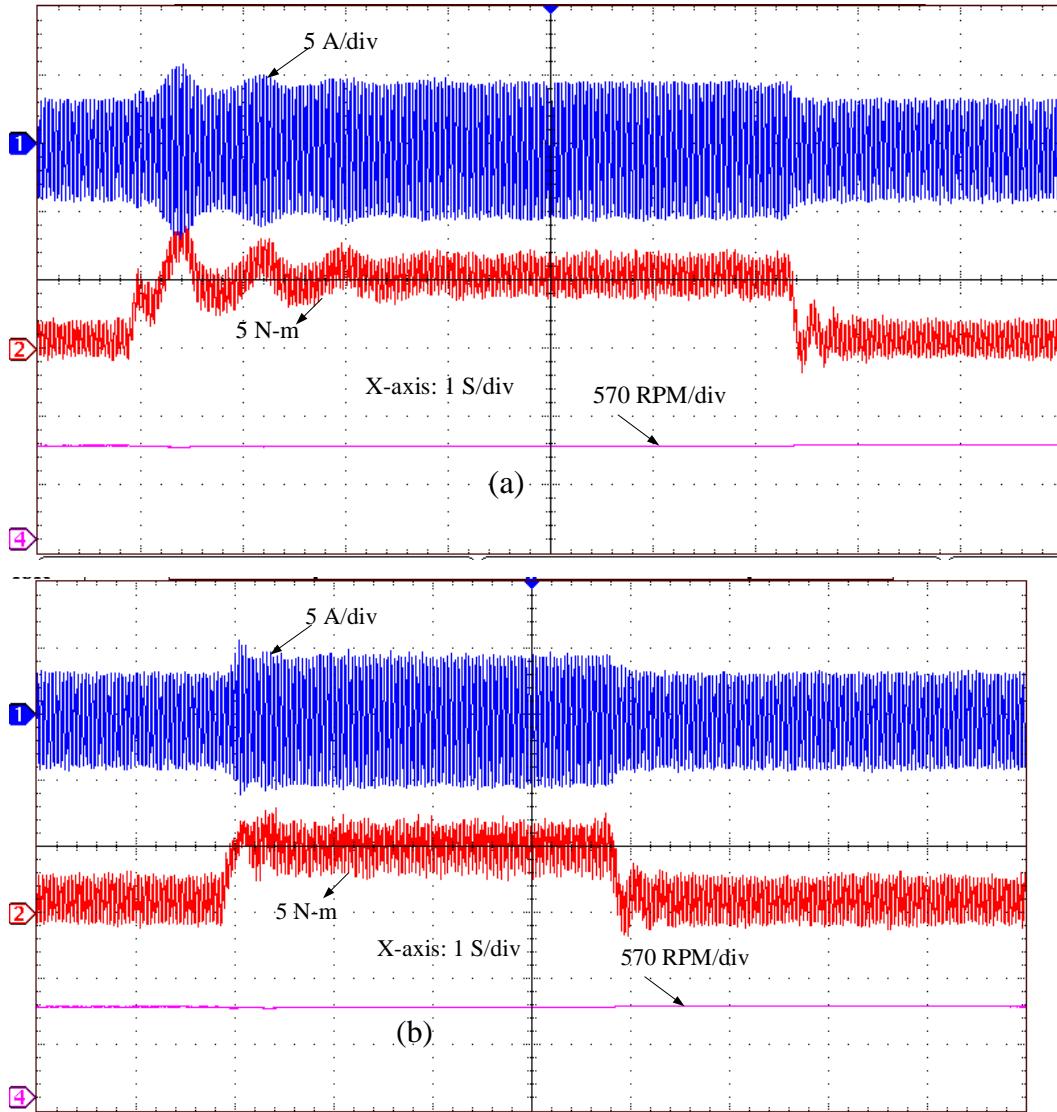

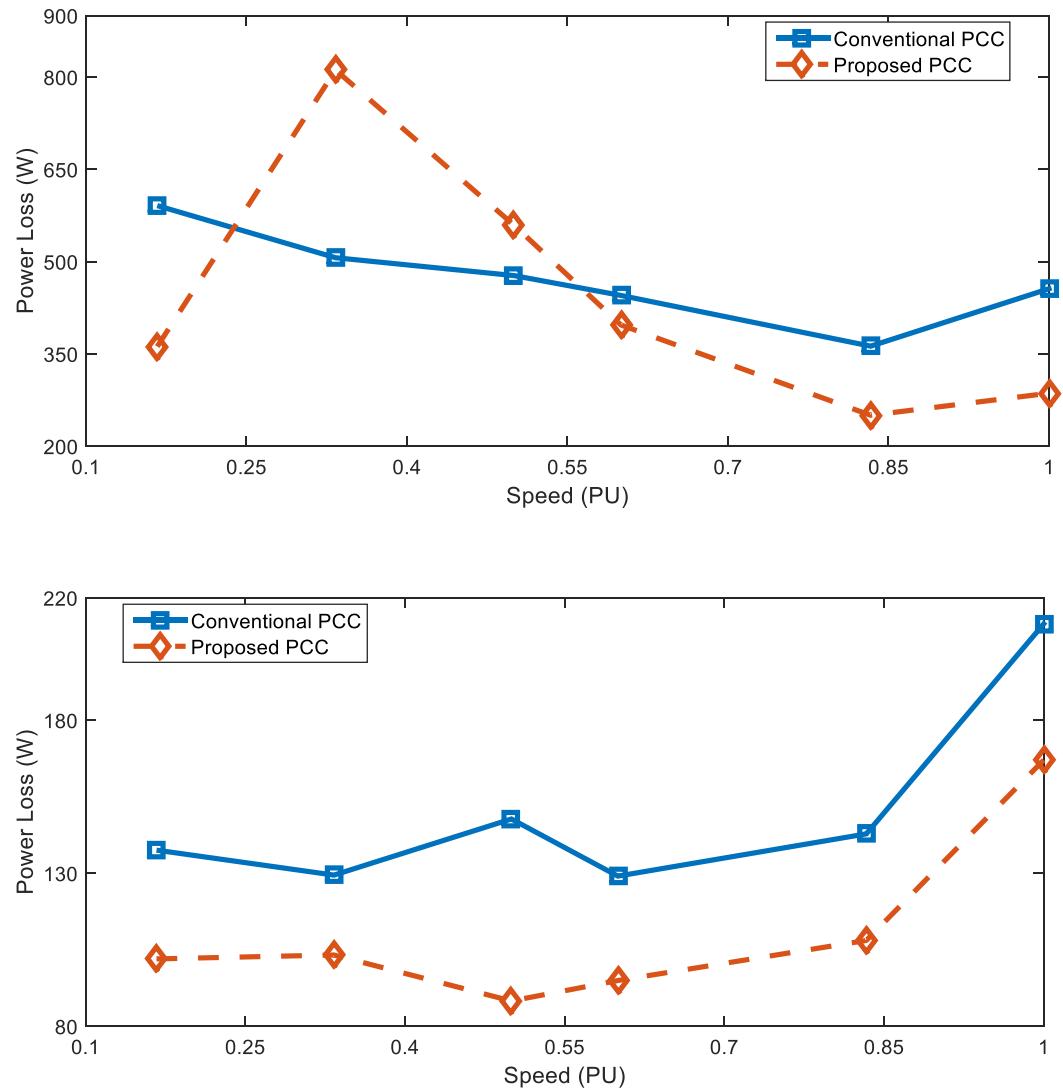

Fig. 5.17 Total power loss of four-level OEWIMD: Dual-inverter loss (top), Ohmic loss (middle), Drive loss (bottom)

5-25

Fig. A.1 A view of experimental set-up of four-level Open-End Winding Induction Motor

A-1

## List of Tables

| <b>Table</b> | <b>Title of the Table</b>                                                       | <b>Page</b> |

|--------------|---------------------------------------------------------------------------------|-------------|

| <b>No.</b>   |                                                                                 | <b>No.</b>  |

| Table 1.1    | Comparison between NPC, FC and CHB converters                                   | 1-11        |

| Table 2.1    | Individual switching states of inverters                                        | 2-5         |

| Table 2.2    | Difference of pole voltages                                                     | 2-5         |

| Table 2.3    | Switching sequences of DDPWM-1, 2, 3 & 4 in sector-1                            | 2-14        |

| Table 2.4    | Parameters of OEWIM                                                             | 2-17        |

| Table 2.5    | Name plate details of the OEWIM                                                 | 2-18        |

| Table 3.1    | Switching sequences of Inverter-1 with PCPWM-1 & 2 in sector-1                  | 3-8         |

| Table 4.1    | Four Levels in the phase voltage of proposed topology                           | 4-4         |

| Table 4.2    | Comparison between 4-L MLI topologies                                           | 4-8         |

| Table 4.3    | Computer simulation conditions                                                  | 4-16        |

| Table 4.4    | Parameters of the OEWIMD                                                        | 4-17        |

| Table 4.5    | Unbalanced voltage levels across phase-A winding of OEWIMD                      | 4-26        |

| Table 5.1    | OEWIMD Parameters                                                               | 5-16        |

| Table 5.2    | Computational burden on the controller with sampling time ( $T_s = 120 \mu s$ ) | 5-20        |

| Table A1     | Hardware specifications of the dual-inverter system                             | A-1         |

## List of Symbols

|                                        |                                                                                                                              |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $V_{DC}$                               | : Input dc-link voltage                                                                                                      |

| $q$                                    | : Number of levels (i.e. $q = 2, 3, 4, \dots$ )                                                                              |

| $v_{ao}$ , $v_{bo}$ , and $v_{co}$     | : Pole voltages of inverter-1                                                                                                |

| $v_{a'o'}$ , $v_{b'o'}$ , $v_{c'o'}$   | : Pole voltages of inverter-2                                                                                                |

| $v_{aa'}$ , $v_{bb'}$ , $v_{cc'}$      | : Stator phase voltages of open-end winding induction motor                                                                  |

| $\theta$                               | : angle subtended by the ‘q-axis’ of the ‘dq0’ reference frame with respect to the axis of the A-phase winding of the stator |

| $v_{aa'r}$ , $v_{bb'r}$ , & $v_{cc'r}$ | : Rotor phase voltages of open-end winding induction motor                                                                   |

| $v_z$                                  | : Zero-sequence voltage                                                                                                      |

| $v_{ref}$                              | : Reference voltage space vector                                                                                             |

| $m_a$                                  | : Modulation index                                                                                                           |

| $f$                                    | : Rated supply frequency                                                                                                     |

| $f_1$                                  | : Fundamental frequency of the drive                                                                                         |

| $T_s$                                  | : Sampling time period                                                                                                       |

| $T_{s1}$                               | : Sampling time period of inverter-1                                                                                         |

| $T_{s2}$                               | : Sampling time period of inverter-2                                                                                         |

| $T_o$                                  | : Time period of fundamental frequency ( $1/f_1$ )                                                                           |

| $\alpha$                               | : Angle subtended by the reference vector with respect to a-phase axis                                                       |

| $v_x^*$                                | : Instantaneous phase reference voltage (where $x \in a, b, c$ )                                                             |

| $2v_a^*/3, 2v_b^*/3, 2v_c^*/3$         | : Instantaneous phase reference voltages of inverter-1                                                                       |

| $v_a^*/3, v_b^*/3, v_c^*/3$            | : Instantaneous phase reference voltages inverter-2                                                                          |

| $T_{xs1}$                              | : Imaginary switching time period of inverter-1 (where $x \in a, b, c$ )                                                     |

| $T_{xs2}$                              | : Imaginary switching time period of inverter-2 (where $x \in a, b, c$ )                                                     |

| $T_{eff}$                              | : Effective time period of dual-inverter                                                                                     |

| $T_{eff1}$                             | : Effective time-period of inverter-1                                                                                        |

| $T_{eff2}$                             | : Effective time-period of inverter-2                                                                                        |

|                                                  |                                                                          |

|--------------------------------------------------|--------------------------------------------------------------------------|

| $T_{\max 1}$                                     | : Maximum amongst the three imaginary switching times of inverter-1      |

| $T_{\min 1}$                                     | : Minimum amongst the three imaginary switching times of inverter-1      |

| $T_{\max 2}$                                     | : Maximum amongst the three imaginary switching times of inverter-2      |

| $T_{\min 2}$                                     | : Minimum amongst the three imaginary switching times of inverter-2      |

| $T_z$                                            | : Zero-vector or null-vector time period                                 |

| $T_{z1}$                                         | : Null-vector time period of inverter-1                                  |

| $T_{z2}$                                         | : Null-vector time period of inverter-2                                  |

| $T_{\text{offset}1}$                             | : Offset time period of inverter-1                                       |

| $T_{\text{offset}2}$                             | : Offset time period of inverter-2                                       |

| $T_{\text{ga}1}, T_{\text{gb}1}, T_{\text{gc}1}$ | : Phase switching time periods of inverter-1                             |

| $T_{\text{ga}2}, T_{\text{gb}2}, T_{\text{gc}2}$ | : Phase switching time periods of inverter-2                             |

| $T_1, T_2$                                       | : Dwell time periods                                                     |

| $T_A^+$                                          | : Top switching device of phase-A leg                                    |

| $T_A^-$                                          | : Bottom switching device of phase-A leg                                 |

| $D_A^+$                                          | : Anti-parallel diode of top switching device of phase-A leg             |

| $D_A^-$                                          | : Anti-parallel diode of bottom switching device of phase-A leg          |

| $P_{\text{sw}}$                                  | : Switching power loss                                                   |

| $P_{\text{con}}$                                 | : Conduction power loss                                                  |

| $v_{\text{sw}}$                                  | : Voltage blocked by the switch in its OFF-state (i.e. $V_{\text{DC}}$ ) |

| $i_{\text{sw}} = I_{\text{ON}}$                  | : Current flowing through the switch in its on-state                     |

| $f_s$                                            | : Switching frequency                                                    |

| $v_{\text{ON}}$                                  | : on-state voltage drop                                                  |

| $t_{\text{ri}}, t_{\text{rv}}$                   | : Rise times of current and voltage respectively                         |

| $t_{\text{fv}}, t_{\text{fi}}$                   | : Fall times of voltage and current respectively                         |

| $t_{\text{ON}}$                                  | : Switch turn-on time                                                    |

| $V_t$                                            | : IGBT fixed voltage drop under zero-current condition                   |

| $R_{\text{CE}}$                                  | : IGBT on-drop resistance                                                |

|                |                                                                   |

|----------------|-------------------------------------------------------------------|

| $V_f$          | : Diode fixed voltage drop under zero-current condition           |

| $R_{AK}$       | : Diode on-drop resistance                                        |

| $R_s$          | : Stator resistance of the OEWIMD                                 |

| $R_{rp}$       | : Rotor resistance of the OEWIMD referred to stator               |

| $x_{ls}$       | : Stator leakage reactance of the OEWIMD                          |

| $x_{lr'}$      | : Rotor leakage reactance of the OEWIMD referred to stator        |

| $X_m$          | : Magnetizing reactance of the OEWIMD                             |

| $J$            | : Moment of inertia of the OEWIMD                                 |

| $B$            | : Friction coefficient of the OEWIMD                              |

| $P$            | : Number of poles of the OEWIMD                                   |

| $V_1$          | : Fundamental voltage component of phase voltage                  |

| $V_n$          | : $n^{\text{th}}$ harmonic voltage component of the phase voltage |

| $n$            | : Harmonic order (i.e. $n = 2, 3, 4, \dots$ )                     |

| $i_1$          | : Fundamental current component of phase current                  |

| $i_n$          | : $n^{\text{th}}$ harmonic current component of the phase current |

| $N_s$          | : Number of samples                                               |

| $\omega_a$     | : Arbitrary angular frequency                                     |

| $v_s$          | : Stator voltage space vector of the OEWIM                        |

| $v_r$          | : Rotor voltage space vector of the OEWIM                         |

| $i_s$          | : Stator current space vector of the OEWIM                        |

| $i_r$          | : Rotor current space vector of the OEWIM                         |

| $\psi_s$       | : Stator flux space vector of the OEWIM                           |

| $\psi_r$       | : Rotor flux space vector of the OEWIM                            |

| $R_r$          | : Rotor resistance of the OEWIM                                   |

| $L_s$          | : Stator inductance of the OEWIM                                  |

| $L_r$          | : Rotor inductance of the OEWIM                                   |

| $L_m$          | : Mutual inductance of the OEWIM                                  |

| $\omega$       | : Electrical rotor angular speed                                  |

| $v_{\alpha s}$ | : Real component of the OEWIM voltage space vector                |

| $v_{\beta s}$  | : Imaginary component of the OEWIM voltage space vector           |

| $i_{\alpha s}$ | : Real component of the OEWIM current space vector                |

$i_{\beta s}$  : Imaginary component of the OEWIM current space vector

$T_e^*$  : Reference torque component from output of speed PI-controller

$\psi_r^*$  : Reference rotor flux equal to the rated rotor flux of the machine

$g_i$  : Cost function based on OEWIM reference and predicted currents

$g_v$  : Cost function based on OEWIM reference and predicted voltages

## List of Abbreviations

|       |   |                                           |

|-------|---|-------------------------------------------|

| VSI   | : | Voltage Source Inverter                   |

| PWM   | : | Pulse Width Modulation                    |

| MV    | : | Medium Voltage                            |

| ASD   | : | Adjustable-Speed Drives                   |

| SVPWM | : | Space Vector PWM                          |

| NPC   | : | Neutral Point Clamped                     |

| FC    | : | Flying Capacitor                          |

| ANPC  | : | Active NPC                                |

| CHB   | : | Cascaded H-Bridge                         |

| HNPC  | : | Hybrid NPC                                |

| IGBT  | : | Insulated-Gate Bipolar Transistor         |

| IEGT  | : | Injection-Enhanced Gate Transistor        |

| GCT   | : | Integrated Gate-Commutated Thyristor      |

| MMC   | : | Modular Multilevel Converter              |

| HVDC  | : | High-Voltage Direct Current               |

| THD   | : | Total Harmonic Distortion                 |

| WTHD  | : | Weighted THD                              |

| OEWIM | : | Open-End Winding Induction Motor          |

| ZSV   | : | Zero-Sequence Voltage                     |

| ZSC   | : | Zero-Sequence Current                     |

| SAZE  | : | Sample Averaged Zero-Sequence Elimination |

| DSAZE | : | Decoupled SAZE                            |

| SPWM  | : | Sine PWM                                  |

|         |   |                                        |

|---------|---|----------------------------------------|

| NSPWM   | : | Near state PWM                         |

| EDPWM   | : | Equal switching Duty PWM               |

| PDPWM   | : | Proportional switching Duty PWM        |

| OEWIMD  | : | Open-End Winding Induction Motor Drive |

| NICSAZE | : | Nested Inverter Clamped SAZE           |

| FOC     | : | Field-Oriented Control                 |

| DTC     | : | Direct-Torque Control                  |

| FS-MPC  | : | Finite Set – Model Predictive Control  |

| PTC     | : | Predictive Torque Control              |

| PCC     | : | Predictive Current Control             |

| EV      | : | Electric Vehicle                       |

| HEV     | : | Hybrid EV                              |

| DDPWM   | : | Discontinuous Decoupled PWM            |

| CSPWM   | : | Center-Spaced PWM                      |

| PCPWM   | : | Phase Clamped PWM                      |

| NSHC    | : | Nearest Sub-Hexagonal Center           |

# Chapter 1

## Introduction

## Contents

|            |                                                                                    |             |

|------------|------------------------------------------------------------------------------------|-------------|

| <b>1.1</b> | <b>Background.....</b>                                                             | <b>1-2</b>  |

| <b>1.2</b> | <b>Literature Review .....</b>                                                     | <b>1-5</b>  |

| 1.2.1      | Recent advances in MLIs .....                                                      | 1-11        |

| 1.2.2      | Open-End Winding Induction Motor drives .....                                      | 1-13        |

| 1.2.3      | Closed loop operation of OEWIMD .....                                              | 1-21        |

| <b>1.3</b> | <b>Applications, advantages and disadvantages of dual inverter fed OEWIND.....</b> | <b>1-23</b> |

| <b>1.4</b> | <b>Motivation .....</b>                                                            | <b>1-24</b> |

| <b>1.5</b> | <b>Objectives .....</b>                                                            | <b>1-25</b> |

| <b>1.6</b> | <b>Organization of the thesis .....</b>                                            | <b>1-26</b> |

| <b>1.7</b> | <b>Summary.....</b>                                                                | <b>1-29</b> |

# Chapter 1

## Introduction

This chapter presents a brief description about the background and the motivation of this thesis. The emergence of multilevel inverter technology, and recent developments with reference to the dual-inverter driven open-ended motors are described. Finally, the objective of this research work is presented along with the organization of the thesis.

### 1.1 Background

Rapid growth of industrialization and depleting fossil fuel resources are the principal causes for the ever-rising demand of electrical energy, which compel efficient and optimal employment of the resources of electrical energy. Also, industrial applications often call for conversion of electrical energy from one form to another, to suit a given application. In the contemporary industrial scenario, digital signal processing and power electronic converters play crucial roles to realize these objectives, while improving the quality of output power.

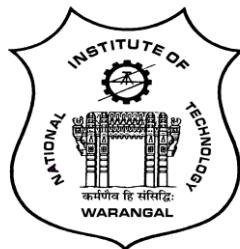

The present-day industry extensively employs power electronic converters such as Voltage-Source Inverters (VSI) in a wide range of applications due to their higher efficiency and performance [1-2]. VSI-driven variable speed induction motor drives are increasingly being employed in applications such as fans, compressors and pumps in industries. For most of these drives, which don't demand high dynamic performance, a simple scalar control is adequate. However, for applications, which demand a high dynamic performance (such as rolling-mill applications), vector-control is being used. A basic three-phase two-level VSI fed induction motor drive is shown in Fig. 1.1. In general, Pulse Width Modulation (PWM) strategies are used to generate the gating pulses to the VSI. The PWM of VSI serves two principal purposes. Firstly, it controls the magnitude and frequency of the fundamental component of the output voltage. Secondly, it improves the harmonic performance of the VSI by reducing the magnitude of the components of higher order harmonics, without the aid of external filters. In general, in VSI-driven induction motor drives, it is desirable to switch power semiconductor devices at high switching frequencies to improve the harmonic

performance. However, increase in the switching frequency increases the switching power loss, which could be significant at high power levels.

Fig. 1.1: Conventional two-level voltage source inverter

The maximum output voltage of the VSI, shown in Fig. 1.1, depends on the maximum modulation index and the dc input voltage [3]. In practice, the dc-input voltage is limited by the blocking voltage of the semiconductor devices.

To avoid high switching power loss and the blocking voltage limitation of the semiconductor devices, multilevel voltage source inverters are being developed for the past few decades [4-8].

In multilevel inverters, fractional voltages of the input dc power supply are obtained with the aid of capacitors. These fractional voltages are then applied to the end connections of the series connected power semiconductor devices. These devices are switched with appropriate PWM schemes to achieve multilevel output voltages. In the last two decades, multilevel inverters have emerged in high power, medium voltage (MV) applications. High power converters and MV drives were first developed in the mid-1980s [5]. The voltage of MV drive-converters range from 3.3 kV to 6.6 kV and the output power ranges from 1 to 50 MW [8].

Applications of multilevel inverters are now widely spread across industry. They include pipeline pumps, gas compressors in the petrochemical industry [9], raw sewage pumps, treatment pumps, freshwater pumps in water pumping stations [10], renewable energy sources [11], reactive power compensators [12], crushers, rolling mills, hoists in mining and metal industry [13], traction drives for locomotives [13], Kiln-induced draft fans, forced draft fans in cement industry [14], naval vessels, shuttle tankers in transportation industry, power distribution, laminators, conveyors, blowers, compressors, adjustable-speed drives (ASDs) for medium-voltage induction motors [15-18] and others [19].

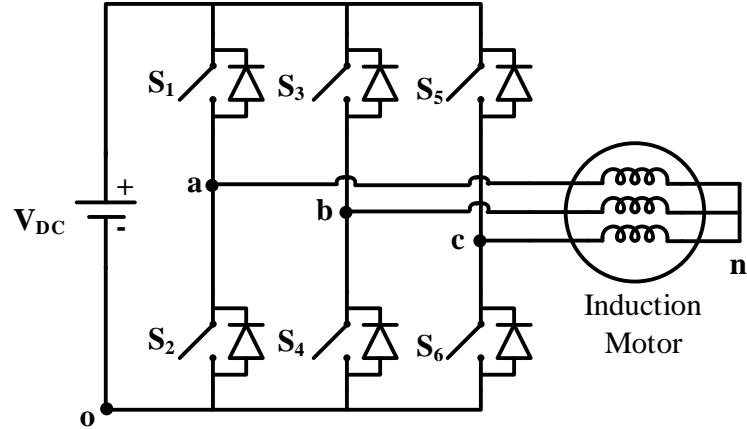

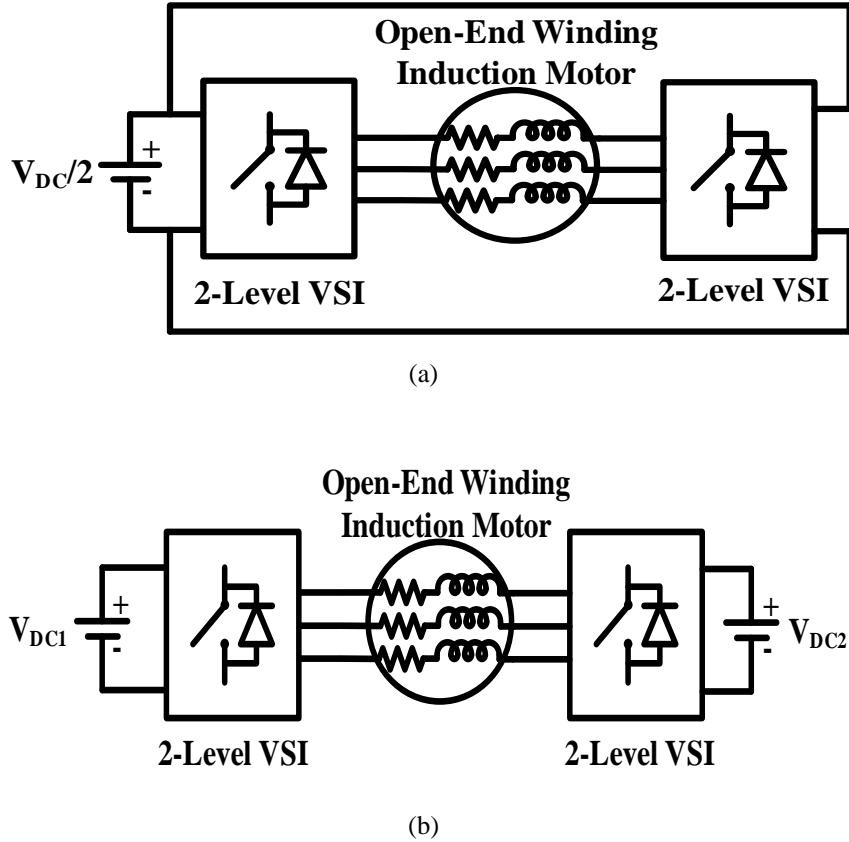

Multilevel converter systems can be divided into two groups, based on the supply techniques. Conventional multilevel inverter topologies use single-ended converter and the load is either star connected (left) or delta connected (right), as shown in Fig. 1.2 (a). The other system uses two power supplies across each phase of the load as shown in Fig. 1.2 (b), known as the dual-inverter system [20]. Two conventional VSIs are sufficient to realize the dual-inverter system to achieve multilevel operation. However, two isolated DC power supplies are needed as compared to the single-ended multilevel converter system.

Fig. 1.2: Inverter topologies based on supply techniques (a) Multilevel inverter with single-ended load (b) Dual-inverter with open-ended load

The dual-inverter system, while retaining all of the advantages of the single-ended multilevel converters, displays the additional advantage of offering more redundancy in terms of switching vector selection. A proper selection of the input dc-link voltages for the dual inverter system facilitates multilevel inversion. When the supplies are symmetrical (i.e. 1:1), three-level inversion is obtained. With asymmetric dc-link voltages, four (i.e. 2:1) or more levels can be achieved. Abundant amount of research work was reported on the topic of *three-level open-end winding induction motor drives*. However, the dual-inverter system with asymmetric input supplies (i.e. four-level operation) has not adequately been explored. This is the motivating factor to undertake the study of the dual-inverter system with asymmetric supplies, which provides four-level inversion.

## 1.2 Literature Review

As stated earlier, multilevel inverter technology is still emerging, showing promise for many industrial applications. Many topologies and new control strategies have been proposed for high power applications [4-8]. These works mainly explain the traditional and well-established inverter topologies, such as, the Neutral Point Clamped (NPC), Flying Capacitor (FC) and the Cascaded H-Bridge (CHB), as well as specific modulation strategies to control their operation.

The main advantages of the multilevel inverters (MLIs), as compared to the two-level inverter are as follows:

- Achievement of higher AC voltages with semiconductor switching devices of lower voltage ratings.

- Enhanced spectral performance i.e. reduced Total Harmonic Distortion (THD), as output voltages are nearly sinusoidal.

- Low  $dv/dt$  on the semi-conductor devices.

- Low Electro Magnetic Interference (EMI).

- Smaller or no requirement of filters.

- Reduction in the stress on winding insulation.

- Operability with lower switching frequencies.

- Reduced common-mode voltages (CMVs), which reduces unwanted bearing currents. Additional modulation methods can be adopted in order to eliminate the CMVs.

In many industrial applications, induction motors are used as variable speed drives, which requires variable voltage and variable frequency. However, the grid provides a fixed voltage and a fixed frequency. Hence, to achieve variable-speed operation, power electronic converters are to be used between the grid and the induction motor. A typical industrial medium voltage motor drive is shown in Fig. 1.3 [19].

Fig. 1.3: General block diagram of industrial MV drive [19]

The general practice prevailing in power electronic converters is to switch power semiconductor devices at high switching frequencies in order to minimize the harmonic content and the filter size [21]. However, the increased switching frequency increases the switching power loss and reduces the overall drive efficiency.

One method to reduce the switching power loss is to construct a resonant circuit by adding an LC network to the hard switched inverter topology. One such resonant converter topology was proposed by R.W. DeDoncker *et. al.* [22]. In this work, the authors proposed an auxiliary resonant commutated pole converter to reduce the switching loss by operating the inverter switches when the voltage is zero.

Another topology was proposed by J. He *et. al.* [23], wherein the converter includes the resonant dc-link. In this proposal, the dc-link circuit is used as an interface between the dc voltage and the PWM inverter to provide a short zero voltage period in the dc-link voltage to allow the zero voltage switchings.

The principal drawbacks with the power circuit configurations proposed in [22] and [23] is that, the inverter peak-currents or the voltages are considerably higher than those encountered in the hard switched converters, which increases the device rating. Also, an added auxiliary triggered resonant commutation circuit increases the system complexity and cost.

In early 1980s, A. Nabae, I. Takahashi, and H. Akagi presented the first multi-level converter [24]. This converter is a three-level voltage source inverter, shown in Fig. 1.4. This inverter is named as the *Neutral Point Clamped* (NPC) inverter, which is also known as the *diode-clamped* inverter [24]. This inverter is a simple modification to a two-level voltage source inverter in that, two more semiconductor switches and clamping diodes are added in series with each leg of Fig. 1.1. For the same dc-link voltage, the voltage ratings of the semiconductors is half as compared to the conventional 2-level VSI. Conversely, if these semiconductors are of the same voltage rating as that of the two-level case, the dc-link voltage can be doubled, enhancing the power handling capability of the inverter. In literature, the proposed topology is extended to more levels [25-27] to increase the power rating of the converter and to enhance the spectral performance. Also, the extension of the NPC configuration for higher number of levels allows its operability with lower switching frequencies, which reduces the switching power loss (compared to the 3-level NPC).

Despite these advantages, the NPC topology has the following drawbacks: i) requirement of high voltage rating for the clamping diodes, ii) unequal device ratings, iii) requirement of higher number of clamping diodes as the levels increases, iv) unbalanced dc-link capacitor voltages, v) complexity of control for higher number of levels, vi) increased switching losses due to the reverse recovery current of clamping diodes, vii) unsymmetrical distribution of power losses in semiconductor switching devices causing unsymmetrical distribution of the semiconductor junction temperature, which demand better strategies for the thermal management [7] and viii) difficulty to extend the converter range by series connection of semiconductors [2, 4, 7, 28].

At present, research is focused to balance the dc-link capacitor voltages using the conventional and advanced strategies such as SVPWM and model predictive control (MPC) [29-30]. Recently, C. Xia *et. al.* proposed a new discontinuous PWM technique for the reduction of the switching loss [31]. T. Bruckner *et. al.* proposed active NPC (ANPC) converter to overcome the unequal loss distribution [32]. Another type of diode clamped converter, called the hybrid neutral point clamped converter [33], proposed by T. B. Soeiro *et. al.*, utilizes extra two semiconductor devices than the traditional NPC converter. The proposed topology is also overcome the unequal loss distribution. However, even this topology suffers from some of the drawbacks which are mentioned above.

Fig. 1.4: Three-level NPC MLI

Another popular three-level inverter topology, named as the *Flying Capacitor Multi-Level Inverter* (FCMLI) was proposed in the year 1992 by T. Maynard *et. al* [34]. This power circuit configuration is shown in Fig. 1.5. This topology is also realized by the series connection of two more semiconductor devices in series with each leg of Fig. 1.1. Unlike the NPC MLI, which uses the clamping diodes to realize the multilevel inversion, the FCMLI uses clamping capacitors. Compared to the NPC based MLI, the FC topology possesses more number of redundant switching states to control the capacitor charge balance [35]. Currently, four-level FCMLIs are being manufactured by an organization, which produces MV industrial

drives [36]. Similar to the NPC MLI, the FCMLI is also extended for more number of levels [34-36].

However, the FCMLI has the following disadvantages [1-2, 4]: i) requirement of excessive number of floating capacitors leading to higher cost, ii) occupation of larger space due to the bulkiness of capacitors, iii) requirement of higher switching frequency, leading to higher switching losses, and iv) requirement of more complex control strategies to balance the floating capacitor voltages.

Fig. 1.5: Three-level FC MLI

P. W. Hammond proposed a cascaded H-bridge converter (CHB) for MV drives in 1990s, wherein single-phase inverters are connected in series with separate dc sources [37] as shown in Fig. 1.6. This is one of the simplest converter structures with reduced cost of commissioning and maintenance. Also, this converter avoids clamping diodes, voltage balancing of flying capacitors, while introducing some fault tolerant capability [38]. The advantage of the CHB converter appears profoundly in such applications, where isolated voltage sources are inherent (example fuel cells, photovoltaic power applications and grid connected battery storage systems) [39-40].