**POWER QUALITY ENHANCEMENT BY

DSTATCOM WITH IMPROVED PERFORMANCE**

*A THESIS*

*submitted by*

**HAREESH MYNENI**

*for the award of the degree*

*of*

**DOCTOR OF PHILOSOPHY**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

MARCH 2019**

## **THESIS CERTIFICATE**

This is to certify that the thesis titled "**POWER QUALITY ENHANCEMENT BY DSTATCOM WITH IMPROVED PERFORMANCE**", submitted by **Mr. Hareesh Myneni**, to the National Institute of Technology, Warangal, for the award of the degree of **Doctor of Philosophy**, is a bonafide record of the research work done by him under my supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

**Dr. G. Siva Kumar**

Supervisor

Assistant Professor

Dept. of Electrical Engineering

NIT-Warangal, 506004

Place: Warangal

Date: December 16, 2019

## ACKNOWLEDGEMENT

I would like to express my deep gratitude towards **Dr. G. Siva Kumar**, Assistant Professor, Electrical Engineering Department for his excellent guidance, support and constant reviewing throughout the course of research work. The interactions with him ensured right direction of this work and helped in completion of the thesis.

I am also thankful to **Prof. S Srinivasa Rao**, **Prof. N. Vishwanathan** and **Prof. V. T. Somasekhar.**, Heads of the Electrical Department during the period of research. I am sincerely grateful to **Prof. M Sydulu**, **Dr. D Sreenivasarao** and **Prof. D. Dinakar** who assessed my work and encouraged me as the members of my doctoral scrutiny committee. I would also like to thank **Dr. M. Raja Vishwanathan**, Assistant Professor, Department of Humanities & Social Science for the proof reading of thesis.

I wish to express my sincere thanks to **Prof. N.V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

My sincere thanks to my colleagues especially Mr. Pranay, Mr. Rathna Rahul, Dr. Ramanjaneya Reddy, Dr. Kiran, Dr. Kasi Rama Krishna Reddy, Mr. Praveen, Mr. Suresh, Mr. Venu Sonti, Dr. Vijay Babu K, Mr. Chinna K, Mr. M Santhose, Mr. O V S R Vara Prasad, Mr. S Viveka Naidu (M,Tech), Mr. C. Amarnath (M,Tech) for answering all the questions whenever I was in need.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal.

I also acknowledge my sincere gratitude to the Ministry of Human Resources Development (MHRD), Government of India for their financial support to carry out this research.

My heartily gratitude to my parents Shri. M Venkateswararao & Smt. M Suchitra, my sister Smt. M Purnima, my brother-in-law Shri. M Srinivas, my son-in-law M Sravan my relatives and my well wishers for their support. Finally, I wish to express my utmost gratitude to my wife M Lakshmi for her support and encouragement throughout my

research work. My deep love to my son, M Sri Charan for bearing the long hours of my absence.

Above all, I thank the almighty for giving me this learning opportunity and blessing me to finish my work successfully.

**Hareesh Myneni.**

## ABSTRACT

**KEYWORDS:** Distribution Static Compensator (DSTATCOM); distribution system; energy management; harmonics; *LCL*-filter; power quality; reactive power; solar photo-voltaic; switching losses; voltage source converter; voltage stress.

In present day, major power consumption loads on distribution system have been reactive in nature, such as fans, pumps, motor drives and power electronic converters. The excessive reactive power consumption results of low power factor and poor voltage regulation and which reduces the active power flow capability in the distribution system. Moreover, the proliferation of power electronic devices in the distribution system worsens the operating conditions and leads to power quality problems. The major power quality issues in the three-phase distribution system are current harmonics, voltage harmonics, reactive power consumption, load unbalancing and excessive neutral current. Harmonic regulation guidelines such as IEEE 519-1992 and IEC 61000 are applied to limit the current and voltage harmonic levels. To satisfy these guidelines, the harmonics must be mitigated by using harmonic filters. Passive and active filters are used either together to form hybrid filters or on an individual basis to mitigate harmonics. In recent years, with the advent of sophisticated electrical and electronic equipment, Power Quality (PQ) has become an issue of concern and extensive research is being done to improve power quality.

A promising group of solutions that deals with power quality problems in the distribution system are Custom Power Devices (CPDs). The family of CPDs includes Distribution Static Compensator (DSTATCOM), Dynamic Voltage Restorer (DVR) and Unified Power Quality Conditioner (UPQC) which are used for compensating power quality problems. Among these members, DSTATCOM is a shunt connected device, which mitigates current related power quality problems. In this thesis, an attempt has been made to develop a split-capacitor DSTATCOM for power quality improvement in three-phase four-wire (3P4W) distribution system.

It is well known that high performance and cost-effective converter are a prerequisite for the realization of DSTATCOM. These converters can be broadly categorized into two classes, namely, Voltage Source Converter (VSC) and Current Source Converter (CSC). The discussion about the performance of the VSC and CSC as a power circuit of DSTATCOM is beyond the scope of this thesis. In the present work, VSC has been considered as a power circuit for DSTATCOM as it has higher market penetration and more noticeable development over the last decades, in comparison to CSC topologies.

In the present work, DSTATCOM has been used to mitigate harmonics, reactive power compensation and balancing of three-phase source currents. A new methodology is proposed to improve the performance of DSTATCOM with more appropriate design of dc-link voltage. For that, a reference dc-link voltage is derived based on the load operating point. With this approach, the switch voltage stress and switching losses are reduced when compared to conventional fixed dc-link voltage method. The switching losses in the proposed method are calculated and are compared with conventional fixed dc-link voltage method. The proposed variable dc-link voltage method is validated by simulation and experimental studies.

An attempt has been made to reduce the required value of interfacing inductance in DSTATCOM applications, since it makes the system bulky and expensive. For that an *LCL*-filter based DSTATCOM is implemented based on switching dynamics, which improves DSTATCOM performance. In addition to current control, the application of *LCL*-DSTATCOM has been extended to voltage control intended for voltage regulation at PCC. The proposed method is validated by simulation and experimental studies.

The method which is available in the literature to reduce the rating of VSC is a *LC*-filter based DSTATCOM topology. In which, an ac-capacitor is connected in series with the interfacing inductor. The series ac-capacitor supports the inverter voltage such that the dc-link voltage requirement is reduced. The amount of dc-link voltage required depends on series ac-capacitor voltage, which indeed depends on the current flowing through the capacitor. In existing methods, the dc-link voltage is fixed even though ac-capacitor voltage is varied, which leads to more voltage drop across interfacing inductor, results in degrading the performance of DSTATCOM. A new methodology is proposed, in which the dc-link voltage requirement corresponding to ac-capacitor voltage support is calculated and it has been maintained, such that the performance is improved.

An attempt has been made to integrate Solar Photo-voltaic (SPV) to grid by DSTATCOM. In general, the SPV is integrated with grid through a DC-DC converter and VSC, which is named as two-stage conversion. In view of efficiency of system, the single-stage conversion becomes more popular and in which Maximum Power Point Tracking (MPPT) of SPV and real power injection are achieved with VSC alone. But, if single-stage conversion system consists of Battery Energy Storage (BES) on dc-side of VSC, then to achieve simultaneous operation of MPPT and real power injection, a co-ordination control is required. In the proposed single-stage grid connected SPV and BES system a co-ordinate control is implemented along with energy management. In this method, the algorithm coordinates VSC and BES system based on the State of Charge (SoC) of the battery and available SPV power so that MPPT and power injection are achieved simultaneously. The proposed method not only injects real power, but also compensates reactive power and mitigate harmonics. Further, an active rectification operation during non-SPV hours is achieved. The multi-functional features of the proposed method are explained using simulation studies and are also validated through experimental studies.

# TABLE OF CONTENTS

|                                                               |              |

|---------------------------------------------------------------|--------------|

| <b>ACKNOWLEDGEMENT</b>                                        | <b>i</b>     |

| <b>ABSTRACT</b>                                               | <b>iii</b>   |

| <b>LIST OF TABLES</b>                                         | <b>x</b>     |

| <b>LIST OF FIGURES</b>                                        | <b>xi</b>    |

| <b>ABBREVIATIONS</b>                                          | <b>xviii</b> |

| <b>NOTATIONS</b>                                              | <b>xx</b>    |

| <b>1 INTRODUCTION</b>                                         | <b>1</b>     |

| 1.1 General Overview . . . . .                                | 1            |

| 1.1.1 High reactive power demand . . . . .                    | 3            |

| 1.1.2 Effect of current harmonics . . . . .                   | 3            |

| 1.1.3 Effect of excess neutral current . . . . .              | 4            |

| 1.2 Power Quality Standards . . . . .                         | 4            |

| 1.3 Solution for Power Quality Problems . . . . .             | 5            |

| 1.3.1 Passive power filters . . . . .                         | 5            |

| 1.3.2 Active power filters . . . . .                          | 7            |

| 1.3.3 Hybrid power filters . . . . .                          | 7            |

| 1.4 Motivation . . . . .                                      | 8            |

| 1.5 Objectives . . . . .                                      | 10           |

| 1.6 Organization of Thesis . . . . .                          | 11           |

| <b>2 LITERATURE ON DSTATCOM TOPOLOGIES</b>                    | <b>13</b>    |

| 2.1 Configuration of DSTATCOM Topologies . . . . .            | 13           |

| 2.1.1 Converter based DSTATCOM topologies . . . . .           | 13           |

| 2.1.2 Distribution supply based DSTATCOM topologies . . . . . | 14           |

| 2.1.3 Design of Split-Capacitor DSTATCOM parameters . . . . . | 19           |

|          |                                                                                                         |           |

|----------|---------------------------------------------------------------------------------------------------------|-----------|

| 2.2      | Control Techniques for DSTATCOM Operation . . . . .                                                     | 24        |

| 2.2.1    | Instantaneous <i>abc</i> Theory . . . . .                                                               | 25        |

| 2.2.2    | Instantaneous Reactive Power (IRP) Theory . . . . .                                                     | 27        |

| 2.2.3    | Synchronous Reference Frame (SRF) Theory . . . . .                                                      | 32        |

| 2.2.4    | Instantaneous Symmetrical Component (ISC) Theory . . . . .                                              | 34        |

| 2.3      | Summary . . . . .                                                                                       | 38        |

| <b>3</b> | <b>POWER QUALITY IMPROVEMENT USING SPLIT-CAPACITOR DSTATCOM WITH DYNAMIC DC-LINK VOLTAGE REGULATION</b> | <b>39</b> |

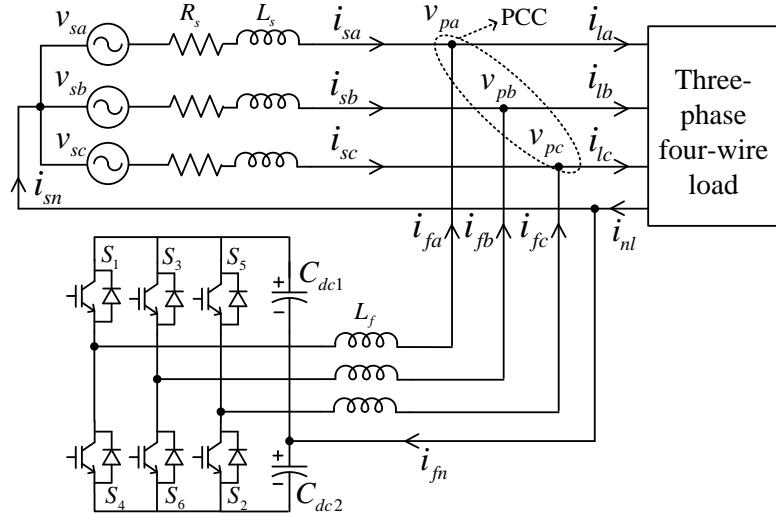

| 3.1      | Conventional Control Algorithm of Split-Capacitor DSTATCOM . . . . .                                    | 39        |

| 3.2      | Proposed Control Algorithm of Split-Capacitor DSTATCOM . . . . .                                        | 42        |

| 3.2.1    | Reference dc-link voltage calculation . . . . .                                                         | 42        |

| 3.2.2    | Dynamic dc-link voltage regulation method . . . . .                                                     | 44        |

| 3.3      | Switching Loss Calculation . . . . .                                                                    | 46        |

| 3.4      | Simulation Studies . . . . .                                                                            | 47        |

| 3.4.1    | Simulation results under stiff voltage source . . . . .                                                 | 48        |

| 3.4.2    | Simulation results under non-stiff voltage source . . . . .                                             | 51        |

| 3.5      | Experimental Studies . . . . .                                                                          | 53        |

| 3.5.1    | Steady state performance of the proposed dynamic dc-link voltage regulation method . . . . .            | 53        |

| 3.5.2    | Transient performance of the proposed dynamic dc-link voltage regulation method . . . . .               | 58        |

| 3.5.3    | Balancing of dc-link voltages . . . . .                                                                 | 61        |

| 3.6      | Advantages and disadvantages of existing and proposed methods . . . . .                                 | 63        |

| 3.7      | Summary . . . . .                                                                                       | 63        |

| <b>4</b> | <b>POWER QUALITY IMPROVEMENT USING <i>LCL</i>-FILTER BASED DSTATCOM</b>                                 | <b>65</b> |

| 4.1      | Introduction . . . . .                                                                                  | 65        |

| 4.2      | <i>LCL</i> -filter based DSTATCOM Topology in Distribution System . . . . .                             | 67        |

| 4.3      | Operation of <i>LCL</i> -DSTATCOM in Current and Voltage Control Modes . . . . .                        | 73        |

| 4.3.1    | Reference voltage generation for CCM mode . . . . .                                                     | 74        |

| 4.3.2    | Reference voltage generation for VCM mode . . . . .                                                     | 75        |

| 4.3.3    | Control of dc-link voltage . . . . .                                                                    | 76        |

| 4.4      | Advantages of the Proposed Method Over Conventional Method . . . . .                                    | 77        |

|          |                                                                                        |            |

|----------|----------------------------------------------------------------------------------------|------------|

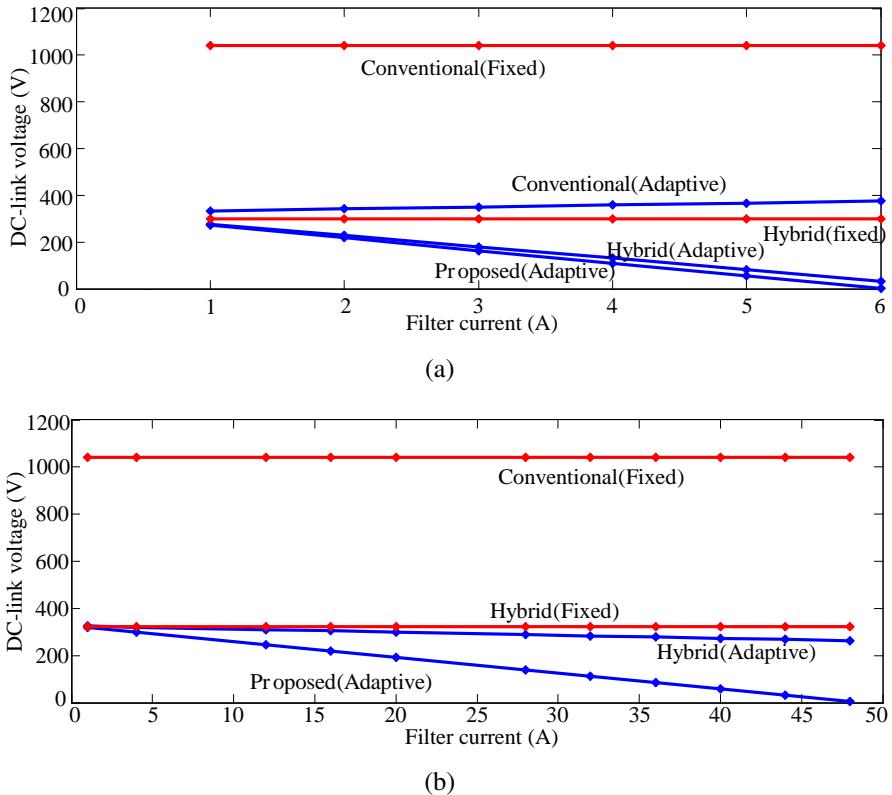

| 4.4.1    | Reduction in dc-link voltage of VSC . . . . .                                          | 77         |

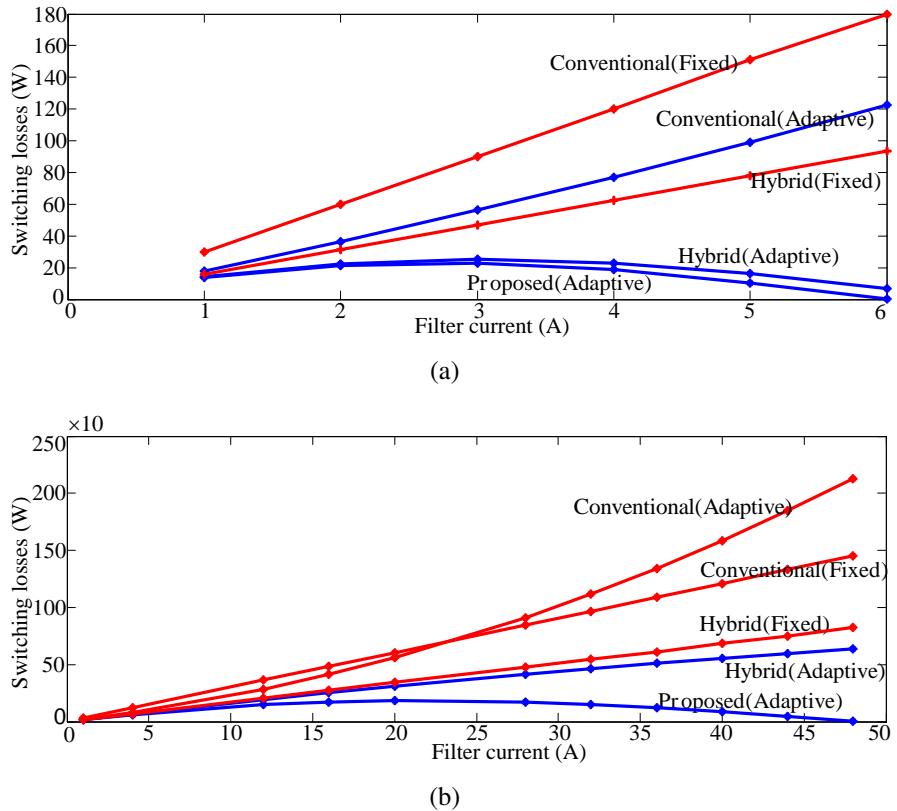

| 4.4.2    | Reduction in energy dissipation ( $E_{sw}$ ) . . . . .                                 | 78         |

| 4.4.3    | Reduction in resistive losses . . . . .                                                | 79         |

| 4.4.4    | Damping losses calculation . . . . .                                                   | 80         |

| 4.5      | Simulation Studies . . . . .                                                           | 81         |

| 4.5.1    | Current control mode . . . . .                                                         | 81         |

| 4.5.2    | Voltage control mode . . . . .                                                         | 83         |

| 4.6      | Experimental Studies . . . . .                                                         | 85         |

| 4.6.1    | Current control mode . . . . .                                                         | 85         |

| 4.6.2    | Voltage control mode . . . . .                                                         | 90         |

| 4.7      | Summary . . . . .                                                                      | 91         |

| <b>5</b> | <b>POWER QUALITY IMPROVEMENT BY HYBRID DSTATCOM WITH ADAPTIVE CONTROL SCHEME</b>       | <b>92</b>  |

| 5.1      | Introduction . . . . .                                                                 | 92         |

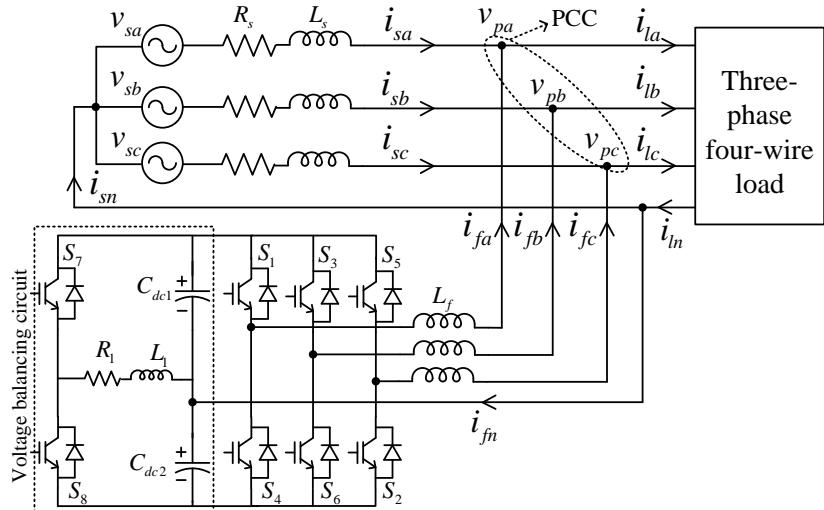

| 5.2      | Structure of Hybrid DSTATCOM . . . . .                                                 | 93         |

| 5.2.1    | Design of series capacitor ( $C_f$ ) . . . . .                                         | 94         |

| 5.2.2    | Design of parameters $L_{fi}$ , $C_r$ and $L_{fg}$ . . . . .                           | 95         |

| 5.3      | Proposed Adaptive Control Scheme for Hybrid DSTATCOM . . . . .                         | 98         |

| 5.3.1    | Proposed variable dc-link voltage reference selection . . . . .                        | 98         |

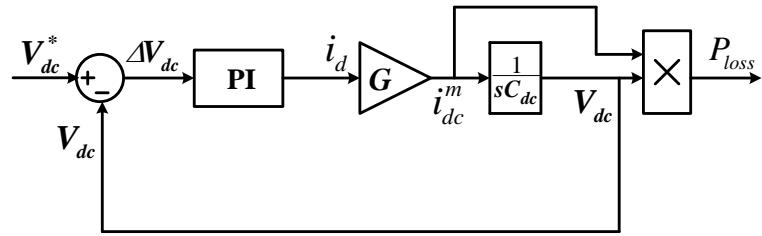

| 5.3.2    | Adaptive control scheme for dc-link voltage regulation . . . . .                       | 100        |

| 5.4      | Simulation Studies . . . . .                                                           | 103        |

| 5.5      | Experimental Studies . . . . .                                                         | 110        |

| 5.6      | Summary . . . . .                                                                      | 115        |

| <b>6</b> | <b>ENERGY MANAGEMENT AND CONTROL OF SINGLE-STAGE SOLAR PV-DSTATCOM WITH BES SYSTEM</b> | <b>116</b> |

| 6.1      | Introduction . . . . .                                                                 | 116        |

| 6.2      | Proposed Single-Stage SPV-DSTATCOM with BES System . . . . .                           | 118        |

| 6.3      | Reference Current Generation in Proposed method . . . . .                              | 120        |

| 6.3.1    | SPM operation during SPV hours . . . . .                                               | 120        |

| 6.3.2    | BPM operation during SPV hours . . . . .                                               | 121        |

| 6.3.3    | DPM operation during SPV hours . . . . .                                               | 121        |

| 6.3.4    | Reference current generation during non-SPV hours . . . . .                            | 122        |

|                   |                                                               |            |

|-------------------|---------------------------------------------------------------|------------|

| 6.4               | Simulation Studies . . . . .                                  | 124        |

| 6.4.1             | Performance during SPV hours with variable load . . . . .     | 125        |

| 6.4.2             | Performance during non-SPV hours with variable load . . . . . | 128        |

| 6.5               | Experimental Studies . . . . .                                | 130        |

| 6.5.1             | Performance during SPV hours . . . . .                        | 132        |

| 6.5.2             | Performance during non-SPV hours . . . . .                    | 137        |

| 6.6               | Summary . . . . .                                             | 140        |

| <b>7</b>          | <b>CONCLUSIONS AND FUTURE SCOPE OF RESEARCH</b>               | <b>141</b> |

| 7.1               | Conclusions . . . . .                                         | 141        |

| 7.2               | Future Scope of Research . . . . .                            | 143        |

| <b>REFERENCES</b> |                                                               | <b>144</b> |

## LIST OF TABLES

|     |                                                                                                                |     |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Comparison between three-phase DSTATCOM topologies . . . . .                                                   | 19  |

| 2.2 | Cost comparison of different DSTATCOM topologies for a rating of 1200 V, 50 A . . . . .                        | 37  |

|     |                                                                                                                |     |

| 3.1 | Simulation parameters of the system with DSTATCOM for dynamic dc-link voltage regulation method . . . . .      | 47  |

| 3.2 | Calculated reference dc-link voltages corresponding to the loads . .                                           | 49  |

| 3.3 | Experimental parameters for dynamic dc-link voltage regulation method                                          | 53  |

| 3.4 | THDs of source currents in conventional and proposed methods . .                                               | 63  |

| 3.5 | Advantages and disadvantages of existing and proposed methods for power quality improvement . . . . .          | 64  |

|     |                                                                                                                |     |

| 4.1 | Literature review on <i>LCL</i> -filter based DSTATCOM topologies . . .                                        | 66  |

| 4.2 | Comparison between <i>L</i> -filter and <i>LCL</i> -filter . . . . .                                           | 72  |

| 4.3 | Simulation parameters for <i>LCL</i> -DSTATCOM . . . . .                                                       | 81  |

| 4.4 | Calculation of percentage reduction of energy dissipation ( <i>E<sub>sw</sub></i> ) . .                        | 82  |

| 4.5 | Comparison of the proposed control method with conventional control methods . . . . .                          | 84  |

| 4.6 | Components required and their specifications for experimental implementation . . . . .                         | 85  |

|     |                                                                                                                |     |

| 5.1 | Simulation parameters for hybrid DSTATCOM operation . . . . .                                                  | 105 |

| 5.2 | Reference dc-link voltage calculation for diode bridge load (Load-1)                                           | 105 |

| 5.3 | Reference dc-link voltage calculation for unbalanced load (Load-2) .                                           | 105 |

| 5.4 | Experimental parameters for hybrid DSTATCOM operation . . . . .                                                | 110 |

|     |                                                                                                                |     |

| 6.1 | Comparison between different grid connected solar PV systems with respect to power conversion stages . . . . . | 124 |

| 6.2 | Simulation parameters for single-stage SPV with BES system . . .                                               | 125 |

| 6.3 | Power flow in the proposed energy management scheme (with reference to Fig. 6.5 and Fig. 6.9(a)) . . . . .     | 131 |

| 6.4 | Experimental parameters for single-stage SPV-DSTATCOM with BES system . . . . .                                | 132 |

## LIST OF FIGURES

|      |                                                                                                                     |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

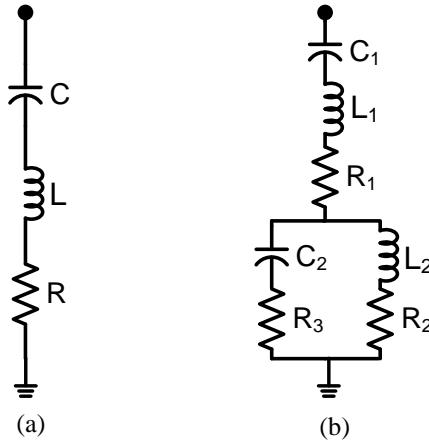

| 1.1  | Passive tuned filters: (a) single-tunned and (b) double tunned . . . . .                                            | 6  |

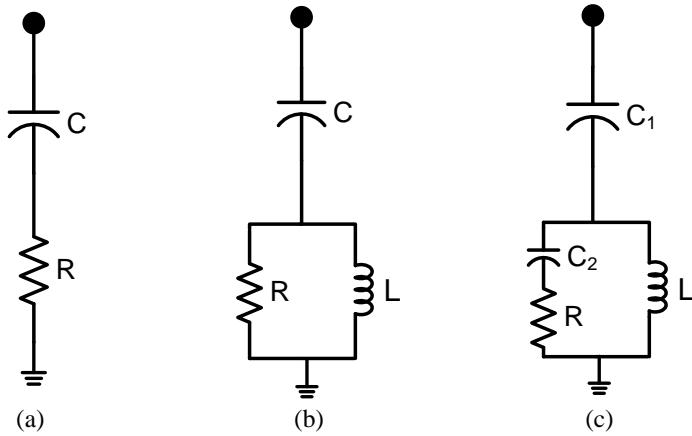

| 1.2  | Passive high pass filters: (a) first order (b) second order and (c) third order . . . . .                           | 6  |

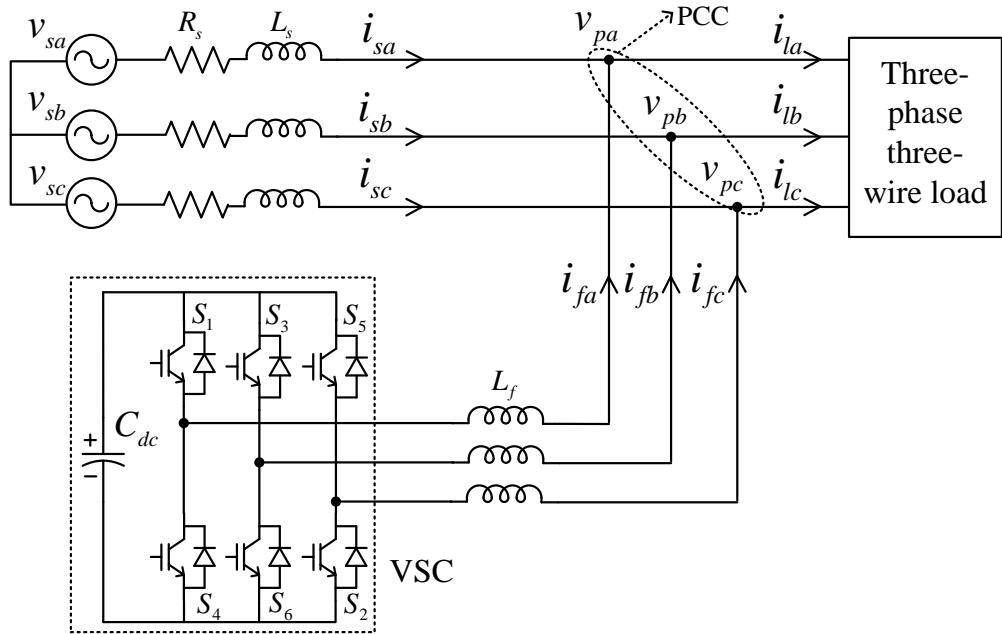

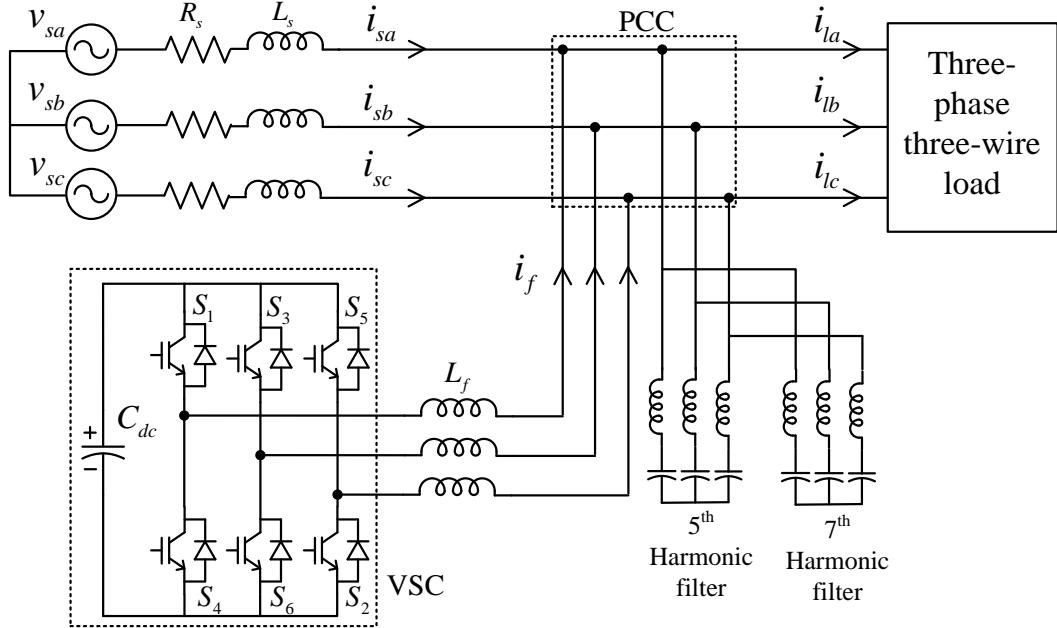

| 1.3  | Shunt active power filter in three-phase three-wire distribution system                                             | 7  |

| 1.4  | Hybrid power filter with combination of shunt passive and shunt active power filters . . . . .                      | 8  |

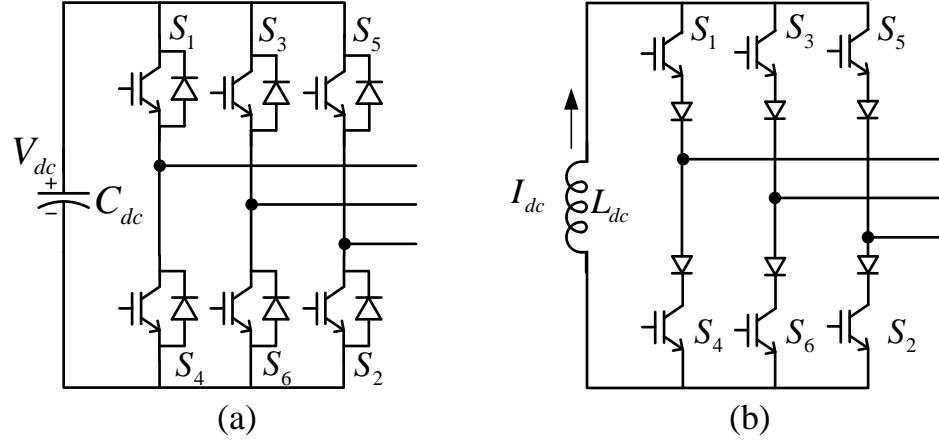

| 2.1  | (a) Voltage source converter and (b) current source converter . . . . .                                             | 14 |

| 2.2  | Single-phase H-bridge DSTATCOM topology . . . . .                                                                   | 15 |

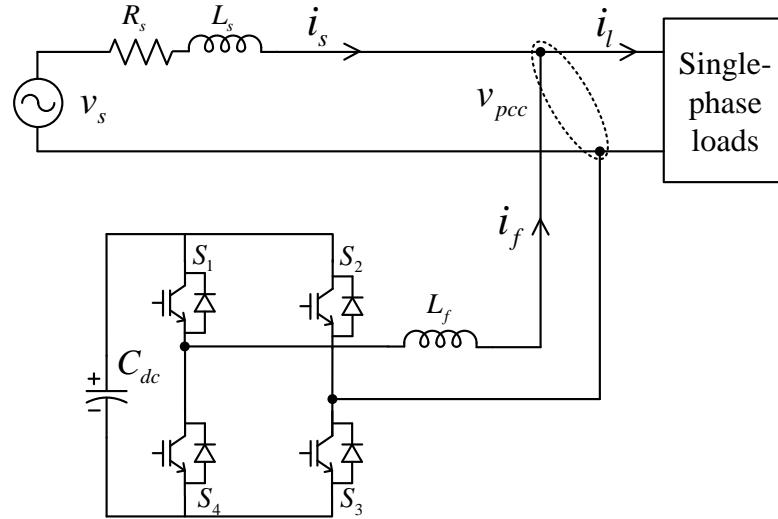

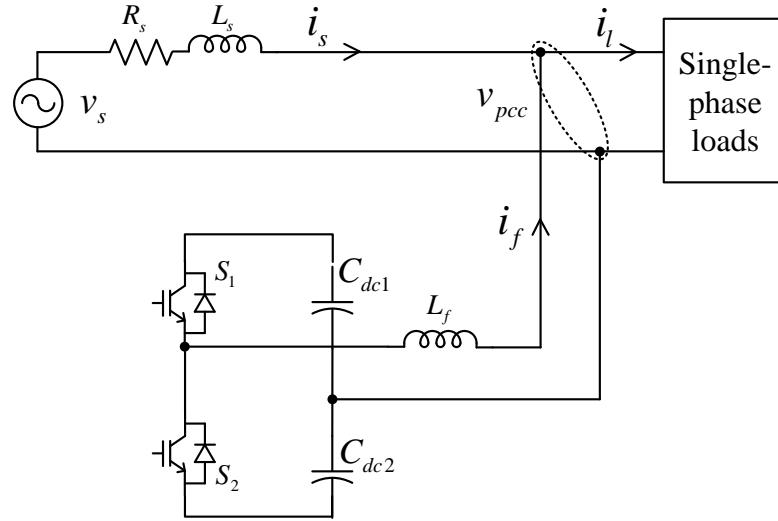

| 2.3  | Single-phase split-capacitor DSTATCOM topology . . . . .                                                            | 15 |

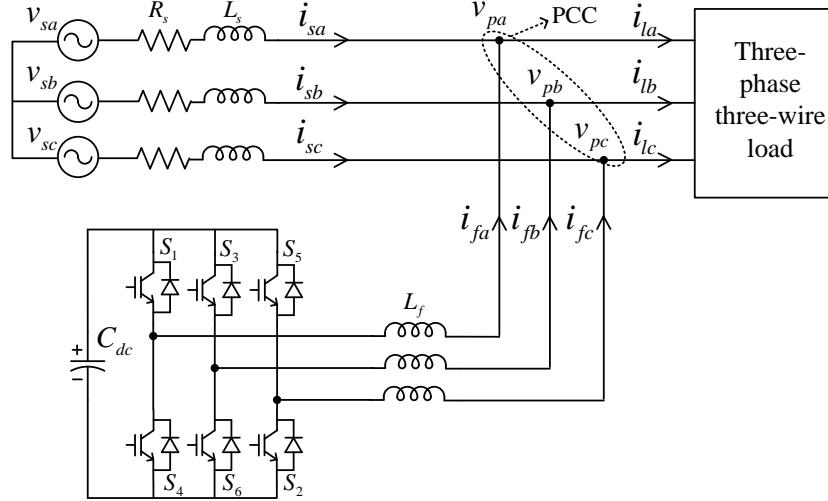

| 2.4  | Three-leg DSTATCOM in three-phase three-wire distribution system                                                    | 16 |

| 2.5  | Three single-phase H-bridge DSTATCOM topology in 3P4W distribution system . . . . .                                 | 16 |

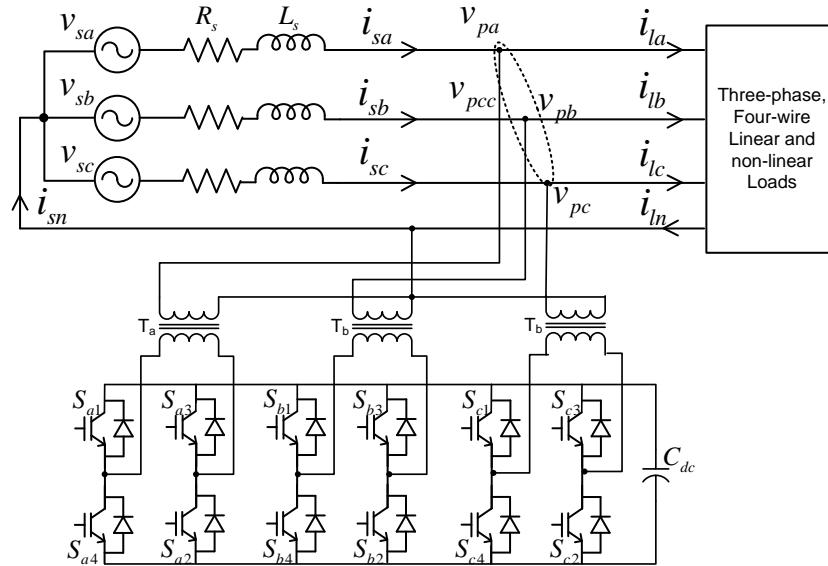

| 2.6  | Four-leg DSTATCOM topology in 3P4W distribution system . . . . .                                                    | 17 |

| 2.7  | Three-phase split-capacitor DSTATCOM topology in 3P4W distribution system . . . . .                                 | 18 |

| 2.8  | Three-leg split-capacitor DSTATCOM topology with voltage-balancing circuit in 3P4W distribution system . . . . .    | 18 |

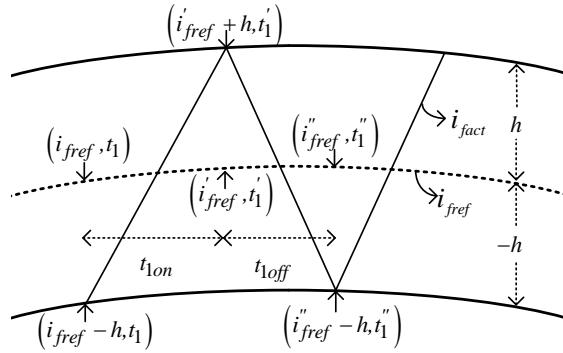

| 2.9  | Switching dynamics of hysteresis controller for $L$ -filter design . . . . .                                        | 21 |

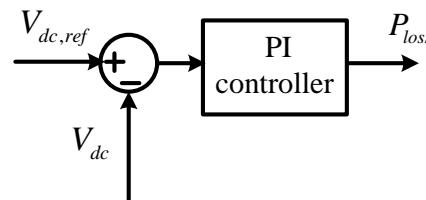

| 2.10 | DC-link voltage regulation loop in IRP theory . . . . .                                                             | 30 |

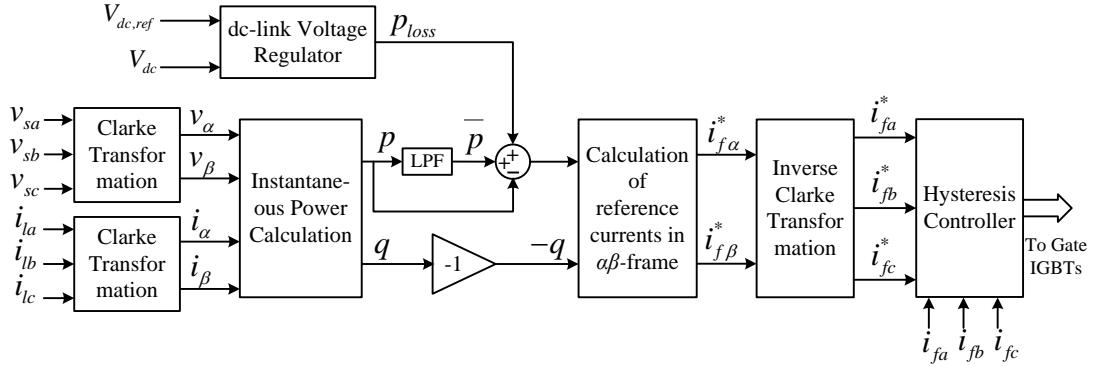

| 2.11 | Control algorithm for DSTATCOM with IRP theory . . . . .                                                            | 31 |

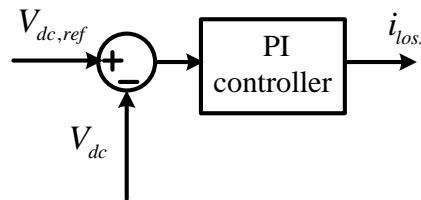

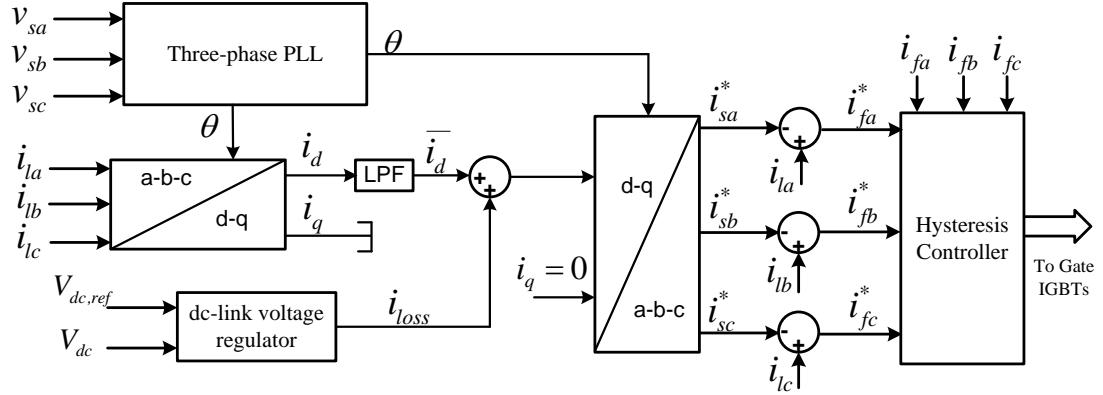

| 2.12 | DC-link voltage regulation loop in SRF theory . . . . .                                                             | 33 |

| 2.13 | Control algorithm for DSTATCOM with SRF theory . . . . .                                                            | 34 |

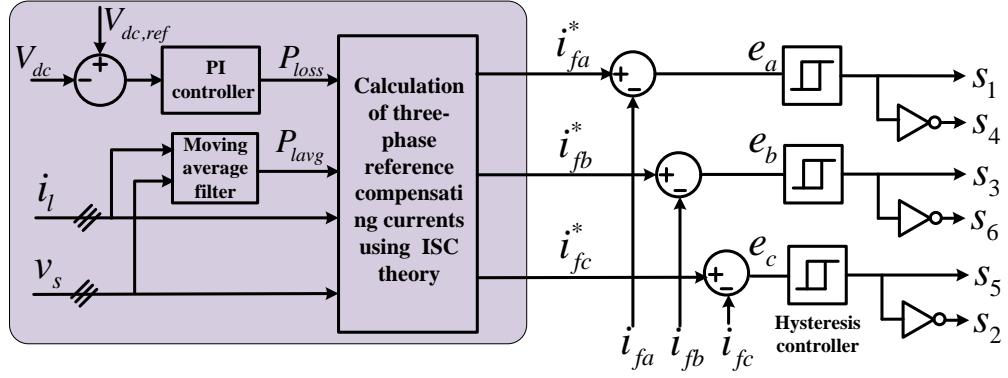

| 2.14 | Control algorithm for DSTATCOM with ISC theory . . . . .                                                            | 37 |

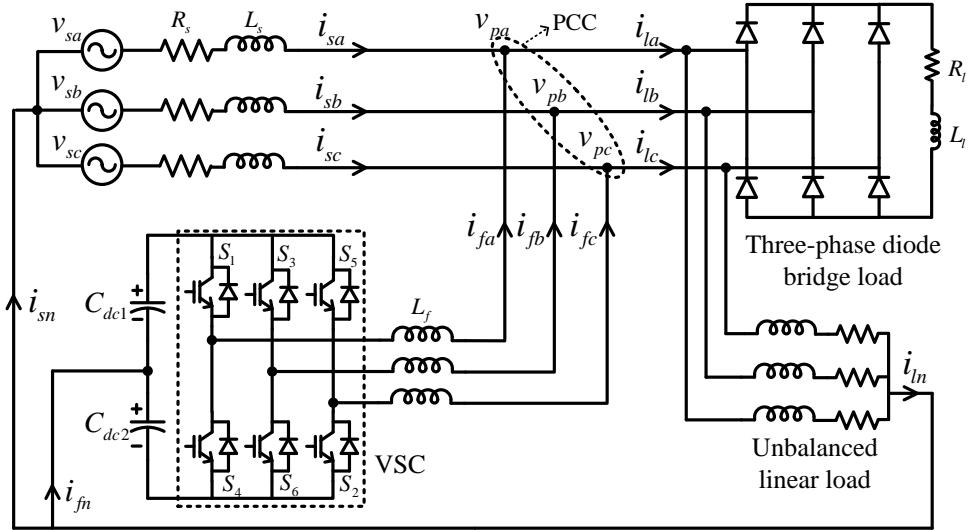

| 3.1  | Three-leg split-capacitor DSTATCOM in three-phase distribution system for power quality improvement . . . . .       | 40 |

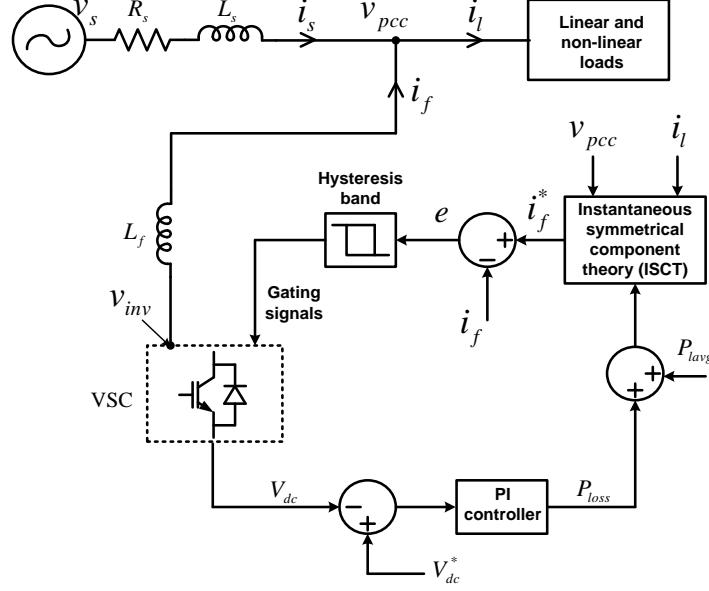

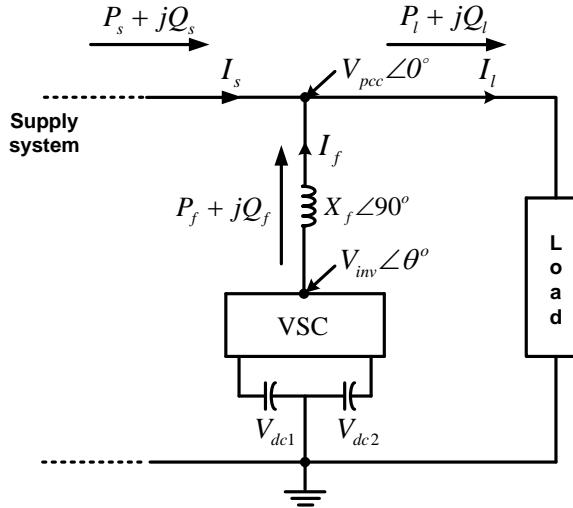

| 3.2  | Single-line diagram of split-capacitor DSTATCOM with fixed dc-link voltage (conventional method) . . . . .          | 41 |

| 3.3  | Single-line diagram of power flow circuit of three-phase system . . . . .                                           | 42 |

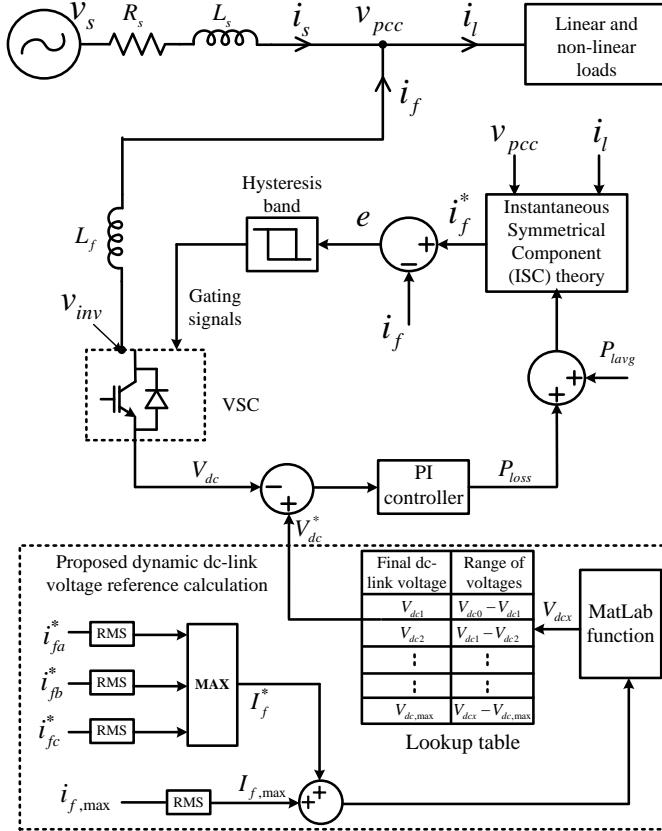

| 3.4  | Single-line diagram of split-capacitor DSTATCOM with dynamic dc-link voltage regulation (proposed method) . . . . . | 45 |

|      |                                                                                                                                                                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

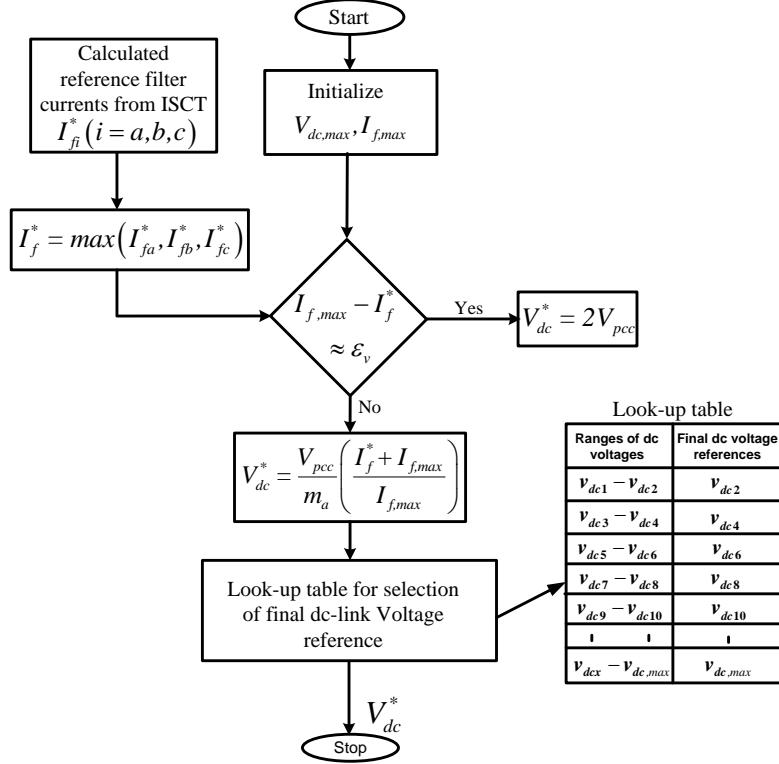

| 3.5  | Flow-chart for the selection of reference dc-link voltage . . . . .                                                                                                                                                                                                                                                                               | 46 |

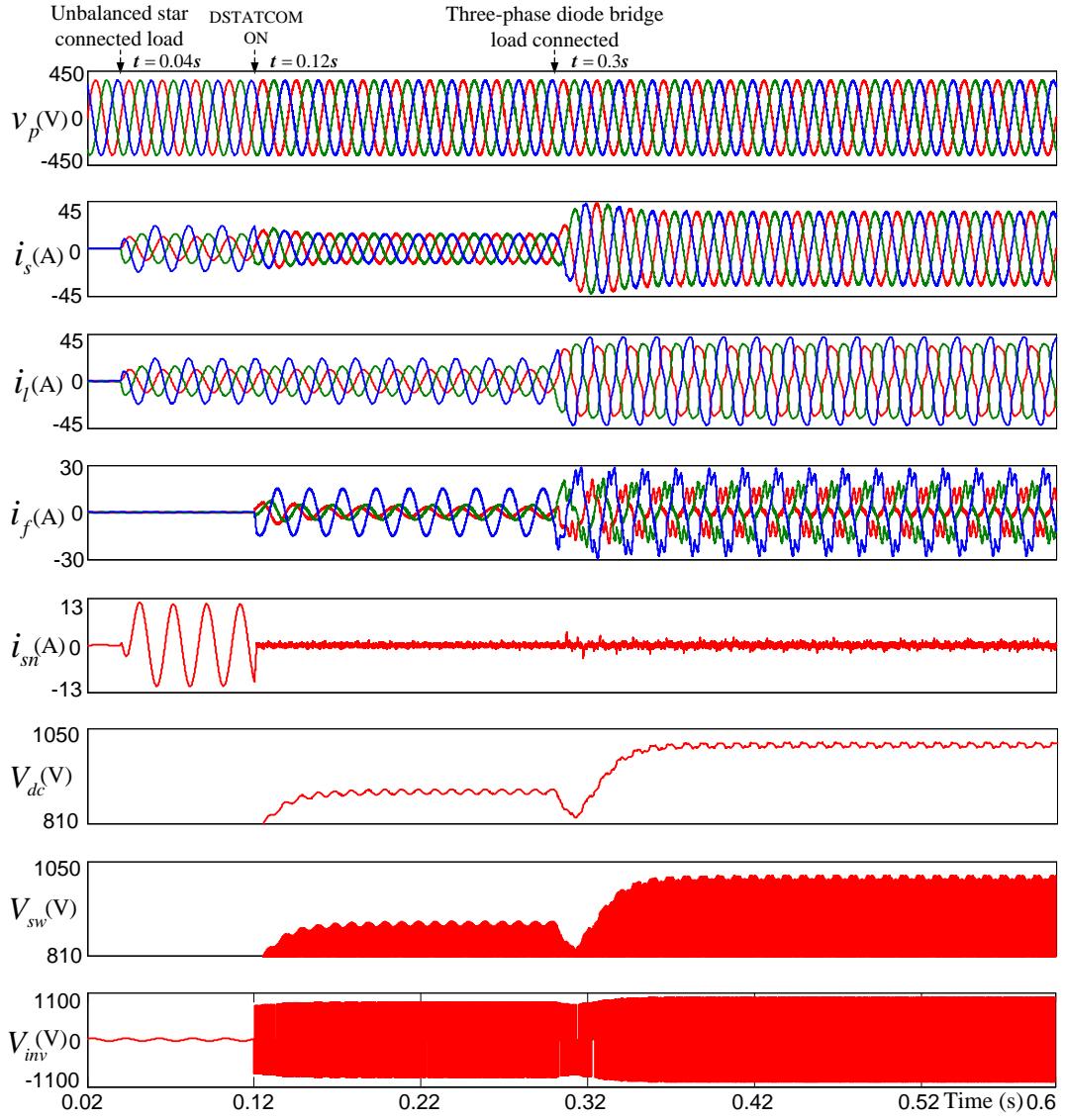

| 3.6  | Performance of DSTATCOM with fixed dc-link voltage regulation (conventional method) . . . . .                                                                                                                                                                                                                                                     | 48 |

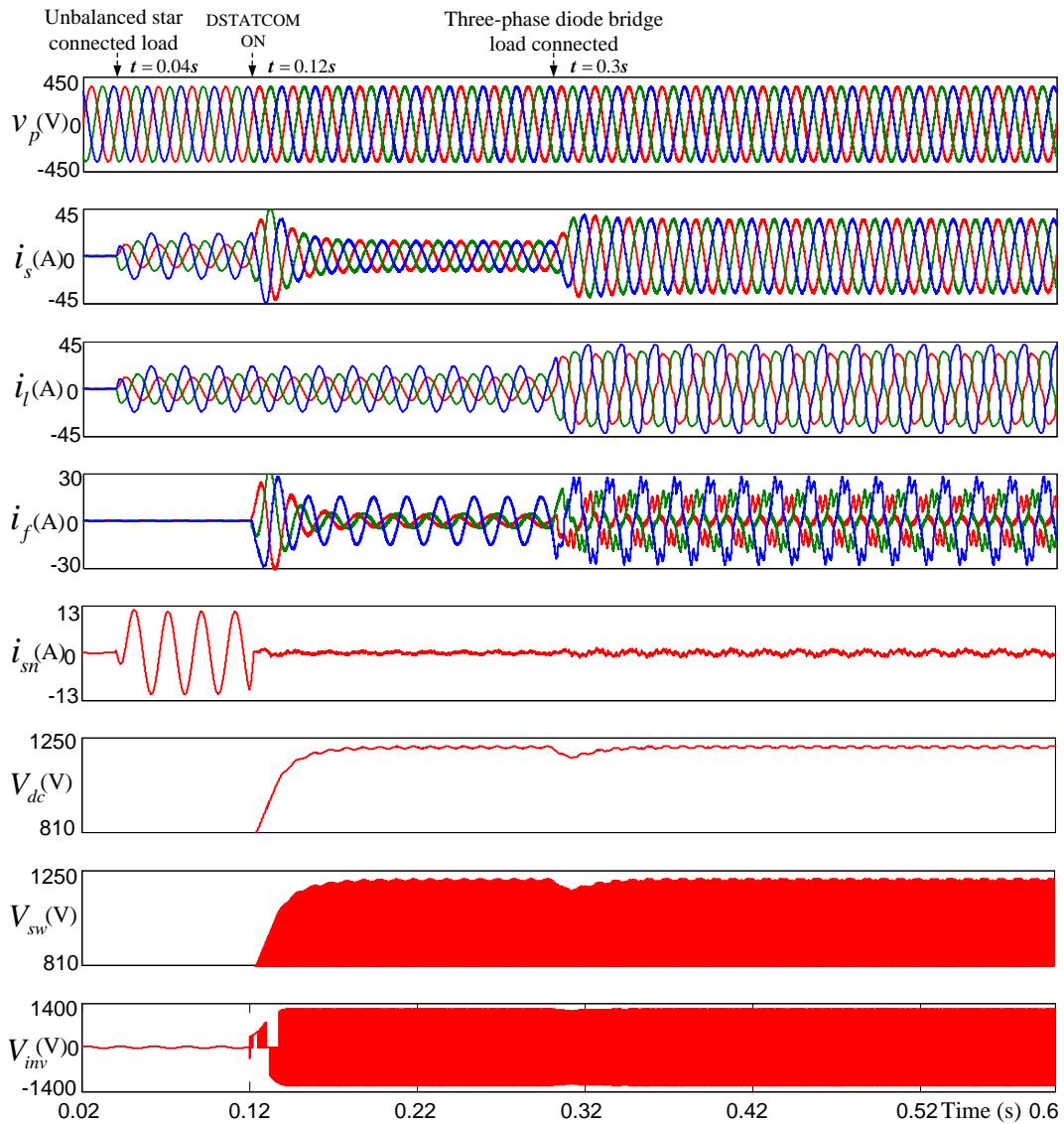

| 3.7  | Performance of DSTATCOM with dynamic dc-link voltage regulation (proposed method) . . . . .                                                                                                                                                                                                                                                       | 50 |

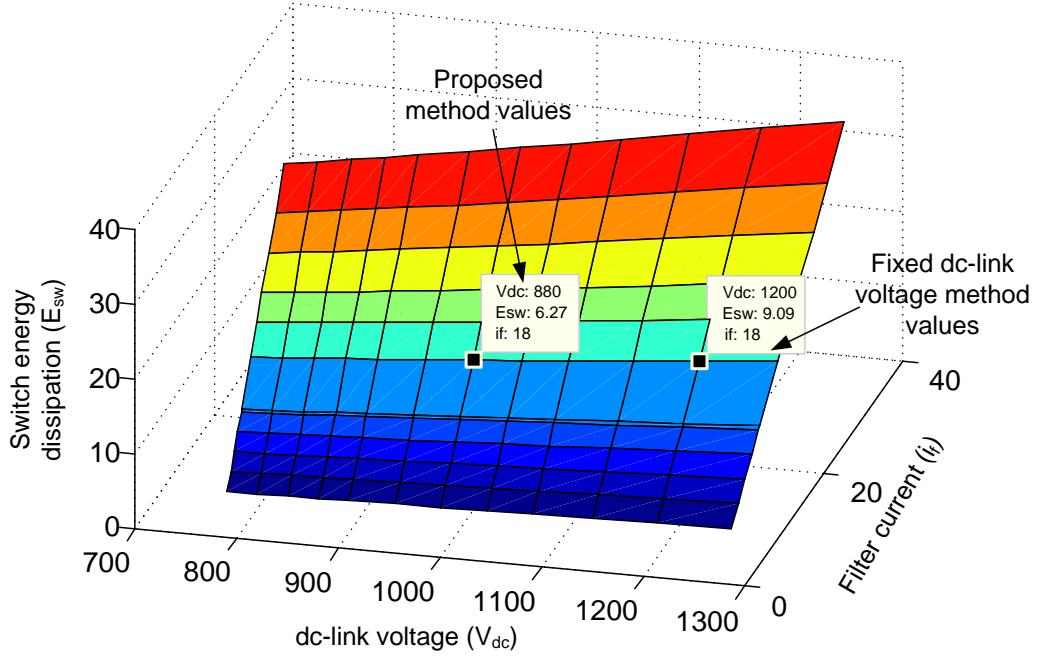

| 3.8  | Variation of energy dissipation of switch with respect to dc-link voltage and filter current . . . . .                                                                                                                                                                                                                                            | 51 |

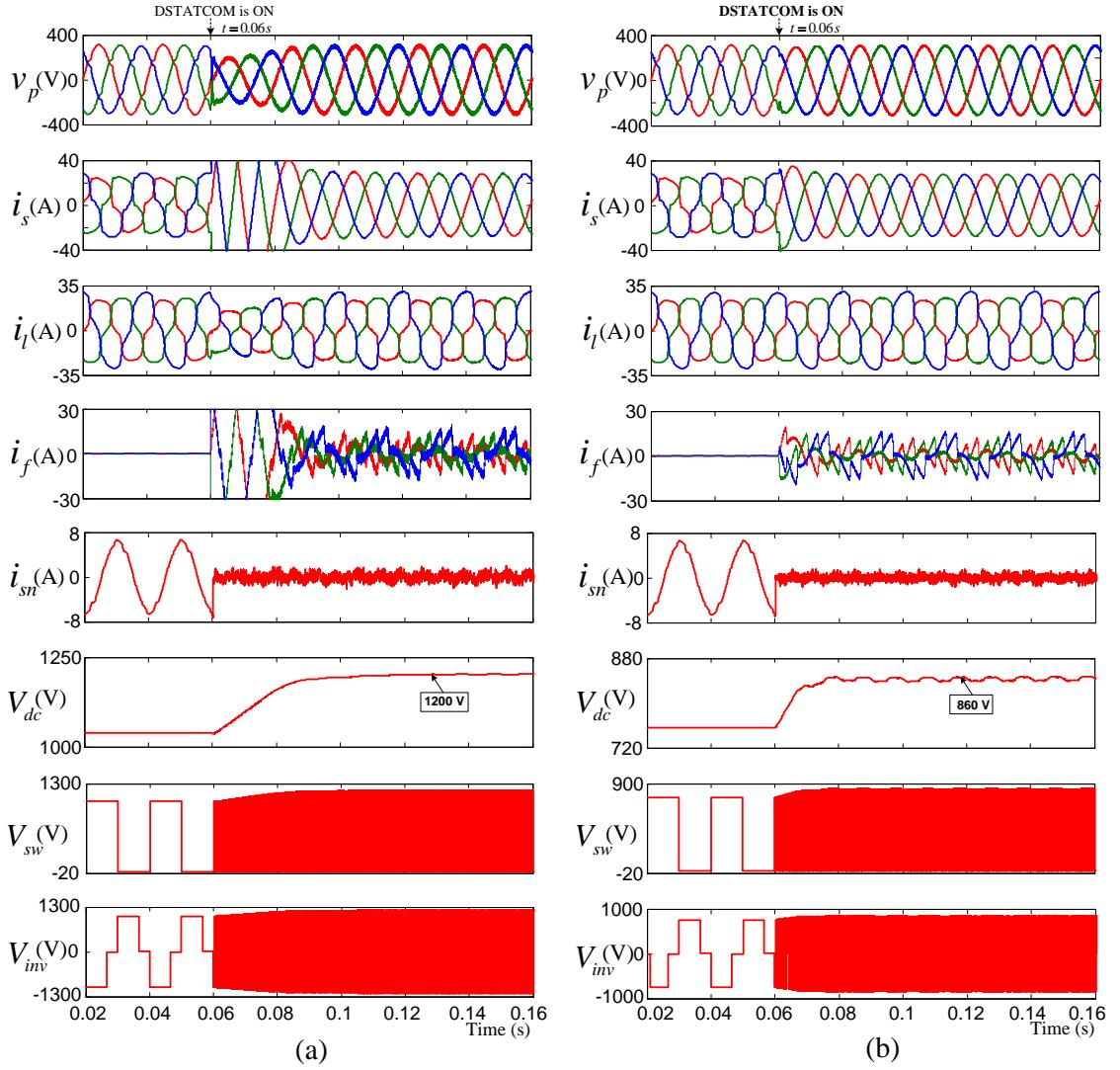

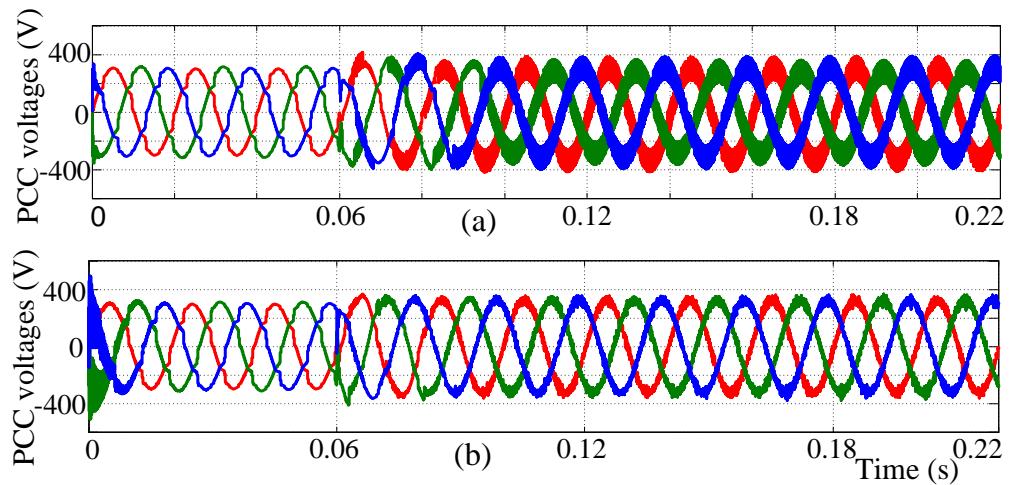

| 3.9  | Simulation results with non-stiff voltage source (a) fixed dc-link voltage method and (b) dynamic dc-link voltage method . . . . .                                                                                                                                                                                                                | 52 |

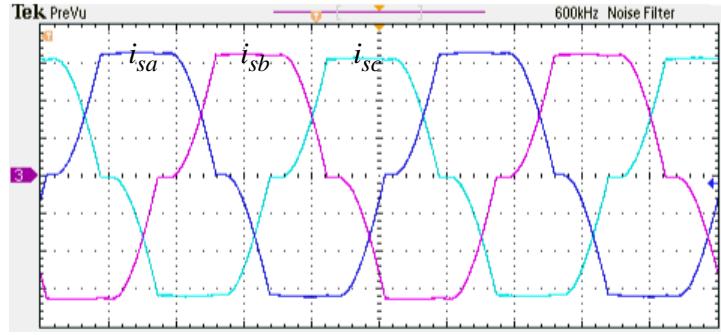

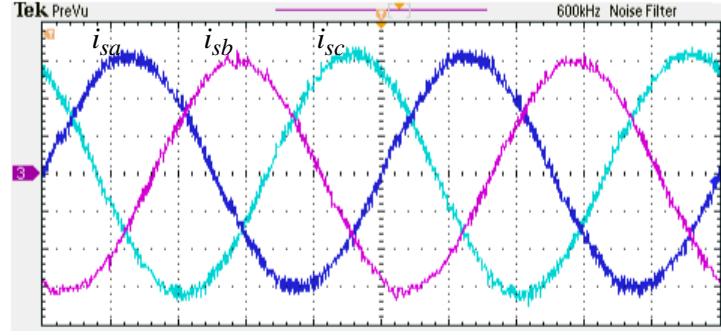

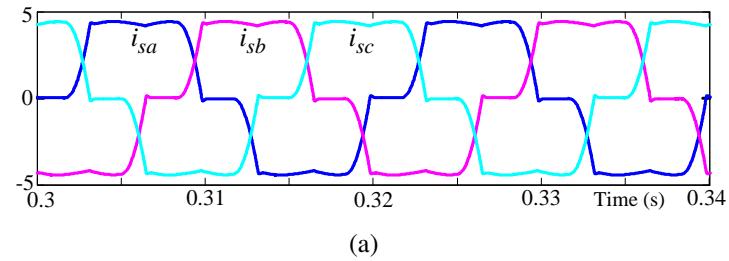

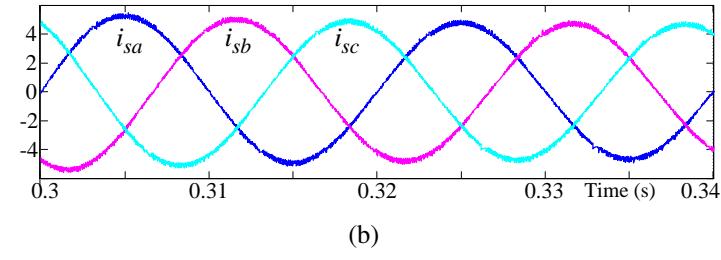

| 3.10 | Experimental waveforms of three-phase source currents ( $i_{sa}, i_{sb}, i_{sc}$ ) for non-linear diode bridge load condition (a) before compensation and (b) after compensation (scale: current 1 A/div) . . . . .                                                                                                                               | 54 |

| 3.11 | Simulation waveforms of three-phase source currents ( $i_{sa}, i_{sb}, i_{sc}$ ) for non-linear diode bridge load condition (a) before compensation and (b) after compensation . . . . .                                                                                                                                                          | 54 |

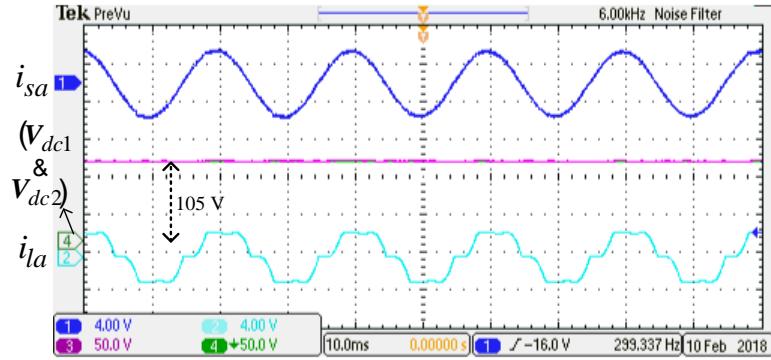

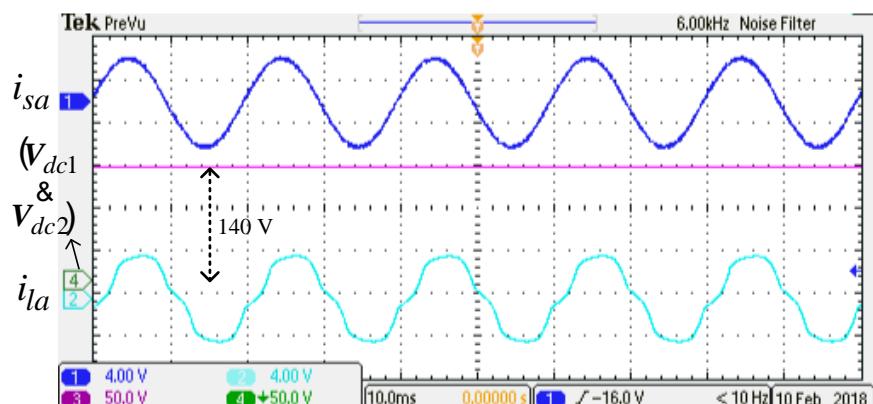

| 3.12 | Experimental waveforms of phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) for non-linear load condition (scale: current 4 A/div, voltage 50 V/div) . . . . .                                                                                                             | 55 |

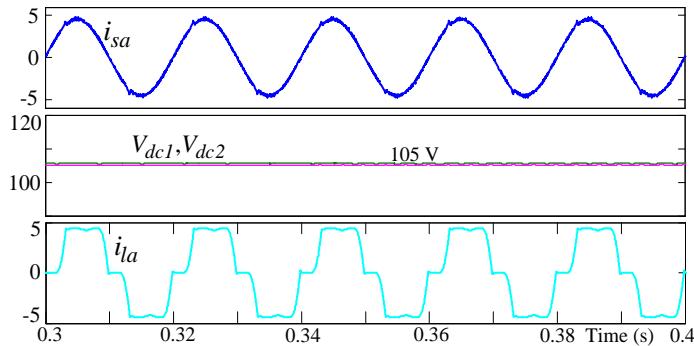

| 3.13 | Simulation waveforms of phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) for non-linear load condition . . . . .                                                                                                                                                          | 55 |

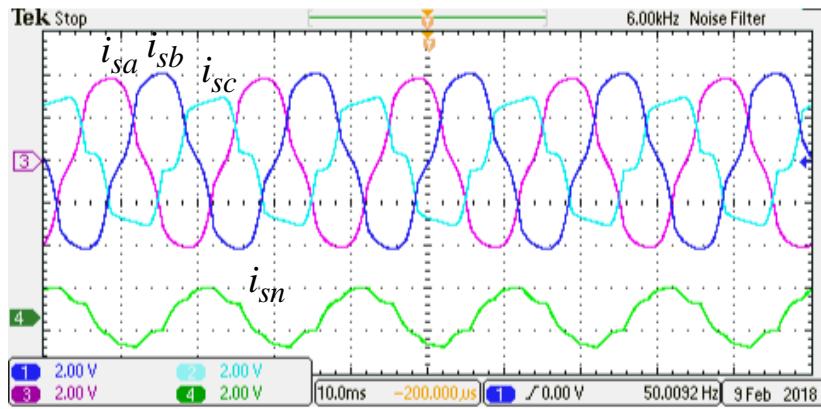

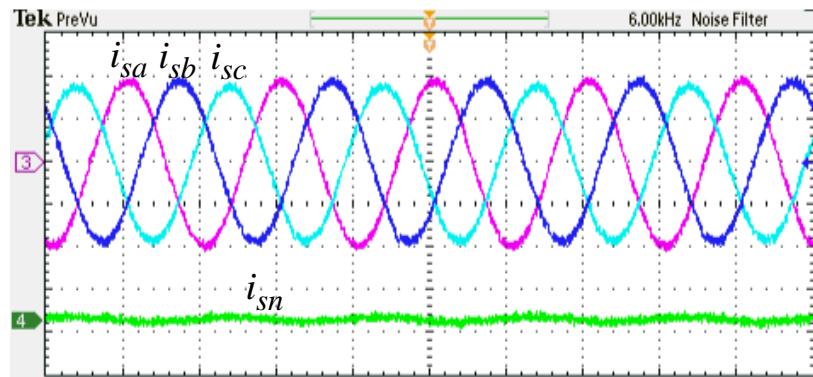

| 3.14 | Experimental waveforms of three-phase source currents ( $i_{sa}, i_{sb}, i_{sc}$ ) and source side neutral current ( $i_{sn}$ ) for unbalanced non-linear load condition (a) before compensation and (b) after compensation (scale: current 2 A/div) . . . . .                                                                                    | 56 |

| 3.15 | Phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) for unbalanced non-linear load condition (scale: current 4 A/div, voltage 50 V/div) . . . . .                                                                                                                            | 56 |

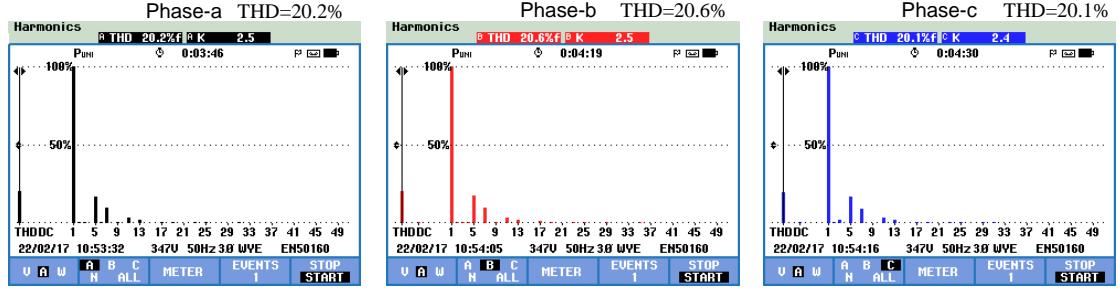

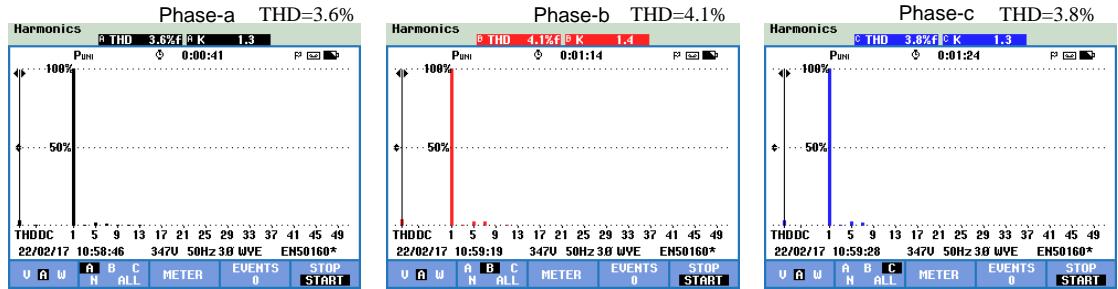

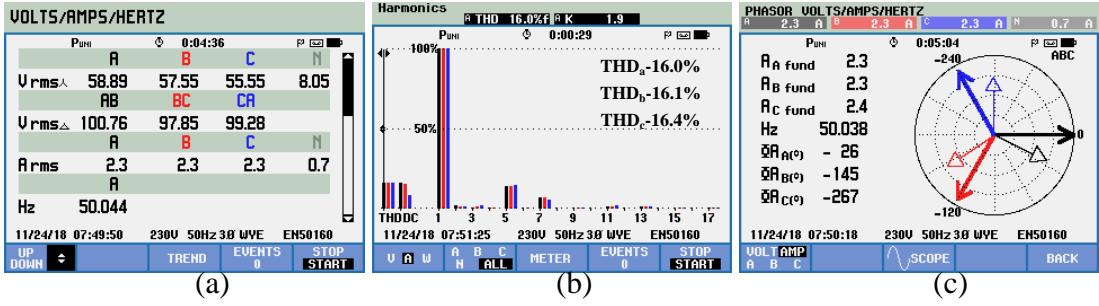

| 3.16 | Before compensation the harmonic spectra of three-phase source currents for non-linear diode bridge load condition . . . . .                                                                                                                                                                                                                      | 57 |

| 3.17 | After compensation the harmonic spectra of three-phase source currents for non-linear diode bridge load condition . . . . .                                                                                                                                                                                                                       | 57 |

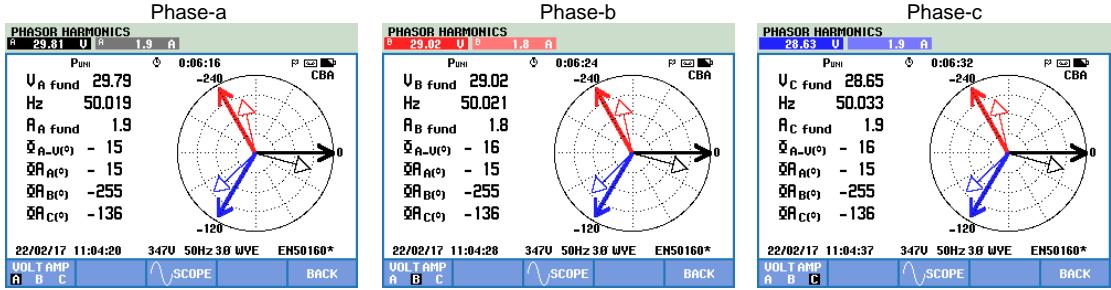

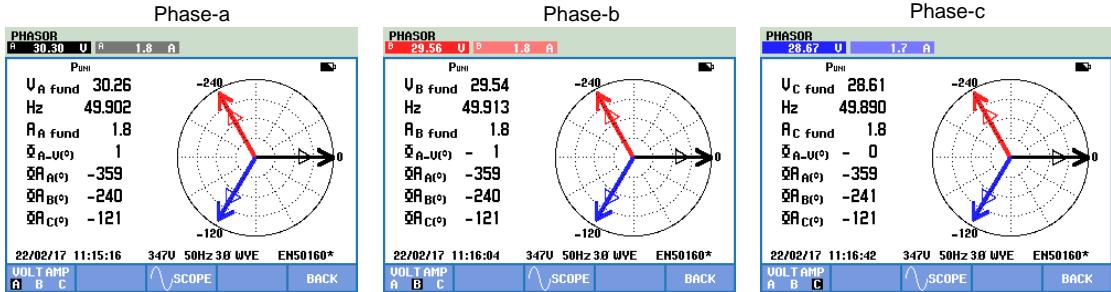

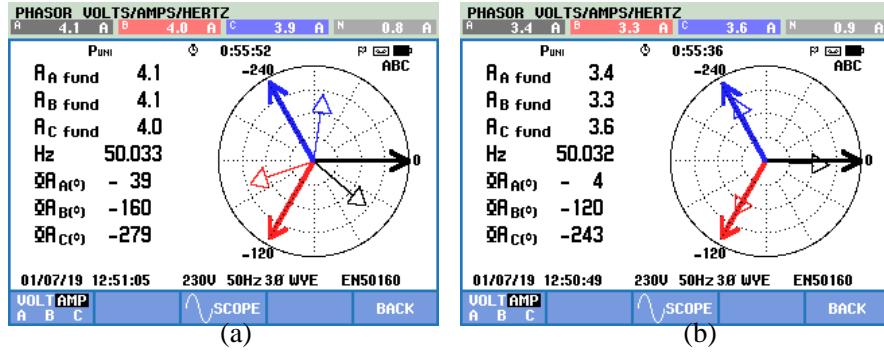

| 3.18 | Before compensation the phasor diagram of three-phase PCC voltages and source currents for non-linear diode bridge load condition . . . . .                                                                                                                                                                                                       | 58 |

| 3.19 | After compensation the phasor diagram of three-phase PCC voltages and source currents for non-linear diode bridge load condition . . . . .                                                                                                                                                                                                        | 58 |

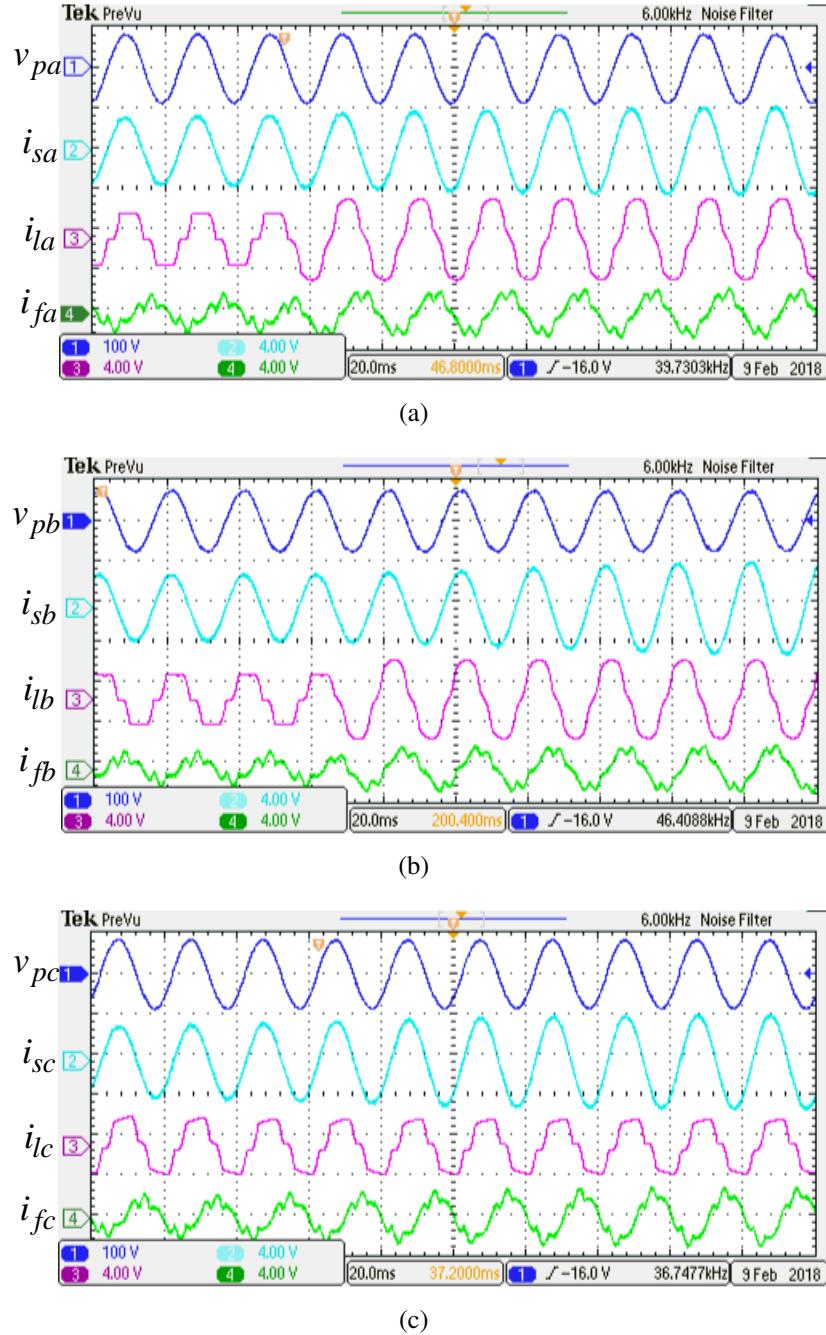

| 3.20 | PCC voltages ( $v_{pa}, v_{pb}, v_{pc}$ ), source currents ( $i_{sa}, i_{sb}, i_{sc}$ ), load currents ( $i_{la}, i_{lb}, i_{lc}$ ) and filter currents ( $i_{fa}, i_{fb}, i_{fc}$ ) for transient load variation with the proposed method (a) phase- $a$ (b) phase- $b$ and (c) phase- $c$ (scale: voltage 100 V/div, current 4 A/div) . . . . . | 59 |

|      |                                                                                                                                                                                                                                                         |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

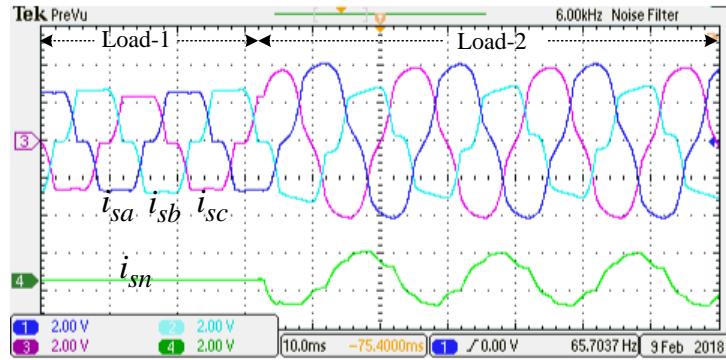

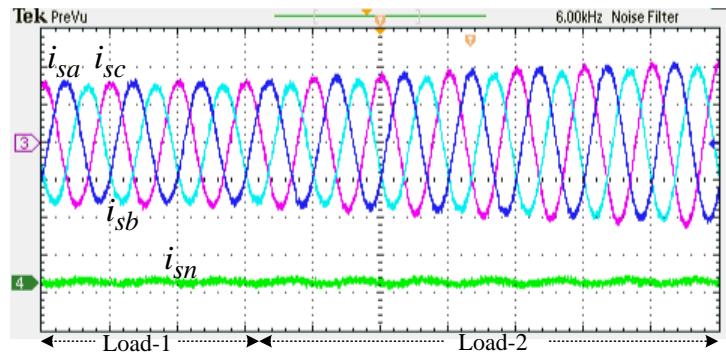

| 3.21 | Experimental waveforms of three-phase source currents ( $i_{sa}, i_{sb}, i_{sc}$ ) and source side neutral current ( $i_{sn}$ ) for load-1 and load-2 (a) before compensation and (b) after compensation (scale: current 2 A/div) . . . . .             | 60 |

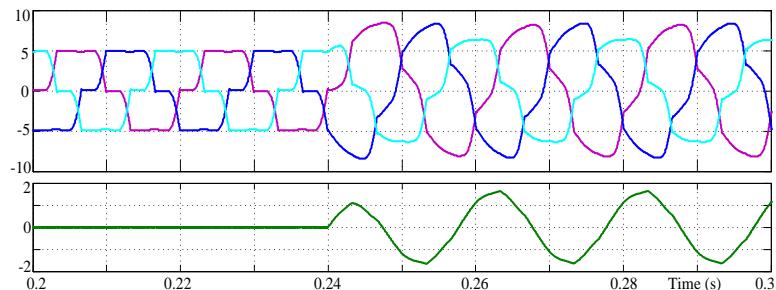

| 3.22 | Simulation waveforms of three-phase source currents ( $i_{sa}, i_{sb}, i_{sc}$ ) and source side neutral current ( $i_{sn}$ ) for load-1 and load-2 (a) before compensation and (b) after compensation . . . . .                                        | 60 |

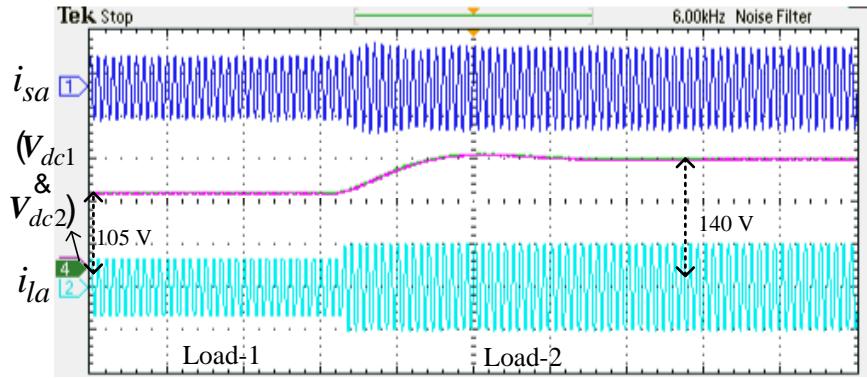

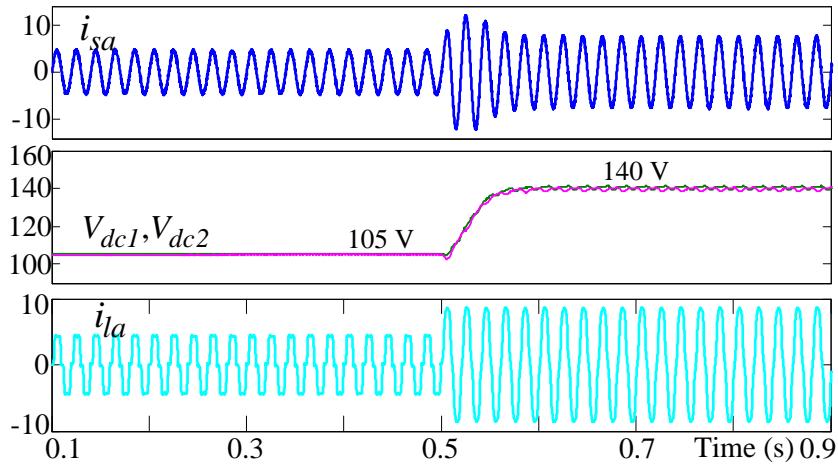

| 3.23 | Experimental waveforms of phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) for transient load variation (scale: current 4 A/div, voltage 50 V/div) . . . . .                    | 61 |

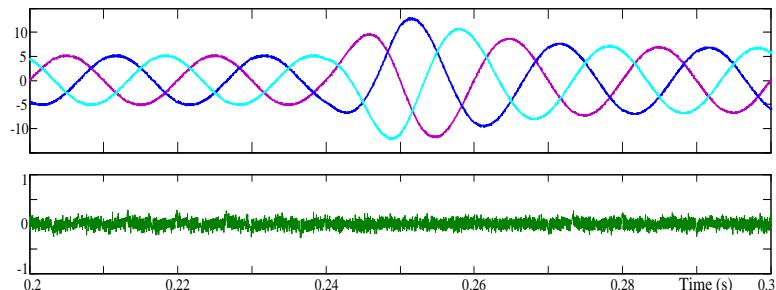

| 3.24 | Simulation waveforms of phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) for transient load variation                                                                           | 61 |

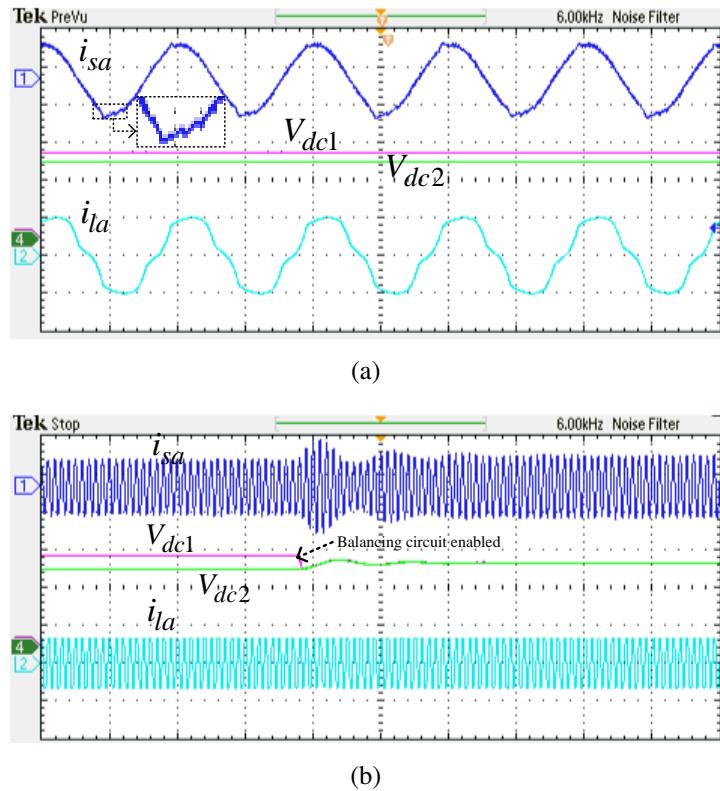

| 3.25 | Phase- $a$ source current ( $i_{sa}$ ), dc-link voltages ( $V_{dc1}, V_{dc2}$ ) and phase- $a$ load current ( $i_{la}$ ) during unbalanced non-linear load condition (a) before voltage balancing and (b) after voltage balancing . . . . .             | 62 |

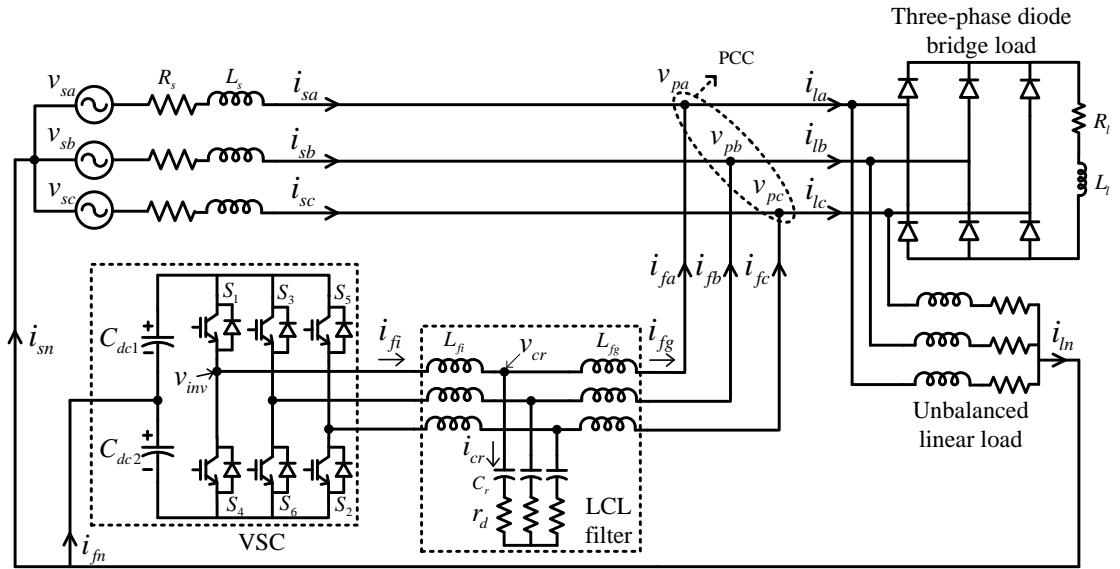

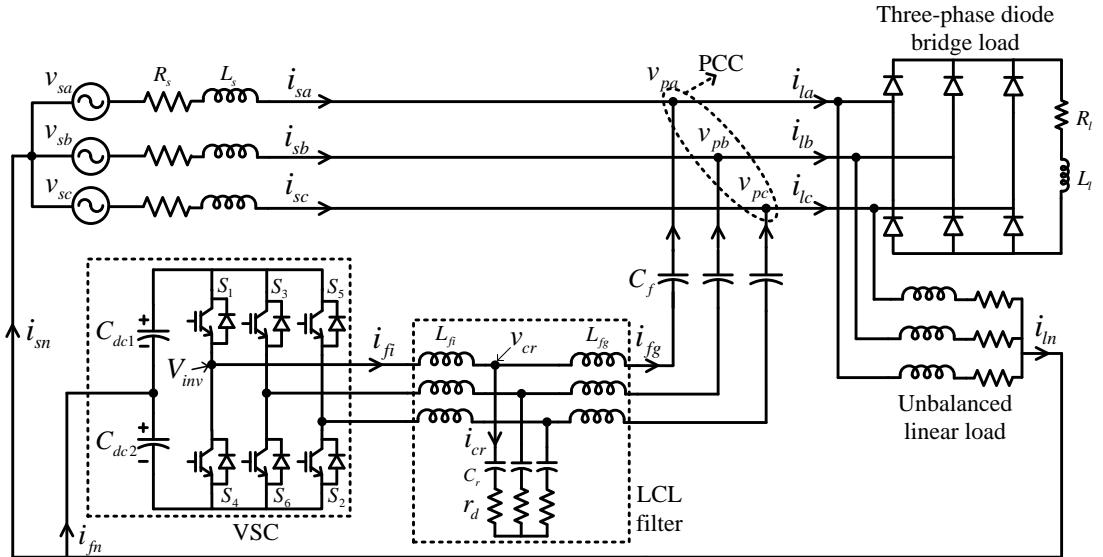

| 4.1  | Schematic diagram of <i>LCL</i> -filter based DSTATCOM connection in three-phase four-wire (3P4W) distribution system for power quality improvement . . . . .                                                                                           | 68 |

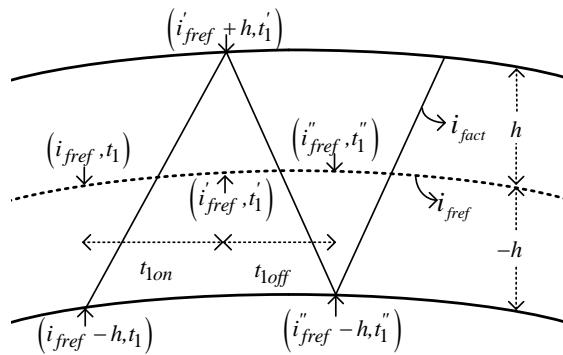

| 4.2  | Switching dynamics of controller for <i>LCL</i> -filter design . . . . .                                                                                                                                                                                | 68 |

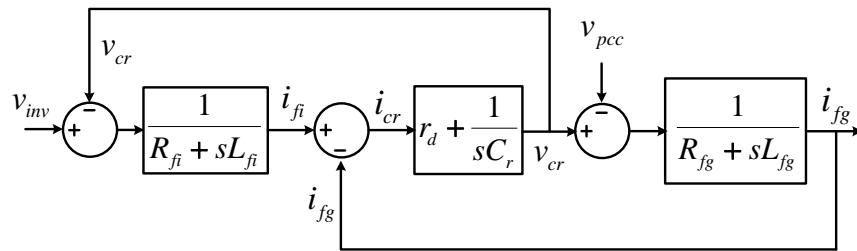

| 4.3  | Block diagram representation of <i>LCL</i> -filter based system . . . . .                                                                                                                                                                               | 70 |

| 4.4  | Frequency response of <i>LCL</i> -filter (a) for different $C_r$ values without damping (i.e., $r_d = 0 \Omega$ ) and (b) for different $r_d$ values when $C_r = 8 \mu\text{F}$                                                                         | 73 |

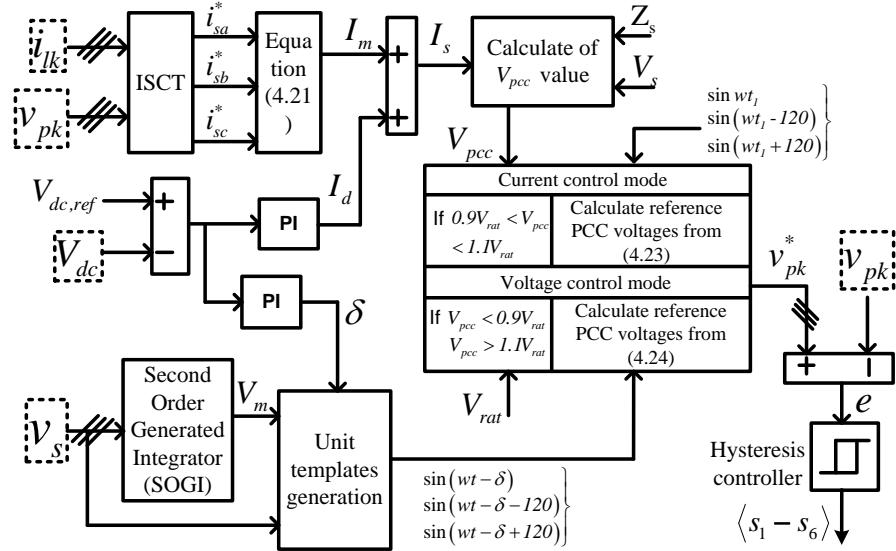

| 4.5  | Control algorithm for CCM and VCM modes of operation . . . . .                                                                                                                                                                                          | 76 |

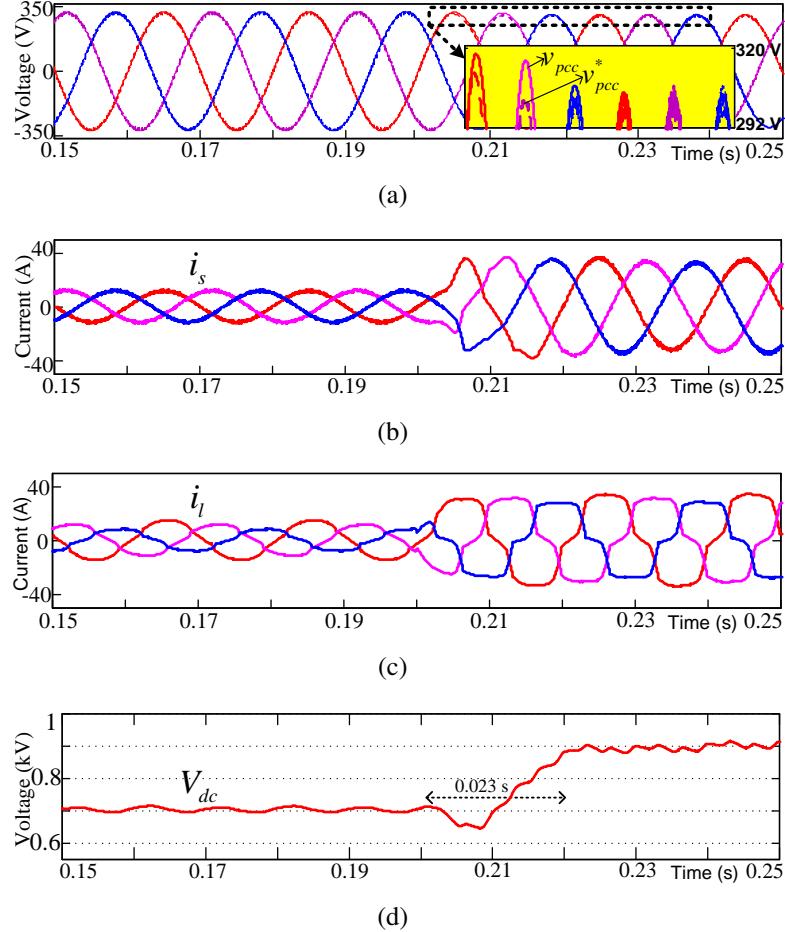

| 4.6  | Results in CCM mode of operation (a) PCC voltages ( $v_{pcc}^*$ and $v_{pcc}$ ) (b) source current ( $i_s$ ) (c) load current ( $i_l$ ) and (d) dc-link voltage ( $V_{dc}$ ) .                                                                          | 82 |

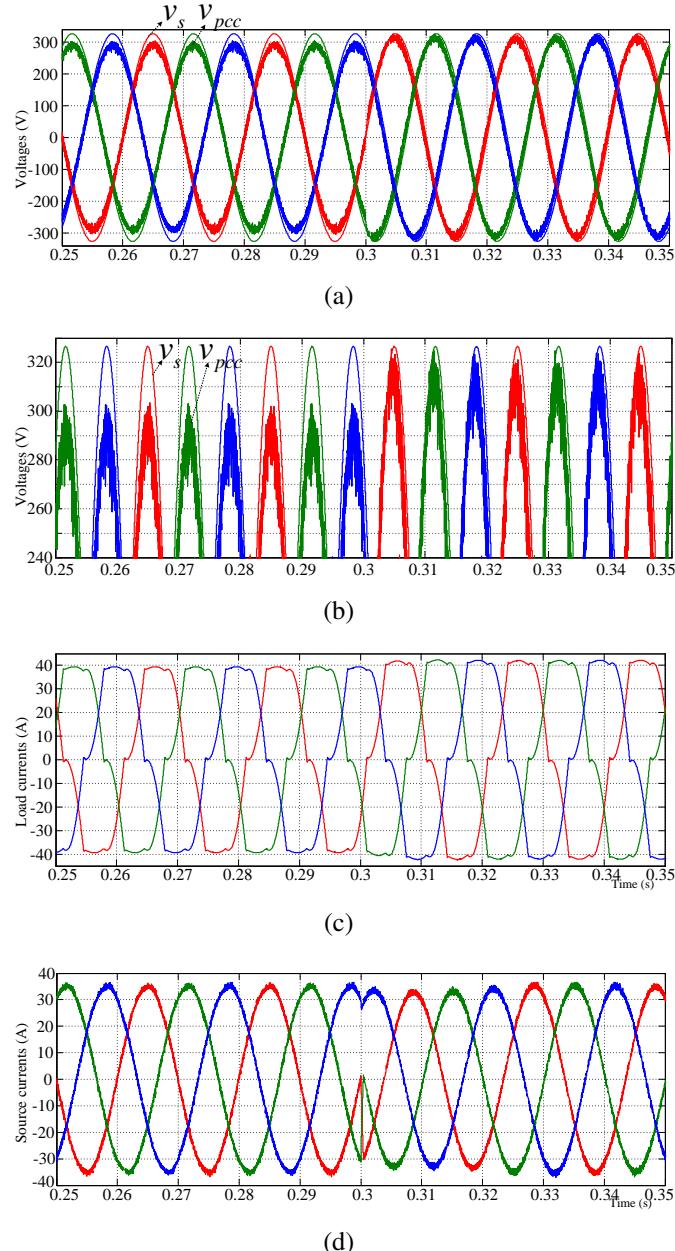

| 4.7  | Results in VCM mode of operation: (a) source voltages ( $v_s$ ) and PCC voltages ( $v_{pcc}$ ), (b) vertically zoomed figure of (a), (c) load currents and (d) source currents . . . . .                                                                | 83 |

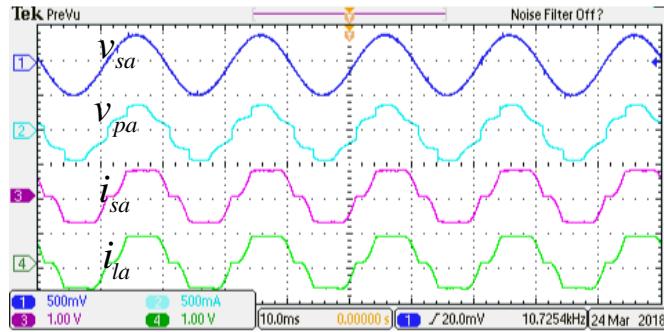

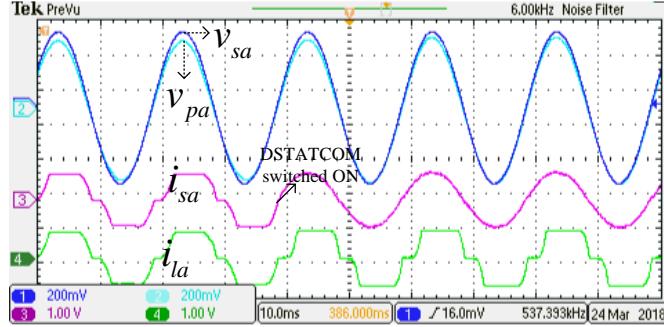

| 4.8  | Before compensation: source voltage ( $v_{sa}$ ), PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ) and load current ( $i_{la}$ ) (scale: voltage 80 V/div, current 2 A/div) . . . . .                                                              | 86 |

| 4.9  | After compensation: source voltage ( $v_{sa}$ ), PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ) and load current ( $i_{la}$ ) with the proposed <i>LCL</i> -DSTATCOM (scale: voltage 40 V/div, current 2 A/div) . . . . .                        | 86 |

| 4.10 | Before and after DSTATCOM operation: source voltage ( $v_{sa}$ ), PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ) and load current ( $i_{la}$ ) (scale: voltage 40 V/div, current 2 A/div) . . . . .                                              | 87 |

| 4.11 | Performance of the proposed <i>LCL</i> -DSTATCOM during transient load variation: source voltage ( $v_{sa}$ ), PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ) and load current ( $i_{la}$ ) (scale: voltage 80 V/div, current 2 A/div) . . . . . | 87 |

|      |                                                                                                                                                                                                                                                                                                                                 |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

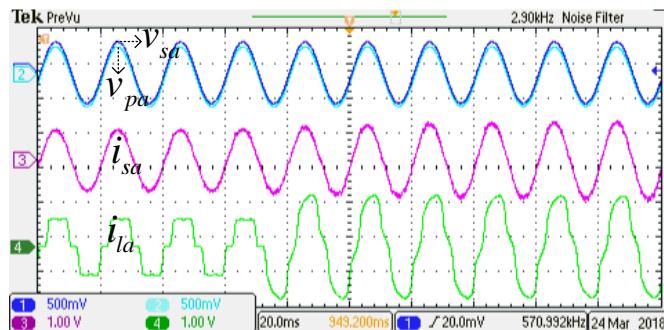

| 4.12 | Performance of the proposed <i>LCL</i> -DSTATCOM with variable dc-link voltage regulation during transient load variation: PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ), load current ( $i_{la}$ ) and dc-link voltage ( $V_{dc}$ ) (scale: PCC voltage 80 V/div, dc-link voltage 20 V/div, current 2 A/div) . . . . . | 88  |

| 4.13 | Zoomed figure of 4.12 during load-1 condition (scale: PCC voltage 80 V/div, dc-link voltage 20 V/div, current 2 A/div) . . . . .                                                                                                                                                                                                | 88  |

| 4.14 | Zoomed figure of 4.12 during load-2 condition (scale: PCC voltage 80 V/div, dc-link voltage 20 V/div, current 2 A/div) . . . . .                                                                                                                                                                                                | 88  |

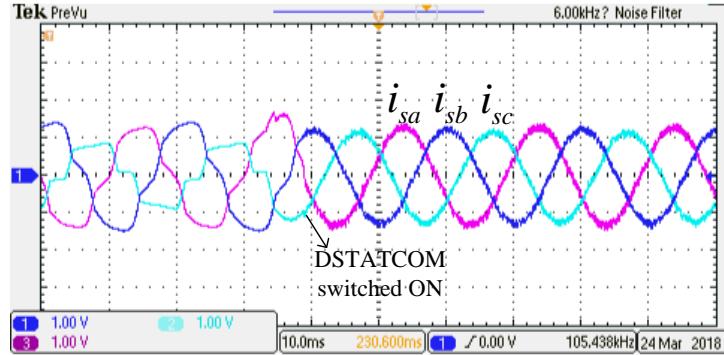

| 4.15 | Three-phase source currents ( $i_{sa}$ , $i_{sb}$ , $i_{sc}$ ) before and after compensation with the proposed method (scale: current 4 A/div) . . . . .                                                                                                                                                                        | 89  |

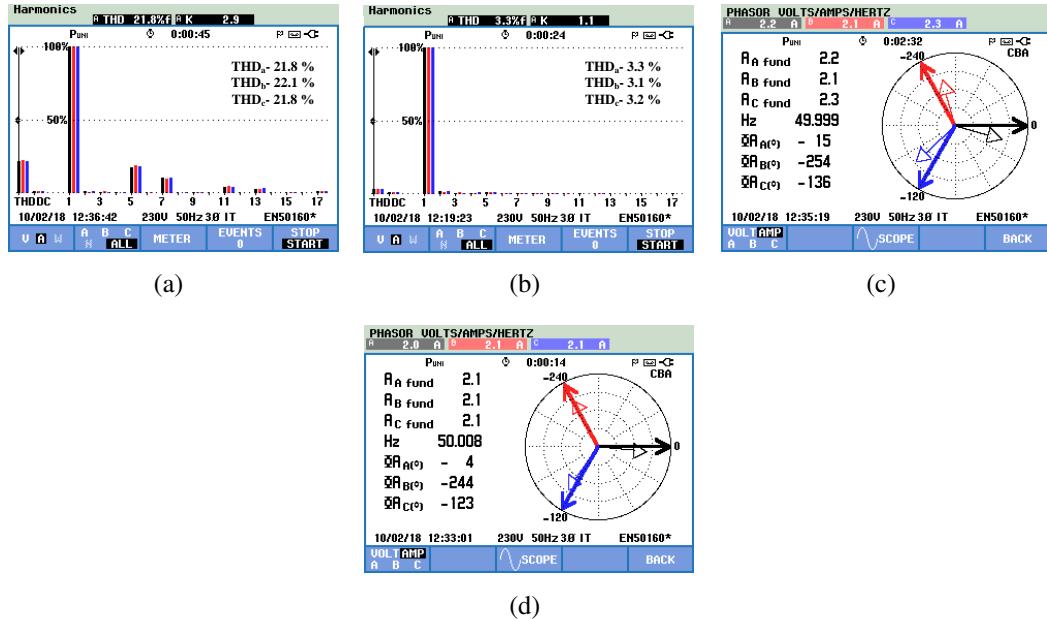

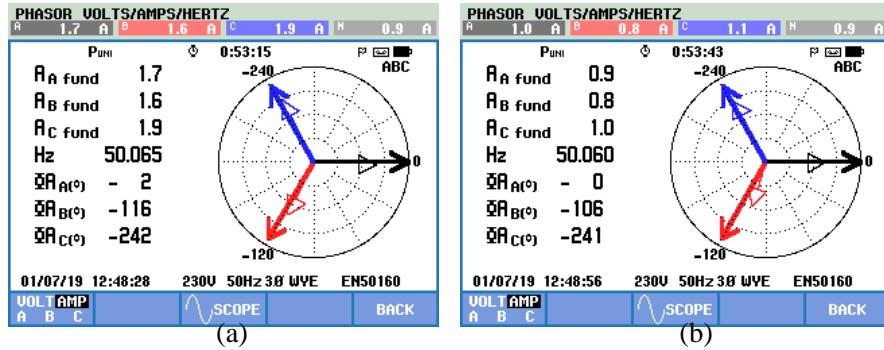

| 4.16 | (a) and (b) Harmonic spectrum of three-phase source currents before and after compensation for load-1 condition, (c) and (d) phasor diagrams of source voltages and source currents before and after compensation for load-1 condition . . . . .                                                                                | 89  |

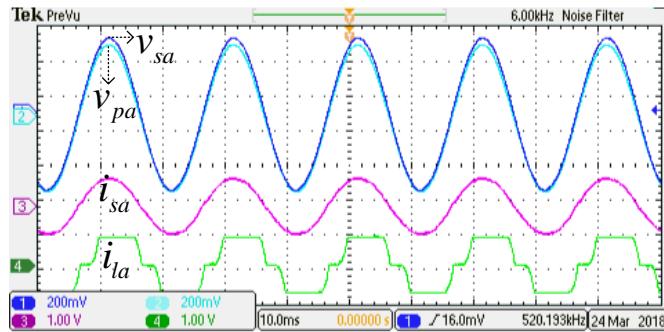

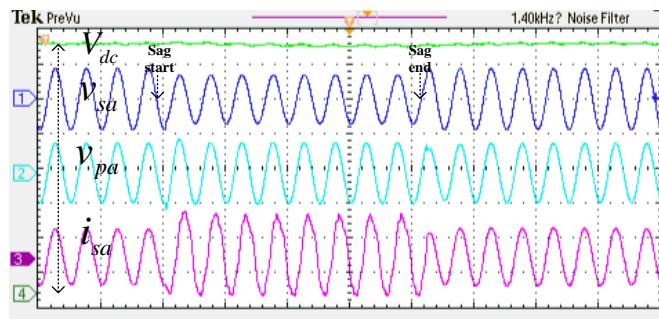

| 4.17 | VCM mode of operation during 20% sag in supply voltage: source voltage ( $v_{sa}$ ), PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ) and dc-link voltage ( $V_{dc}$ ) (scale: PCC voltage and source voltage 80 V/div, dc-link voltage 20 V/div, current 2 A/div) . . . . .                                               | 90  |

| 5.1  | Hybrid DSTATCOM topology for power quality improvement in three-phase four wire (3P4W) distribution system . . . . .                                                                                                                                                                                                            | 94  |

| 5.2  | Block diagram of the dc-link voltage controller . . . . .                                                                                                                                                                                                                                                                       | 100 |

| 5.3  | Graph between dc-link voltage and filter current for different series ac-capacitor values . . . . .                                                                                                                                                                                                                             | 102 |

| 5.4  | Graph between filter current and required dc-link voltage for different topologies (a) when $C_f=56\ \mu\text{F}$ and (b) when $C_f=336\ \mu\text{F}$ . . . . .                                                                                                                                                                 | 103 |

| 5.5  | Graph between filter current and switching losses in VSC (a) for $C_f=56\ \mu\text{F}$ and (b) for $C_f=336\ \mu\text{F}$ . . . . .                                                                                                                                                                                             | 104 |

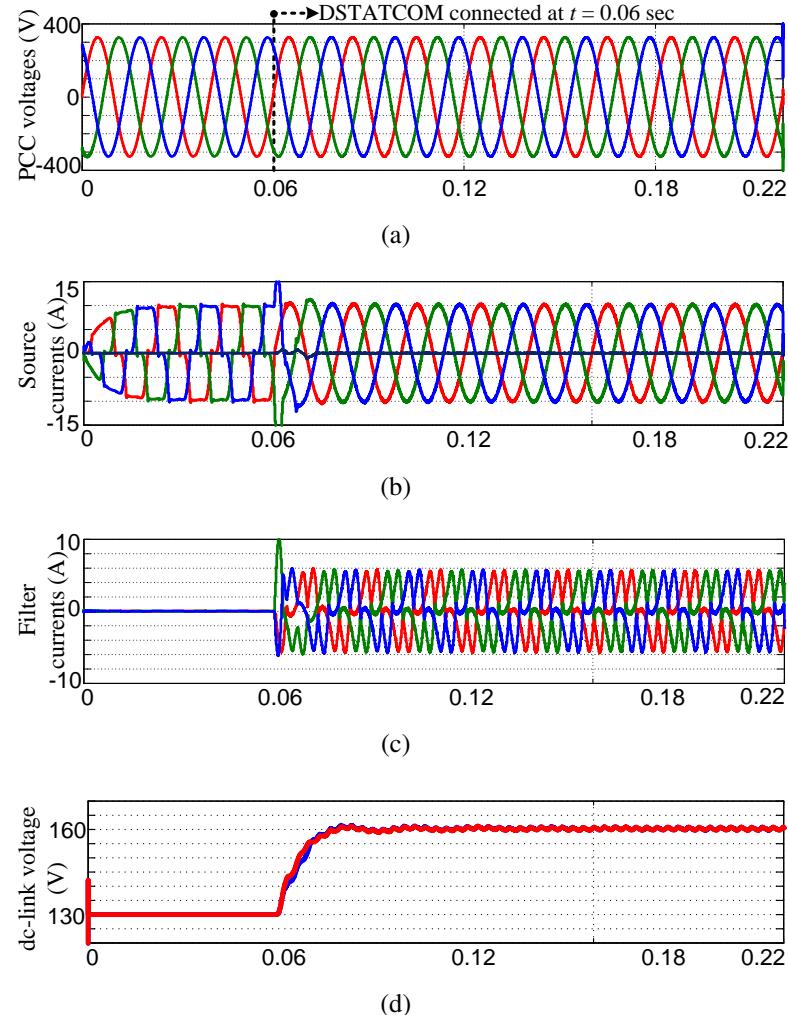

| 5.6  | Simulation results of the proposed method for hybrid DSTATCOM switching at $t = 0.06\ \text{s}$ : (a) PCC voltages ( $v_{pcc}$ ), (b) source currents ( $i_s$ ), (c) filter currents ( $i_f$ ) and (d) dc-link voltages ( $V_{dc1}$ , $V_{dc2}$ ). . . . .                                                                      | 106 |

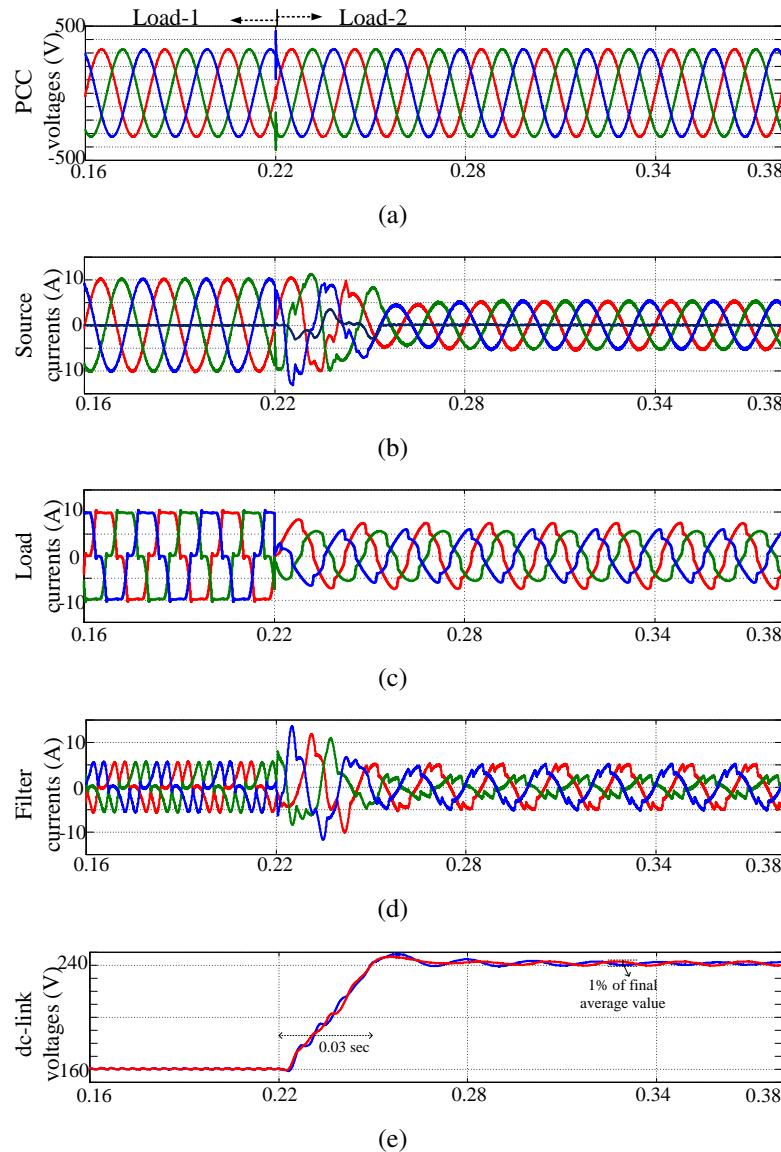

| 5.7  | Simulation results of the proposed method during dynamic load variation at $t=0.22\ \text{s}$ : (a) PCC voltages ( $v_{pcc}$ ), (b) source currents ( $i_s$ ), (c) load currents ( $i_l$ ), (d) filter currents ( $i_f$ ) and (e) dc-link voltages ( $V_{dc1}$ , $V_{dc2}$ ). . . . .                                           | 107 |

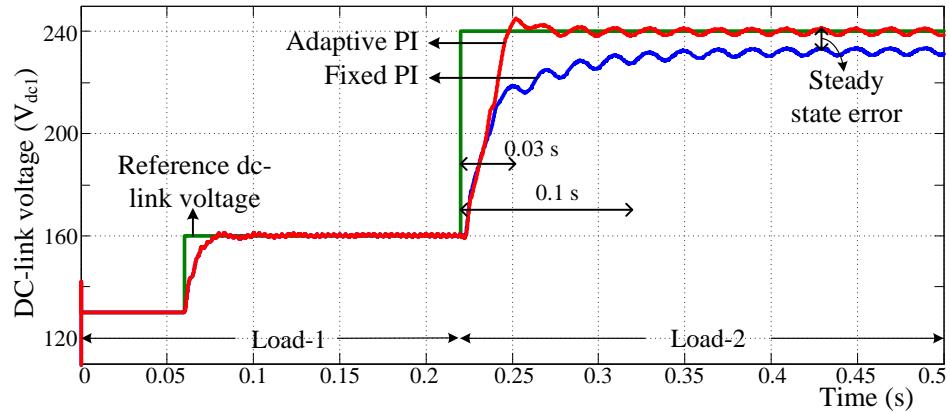

| 5.8  | DC-link voltage dynamics with fixed and adaptive PI controllers . .                                                                                                                                                                                                                                                             | 108 |

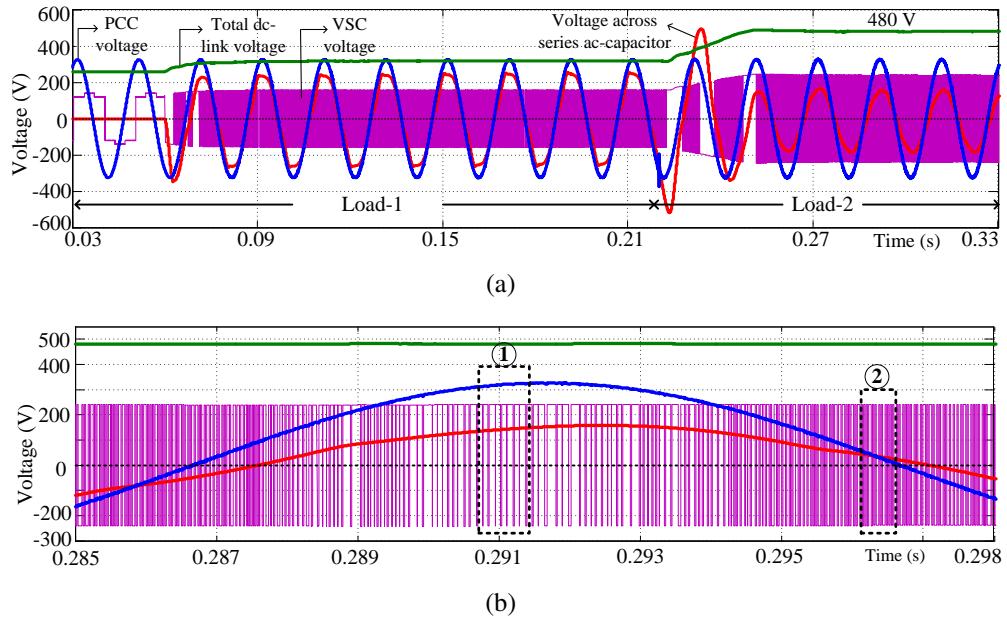

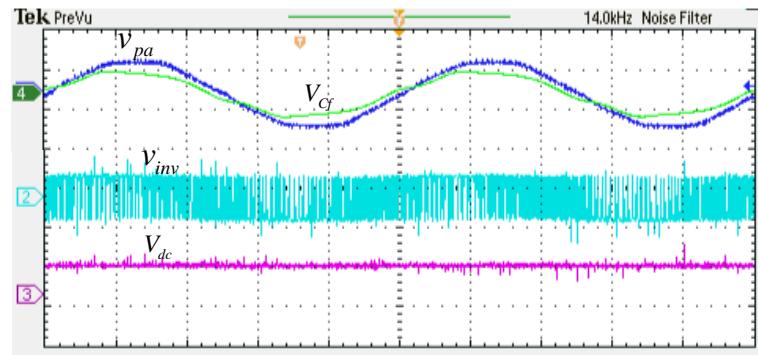

| 5.9  | (a) Phase- <i>b</i> PCC voltage ( $v_{pcc}$ ), VSC voltage ( $v_{inv}$ ), series ac-capacitor voltage ( $v_{cf}$ ) and total dc-link voltage ( $V_{dc1}+V_{dc2}$ ) and (b) zoomed figure of (a) from $t = 0.285\ \text{s}$ to $0.298\ \text{s}$ . . . . .                                                                       | 108 |

| 5.10 | PCC voltages under non-stiff voltage source (a) conventional method and (b) hybrid DSTATCOM with proposed method . . . . .                                                                                                                                                                                                      | 109 |

|      |                                                                                                                                                                                                                 |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

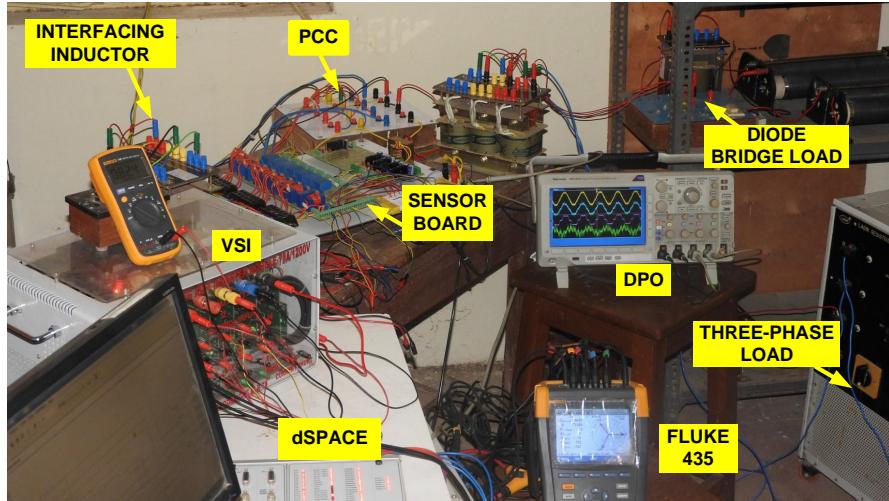

| 5.11 | Experimental set-up photograph                                                                                                                                                                                  | 110 |

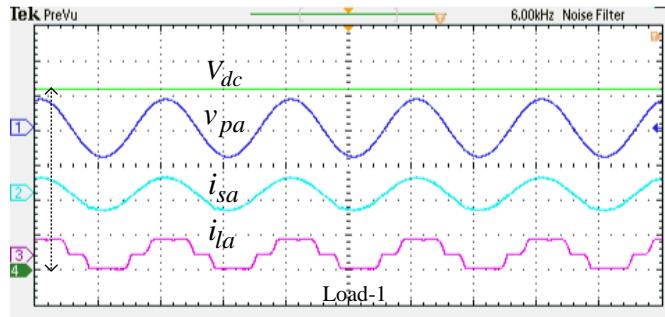

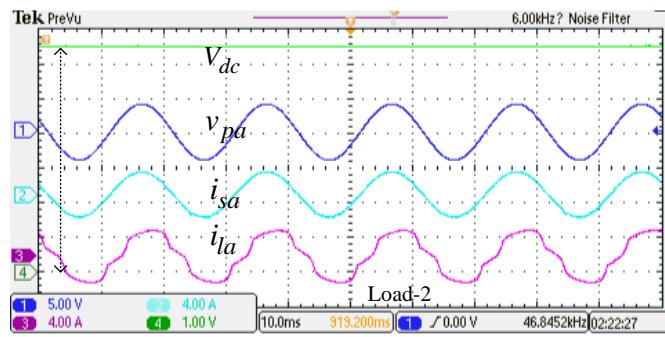

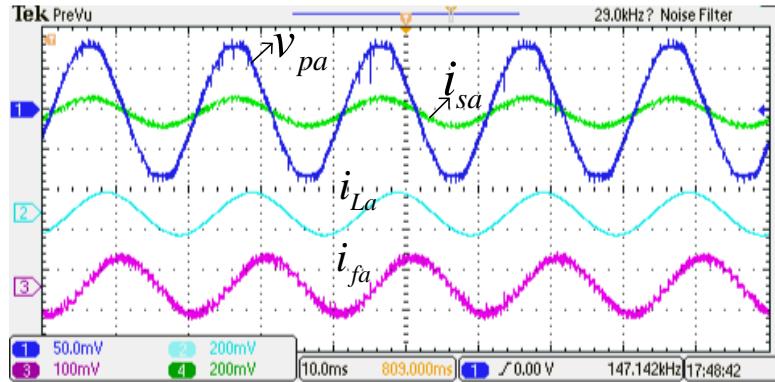

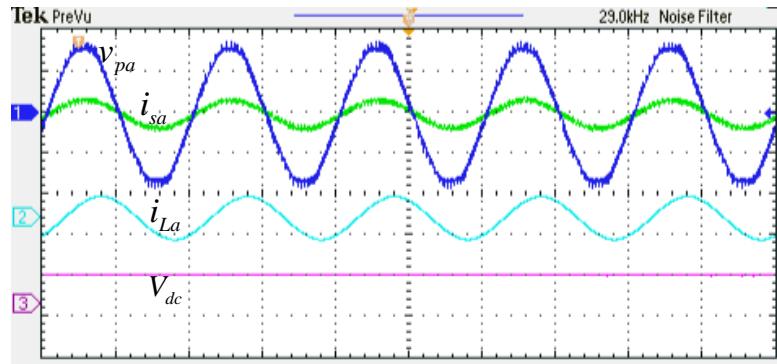

| 5.12 | Compensation performance with hybrid DSTATCOM during load-1 (scale: voltage 50 V/div, current 2 A/div)                                                                                                          | 111 |

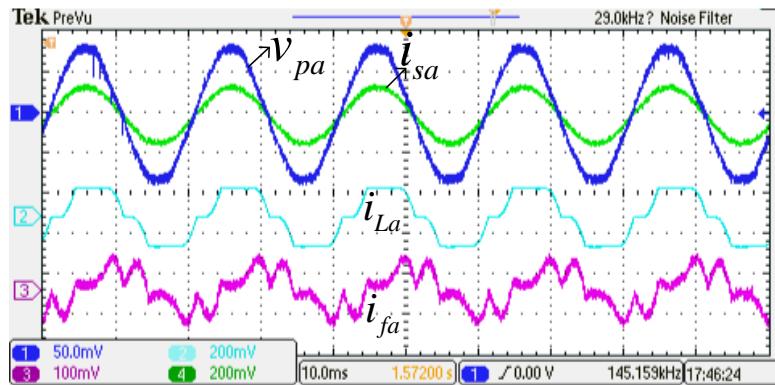

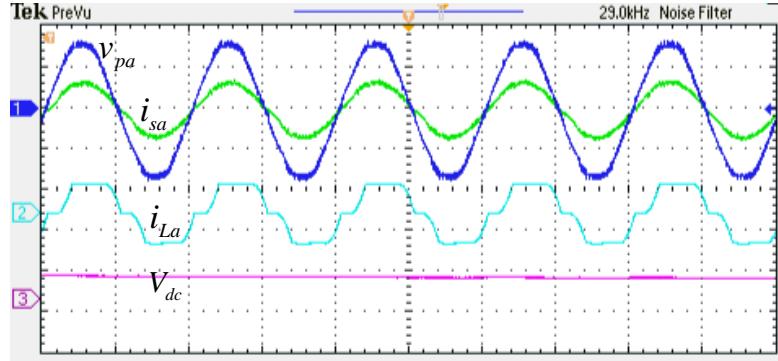

| 5.13 | Compensation performance with hybrid DSTATCOM during load-2 (scale: voltage 50 V/div, current 2 A/div)                                                                                                          | 111 |

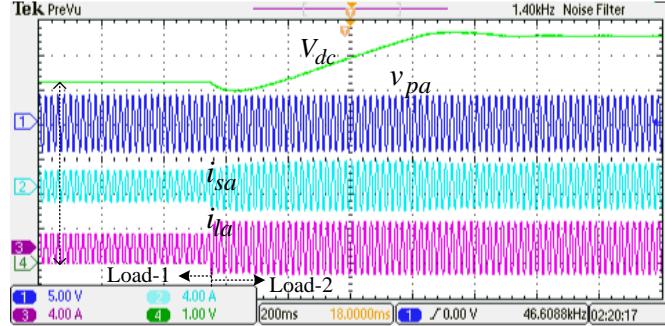

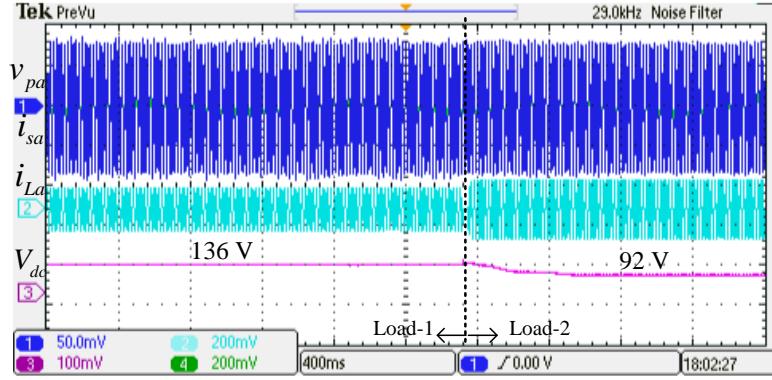

| 5.14 | Dynamics of PCC voltage ( $v_{pa}$ ), source current ( $i_{sa}$ ), load current ( $i_{La}$ ) and dc-link voltage ( $V_{dc}$ ) during compensation                                                               | 112 |

| 5.15 | Zoomed figure of Fig. 5.14 during load-1                                                                                                                                                                        | 112 |

| 5.16 | Zoomed figure of Fig. 5.14 during load-2                                                                                                                                                                        | 112 |

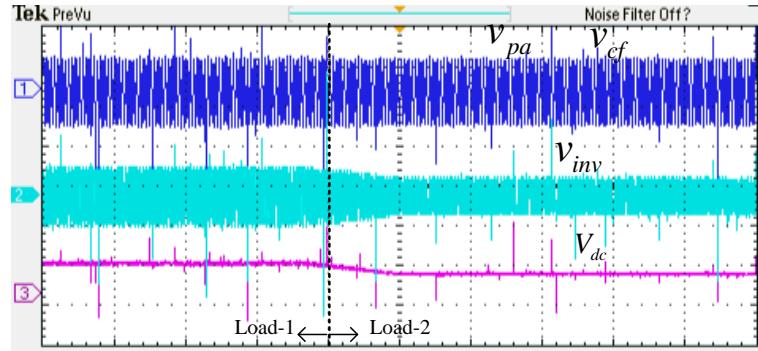

| 5.17 | Dynamics of instantaneous PCC voltage ( $v_{pa}$ ), series ac-capacitor voltage ( $v_{cf}$ ), inverter output voltage ( $v_{inv}$ ) and dc-link voltage ( $V_{dc}$ ) during compensation                        | 113 |

| 5.18 | Zoomed figure of Fig. 5.17 during load-1                                                                                                                                                                        | 113 |

| 5.19 | Zoomed figure of Fig. 5.17 during load-2                                                                                                                                                                        | 113 |

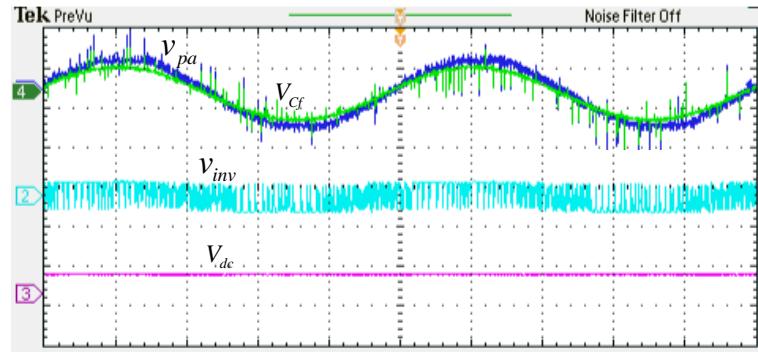

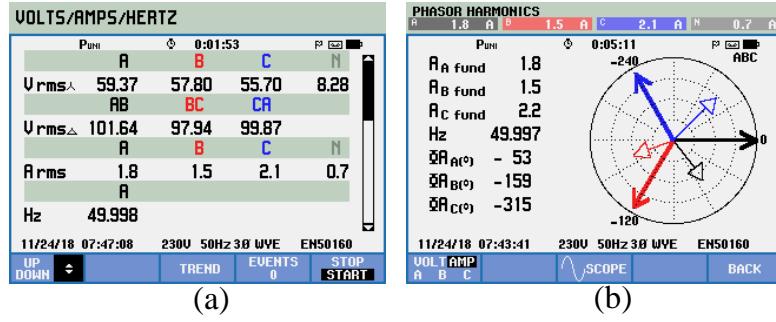

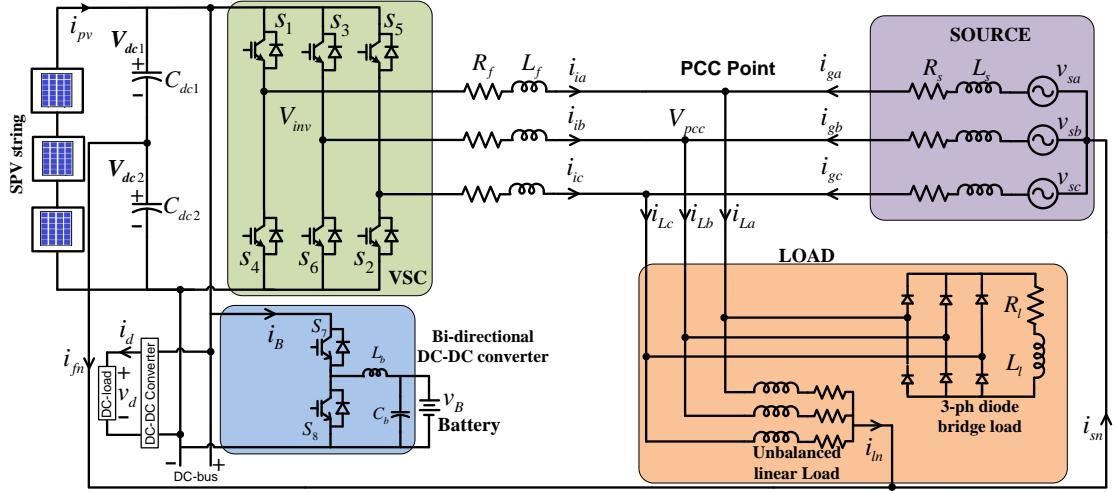

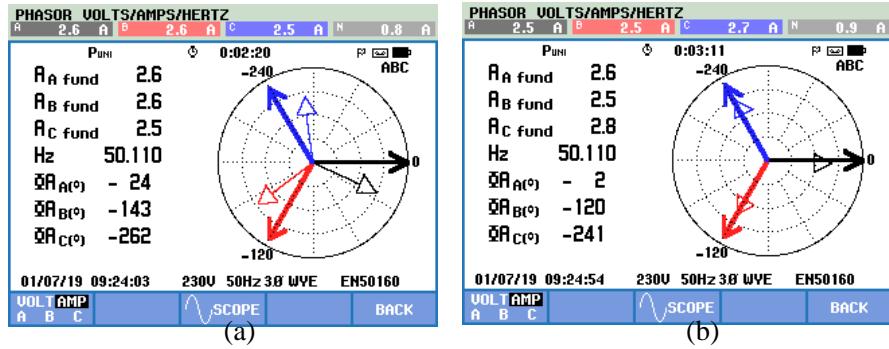

| 5.20 | Before compensation: (a) Magnitude of three-phase PCC voltages ( $V_{rms}$ ), source currents ( $A_{rms}$ ) and supply frequency (Hz) and (b) phasor diagram                                                    | 114 |

| 5.21 | After compensation: (a) Magnitude of three-phase PCC voltages ( $V_{rms}$ ), source currents ( $A_{rms}$ ) and supply frequency (Hz) and (b) phasor diagram                                                     | 114 |

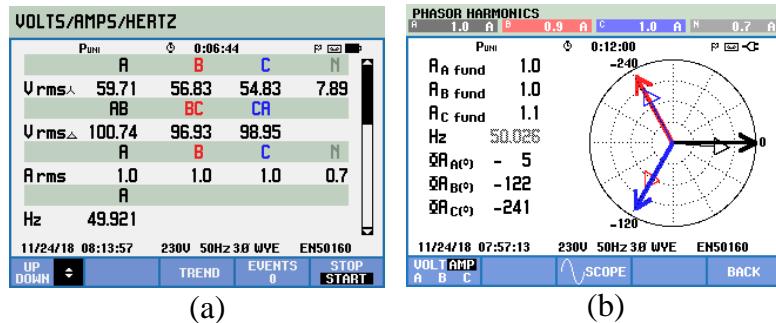

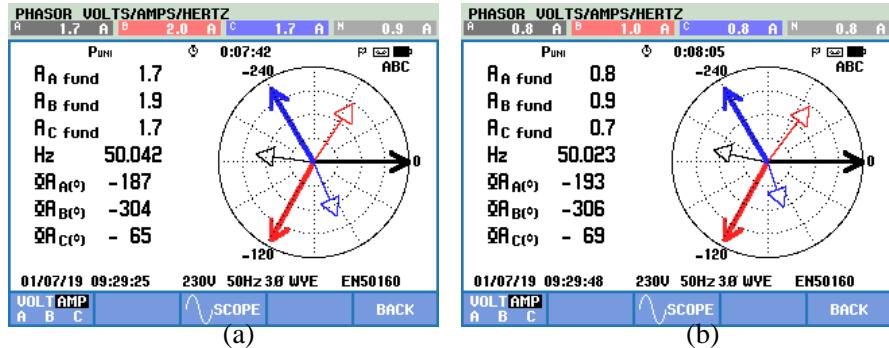

| 5.22 | Before compensation: (a) Magnitude of three-phase PCC voltages ( $V_{rms}$ ), magnitude of source currents ( $A_{rms}$ ) and supply frequency (Hz), (b) source current harmonic spectrum and (c) phasor diagram | 115 |

| 5.23 | After compensation: (a) Magnitude of three-phase PCC voltages ( $V_{rms}$ ), magnitude of source currents ( $A_{rms}$ ) and supply frequency (Hz), (b) source current harmonic spectrum and (c) phasor diagram  | 115 |

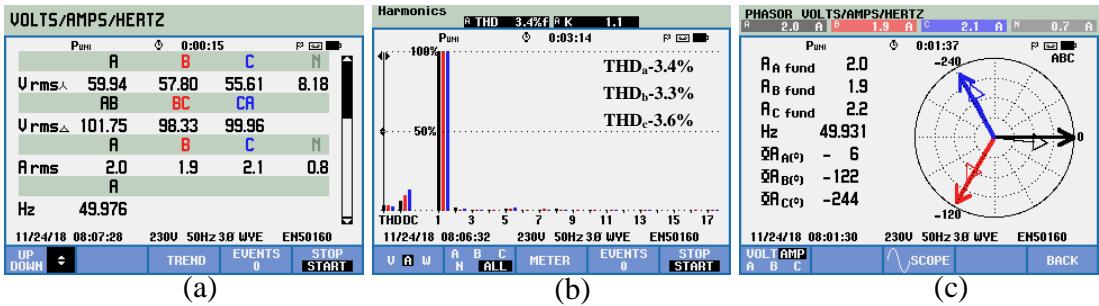

| 6.1  | Grid connected SPV systems: (a) two stage (b) single-stage (c) two-stage with BES and (d) single-stage with BES                                                                                                 | 117 |

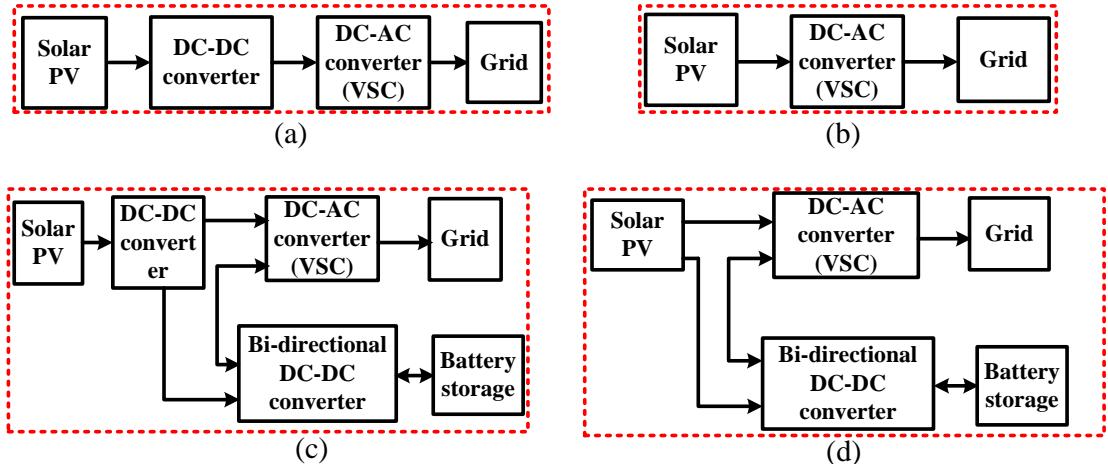

| 6.2  | Grid connected SPV and BES system in a three-phase four-wire distribution system                                                                                                                                | 119 |

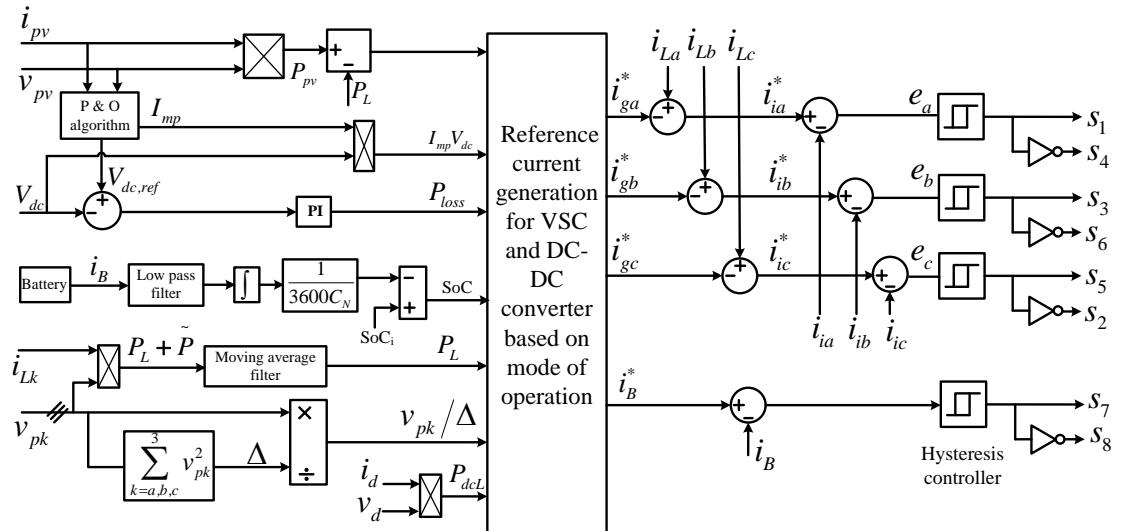

| 6.3  | Overall control algorithm for switching pulses generation in the proposed method                                                                                                                                | 119 |

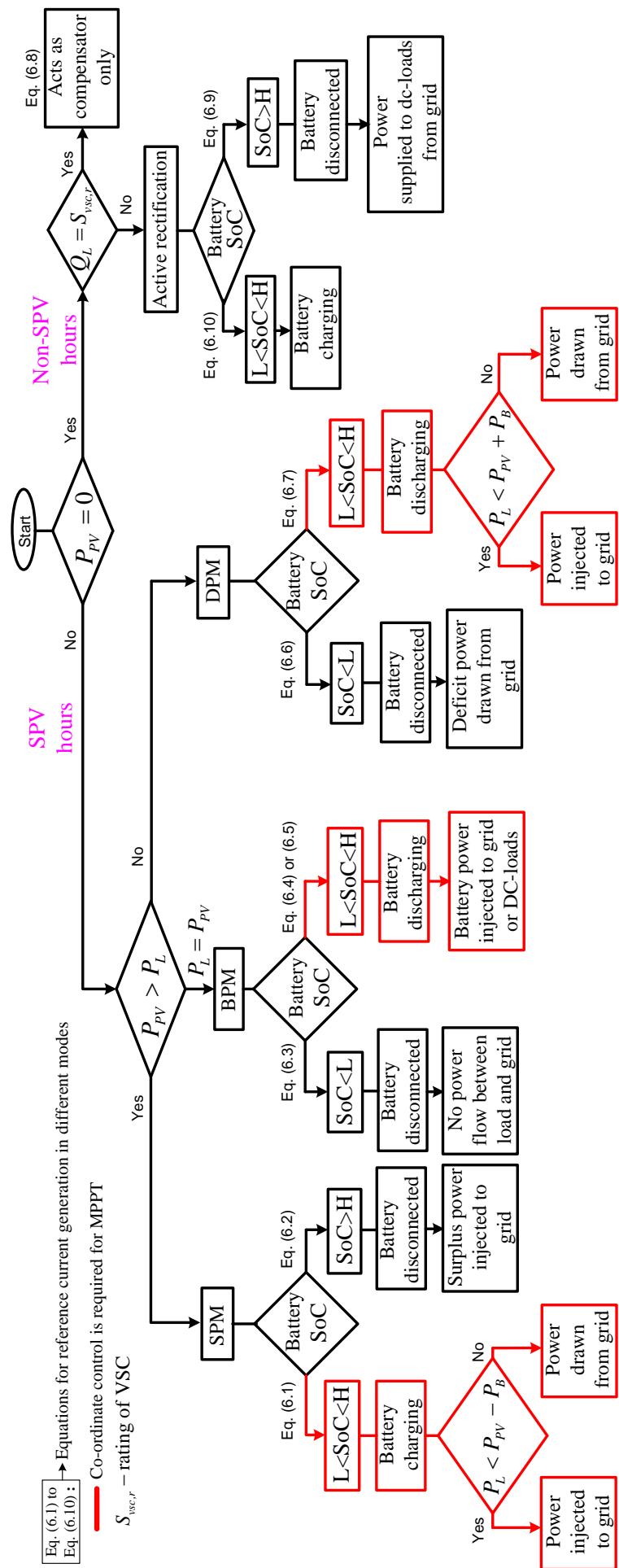

| 6.4  | Flow-chart for different modes of operation in SPV and BES system with the proposed energy management scheme                                                                                                    | 123 |

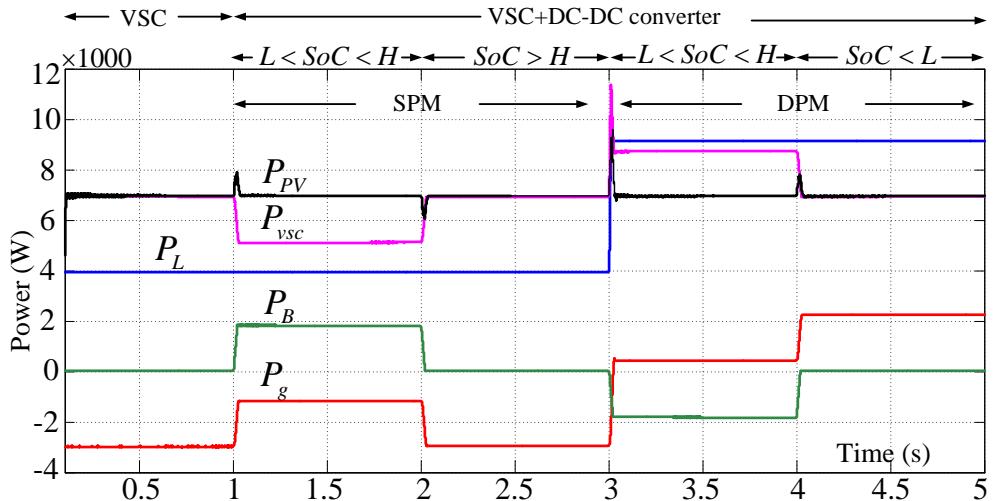

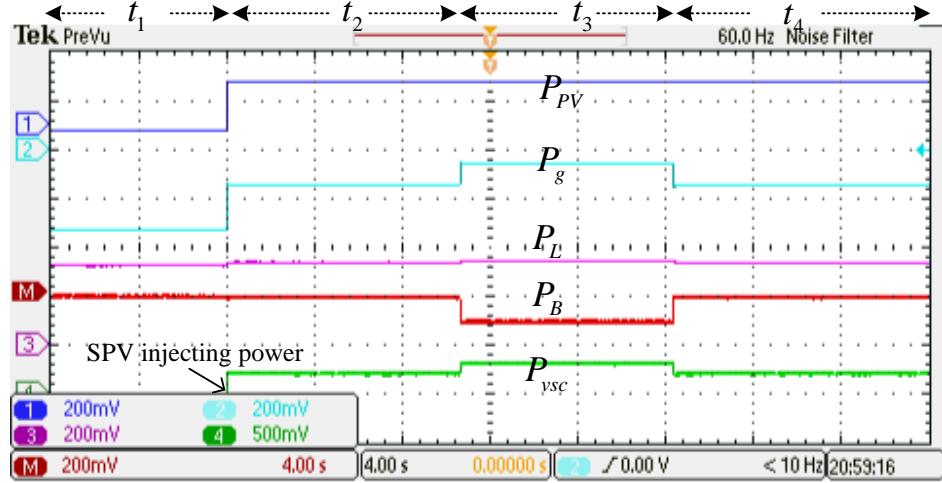

| 6.5  | Dynamics of real powers flow during SPV hours ( $P_{pv}$ : SPV power, $P_{vsc}$ : VSC injecting power, $P_L$ : load real power, $P_B$ : battery power, $P_g$ : grid power)                                      | 126 |

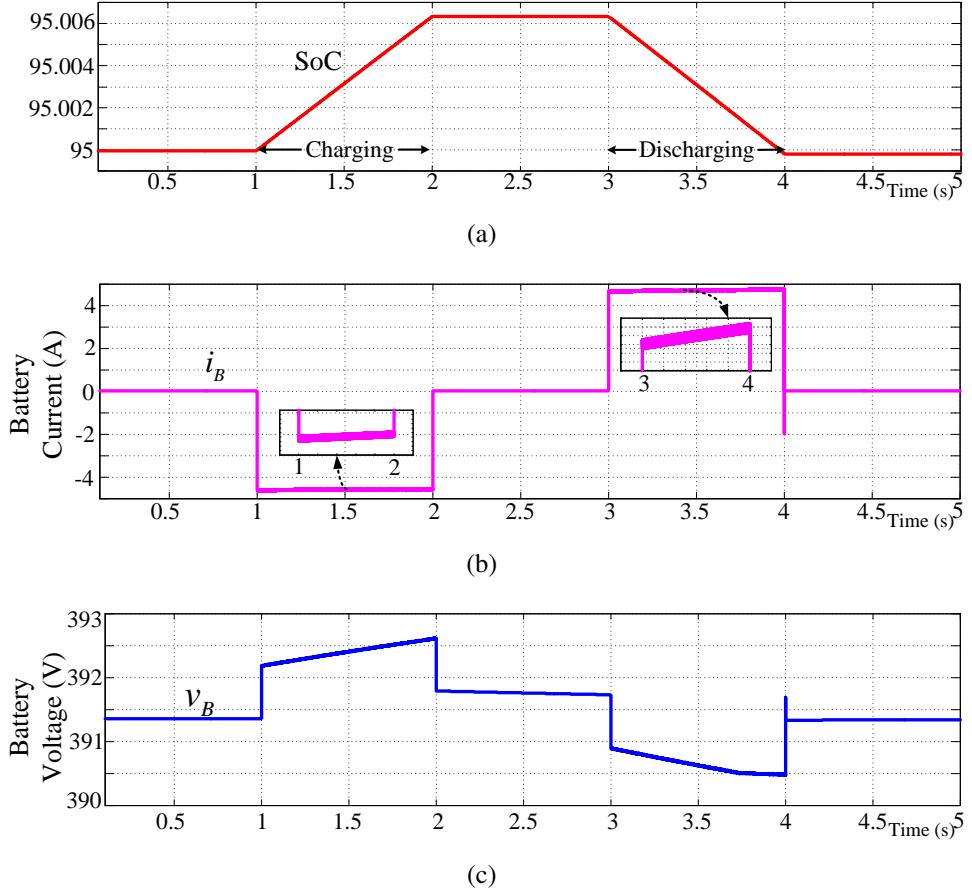

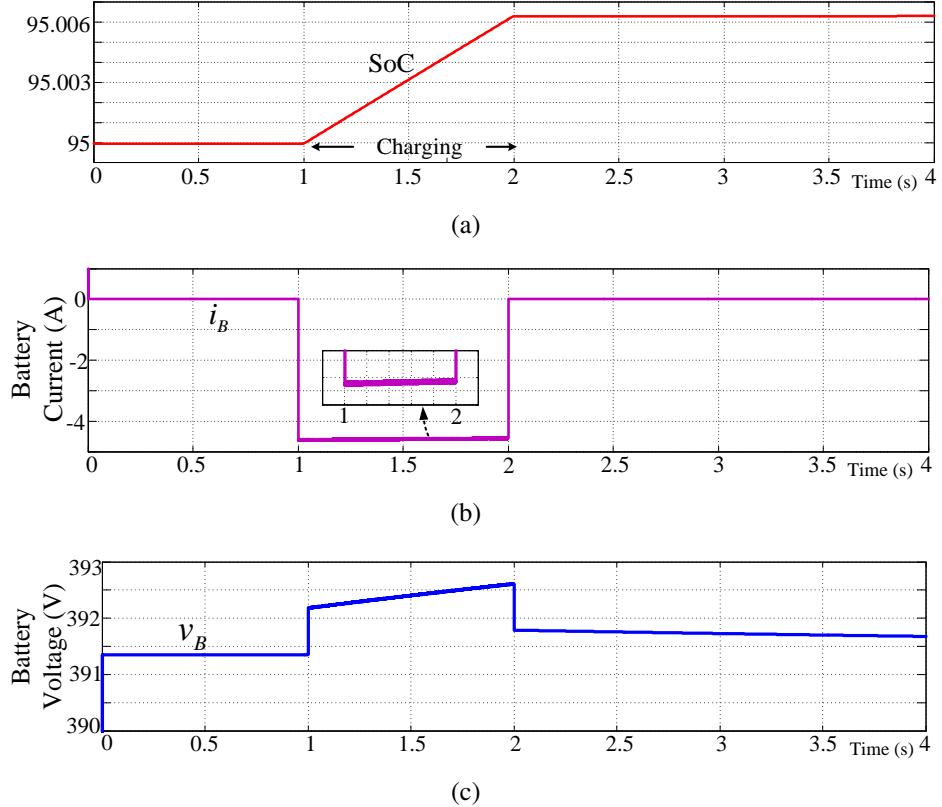

| 6.6  | Dynamics of battery during SPV hours (a) SoC curve (b) battery current ( $i_B$ ) and (c) battery voltage ( $v_B$ )                                                                                              | 127 |

|      |                                                                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

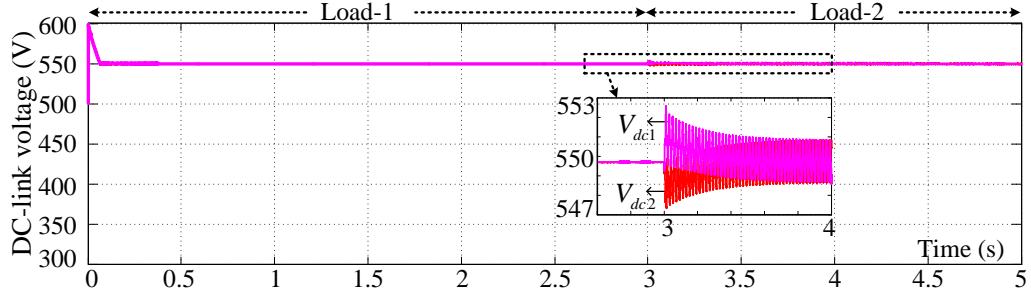

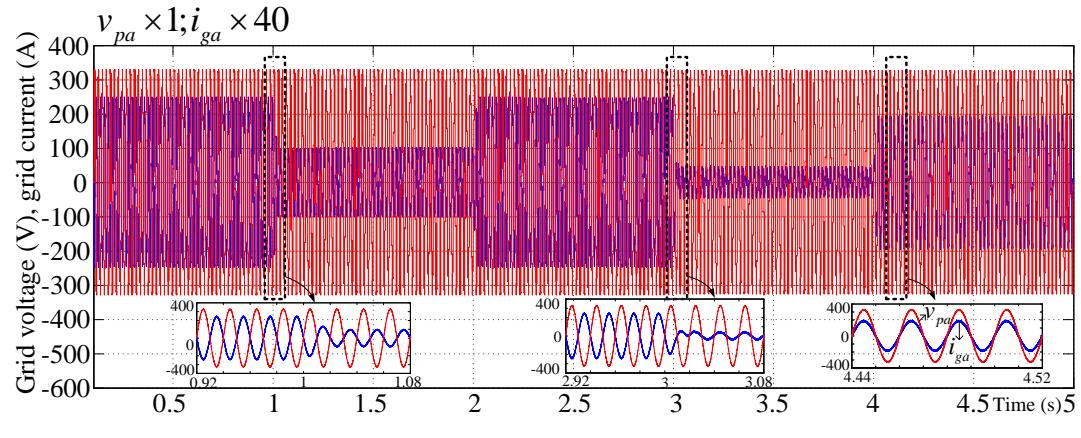

| 6.7  | Dynamics of dc-link voltages ( $V_{dc1}, V_{dc2}$ ) . . . . .                                                                                                                                                                               | 128 |

| 6.8  | (a) Grid voltage ( $v_{pa}$ ) and load current ( $i_{La}$ ) (b) grid voltage ( $v_{pa}$ ) and grid current ( $i_{ga}$ ) . . . . .                                                                                                           | 128 |

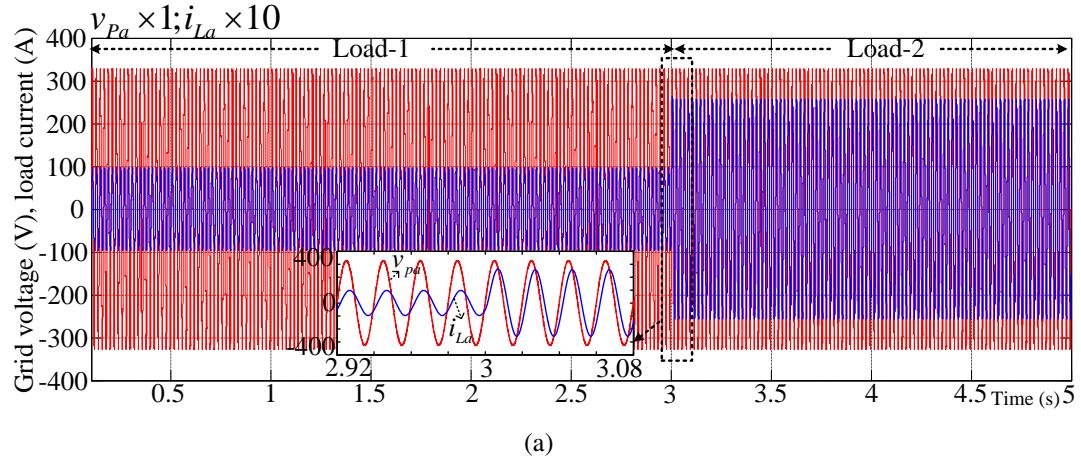

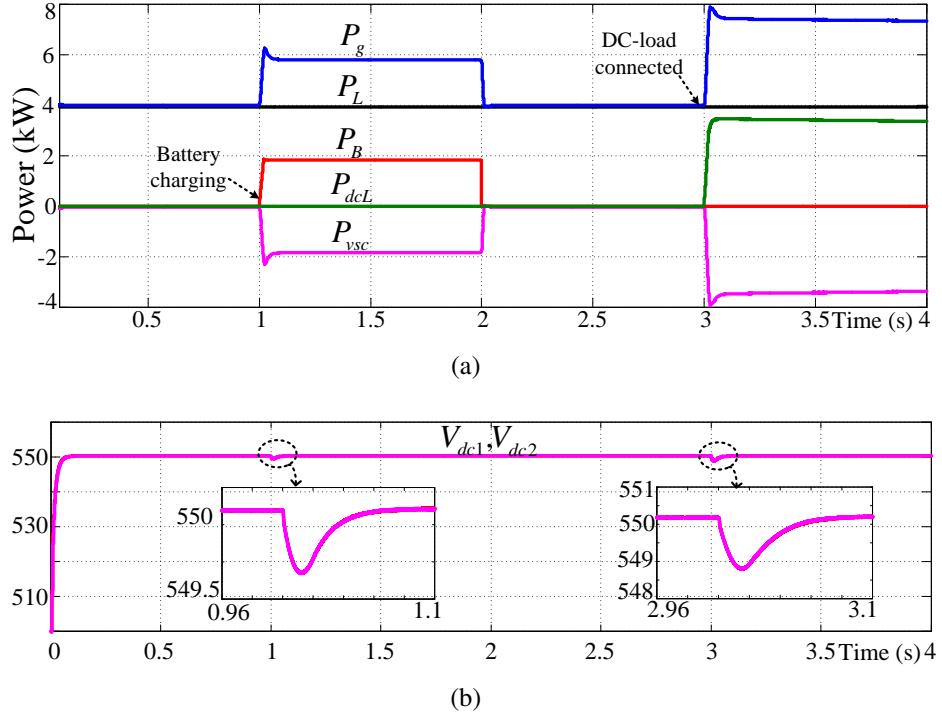

| 6.9  | (a) Dynamic of real powers flow during non-SPV hours ( $P_{dcL}$ : dc load power, $P_{vsc}$ : VSC injecting power, $P_L$ : ac load power, $P_B$ : battery power, $P_g$ : grid power) and (b) dc-link voltages . . . . .                     | 129 |

| 6.10 | Dynamics of battery during non-SPV hours (a) SoC curve (b) battery current ( $i_B$ ) and (c) battery voltage ( $v_B$ ) . . . . .                                                                                                            | 130 |

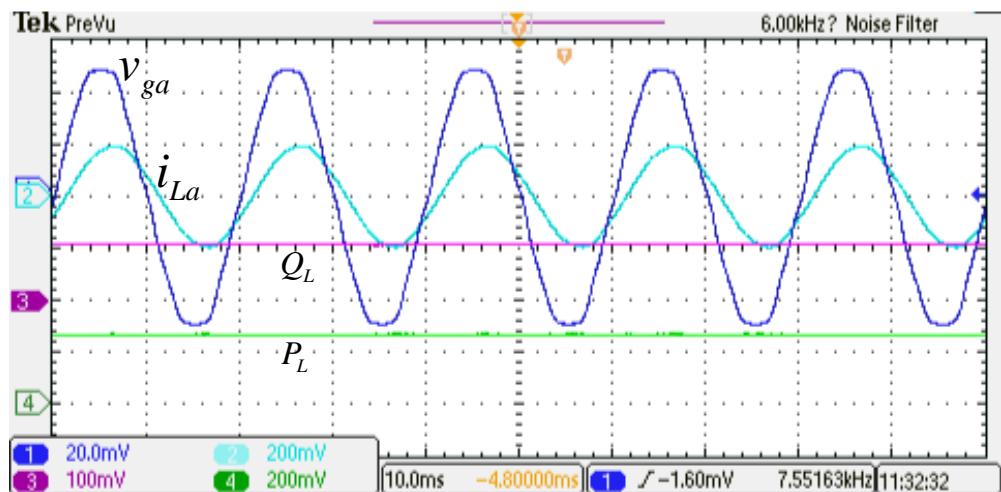

| 6.11 | Experimental waveforms on grid side without real power injection from SPV and without compensation ( $v_{ga}$ 20 V/div, $i_{La}$ 4 A/div, $Q_L$ 100 var/div and $P_L$ 200 W/div) . . . . .                                                  | 132 |

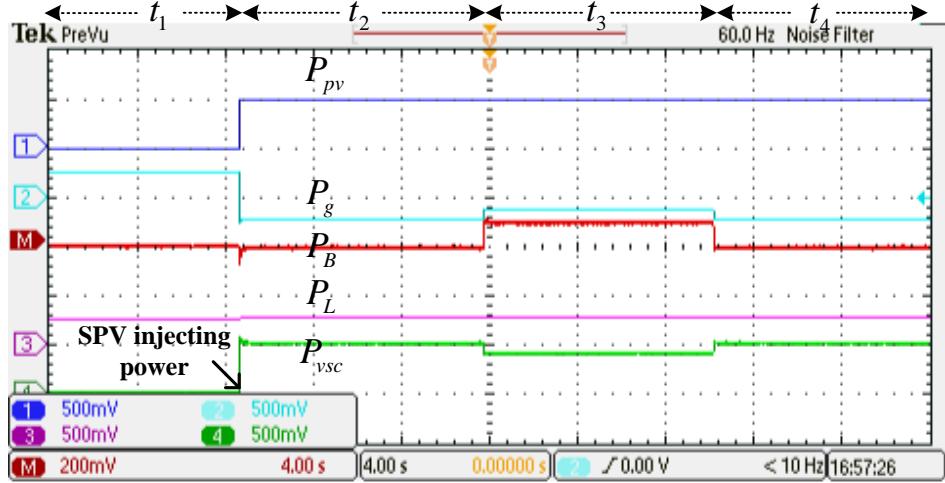

| 6.12 | Dynamics of real powers in the system during SPM operation ( $P_{pv}, P_g, P_L, P_{vsc}$ 500 W/div, $P_B$ 200 W/div) . . . . .                                                                                                              | 133 |

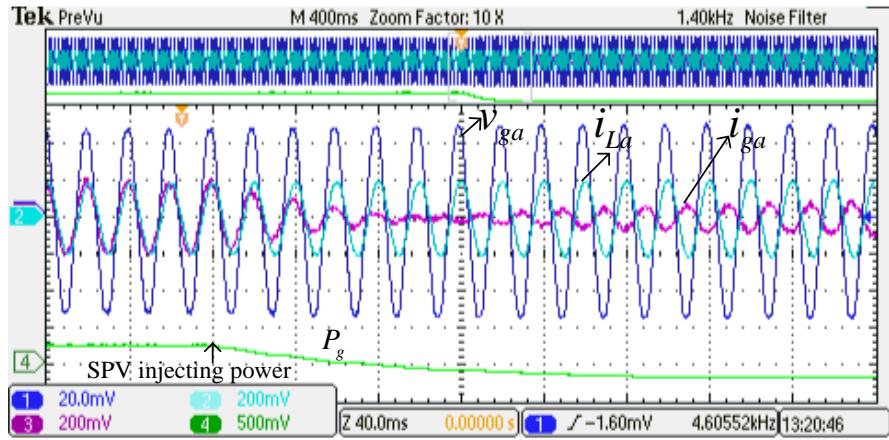

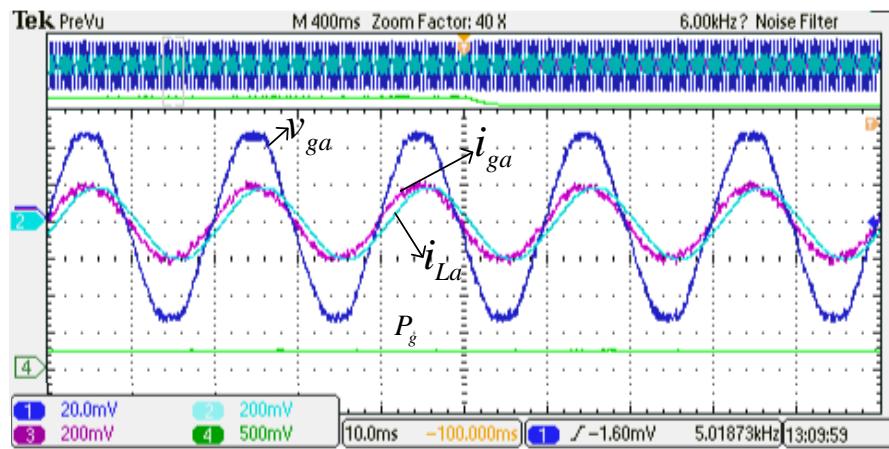

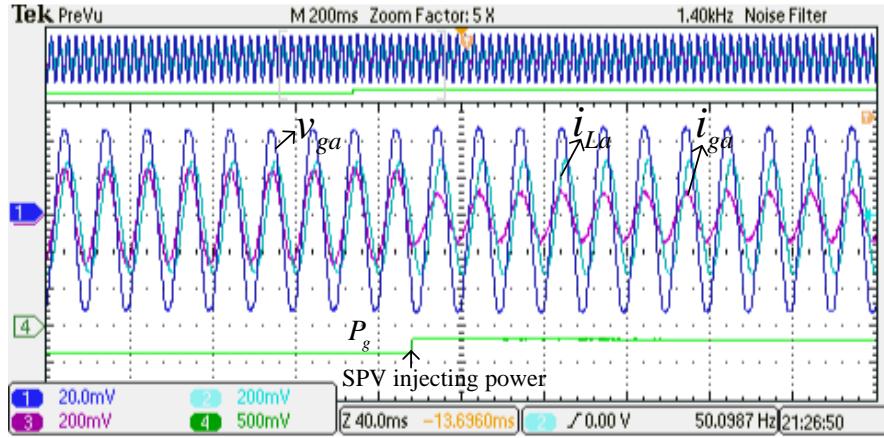

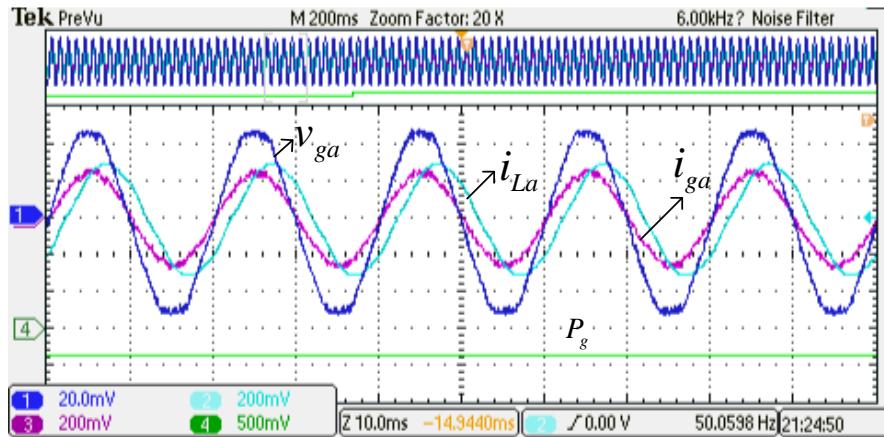

| 6.13 | SPM operation (a) dynamics of system before and after solar power injection, (b)&(c) are zoomed figures of (a) before and after SPV injection, respectively ( $v_{ga}$ 20 V/div, $i_{ga}, i_{La}$ 4 A/div and $P_g$ 500 W/div) .            | 134 |

| 6.14 | Three-phase grid voltages and grid currents phasors without SPV injecting power for load-1 (a) before compensation and (b) after compensation . . . . .                                                                                     | 135 |

| 6.15 | Three-phase grid voltages and grid currents phasors with SPV power injection during SPM operation (a) without charging or discharging of battery and (b) with charging battery during the time period of $t_3$ shown in Fig. 6.12 . . . . . | 135 |

| 6.16 | Dynamic of real powers in the system during DPM operation ( $P_{pv}, P_g, P_B, P_L$ 200 W/div, $P_{vsc}$ 500 W/div) . . . . .                                                                                                               | 136 |

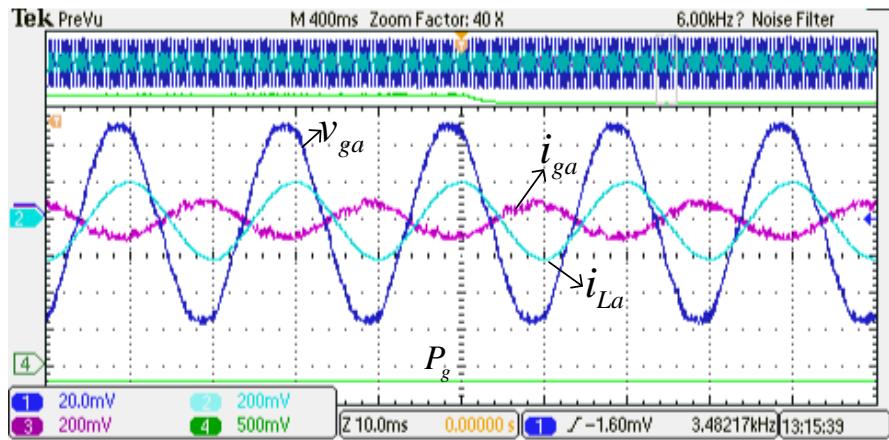

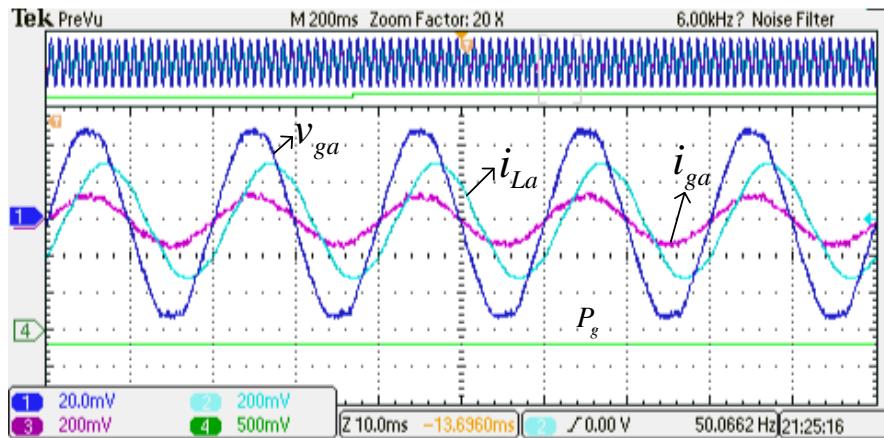

| 6.17 | DPM operation (a) dynamics of system before and after solar power injection, (b)&(c) are zoomed figures of (a) before and after SPV power injection, respectively ( $v_{ga}$ 20 V/div, $i_{ga}, i_{La}$ 4 A/div and $P_g$ 500 W/div)        | 137 |

| 6.18 | Three-phase grid voltage and grid current phasors without SPV injecting power for load-2 (a) before compensation and (b) after compensation . . . . .                                                                                       | 138 |

| 6.19 | Three-phase grid voltages and grid currents phasors with SPV power injection during DPM operation (a) without charging or discharging of battery and (b) with discharging battery during periods of $t_3$ shown in Fig. 6.16 . . . . .      | 138 |

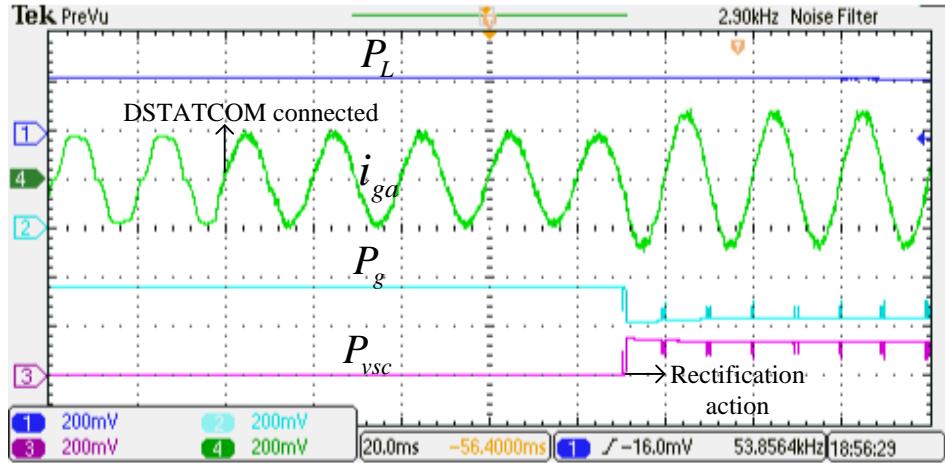

| 6.20 | Dynamics of real power in the system during non-SPV hours ( $P_L, P_g, P_{vsc}$ 200 W/div, $i_{ga}$ 4 A/div) . . . . .                                                                                                                      | 139 |

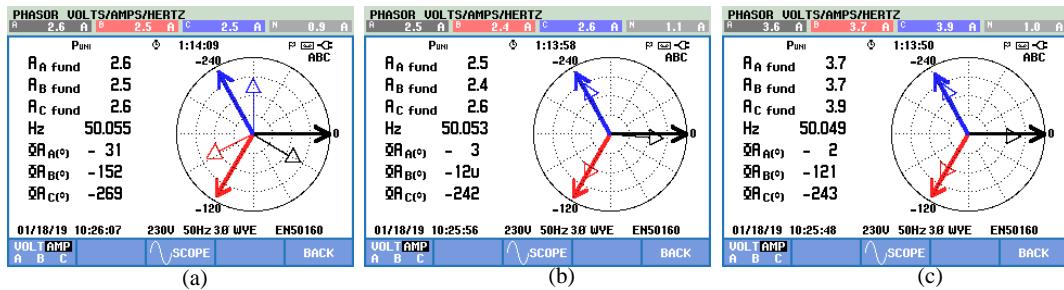

| 6.21 | Three-phase grid voltages and grid currents phasors (a) without compensation (b) with compensation and (c) with compensation plus rectification (i.e., during periods of $t_1, t_2$ and $t_3$ shown in Fig. 6.20, respectively) . . . . .   | 139 |

|                                                                                                                                     |     |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

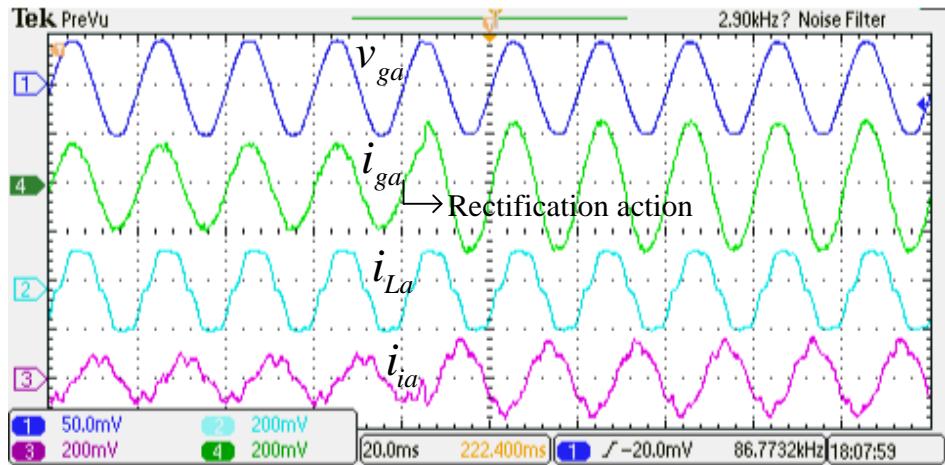

| 6.22 Before and after rectification action during non-SPV hours ( $v_{ga}$ 50 V/div,<br>$i_{ga}, i_{La}, i_{ia}$ 4 A/div) . . . . . | 140 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

## ABBREVIATIONS

|                 |                                                   |

|-----------------|---------------------------------------------------|

| <b>AC</b>       | Alternating Current                               |

| <b>APF</b>      | Active Power Filter                               |

| <b>CPD</b>      | Custom Power Device                               |

| <b>DC</b>       | Direct Current                                    |

| <b>DSTATCOM</b> | Distribution Static Compensator                   |

| <b>DVR</b>      | Dynamic Voltage Restorer                          |

| <b>IEEE</b>     | Institute of Electrical and Electronics Engineers |

| <b>IEC</b>      | International Electrotechnical Commission         |

| <b>IGBT</b>     | Insulated Gate Bipolar Transistor                 |

| <b>PCC</b>      | Point of Common Coupling                          |

| <b>PI</b>       | Proportional Integral                             |

| <b>PQ</b>       | Power Quality                                     |

| <b>PWM</b>      | Pulse Width Modulation                            |

| <b>rms</b>      | root mean square                                  |

| <b>THD</b>      | Total Harmonic Distortion                         |

| <b>TDD</b>      | Total Demand Distortion                           |

| <b>VA</b>       | Volt-Ampere                                       |

| <b>VSC</b>      | Voltage Source Converter                          |

| <b>CSC</b>      | Current Source Converter                          |

| <b>CCM</b>      | Current Control Mode                              |

| <b>VCM</b>      | Voltage Control Mode                              |

| <b>SOGI</b>     | Second Order Generalized Integrator               |

| <b>HC</b>       | Hysteresis Controller                             |

| <b>UCC</b>      | Unit Capacitor Constant                           |

| <b>ISC</b>      | Instantaneous Symmetrical Component               |

| <b>IRT</b>      | Instantaneous Reactive Power                      |

| <b>SRF</b>      | Synchronous Reference Frame                       |

| <b>3P4W</b>     | Three-phase Four-wire                             |

|                |                              |

|----------------|------------------------------|

| <b>3P3W</b>    | Three-phase Three-wire       |

| <b>SPV</b>     | Solar Photo-voltaic          |

| <b>MPPT</b>    | Maximum Power Point Tracking |

| <b>BES</b>     | Battery Energy Storage       |

| <b>SoC</b>     | Stage of Charge              |

| <b>P&amp;O</b> | Perturb and Observe          |

| <b>PLL</b>     | Phase Locked Loop            |

## NOTATIONS

|                        |                                           |

|------------------------|-------------------------------------------|

| $v_s$                  | Instantaneous source voltage              |

| $i_s$                  | Instantaneous source current              |

| $i_l$                  | Instantaneous load current                |

| $i_f$                  | Instantaneous filter or DSTATCOM current  |

| $i_{ln}$               | Instantaneous load neutral current        |

| $i_{sn}$               | Instantaneous source side neutral current |

| $v_p$                  | Instantaneous voltage at PCC              |

| $R_s$                  | Equivalent resistance of feeder           |

| $L_s$                  | Equivalent inductance of feeder           |

| $L_f$                  | Interfacing inductance                    |

| $C_{dc}$               | DC-link capacitance                       |

| $P_s$                  | Source real power                         |

| $Q_s$                  | Source reactive power                     |

| $P_l$                  | Load real power                           |

| $Q_l$                  | Load reactive power                       |

| $P_f$                  | DSTATCOM real power                       |

| $Q_f$                  | DSTATCOM reactive power                   |

| $I_s$                  | rms source current                        |

| $I_l$                  | rms load current                          |

| $I_f$                  | rms filter current                        |

| $m_a$                  | Amplitude modulation index                |

| $Q_{f,max}$            | Maximum DSTATCOM reactive power           |

| $I_{f,max}$            | Maximum filter current                    |

| $Q_f^*$                | Reference DSTATCOM reactive power         |

| $V_{dc}^*, V_{dc,ref}$ | Reference dc-link voltage                 |

| $I_f^*$                | Reference rms filter current              |

| $f_{sw}$               | Switching frequency                       |

| $E_{sw}$               | Energy dissipation in switch              |

|            |                                                      |

|------------|------------------------------------------------------|

| $P_{sw}$   | Switching losses                                     |

| $T_j$      | Junction temperature of switch                       |

| $I_{f,n}$  | Nominal rms filter current                           |

| $V_{dc,n}$ | Nominal dc-link voltage                              |

| $T_{j,n}$  | Nominal junction temperature of switch               |

| $k_i$      | Current dependency factor of IGBT                    |

| $k_v$      | Voltage dependency factor of IGBT                    |

| $TC_{sw}$  | Temperature co-efficient of switching losses         |

| $r_d$      | Damping resistance                                   |

| $C_r$      | Resonance capacitance                                |

| $i_{cr}$   | Instantaneous current through resonance capacitor    |

| $C_f$      | Series ac-capacitance                                |

| $L_{fi}$   | Converter side inductance                            |

| $L_{fg}$   | Grid side inductance                                 |

| $h$        | Hysteresis band                                      |

| $P_{lavg}$ | Average real or active power of load                 |

| $i_p$      | Active current component of load                     |

| $i_q$      | Reactive current component of load                   |

| $v_{inv}$  | Instantaneous inverter or converter ac side voltage  |

| $f$        | Fundamental supply frequency                         |

| $\omega$   | Fundamental frequency of the supply voltage in rad/s |

| $\theta$   | Angle between voltage and current                    |

# CHAPTER 1

## INTRODUCTION

This chapter introduces the research work. It starts with a brief background to foremost power quality problems in distribution system. Then, the solutions to the power quality problems have been discussed, through which DSTATCOM is selected as a compensator in distribution system. Next, motivations, objectives, and organization of thesis are explained.

### 1.1 General Overview

In alternating current (AC) power system, the term Power Quality (PQ) is used to estimate and maintain the quality of power at the level of generation, transmission, distribution, and utilization. The quality of power is quantified in terms of voltage, current and frequency deviation of the supply system. Typically, voltage related power quality problems at the point of common coupling (PCC) consist of voltage sag, swell, harmonics, surge, fluctuations, notches, voltage unbalance, glitches, spikes, flickers, outages, and so on, while current related PQ problems are poor power factor, current unbalance, an excessive neutral current due to unbalance, and harmonic currents generated by non-linear loads. Some of the reasons for power quality problems in AC power system are summarized below.

- Operation of non-linear loads such as adjustable speed drives (ASDs), uninterrupted power supplies (UPSs), switched mode power supplies, arc furnaces, high efficiency lighting.

- Natural reasons include flashover, lightning phenomena, fault conditions, and failure of electrical equipment (e.g. electrical cables and transformers).

- Unequal distribution of all single-phase loads among the three-phases of distribution system.

- Energization of large capacitor banks and transformers.

- Frequent switching or start and stop of large loads such as electric motors and oscillating loads.

Due to power quality issues, the following problems occur in AC distribution power system:

- Increased losses in the distribution system

- Excessive current due to resonance

- Negative sequence currents in generators and motors

- Failure of capacitor banks

- Overheating of cables and transformers

- Interference with communication systems

- Relay and breaker malfunctions due to signal interference, false metering, interferences with the motor controllers and digital controllers

- Dielectric breakdown, noise and vibrations.

The severity of PQ problems is much more at the utilization level, therefore the study of PQ becomes an important area in electrical engineering, especially in distribution system. These power quality problems become more serious with the use of solid-state devices, which cannot be dispensed due to the benefits of size reduction, ease of control, and other reduced maintenance requirements in modern electric equipment. However, the adverse effects of power quality issues in terms of cost is very high in distribution system [1]–[3]. Therefore, it has created a great challenge to both manufacturers and the electric utilities. The manufacturers must develop electric equipment, which must be immune to or override the power quality disturbances and the utilities must supply good quality power to consumers for satisfactory operation of their equipment. For completeness, the current related power quality problems, such as reactive power burden, current harmonics and excessive neutral current are briefly discussed below.

### 1.1.1 High reactive power demand

In distribution system, some loads demand high reactive power for successful operation. When enough reactive power is not available in the system, it is not possible to transfer the real power demanded by the loads through feeder lines [4]. Some of the loads, which demand high reactive power in distribution system are:

- Phase-controlled rectifiers

- Motors

- Transformers, tap-changing transformers

- Choke inductors of loads

Due to high reactive power demand, the following problems are associated in the distribution system.

- Losses will be more in the distribution system

- Low efficiency owing to more losses

- Low power factor and poor voltage regulation

### 1.1.2 Effect of current harmonics

Harmonics are basically the additional frequency components present in the fundamental voltage or current and which are integral multiples of the fundamental frequency. Harmonics are produced by operating non-linear loads in the distribution system. Some sources of harmonics are rectifiers, cycloconverters, ac voltage controllers, adjustable speed drives, soft starters, electronic ballast for discharge lamps, switched-mode power supplies and HVDC transmission. The harmonic distortions change the sinusoidal nature of the ac current, and results in disruption in the ac distribution power system. It causes interference with communication system, damages capacitors, and causes malfunction of other electrical and electronic equipments connected to the same system [5], [6]. The maximum acceptable values of harmonic contamination are specified in Institute of Electrical and Electronics Engineers (IEEE) standard in terms of total harmonic distortion (THD) and Total Demand Distortion (TDD).

### 1.1.3 Effect of excess neutral current

In many residential and office buildings, power is supplied from a three-phase four-wire (3P4W) distribution system [7]. The unequal distribution of single-phase loads among three-phases create unbalance in the system and results of excessive neutral current flow. The equipment, which produce neutral currents are switched-mode power supplies, such as PCs, printers, photocopiers, and any triplets generator [8]. Neutral current seriously affects the neutral conductor temperature and overloading of distribution feeders and transformers. Some temporary solutions for handling excess neutral current are, 1) over sizing the neutral conductor, 2) derating of distribution feeders and transformers and 3) providing separate neutral conductor.

Due to the above discussed power quality problems, there are distortions and deviations in the various electrical quantities, such as voltage, current and power factor. To limit the level of deviation and distortion, several standards have been developed, recommended, and enforced depending upon the evolution of technology to maintain and quantify the level of power quality.

## 1.2 Power Quality Standards

Power quality problems affect customers in many ways, such as equipment failure, economic penalty due to power loss, interruption in the process, malfunction of equipment and loss of production. In view of these facts, various terms and definitions are used to quantify the power quality problems in terms of different performance indices. Moreover, various organizations at national and international levels have been working closely with engineers, equipment manufacturers, and research organizations to come up with standards governing guide lines, recommended practices, and harmonic limits [6]. The primary objective of the standards is to provide a common ground for all the parties involved to work together to ensure compatibility between the end-user equipments and the supply system. The most commonly used harmonic standards are IEEE-519-1992 [9], International Electrotechnical Commission standard IEC-61000 [10] and European standard EN-50160. IEEE-519-1992 standard limits the amount of current harmonics injected by a user at the Point of Common Coupling (PCC) [9]. For example, the IEEE-519-1992 standard recommends a limit of 5% Total Harmonic Distortion

(THD) in the current at the PCC in a weak system.

## 1.3 Solution for Power Quality Problems

Electricity consumers are affected in many ways due to low quality power. This causes damage to the equipment or appliances connected to the system, loss of production and sometimes may also be detrimental to human health. Therefore, it is very important to maintain good power quality in the distribution system. Researchers all over the world have worked for decades and provided solutions for power quality problems. In earlier, passive filters are used as solution for PQ problems in distribution system. But, in general, the operating load in distribution system changes frequently, during which passive elements do not respond correctly. In recent years, due to easy control and reduced cost of semiconductor devices, power electronic converters are an affordable solution for power quality problems.

### 1.3.1 Passive power filters

Passive power filters consist of inductors, capacitors, and resistors, and they are classified into passive tuned filters and high pass filters. The power quality problems can be resolved to some extent by using passive power filters [11]. Depending on the type of connection with load, passive power filters are categorized as shunt and series passive filters. In case of shunt passive filter, the filter is connected in parallel with the load, which is traditionally used to bypass current harmonics in distribution systems [12]. Shunt passive filters provide low impedance path to divert current harmonics to ground such that, it is not allowed into the distribution system. The disadvantages of using passive filter are that they are tuned for a particular harmonic elimination, bulky in size and have resonance problem [12], [13]. There are different types of shunt passive filters available [14], but the most commonly used passive tuned filters are: single-tuned and double tuned, while high pass filters are: first order, second order and third order filter. The tuned filters and high pass filters are shown in Fig. 1.1 and Fig. 1.2, respectively.

In earlier, passive filters have been used in power system, because of the following advantages [12]:

Fig. 1.1 Passive tuned filters: (a) single-tuned and (b) double tuned

Fig. 1.2 Passive high pass filters: (a) first order (b) second order and (c) third order

1. Simple to implement and almost maintenance free.

2. High efficiency due to absence of switching and conduction losses.

3. Supporting voltage on critical buses and reactive power compensation.

However, passive filters have many disadvantages, which are mentioned below [14]:

1. The size of the passive filter is bulky and it is also expensive.

2. Passive filters do not support dynamic condition in the power system.

3. The resonance between system and passive filter components may damage the equipment because of amplification of current or voltage at resonance condition.

The disadvantages with the passive filters as compensator has encouraged the development of power electronic devices based compensator, which is commonly referred to as Active Power Filters (APF) [14]–[17].

### 1.3.2 Active power filters

The active power filters are classified into series active power filters and shunt active power filters with respect to the circuit configuration [14]–[16]. Out of these two configurations, shunt active power filter is used for current related power quality problems and its circuit is shown in Fig. 1.3. Still, the Active Power Filter (APF) technology has been under research for providing solutions for power quality problems, such as reactive power compensation, mitigation of harmonics, and neutral current minimization [14]–[17]. In starting stages, the APFs are fabricated by using Bipolar Junction Transistor (BJTs), thyristors, power MOSFETs, Gate Turn-off thyristors (GTOs) and Static Induction Thyristors (SITs). Later, with introduction of Insulated Gate Bipolar Transistors (IGBTs), the APF technology got a real boom for many applications. An important factor for promoting APF technology is the advent of solid state devices of fast self-commutating nature.

Fig. 1.3 Shunt active power filter in three-phase three-wire distribution system

### 1.3.3 Hybrid power filters

The combination of passive and active power filters is termed as hybrid power filters. Out of several possible combinations, a typical combination of shunt passive filter and shunt active filter topology is shown in Fig. 1.4. Hybrid power filters improve the

compensation characteristics of passive filters, and allow the use of relatively low rating active power filters in high-power applications at a relatively low cost. Moreover, compensation characteristics of already installed passive filters can be significantly improved by installing an active power filter at its terminals, giving more flexibility to the compensation scheme [13], [18]–[20].

Fig. 1.4 Hybrid power filter with combination of shunt passive and shunt active power filters

The above discussed conventional power quality mitigation equipments (passive filters, active power filters and hybrid power filters) do not provide an adequate solution for an increasing number of applications in distribution system. This fact has attracted the attention of electrical engineers to develop dynamic and adjustable solutions to power quality problems. One modern and very promising group that deals with load current and supply voltage imperfections is Custom Power Devices (CPDs) [21], which are discussed in the next chapter.

## 1.4 Motivation

Custom power devices solve most of the power quality problems in distribution system because of their versatile functions, and also cost effective. Among CPDs, DSTATCOM is connected in shunt with load to solve current related PQ issues in distribution system

[22]–[28]. DSTATCOM consists of a voltage source converter (VSC) supported by dc-link capacitor voltage and interfacing inductor. Based on literature review on different DSTATCOM topologies, the following observations are made.

1. In existing DSTATCOMs, the required dc-link voltage magnitude is selected from a rated load condition and maintained for all load operating conditions. Due to this, the switching devices of voltage source converter are subjected to more voltage stress under reduced load condition. A continuous high voltage stress across switching devices reduces the life span of switches. The switching losses in voltage source converter depends on dc-link voltage, which appears across switch and current passing through switch. As the dc-link voltage is high during reduced load condition, the switching losses are high in conventional fixed dc-link voltage methods.

2. In a general circuit of DSTATCOMs, the VSC is connected to PCC through the interfacing unit, which consists of high value of inductance (*L*-filter), which is expensive and bulky. The DSTATCOM with *LCL*-filter as an interfacing unit consists of low value of inductance, but it requires a proper design, which is a crucial and sensitive task in power quality applications. Because, the DSTATCOM is ideally designed to operate within the possible wide frequency bandwidth of the load.

3. The rating of VSC in DSTATCOM depends on dc-link voltage and filter current injected by compensator. In case of more reactive power compensation, the required rating of VSC is high, which increases the system cost. Therefore, a proper selection of hybrid DSTATCOM topology is necessary to reduce the rating of VSC, and which in turn reduces the required dc-link voltage. As the dc-link voltage is reduced, the device voltage stress and switching losses are reduced.

4. DSTATCOM can be used for multi-functional applications, such as solar PV power injection to grid, power quality improvement and active rectification operation. In solar PV applications with DSTATCOM, the reliable and efficient operation is considerable in low power applications. To improve the efficiency,

conversion stages need to be reduced and for energy management, battery energy storage system is required. In reduced conversion stages method (single-stage), the MPPT operation and power injection to grid along with battery charging or discharging are not achieved simultaneously.

From the above discussions, there is an adequate scope for further research in the area of development of DSTATCOM in the distribution system.

*The proposed research work focuses on the enhancement of DSTATCOM performance for power quality improvement in the distribution system. It aims to reduce the switching losses and switching voltage stress in along with the reactive power compensation and harmonics mitigation. Also, it aims to reduce the interfacing inductance without compromising DSTATCOM performance. The multi-functional capability of DSTATCOM for real power injection to grid is implemented for the energy management scheme.*

## 1.5 Objectives

This research is focused on improvisation of DSTATCOM performance in terms of reduction of switching losses and voltage stress across switching devices. To achieve this an adaptive dc-link voltage regulation method is proposed. An *LCL*-filter based DSTATCOM is implemented to improve the performance with the system operated in current and voltage control modes. The work is extended to hybrid DSTATCOM to reduce VSC rating and thereby performance is improved. In addition to power quality improvement by DSTATCOM, the real power injection into grid from solar PV system and active rectification operation are implemented based on energy management scheme. In this regard, the main objectives of the present work are as follows: