# **SIGNAL INTEGRITY ANALYSIS OF ON-CHIP INTERCONNECTS USING MRTD**

*Submitted in partial fulfillment of the requirements

for the award of the degree of

**DOCTOR OF PHILOSOPHY***

*by*

**REBELLI SHASHANK**

(Roll No: 715045)

Supervisor:

**Prof. N. BHEEMA RAO**

Professor

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

TELANGANA STATE-506004, INDIA

2019

**Dedicated to**

*My family & Teachers*

# Approval Sheet

This thesis entitled "**Signal Integrity Analysis of On-Chip Interconnects using MRTD**" by **Rebelli Shashank** is approved for the degree of Doctor of Philosophy.

---

---

---

Examiners

---

---

---

Supervisor (s)

---

Chairman

Date: \_\_\_\_\_

# DECLARATION

This is to certify that the work presented in the thesis entitled "**Signal Integrity Analysis of On-Chip Interconnects Using MRTD**" is a bonafide work done by me under the supervision of **Prof. N.Bheema Rao**, Professor, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

Rebelli Shashank

(Roll No: 715045)

Date: .....

**DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**TELANGANA STATE-506004, INDIA**

## **CERTIFICATE**

This is to certify that the thesis entitled "**Signal Integrity Analysis of On-Chip Interconnects Using MRTD**", which is being submitted by **Mr. Rebelli Shashank**(Roll No: 715045), in partial fulfillment for the award of the degree of Doctor of Philosophy to the Department of Electronics and Communication Engineering of National Institute of Technology Warangal, is a record of bonafide research work carried out by him under my supervision and has not been submitted elsewhere for any degree.

Prof. N.Bheema Rao

(Supervisor)

Professor

Department of E.C.E.

N.I.T. Warangal

Warangal - 506004, India

# ACKNOWLEDGEMENTS

Firstly, I would like to express my sincere gratitude to Prof. N. Bheema Rao (Supervisor and Head of the department, ECE) for the continuous support of my Ph.D study and related research, for his patience, motivation, and guidance. My sincere thanks to him for providing me an opportunity to join the institute as a Ph.D. research scholar and giving me access to the research facilities. Without his precious support it would not have been possible to conduct this research.

Besides my supervisor, I would like to take this opportunity to thank my Doctoral Scrutiny Committee members, Prof. L. Anjaneyulu, Professor (Department of Electronics and Communication Engineering, NIT Warangal), Prof. J. V. Ramana Murthy, Professor (Department of Mathematics, NIT Warangal) and Dr. T.V.K. Hanumantha Rao, Associate Professor (Department of Electronics and Communication Engineering, NIT Warangal) for their continuous support, suggestions and advices during my research period whenever required.

I thank Dr. Atul Kumar Nishad, Assistant Professor, Electronics and communication Engineering Department, NIT Warangal for his support, suggestions and advices to carry out the research.

It is my pleasure to show my indebtedness to my co-scholars at NIT like Dr. P. Akhendra Kumar, Dr. Sudeep Surendran, Dr. Mudasir Bashir, Mr. M. A. Mushahhid Majeed, Mr. D. Pawan Kumar Sharma, Mr. T Sunil Kumar, Mr. V. Santhosh Kumar, Mr. R. Sahoo, Mr. B. Ravi, Mr. B. Roshan, Dr. Nagesh Deevi, Dr. A. Suresh, Mr. S. Subbarao, Mr. D. Kiran and Mr. Jailsingh Bookya for their help during the course of this work.

I find no words inadequate to express any form of acknowledgement to my parents, Mr. Rebelli Venkata Ramana and Mrs. Rebelli Sumithra Devi and my wife, Mrs. Rebelli Mrunalini for their love, support and patience for making my dream come true.

Finally, I thank God, for filling me every day with new hopes, strength, purpose and faith.

# ABSTRACT

With the advent of technology scaling, the efficiency of the interconnects effect the overall performance of the circuit. Although active devices mostly benefited from scaling, the performance of intermediate and global interconnects has degraded because long interconnects do not scale with the technology. Apart from power dissipation and overshoot issues, signal integrity issues such as propagation delay of long interconnects become a bottleneck in high-speed operation of ICs. Also, functional/dynamic crosstalk result in malfunctions in the circuit leading to reliability problems. Hence, there is a great demand for estimation of propagation delay and crosstalk noise of coupled interconnect lines in the early stages of VLSI design.

This thesis focuses on the development of a novel time-domain numerical method with significant numerical dispersion characteristics based on the wavelet scaling functions to address the signal integrity issues of on-chip interconnects. The multiresolution time domain (MRTD) model with its unique features is tailored for modeling VLSI interconnects. To build further credence to this and its profound existence in the recent state-of-the-art, simulations for inclusive crosstalk noise, on driver-interconnect-load (DIL) system, using the MRTD model and conventional finite-difference-time-domain (FDTD) model are performed.

Initially, in this thesis, an attempt is made to derive an MRTD scheme for two coupled copper (Cu) interconnect lines driven by the linear resistive driver in 130 nm CMOS standard process to compute the effect of coupling parasitics (i.e., coupling capacitance and mutual inductance) on peak crosstalk noise and propagation delay. For different values of coupling parasitics, the variation in peak crosstalk noise and propagation delay is observed and a comparison is done between the obtained results with those of the conventional FDTD model with respect to HSPICE simulation results. Moreover, variation in accuracy of the proposed MRTD model for a range of frequencies is observed and encouragingly it is found that approximately 100 % accuracy is maintained for a broad frequency range although a slight perturbation does exist within a short range of frequencies.

However, in DIL systems, replacement of non-linear CMOS driver with a simple linear resistor leads to a discrepancy in the results as about half of the operating time of MOSFET is in the saturation region, whereas the other half is divided between the cutoff and the triode regions. Therefore, the proposed MRTD model is extended to include the non-linear characteristics of the CMOS driver in the DIL system for 32-nm technology node. The non-linear CMOS driver is analyzed by employing the  $n$ -th-power law model. For the robustness of the model, a different number of test cases in terms of input transition time are considered and the peak crosstalk

noise and peak noise timing are also computed for the two coupled Cu interconnects. Further, the model is extended to three mutually-coupled Cu interconnect lines.

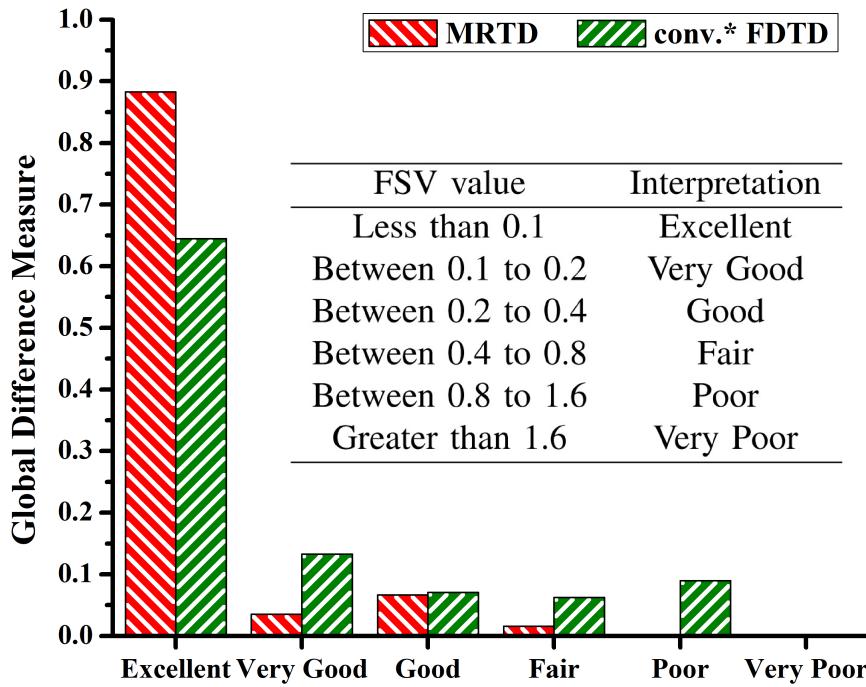

Further scaling of interconnect dimensions have made surface scattering and grain boundary scattering more prominent, resulting in increased resistivity of Cu material. Therefore, the requirements of novel material as VLSI interconnect has increased. In recent times, carbon nanomaterials such as carbon nanotubes (CNTs) and graphene nanoribbons (GNRs) act as the most promising candidates proposed as a substitute for Cu interconnects in advanced VLSI circuits. Thus, the proposed MRTD method is extended to analyse the inclusive crosstalk effects in CMOS gate driven two and three mutually-coupled MWCNT interconnects at 32-nm technology node. It is observed that a peak overshoot/undershoot occurs in the response of line 2 (victim line) as the conventional FDTD method has higher dispersion errors. Nevertheless, the numerical dispersion properties in MRTD model acts as an added advantage over the conventional FDTD model for achieving better accuracy. Finally, it is concluded that the proposed MRTD method is in good agreement with HSPICE simulations and dominates the conventional FDTD method. Furthermore, the validation of the proposed model with future selective validation (FSV) proves its accuracy and efficiency for analyzing the crosstalk effects in mutually coupled MWCNT interconnects.

This thesis shows that the proposed MRTD method is more time efficient than HSPICE, although the elapsed CPU time of the proposed MRTD method is higher than the conventional FDTD method, due to an increased number of iterations for better accuracy. Hence, there exists a trade-off between simulation time and accuracy. The analysis has been carried out on two coupled and three-coupled interconnects, but can also be extended to N-mutually coupled interconnects.

# Contents

|                                                        |             |

|--------------------------------------------------------|-------------|

| <b>Approval Sheet</b>                                  | <b>ii</b>   |

| <b>Acknowledgements</b>                                | <b>v</b>    |

| <b>Abstract</b>                                        | <b>vi</b>   |

| <b>List of Figures</b>                                 | <b>xi</b>   |

| <b>List of Tables</b>                                  | <b>xiii</b> |

| <b>List of Abbreviations</b>                           | <b>xiv</b>  |

| <b>List of Symbols</b>                                 | <b>xvi</b>  |

| <b>1 Introduction</b>                                  | <b>1</b>    |

| 1.1 Background . . . . .                               | 1           |

| 1.2 On-chip interconnects in CMOS technology . . . . . | 6           |

| 1.2.1 Technology Scaling . . . . .                     | 6           |

| 1.2.2 ITRS Predictions . . . . .                       | 8           |

| 1.3 Evolution of Interconnect Materials . . . . .      | 10          |

| 1.3.1 Aluminum Interconnects . . . . .                 | 10          |

| 1.3.2 Cu as a substitute for Al Interconnect . . . . . | 10          |

| 1.3.3 Necessity of Future Interconnects . . . . .      | 11          |

| 1.4 Motivation . . . . .                               | 12          |

| 1.5 Problem statement . . . . .                        | 13          |

| 1.6 Objectives . . . . .                               | 13          |

| 1.7 Organization of Work . . . . .                     | 14          |

| <b>2 Literature Survey</b>                             | <b>15</b>   |

| 2.1 Introduction . . . . .                             | 15          |

|          |                                                                                                   |           |

|----------|---------------------------------------------------------------------------------------------------|-----------|

| 2.2      | Extraction of interconnect electrical parameters . . . . .                                        | 16        |

| 2.2.1    | Analytical Capacitance Extraction . . . . .                                                       | 16        |

| 2.2.2    | FastCap . . . . .                                                                                 | 17        |

| 2.2.3    | FastHenry . . . . .                                                                               | 17        |

| 2.2.4    | W-Model and TL Parameters Extractor . . . . .                                                     | 18        |

| 2.3      | Various interconnect models . . . . .                                                             | 19        |

| 2.3.1    | Analytical models for estimation of delay and peak crosstalk noise in the interconnects . . . . . | 21        |

| 2.3.2    | On-chip interconnect modeling based on FDTD method . . . . .                                      | 24        |

| 2.3.3    | Review on Multiresolution time domain (MRTD) method . . . . .                                     | 26        |

| 2.4      | Summary . . . . .                                                                                 | 27        |

| <b>3</b> | <b>Signal Integrity Analysis of Resistive Driven Coupled Cu Interconnects using MRTD</b>          | <b>28</b> |

| 3.1      | Introduction . . . . .                                                                            | 28        |

| 3.2      | Development of the proposed MRTD model . . . . .                                                  | 29        |

| 3.2.1    | Near-end terminal . . . . .                                                                       | 33        |

| 3.2.2    | Far-end terminal . . . . .                                                                        | 35        |

| 3.3      | Simulation setup . . . . .                                                                        | 38        |

| 3.4      | Validation of the MRTD model and results . . . . .                                                | 38        |

| 3.5      | Summary . . . . .                                                                                 | 44        |

| <b>4</b> | <b>MRTD Model for the Analysis of Crosstalk in CMOS Driven Coupled Cu Interconnects</b>           | <b>46</b> |

| 4.1      | Introduction . . . . .                                                                            | 46        |

| 4.2      | Formulation of the MRTD Method . . . . .                                                          | 47        |

| 4.2.1    | Modeling of Coupled VLSI Interconnects . . . . .                                                  | 48        |

| 4.2.2    | Modeling of CMOS Driver . . . . .                                                                 | 49        |

| 4.2.3    | Modeling of DIL System . . . . .                                                                  | 51        |

| 4.3      | Simulation Setup and Validation of Results . . . . .                                              | 55        |

| 4.3.1    | Transient Analysis of coupled two interconnect lines . . . . .                                    | 55        |

|                             |                                                                                         |            |

|-----------------------------|-----------------------------------------------------------------------------------------|------------|

| 4.3.2                       | Transient Analysis of three mutually coupled interconnect lines . . . . .               | 59         |

| 4.4                         | Summary . . . . .                                                                       | 61         |

| <b>5</b>                    | <b>Crosstalk Noise Modeling of CMOS-Gate Driven Coupled MWCNT...</b>                    | <b>63</b>  |

| 5.1                         | Introduction . . . . .                                                                  | 63         |

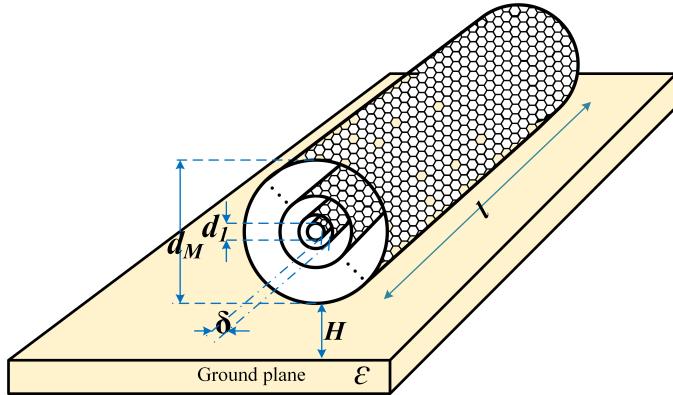

| 5.2                         | ESC model for MWCNT interconnects . . . . .                                             | 64         |

| 5.3                         | Development of the MRTD model for MWCNT interconnects . . . . .                         | 66         |

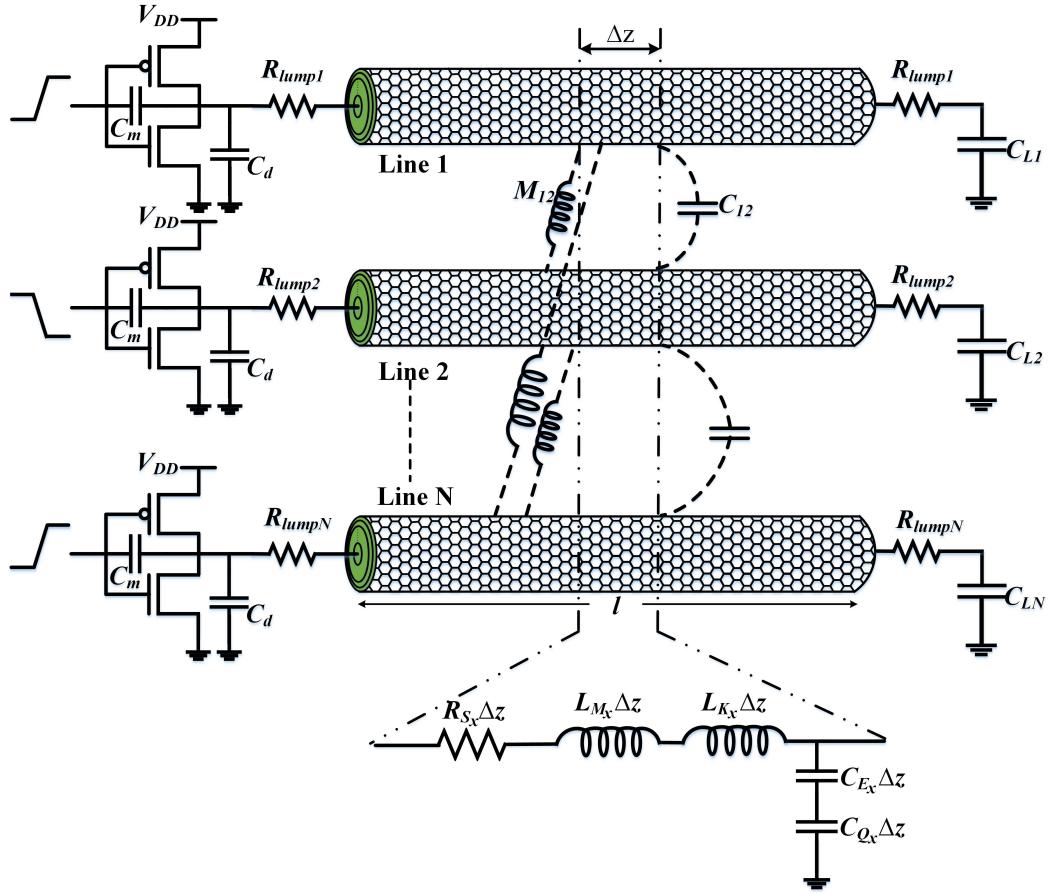

| 5.3.1                       | Modeling of mutually coupled MWCNT interconnects . . . . .                              | 66         |

| 5.3.2                       | Incorporating the boundary conditions in DIL system . . . . .                           | 68         |

| 5.3.3                       | Voltage and Current equations at the interior points of the boundary . .                | 70         |

| 5.4                         | Comparison and validation of the proposed MRTD model . . . . .                          | 73         |

| 5.4.1                       | Inclusive crosstalk analysis of two mutually coupled MWCNT intercon-<br>nects . . . . . | 75         |

| 5.4.2                       | Extensions and observations . . . . .                                                   | 76         |

| 5.5                         | Summary . . . . .                                                                       | 82         |

| <b>6</b>                    | <b>Conclusions And Future Scope</b>                                                     | <b>84</b>  |

| 6.1                         | Conclusions . . . . .                                                                   | 84         |

| 6.2                         | Future Scope . . . . .                                                                  | 85         |

| <b>A</b>                    |                                                                                         | <b>87</b>  |

| <b>References</b>           |                                                                                         | <b>89</b>  |

| <b>List of Publications</b> |                                                                                         | <b>100</b> |

# List of Figures

|      |                                                                                                                                                                                  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Cross sectional view on the stack of layers in an IC [1]. . . . .                                                                                                                | 2  |

| 1.2  | On-chip interconnect delay across different technology nodes [1] . . . . .                                                                                                       | 4  |

| 1.3  | Crosstalk in closely placed interconnects . . . . .                                                                                                                              | 5  |

| 2.1  | The star-HSPICE W-Element method . . . . .                                                                                                                                       | 19 |

| 2.2  | 3-D and cross sectional view of an interconnect structure . . . . .                                                                                                              | 19 |

| 2.3  | Validity of different interconnect models with respect to frequency [3]. . . . .                                                                                                 | 20 |

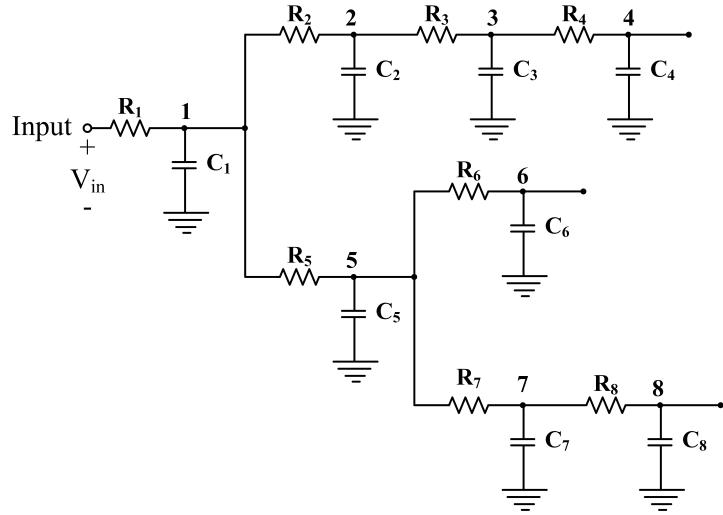

| 2.4  | RC interconnect tree network. . . . .                                                                                                                                            | 21 |

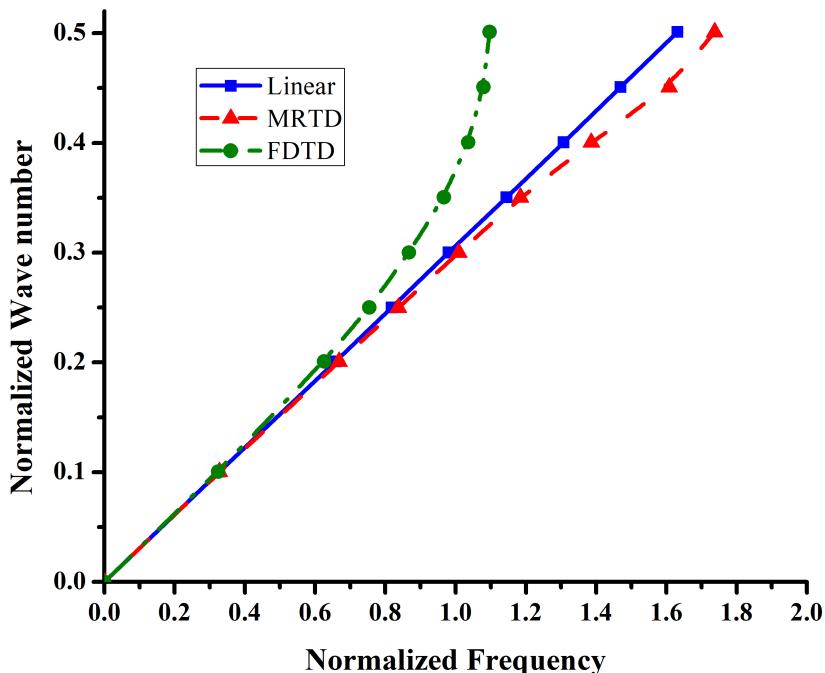

| 2.5  | Dispersion curves of the MRTD scheme based on Battle-Lemarie scaling function and FDTD scheme with respect to ideal linear case [49] . . . . .                                   | 26 |

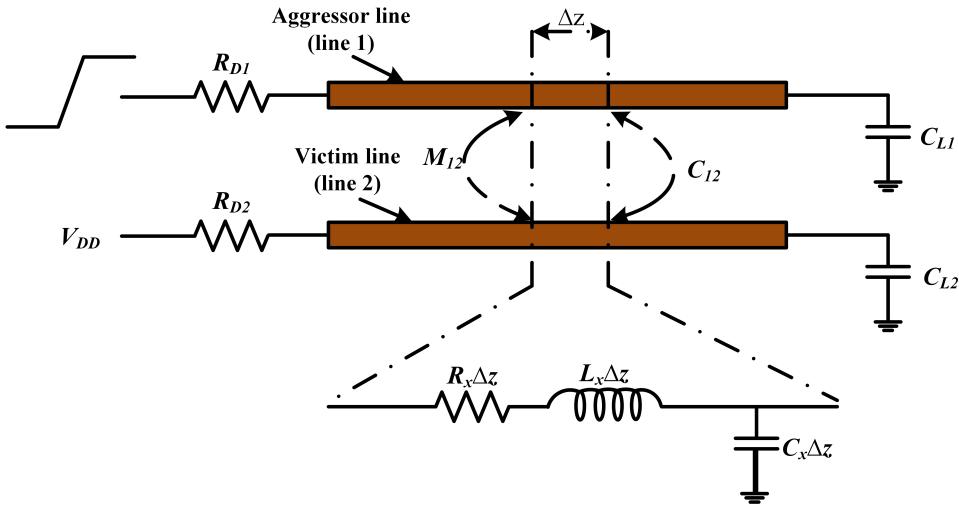

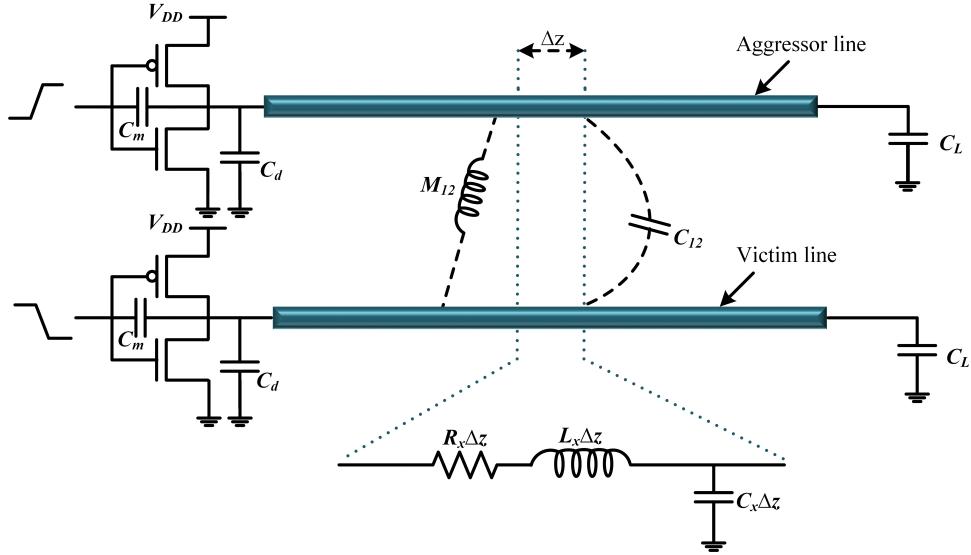

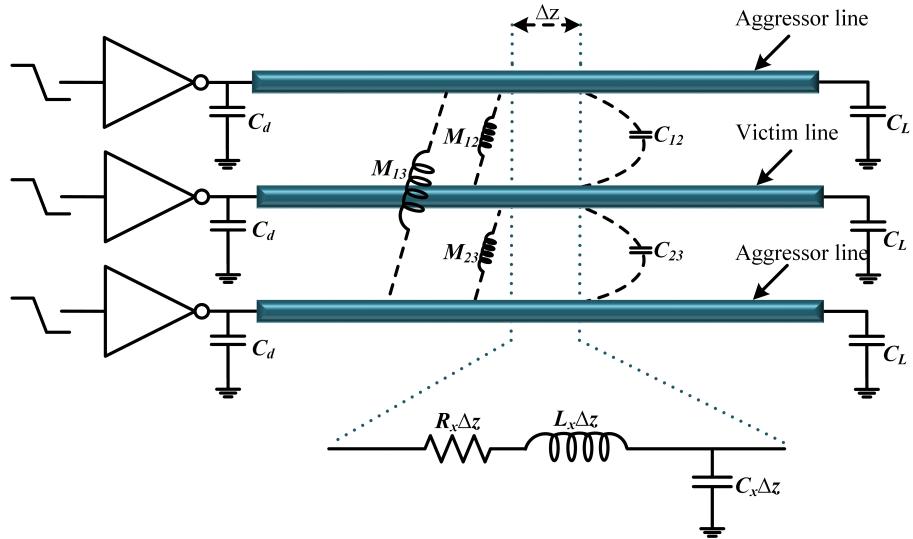

| 3.1  | DIL system for coupled Cu interconnects . . . . .                                                                                                                                | 29 |

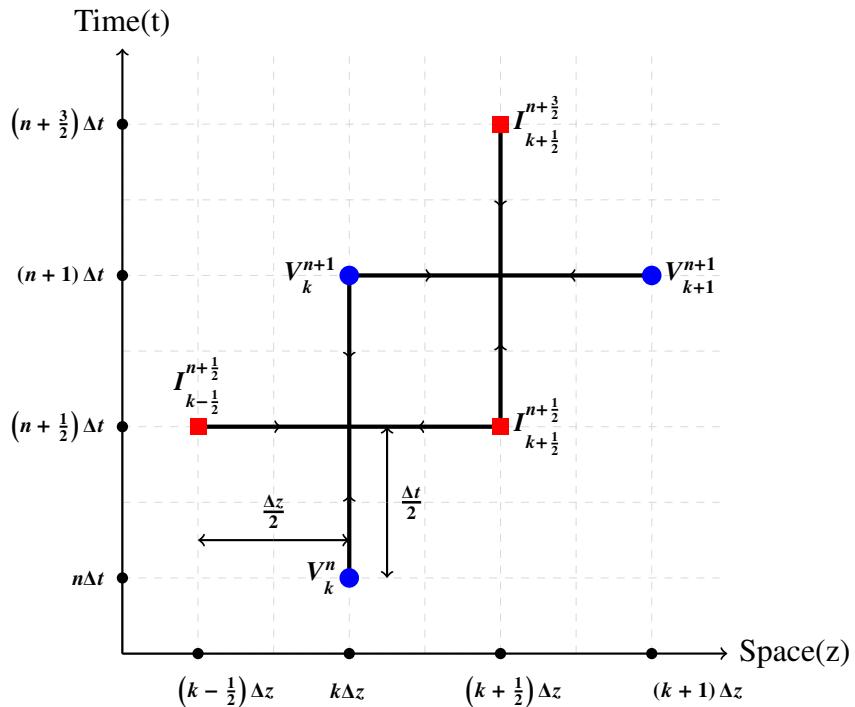

| 3.2  | Relation between discretizations of space and time. . . . .                                                                                                                      | 30 |

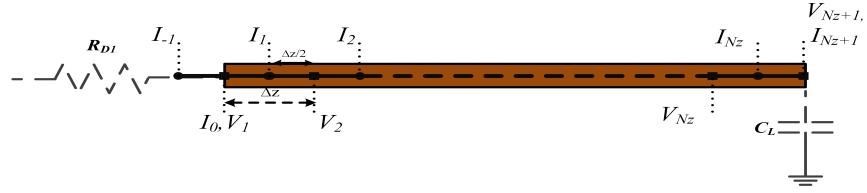

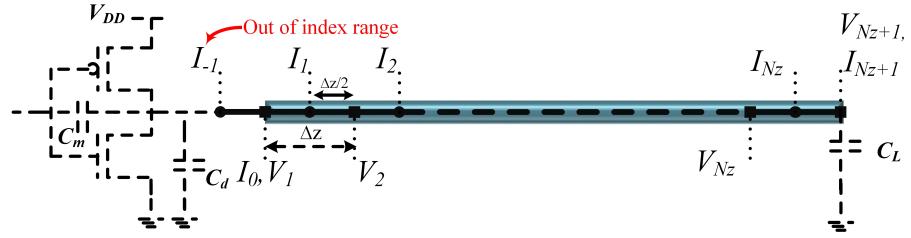

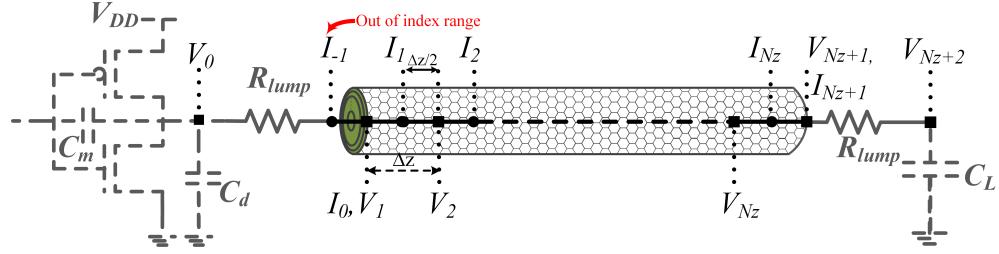

| 3.3  | Spatial discretization of interconnect line for MRTD technique . . . . .                                                                                                         | 31 |

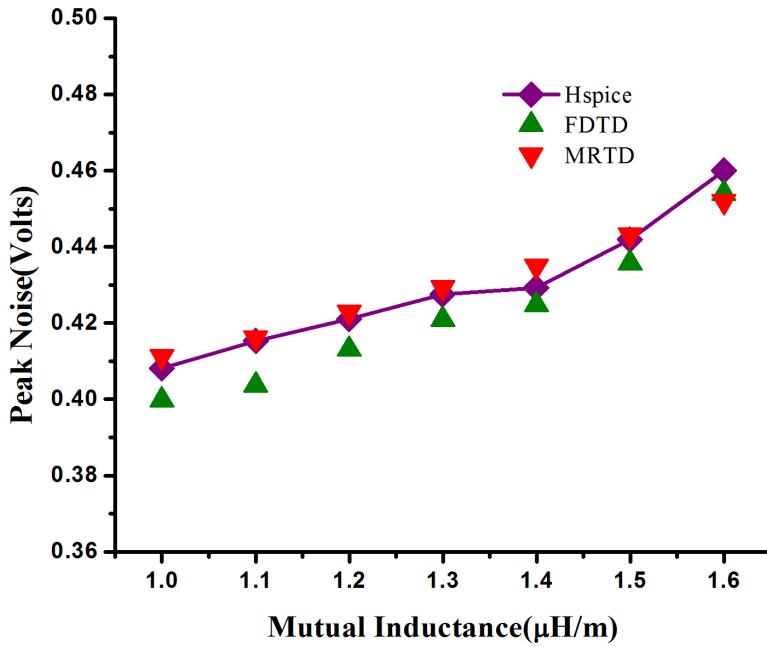

| 3.4  | Dependency of crosstalk noise on mutual inductance . . . . .                                                                                                                     | 39 |

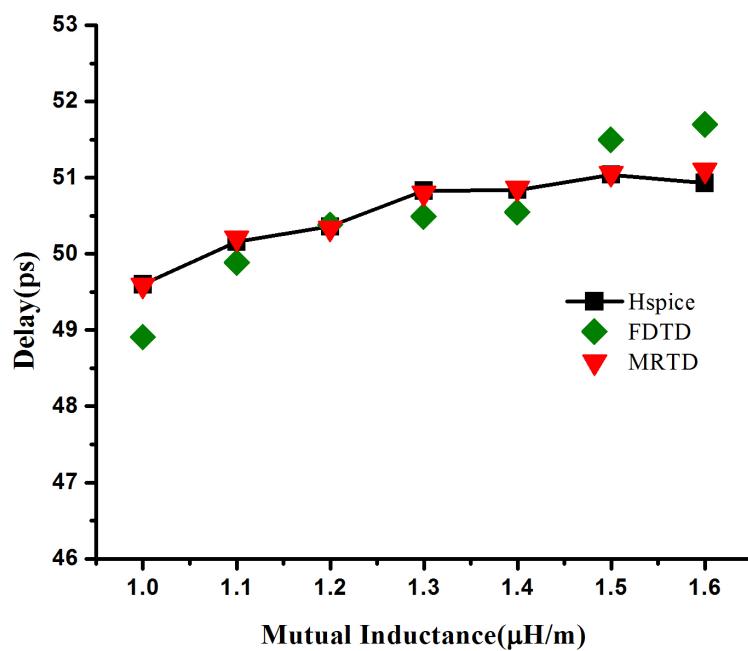

| 3.5  | Dependency of in-phase delay on mutual inductance . . . . .                                                                                                                      | 39 |

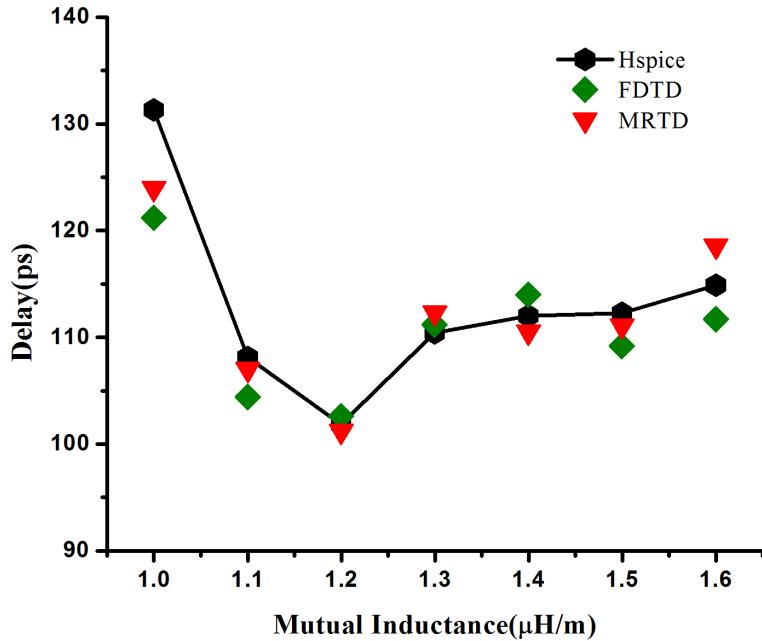

| 3.6  | Dependency of out-phase delay on mutual inductance . . . . .                                                                                                                     | 40 |

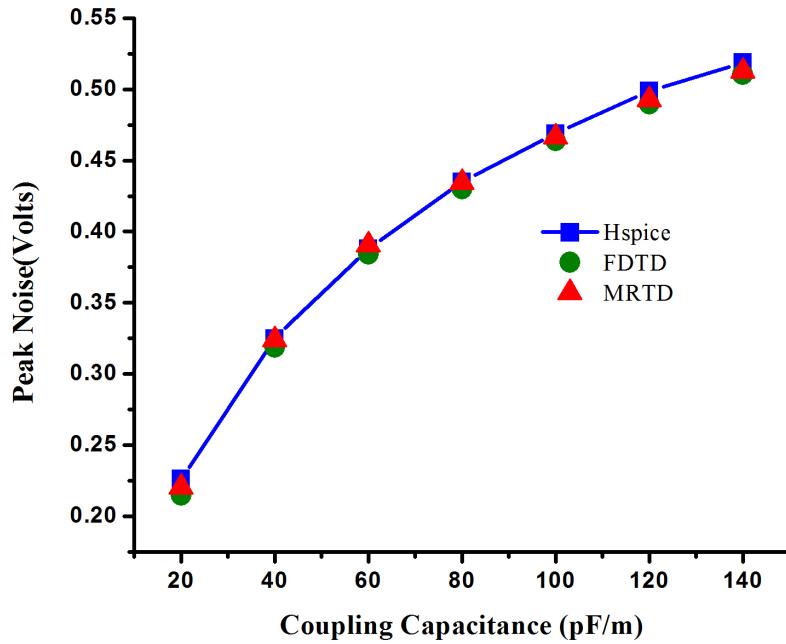

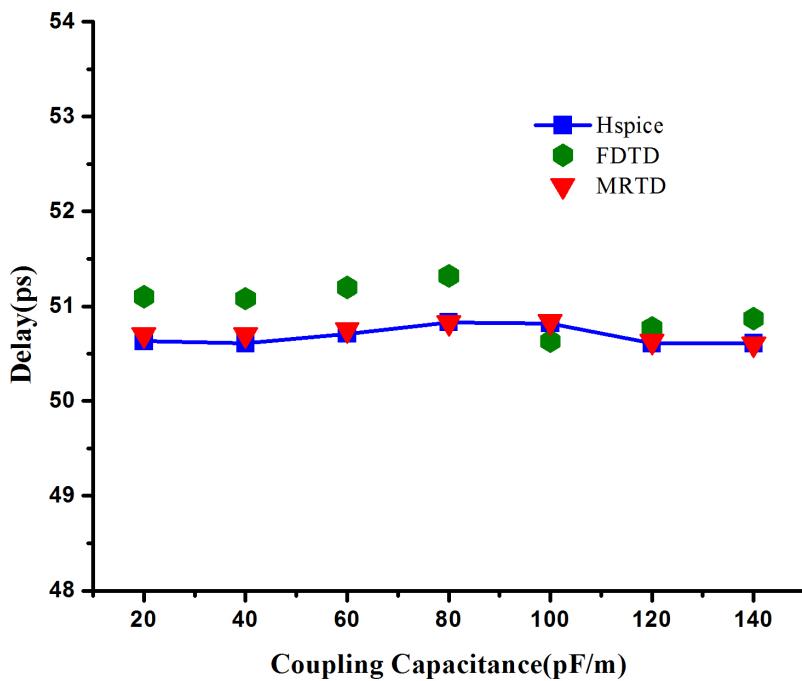

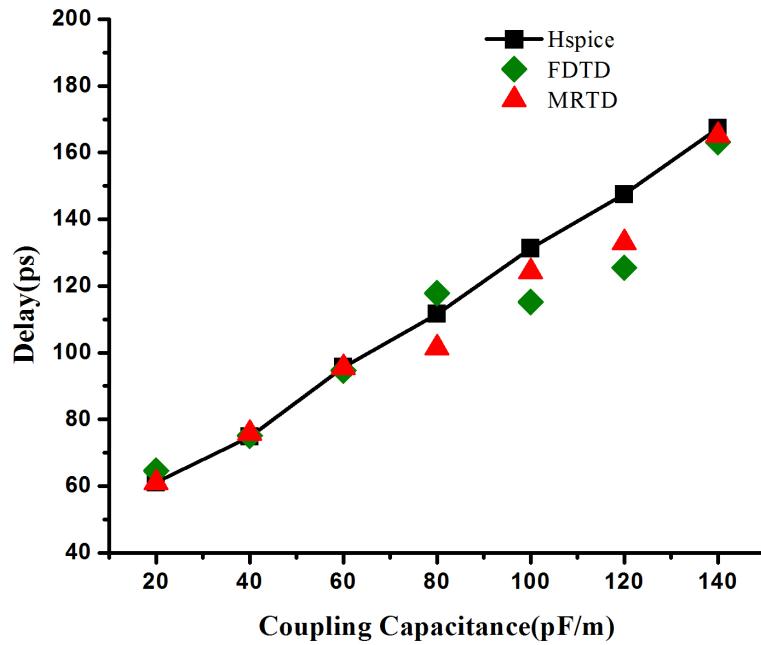

| 3.7  | Variation of crosstalk noise as a function of coupling capacitance . . . . .                                                                                                     | 41 |

| 3.8  | Variation of in-phase delay as a function of coupling capacitance . . . . .                                                                                                      | 41 |

| 3.9  | Variation of out-phase delay as a function of coupling capacitance . . . . .                                                                                                     | 42 |

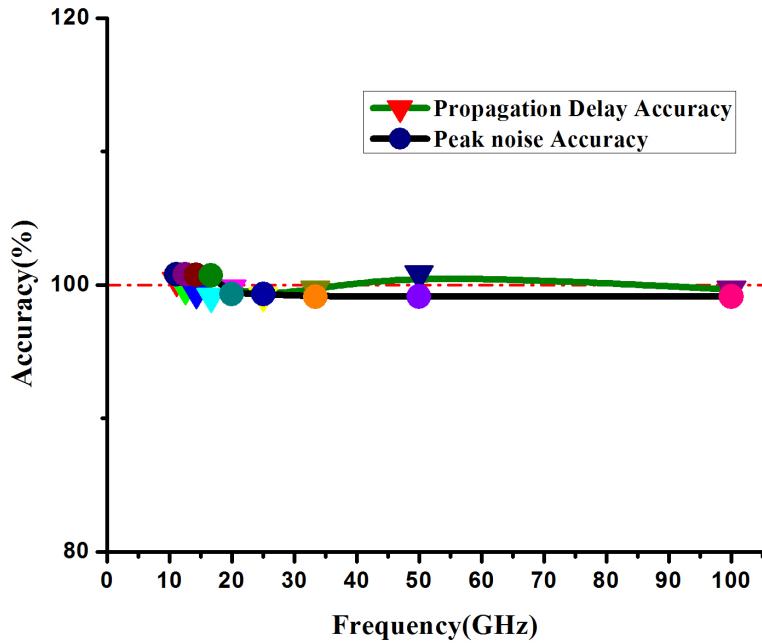

| 3.10 | Effect of frequency on accuracy of the model . . . . .                                                                                                                           | 44 |

| 4.1  | DIL system for CMOS driven coupled Cu interconnects. . . . .                                                                                                                     | 47 |

| 4.2  | Spatial discretization of MRTD technique for DIL system. . . . .                                                                                                                 | 48 |

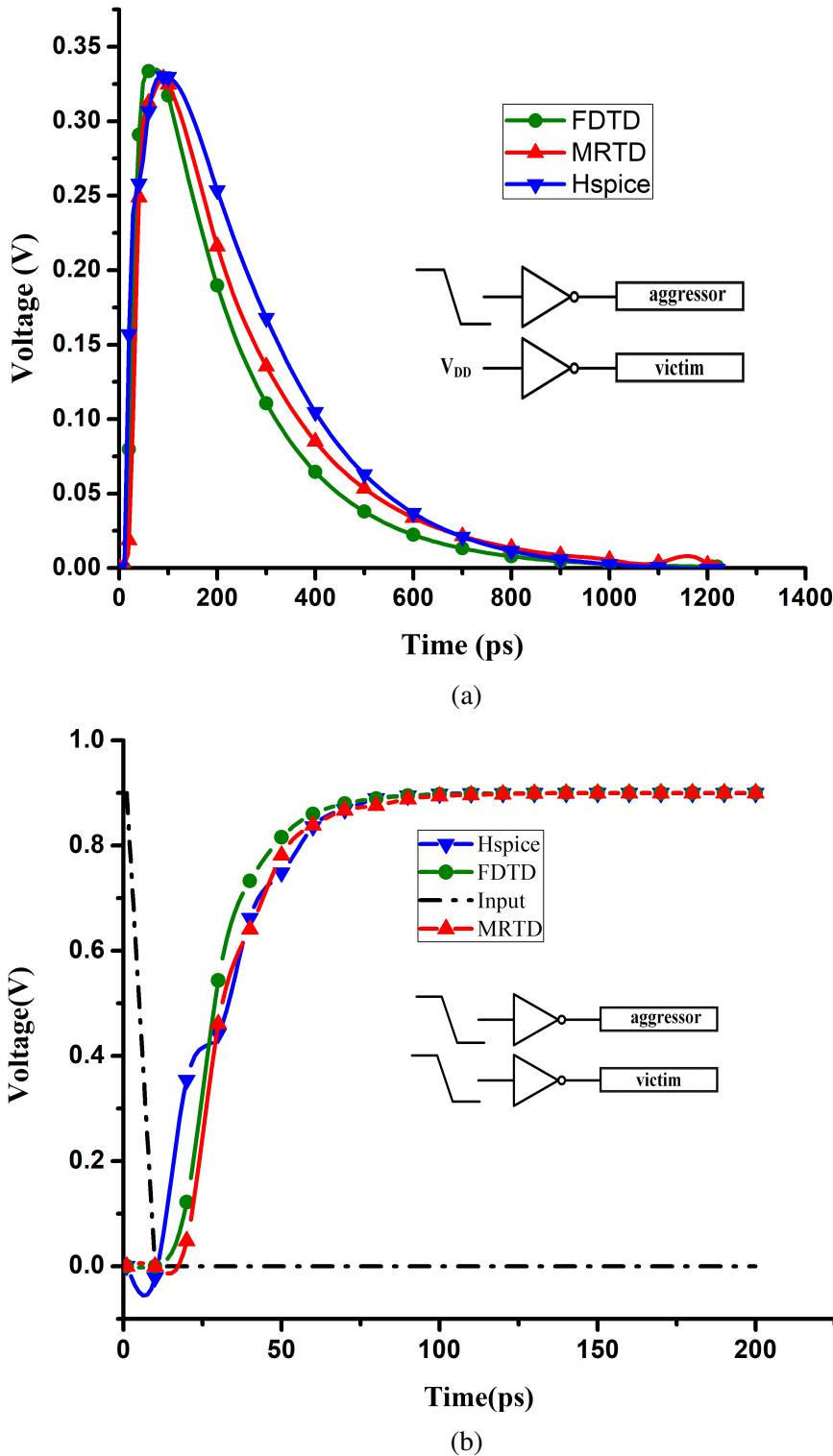

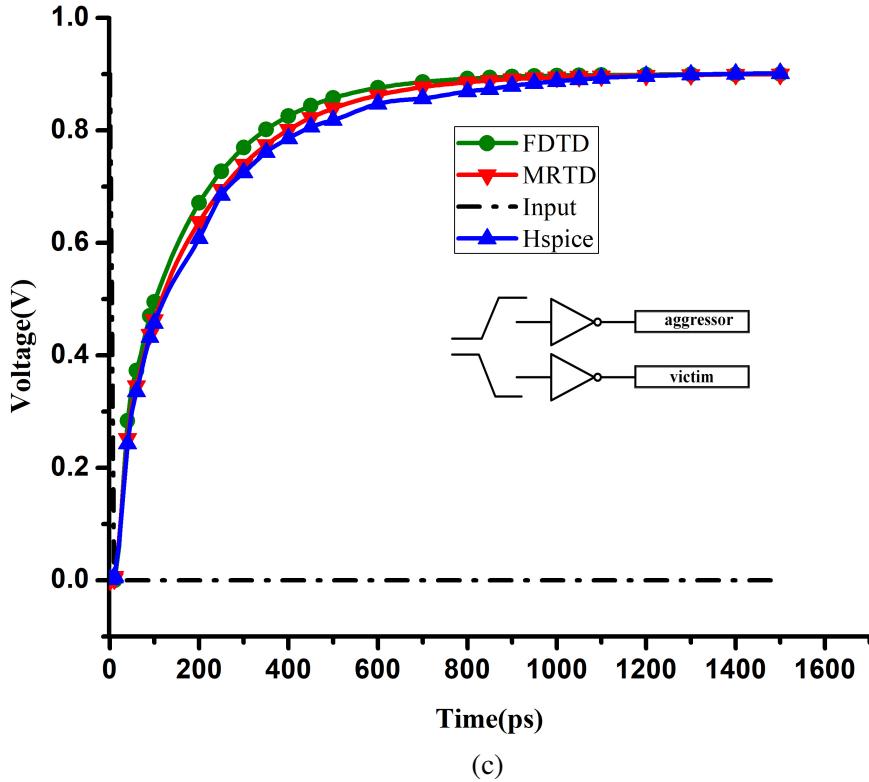

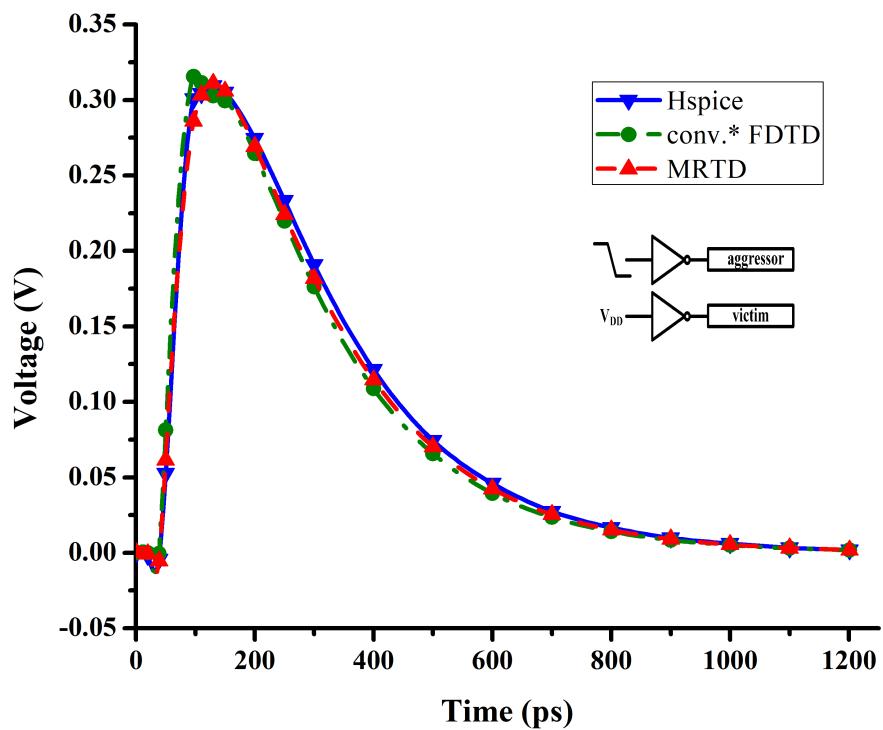

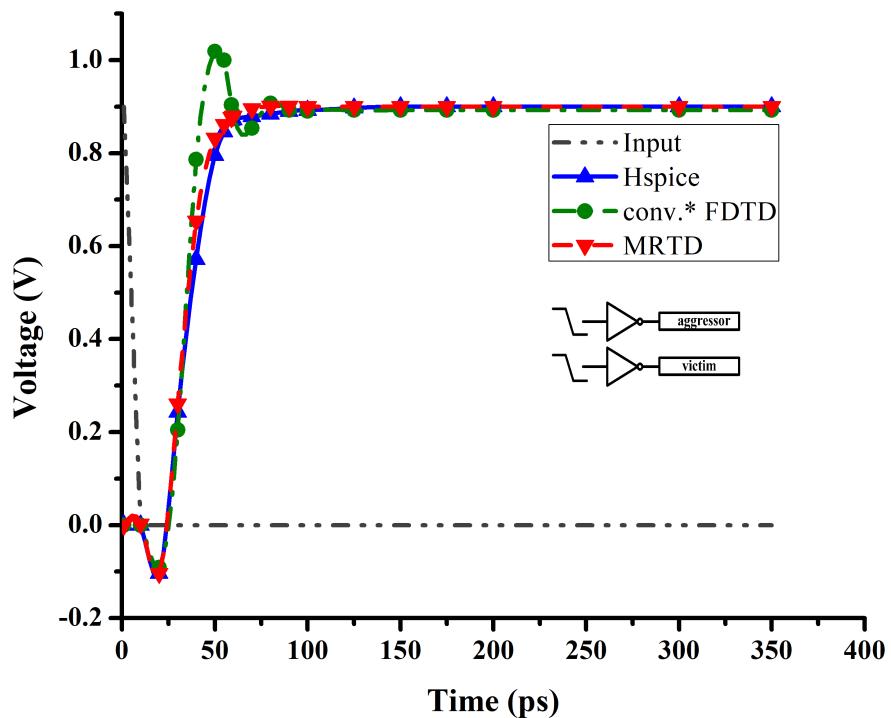

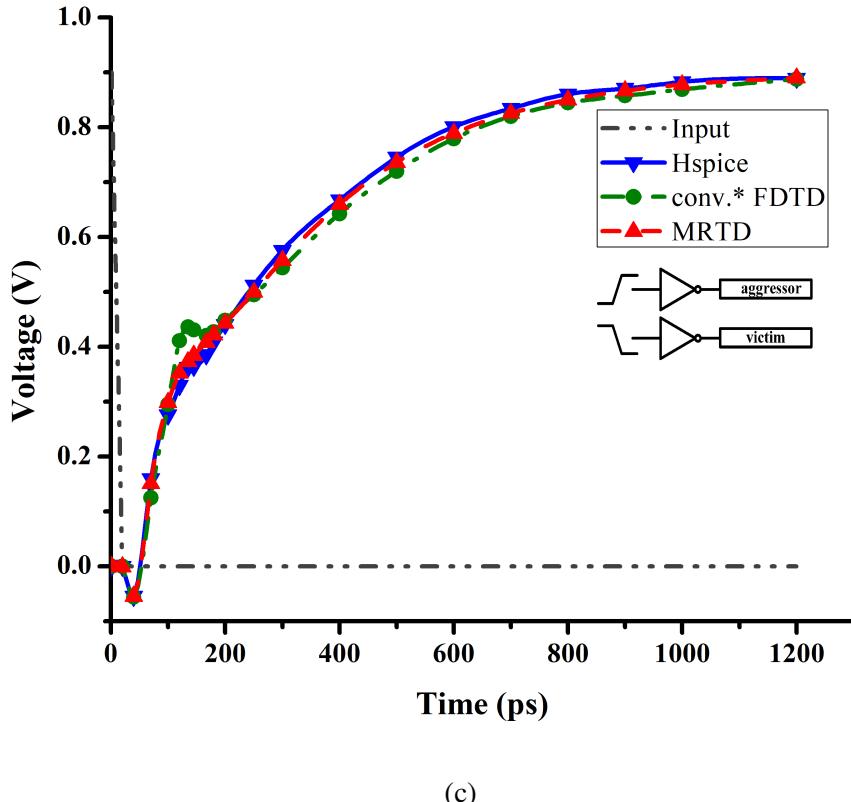

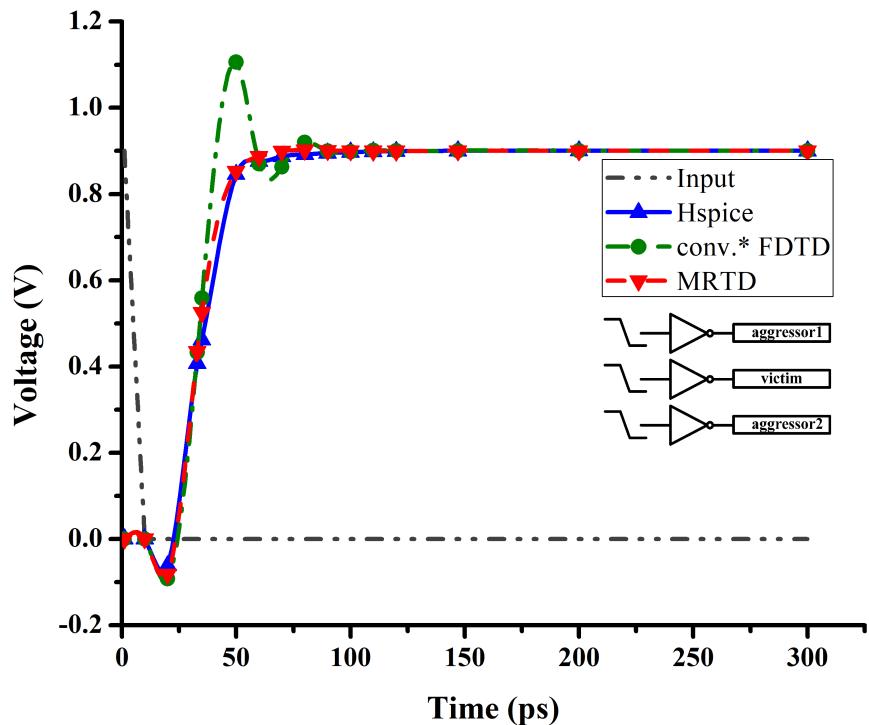

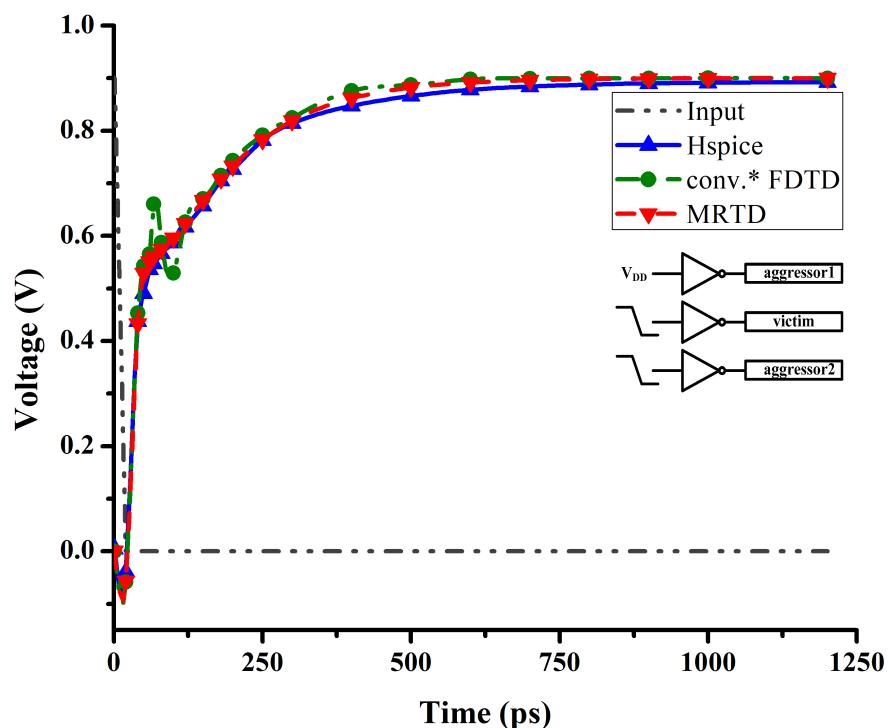

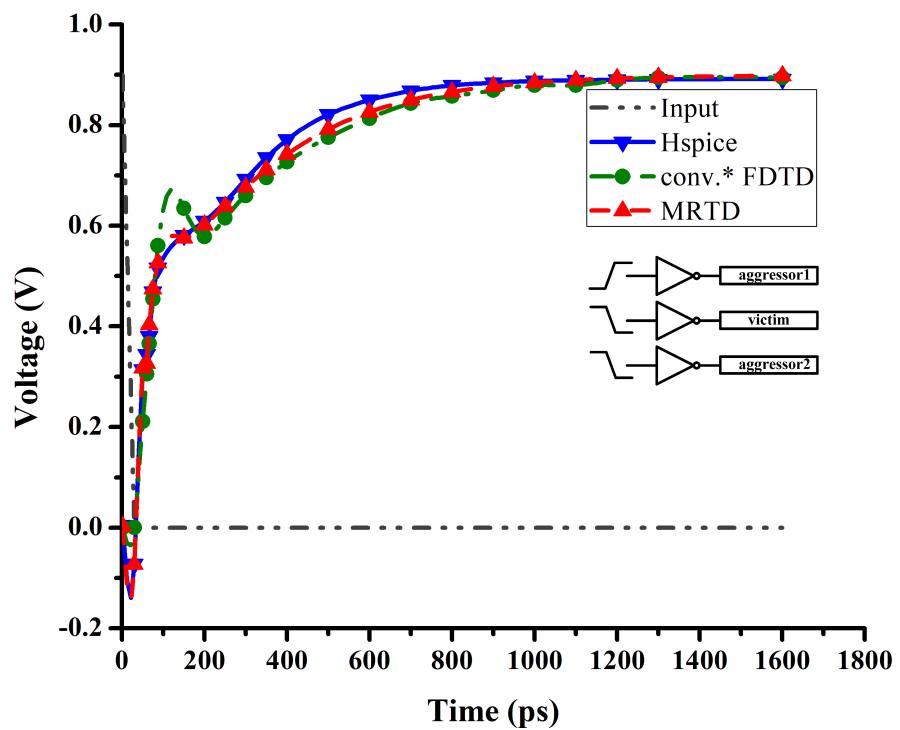

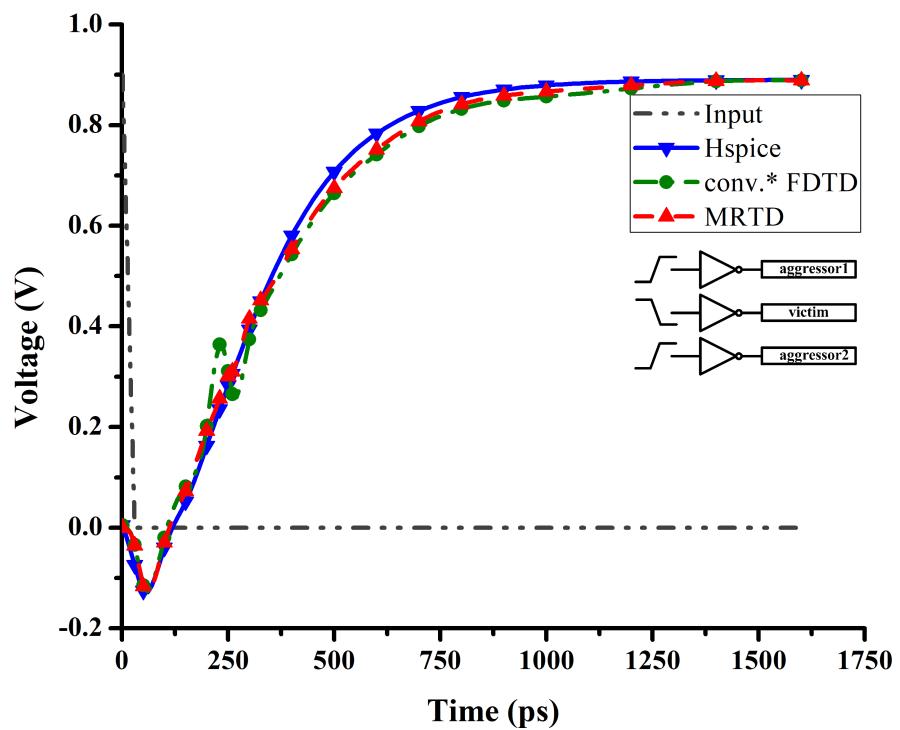

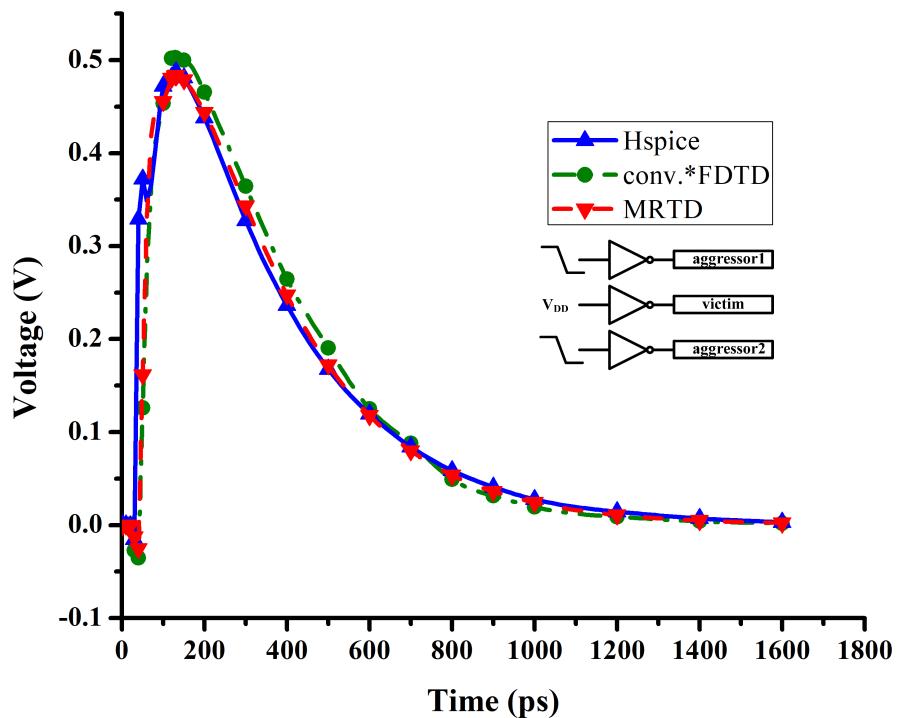

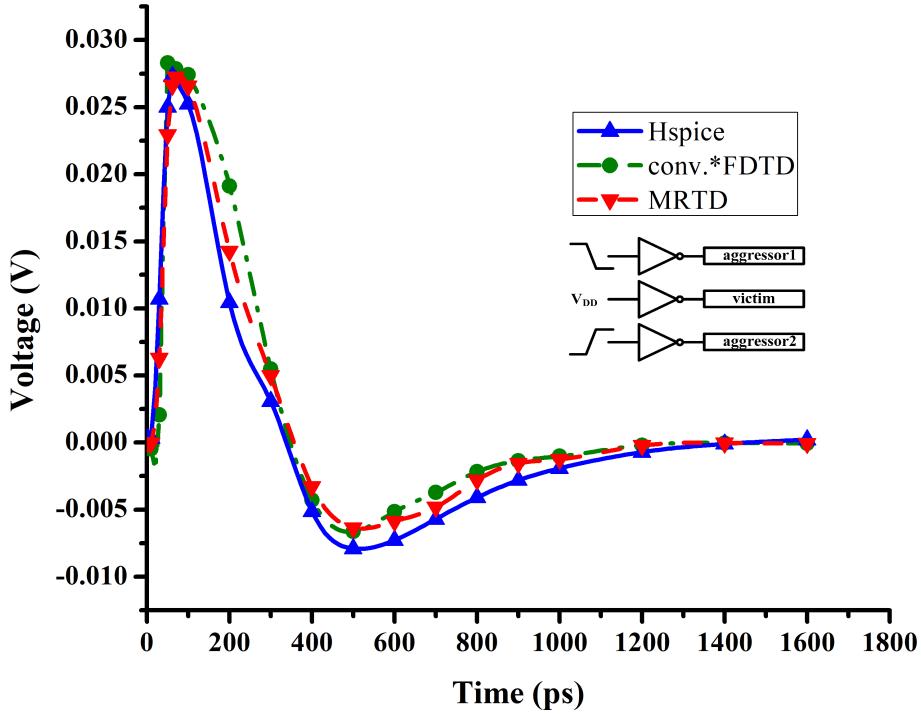

| 4.3  | Transient response at the far-end terminal of the victim line during the switching of (a) functional crosstalk (b) dynamic in-phase and (c) dynamic out-phase crosstalk. . . . . | 57 |

|     |                                                                                                                                                           |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4 | Schematic of CMOS driven three-coupled interconnect lines. . . . .                                                                                        | 59 |

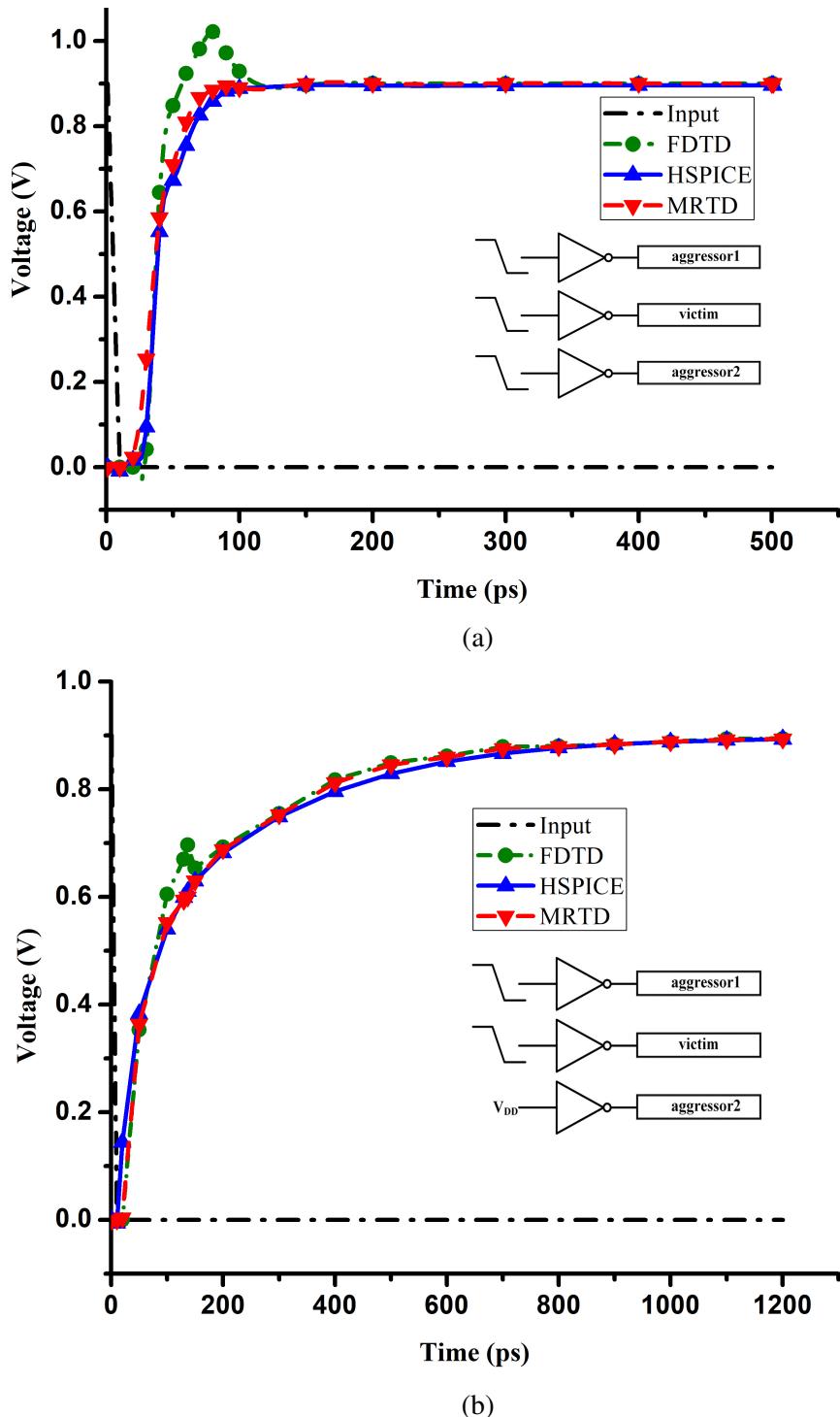

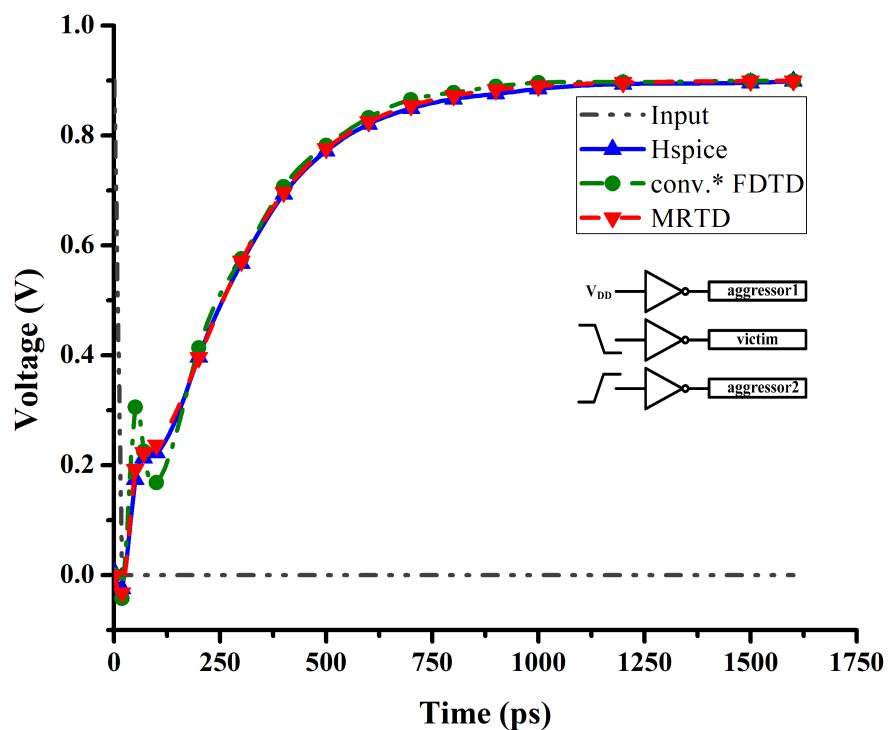

| 4.5 | Crosstalk induced 50% Delay analysis on victim line due to aggressor lines (a) test case-1, (b) test case-2 for three-coupled interconnect lines. . . . . | 60 |

| 5.1 | Geometry of the MWCNT over a ground plane. . . . .                                                                                                        | 64 |

| 5.2 | Schematic of the ESC model of mutually N-coupled MWCNT interconnects driven by CMOS driver . . . . .                                                      | 65 |

| 5.3 | Spatial discretization of MRTD model for driver-interconnect-load system. . . .                                                                           | 67 |

| 5.4 | Comparison of the transient response of line 2 during the (a) functional switching (b) dynamic in-phase and (c) out-phase switching. . . . .              | 75 |

| 5.5 | Transient response on line 2 (victim) due to lines 1 and 3 (aggressors) for three-coupled interconnects. . . . .                                          | 81 |

| 5.6 | Histogram from the data-sets of Figure 5.5a using feature selective validation (FSV) tool. . . . .                                                        | 82 |

# List of Tables

|     |                                                                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Scaling effects on MOS device . . . . .                                                                                                   | 7  |

| 1.2 | Scaling of Local Interconnects . . . . .                                                                                                  | 7  |

| 1.3 | Ideal scaling of Intermediate/Global Interconnects . . . . .                                                                              | 8  |

| 1.4 | ITRS prediction on scaling trends[26, 27] . . . . .                                                                                       | 9  |

| 1.5 | Resistivity of conductor materials [30] . . . . .                                                                                         | 11 |

| 3.1 | Connection coefficients $a(i)$ of Daubechies' scaling functions ( $D_4$ ) [99]. . . . .                                                   | 32 |

| 3.2 | Comparison of computational error involved in crosstalk noise due to the mutual inductance. . . . .                                       | 42 |

| 3.3 | Comparison of computational error involved in crosstalk noise due to the coupling capacitance. . . . .                                    | 43 |

| 3.4 | Comparison of Computational Efforts Between the Methods. . . . .                                                                          | 43 |

| 4.1 | Model parameters of pMOS and nMOS for 32-nm technology node [87]. . . . .                                                                 | 51 |

| 4.2 | Interconnect parasitics for setup mentioned in section 4.3(A*-Aggressor, V*-Victim). . . . .                                              | 58 |

| 4.3 | Computational error involved for peak crosstalk noise and peak noise timing on victim line (conv.*-conventional). . . . .                 | 58 |

| 4.4 | Computational error involved for 50% Delay on victim line of three-coupled interconnects (Agg.*-Aggressor & conv.*-conventional). . . . . | 61 |

| 4.5 | Comparison of elapsed CPU time of the methods for two and three mutually coupled interconnects (conv.*-conventional). . . . .             | 61 |

| 5.1 | Computational Error Associated with the Estimation of Dynamic Crosstalk Effects on Line 2 (Victim). . . . .                               | 77 |

| 5.2 | Computational Error Involved for 50% Propagation Delay on Line 2 of Three Mutually Coupled Lines. . . . .                                 | 77 |

| 5.3 | Comparison of Computational Efforts Between the Methods. . . . .                                                                          | 81 |

# List of Abbreviations

|             |                                                     |

|-------------|-----------------------------------------------------|

| <b>3-D</b>  | Three Dimensional                                   |

| <b>2-D</b>  | Two Dimensional                                     |

| <b>BEM</b>  | Boundary Element Method                             |

| <b>CAD</b>  | Computer Aided Design                               |

| <b>CDF</b>  | Cohen-Daubechies-Feauveau                           |

| <b>CFL</b>  | Courent-Friedrich-Lewy                              |

| <b>CMOS</b> | Complemtary Metal Oxide Semiconductor               |

| <b>CMS</b>  | Current-mode signaling                              |

| <b>CNT</b>  | carbon nano-tube                                    |

| <b>CPU</b>  | Central Processing Unit                             |

| <b>DSM</b>  | Deep Sub-micron                                     |

| <b>DIL</b>  | Driver-Interconnect-Load                            |

| <b>ECAD</b> | Electrical Computer Aided Design                    |

| <b>EM</b>   | Electro Magnetic                                    |

| <b>ESC</b>  | Equivalent Single Conductor                         |

| <b>FDTD</b> | Finite Difference Time Domain                       |

| <b>FMM</b>  | Fast Multi-pole Method                              |

| <b>FSV</b>  | Feature Selective Validation                        |

| <b>GDM</b>  | Global Difference Measure                           |

| <b>GNR</b>  | graphene nano-ribbon                                |

| <b>IC</b>   | Integrated Circuit                                  |

| <b>IP</b>   | Intellectual Property                               |

| <b>ITRS</b> | International Technology Roadmap for Semiconductors |

| <b>MCB</b>  | Mixed-carbon nano-tube bundle                       |

| <b>MEMs</b> | Micro Electromechanical Systems                     |

| <b>MFP</b>  | mean free path                                      |

| <b>MIT</b>  | Massachusetts Institute of Technology               |

|               |                                                     |

|---------------|-----------------------------------------------------|

| <b>MLGNR</b>  | multi-layer graphene nanoribbon                     |

| <b>MOSFET</b> | Metal Oxide Semiconductor Field Effect Transistor   |

| <b>MRTD</b>   | Multiresolution-time-domain                         |

| <b>MWCNT</b>  | multi-walled carbon nanotube                        |

| <b>nMOS</b>   | n-channel Metal-Oxide-Semiconductor                 |

| <b>PCB</b>    | Printed Circuit Board                               |

| <b>PDE</b>    | Partial Differential Equations                      |

| <b>pMOS</b>   | p-channel Metal-Oxide-Semiconductor                 |

| <b>p.u.l</b>  | per unit length                                     |

| <b>RC</b>     | Resistance Capacitance                              |

| <b>RLC</b>    | Resistance Inductance Capacitance                   |

| <b>SLGNR</b>  | single layer graphene nano-ribbon                   |

| <b>SoC</b>    | System On-Chip                                      |

| <b>SPICE</b>  | Simulation Program with Integrated Circuit Emphasis |

| <b>SWCNT</b>  | single walled carbon nano-tube                      |

| <b>TEM</b>    | Transverse Electromagnetic                          |

| <b>TL</b>     | Transmission Line                                   |

| <b>TSV</b>    | Through-Silicon Via                                 |

| <b>VLSI</b>   | Very Large Scale Integration                        |

| <b>VMS</b>    | Voltage-mode signaling                              |

# List of Symbols

|                               |                                                          |

|-------------------------------|----------------------------------------------------------|

| $S$                           | Scaling Factor                                           |

| $L_{ch}$                      | Channel Length                                           |

| $t_{ox}$                      | Gate Oxide Thickness                                     |

| $W$                           | Channel Width                                            |

| $V_{DD}$                      | Supply Voltage                                           |

| $\tau_g$                      | Gate Delay                                               |

| $w$                           | Interconnect Width                                       |

| $s$                           | Spacing between the two coupled interconnects            |

| $t$                           | Interconnect Thickness                                   |

| $l$                           | Length of the interconnect                               |

| $A_c$                         | Chip Area                                                |

| $\tau$                        | RC Delay                                                 |

| $\lambda_d$                   | Finite Drain Conductance Parameter                       |

| $\epsilon$                    | Dielectric Constant                                      |

| $R$                           | Line Resistance p.u.l                                    |

| $L$                           | Line Inductance p.u.l                                    |

| $G$                           | Line Conductance p.u.l                                   |

| $C$                           | Line Capacitance p.u.l                                   |

| $C_{12}$                      | Coupling Capacitance between Line 1 & Line 2             |

| $C_{23}$                      | Coupling Capacitance between Line 2 & Line 3             |

| $M_{12}$                      | Mutual Inductance between Line 1 & Line 2                |

| $M_{23}$                      | Mutual Inductance between Line 2 & Line 3                |

| $M_{13}$                      | Mutual Inductance between Line 1 & Line 3                |

| $C_L$                         | Load Capacitance                                         |

| $R_D$                         | Driver Resistance                                        |

| $\Delta z$                    | Space discretization interval                            |

| $\Delta t$                    | Time discretization interval                             |

| $N_z$                         | Number of space segments                                 |

| $\phi(z)$                     | Daubechies' scaling function                             |

| $h(t)$                        | Pulse function                                           |

| $\delta_{n,n'}/\delta_{n,n'}$ | Kronecker symbol                                         |

| $S_b$                         | Effective support size                                   |

| $D_4$                         | Daubechies' scaling function with four vanishing moments |

| $\hat{\phi}(\lambda)$         | Fourier transform of a scaling function $\phi(z)$        |

|             |                                          |

|-------------|------------------------------------------|

| $a(i)$      | Connection Coefficient                   |

| $q$         | Courant number                           |

| $\vartheta$ | phase velocity                           |

| $C_d$       | Drain diffusion capacitance              |

| $C_m$       | Gate-to-Drain coupling capacitance       |

| $I_{DSAT}$  | Drain saturation current                 |

| $V_{DSAT}$  | Drain saturation voltage                 |

| $V_T$       | Threshold Voltage                        |

| $\delta$    | van der Waals gap                        |

| $R_{lump}$  | Lumped Resistance                        |

| $R_q$       | Quantum Resistance                       |

| $R_{mc}$    | Imperfect contact Resistance             |

| $R_s$       | Scattering Resistance                    |

| $L_M$       | Magnetic Inductance                      |

| $C_E$       | Electrostatic capacitance                |

| $d_M$       | Outer-most diameter of MWCNT             |

| $d_1$       | Inner-most diameter of MWCNT             |

| $M$         | Number of concentric shells in the MWCNT |

# Chapter 1

## Introduction

### 1.1 Background

The density and complexity of Very Large Scale Integrated (VLSI) circuits has increased exponentially over the last two decades resulting in high performance electronic systems for a wide range of applications such as reconfigurable computing, mobile and satellite communication, multimedia, micro-electromechanical systems (MEMS) and robotics. The count of active devices has reached hundreds of millions, while connecting wires among the devices tend to grow linearly with the transistor counts [1].

An integrated circuit (IC) comprises of several components and functional blocks, such as transistors, gates, sub-circuits etc., which are interconnected using aluminum (Al)/ copper (Cu) metals or graphene-based materials. Interconnects are capable of transmitting data from one block to the other, in the form of current or voltage. Ideally, the signal transmission/reception between the two interconnected blocks should be instantaneous with no delay. However, this cannot be achieved in practical situations, due to the fact that there always exists a signal propagation time during the transmission of data from one block to the other. If the signals vary rapidly (high frequency applications) compared to the propagation time, several effects may be observed such as Delay, Overshoot, and Crosstalk [2]. Currently in the deep submicron (DSM) regime, performance of electronic systems depends on these effects introduced by interconnections. Hence, it is very important to have accurate and efficient estimation models of the interconnection effects at the design phase itself to avoid pitfalls and to reduce the time to market of VLSI chips.

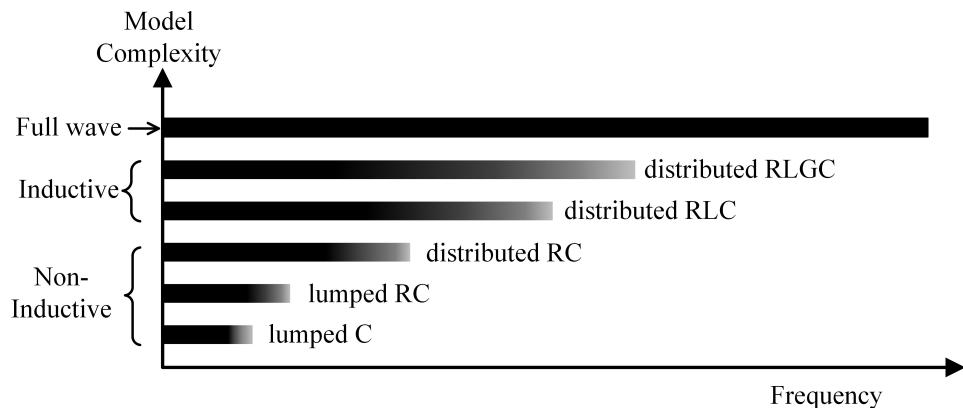

In the state of the art, there are several viable models developed (with variable degrees of accuracy), starting from a simple capacitor model to a frequency-dependent transmission line model. These models are more or less a simplified analysis of the fundamental physical event i.e., the propagation of an electromagnetic (EM) wave in the complex metal-dielectric structure formed by the interconnection network of an electronic circuit. Here, the complication is that a comprehensive EM analysis of an IC is beyond the present day computation capabilities. Hence, the EM phenomena are replaced with electrical models. Even complex electrical models are replaced with simpler electrical models when accuracy is not critical, because the simulation time of complete system would otherwise be extremely long [3].

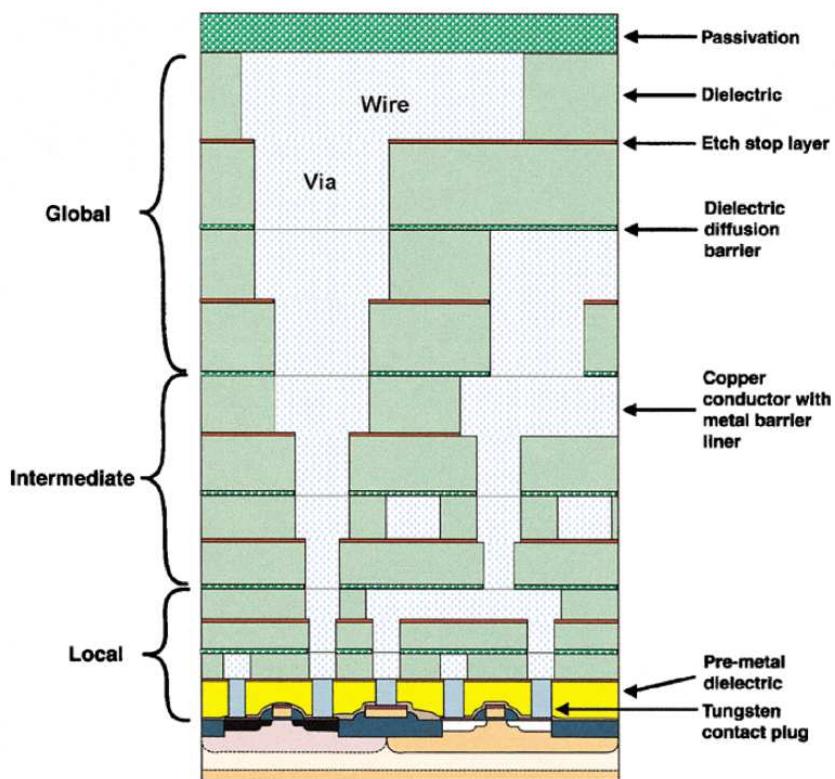

Figure 1.1: Cross sectional view on the stack of layers in an IC [1].

Depending on the length, interconnects are classified into local, intermediate and global interconnects [4]. Local interconnects are very thin wires and are used to connect gates and transistors within any block on a chip. This type of interconnects generally occupies the lower few metal layers in a multi-layered interconnect structure as shown in Figure 1.1. Intermediate interconnects are used to distribute clock/data signals within a functional block or between the adjacent blocks and where the typical length between the blocks can vary up to 2.5 mm. Generally, these types of interconnects occupy few layers above the local interconnects. Global interconnects are used to connect a large number of intellectual property (IP) blocks, such as filters, memory, processing elements and interfaces. As these IP blocks need to communicate

with each other over long distances, they need long wires that span most of the length of the entire chip size. Global interconnects are wide and long metal layers in a multi-layer structure and fill top few layers. Typical lengths of these global interconnects are greater than 2.5 mm and sometimes as long as half of the chip's perimeter. Generally, the top metal layers are reserved for routing of the power/ground/clock signals. The dimensions of local interconnects perfectly scale with technology scaling, whereas the dimensions of intermediate and global interconnects do not scale proportionally with technology scaling.

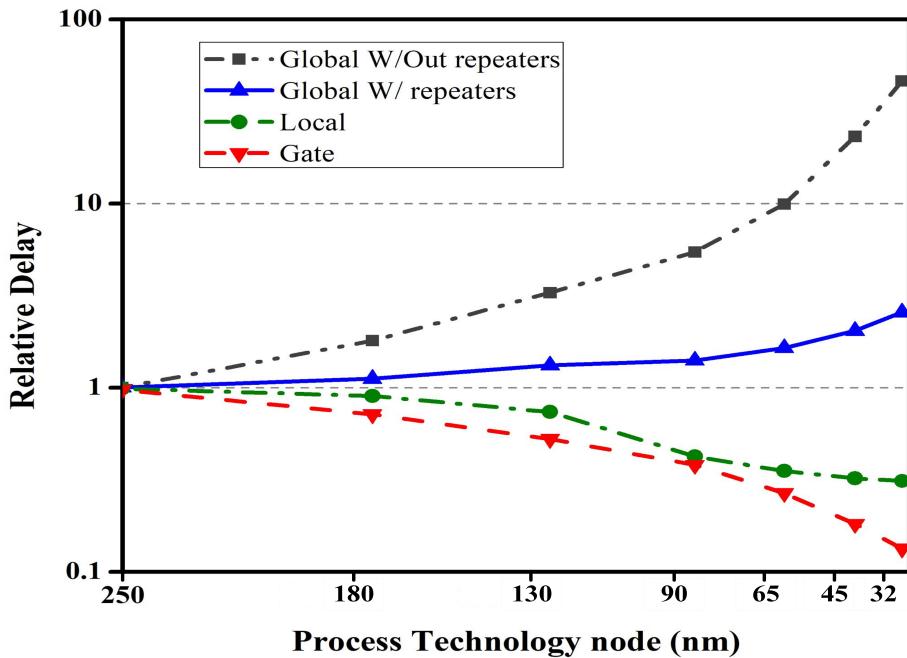

With the technology scaling the gate/transistor delay and wire delay of the local interconnects decreases, whereas the delay of the intermediate/global interconnects increases. Advanced scaling techniques such as the use of low K dielectric materials improves the delays of the local interconnect. However, with the scaling of every successive technology node below  $0.25 \mu\text{m}$ , the delays of intermediate/global interconnect become much worse than gate delays [1]. In addition, as compared to the local interconnect, the length of global interconnect is not scaled with technology leading to an increase in delays as these wires need to run across the entire chip. Thus, as compared to the gate delay and local interconnect delay the global interconnect delay becomes a limiting factor in determining the overall circuit performance in the present day VLSI chips. Global wiring among the functional blocks provides the distribution of clock/signal and delivers ground/power to all functions on an IC. Figure 1.2 illustrates the local and global interconnect delay in future generations. To reduce the delay in global wiring, the repeaters can be incorporated by compromising the power consumption and chip area.

In DSM VLSI regime, the speed of any electrical signal depends on two factors, namely the transistor gate delay and the propagation delay of interconnects. The major challenges in VLSI circuits are global interconnect delays and crosstalk noise between multiple interconnects. These signal integrity problems in interconnects decide the overall performance of VLSI circuits. For the iterative layout design of densely populated IC's accurate analytical models are needed to efficiently predict signal degradation due to propagation delay, crosstalk noise, and signal overshoot in the early design cycles [5]–[7]. The existing computer aided design (CAD) tools for signal integrity analysis are more time-consuming and inefficient. Hence, interconnect simulations suffer from a number of signal integrity issues which require sophisticated CAD tools for analysis. Computationally high-speed and accurate interconnect models are needed at the initial stages of an IC design for design optimization and post-layout verification, respectively. During the physical design, interconnect area, propagation delay, overshoot, power and crosstalk noise estimations are the main performance metrics. This thesis addresses the estimation of propagation delay and crosstalk noise in the mutually coupled on-chip interconnects.

Figure 1.2: On-chip interconnect delay across different technology nodes [1]

In the early phase, the gate capacitance of transistors dominated the interconnect parasitic capacitance, which makes use of the assumption of modeling of interconnects as short circuits. Later on, with technology scaling, the interconnect parasitic capacitance dominates the gate capacitance and interconnect was modeled as a lumped capacitance [8, 9]. With the further technology downscaling, inclusion of resistance effect in on-chip interconnect became mandatory for global interconnects which increases the accuracy. This results in introduction of lumped resistance-capacitance (RC) models for the performance analysis of on-chip interconnects [10, 11]. However, the lumped RC models are treated as the distributed RC model [5] for better accuracy. Currently, because of the high switching frequencies and the adoption of low resistive interconnect materials, the parasitic inductance plays an important role in the performance of on-chip interconnects. To estimate the performance of the interconnects accurately, they must be considered as transmission lines or as distributed resistance-inductance-capacitance (RLC) interconnect lines [12].

Initially, crosstalk noise estimation models considered only capacitive coupling [13, 14]. However, inductive-crosstalk effects should be included at current high-frequency operations for the inclusive analysis of coupling noise. At high frequencies, the transient crosstalk, i.e., the undesired effect of a signal transmitted on one line over another, is produced due to closely packed interconnects [15]–[17]. The propagation delay of the signal is strongly influenced by

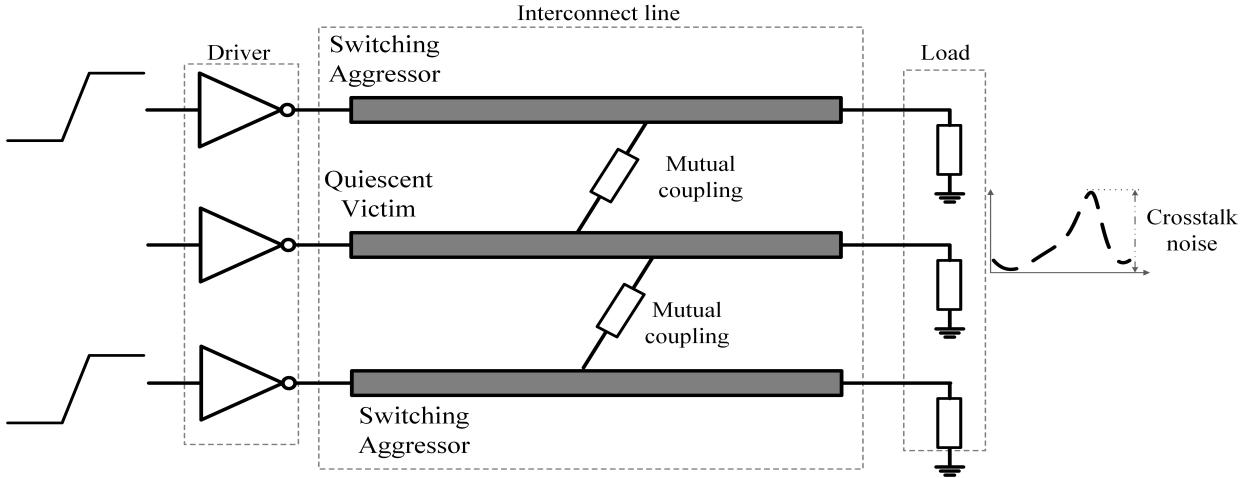

Figure 1.3: Crosstalk in closely placed interconnects

the crosstalk noise, which results in functional failure or circuit malfunction. The crosstalk between the coupled lines is considered to be dynamic and functional crosstalks, depending on the input switching transitions in the coupled interconnects. Dynamic crosstalk occurs when the adjacent lines are simultaneously switching either in-phase or out-phase. Whereas, the functional crosstalk appears as a voltage spike when the victim line is at quiescent while switching an aggressor line as shown on Figure 1.3. A change in propagation delay and logic value can be observed under dynamic and functional crosstalks, respectively. In addition, the crosstalk noise effects include ringing and signal overshoot/undershoot. Therefore, there is a need for an accurate estimation of performance parameters for designing high-performance on-chip interconnects incorporating the effect of crosstalk noise.

A noise model [18] was proposed for the analysis of noise effects in two coupled RLC lines, but it is limited to loosely coupled interconnect lines where coupling capacitance and mutual inductance are negligible as compared to ground capacitance and self-inductance, respectively. Similarly, another analytical model [19] was proposed for coupled on-chip RLC line, in which two lines were isolated. Further, each isolated line is approximated as a one-segment RLC  $\pi$ -circuit. The major limitation of this method is that it can be applied only to isolated lines with separated drivers. Agarwal et al. [20] proposed an analytical scheme to model crosstalk noise in the coupled RLC interconnects by considering the linear characteristics of CMOS (complementary metal oxide semiconductor) driver i.e., linear resistive driver. This model is further extended to a nonlinear CMOS driver considering  $\alpha$ -power law model to analyze dynamic crosstalk effects [21] and functional crosstalk effects [22] by Kaushik et al. The models that are purely limited to two coupled interconnect lines based on even-odd modes reported in [20]–[22]. Furthermore, only the ideal or lossless lines are considered for the transient analysis.

The modeling of CMOS driver based distributed RLC lines suffer from time/frequency domain conversion issue. This issue occurs because the CMOS driver is modeled in the time domain, whereas the partial differential equations (PDEs) are used to solve the transmission line (TL) model in the frequency domain. Therefore, many researchers [15], [20], [23] substitute the nonlinear CMOS driver with a linear resistive driver compromising the overall accuracy of the model. In the recent past, the TL equations in the time domain were solved using finite-difference time-domain (FDTD) method [24] to avoid the conversion problem.

## 1.2 On-chip interconnects in CMOS technology

CMOS is the most widely used technology for building of VLSI chips. In CMOS technology, transistors are fabricated in a doped silicon substrate, usually with a gate of polysilicon on the top of the oxide layer. Transistors can be connected to power, ground/clock lines, and a stack of metal layers [25]. Different metal layers are connected using Vias and the space between metal layers is filled with dielectric material.

### 1.2.1 Technology Scaling

The technology scaling reduces the dimensions of the MOSFET (Metal Oxide Semiconductor Field Effect Transistor) and associated interconnects, which enhances the performance and the component density per area. The constant electric field scaling scales down the dimensions of the MOSFETs by a factor of  $\frac{1}{S}$  and the resultant first order effects are given in Table 1.1. This kind of scaling increases the device density by a factor of  $S^2$  and decreases the gate delay and power dissipation by  $\frac{1}{S}$  and  $\frac{1}{S^2}$  factors, respectively [5]. Hence, the scaling of MOSFET dimensions increases the overall circuit performance.

The technology scaling poses major challenges to interconnects especially in high speed/performance ICs. As chip size grows larger and interconnect geometries are scaled, resistive, inductive and capacitive effects associated with the interconnects effects the performance of high-speed ICs in DSM regime.

Table 1.2 shows the ideal scaling of local interconnects, where all horizontal and vertical dimensions are reduced by the same factor [5]. Local interconnects length usually shrinks at the same rate of technology scaling. The other dimensions also shrink by the same factor of  $\frac{1}{S}$ .

Table 1.1: Scaling effects on MOS device

| Parameter                                                                                              | Scaling factor  |

|--------------------------------------------------------------------------------------------------------|-----------------|

| Channel Length ( $L_{ch}$ ), Gate oxide thickness ( $t_{ox}$ ), width ( $W$ ) and Voltage ( $V_{DD}$ ) | $\frac{1}{S}$   |

| Current per device ( $I_{DS}$ )                                                                        | $\frac{1}{S}$   |

| Gate capacitance ( $C_g$ )                                                                             | $\frac{1}{S}$   |

| Transistor ON resistance ( $R_g$ )                                                                     | 1               |

| Gate delay ( $\tau_g$ )                                                                                | $\frac{1}{S}$   |

| Device area ( $A$ )                                                                                    | $\frac{1}{S^2}$ |

| Power dissipation ( $P$ )                                                                              | $\frac{1}{S^2}$ |

The parasitics such as capacitance decrease by a factor of  $\frac{1}{S}$  and resistance increases by  $S$ . As a result, local interconnect delay remains unchanged in ideal scaling.

Table 1.2: Scaling of Local Interconnects

| Parameter                                                                                         | Scaling factor |

|---------------------------------------------------------------------------------------------------|----------------|

| Local interconnect width ( $w$ ), Substrate height ( $h$ ), Spacing ( $s$ ) and Thickness ( $t$ ) | $\frac{1}{S}$  |

| Local interconnect length ( $l$ )                                                                 | $\frac{1}{S}$  |

| Resistance ( $R$ )                                                                                | $S$            |

| Capacitance ( $C$ )                                                                               | $\frac{1}{S}$  |

| RC delay ( $\tau$ )                                                                               | 1              |

| Voltage drop ( $I \times R$ )                                                                     | 1              |

| Current density ( $J$ )                                                                           | $S$            |

Over the many years, scaling has become a problem of growing importance in case of intermediate/global interconnects. As the technology is scaled, the length of the intermediate/global interconnects increases instead of shrinking. This is because the chip area of each new technology generation keeps increasing to accommodate more functionalities and hence more components are needed to implement those extra functions. This causes an increase in intermediate/global interconnects lengths to connect all the devices.

Table 1.3 shows the ideal scaling effects of intermediate/global interconnects [5]. Scaling of the intermediate/global interconnects increases the delay in proportion to the wire length and wire resistance. Because intermediate/global interconnects length is dependent on the chip area ( $A_c$ ) and the length of the longest global interconnect is related to the chip area approximately

Table 1.3: Ideal scaling of Intermediate/Global Interconnects

| Parameter                                                                                                          | Scaling factor    |

|--------------------------------------------------------------------------------------------------------------------|-------------------|

| Intermediate/Global interconnect width ( $w$ ),<br>Substrate height ( $h$ ), Spacing ( $s$ ) and Thickness ( $t$ ) | $\frac{1}{S}$     |

| Intermediate/Global interconnect length ( $l_{gb}$ )                                                               | $S_C$             |

| Resistance ( $R_{gb}$ )                                                                                            | $S^2 \cdot S_C$   |

| Capacitance ( $C_{gb}$ )                                                                                           | $S_C$             |

| RC delay ( $\tau$ )                                                                                                | $S^2 \cdot S_C^2$ |

| Voltage drop ( $I \times R$ )                                                                                      | $S \cdot S_C$     |

by  $\frac{\sqrt{A_c}}{2}$  [4]. Hence, scaling of these interconnects will not shrink in the same proportion as that of transistor gate length.

In summary, technology scaling decreases the gate delay (transistor delay) and local interconnects delay whereas intermediate/global interconnects delay increases. Advanced techniques of scaling such as usage of low-dielectric-constant-insulator and weak scaling of line thickness improve the situation, so that interconnect delays nearly track the gate/transistor delays. However, intermediate/global interconnect delays become much worse than gate delays for technology nodes below  $0.25 \mu\text{m}$  as can be seen from Figure 1.2. Thus, the intermediate/-global interconnect delay becomes a limiting factor in determining the overall circuit performance in the present day VLSI chips.

### 1.2.2 ITRS Predictions

The ITRS 2012 [26] predictions on the future trend of interconnect dimensions, delay, technology nodes etc. are given in Table 1.4. The total length of on-chip interconnects increases linearly with technology down scaling and it will approach approximately  $16700 \frac{\text{m}}{\text{cm}^2}$  by 2027. In addition, the delay of intermediate and global interconnects will increase quadratically with technology and it will reach to 310 ns and 110 ns, respectively.

As per the ITRS 2012 [26] and 2013 [27], feature sizes of the devices are scaling down roughly at a rate of 0.7 in every two years, which results in the doubling of gate density, reduction of gate delay by 30% and reduction of energy per switching by 65%. Thus, scaling the transistor dimensions lead to improvements in both performance and cost.

Table 1.4: ITRS prediction on scaling trends[26, 27]

| Parameter                                              | Year | 2012         | 2015         | 2018         | 2021         | 2024         | 2027         |

|--------------------------------------------------------|------|--------------|--------------|--------------|--------------|--------------|--------------|

| <b>Technology None (nm)</b>                            |      | 36           | 25           | 18           | 12           | 9            | 6            |

| <b>Number of metal levels</b>                          |      | 12           | 13           | 14           | 15           | 15           | 16           |

| <b>Total interconnect length (m/cm<sup>2</sup>)</b>    |      | 3,125        | 4,762        | 6,667        | 9,434        | 13,333       | 16,779       |

| <b>Intermediate wiring pitch (nm)</b>                  |      | 64           | 42           | 30           | 21           | 15           | 12           |

| <b>Aspect Ratio (AR) of intermediate interconnects</b> |      | 1.9          | 1.9          | 2.0          | 2.1          | 2.1          | 2.2          |

| <b>Intermediate interconnects RC delay (ps)</b>        |      | 4,814        | 13,716       | 29,761       | 64,552       | 141,966      | 310,000      |

| <b>Global interconnect wire pitch (nm)</b>             |      | 96           | 63           | 45           | 32           | 23           | 17           |

| <b>Aspect Ratio (AR) of global interconnects</b>       |      | 2.34         | 2.34         | 2.34         | 2.34         | 2.34         | 2.40         |

| <b>Global interconnects RC delay (ps)</b>              |      | 1,528        | 4,005        | 9,127        | 21,542       | 44,064       | 110,000      |

| <b>Effective dielectric constant (k)</b>               |      | 2.8<br>- 3.2 | 2.5<br>- 3.0 | 2.4<br>- 2.8 | 2.1<br>- 2.5 | 1.8<br>- 2.3 | 1.6<br>- 2.0 |

| <b>Copper effective resistivity (μΩ-cm)</b>            |      | 4.53         | 5.58         | 6.7          | 8.51         | 12.91        | 14.06        |

| <b>Wafer diameter (mm)</b>                             |      | 300          | 450          | 450          | 450          | 450          | 450          |

The lengths of the local interconnect and transistor gate lengths scale down similarly, whereas intermediate/global interconnects tend to track the dimensions of a chip. Generally, in consecutive technology generations, the die area should decrease by 50% but advanced designs integrate more transistors and functionalities per chip, results in a requirement for more die area. Over the years, die area and total interconnect length has increased by approximately 13% and 6% per year, respectively, resulting in an overall increase of interconnect delay by approximately 120% [28]. More delay implies increased power consumption, signal attenuation, ringing effects etc. Hence, intermediate/global interconnects play a major role in determining the performance of the present-day ICs. In DSM VLSI designs the global interconnect lengths may run to several hundreds of meters.

## 1.3 Evolution of Interconnect Materials

The continuous growth in an IC technology leads to reduced device dimensions, increased complexity and larger chip sizes. Also, a tremendous increase in the demand for the IC's with component density and higher speed [29]. Initially, IC designers adopted Al metal as a VLSI interconnect due to its compatibility with silicon (Si). Later on, with the downscaling of device dimensions the reliability of Al interconnect decreased. In the recent past, Cu is considered as a interconnect material alternative to Al due to its high current density. Further, as the high frequency of operations are becoming more intense, researchers are forced to look for new and reliable materials such as optical [30], Graphene [31] material based interconnects in the near future.

### 1.3.1 Aluminum Interconnects

Recent IC's require a large number of closely separated wires that integrate the components on a single chip. To achieve lesser transit delays and higher packing densities, the multi-layer interconnections must be considered with the growing IC technology [32].

For several generations of semiconductor technology, Al has been considered to form metal interconnects due to its compatibility with Si and low resistivity. With the downscaling of device dimensions the current density increases. This has a negative impact on the reliability of IC's that is due to the formation of hillock and electromigration, which causes electrical shorts between consecutive levels of Al.

### 1.3.2 Cu as a substitute for Al Interconnect

With the advancement in technology, Al was unable to fulfil the demands due to its demerits. Thus, the researcher's lookout for promising options with lower electrical resistivity such as gold (Au), silver (Ag) and copper (Cu) as replacement of Al metal. Table 1.5 shows the resistivity of these potential metals.

Au has low resistivity than Al, but it shows larger resistance to electromigration. Major demerit is that gold establishes deep-levels in the bandgap due to the diffusion of gold in silicon and thus badly influence the electronic characteristic of the device. Similarly, Ag establishes deep-levels in the bandgap of silicon and diffuses in silicon dioxide ( $\text{SiO}_2$ ) consecutively due

Table 1.5: Resistivity of conductor materials [30]

| Material  | Thin-film resistivity<br>( $\mu\Omega$ cm) | Bulk resistivity<br>( $\mu\Omega$ cm) |

|-----------|--------------------------------------------|---------------------------------------|

| Al        | 2.7                                        | 2.65                                  |

| Au        | 4.1                                        | 2.4                                   |

| <b>Cu</b> | <b>2.1</b>                                 | <b>1.7</b>                            |

| Ag        | -                                          | 1.6                                   |

to its lower resistivity. Moreover, Ag exhibits a low melting point results in low resistance to electromigration. However, Cu with low resistivity, higher melting point compared to Al delivers better performance with respect to electromigration effects and stress. Today, Cu is broadly used on-chip interconnect material in advanced IC's.

### 1.3.3 Necessity of Future Interconnects

Further scaling down of interconnect dimensions have made surface scattering and grain boundary scattering more prominent, resulting in increased resistivity of Cu material [16]. In addition to this, the skin effect, electromigration effect, low thermal and electrical conductivity, small mean free path (MFP) and limited current density also degrade the performance of an IC [33]–[35]. Therefore, the requirements of new and reliable materials for IC interconnects has increased. In the recent times, graphene-based nanomaterials such as carbon nanotubes (CNTs) and graphene nanoribbons (GNRs) are considered as the most promising candidates proposed as a substitute for Cu interconnects in advanced VLSI circuits [36, 37].

#### 1.3.3.1 Carbon Nanotubes (CNTs)

CNTs are cylindrically rolled up single layered graphene sheets having diameters varying from 1 to 5 nm. CNTs with their outstanding thermal and electrical properties, such as high melting point (3800 K), higher thermal stability, large mean free paths and the maximum current density ( $10^{10}$  A/cm<sup>2</sup>), outperform the conventional Cu interconnect [38]. Based on the physical properties, carbon nanotubes are classified into two types: single-walled CNTs (SWCNTs) and multi-walled CNTs (MWCNTs) [39, 40]. The MWCNTs have few concentric shells of rolled up graphene sheets with their diameter ranging from few nanometers to tens of nanometers. Based on the chirality of graphene sheets, the SWCNT exhibits either metallic or semiconductor be-

haviour whereas the MWCNT exhibits only metallic behaviour [37]. Due to the large diameter and considering all the shells adequately connected to the metal contacts, MWCNTs have long electron MFPs and a great number of conducting channels compared to SWCNTs. Although the MWCNTs provide similar current carrying capability as SWCNTs, they are simpler to fabricate due to their greater control over the growth process [41].

#### 1.3.3.2 *Graphene Nanoribbons (GNRs)*

GNRs are strips of graphene layer with ultra-thin width. They are attracting many researchers as a powerful alternative material for next generation VLSI interconnects [42, 43]. Most of the electrical and physical properties of GNRs are identical to the CNTs. However, the advantage of GNRs over CNTs is that the fabrication of both interconnects and transistors can be done on the same graphene layer [44]. Based on the number of stacked layers of graphene, GNRs are categorized into two types: single-layer GNRs (SLGNRs) and multi-layered GNRs (MLGNRs). Compared to SLGNRs, MLGNRs are mostly preferred as interconnect material because of the easy fabrication process and lower resistivity. However, the major demerit is that the fabricated MLGNRs show a little edge roughness [45, 46], resulting in decreased electron MFP that considerably reduces the conductance of MLGNRs.

## 1.4 Motivation

In the early days of very large scale integration design, the relatively low integration density and low frequency of operation have suppressed the crosstalk-induced signal integrity effects. However, owing to the technology scaling in the submicron regime, there were significant changes in the electrical characteristics and overall structure of interconnects [47, 48]. Thus, the overall performance and robustness of an IC mainly depend on the interconnect lines and the electrical behavior of the interconnect model is in turn influenced by the line parasitic elements. Therefore, there is a need for accurate models to analyze the crosstalk-induced signal integrity effects in the driver-interconnect-load (DIL) system.

To analyze the signal integrity issues, such as functional crosstalk and dynamic crosstalk effects, there are several methods, such as analytical and SPICE solutions have been proposed to model a DIL system as reported in [22]. However, in the present state of the art, most of the researchers rigorously studied the crosstalk effects based on the conventional FDTD

algorithm due to its accuracy [24]. The conventional FDTD model is a significant numerical model for solving electromagnetic (EM) problems and partial differential equations. However, the conventional FDTD method with better accuracy causes numerical dispersion error during the propagation along the discretization [49, 50], leading to discrepancy in the results. Hence, there is an extensive requirement of a novel method with an advantage in numerical dispersion properties.

## 1.5 Problem statement

To model and analyze the crosstalk noise effects in DSM VLSI interconnects, in the recent state of the art, most of the researchers used the conventional FDTD algorithm due to its accuracy. However, the conventional FDTD model with better accuracy causes a numerical dispersion error during the propagation along the discretization, leading to discrepancy in the results.

## 1.6 Objectives

The objectives of the work are:

1. A novel mathematical model with an added advantage in numerical dispersion properties need to be proposed for achieving better accuracy with respect to present state of the art.

2. To analyze the effect on propagation delay and crosstalk noise by varying coupling parasitics in resistive driven coupled Cu interconnects using the proposed method.

3. To analyze the crosstalk noise effects in CMOS driven coupled Cu interconnects based on the proposed model.

4. To analyze the inclusive crosstalk effects in CMOS driven multiple coupled MWCNT interconnects using the proposed model.

## 1.7 Organization of Work

The thesis is organized into six chapters. The following section gives a summary of chapters.

Chapter I presents a brief introduction to the importance of VLSI interconnects, various delay and crosstalk models. The motivation behind this research work and the thesis objectives and contributions are also presented. In the end, the organisation of the thesis is elaborated.

Chapter II reviews the recent related state of the arts available in the literature and a brief outline of the thesis is also presented.

Chapter III explains the proposed MRTD model for signal integrity analysis of coupled copper interconnects driven by the linear resistive driver at the 130-nm technology node. The proposed model captures the behaviour of propagation delay and peak crosstalk noise on victim line against coupling parasitics ( $M_{12}$  and  $C_{12}$ ), which is in close agreement with those of HSPICE simulation results and dominates over the FDTD method.

In chapter IV, the proposed MRTD model is extended to non-linear CMOS driver for the analysis of crosstalk noise in the coupled copper interconnects at the 32-nm technology node. The non-linear characteristics of the CMOS gate are analyzed using the nth-power law model. The robustness of the model is tested for the peak noise voltage and peak noise timing at different input transition times for two coupled interconnects. Further, the model is extended to three mutually coupled interconnect lines. Moreover, for the transient analysis, the MRTD method is more time efficient than HSPICE.

Chapter V deals with an advanced interconnect material, i.e., multi-walled carbon nanotube (MWCNT) interconnect. The proposed MRTD model is used for the inclusive crosstalk noise analysis of the CMOS-gate driven coupled MWCNT interconnects at 32 nm technology node. The  $n$ -th-power law model is used to model the non-linear CMOS driver. The robustness of the model is validated by testing it for dynamic crosstalk effects over different capacitive load ( $C_L$ ) values. Then, the proposed model is extended to three mutually coupled MWCNT interconnects and the same is validated for different input switching modes. Furthermore, the validation of the proposed model with future selective validation (FSV) proves its accuracy and efficiency for analyzing the crosstalk effects in mutually coupled MWCNT interconnects.

The conclusions and future scope of the thesis are presented in Chapter VI.

# Chapter 2

## Literature Survey

This chapter provides the literature on interconnect parasitic extraction methods and different modeling approaches for analyzing delay and noise in on-chip interconnects. The recent modeling techniques based on analytical and numerical methods are discussed.

### 2.1 Introduction

Interconnects are the physical links between electrical devices in ICs, printed circuit boards (PCB), electrical packages, multiple circuit blocks, backplanes in an electronic system. In VLSI, interconnect is a connecting path, usually a metal (Al/Cu) line, that joins different points in the circuit. Whenever any signal propagates through the circuit, interconnect responds in such a way that signal integrity suffers. The interconnect responds against the propagation of any signal in terms of delay, noise, reflection and these depend on many factors which can be classified into two groups. One group includes the factors associated with physical issues such as interconnect dimensions and its material. Another group consists of factors related to signal dependent issues such as the signal's amplitude and transition time. Interconnects behave as short circuit at low frequencies while at higher frequencies they behave as transmission lines (TLs). At higher frequencies, the interconnects are more responsible for majority of the signal degradation effects such as distortion, ringing, attenuation, signal delay, and crosstalk.

## 2.2 Extraction of interconnect electrical parameters

The primary requirement for interconnect modeling is mapping the physical parameters of the interconnect such as cross-sectional dimension, dielectric, length, and metal properties into relevant electrical parameters (R, L, G, C per unit length (p.u.l)). This process is called as parasitic extraction of interconnects. Extraction of interconnect electrical parameters using physical parameters can be done in two ways. One way makes use of analytical expressions developed by Golzar et al. [51]. Another way for finding per unit length electrical parameters is using 2-D field solvers, 2.5-D field solvers and 3-D field solvers [52, 53]. These field solvers provide good accuracy as compared to the analytical expressions at the expense of computational complexity.

### 2.2.1 Analytical Capacitance Extraction

In the past, there are comparatively few analytical models available for the capacitance extraction. The most popular model presented in [54] estimates the ground and coupling capacitances. The formulae presented in [54] have an accuracy of 10-15% when compared with the system level performance simulators [55]. In addition, a new model [56] includes inter-layer (or crossover) capacitance evaluation and achieves 5% error as compared to numerical field solvers [55].

It is essential to figure out the advantages and disadvantages associated with the use of analytical capacitance models. The main advantage is that the estimation of fast capacitance due to their closed-form nature. However, with technology scaling, the accuracy of closed-form equations becomes poor. Also, these expressions are restricted to a small set of structures. In these closed-form expressions, the numerical coefficients are retrieved by adopting the least-mean-squares-errors approach fitting from numerical models or experimental results that also contain errors. Although the accuracy is good still these models cannot be compared with field solvers extractions.

To compute the efficient capacitance and inductance of the interconnect segment, a powerful three-dimensional (3-D) field solver tools were developed at Massachusetts Institute of Technology (MIT) namely, FastCap [57] and FastHenry [58]. FastCap is used for the extraction of 3-D capacitance that calculates ground capacitance and coupling capacitance for ideal conductors of arbitrary shape, size, and orientation embedded in arbitrary dielectric regions. Similarly, FastHenry is used for the extraction of 3-D inductance that calculates self and mutual inductances and resistances between conductors of arbitrary shape.

### 2.2.2 FastCap

The field solver tool, FastCap, is particularly suitable to solve Maxwell's equations. This software helps users to reduce complicated structures to electromagnetically equivalent ones in terms of capacitive elements. In the particular case, this equivalence is valid up to a frequency bound of the harmonic content of the signals involved. Usually, this limitation is referred to as the Quasi-Static approximation against the full-wave approach. In the field solvers, the first distinction is observed at the dimensions of the geometries based on extraction. In the literature, there exist three levels of parasitic extractors as follows:

*2-D Extraction:* In this process, the effect of lateral capacitance along the wire is assumed to be uniform. The capacitance p.u.l. matrices are calculated by modeling the wires with infinite length along the 3-D.

*2.5-D Extraction:* In this process, a combination of two orthogonal 2-D structures are considered to model the 3-D effects. Once each section is transferred to a 2-D solver, the corresponding results are combined based on matrix operations.

*3-D Extraction:* This solver can calculate the ground and coupling capacitances of a set of 3-D structures sunk in a dielectric. The open source software, FastCap, belongs to this category.

To summarize, FastCap offers an excellent accuracy and is applicable for a wide range of structures as compared to analytical models. But the accuracy comes with a price of higher computation time and more hardware.

### 2.2.3 FastHenry

The FastHenry tool is developed for the extraction of 3-D inductance that calculates self and mutual inductances, conductance, and resistances between conductors of arbitrary shape. Rather than the rectangular panels, geometries of the conductor are represented as linear segments connecting endpoint nodes. Segments and nodes are assigned to the input file in the general form.

The fast multipole method (FMM) [59] was initially developed for the problems of particle simulation. This is used with recursive methods to solve the dense integral equation matrices resulting from the Laplace expressions. The tools for parameter extraction like FastCap [60]

and FastHenry [61] adopts the FMM for accelerating the dense matrix-vector products required by a recursive solver.

The freely available FastCap and FastHenry 3-D field solvers are accurate and powerful tools for VLSI interconnect modeling, simulation, and parasitic extraction. However, their application is restricted to simple structures and layouts, because layout extraction interface or non-commercial graphical modeling to these tools are currently not available, and input model files must be developed manually.

## 2.2.4 W-Model and TL Parameters Extractor

Another important ECAD (Electrical Computer Aided Design) tool, Avant Star-HSPICE [62] is used to extract electrical parameters and to perform electrical simulations. This tool typically computes the accuracy of the electrical timing simulator in two ways:

### 2.2.4.1 *Field Solver*

It is based on the upgraded version of the filament approach (for extraction of inductance) and boundary-element method (BEM) (for extraction of capacitance). These models are also included in Avant Raphael [63], a commercial EM field-solver, RLGC matrices are obtained from a quasi-static analysis, in which TLs support only pure transverse electromagnetic (TEM) waves. Arbitrary polygonal shaped conductors embedded in a vertically multilayered medium, with various viable configurations of meshes and ground planes can be simulated with this software. Complete verification of this field-solver is presented in [64].

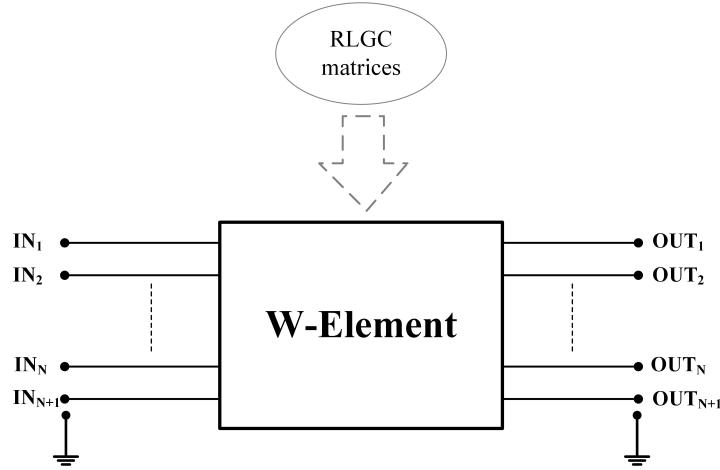

### 2.2.4.2 *W-Element*

It is one of the HSPICE transmission line models, used to simulate simple lossless lines as well as lossy coupled lines with better accuracy and efficiency. The model can be applied to non-uniform and uniform TLs that are represented with ad-hoc approaches in order to obtain the transfer function. The W-element with  $(N + 1)$  ports are specified with  $N$  number of inputs and outputs, and two reference terminals is illustrated in Figure 2.1. There is no limit on the number of coupled conductors. The main limitation of the W-element model is it can work only for symmetric RLGC matrices per unit length.

Figure 2.1: The star-HSPICE W-Element method

The advantages of HSPICE field solver are mainly represented by reduced simulation time and more accuracy when compared to other 3-D parameter extractors. Additionally, with just one W-element model tool, a complete characterization of RLGC can be retrieved and that can be imported easily into more complex HSPICE netlists. This is the motivation for using HSPICE field solver for extraction of parasitics in this research work.

## 2.3 Various interconnect models

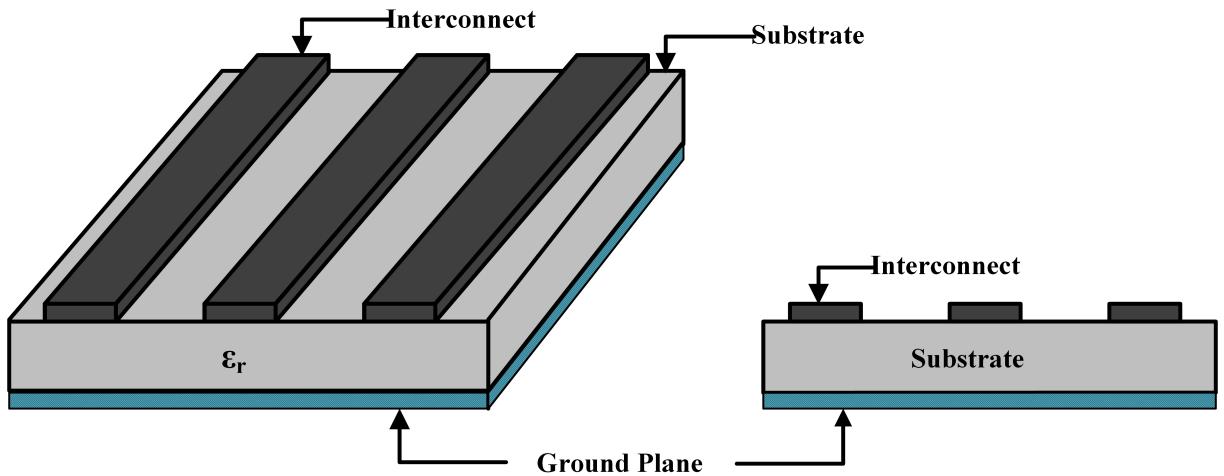

Figure 2.2: 3-D and cross sectional view of an interconnect structure