# **SOME INVESTIGATIONS ON HIGH SPEED SERIAL INPUT OUTPUT CIRCUIT STRATEGIES FOR BACKPLANE CHANNELS**

*Submitted in partial fulfilment of the requirements*

*for the award of degree of*

**DOCTOR OF PHILOSOPHY**

by

**D PAVAN KUMAR SHARMA**

**(Roll No: 701248)**

Supervisor:

**DR P.SREEHARI RAO**

Associate Professor

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

TELANGANA STATE-506004, INDIA

2019

## **Dedicated to**

I dedicate this thesis to my mother, **Annamaraju Shakunthala**, for her limitless love,prayers and blessings without which I would never stand here, to my father ,**Devulapalli Rajendra Prasad**, for standing by me during my difficult times and my Dear wife **Devulapalli Lakshmi Kalyani** and two precious gifts from almighty, **Snigdha Sharma** and **Keshav Sharma**

# DECLARATION

This is to certify that the work presented in this thesis entitled "**Some Investigations on High Speed Serial Input Output Circuit Strategies for Backplane Channels**" is a bonafide work done by me under supervision of **Dr. P Sreehari Rao**, Professor, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my words and where others' idea or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

D Pavan Kumar Sharma

(Roll No: 701248)

Date:

**DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**TELANGANA STATE-506004, INDIA**

## **CERTIFICATE**

This is to certify that the thesis entitled "**Some Investigations on High Speed Serial Input Output Circuit Strategies for Backplane Channels**", which is being submitted by **Mr . D Pavan Kumar Sharma (Roll no:701248)**, in partial fulfillment for the award of the degree of Doctor of Philosophy to the Department of Electronics and Communication Engineering of National Institute of Technology, Warangal, is a record of bonafied research work carried out by him under my supervision and has not been submitted elsewhere for any degree.

Dr. .Sreehari Rao

(Supervisor)

Associate Professor

Department of E.C.E

N.I.T.Warangal

# ACKNOWLEDGEMENTS

The journey of thousand miles begins always with a single step. I am very fortunate to have company of many kind hearted people in this wonderful journey and sometimes rusty journey without acknowledging them I felt the thesis is in-complete.

I would like to first thank my supervisor Dr.P. Sreehari Rao for his in-depth knowledge in the field of Analog and Mixed Signal Design. His patience and ability to provide insight into designs amazes me. Thank you sir, for introducing me to field of High Speed Serial Interfaces.

I would like to thank Doctoral Scrutiny Committee members; Prof. Dr. N.Bheema Rao(Chairman of D.S.C and Head of the Department), Prof. Dr. J.V Ramana Murthy, Prof. Dr. N. Vishwanathan for their constant encouragement and guidance, which has helped to improve the research work.

I would like to thank all my friends at Mixed Signal Design Lab for standing by me during the learning process and making it a wonderful experience. I must thank all the past and present colleagues Dr. Mudasir Bashir, M.A Mushahhid Majeed, Ravi Chandra, Pavan N, Baba Fayaz D, Shashank N, Subba Reddy S, Bayapu Reddy N, Vasu Bevara, Srikar V, Santhosh V, Ravi,Sireesha B, Richa Agarwal, Sridhar Reedy P,Manoja, Pradeep, Nikhil Sawarkar, Debashish Diwedy, Anil P, Anil B, Basha,M-Tech VLSI-SD (Batches of 2011-2013,2012-2014,2013-2015,2014-2016,2015-2018,2016-2019,2017-2019,2018-2020,2019-2021).

I wish to thank my friends Dr. M.Rajinth Kumar, Dr. B. Shravan kumar, Kiran D,Shashank R, Roshan B and Sunil Kumar N for their selfless love and jovial nature.

I would also like to profoundly thank the Department of Information Technology, Ministry of Information Technology, Government of India for providing us the resources and related software's at the Mixed Signal Design Lab under Special Manpower Development Program Chip to System for VLSI design and related software (SMDP-C2S).

Finally, I would like to thank my parents for their unconditional love and sacrifices for supporting me to follow academic goals. I would like to thank my Dear wife and sweetheart, D. Lakshmi Kalyani for her patiently listening to me and bearing me all these years in addition to managing kids, the blessings from almighty Snigdha Sharma and Keshav Sharma during my absence. Their self-sacrifices, unconditional love and encouragement has been the source of my strength and I shall be indebted always.

# ABSTRACT

The technology scaling has increased the computational efficiency of on-chip devices while approaching almost the transistor transition frequency ( $f_T$ ) on the data rate. However, this advantage is now constrained by the transfer medium which consists mostly of traces of wires on printed circuit board (PCB) of backplane channel. The high-speed serial links consists of transmitter, receiver, Phase Locked Loop (PLL), clock data recovery circuit and the channel. The channel or backplane consists of various materials such as line card and backplane trace and vias. The bandwidth required to transfer the data at high-speed can be intra-chip or inter-chip (high-speed serial link) depending upon the applications, such as server access across internet, display devices and gaming consoles, which is limited by dielectric loss, skin effect and impedance mismatches. The problems associated with high data transfer rate are conventionally addressed by employing parallel channels and logic duplication. However, both these options increase the pin count simultaneously increasing the overall power consumption which needs to be minimized for efficient data transfer. There is a need to transfer data at a very high rate (i.e.,  $> 2\text{GS/s}$ ) through single channel meeting constraints such as minimum power consumption, reflection loss, channel attenuation in addition to the errors induced by clock jitter and skew variations. This makes the design of high-speed serial link Input Output (I/O) for backplane channels a challenging field of research. In this thesis an attempt is made to develop circuit strategies for clock generation, clock recovery, on-die termination and equalization suitable for data-transfer at high speeds across backplane channels.

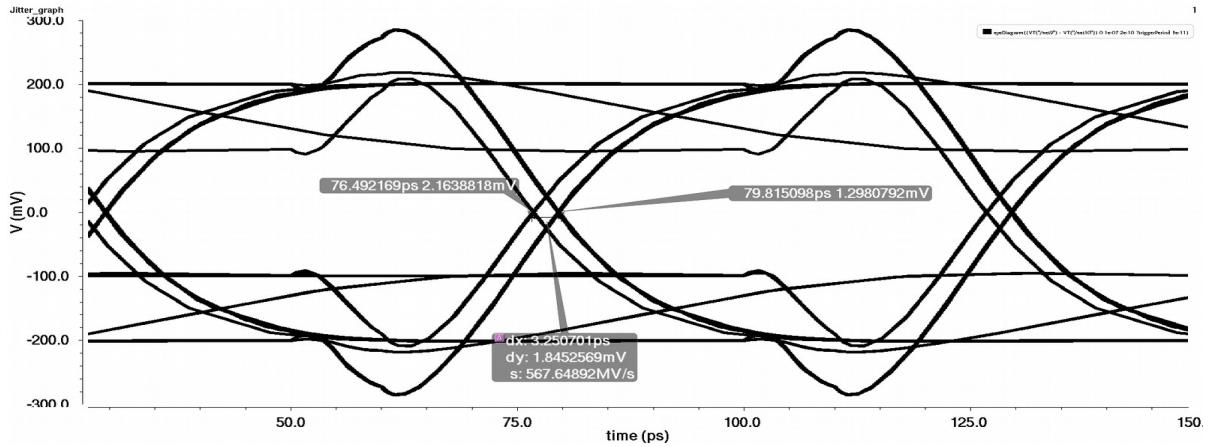

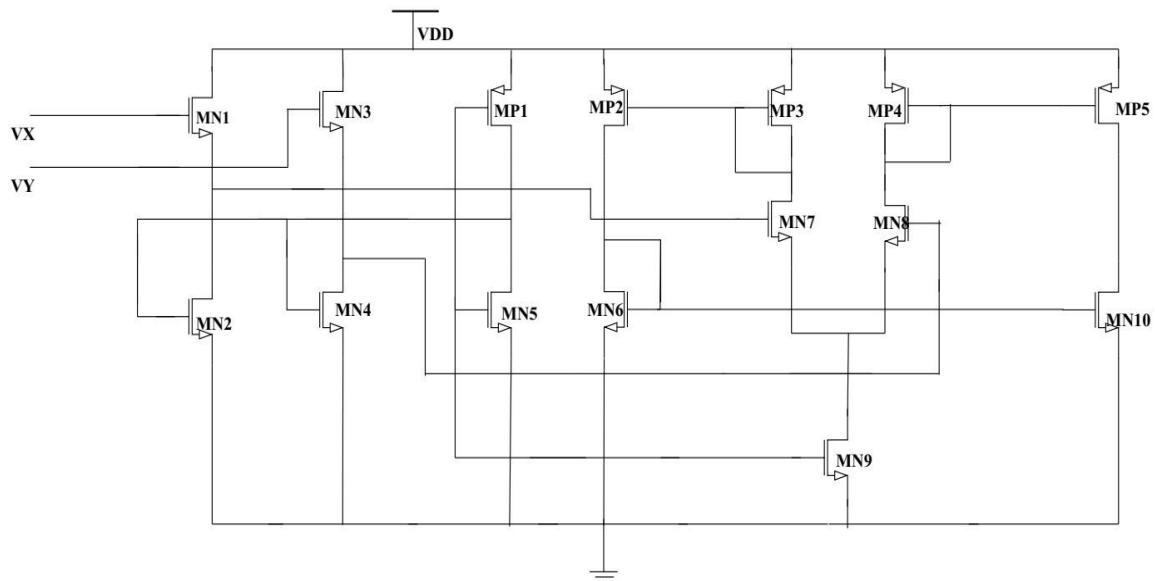

Equalization and termination matching can be easily achieved in feed forward equalizer with current mode logic(CML). However it suffers from poor efficiency, hence an open drain CML architecture is chosen with the termination implemented using cross coupled transistors minimizing power consumption. The designed on die termination is used to drive data across a 32inch backplane at 10Gb/s with swing of  $0.6\text{V}_{\text{p-p}}$  and efficiency of  $0.603\text{pJ/bit}$  and generate random jitter of  $3.25\text{ps}$  which meets the jitter and swing specifications of 10BaseKR standard. This design achieves better performance by striking a tradeoff between power consumption of  $0.6\text{mW}$  and jitter of  $3.25\text{ps}$  on competing with state of art literature.

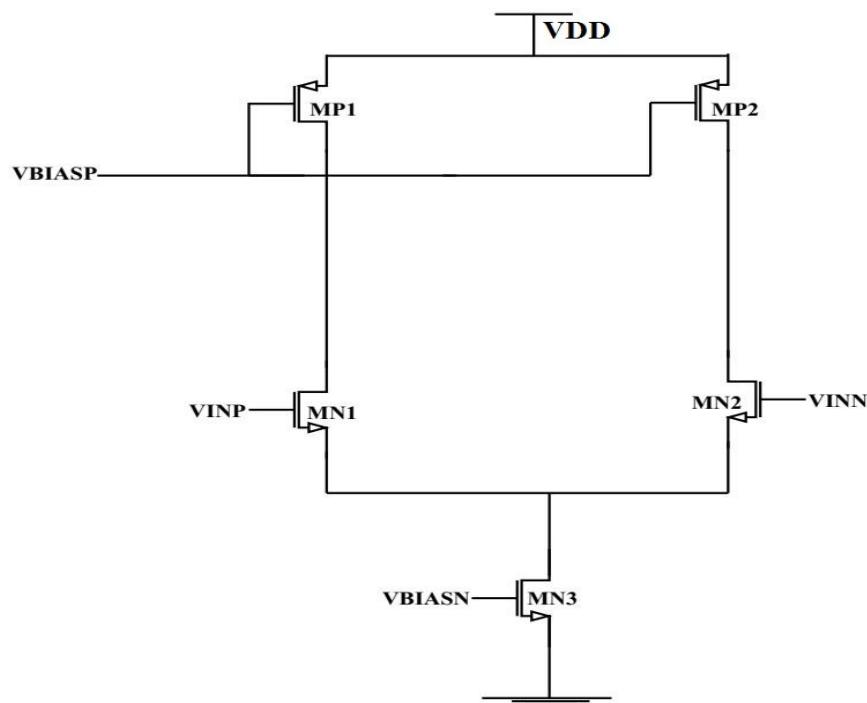

Comparator constitutes an important subsystem of the receiver corresponding to high speed serial data link. The receiver driver is primarily affected by the bit error rate and input referred noise of the comparator. Noise fed back(kick back noise) associated with regenerative comparators demands significant power without which eye opening is constrained leading to poor performance against noise. Hence, a gain boosted cascode amplifier is added to the cross coupled regenerative pair which further increases the output impedance which in turn decreases the input referred noise. This results in reduction of the output impedance of the pre-amplifier stage of the designed circuit. The designed gain boosted dynamic comparator has resolving capability of 5mV in 0.133ns. The gain boosted comparator has kick back noise of  $29\mu\text{V}$  with input referred noise of 1.75mV.

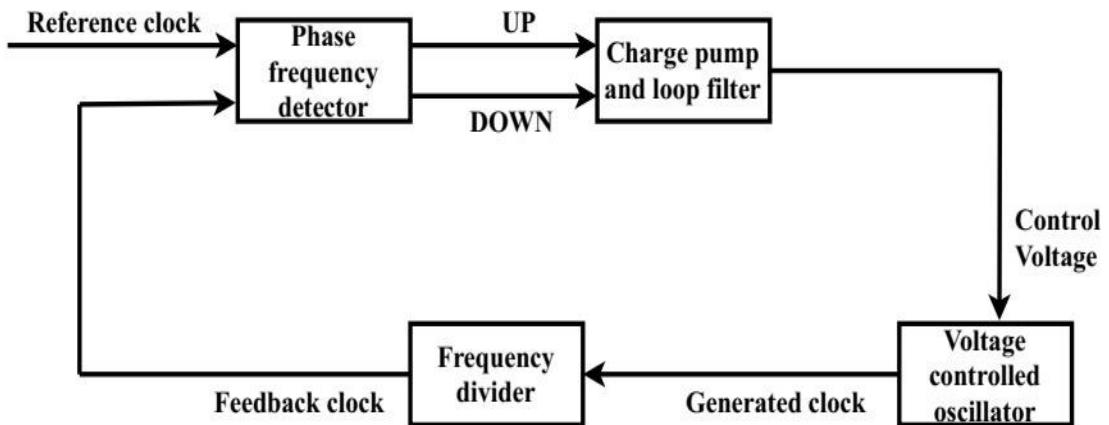

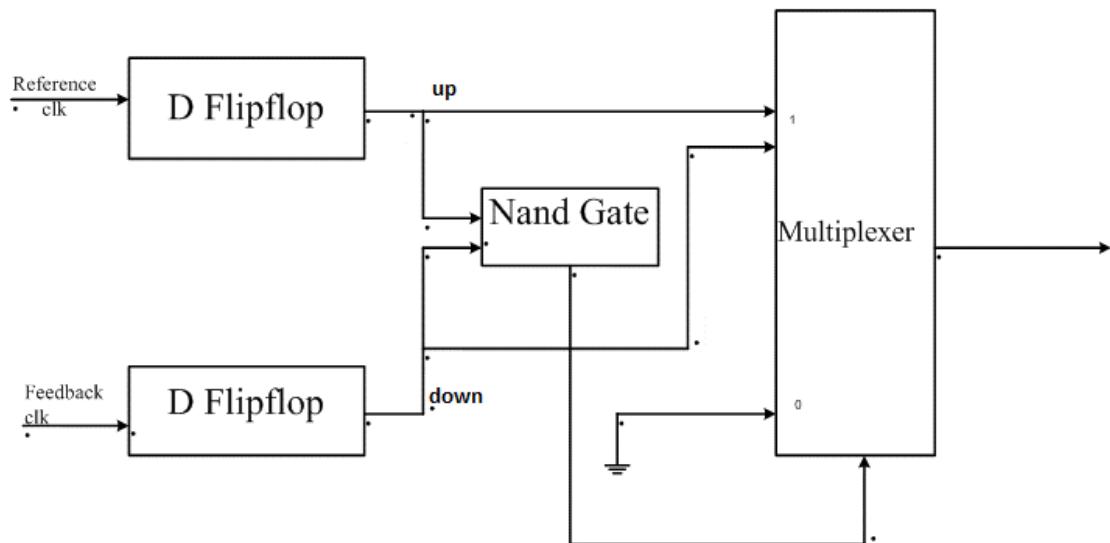

Serial data link operating at high speed require high frequency clock. The jitter associated with clock needs to comply with chosen 10base KR standard. When phase locked loop is employed in clock and data recovery circuitry, the initial phase acquisition loop needs to have a minimum phase error which is mainly dependent on minimum phase difference that can be detected by the phase detector. When reference less phase locked loop is used, the feedback clock transitions are to be in synchronous with data. A modified phase detector is presented to reduce the effects of phase error variation of the recovered clock. The modified phase detector has a mux which increases the minimum resettable delay in the feedback path. The addition of multiplexer increases the minimum width of up and down signals from the phase detector. The designed phase locked loop has a phase noise of  $-114\text{dBc/Hz}$  at an offset of 1MHz with power consumption of 6.64mW. It exhibits better FOM of -192.4 as compared to that of counterpart cited in the literature[-185] T.H Lee et .al.

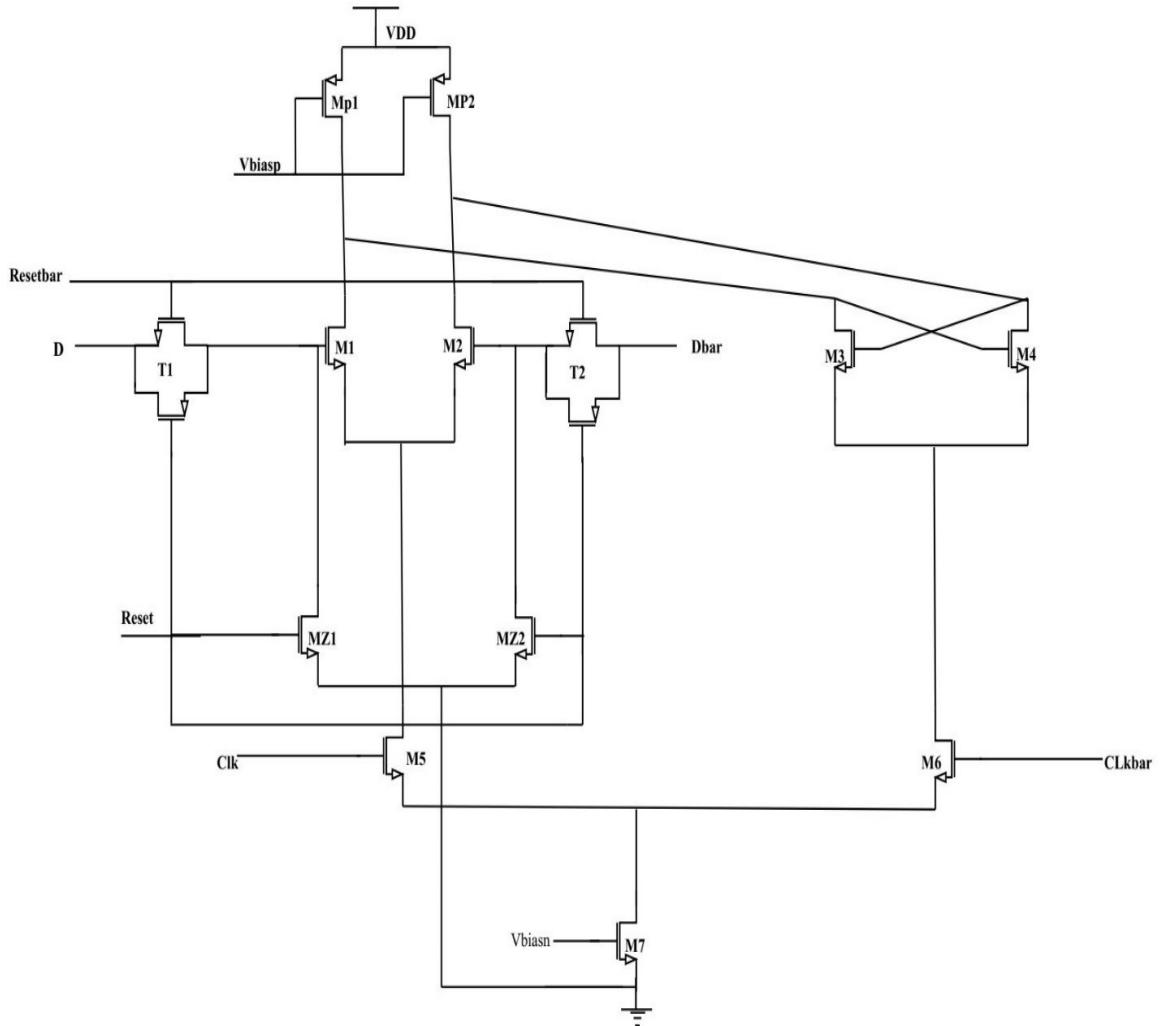

A clock and data recovery circuit is presented that employs modified dual loop architecture. The proposed circuit employs a asynchronous input latch signal in addition to clock which aids to latch the input data. The main advantage of the modified latch is that the regeneration phase begins immediately after the sampling phase. The designed clock and data recovery circuit has recovered clock jitter of 4.2ps with power consumption of 27mW which is lower than the state of art cited in literature.

# Contents

|                                                                                                                  |             |

|------------------------------------------------------------------------------------------------------------------|-------------|

| <b>Acknowledgements</b>                                                                                          | <b>iv</b>   |

| <b>Abstract</b>                                                                                                  | <b>vi</b>   |

| <b>List of Figures</b>                                                                                           | <b>x</b>    |

| <b>List of Tables</b>                                                                                            | <b>xii</b>  |

| <b>List of Abbreviations</b>                                                                                     | <b>xiii</b> |

| <b>List of Symbols</b>                                                                                           | <b>xv</b>   |

| <b>1 Introduction</b>                                                                                            | <b>1</b>    |

| 1.1 Motivation.....                                                                                              | 1           |

| 1.2 Backplane channel.....                                                                                       | 2           |

| 1.2.1 Inter Symbol Interference.....                                                                             | 2           |

| 1.3 Organization of Thesis.....                                                                                  | 3           |

| <b>2 Literature Survey</b>                                                                                       | <b>4</b>    |

| 2.1 Introduction.....                                                                                            | 5           |

| 2.2 On Die Termination.....                                                                                      | 14          |

| 2.3 Dynamic Comparator.....                                                                                      | 16          |

| 2.4 Phase Locked Loop.....                                                                                       | 17          |

| 2.5 Clock and Data Recovery Circuit.....                                                                         | 22          |

| <b>3. 0.603pJ/bit On-die Termination Using Current Mode Logic<br/>in CMOS 130nm For 10Gb/s Backplane channel</b> | <b>25</b>   |

| 3.1 Introduction.....                                                                                            | 25          |

| 3.2 Circuit Operation.....                                                                                       | 26          |

| 3.3 Conclusion.....                                                                                              | 29          |

| <b>4 A Low Input Referred Noise Dynamic Comparator for</b>                                                       |             |

|                                                                                                        |           |

|--------------------------------------------------------------------------------------------------------|-----------|

| <b>High Speed Application</b>                                                                          | <b>30</b> |

| 4.1 Introduction.....                                                                                  | 30        |

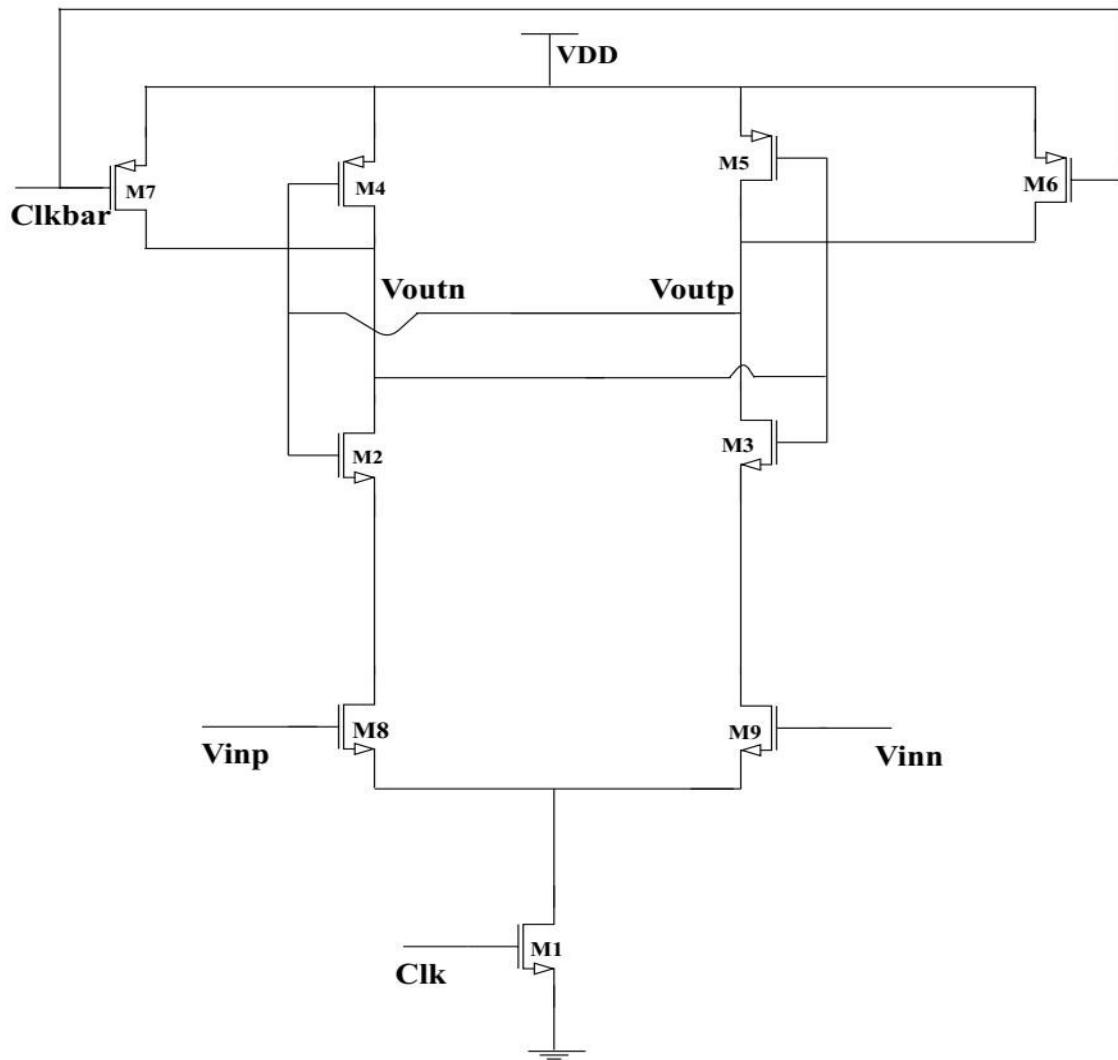

| 4.2 Conventional Dynamic Comparator.....                                                               | 30        |

| 4.3 Conventional Double Tail Comparator.....                                                           | 32        |

| 4.3.1 Operation.....                                                                                   | 30        |

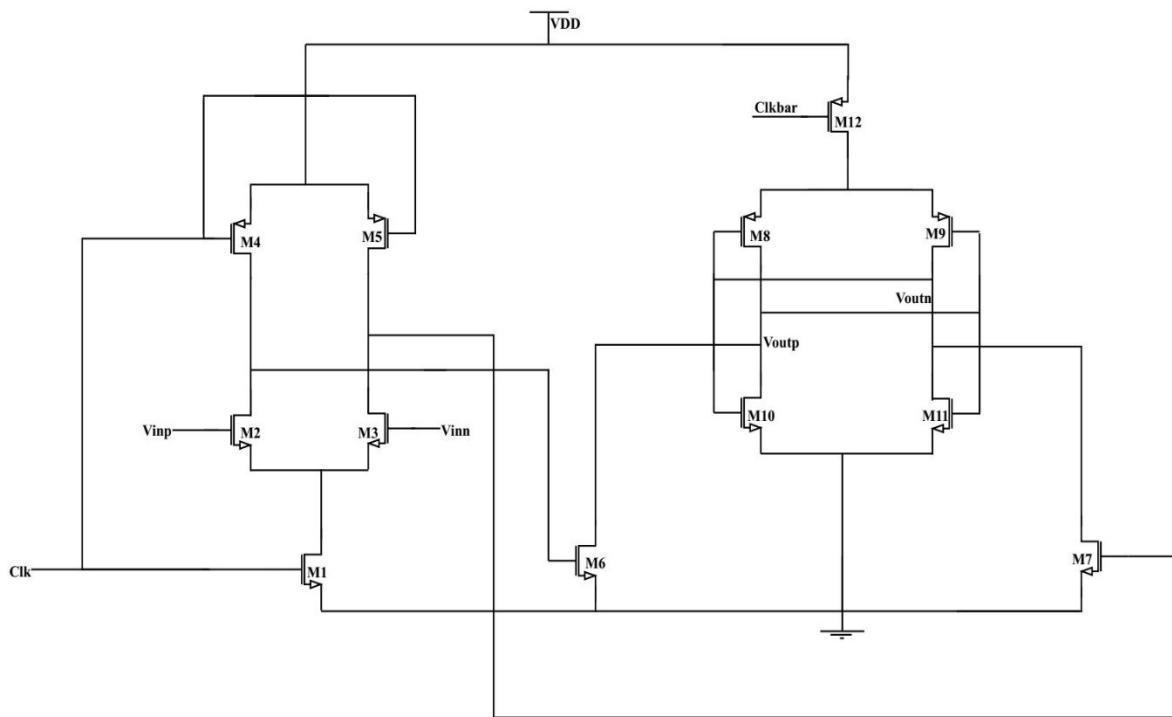

| 4.4 Double Regenerative Double Tail Comparator.....                                                    | 33        |

| 4.4.1 Operation.....                                                                                   | 33        |

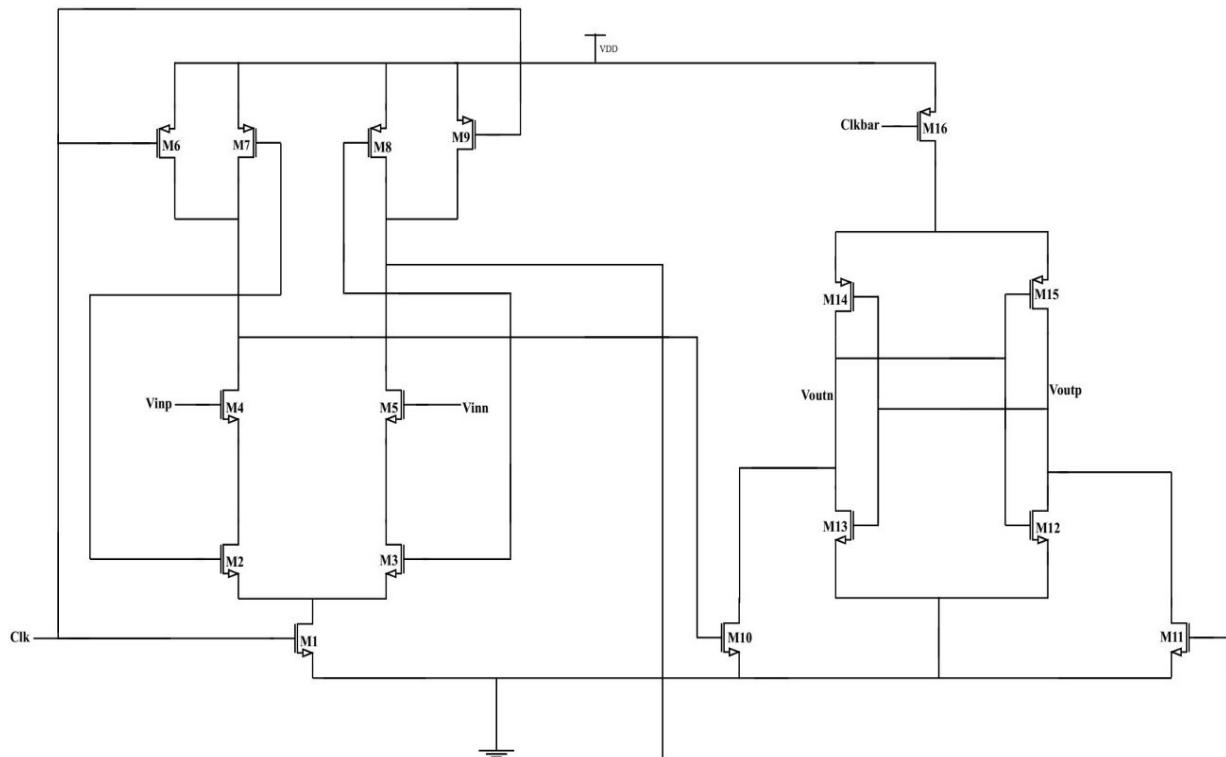

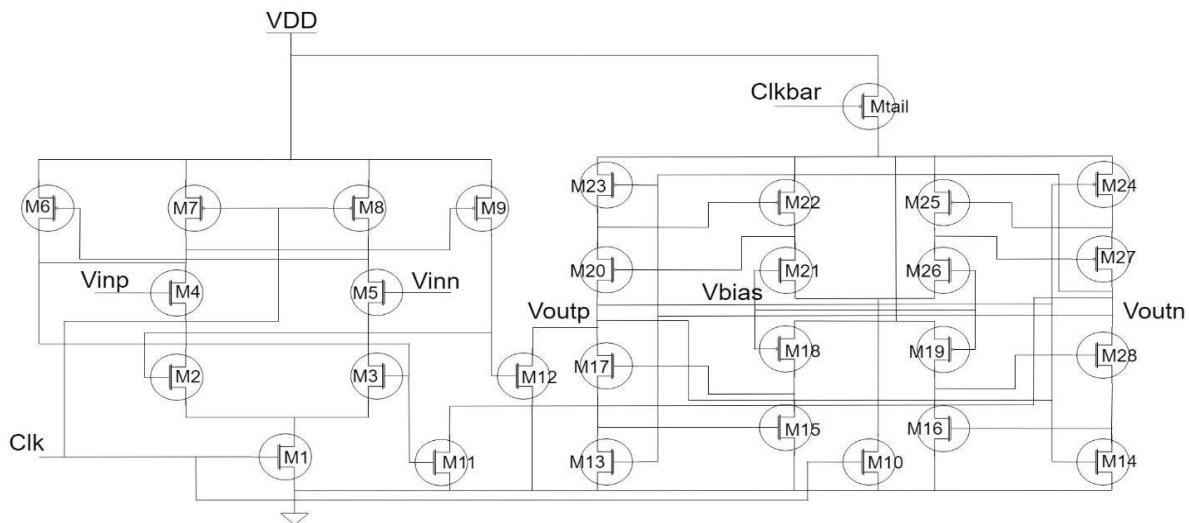

| 4.5 Proposed Regenerative Dynamic Comparator.....                                                      | 35        |

| 4.5.1 Operation.....                                                                                   | 35        |

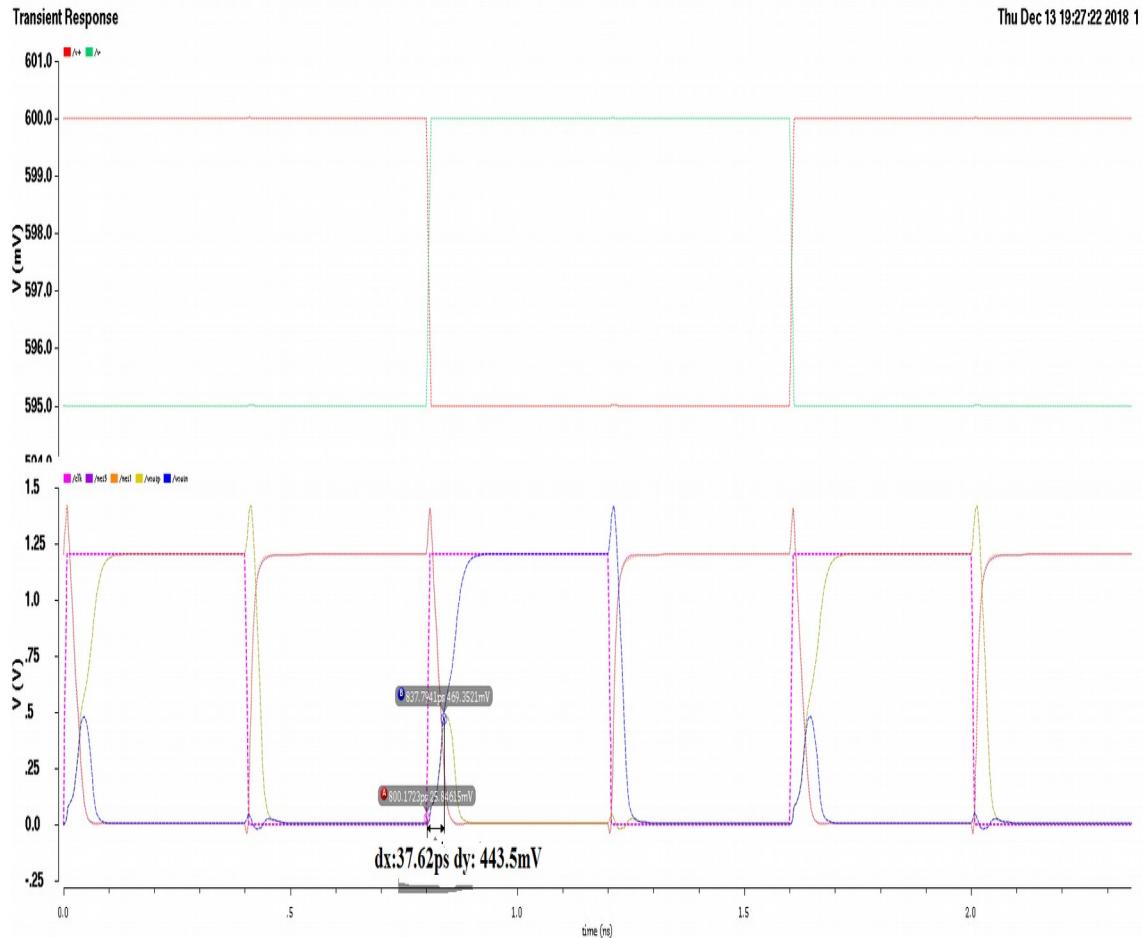

| 4.6 Results and Discussion.....                                                                        | 38        |

| 4.7 Conclusion.....                                                                                    | 40        |

| <b>5 Clock Generation and Recovery Circuits in High Speed Serial Links</b>                             | <b>41</b> |

| 5.1 Introduction.....                                                                                  | 41        |

| 5.1.1 A Low Jitter Phase Locked Loop for High Speed Serial Interfaces.....                             | 41        |

| 5.1.1.1 Phase Locked Loop.....                                                                         | 42        |

| 5.1.1.2 Modified Phase Frequency Detector.....                                                         | 42        |

| 5.1.1.3 Conclusion.....                                                                                | 49        |

| 5.1.2 A 10Gb/s Clock and Recovery Circuit for Backplane Applications Using Dual Loop Architecture..... | 50        |

| 5.1.2.1 Introduction.....                                                                              | 50        |

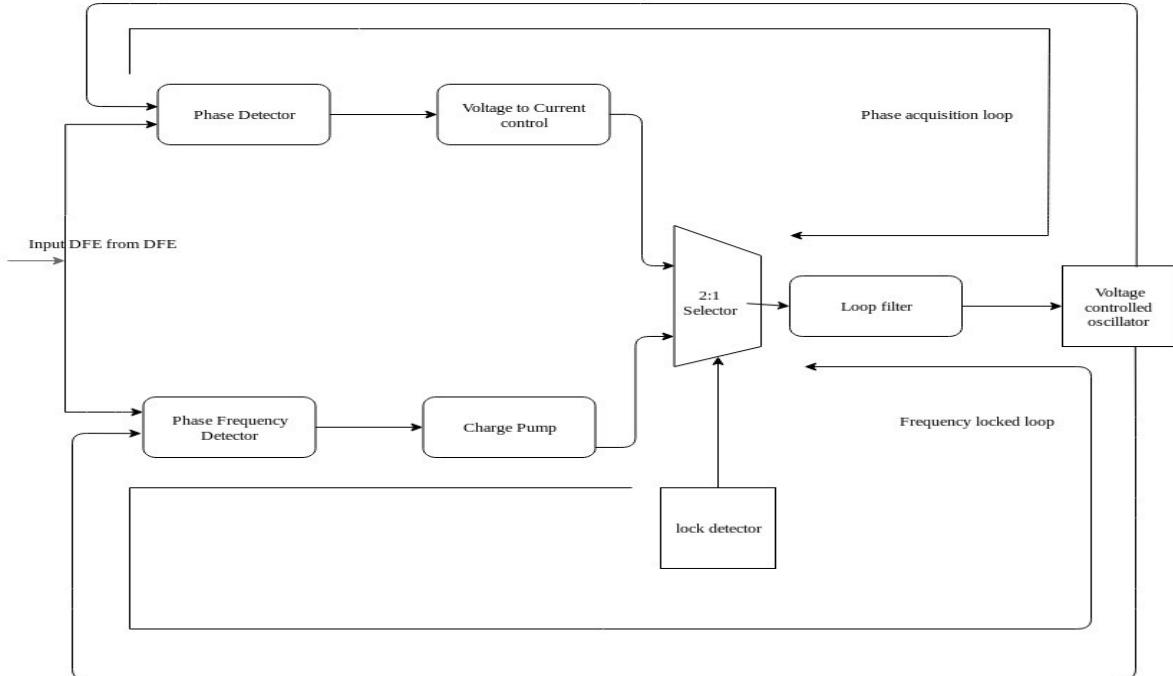

| 5.1.2.2 Architecture.....                                                                              | 51        |

| 5.1.2.3 Frequency Tracking Loop.....                                                                   | 54        |

| 5.1.2.4 Voltage Controlled Oscillator.....                                                             | 56        |

| 5.1.2.5 Conclusion.....                                                                                | 56        |

| <b>6 Conclusions and Future Scope</b>                                                                  | <b>62</b> |

| 6.1 Major Finding.....                                                                                 | 62        |

| 6.2 Future Scope.....                                                                                  | 63        |

| <b>References.....</b>                                                                                 | <b>64</b> |

| <b>List of Publications.....</b>                                                                       | <b>80</b> |

# List of Figures

|          |                                                                                   |    |

|----------|-----------------------------------------------------------------------------------|----|

| 1.1      | Backplane serial link Model.....                                                  | 2  |

| 2.1      | Block Diagram of High Speed Serial link.....                                      | 4  |

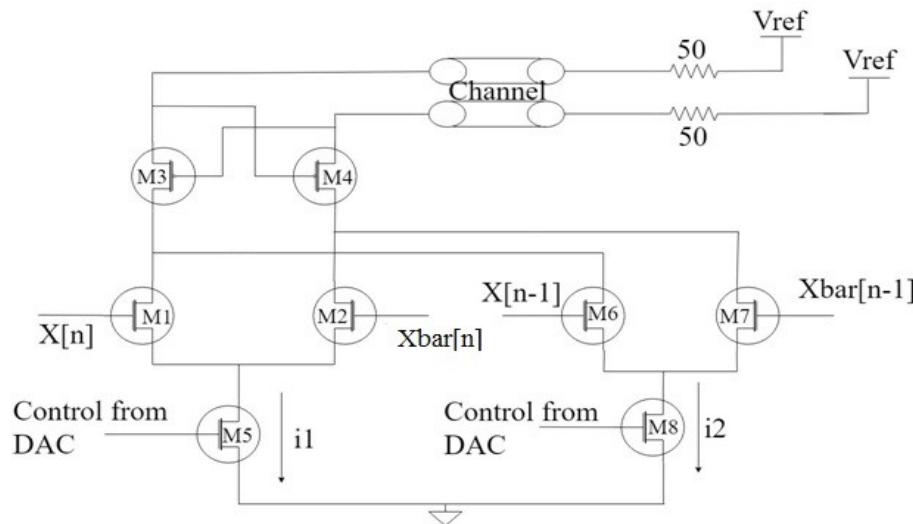

| 3.1      | Proposed On-die termination with pre-emphasis filter.....                         | 24 |

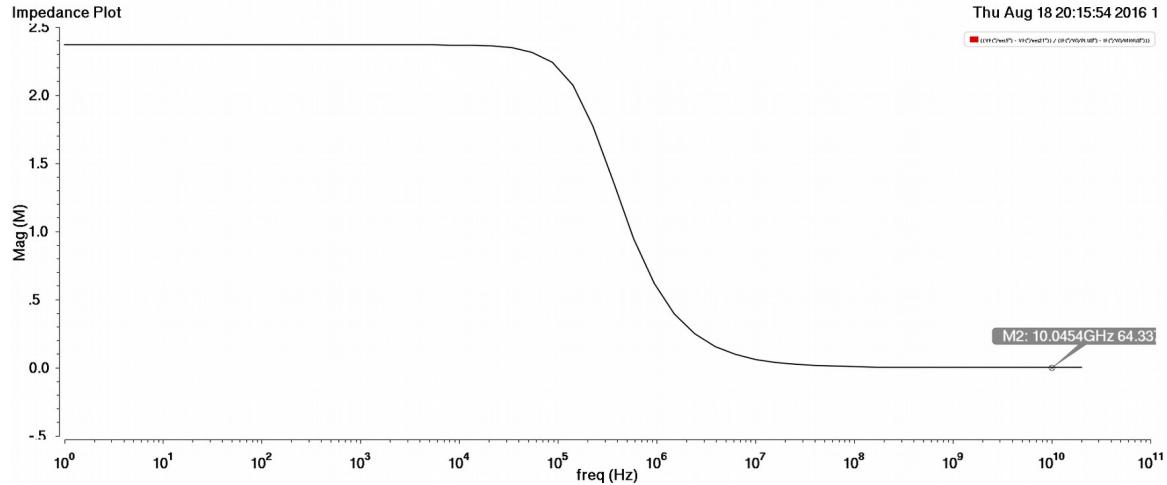

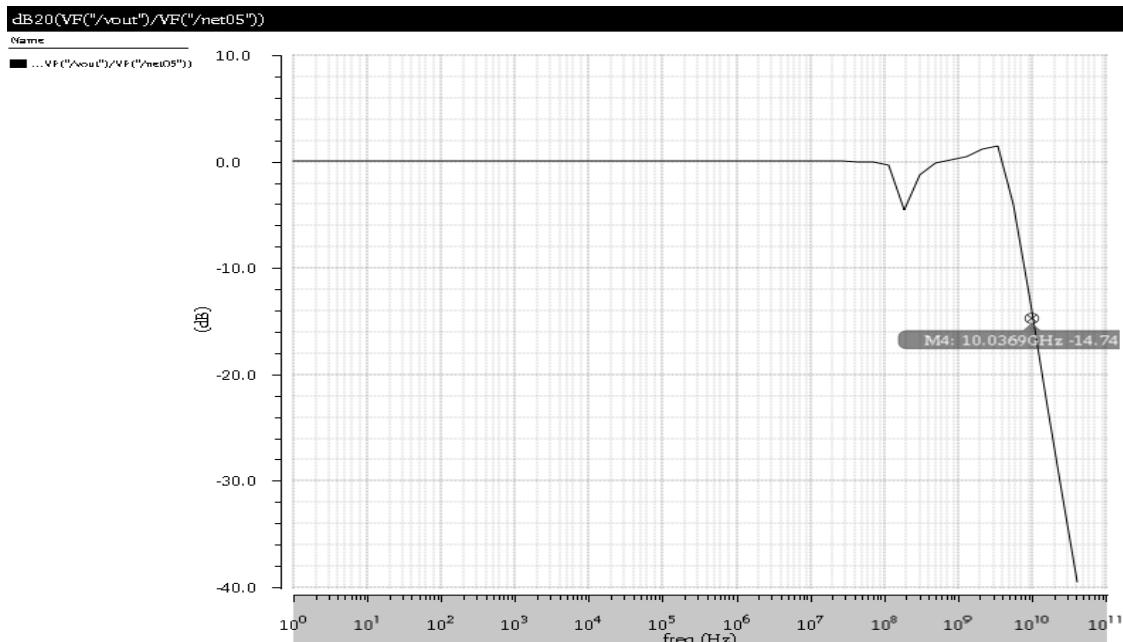

| 3.2      | Output impedance of the circuit.....                                              | 25 |

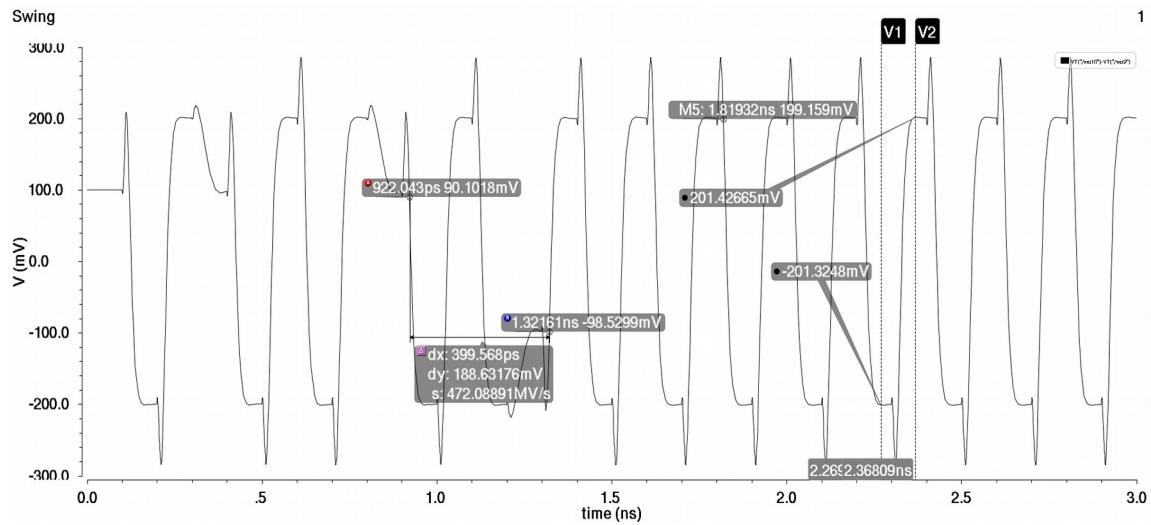

| 3.3      | Output swing across the On-die termination.....                                   | 25 |

| 3.4      | Eye diagram at the output of transmitter.....                                     | 26 |

| 4.1      | Schematic of conventional dynamic comparator.....                                 | 29 |

| 4.2      | Schematic of conventional dual tail dynamic comparator.....                       | 30 |

| 4.3      | Output of conventional double tail comparator.....                                | 31 |

| 4.4      | Double regenerative double tail comparator.....                                   | 32 |

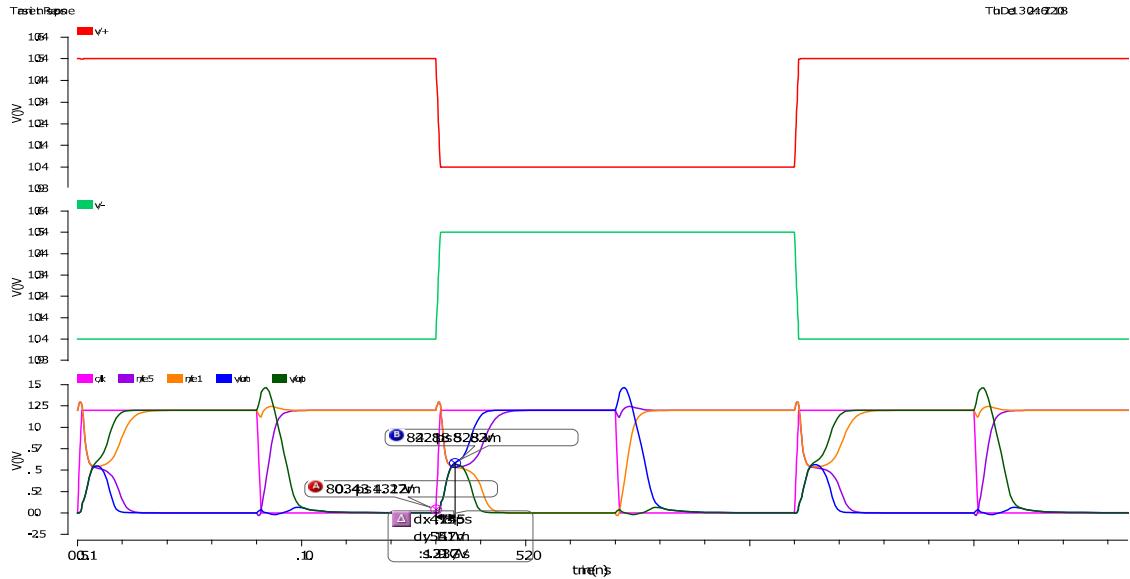

| 4.5      | Output of double regenerative double tail comparator.....                         | 33 |

| 4.6      | Modified regenerative dynamic comparator.....                                     | 35 |

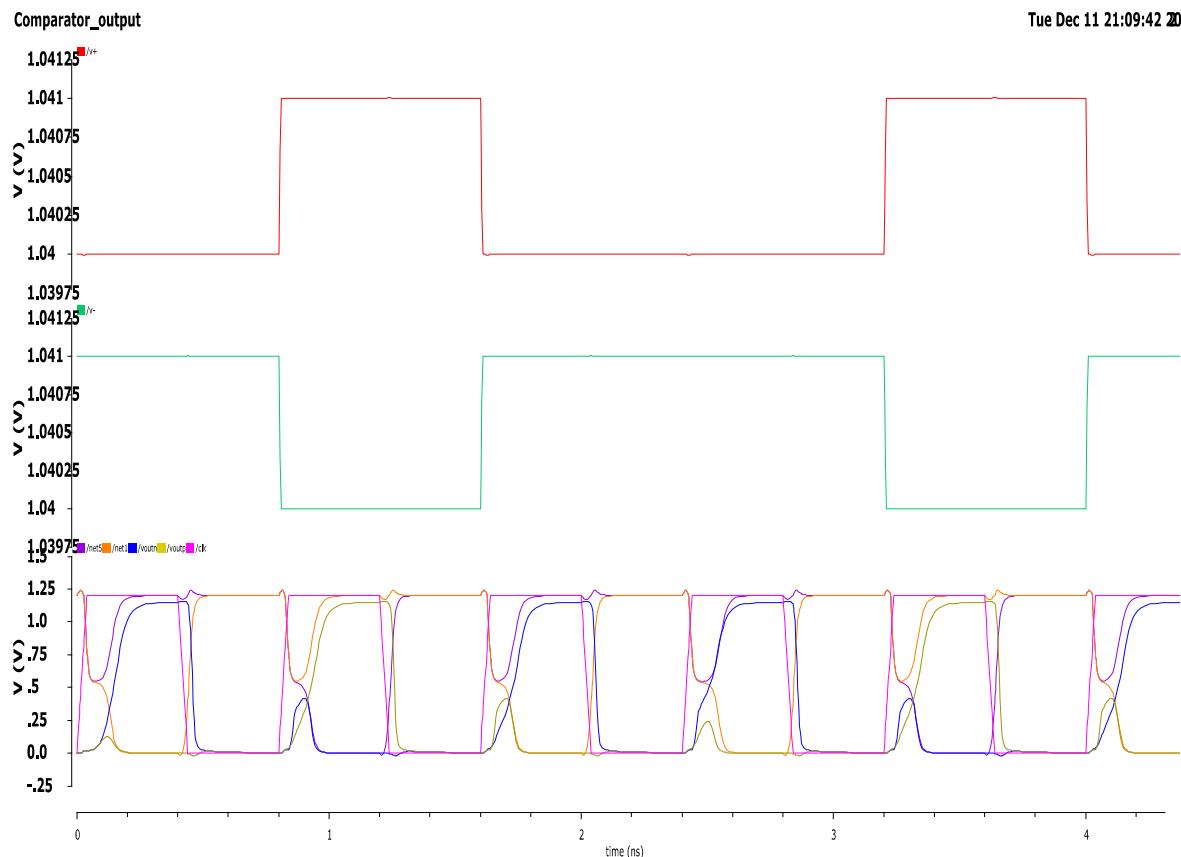

| 4.7      | Output of modified regenerative dynamic comparator.....                           | 35 |

| 4.8      | Circuit used for calculating output impedance in proposed dynamic comparator..... | 36 |

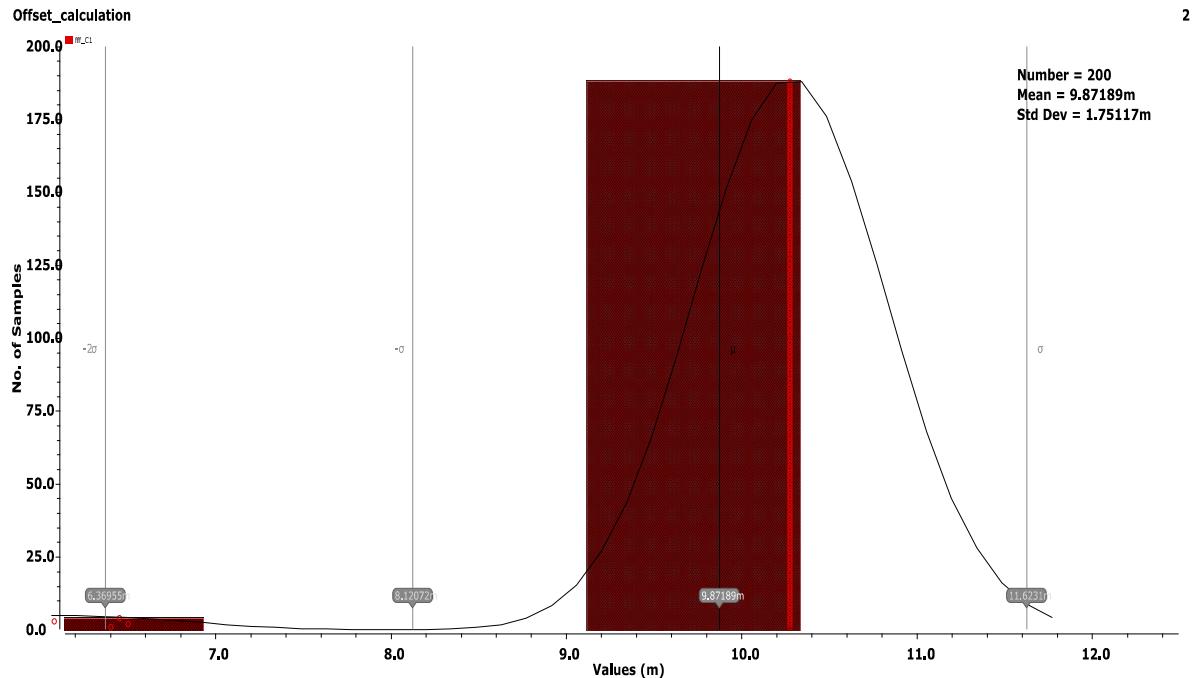

| 4.9      | Output offset of modified regenerative dynamic comparator.....                    | 37 |

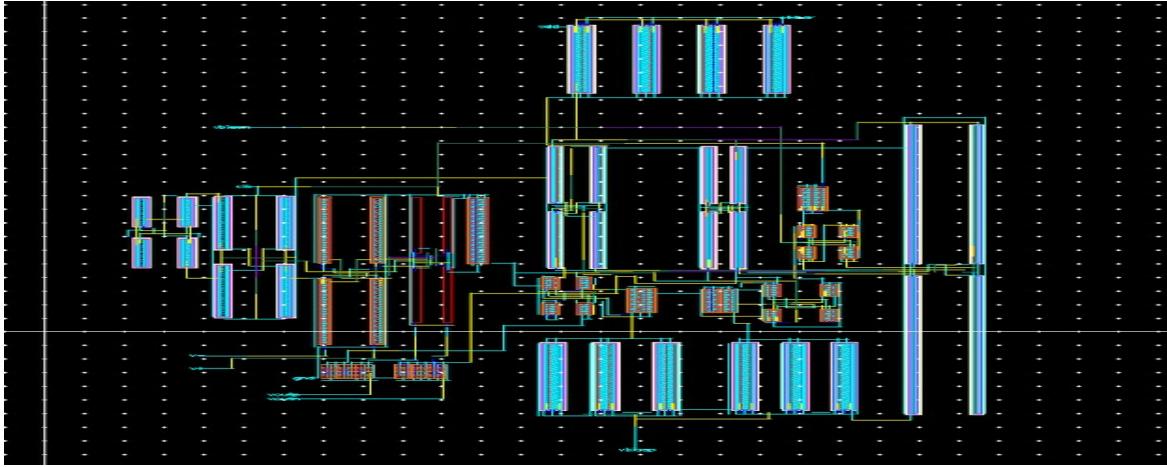

| 4.10     | Layout of modified dynamic comparator.....                                        | 37 |

| 5.1.1    | Block diagram of Phase Locked Loop.....                                           | 40 |

| 5.1.2    | Block diagram of modified PFD.....                                                | 41 |

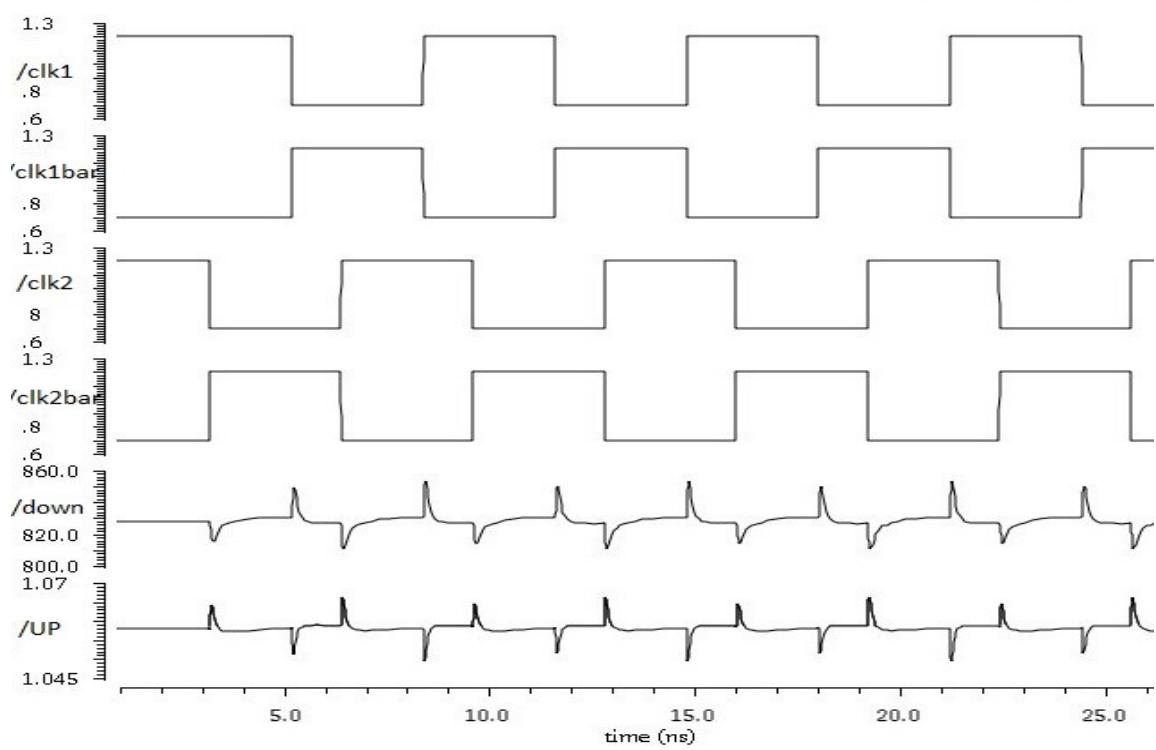

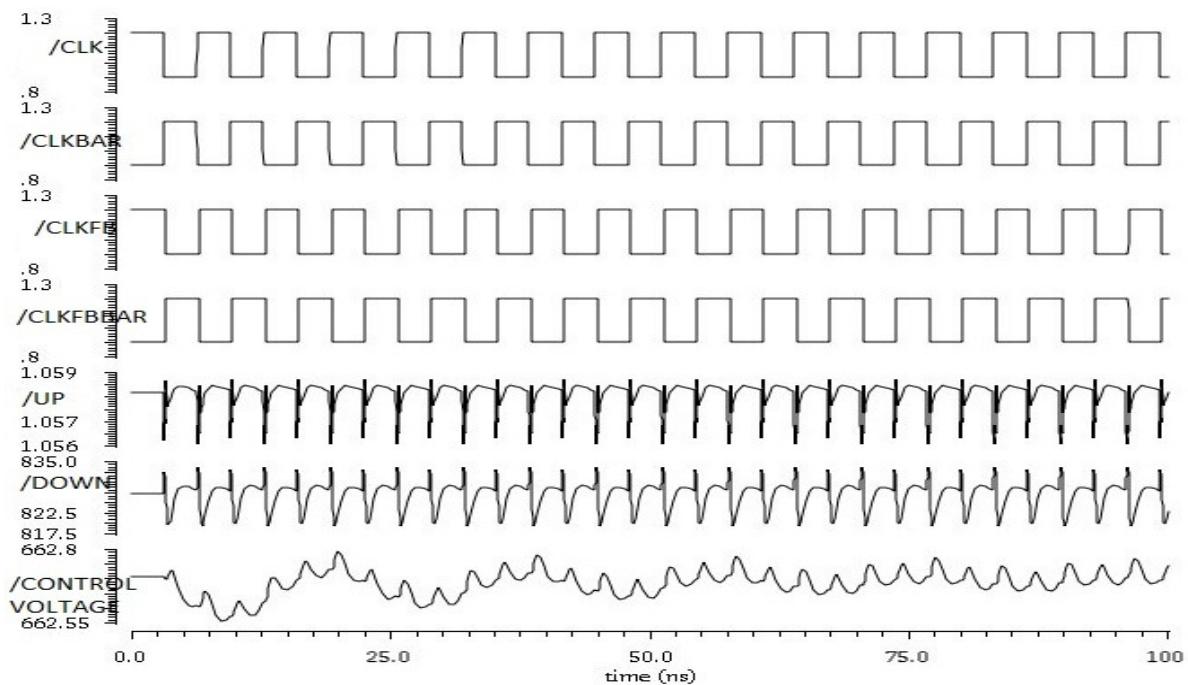

| 5.1.3    | Output of Phase frequency detector.....                                           | 42 |

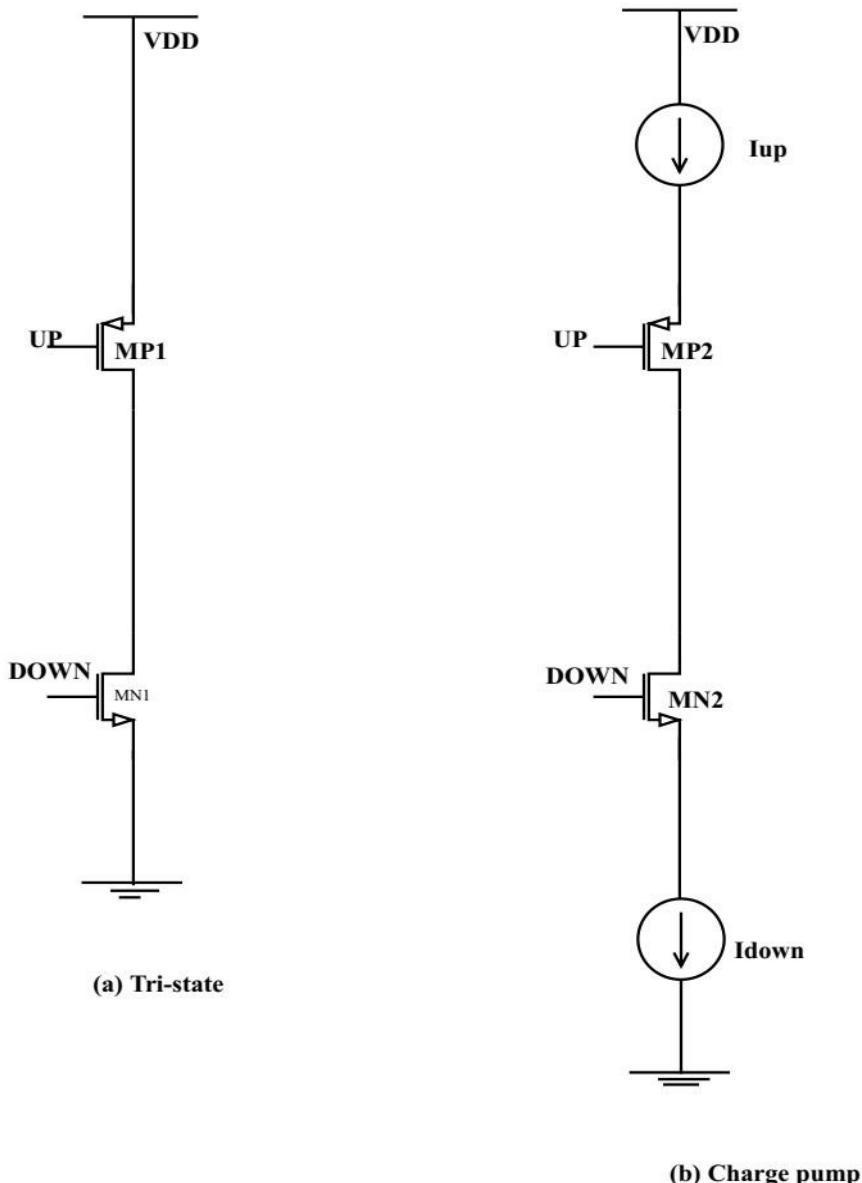

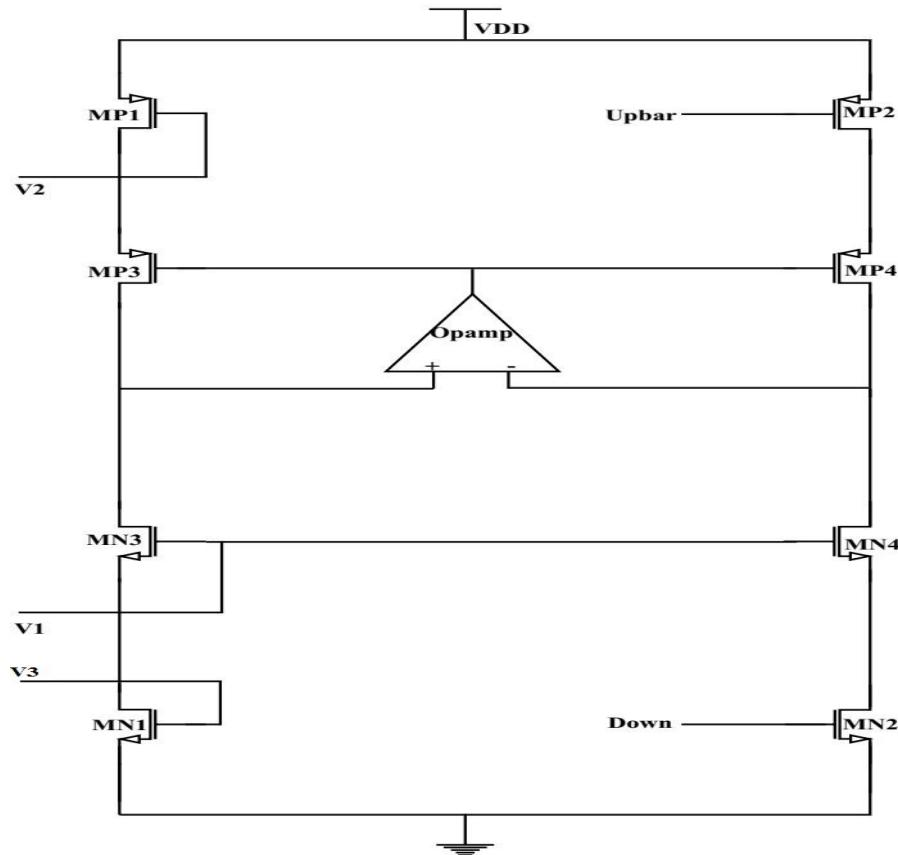

| 5.1.4(a) | Tristate charge pump .....                                                        | 43 |

| (b)      | Cascode charge pump.....                                                          | 43 |

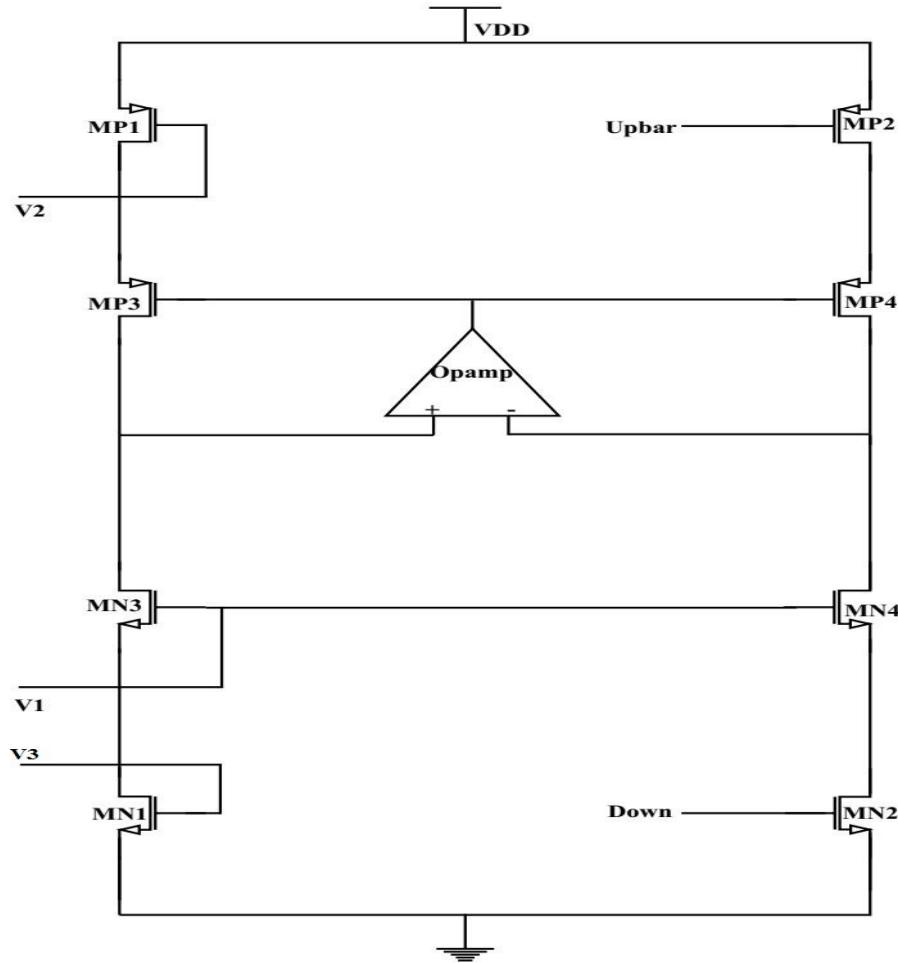

| 5.1.5    | Schematic of charge pump.....                                                     | 44 |

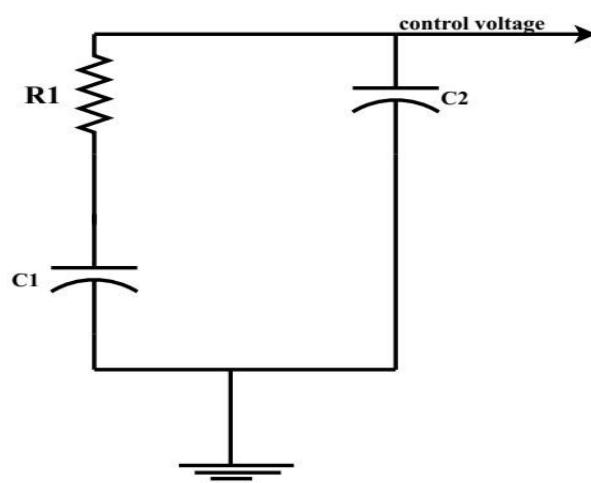

| 5.1.6    | Schematic of loop filter.....                                                     | 44 |

| 5.1.7    | Output of loop filter.....                                                        | 45 |

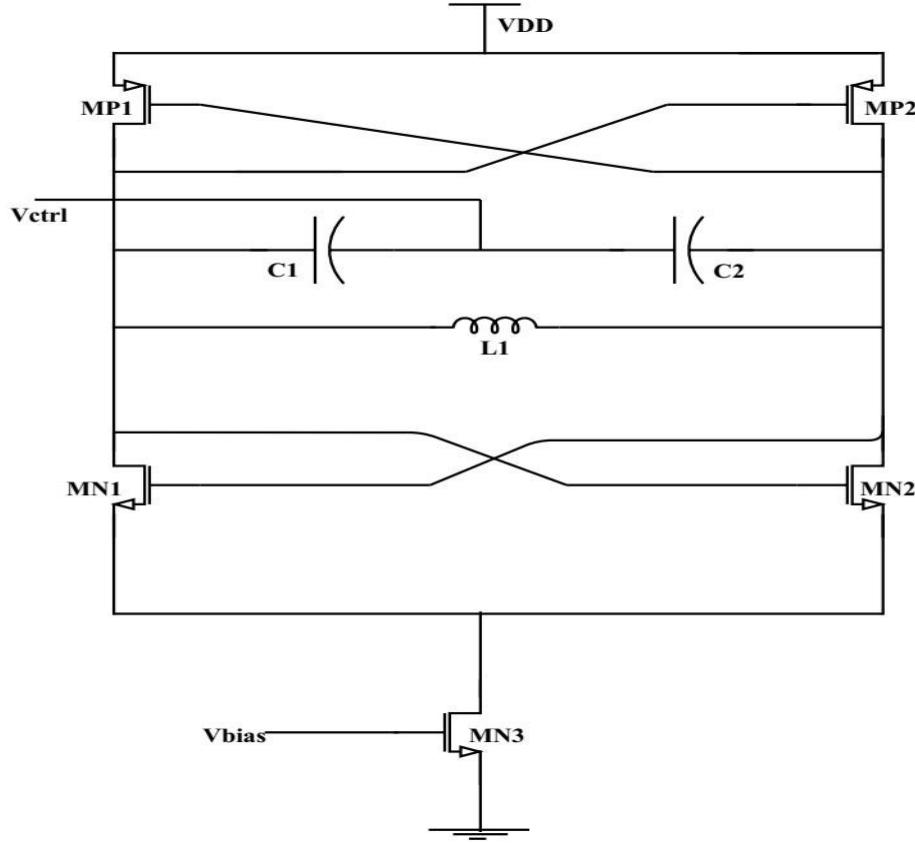

| 5.1.8    | Schematic of LC oscillator.....                                                   | 46 |

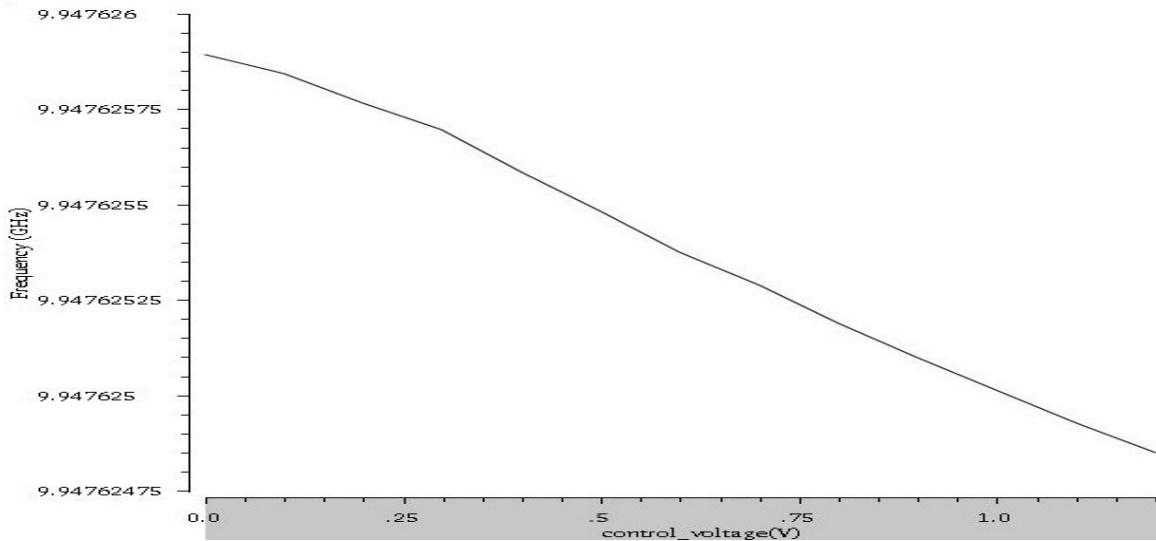

| 5.1.9    | Tuning range of LC-VCO.....                                                       | 47 |

|        |                                                                                 |    |

|--------|---------------------------------------------------------------------------------|----|

| 5.2.1  | Block diagram of Dual loop Clock and Data Recovery Circuit.....                 | 49 |

| 5.2.2  | Frequency response characteristics of Molex FR4 21 inches backplane.....        | 50 |

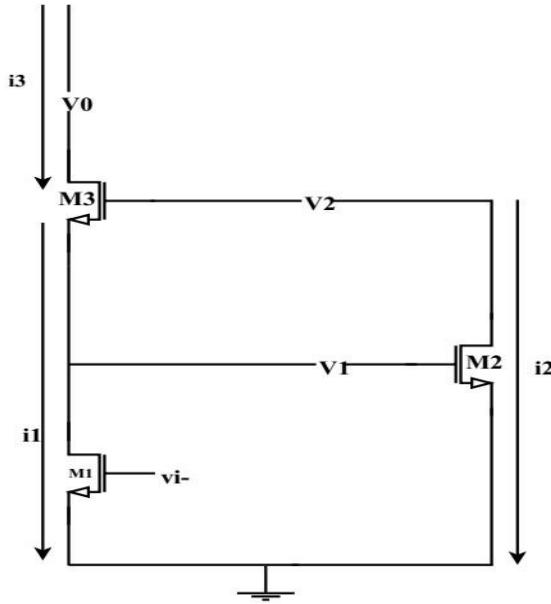

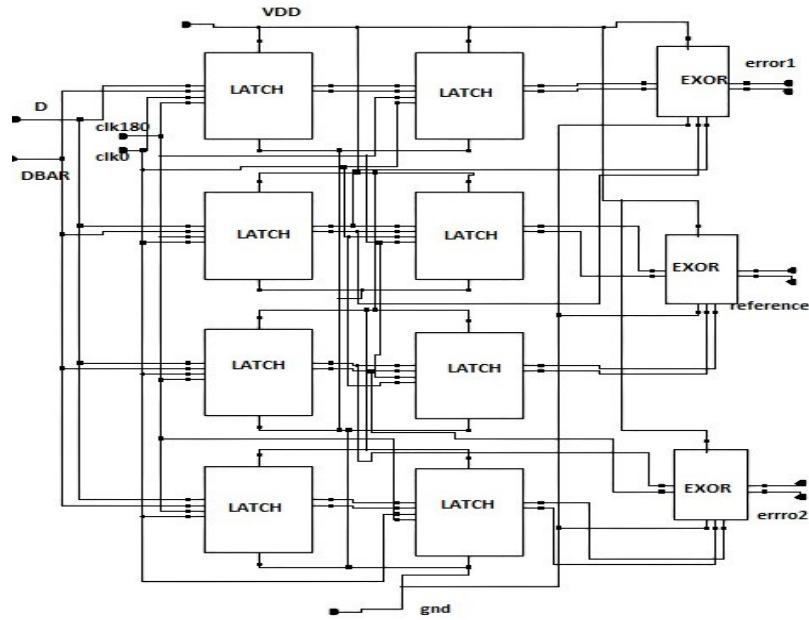

| 5.2.3  | Schematic of half rate phase detector.....                                      | 51 |

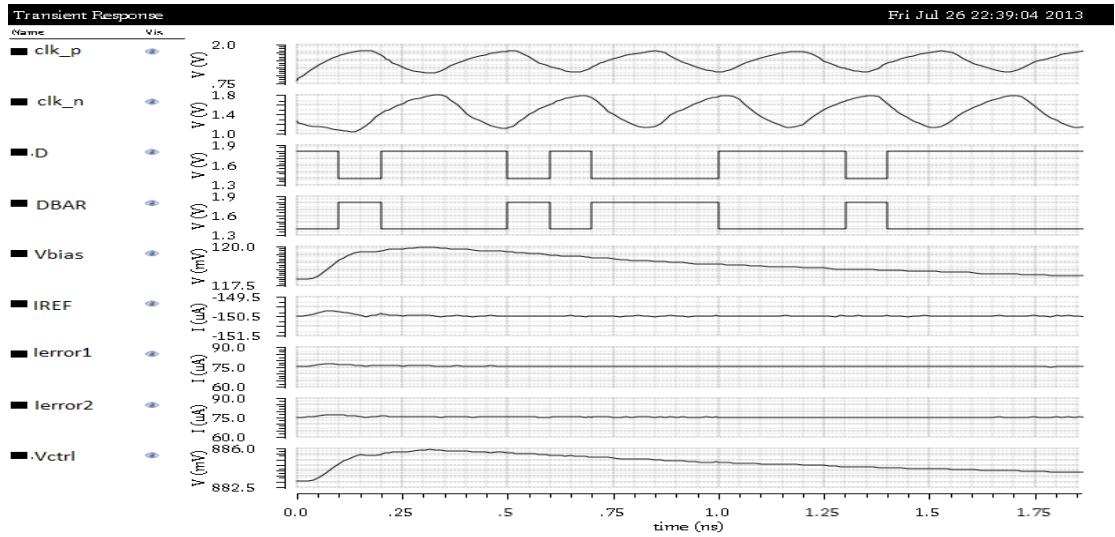

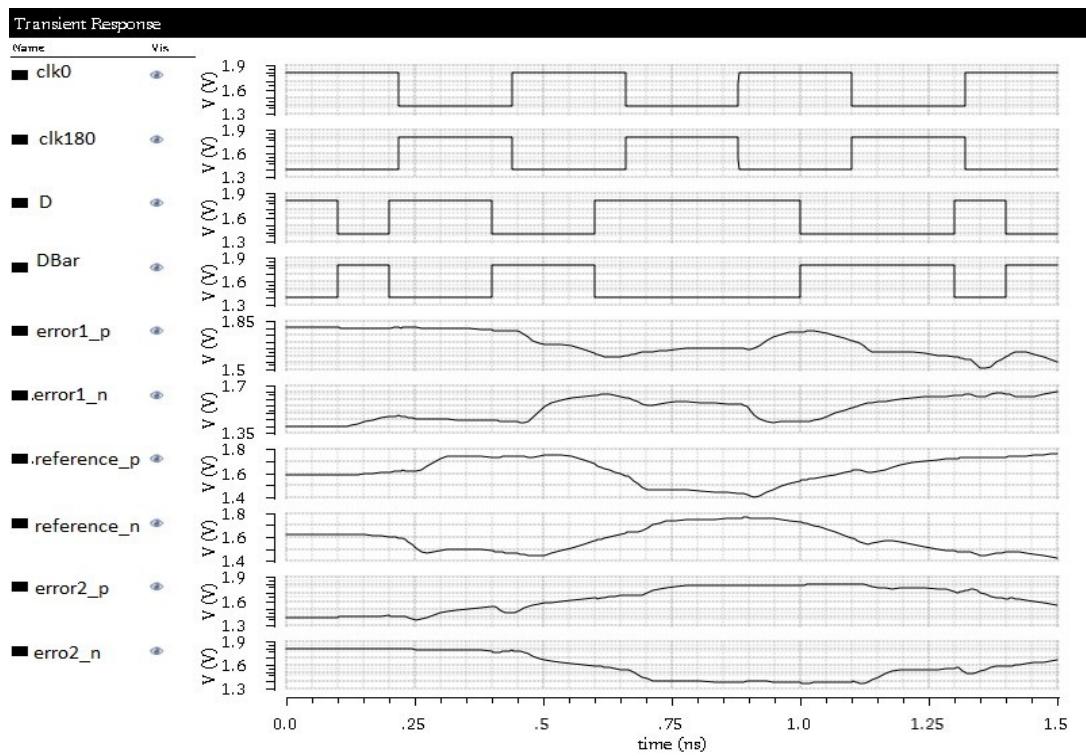

| 5.2.4  | Output of Phase tracking loop.....                                              | 52 |

| 5.2.5  | Output of half-rate Phase detector.....                                         | 53 |

| 5.2.6  | CML to CMOS converter.....                                                      | 53 |

| 5.2.7  | Schematic of Modified Delay latch.....                                          | 54 |

| 5.2.8  | Schematic of charge pump.....                                                   | 55 |

| 5.2.9  | Schematic of differential CML Inverter.....                                     | 55 |

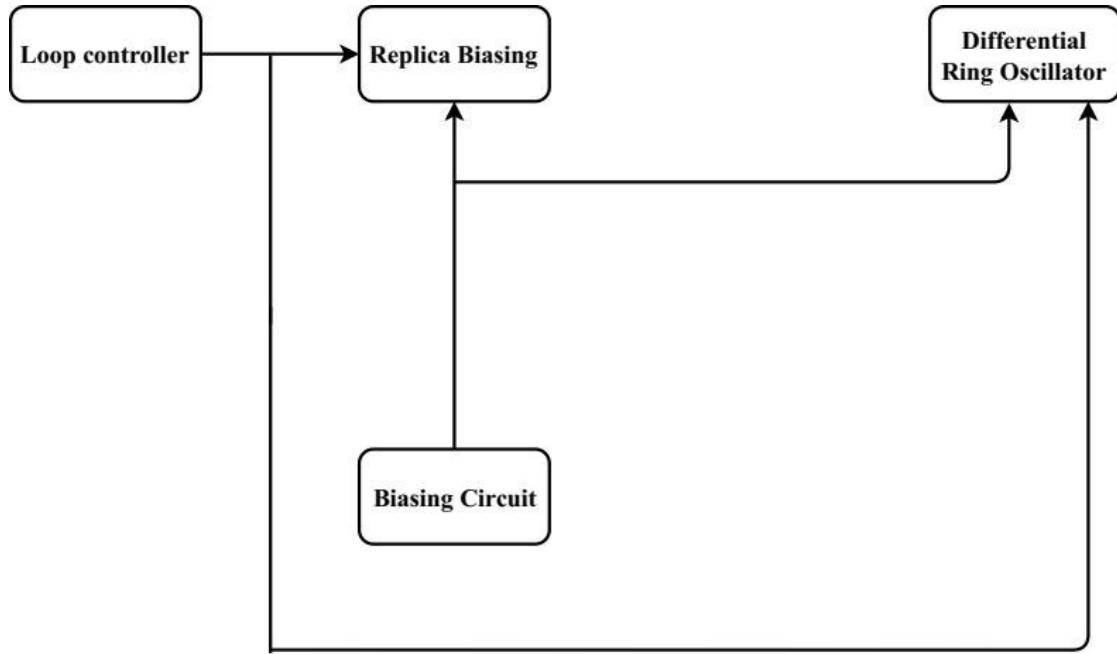

| 5.2.10 | Block diagram of voltage controlled oscillator.....                             | 56 |

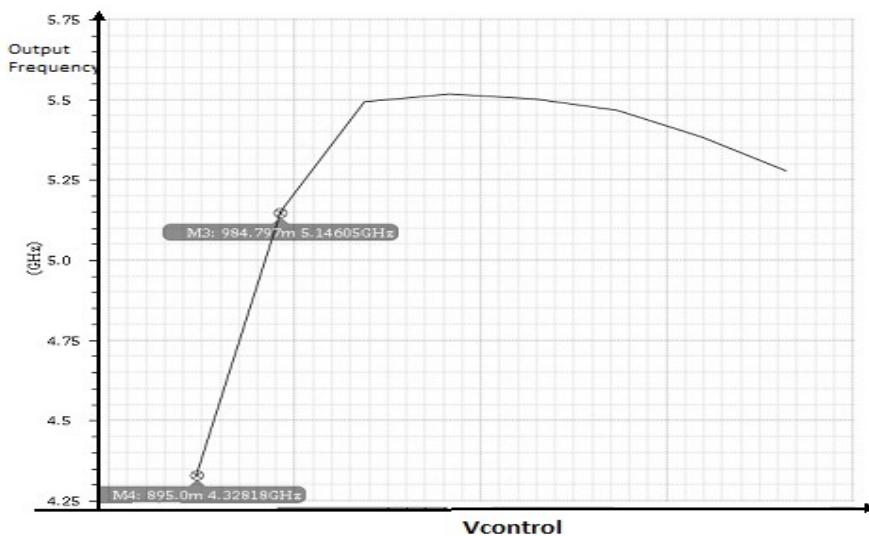

| 5.2.11 | Gain curve of voltage controlled oscillator.....                                | 56 |

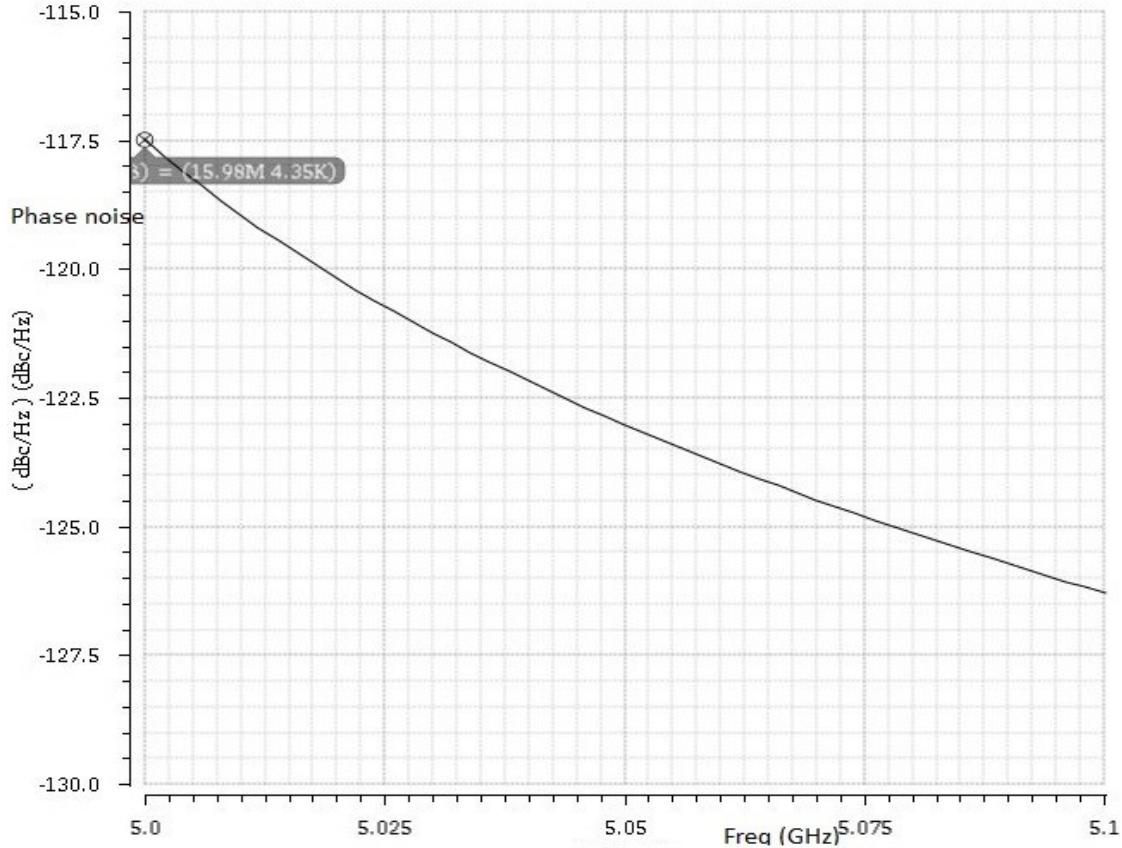

| 5.2.12 | Phase noise plot of voltage controlled oscillator.....                          | 57 |

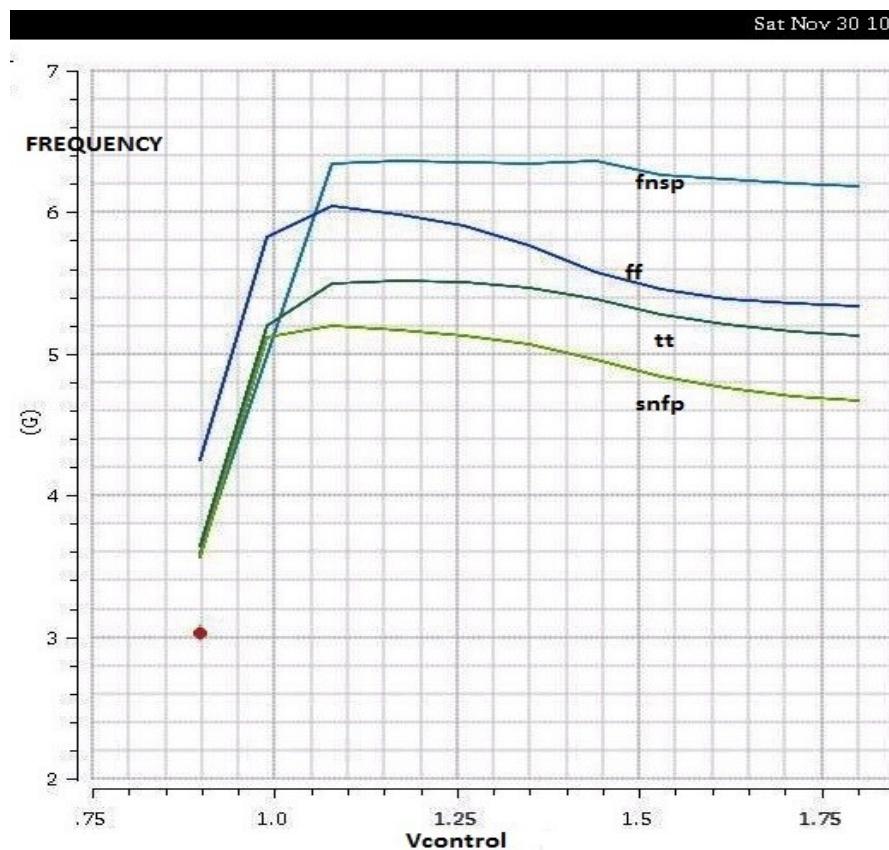

| 5.2.13 | Effects of process corners on phase noise of voltage controlled oscillator..... | 58 |

# List of Tables

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 3.1 Performance comparison of various feed forward equalizers.....  | 26 |

| 4.1 Performance comparison of state of art dynamic comparators..... | 38 |

| 5.1.1 Performance comparison of LC VCO.....                         | 47 |

| 5.2.1 Performance comparison of various CDR topologies.....         | 59 |

# List of Abbreviations

|             |                                                     |

|-------------|-----------------------------------------------------|

| <b>ADC</b>  | Analog to Digital Converter                         |

| <b>AEQ</b>  | Adaptive Equalizer                                  |

| <b>BGR</b>  | Band Gap Reference                                  |

| <b>BER</b>  | Bit Error Rate                                      |

| <b>CMOS</b> | Complementary Metal Oxide Semiconductor             |

| <b>CDR</b>  | Clock and Data Recovery                             |

| <b>CTLE</b> | Continuous Time Linear Equalizer                    |

| <b>CP</b>   | Charge Pump                                         |

| <b>CGA</b>  | Common Gate Amplifier                               |

| <b>CML</b>  | Current Mode Logic                                  |

| <b>DMT</b>  | Discrete Multi-Tone                                 |

| <b>DLL</b>  | Delay Locked Loop                                   |

| <b>DAC</b>  | Digital to Analog Converter                         |

| <b>DDJ</b>  | Data Deterministic Jitter                           |

| <b>DFE</b>  | Decision Feedback Equalizer                         |

| <b>EOM</b>  | Eye Opening Monitor                                 |

| <b>FOM</b>  | Figure Of Merit                                     |

| <b>FO4</b>  | Fan Out of 4                                        |

| <b>FFE</b>  | Feed Forward Equalizer                              |

| <b>FIR</b>  | Finite Impulse Response                             |

| <b>FR4</b>  | Flame Retardant                                     |

| <b>FLL</b>  | Frequency Locked Loop                               |

| <b>FD</b>   | Frequency Detector                                  |

| <b>HF</b>   | High Frequency                                      |

| <b>ITRS</b> | International Technology Roadmap for Semiconductors |

| <b>IC</b>   | Integrated Circuit                                  |

| <b>ISI</b>  | Inter Symbol Interference                           |

| <b>IIR</b>  | Infinite Impulse Response                           |

|                       |                                                          |

|-----------------------|----------------------------------------------------------|

| <b>I/O</b>            | Input/Output                                             |

| <b>KB<sub>N</sub></b> | <b>Kick Back Noise</b>                                   |

| <b>LV<sub>Z</sub></b> | <b>Low Voltage Zero</b>                                  |

| <b>LF</b>             | <b>Loop Filter</b>                                       |

| <b>MOSFET</b>         | <b>Metal Oxide Semiconductor Field Effect Transistor</b> |

| <b>NC</b>             | <b>Noise Cancellation</b>                                |

| <b>NLC</b>            | <b>Non Linear Cancellation</b>                           |

| <b>NR<sub>Z</sub></b> | <b>Non Return to Zero</b>                                |

| <b>ODT</b>            | <b>On Die Termination</b>                                |

| <b>PLL</b>            | <b>Phase Locked Loop</b>                                 |

| <b>PAM4</b>           | <b>Pulse Amplitude Modulation 4-level</b>                |

| <b>PD</b>             | <b>Phase Detector</b>                                    |

| <b>PFD</b>            | <b>Phase Frequency Detector</b>                          |

| <b>PVT</b>            | <b>Process Voltage Temperature</b>                       |

| <b>PAL</b>            | <b>Phase Acquisition Loop</b>                            |

| <b>PSRR</b>           | <b>Power Supply Rejection Ratio</b>                      |

| <b>PCB</b>            | <b>Printed Circuit Board</b>                             |

| <b>Q</b>              | <b>Quality Factor</b>                                    |

| <b>RJ</b>             | <b>Random Jitter</b>                                     |

| <b>RL</b>             | <b>Reflection Loss</b>                                   |

| <b>SNR</b>            | <b>Signal to Noise Ratio</b>                             |

| <b>SST</b>            | <b>Self Termination</b>                                  |

| <b>SS-LMS</b>         | <b>Sign-Sign Least Mean Square</b>                       |

| <b>SFF</b>            | <b>Sum Feedback Filter</b>                               |

| <b>SB</b>             | <b>Spectrum Balancing</b>                                |

| <b>UI</b>             | <b>Unit Interval</b>                                     |

| <b>VCO</b>            | <b>Voltage Controlled Oscillator</b>                     |

| <b>VM</b>             | <b>Voltage Mode</b>                                      |

# List of Symbols

|              |                                                            |

|--------------|------------------------------------------------------------|

| c            | Speed of light                                             |

| D            | Wire diameter                                              |

| $\rho_r$     | Wire resistivity                                           |

| $f_T$        | Transition Frequency of Transistor for specific Technology |

| $\tan\alpha$ | Loss tangent                                               |

| $\epsilon_r$ | Relative permittivity                                      |

| $\alpha$     | Pre-emphasis coefficient                                   |

# Chapter 1

## Introduction

### 1.1 Motivation

The exponential growth of data computation on chip coupled by device scaling has boosted the performance of many digital circuits. High-speed data transfer with power efficiency forms the focus of many speed communications architectures. The performance of high-speed serial I/O circuits are measured in terms of bit error rate (BER). The bit error rate is limited by the bandlimited characteristics of the communication medium which requires compensation at both receiver and transmitter to improve the signal integrity aspects of the high-speed I/O design.

The explosive growth of many high-speed data computation applications such as cloud storage/computation, sensor networks, the required data rate computed from ITRS shows above  $>70\text{Gb/s}$  in a span of 10 years, which proportionally keeping lower power bounds has motivated the serial-link architects to look for energy-efficient high speed serial link.

The band-limited nature of the channel causes large inter-symbol interference (ISI) and in-addition to impedance mismatches causes reflections which degrade the signal reception at the receiver. To deal with attenuation caused by channel, equalizers are being implemented at the transmitter and receiver. At very high data-rates, the amount of pre-emphasis and reflection loss coefficient varies with both frequency and channel length, this motivated the high-speed serial link architects to model and design energy-efficient circuit topologies.

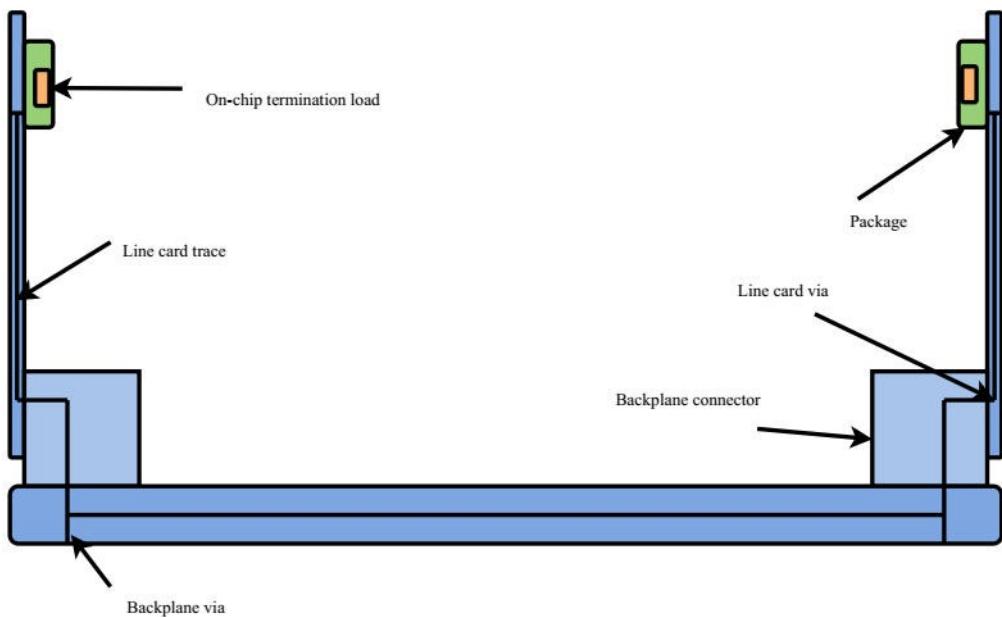

## 1.2 Backplane channel

The data-rates are previously very less attenuated by optical fiber cables. When being used for chip –to-chip data transfer it is limited by the performance of integrated photo detectors. The focus of this thesis is on copper channels. The backplane channels are composite of various materials such as line card trace, backplane trace, package and line card vias, and backplane connectors. The back-plane channel is shown in Fig.1.1.

Fig 1.1 Backplane serial link model [33]

The frequency dependent loss varies with channel length and frequency and it is low-pass in nature. The channel attenuation increases more for with narrow width pulses when sent through the channel, which results in a broader pulse at the other end. This effect is called as ISI and is most important effects which is design bottleneck of high-speed backplane links

### 1.2.1 Inter-Symbol Interference

Pulse dispersion is one of the major issues associated with ISI. At multi-giga hertz frequency range, the back-plane characteristics resemble of transmission lines and the skin-effect and di-electric loss causes frequency dependent losses. At high frequencies, the current flowing through the conductor flows in outer cross-section of wires, which is limited in area and cross-section. This effect increases the resistance which in-turn causes losses which are non-linearly proportional to frequency[33].

$$R_{AC}(f) = \left( \frac{2.16 \times 10^{-7}}{\pi D} \right) (\sqrt{P_r} * f) \quad (1.1)$$

D is wire diameter ( $\Omega/\text{in}$ ),  $P_r$  is wire resistivity.

The dielectric constant associated with the dielectric material encapsulates transmission line offers loss called di-electric loss, which varies linearly with frequency.

$$\alpha_D = \left( \frac{\pi \sqrt{\epsilon_r}}{c} \right) (f \tan \delta) \quad (1.2)$$

Where  $\tan \delta$  is loss tangent,  $c$  and  $\epsilon_r$  are speed of light and relative permittivity.

### 1.3 Organization of the work

The thesis the design of high speed serial link for backplane channels. The thesis is divided into eight chapters. The gist of each chapter is as follows:

Chapter 1 presents the introduction of high speed serial link followed by motivation, problem statement and contribution to the thesis.

Chapter 2 gives the overview of various circuit and block topologies of high speed serial links

Chapter 3 describes the design of on die termination circuitry with equalization functionality included used in the design of high speed serial links.

Chapter 4 demonstrates the design and results of high speed comparator employed used in receiver frontend.

Chapter 5 presents the design of clock generation and recovery circuits used in data transfer across backplane channels.

Chapter 6: Provides the summary of work and future work in design of high speed serial links.

# Chapter 2

## Literature Survey

### 2.1 Introduction

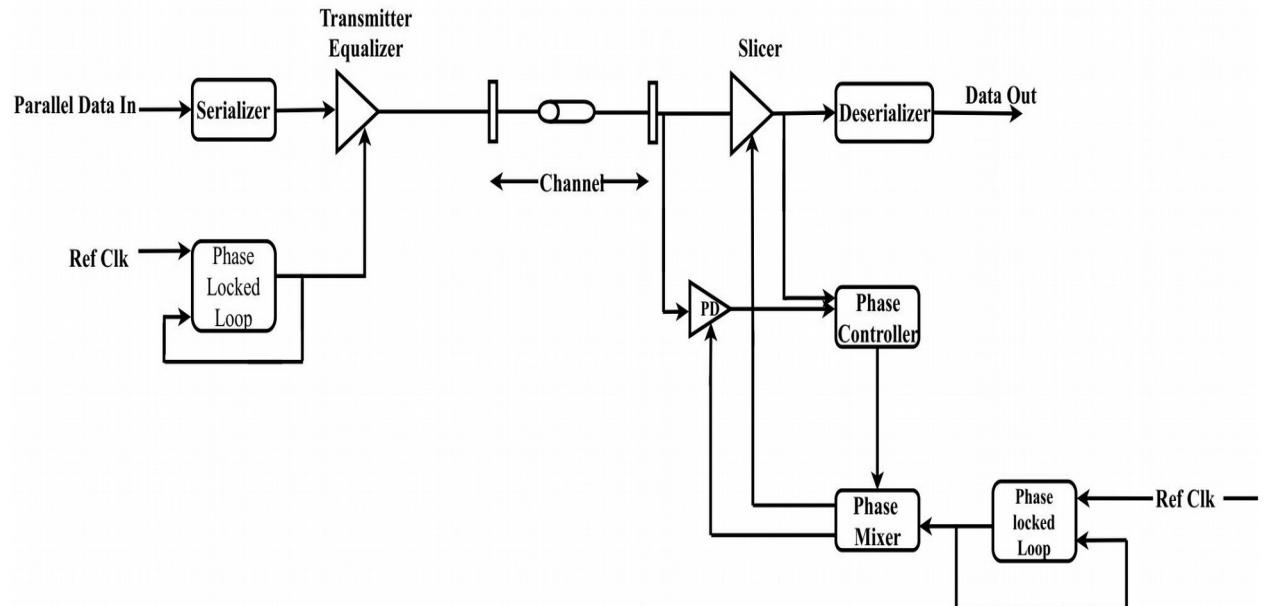

A high-speed serial link consists of basically three units such as transmitter, channel and the receiver as shown in Fig2.1.

Fig 2.1 Block Diagram of High speed serial link [6]

The functions of transmitter and receiver are as follows.

1. To serialize the low frequency digital data into a high frequency streamlined data and send it across the channel.

2. To recover the clock and data from the random attenuated data.

The transmitter sends the data in different forms of signaling such as Non Return to Zero(NRZ), Pulse Level Modulation-4(PAM4) and duo-binary depending on constraints such as data-rate and channel-loss. The time difference between each high and low voltages levels is the bit duration or time. The critical design issue of transmitter lies in serializing random data in-order to deliver a clear high speed data signal.

Conventionally channels are realized using co-axial cable, unshielded twisted-pair, Printed Circuit Board (PCB) traces etc. A Channel that offers minimum data loss is very expensive and there exists a trade-off between production cost and quality of channel. Hence the cost is optimized by employing PCB traces along with necessary circuitry to compensate the loss.

The random data are received at the receiver unit are distorted after passing through the channel. The receiver needs to amplify the signals of lower voltage levels to enable it for further data processing and error correction in addition clock recovery from the resolved data efficiently.

The (SerDes) (composed of Serializer and De-serializer) pairs. SerDes architectures opens the hatchway to immense rise in data-rate, developing a domain in which SerDes functions are expeditiously evolving to meet the demand for denser, high performance communications. By compressing populous inputs into differential pairs, accelerated throughput can also be universally actualize in a multitude of purposes [1].

The implementation of serial-links has become a challenging design with power analysis being performed on models before the design. In this direction the high speed link was analyzed by [2] and power hungry DFE was replaced by adaptive CTLE in the receiver with the CTLE eye opening being monitored and used as objective function in error minimization.

Serial I/O architectures with emphasis on signal integrity aspects were explored by [3] for power efficient circuit methodologies. To counter the power dissipation and to increase the throughput of serial-links, a voltage mode four-level pulse-amplitude modulation PAM4 serial link transmitter.

The PAM4 voltage-mode implementation consists of a pull up and down network, instead of constant tail current source, thereby having large swing at the transmitter. As the output impedance diverges with the PVT, the driver produces in-accurate output voltage levels. This topology employs calibrating control logic in order to reduce the reflection loss. The exponential increase in data-transfer rates across back-plane channels which of bandlimited nature necessitates, the designer to look for pre-emphasis/de-emphasis power-effective circuit implementation topologies keeping the design complexity low. An attempt was made by [4] to keep the design complexity low by using cascaded combination of two voltage mode drivers.

Designing an energy-efficient DFE for high-speed I/O is challenging task at high-data rates. This problem increases four-fold when the DFE are operated at transition frequency ( $f_T$ ) limits of process technology. To solve the above problem [5] has proposed to merge the summer and latch blocks and further decreasing the settling time of latch. Loop speculative DFE architectures suffer from speed and voltage headroom issues in sub-micron technologies when data-rates are very high. To mitigate this issue, the CML mux logic was replaced by majority-voting architecture by [7].

As data-rates required by the application are exponentially increasing, the power consumption is to be kept at minimum with channel attenuation becoming the design bottleneck. The serial link architect needs to explore alternative design blocks with no or marginal change in channel material. To overcome this issue, [8] proposed adaptive DFE at the receiver. In-addition to cancellation of the post cursor ISI by taps implemented by the adaptive IIR filter for keeping the jitter minimum and maximizing receiver eye height. The optimal design of the adaptive receivers (DFE-IIR) can be used to minimize the reflection loss coefficient. The required number of IIR filter taps is a non-linear function of power dissipation and ISI cancellation.

The low-pass nature of channel attenuates fast varying signals which are composed of R and C circuits, where ‘R’ and ‘C’ are unit resistance and capacitance in the channel such as high density silicon interconnects where source synchronous I/O systems are being used. To make

up the channel losses under limited power budget, [9] has proposed the use of DFE-IIR architecture. The continuous time IIR filter is tuned by both varying the resistive and capacitive components. This architecture is particularly suitable for channels dominated by R and C elements, altogether reducing the power consumption by implementing all post-cursor ISI taps by continuous time IIR filter as it has exponentially decaying pulse response characteristics.

The design of high speed serial link becomes more critical with low power constraints. Such designs meeting the settling time issue of full rate DFE, which is further tightened by parasitic capacitance at the summation node of DFE has motivated serial link designers to increase the design space to explore more circuit topologies [10]. To decrease the effect of parasitic capacitance, the back-gate (bulk) was used as an input terminal which helps in systematic isolation between input and feedback paths present in the design of higher speed summer.

The maximum data-transfer rate across the back-plane is not only limited by channel-loss but also by the power dissipation for minimizing the effects of pulse-dispersion. To reduce the loss at high frequencies, a zero is introduced in the adaptive equalizer (AEQ) in the receiver by [11]. So the AEQ is adapted based on slope minimization between the data transition edges at input and output of slicer. An attempt was made to make the design independent of PVT. To increase the SNR even at high-frequencies, a NC was employed which offers noise cancellation for a wide range of frequencies with DC gain achieved by the high frequency [HF] boosting.

The power hungry circuits in a serial link are DFE, summer and slicer. To minimize the power consumption FFE uses half rate topology at the transmitter along with that a full rate DFE at the receiver. In this direction [12] proposed full-rate DFE architecture, the summer and comparator are merged into flip-flop meeting the settling time required remarkably increasing the operating speed of the main critical loop, thereby removing the speed bottleneck in design of high-speed I/O.

The power dissipation to compensate PCI express channel loss needs to be minimum with minimum hardware overhead. Towards this, various design methodologies were attempted A low-voltage zero (LVZ) is placed in equalizer at the receiver for high frequency gain boosting. A SB technique was employed[13] which tunes LVZ by minimizing the power difference between the high and low frequency components at the input and output of slicer .

Here an attempt was made to tune LVZ using power detector instead of using inductor for HF boosting in order to reduce area.

The attenuation provided by FR4 channel depends on the data-rate and channel length. To meet the ever increasing signal integrity issue as stated above, equalizers are implemented at both transmitters and receivers which are adapted at the receiver. To minimize the effect of post cursor ISI and minimize power consumption, an IIR filter was used by [14] in lieu of post cursor taps. The topology is tuned to meet the settling time requirements increasing the serial-link efficiency.

The back-plane is very complex environment which is composed of various materials with diverse frequency characteristics. Any impedance mismatch between the channel and termination circuitry at both transmitter and receiver causes reflections and are quantified as reflection loss coefficient. The high frequency signals are attenuated by the channel due to its band-limiting nature in-turn causing ISI, which varies with frequency, PVT variations. To compensate the channel loss and retrieve the high-frequency signal from the corrupted signal, equalization is usually employed in the transceiver. To adapt the receiver equalizer, many techniques such as SB and EOM are being implemented. The SB technique mentioned above fails to perform for non-random data pattern in multi-rate applications and EOM burns huge power dissipation. To deal with above problem an adaptation strategy was proposed [15] in digital domain to reduce power consumption effectively.

The conventional resistance based summers in high-speed serial links are power hungry and have settling times constraints, So they are replaced by a resettable current integrating summer reduces the power consumption considerably as the output nodes are pre-charged during the sampling phase for low frequency data-signals. The integrating summers suffer from frequency dependency loss of about 3.9dB at higher frequencies, so to mitigate this issue [16] has proposed to design a transmission-gate based sample and hold topology used.

Signal-to-Noise ratio plays an important role in any serial communication link. Equalizers are employed to cancel post and pre-cursor ISI. The main problem with the FFE present at the transmitter is lack of its adaptability and introduction of noise. This necessitates to keep a front-end amplifier circuitry to improve the signal swing mostly for multi-level signaling schemes. To improve the data-transfer rate, at the receiver equalizer either CTLE or DFE can be adapted, that can reduce the noise introduced into the circuitry. Towards this end a

summer amplifier or integrator and DFE are both combined by [17] that reduces the noise generation and power consumption.

The power consumed by the I/O circuits needs to be fraction of data processing units on the IC. To further reduce the power consumption, different variations of equalizers were modeled to evaluate the power efficient architectures. In this direction an Infinite Impulse Response-Decision Feedback Equalizer (IIR-DFE) combination filters were used for a very power and area efficient serial I/O circuitry [18]. The pulse response of an IIR filter matches to the exponentially decaying nature of signal when sent across a back-plane channel. This idea changed the phase of design from two or more symbol spaced DFE to single tap DFE and an additional tap comprising of IIR filter which can be tuned by the error function at input of DFE. This novel architecture has not only reduced the power consumption but also reduced the overall area drastically.

Data transfer across back-plane or serial links of various flavors is not limited only by the operating frequency of signal but also by stub-length, receiver eye sensitivity and required BER vs power consumed trade-off. It was shown that it is highly efficient to send data using NRZ signaling when BER and power consumption are primarily important, whereas in case high-rates are demanded by the application, partial-response signaling or duo-binary signaling is preferred as appropriate choice for both long-distance and medium complexity. Further PAM4 is preferred when very high data rates and long-channel lengths are needed but the latter causes increased power consumption caused by the amplifier stages present at the front-end of comparator [19].

To compensate the channel loss due to traces of FR4, pre-emphasis technique was employed at the transmitter which causes reduction in dynamic range of signal for data-rates above 10Gb/s. To counter this effect and reduce the power consumption, various techniques such as 1) peaking by complex poles 2) peaking by passive networks and reverse scaling were proposed [20]. The receiver equalizer was tuned by Spectrum Balancing (SB) technique.

The second most power hungry circuit in the receiver block of serial link is the current integrating summer. To reduce the power consumption of the summer, a charge transfer mode summer topology was proposed [21]. Two reference voltages namely  $V_{CM}$ ,  $V_{REF}$  are taken from a stable voltage reference generator such as band-gap reference (BGR). The summer acts as front end to loop unrolled DFE to generate the required voltages. The

capacitor  $C_s$  is charged to effective voltage of  $V_i - V_{CM}$  initially and during the evaluation phase, the charge across the output is  $V_i \pm V_{REF}$ .

To adapt a full-rate DFE at high data rates, the power consumed by the summer, comparator and coefficient adaptation logic are very high. To reduce the power consumption in full-rate DFE architecture, unrolled DFE, partial -response DFE, or loop speculative technique were employed. The power is further reduced when half-rate or quarter rate loop unrolling technique was used for cancelling only first tap used in DFE. However it increases the hardware requirement exponentially, So keeping this constraints as design objective, a time-interleaved soft decision technique was proposed by [22]. This technique not only mitigates the above problems but also increases the evaluation time required as the latch was used in place of power hungry and high-offset prone edge triggered slicer.

Band-limited channels attenuate fast varying signaling, which causes ISI. To reduce the impact of ISI, an adaptive DFE is categorically employed at the receiver, which may run at full-rate or half-rate depending up-on the power budget. The receiver DFE circuitry composes a summer in feedback-loop to cancel the ISI, without amplifying noise which is boon as Signal to Noise Ratio (SNR) is increased drastically. This causes the power consumption to shoot up in summer and comparator. To minimize the power consumption [23] proposed pre-charge based summer. The summer not only reduces power consumption but also lowers settling time requirement as the output nodes are pre-charged before sampling and decision making phase.

At data-rates above 2Gb/s, the attenuation provided by the channel needs to be compensated. To solve this problem [24] proposed a sum-feedback filter[SFF] which relaxes the timing requirement compared to FFE at the receiver. To further reduce the channel-loss, a PAM4 signaling was adopted which increases the data-rate 4- fold.

To decrease the power consumption and decrease the circuit design complexity of high speed serial link, continuous Time Linear Equalizer (CTLE) was adapted by [25]. The adaptive algorithm relies heavily on spectrum balancing technique where balancing the power components of both high and low frequency components of signal is the design objective, thereby boosting the gain and increasing the data spectrum judiciously.

Half-rate, quarter-rate loop speculative algorithms which are power efficient are used to aid while designing DFE but suffers from the drawback of causing additional pattern jitter. This motivates the designer to look for architectures[26] to decrease the DDJ. In this direction

LMS algorithm and edge equalization are both combined to create voltage margin and timing margin in DFE circuitry in the design of serial links.

The bandwidth to send a high-frequency signals over back-plane is primarily limited by channel attenuation which is also called 'channel-loss'. The attenuation measured in decibels (dB) varies with many factors such as signal bandwidth required, channel-length and type of materials used during channel design. [27] proposed a power-efficient design in which duo-binary signaling was preferred signaling method which has the advantages of multi-level signaling. So more bits are sent through the channel in 1UI and the required bandwidth decreases to almost two thirds. The design uses an FIR filter which compensates the phase and amplitude distortion due varying nature of channel and thus power efficient realization of near duo-binary signaling scheme was made possible.

To increase the operating frequency range, an adaptive FIR equalizer with fractional spaced structure which has inverter with an active inductor as load element was proposed [28] for usage in high-speed data communication. A pulse extraction method was used as closed loop adaptation technique to demonstrate its inherent low-power and area efficient implementation.

To maximize the received voltage the equalizer employs several interpolator sampling phases, thereby decreasing the power consumption and design complexity. To further reduce the power consumption, zero-forcing and Sign-Sign Least Mean Square (SS-LMS) algorithms were modified to implement adaptive equalization in digital domain by [29] where-in the frequency of updates can be further reduced. The power consumption of receiver is proportional to receiver sensitivity, which mainly is contributed by offset component of comparator hence the offset of comparator is cancelled, and sampling clocks utilized by the comparator are de-skewed to take care of static mismatches which resulted in minor variations in filter coefficients.

Eye opening at the input of the receiver determines the BER of the transceiver. To measure the eye-opening, eye diagrams are measured on the fly using eye-opening monitors (EOM), which maps the received signal to high-speed signal. To generate EOM, phase rotators and digital-to-analog converters (DAC) are used in different sizes of rectangular masks which are overlapped with the received signal at the receiver. The worst case mismatch is determined by signal transitions at the middle of eye and thus can be used as error signal to adapt the receiver by means of co-efficient optimization. This method of BER detection using

EOM[30] is independent of decision at the output of receiver and does not depend on pattern matching, which in-turn reduces the complexity of the receiver design.

To increase the performance in serial links at higher frequencies, three equalization methods such as FFE at transmitter, discrete equalization and receiver equalization for high speed differential serial links was proposed by [31].

The back-plane environment is very complex since it is composed of different materials which causes not only reflections but also channel loss which varies with stub length, frequency and data -rate. The proposed architecture implements both NRZ and PAM4 with little change in the selection hardware which achieves high throughput in terms of low reflection loss and low power overhead over broad range of frequencies [32].

More complex signaling techniques such as PAM4, duo-binary are employed for meeting the BER specifications. A dual-mode architecture was by [33] proposed for implementing both the NRZ and PAM4 signaling with a minor modification for implementation. Loop-speculative single tap DFE was adopted as receiver equalization. The receiver equalizer is adapted by popular sign-sign LMS procedure, with maximum voltage swing as main problem objective with the data based filtering, which in-turn reduces the hardware at the front-end of the sampler thus reducing the power consumption in the receiver.

To meet the BER specifications in band-limited channels, the effective input referred noise plays a very important role in the design of high speed serial links [34].

To improve the bandwidth-power trade-offs, duo-binary signaling was implemented for the required bandwidth for efficient design of adaptive equalization technique [35].

The bandwidth required to implement multi-level signaling is less compared to the full-rate signaling schemes, as the gain boosting required to counter the channel loss decreases which makes the architecture power-efficient.

A data-look ahead technique was presented by [36] is used to drive the main tap current sources when reduced swing is preferred.

A back channel communication path was employed using common mode signaling in order to adapt FFE by [37] for a self-contoured adaptive differential high-speed transceiver cell. To minimize the hardware costs, an extra data update information from receiver to the

transmitter uses a three level return to zero signaling scheme with simultaneous voltage and timing references.

Duo-binary signaling exploited by [38] to improve sampling rates. Controlled amount of ISI was introduced so that it can be removed afterwards at the receiver. The data-rate is not only limited by the PCB traces and back-plane but also by data computation unit's on-chip.

A continuous time filter has advantages of wide tuning range. A tap continuous time filter is used to implement transmitter Finite Impulse Response (FIR) filter used for implementing pre-emphasis functionality for data rates above 1Gb/s data transfer rates[39] . Each tap on the pre-emphasis filter is implemented by a second order low-pass filter. The major challenge involved in design of tap filter is that it need to have constant amplitude and group delay response across the signal bandwidth.

Spectral efficiency is higher when more than one bit is transmitted per 1UI. In this direction [40], has attempted the use of PAM4 for data transfer across backplane. In this direction, to compensate the channel loss and reduce the distortion, the transmit equalizer is continuously adapted.

To keep up with increased data transfer rate across the back plane, [41] proposed usage of multi-level data transmission or usage of DFE. To maintain compatibility the same hardware can be used to implement both 4PAM and NRZ signaling using loop-speculative DFE at the receiver. To tackle ISI, FFE at the transmitter is tuned using back-channel. Data based updates are used to tune back channel and the receiver equalizer is adapted based on error signal from the summer, thus minimizing the hardware required at sampler-front end and this drastically encourages multi-level signaling.

To keep up with the demands of high data rates above 1Gb/s multi-level signaling such as PAM4 is usually preferred for meeting the trace attenuation or channel-loss which varies with both frequency and length. To show the effectiveness of this technique[42], a low cost BGA packing was employed. To counter the effects of signal interference transmitter equalization ,cross talk cancellation circuitry are used in parallel and current summing integrator topologies are employed at the receiver.

Data transmission at high data-rates is limited by transition frequency of technology used and the channel loss [43].The multi level signaling is proposed with half ,quarter and octave rates

for data transfer retrieved by[44] . Power dissipation can be reduced by using clock at lower operating frequencies.

A voltage-mode switched-capacitor based circuit as summer circuitry was proposed by [45]. to reduce the power consumption. A fixed co-efficient Feed Forward Equalizer (FFE) is used to cancel pre-cursor ISI. A timing function is created by using fully adaptive Decision Feedback Equalizer (DFE) and mixed signal current-summing circuit to cancel post-cursor and baseline wander.

Next generation of gaming applications requires very high speed data transfers between graphical processing units and gaming consoles. In this direction a high-speed transceiver was proposed by [46], wherein the multi-level signaling (4PAM) and pre-shaping are employed at transmitter along with adaptive equalization at the receiver.

Techniques for high-speed implementation of nonlinear cancellation were proposed by sanjay et al [47] .Non Linear Cancellation (NLC) significantly limits ISI in long haul direct-detection structures and thereby doubling the information rate limited by pulse dispersion. The ISI reduced through NLC which is carried out through subtracting the interference brought on by previously detected symbols. This subtraction, on the other hand requires previous selections to be sent-back to the comparator element. However delays in the feedback back loop can severely worsen the required signaling rate of a detector operating with NLC. The problem was addressed by modifying the feedback loop with help of analog signal switching through multiple decision feedbacks each with a unique threshold value. An associated look in advance computation facilitates the feedback loop to complete the computation within permissible time.

## 2.2 On Die Termination

To reduce the power consumption a voltage mode transmitter is proposed which performs both equalization and impedance matching to the channel. To further reduce the power, a low common mode signaling is employed [48] which requires complex finite state machines for impedance matching and the amount of required equalization to reduce the channel loss.

Signal integrity needs to be explored for large design space to transfer data across backplanes. Impedance mismatch between driver termination, vias and stub impedance mismatch which results in reflections leading to closed eye at the receiver front end. The is

further exacerbated degraded due to high attenuation of traces and cross talk between adjacent channels. To improve the BER specifications adaptive equalization is required at transmitter and/or at the receiver [49]-[58].

Transmit and receive equalizers are employed to compensate the channel loss, which in turn reduce ISI resulting from band-limited channels. To reduce the reflection coefficient, a transceiver was proposed [59] that employs a 4-tap FFE followed by DAC which is used for impedance matching while introducing programmability into the design. The calibration mechanism employed in the architecture is limited by quantization error of the calibration bits which increases proportionally to data rate for data transfer applications across multi data rates.

Power integrity analysis of serial-link drives the serial-link architect to explore the design space for possible power saving topologies meeting the required data rate required. In this direction [60], has modeled the power analysis of high speed serial links by employing SST drivers at transmitter in addition to enabling equalization capability at the transmitter. However FFE draws more power. The architecture can be made more power efficient by implementing adaptive CTLE at the receiver.

There are various problems associated with design link such as channel attenuation, reflection loss. The problem is further aggravated when multi-rate applications are to be designed in lower technology nodes with primary emphasis on low-power architectures. To deal with signal and power integrity issues in the context of transceiver termination in addition to boosting of high frequency signals, a combination of voltage-mode driver for transmitter termination and current mode driver implementing pre-emphasis called hybrid mode implementation was proposed[61]. The SST has advantage of power savings of 4X the current mode while the later offers low complexity and boosting the High Frequency (HF) signals. To avoid the loading effects, complex segmented drivers in case of voltage-mode implementation, in addition to provide signal isolation between the serializer block and signal transistors, a pre-driver circuitry is employed. The termination in transmitter is implemented by series termination where an impedance control loop which adjusts the output transistors in the driver's section to distribute the equivalent segmented tap weights which out-grow geometrically for higher resolutions. In the current-mode implementation the added advantage is high-resolution equalization without significant increase in pre-driver design complexity which is controlled by a current controlled DACs.

Impedance match for wide range of frequencies and for multi-standards with the lower power consumption has been a design challenge for transferring data across serial links in particular at lower technology nodes. To combat these bottle necks at lower voltages, a near ground termination is implemented in SST design style by using a common gate-amplifier (CGA) to match replica transconductance impedance which controls impedance matching in the presence of common mode noise. The impedance calibration control logic was presented by [62] to operate for multi-standard's which burns more power as calibrating effective transconductance across Process Voltage and Temperature [PVT] slows down the achievable data transfer rate.

There are two forms of on-die termination (ODT) Viz., current –mode and voltage mode. The current mode design style is power inefficient, so voltage mode is usually preferred as it consumes less than quadrant of power consumed by current mode. To increase the power efficiency a shunt branch is added in parallel to that of the channel impedance, this form of termination is called Impedance modulated pre-emphasis voltage-mode transmitter [63]. The topology achieves equalization at the cost of impedance mismatch , this situation further degrades for backplane channels as number of discontinuities are introduced due to packages and vias which were introduced for signal coupling across the backplane. The whole process introduces impedance mismatch which leads to high reflection loss coefficient which in turn takes away majority benefit when used for long haul backplanes.

The voltage mode ODT suffers from various issues such as degraded HF boosting at very high data rates coupled with high power dissipation incurred in pre-drivers and its digital logic control circuitry. To improve the performance of serial-link termination circuitry, a common-drain amplifier was proposed to be used [64] in place of resistors which act as load with a pseudo CML implementation. The above described technique has no impedance control over vast frequency range and multi data standards.

This thesis explores circuit strategies to implement power efficient on die termination with equalization.

## 2.3 Dynamic Comparator

To decrease the resolving time, a bandwidth modulation technique is employed that introduces negative feedback which also reduces the reset time of the regenerative stage of

dynamic comparator [65]. The above described bandwidth modulation technique when applied to comparators used in multi standards application like USB2,USB3 and PCI-express gen 4 under performs the power bandwidth product criteria as power quadratically increases with loop bandwidth.

Digitization has made signal processing an easy task but converting the analog signal to the equivalent digital code is cumbersome in power constrained architectures. The main component used in Analog to Digital Converter (ADC) is dynamic comparator which employs positive feedback to convert small input differential voltage to full-scale voltages. The peak-to-peak voltages are coupled back to the input node during regeneration, which causes spikes or some-times perturb the common-mode level which is called as kickback noise (KBN). To minimize KBN, various noise reduction techniques viz 1) Node isolation and 2) Neutralization techniques are being proposed [66].

Comparators act as decision making logic in many circuits, the performance of comparators are limited primarily by the offset voltage at the input of comparator, whose contribution is more in dynamic comparator relative to the static one due various mismatches such as threshold, transconductance and effective load capacitance at the output node during regenerative phase. To reduce the effect of offset, while trading carefully with power consumption, an offset cancellation (OC) was proposed [67] where the body voltages of the input transistors are tuned to capture the change in output voltage during regeneration phase. This scheme essentially requires a single clock phase. The above proposed technique is novel in nature which assumes the PVT across the design is constant which when inspected from yield point of view but the offset cancellation degrades as no on die trimming mechanism is employed to have threshold control across process corners.

The usage of high speed ADCs at the front end of high speed serial links is gaining momentum in the recent past. To resolve this tangle an attempt was made [68] through a topology in which dual tail dynamic comparator which has regenerative feedback in both pre-amplifier and output stage. To minimize KBN low impedance path is created from output of first stage to both input of output stage and ground.

This thesis attempts to design circuit strategy for comparators in order to minimize KBN and input referred noise suitable for high speed serial links.

## 2.4 Phase Locked Loop

As clock speeds have entered into Giga hertz regime, constraint on clock jitter and duty-cycle distortion has made specification more stringent.[69]. For meeting excessive tuning range specifications in LC-VCO, a multiplier pass loop ring oscillator structure with saturated gain approach was proposed[70]. The attractive aspects of this approach stems from its simplicity. The ring oscillator can be realized with ease in any Complementary Metal Oxide Semiconductor (CMOS) process node.

The output voltage of the ring oscillator is being affected generally by tail current source and besides tank loading effects. The effect of numerous noise sources in the circuit used were analyzed by [71] and it is shown that the cumulative noise added by means of the transistors in the differential pair can be scaled down at ease by exploiting cyclo-stationary effects of the sources.

A PLL is used at front-end to preserve synchronization in the serializer/de-serializer pair. The negative-feedback present in the PLL corrects any difference in time period detected at the input of Phase detector (PD). To grasp the SerDes technology, it is essential to have a basic perception of how a PLL operates. The underlying functionality of SerDes PLLs is to synchronize the input frequency (typically  $\text{clkin}$ ) and a generate core frequency. The designed center frequency is accountable for the serialization timing generated from the PLL. A phase detector is used in the front of the loop to assign a small delta change which is generally fed into a filter, whose output voltage controls Voltage Controlled Oscillator (VCO) which in turn tunes the output frequency. A divide by means of switch function is then responsible for the last charge of the ' $\text{clkin}$ ' to the PLL frequency.

The evaluation of clock jitter has advanced as signaling rates have increased. In high pace serial links clock jitter influences the receiver efficiency. The emphasis is now on quantifying the relativity of clock quality to device realization in terms of the BER [72].

A series of direct coupled cascaded chain of inverters is being proposed as a new delay generator. The delays achieved by circuit is proportional to the buffer delay. The advantage of this architecture is that the array of inverters have uniform offset in phase in constant fraction to the buffer delay [73] which varies across PVT and thus has degraded phase noise performance which is not suitable for designs which require minimum cycle to cycle jitter.

The timing jitter of entire design is proven to depend on the jitter generated by the ring oscillator and its rate of accumulation is inversely proportional to the bandwidth of the phase locked loop (PLL)[74].

Charge pumps are utilized to convert the timed logic into analog quantities for controlling the locked oscillators [75]. Practical limits of multi-tone signaling over very high data-rate backplane electrical communication channels are presented in [76]. Application of discrete multi-tone (DMT) signaling to high speed backplane interconnects requires fundamental adjustments to the standard evaluation strategies utilized in wire line communication systems. Tight energy budgets in backplane links impose severe constraints on DMT block dimension and use of channel shortening filter in the system. First order evaluation of a linear oscillatory systems leads to a noise shaping function and a new definition of quality factor (Q). A linear mannequin of CMOS ring oscillator is used to calculate its phase noise along with three segment noise viz. additive noise, high frequency multiplication noise and low frequency multiplication noise [5].

There are three most important predicaments that can limit the overall performance of high-speed links namely clock frequency, channel bandwidth and timing accuracy. It makes use of the figure of merit of a (FO-4) inverter to measure the overall performance of circuits that must scale with technology. Since the quandary (in terms of FO4) remains roughly consistent with scaling, limitations that do not scale with technology are measured in pico-seconds and likely establish a closing bound to a serial-link performance [6].

The effect of numerous noise sources in the circuit used are analyzed and it is shown [78] that the cumulative noise added by means of the transistors in the differential pair can be scaled down by exploiting cyclo-stationary effects of the sources.

Initially state -equation methodology was adopted to analyze the large -signal lock acquisition process and small signal linear tracking behavior of a third-order charge-pump PLL. To have intuitiveness of the PLL, noise transfer function is analyzed in Z-domain and the non-linear state equations are worked out for small perturbations. Secondly, impulse-invariant transformation and s-domain methods are compared [79].

The spectral characteristics of PLL were analyzed using stochastic partial differential equations taking into boundary conditions caused by the loop filter, Phase-Frequency Detector (PFD) and VCO [80].

Power supply rejection ratio constitutes an important specification of PLL that influences PLL's jitter characteristic. A CMOS quad transceiver was proposed by [81], which has dual-loop PLL. To mitigate the jitter introduced by the supply, the dual-loop PLL was designed to have two supply regulators, whose band width is adaptive, one with high bandwidth and latter having low bandwidth for digitally controlled phase interpolator which reduces the power supply rejection ratio (PSRR). Current starved ring oscillator was being employed which has wide tuning range that can be used for robust integration with various serial-link interfaces.

A discrete-time open-loop dynamic model of PLL and DLL was presented by [82] that exhibits adaptive bandwidth optimizes the performance over wide frequency range over Process Voltage Temperature (PVT). This was characterized based on the sampled error from the response.

As discussed earlier Power supply rejection ratio (PSRR) forms an important specification in designing analog circuits especially, signal processing circuits with special emphasis on PLL. Deterministic jitter is caused by random variations in the circuits such as power supply hence the design of voltage regulator needs a special care in context of PLL. To decrease the jitter caused by PSRR, another compensation technique was proposed by [83], which employs replica based biasing and thus the stability of loop can further be improved. The main draw back of the proposed PLL with replica based biasing is that there is no control mechanism on effective transconductance of replica pair with process, which further needs to have a constant transconductance circuit that limits the tuning range.

Inverters are generally used as leaf cell in the design of ring oscillator (RO). To analyze the noise component in inverter, a time-domain jitter calculation method was proposed by [84] to quantize and simulate white noise and flicker noise component by VCO modulation.

Tuning range plays a very important role while integrating a PLL across different process nodes and serial link standards. A regulated tuned supply is being proposed to improve PSRR and satisfy the jitter specifications [85].

The channel attenuation and reflection loss play a pivotal role in design of a high speed serial transceivers. To mitigate the above affects, a 5-tap DFE and 4-tap FFE was proposed by [86] at the transmitter and receiver to reduce the BER. Further a low jitter PLL was synthesized using LC VCO in the transceiver which trades off being with lower tuning range, higher power consumption, area and mostly need additional fractional divider circuitry for multi standard which further reduces the gain of VCO.

To increase the program-ability and to have independent control on the loop bandwidth and settling time in PLL, [87] has proposed a dual-loop PLL architecture which replaces the resistor in proportional path with a sample-hold circuitry which further decreases the noise. This proposed PLL reduces the thermal noise with increase in shot noise. In addition the designed circuit needs to have constant impedance control mechanisms within tolerable limits which further questions the system stability when used for multi standard applications.

Power optimization without compromising the signal integrity is the main focus of multi-rate data transfer over back-plane channels. To meet the power constraints, the design parameters such supply voltage and current are scaled based on the required signaling rate whose optimization is characterized by nonlinear cost function. To boost the signal across the receiver, PLL (which functions as frequency synthesizer) is shared across the transceiver, in addition to minimizing the offset at front-end of the receiver which now saves large chunk of power while adopting active inductor approach[88].

The jitter needs to be made independent of both input and output clocks. The data dependent jitter was proposed to be minimized by[89]. Applying techniques such as minimizing the power consumption of VCO and loop filter. Also the loop bandwidth is chosen aptly that minimizing phase noise contribution of PD, LPF, VCO and frequency divider.

Phase noise forms an important design specification in the design of CDR architectures, which may be degraded by limited acquisition range of frequency locked loop FLL, phase error caused by glitch in control voltages of VCO and high gain or VCO. To counter this, [90] a dual-loop CDR architecture was proposed which smoothly shifts the control from phase acquisition loop (PAL) to the frequency loop (FL), thereby minimizing the phase noise degradation and in addition maintaining the minimum phase margin to design a stable system. To increase the conversion efficiency of charge-pump (CP) and LF circuitry, the width of error signal from the PD is increased by modifying the half-rate PD there by reducing the phase error between the recovered clock and random data signals. The designed

PD increases the width of error , up and down pulses but when the circuit is used for full rate applications, the V-I converter which follows the PD may not settle suitably thereby creating ripples across the control voltage, losing the loop locking mechanism.

To meet the jitter, power and swing specifications of multi-standard PLL and CDR, [91] proposed an architecture with the following features such as employing an equalizer both at transmitter and receiver. The swing across the transmit FFE was made programmable while DFE was made adaptive.

A discrete-time delay cell was proposed by [92] to add a zero in the open loop transfer function of the phase-locked frequency synthesizer which also in-turn reduces the thermal noise introduced by the resistor in the loop filter. The introduction of zero stabilizes the loop in-addition to which eases the design cycle aspect pertaining to settling time and magnitude of spectral components outside the desired band of frequencies which are called as reference spurs.

The urge to decrease the power consumption in frequency synthesis has brought the PLL based clock multiplier and DLL(Delay Locked Loop) as available architectures of which PLL based topology generates less jitter while power consumption is more in DLL based ring oscillator. The jitter accumulation which determines the jitter tolerance when employed in CDR is less in VCO of PLL [93].

Power and speed constraints are important bottleneck of serial links. To obtain a tradeoff, a chain of interpolating inverters were proposed to be used to generate multi-phase clocks by [94]. This technique is employed in feedback loops to obtain higher speed of operation and precise phase spaced clocks which allow the feasibility of higher speed operation in CMOS based PLL.

Loop bandwidth plays a vital role which determines the settling time of a system. Adaptive control of reference clock frequency and frequency divide ratio extends the loop bandwidth considerably [95].

In this research, an attempt is made to design a PD used in the front end of PLL to improve the jitter characteristics.

## 2.5 Clock and Data Recovery

In order to reduce the systematic phase offset present in PD, a circuit strategy was proposed by [96] that exhibits linear characteristics, retiming and de-multiplexes. The proposed architecture also employs an interpolating VCO phase-locked CDR. A phase interpolator was introduced which needs to have a overlapping interval across process corners. This feature when evaluated across PVT limits the control voltage of the PLL which in turn reduces the tuning range and gain of VCO increasing jitter.

Jitter is defined as random movement of signal depending on the traversing path, generating source and interference. The data-dependent jitter (DDJ) is a time domain representation of multiple dispersed bits more than 1UI. The serial-link figure of merit (FOM) in terms of BER degrades for high-date signals due to limited bandwidth of the back-plane. A method to quantify DDJ was proposed by [97] which uses step response of current and preceding bits as the starting factor, seemingly the computation time grows linearly instead of exponential nature.