# **Design and Realization of Novel Adaptive Digital Beam Former Architecture for Active Phased Array Radar**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**Doctor of Philosophy**

by

**Govind Rao Doddamani

(Roll No. 701144)**

Supervisor (s):

**Dr. T. Kishore Kumar**

**Dr. A. Vengadarajan**

**DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

**NATIONAL INSTITUTE OF TECHNOLOGY**

**WARANGAL – 506004, INDIA.**

**February 2019**

## APPROVAL SHEET

This Thesis entitled "**Design and Realization of Novel Adaptive Digital Beam Former Architecture for Active Phased Array Radar**" by **Mr. Govind Rao Doddamani** is approved for the degree of **Doctor Philosophy**.

### Examiners

.....

.....

### Supervisor (s)

.....

**Dr. T. Kishore Kumar**

**ECE Dept., NIT Warangal**

.....

**Dr. A. Vengadarajan, Sc-G**

**LRDE, DRDO, Bangalore**

### Chairman

.....

**ECE Dept., NIT WARANGAL**

Date:

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Design and Realization of Novel Adaptive Digital Beam Former Architecture for Active Phased Array Radar**" is a bonafide work done by me under the supervision of Dr. T. Kishore Kumar, ECE Dept., NIT Warangal and Dr. A. Vengadarajan, Director, DG ECS Office, DRDO, Bangalore, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission brings my own ideas in my own words and others ideas or words have not been included. I have sufficiently quoted and referenced the original sources wherever it was used. I have followed to all principles of academic honesty and integrity and have not misused or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been suitably cited or from whom proper permission has not been taken when needed.

**(D. Govind Rao)**

**(Roll No. 701144)**

**Date:**

# National Institute of Technology, Warangal

(Deemed University)

## CERTIFICATE

This is to certify that the thesis entitled "**Design and Realization of Novel Adaptive Digital Beam Former Architecture for Active Phased Array Radar**" being submitted by **Mr. Govind Rao Doddamani** in partial fulfilment for the award of the degree of **Doctor of Philosophy** to the Department of Electronics and Communication Engineering of National Institute of Technology Warangal, is a record of bonafide research work carried out by him under our supervision and has not been submitted elsewhere for any degree.

**Dr. T. Kishore Kumar,**

(Supervisor)

Dept. of Electronics & Communication

Engineering,

National Institute of Technology,

Warangal – 506004, India.

**Dr. A. Vengadarajan,**

(Co-Supervisor)

LRDE,

DRDO, Govt of India

C. V. Raman Nagar

Bangalore – 560093, India.

## ACKNOWLEDGEMENTS

At the outset, I take immense pleasure to convey my sincere gratitude to my supervisors **Dr. T. Kishore Kumar, Prof. N.S. Murthy and Dr. A. Vengadarajan**, Director D.G ECS Office, DRDO, Bangalore, for their perpetual encouragement and supervision. Their steady influence throughout my Ph.D. career has oriented me in a proper direction and supported me with promptness and care. They listened to my ideas and discussions led frequently to key insights and gave full support even in the state of despair. I truly appreciate their logical and thought provoking advice both technically and morally which I will follow for the rest of my life.

I thank all the faculty and non-teaching staff of Dept. of ECE at NIT Warangal who helped me during the course. I am also grateful to Prof. N.V.S.N. Sarma, Dr. B. Laxmi and Dr. L. Anjeneyulu Department of Electronics & Communication Engineering, for his invaluable assistance and suggestions that he shared during my research tenure.

I take this privilege to thank all my Doctoral Scrutiny Committee members, Prof. K.S.R. Krishna Prasad, Professor of Department of Electronics & Communication Engineering, Prof. Vinod Kumar, Electrical & Electronics Engineering Department, Prof. T.Ramesh, Computer Science Engineering Department and Prof. G. Radhakrishnamacharya, Mathematics Department, for their detailed analysis, productive suggestions and exceptional advice during the progress of this research work.

I thank my nation India and all the people supported me directly and indirectly including Director LRDE, DRDO Bangalore for supporting me to carry out my research work at the NIT Warangal.

I also extend my heartfelt appreciation to all my colleague scholars, friends and well-wishers who helped to write my thesis with their support. Finally I would like to acknowledge my biggest debt to my parents and my wife for their constant support.

**(D. Govind Rao)**

## ABSTRACT

The concept of beam forming in phased array was implemented with analog or mechanical solutions. The present day need is to have every element level beam formation instead of a group of elements combined in the RF domain. Element level beam formation was a major challenge to realize in hardware. Due to this limitation researchers have developed sub array level beam formers for phased array application but this brings many limitations like roll off of the sub array pattern which causes a gain loss in the re-steered direction (Reduces the range of the radar) and produces grating lobes.

The digital systems have become powerful to carry out the huge number of tasks required for real-time digital beam formation. Today many applications are using beam forming to enhance the effective channel utilization both in frequency and space, more digital dedicated architectures are proposed for the parallel and pipelined processing for communication applications. With the help of reconfigurable system, the same hardware platform can be reutilised for different applications with different processing needs. This thesis designed a novel method of hardware design and realization of adaptive digital beam former for phased array Radar application.

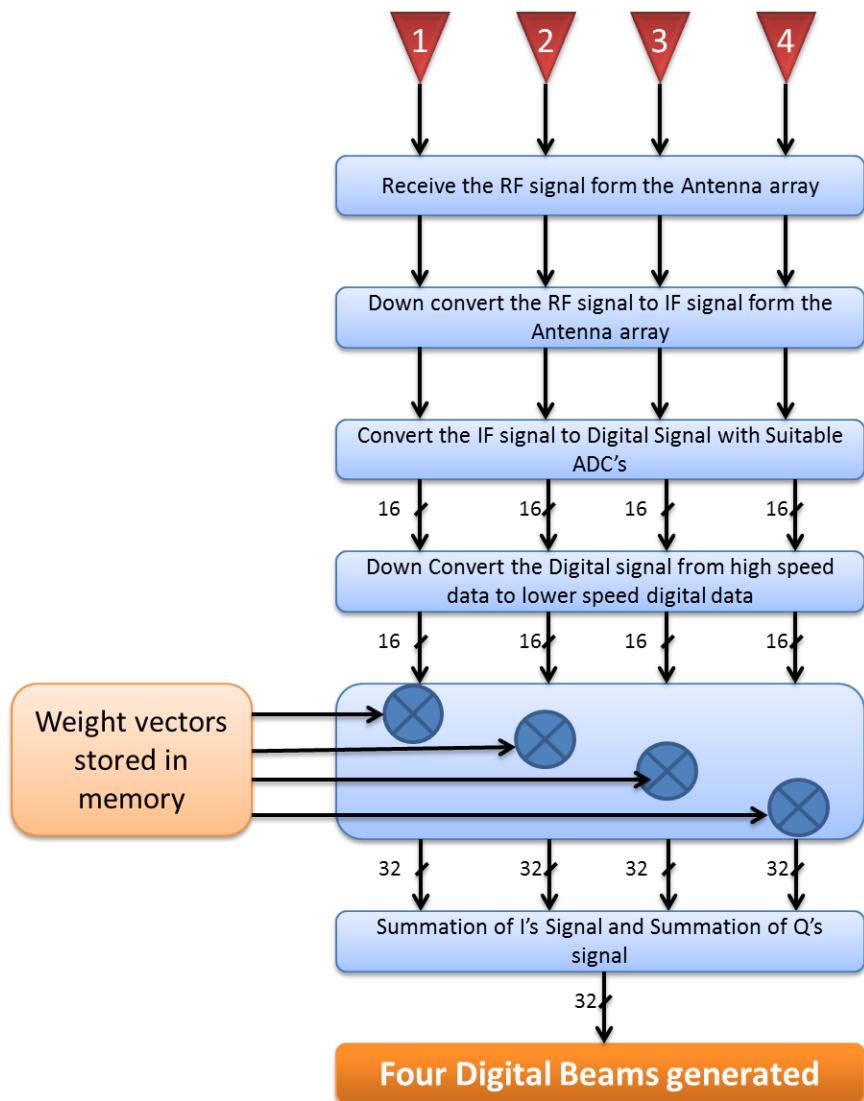

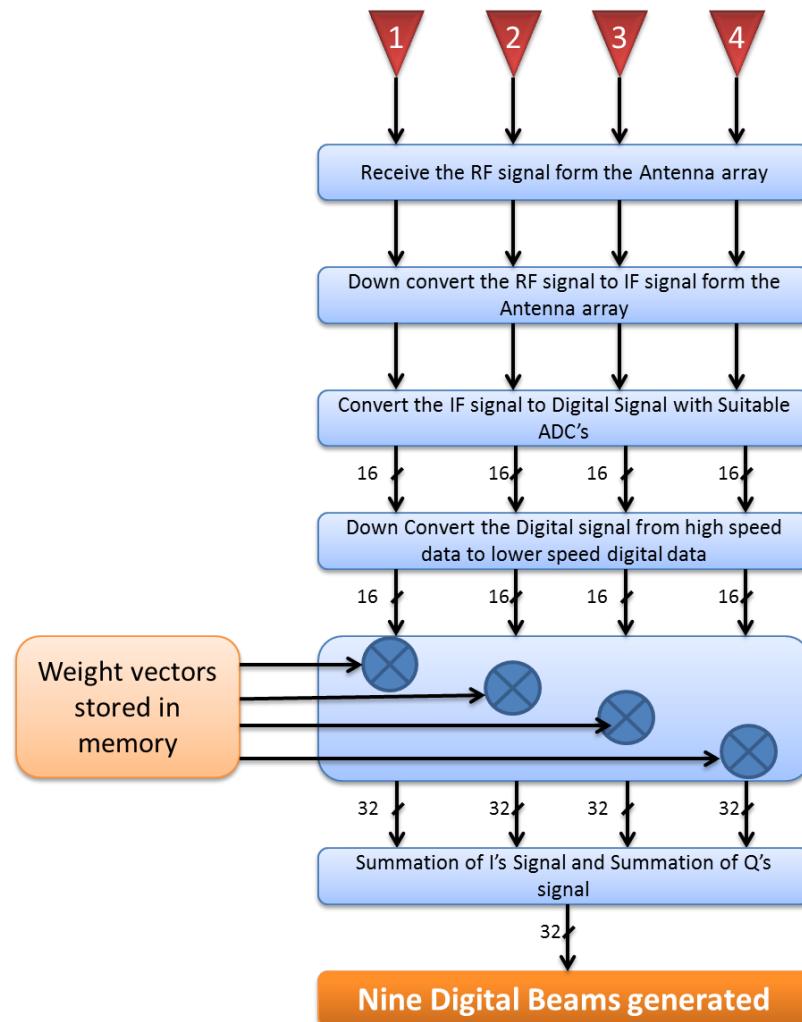

This research work was carried out considering a typical case of sixteen element planar phased array. Initially multiple digital beam formation is achieved using the computation of weights off line and stored in the memory of the digital board and 4 and 8 receive beams were formed. The digital beam formation with fixed weights architecture is designed and functional simulation has been carried out. The same architecture is implemented on the Virtex-VI FPGA based hardware and multiple receive beams were formed.

Further the architecture development is extended to computation of adaptive weights online and a parallel pipelined architecture is designed. A survey of various algorithms has been carried out for adaptive weight calculation and QR-Decomposition based Recursive Least Square (QRD-RLS) is identified as most suitable. Since this algorithm is computationally complex and takes more time for the optimal weight calculation a modified algorithm is developed for online weight calculation. The Inverse QRD-RLS algorithm is a most efficient adaptive algorithm and from the hardware realisation point of view it is optimised. A systolic structure method can be employed to calculate the weights in a given time and is numerically stable compared to other traditional algorithms.

The most suitable algorithm for pipelined and parallel implementation architecture is the inverse QRD-RLS algorithm. For phased array radar applications optimal weights must be computed in a short time of the order of few micro seconds with very good accuracy. In such cases Inverse QRD-RLS is most suitable.

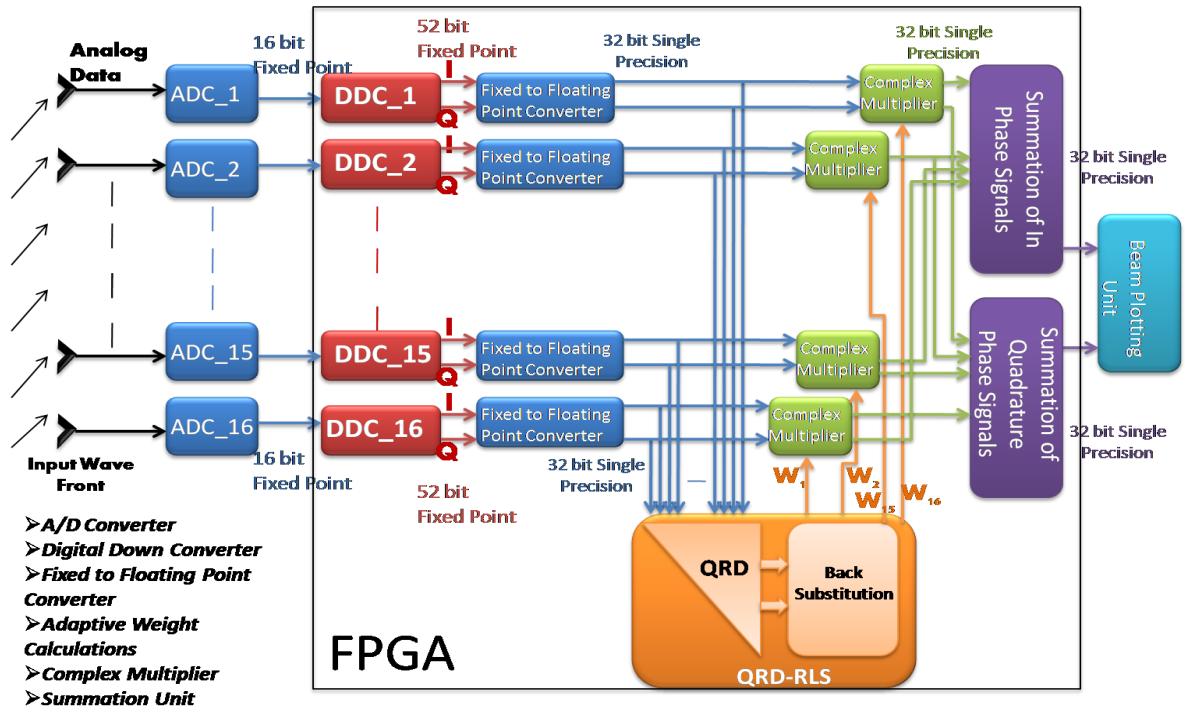

The novel architecture is developed for sixteen element planar phased array to form multiple receive beams for radar applications. Present day FPGA's are capable of concurrent processing, a three FPGA architecture is developed to form the adaptive beams simultaneously.

The outcome of this research work is realisation of generic, modular, scalable adaptive digital beam former architecture for a sixteen element planar antenna array configuration. This also can be extended for larger dimension in the phased array application.

# Contents

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>ACKNOWLEDGEMENTS .....</b>                                     | <b>1</b>  |

| <b>ABSTRACT.....</b>                                              | <b>3</b>  |

| <b>LIST OF TABLES .....</b>                                       | <b>12</b> |

| <b>LIST OF ABBREVIATIONS .....</b>                                | <b>13</b> |

| <b>Chapter 1.....</b>                                             | <b>15</b> |

| Introduction.....                                                 | 15        |

| 1.1    Beam Formation .....                                       | 15        |

| 1.2    Phased Arrays.....                                         | 17        |

| 1.3    Adaptive Filter.....                                       | 18        |

| 1.4    Motivation .....                                           | 19        |

| 1.5    Objectives and Contributions .....                         | 20        |

| 1.6    Thesis Organization.....                                   | 23        |

| 1.7    Summary .....                                              | 24        |

| <b>Chapter 2.....</b>                                             | <b>26</b> |

| Literature Review.....                                            | 26        |

| 2.1    Phased Array Radar .....                                   | 26        |

| 2.2    Digital Beam formation in phased array Radar .....         | 26        |

| 2.3    QR decomposition .....                                     | 27        |

| 2.4    Adaptive Phased Array .....                                | 28        |

| 2.5    Phased Array Systems and Applications in Radar .....       | 29        |

| 2.6    Fixed point operations and floating point operations ..... | 30        |

| 2.7    Papers Referred .....                                      | 31        |

|                                                                 |                                                                    |           |

|-----------------------------------------------------------------|--------------------------------------------------------------------|-----------|

| 2.8                                                             | Summary .....                                                      | 35        |

| <b>Chapter 3.....</b>                                           |                                                                    | <b>37</b> |

| Adaptive Filter Algorithms .....                                | 37                                                                 |           |

| 3.1                                                             | Introduction .....                                                 | 37        |

| 3.2                                                             | Recursive Least Squares approach .....                             | 39        |

| 3.3                                                             | Conventional QRD-RLS Algorithm.....                                | 40        |

| 3.4                                                             | Mathematical Model of Inverse QRD-RLS Adaptive Filter.....         | 41        |

| 3.5                                                             | Summary .....                                                      | 44        |

| <b>Chapter 4.....</b>                                           |                                                                    | <b>46</b> |

| Design and Modeling of Adaptive Digital Beam Former System..... | 46                                                                 |           |

| 4.1                                                             | Introduction .....                                                 | 46        |

| 4.2                                                             | Phased Array Antenna Model.....                                    | 46        |

| 4.3                                                             | Planar Phased Array Theoretical Background For Beam Formation..... | 47        |

| 4.4                                                             | QRD-RLS Algorithm .....                                            | 50        |

| 4.5                                                             | Implementation using Systolic Array Method.....                    | 51        |

| 4.6                                                             | Summary .....                                                      | 54        |

| <b>Chapter 5.....</b>                                           |                                                                    | <b>56</b> |

| Development of Adaptive Digital Beam Former Architecture .....  | 56                                                                 |           |

| 5.1                                                             | Introduction .....                                                 | 56        |

| 5.2                                                             | FPGA implementation of systolic array .....                        | 56        |

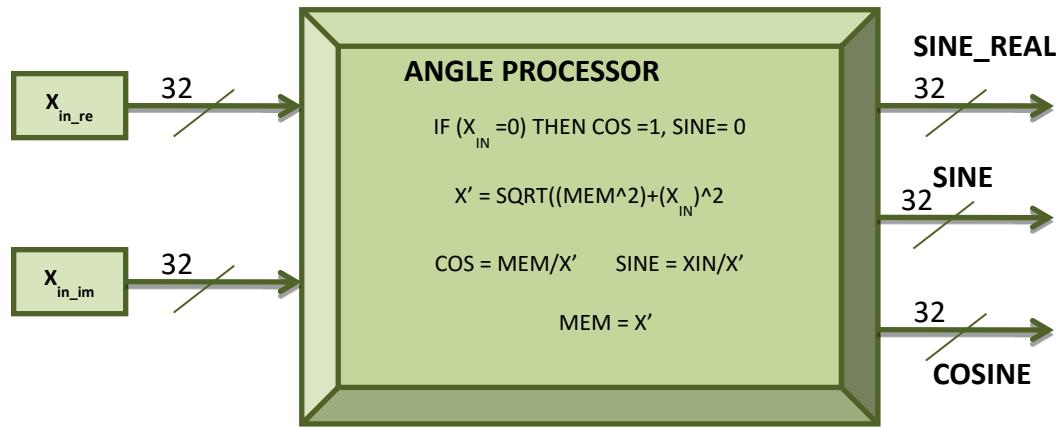

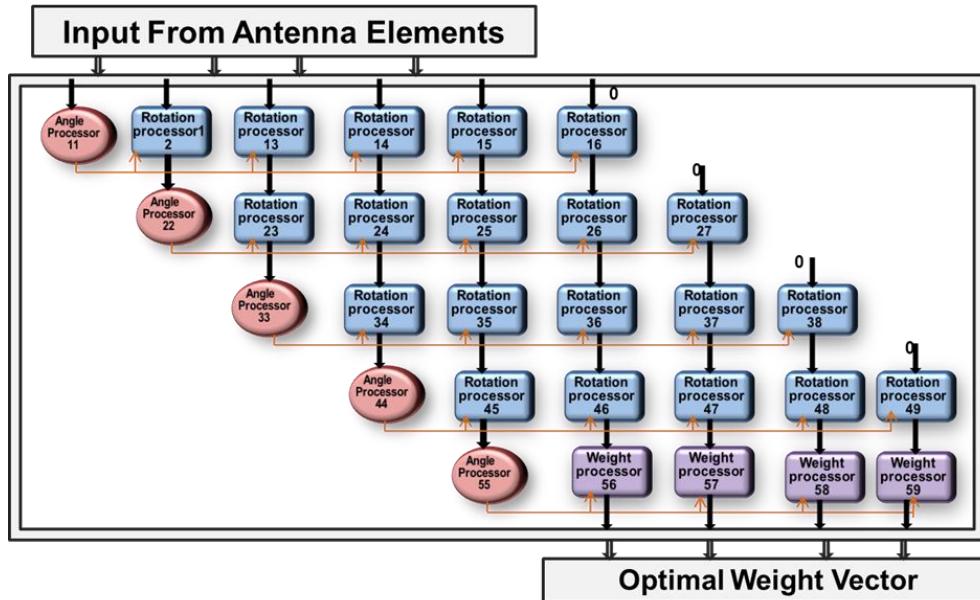

| 5.2.1                                                           | Angle processor:.....                                              | 57        |

| 5.2.2                                                           | Rotation processor:.....                                           | 57        |

| 5.2.3                                                           | Weight processor.....                                              | 58        |

| 5.3                                                             | Adaptive optimal weight computation Methods.....                   | 59        |

| 5.4                                                             | Adaptive weight computation using QRD RLS method.....              | 59        |

---

|                                                                 |                                                                                             |            |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|

| 5.5                                                             | Adaptive weight computation using IQRD RLS method .....                                     | 61         |

| 5.6                                                             | Fixed weight four element Beam Former architecture to form four simultaneous beams.....     | 64         |

| 5.7                                                             | Fixed weight Sixteen element Beam Former architecture to form nine simultaneous beams. .... | 66         |

| 5.8                                                             | Adaptive beam former architecture to form multiple beams .....                              | 68         |

| 5.9                                                             | Summary .....                                                                               | 73         |

| <b>Chapter 6.....</b>                                           |                                                                                             | <b>75</b>  |

| Hardware Realization of Adaptive Beam Former Architecture ..... |                                                                                             | 75         |

| 6.1                                                             | Realization of Fixed Weight Digital Beam Former .....                                       | 75         |

| 6.2                                                             | Realization of Beam Former Using Systolic Array .....                                       | 83         |

| 6.3                                                             | Realization of adaptive beam former architecture .....                                      | 87         |

| 6.4                                                             | Resource comparison.....                                                                    | 93         |

| 6.5                                                             | Summary .....                                                                               | 96         |

| <b>Chapter 7.....</b>                                           |                                                                                             | <b>98</b>  |

| Experimental Results and Discussions.....                       |                                                                                             | 98         |

| 7.1                                                             | Introduction .....                                                                          | 98         |

| 7.2                                                             | Results of Adaptive and fixed weights beam former architecture .....                        | 105        |

| 7.3                                                             | Results of Adaptive Beam Former using multiple FPGA configuration .....                     | 114        |

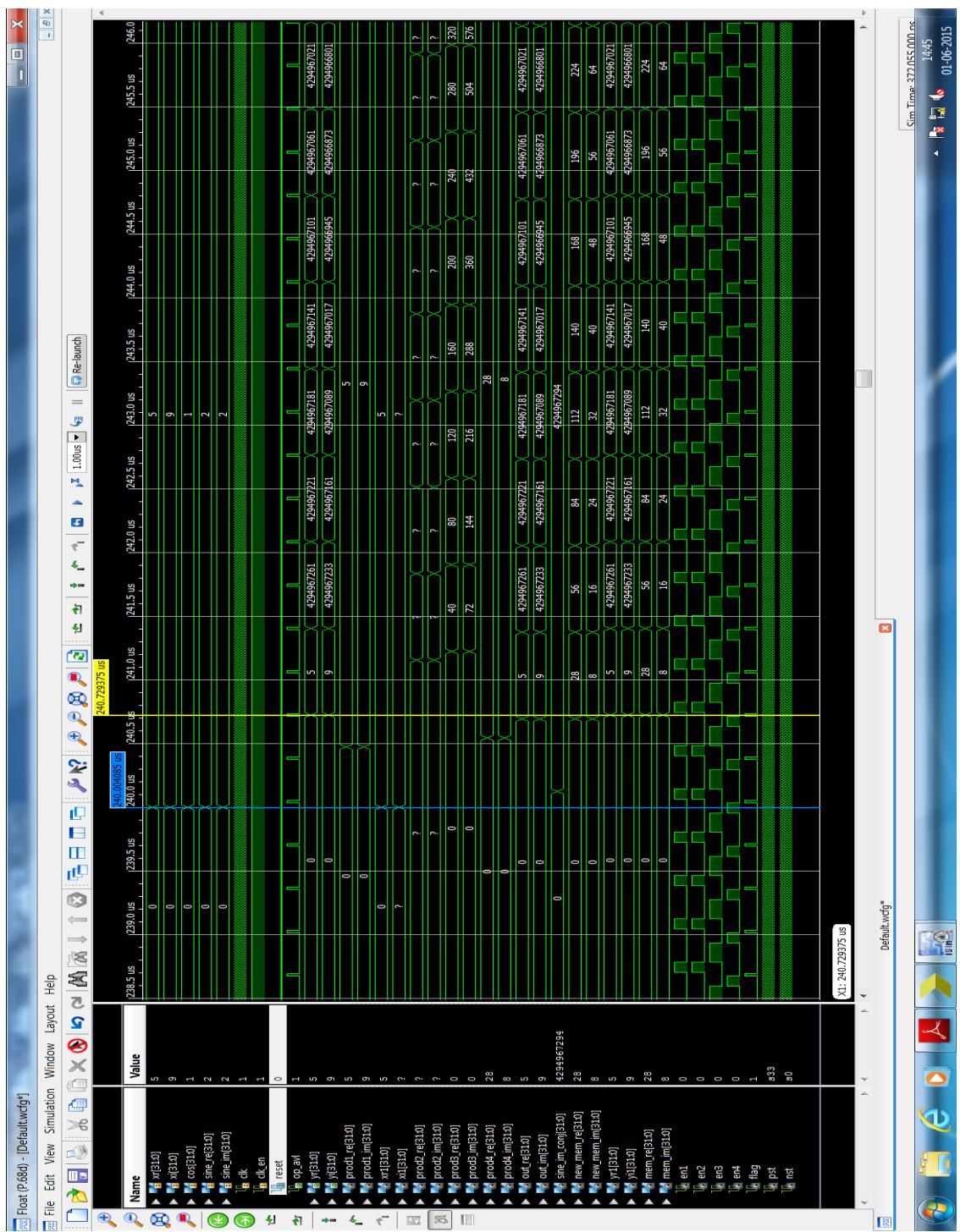

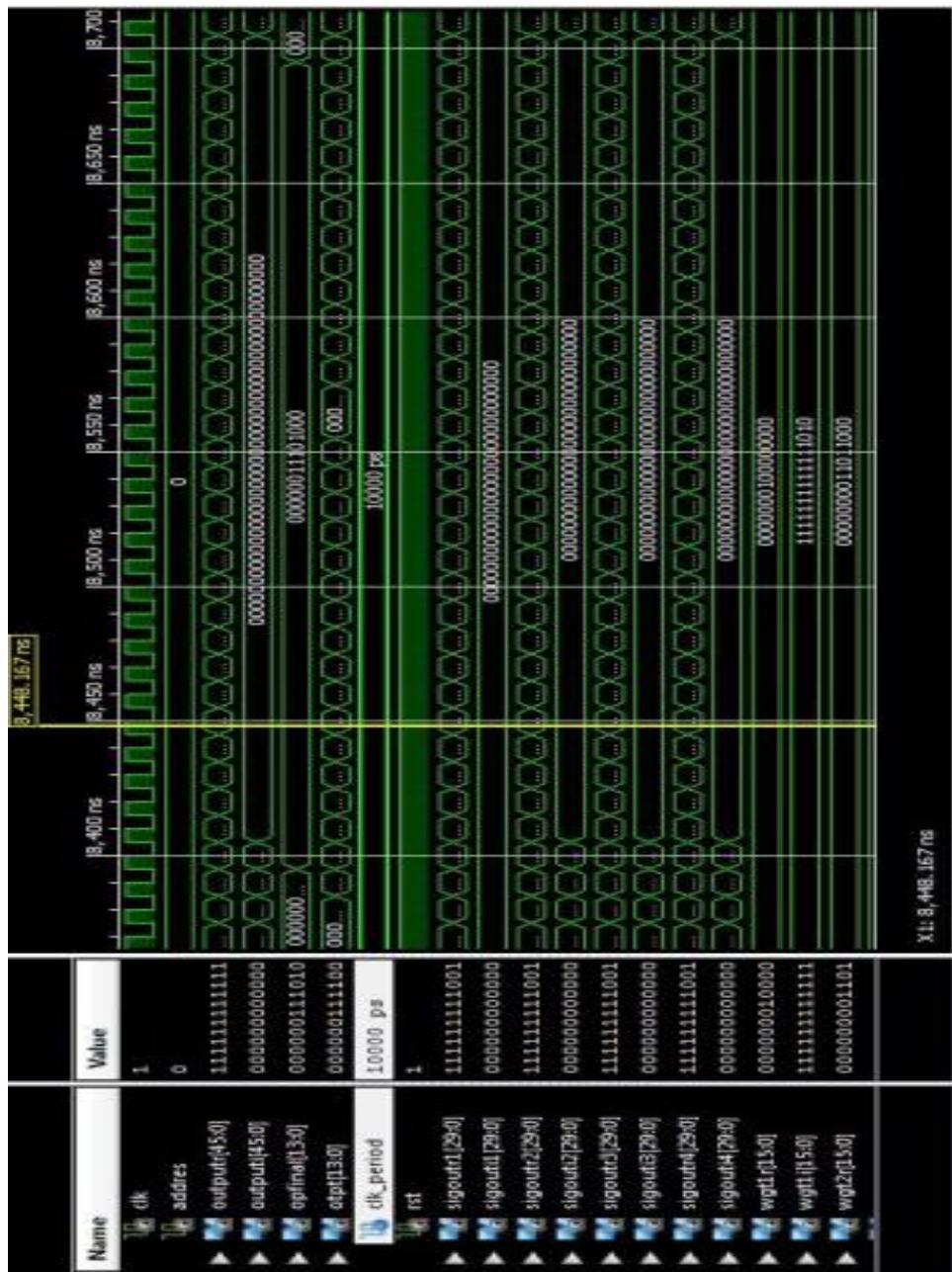

| 7.4                                                             | Results of Adaptive beams formed with Fixed point Operations .....                          | 118        |

| 7.5                                                             | Results of Adaptive beams formed with Floating point Operations .....                       | 120        |

| 7.6                                                             | Fixed and Floating point Error Analysis.....                                                | 123        |

| 7.7                                                             | Summary .....                                                                               | 124        |

| <b>Chapter 8.....</b>                                           |                                                                                             | <b>126</b> |

| Conclusions and Future Scope .....                              |                                                                                             | 126        |

| 8.1                                                             | Conclusions .....                                                                           | 126        |

| 8.2                                                             | Future Scope .....                                                                          | 128        |

---

|                   |     |

|-------------------|-----|

| Publications..... | 129 |

| References.....   | 130 |

## **LIST OF FIGURES**

|                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2-1: Generic Phased Array Receiver.....                                                        | 30 |

| Figure 3-1: Basic adaptive filter structure .....                                                     | 38 |

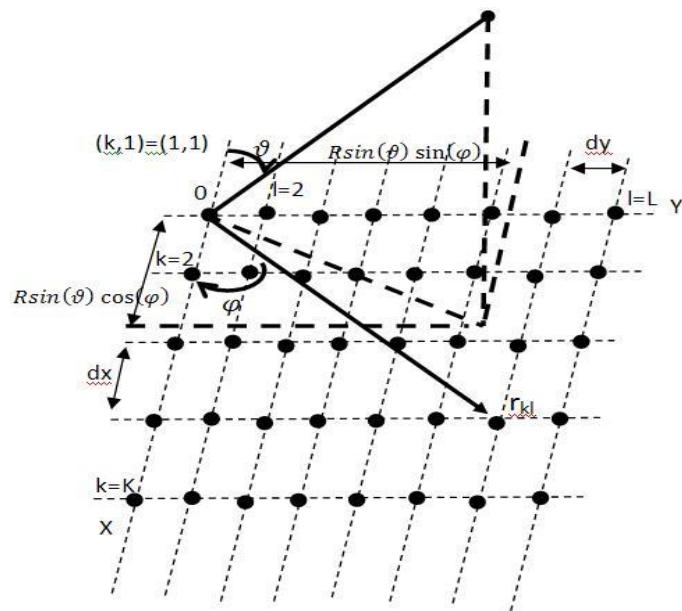

| Figure 4-1: Array Matrix of $K \times L$ elements represented in Cartesian coordinate system.....     | 47 |

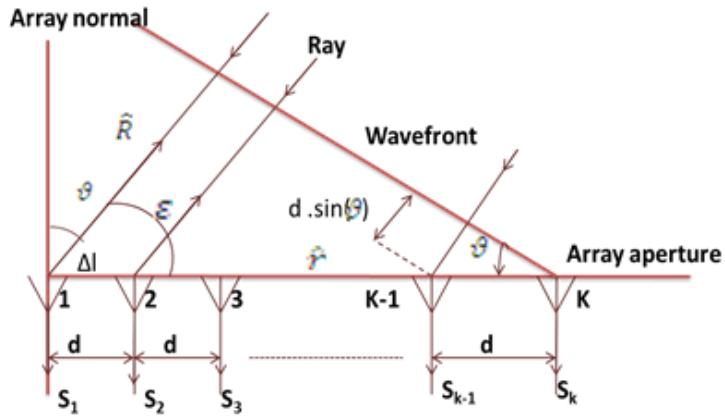

| Figure 4-2: A linear array of $K$ elements with $d$ as the inter-element distance. ....               | 48 |

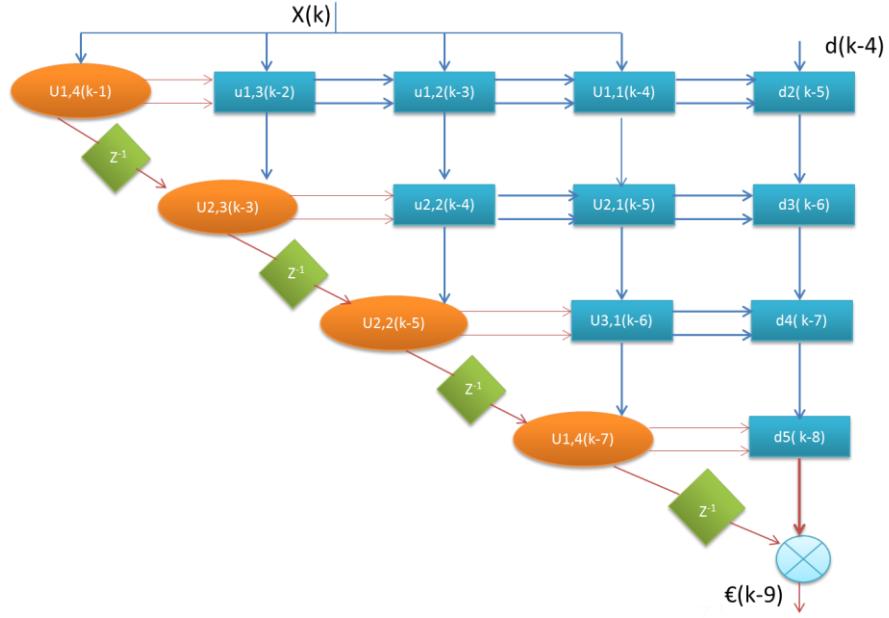

| Figure 4-3: Parallel and pipelined data flow in systolic array.....                                   | 52 |

| Figure 5-1: Angle Processor cell of Inverse QRD-RLS Algorithm. ....                                   | 57 |

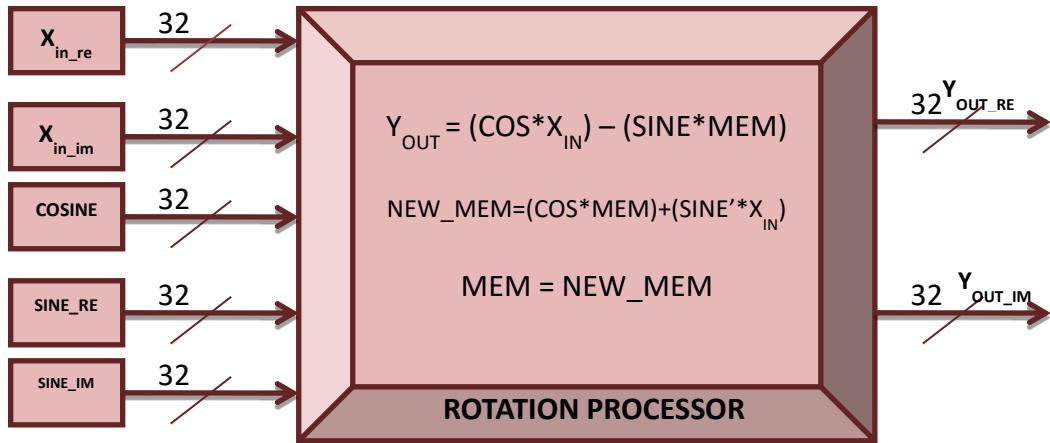

| Figure 5-2: Rotation processor of Inverse QRD-RLS Algorithm. ....                                     | 58 |

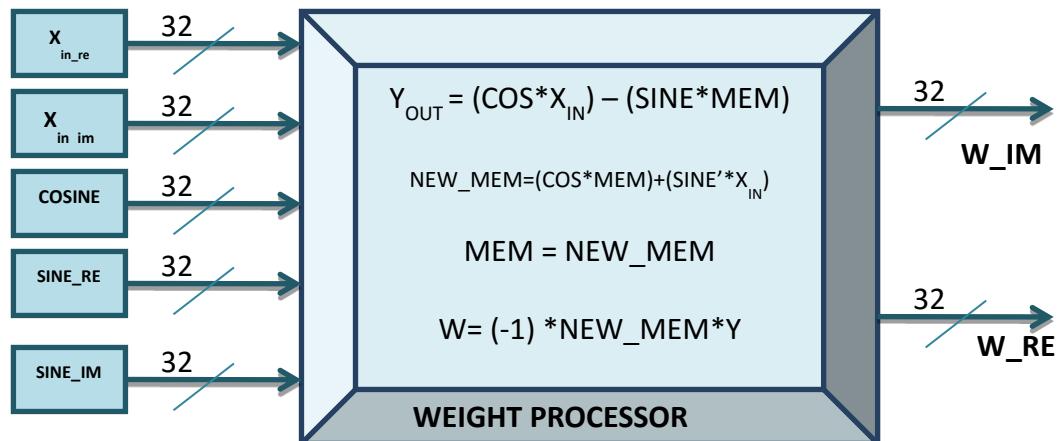

| Figure 5-3: Weight processor of Inverse QRD-RLS Algorithm .....                                       | 58 |

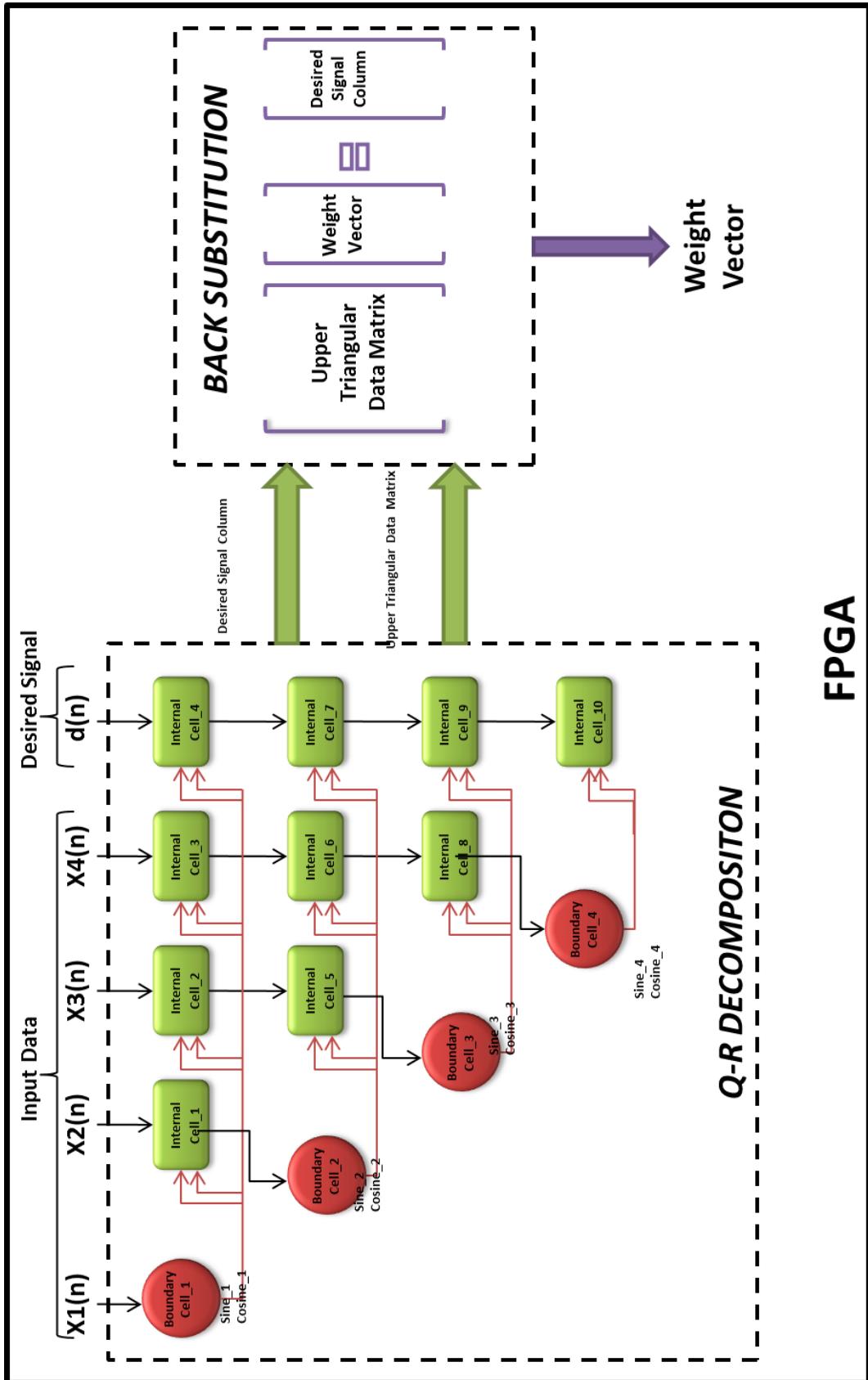

| Figure 5-4: Data flow of Inverse QRD-RLS algorithm for optimal weight calculation.....                | 60 |

| Figure 5-5: Pipelined Architecture of IQRD-RLS dataflow for VLSI Implementation.....                  | 61 |

| Figure 5-6: Data flow chart of four element fixed weight beam former to form four digital beams.....  | 64 |

| Figure 5-7: Architecture of Four element fixed weight beam former to form nine digital beams. ....    | 65 |

| Figure 5-8: Data flow chart of four element fixed weight beam former to form nine digital beams. .... | 66 |

| Figure 5-9: Architecture sixteen element fixed weight beam former to form four digital beams. ....    | 67 |

| Figure 5-10: Architecture four element fixed weight beam former to form one digital beam. ....        | 68 |

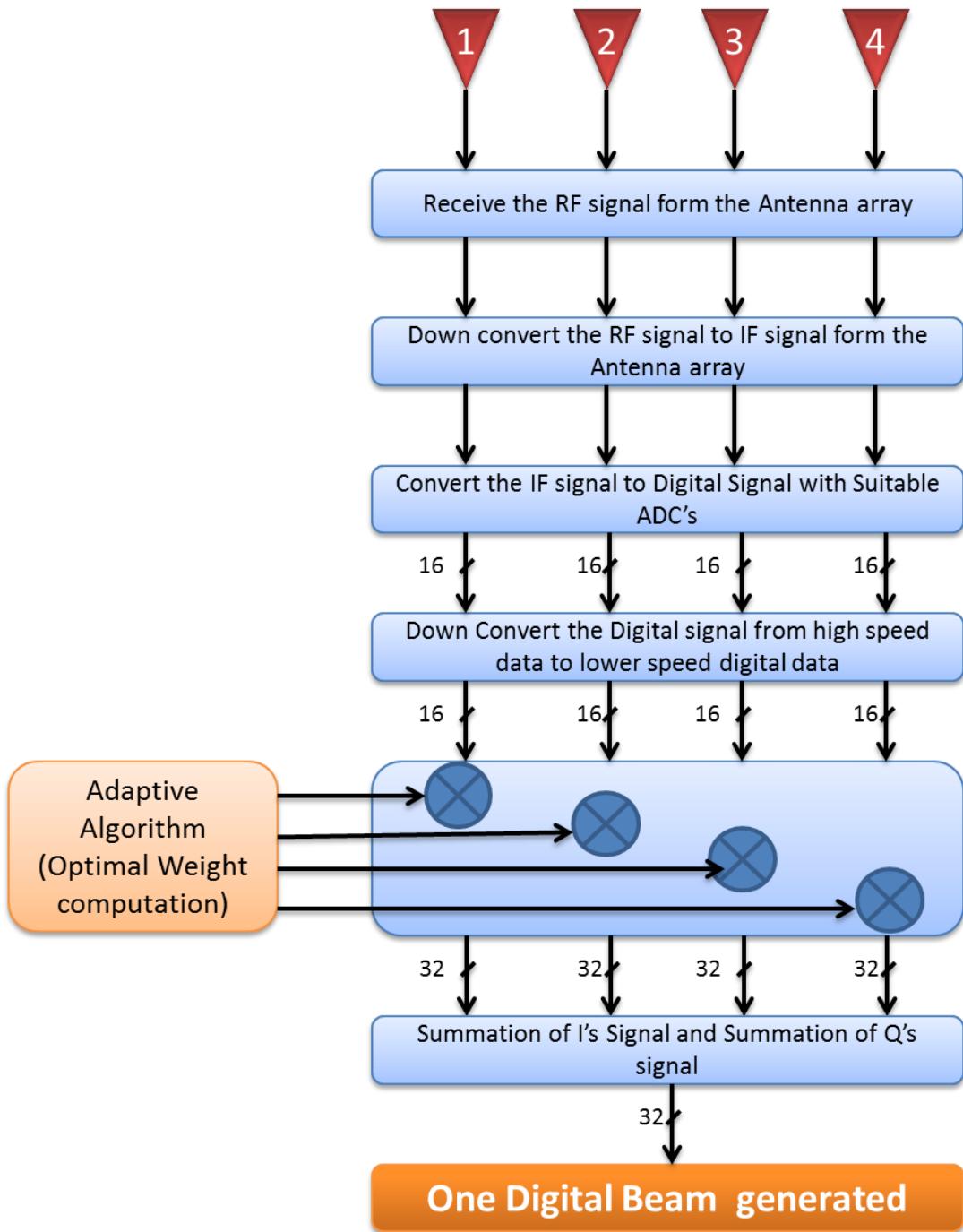

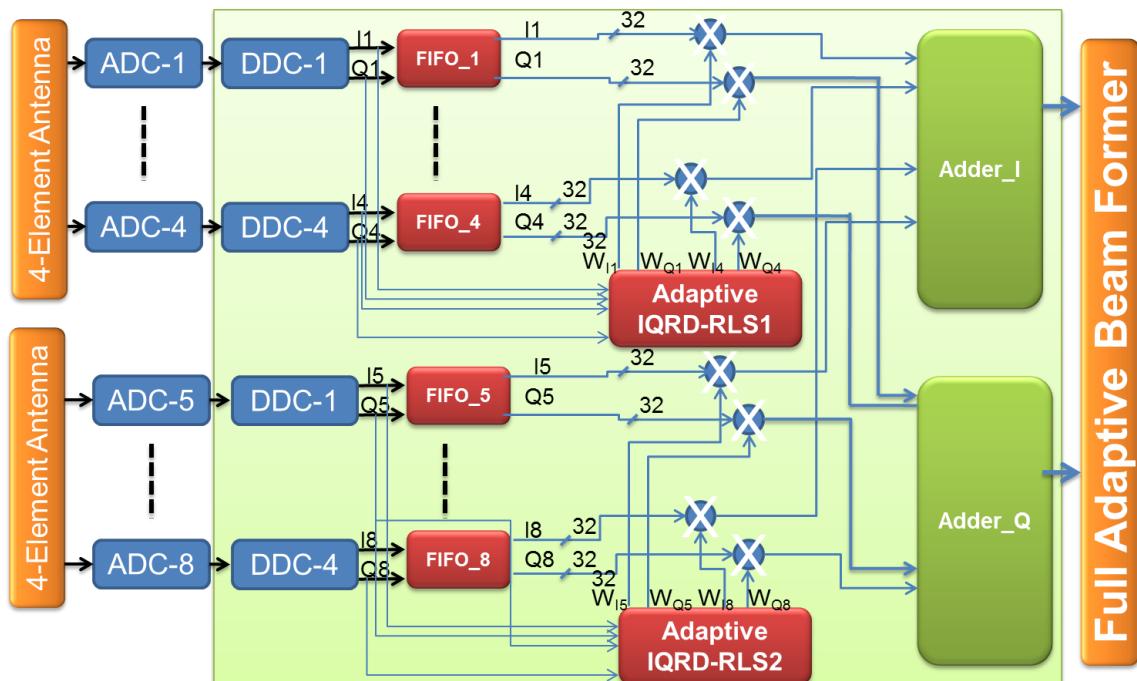

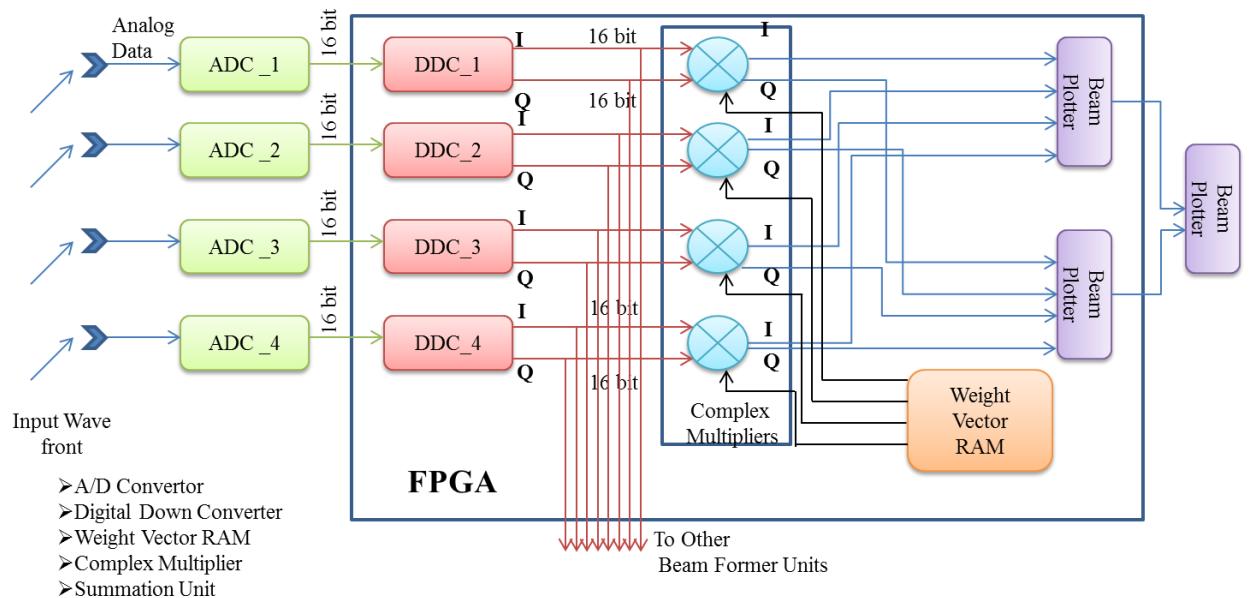

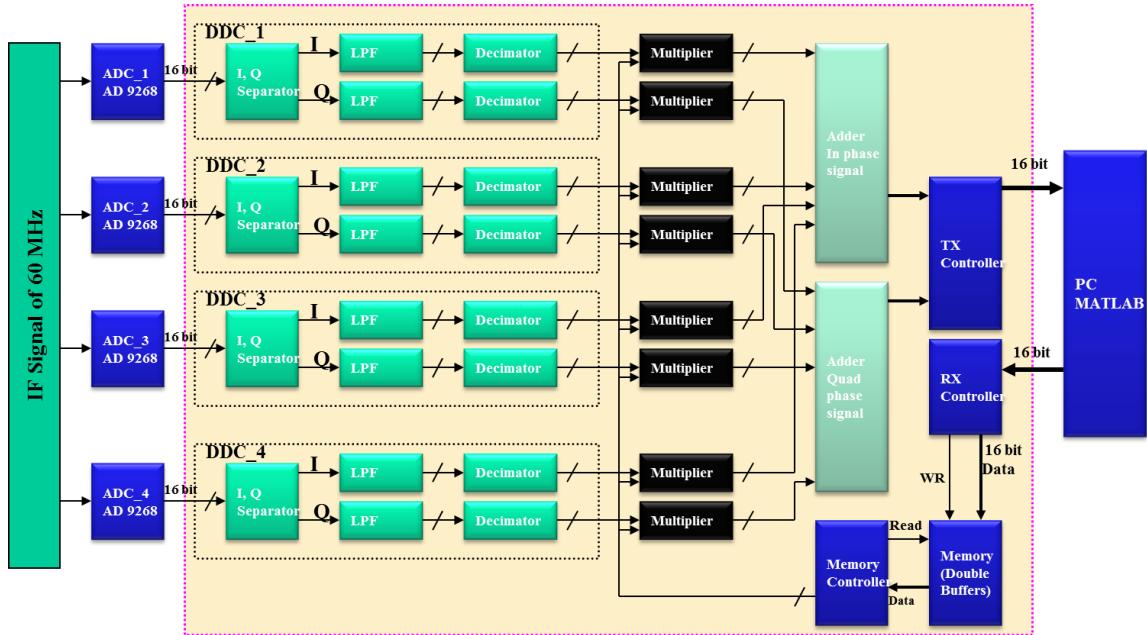

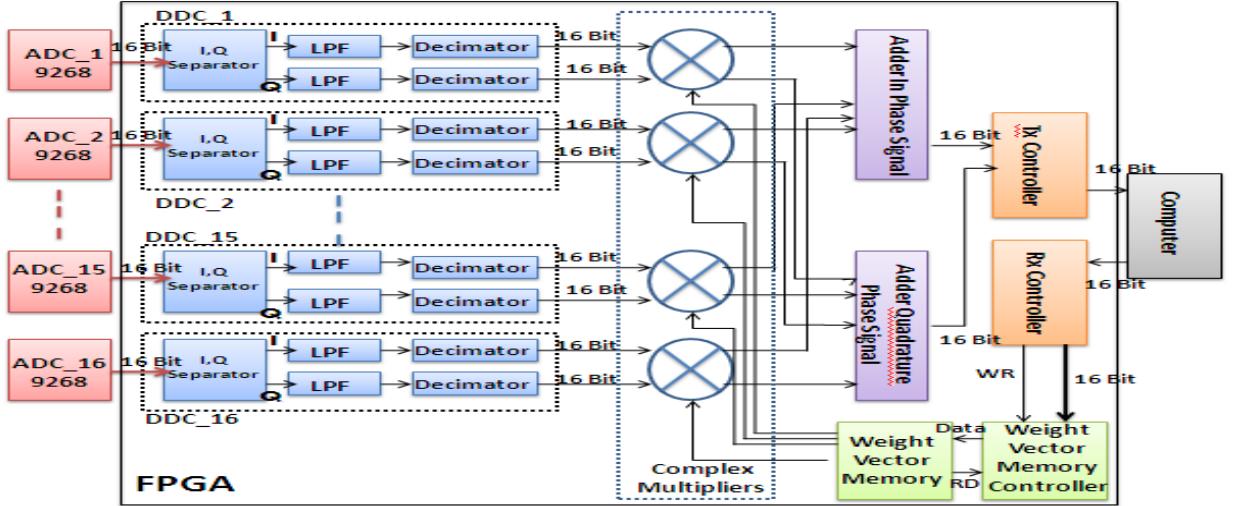

| Figure 5-11: VLSI Architecture of FPGA1 and FPGA2 with ADC and DDC .....                              | 69 |

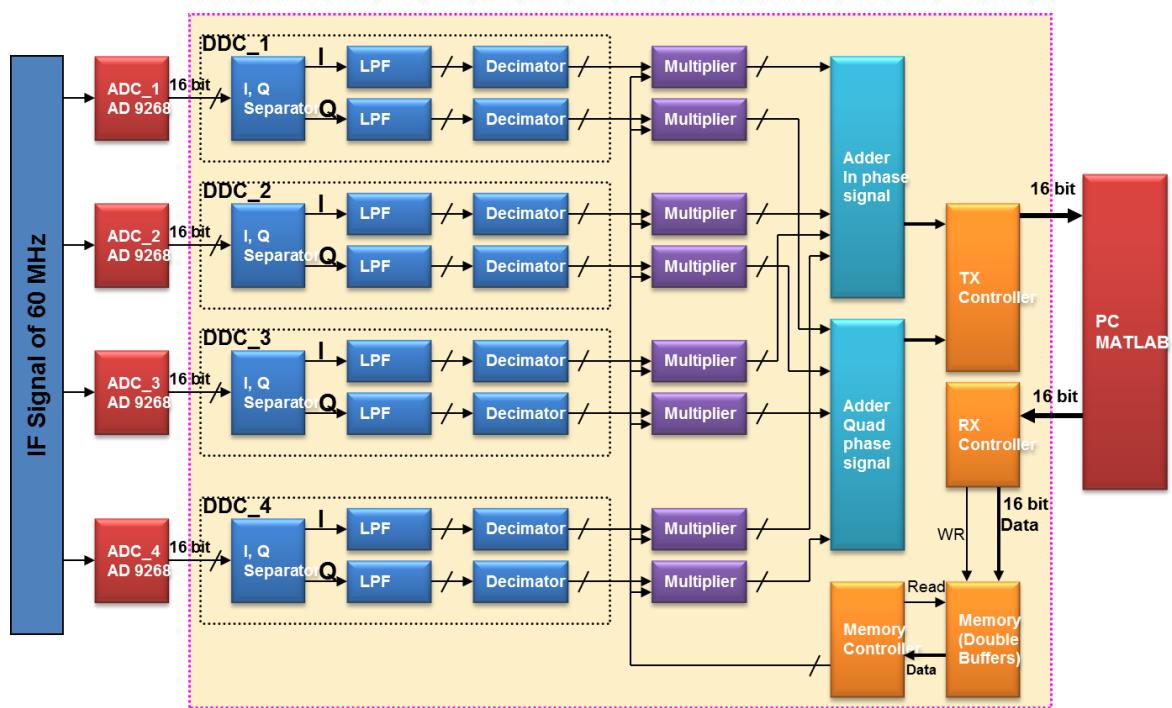

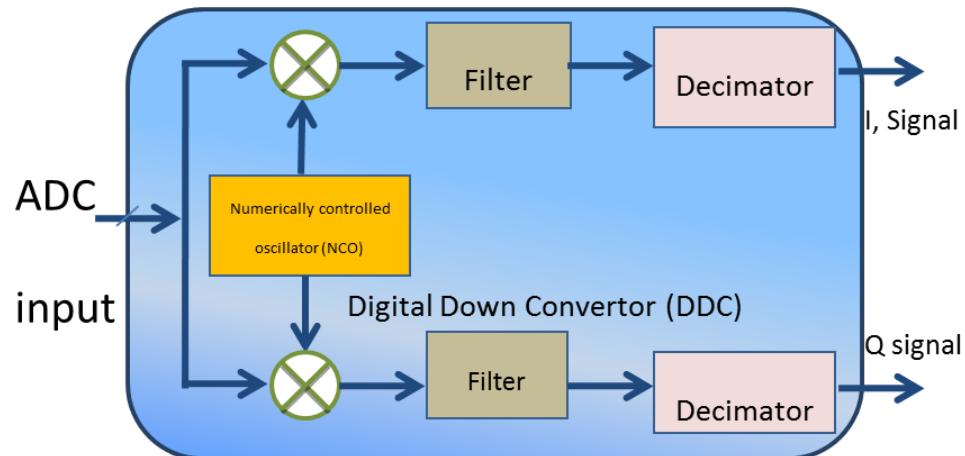

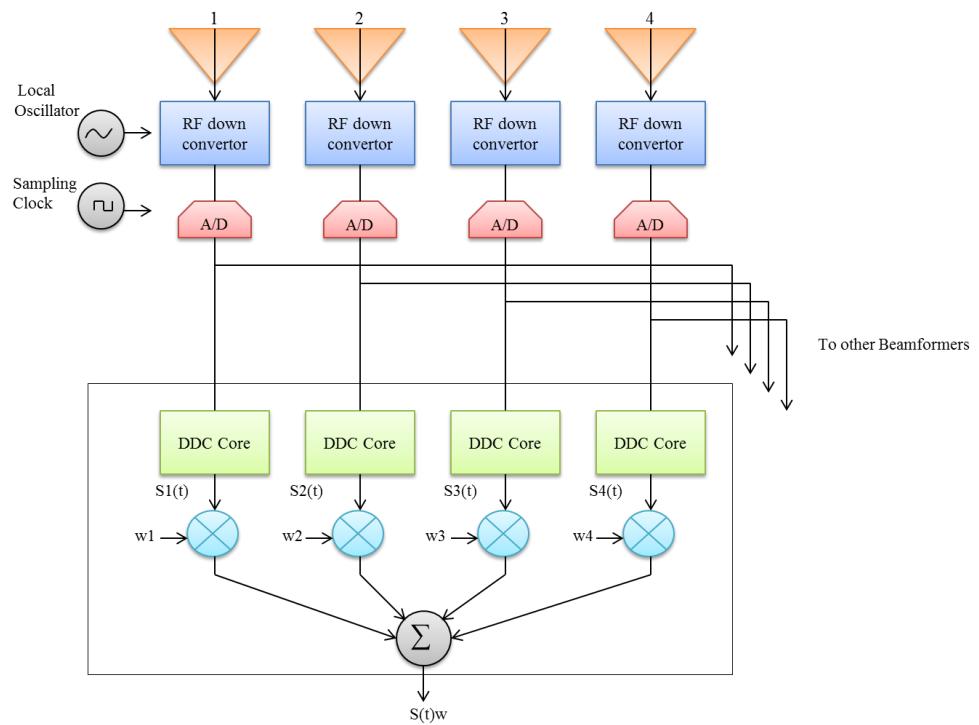

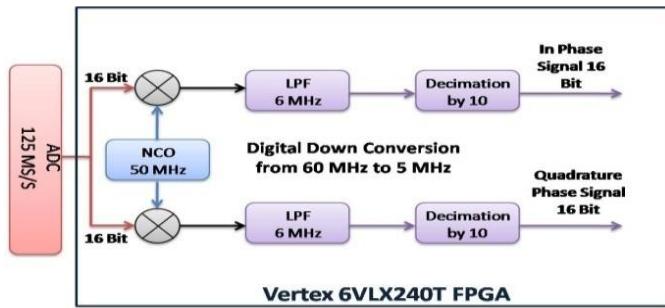

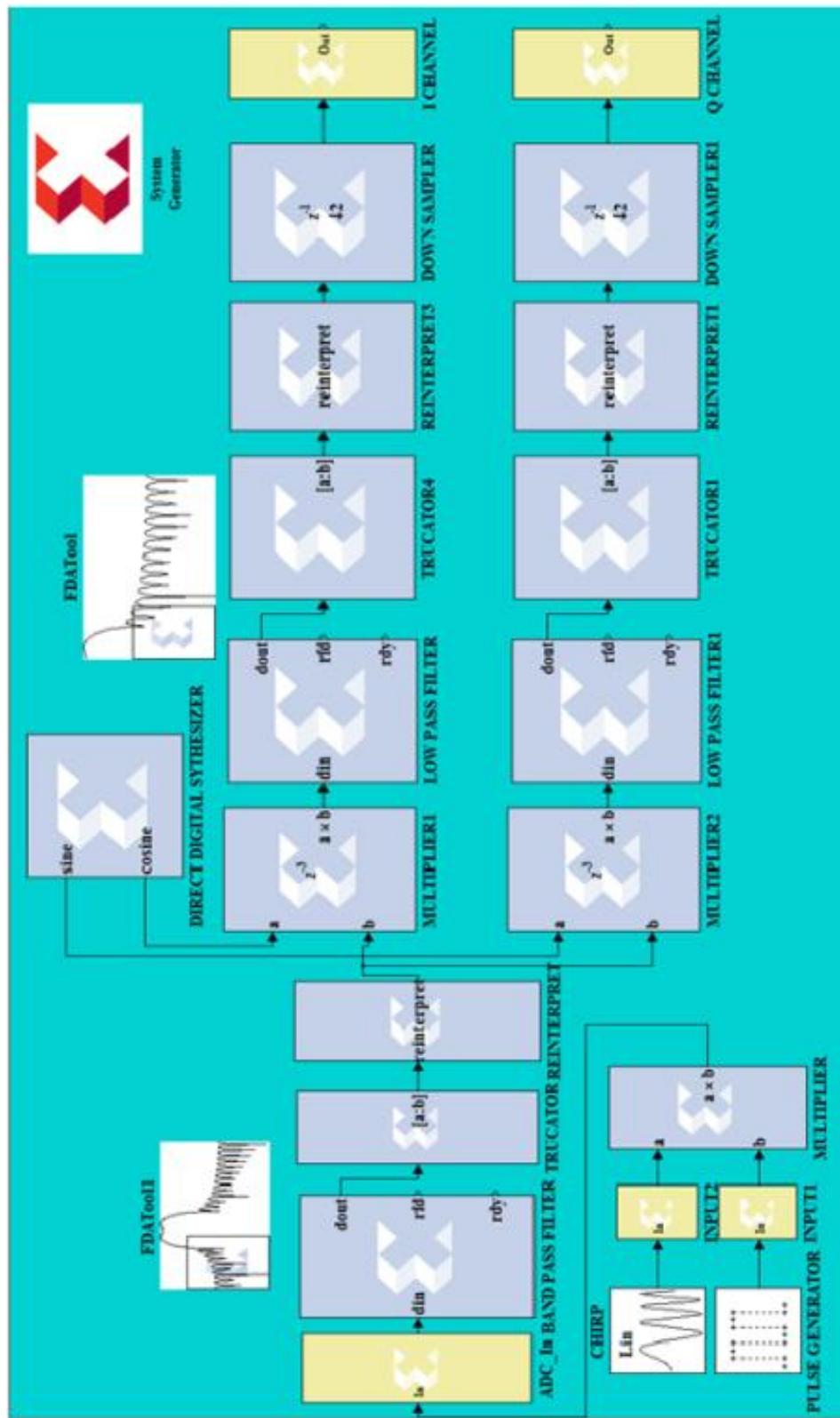

| Figure 5-12: Digital down Convertor (DDC) functional Block Diagram .....                              | 70 |

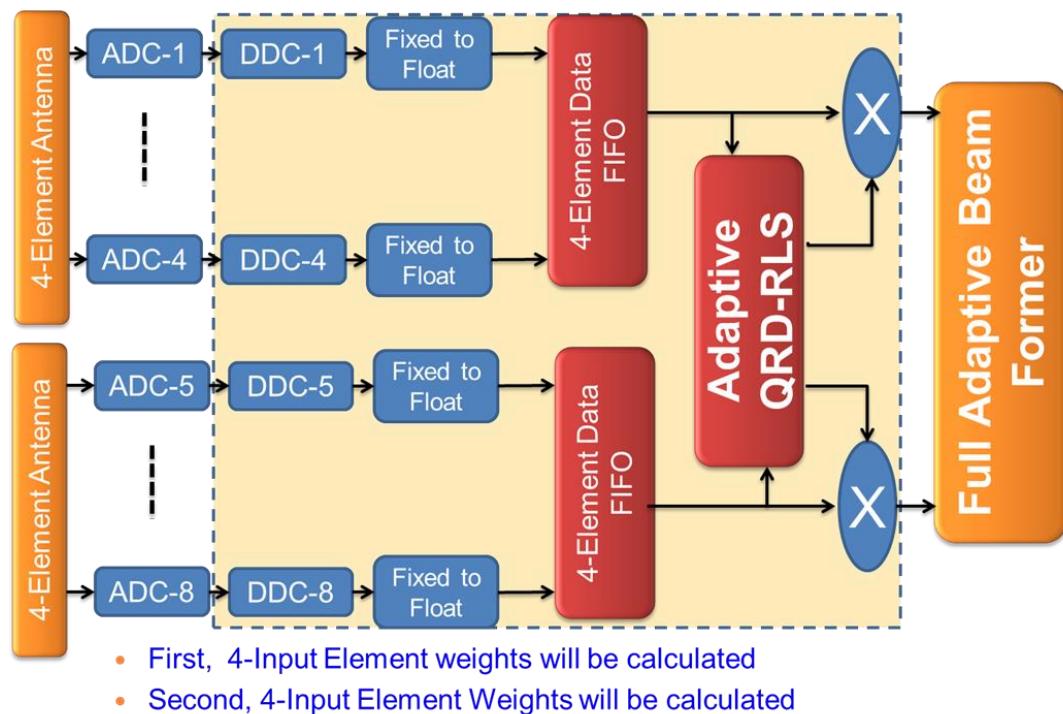

| Figure 5-13: Adaptive Beam former VLSI Architecture with Floating Point Operation .....               | 71 |

| Figure 6-1: Fixed weight DBF architecture for four element array .....                                | 75 |

| Figure 6-2: DBF architecture for four element array. ....                                             | 76 |

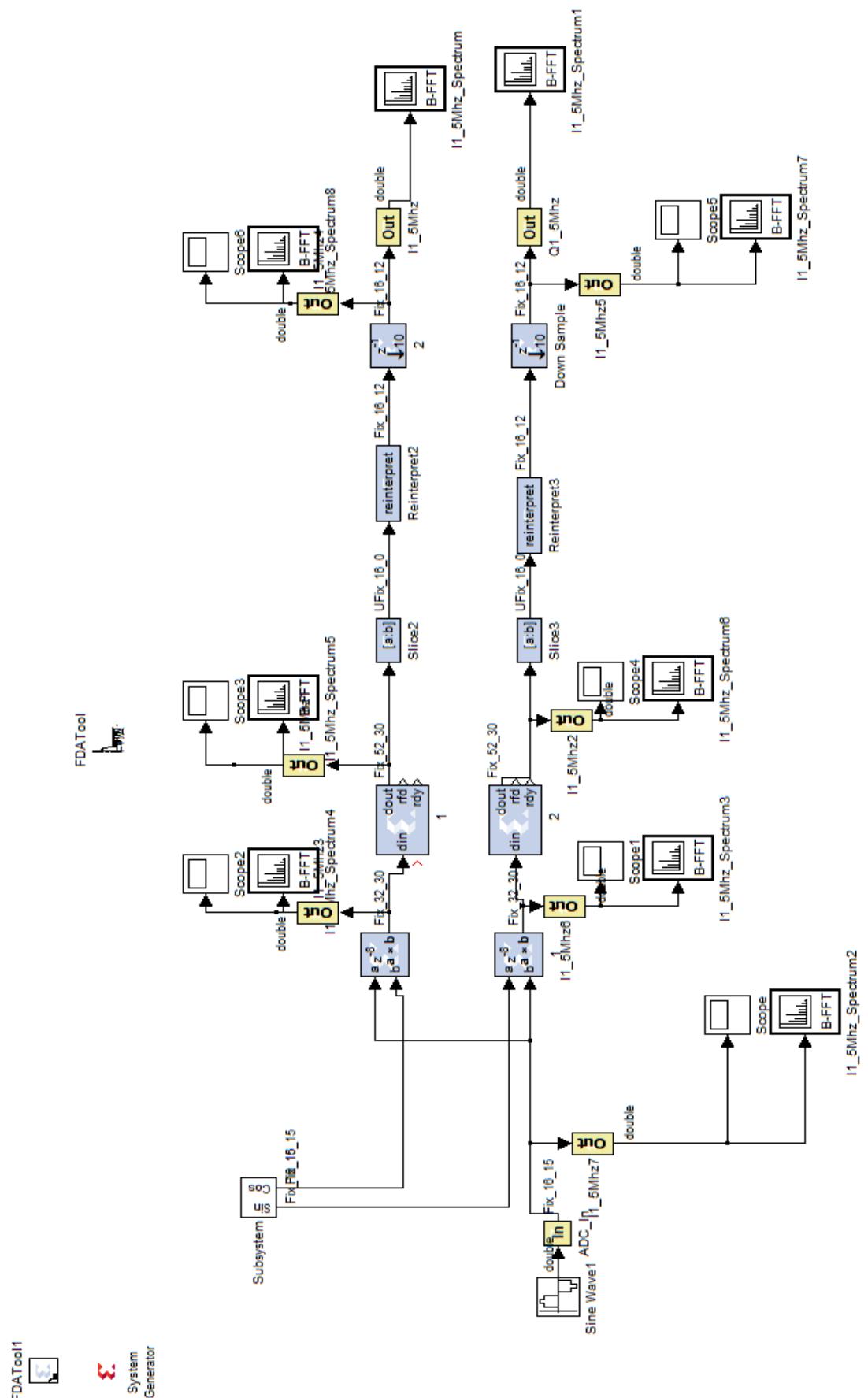

| Figure 6-3: Digital down convertor internal architecture.....                                         | 77 |

| Figure 6-4: Digital down convertor implementation.....                                                | 78 |

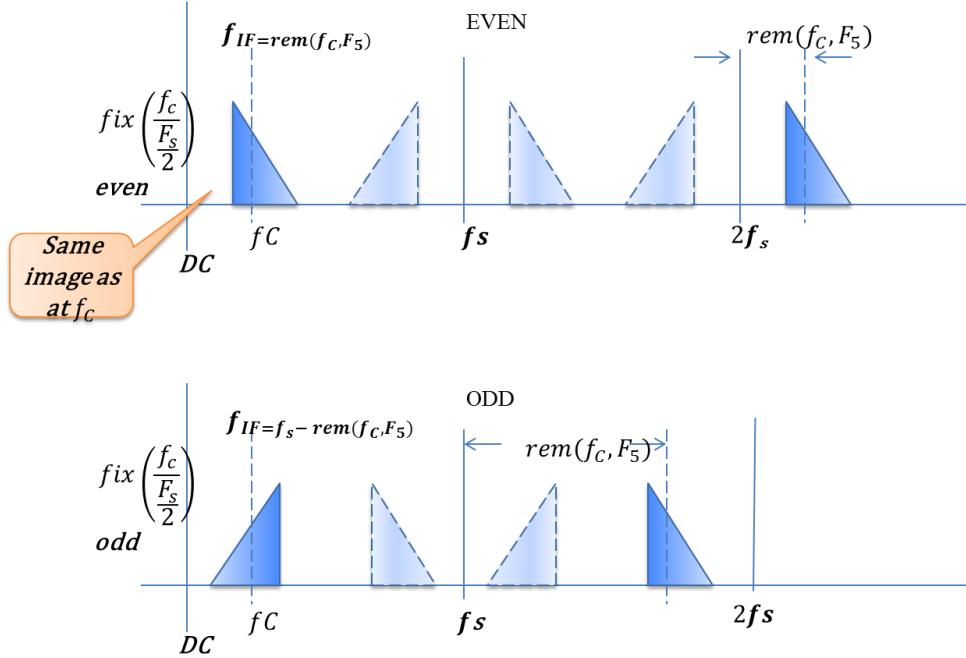

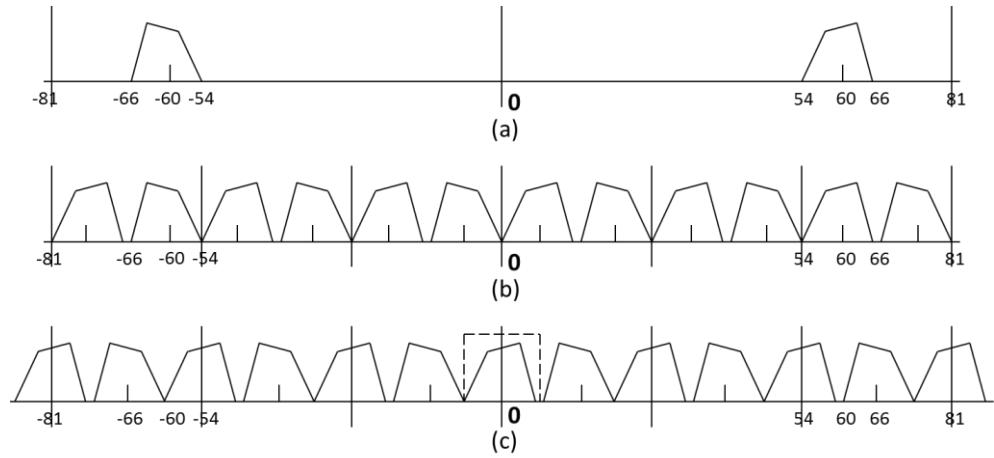

| Figure 6-5: Nyquist zone for $f_c=60$ MHz and $f_s=50$ MHz.....                                       | 79 |

| Figure 6-6: DBF architecture for four element array .....                                             | 79 |

| Figure 6-7: Digital beam former architecture developed using prototype hardware.....                  | 81 |

| Figure 6-8: sixteen element DBF architecture for generation of multiple digital beams. ....           | 83 |

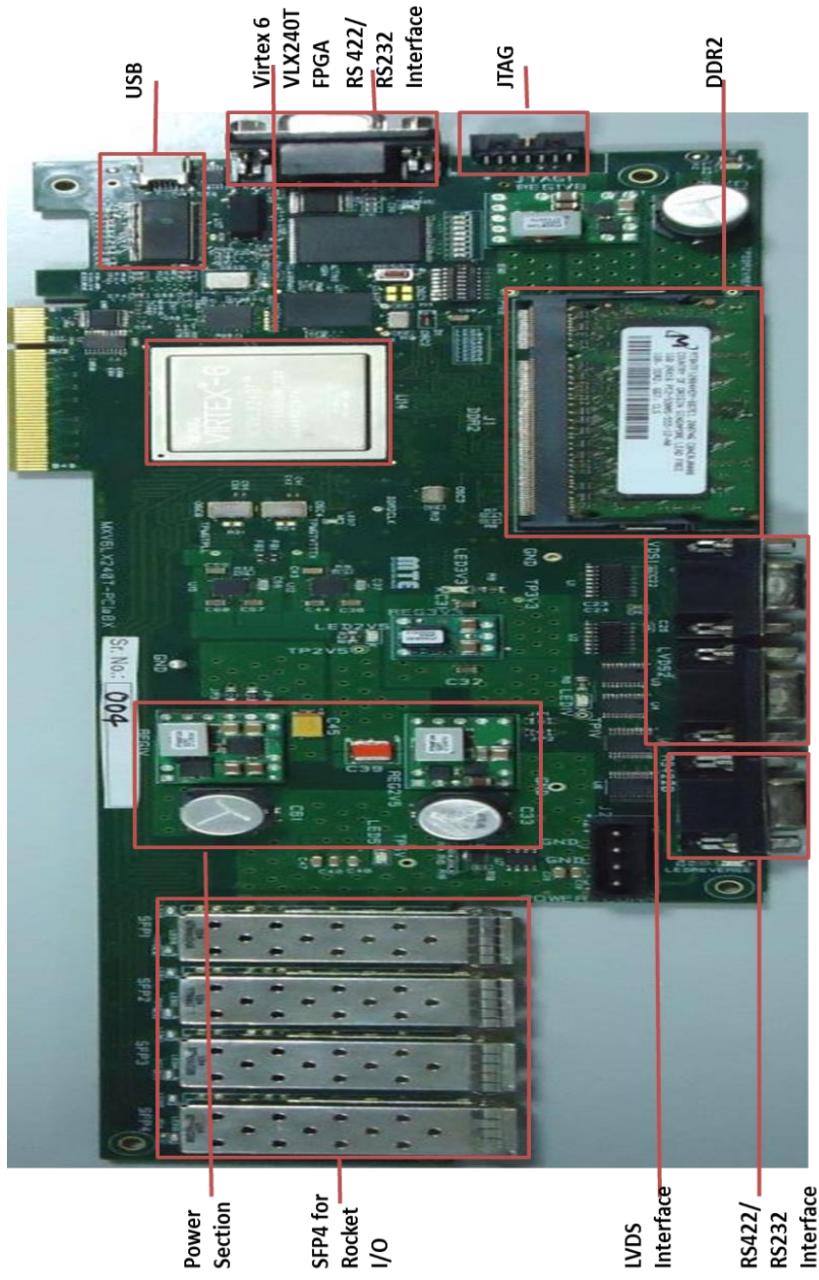

| Figure 6-9: FPGA based digital down convertor .....                                                   | 83 |

| Figure 6-10: Digital down convertor implementation.....                                               | 84 |

| Figure 6-11:Nyquist zones for $f_c=60$ MHz and $f_s=50$ MHz .....                                     | 85 |

|                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6-12: Prototype hardware used to form nine digital beams in the direction of arrival.....                                                                       | 86  |

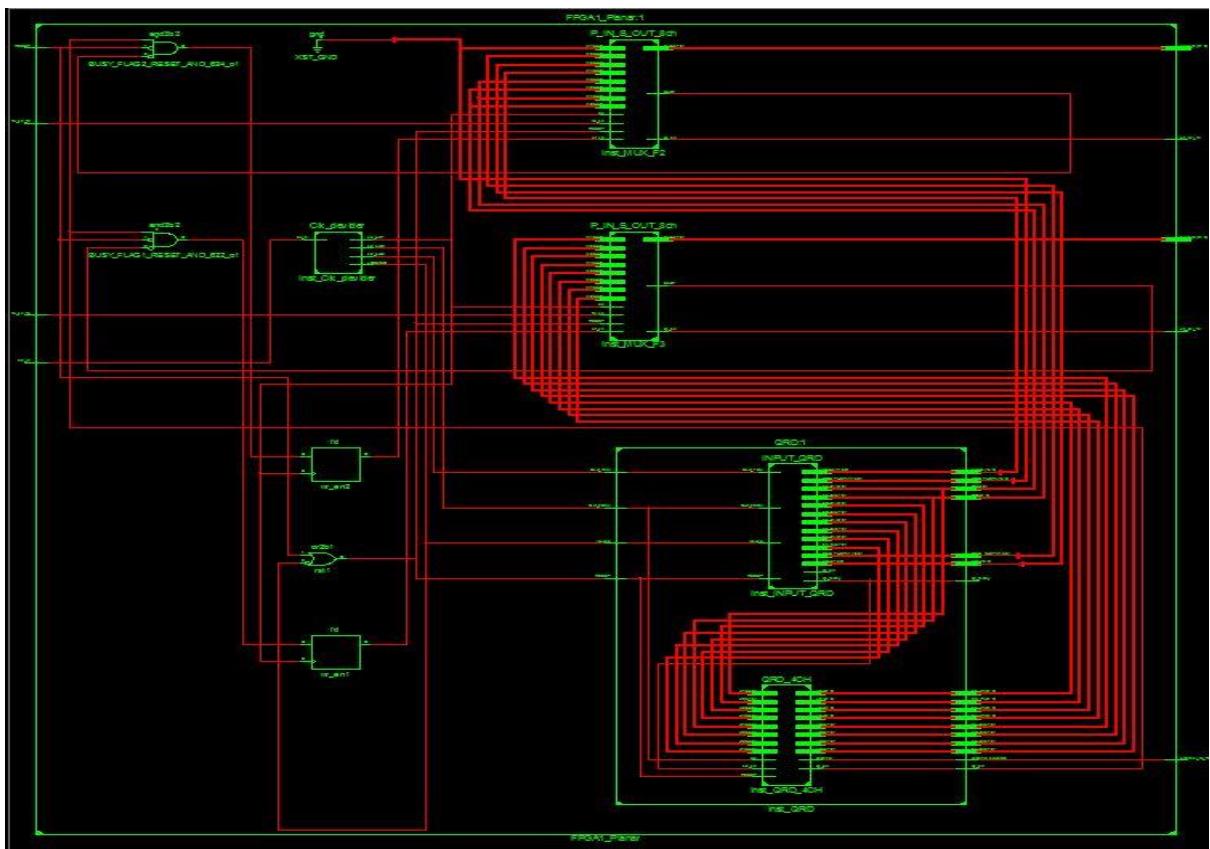

| Figure 6-13: VLSI Architecture of FPGA1 and FPGA2 without ADC and DDC .....                                                                                            | 88  |

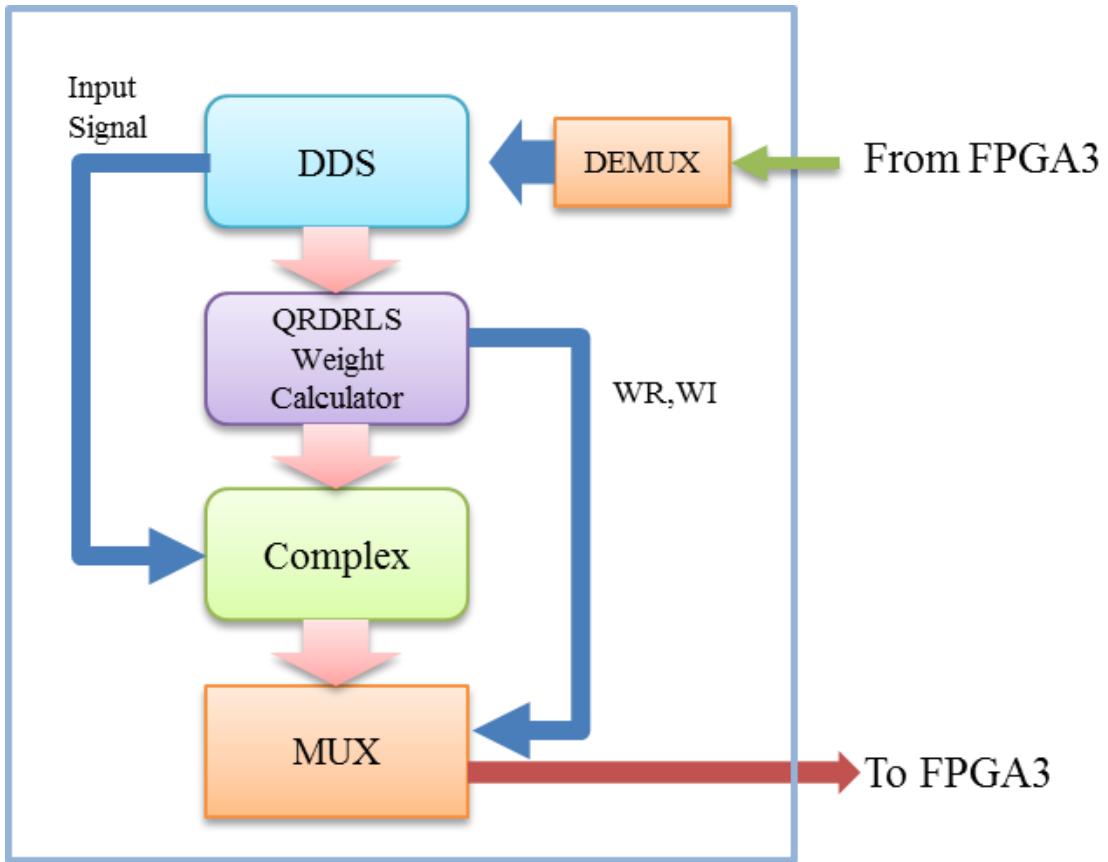

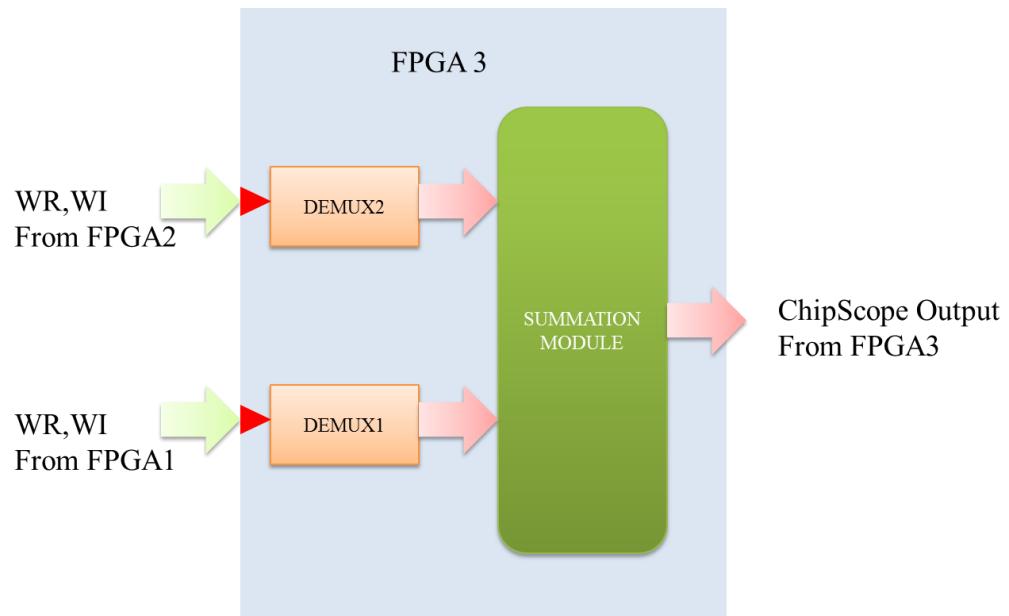

| Figure 6-14: VLSI Architecture of FPGA3.....                                                                                                                           | 88  |

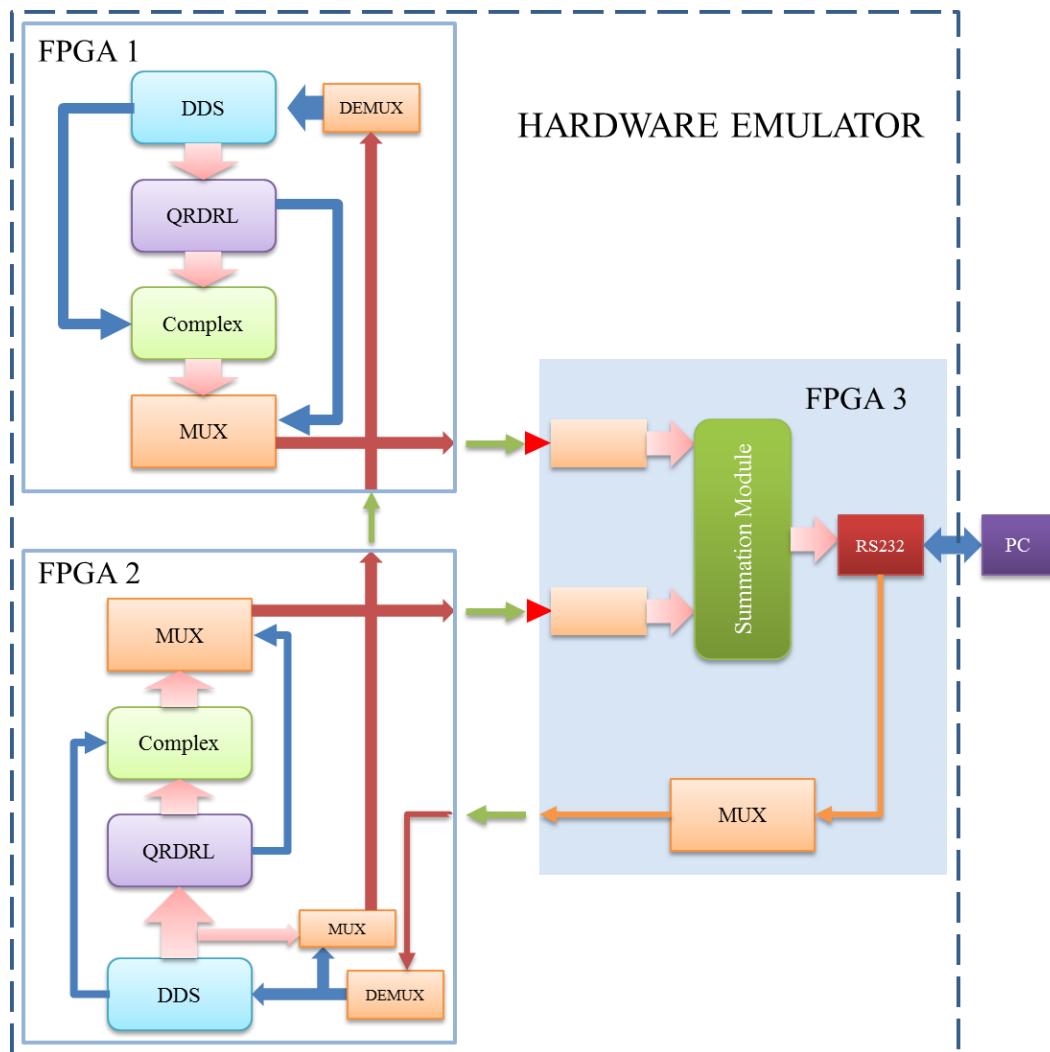

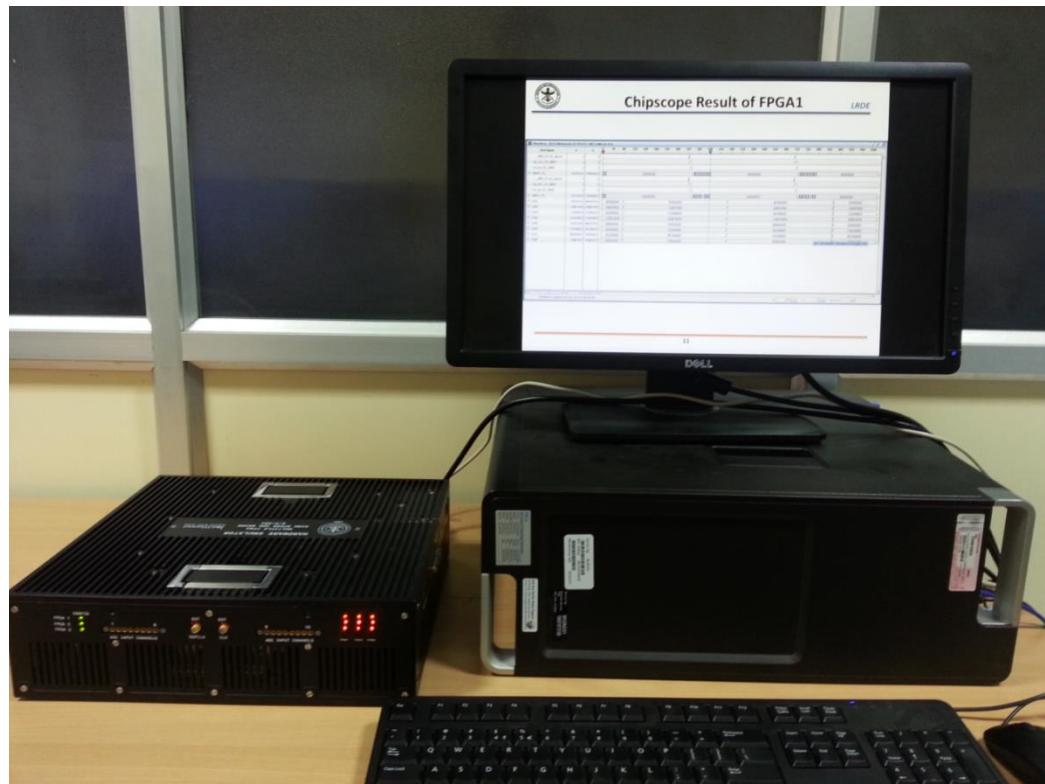

| Figure 6-15: Complete test setup including Hardware Emulator .....                                                                                                     | 89  |

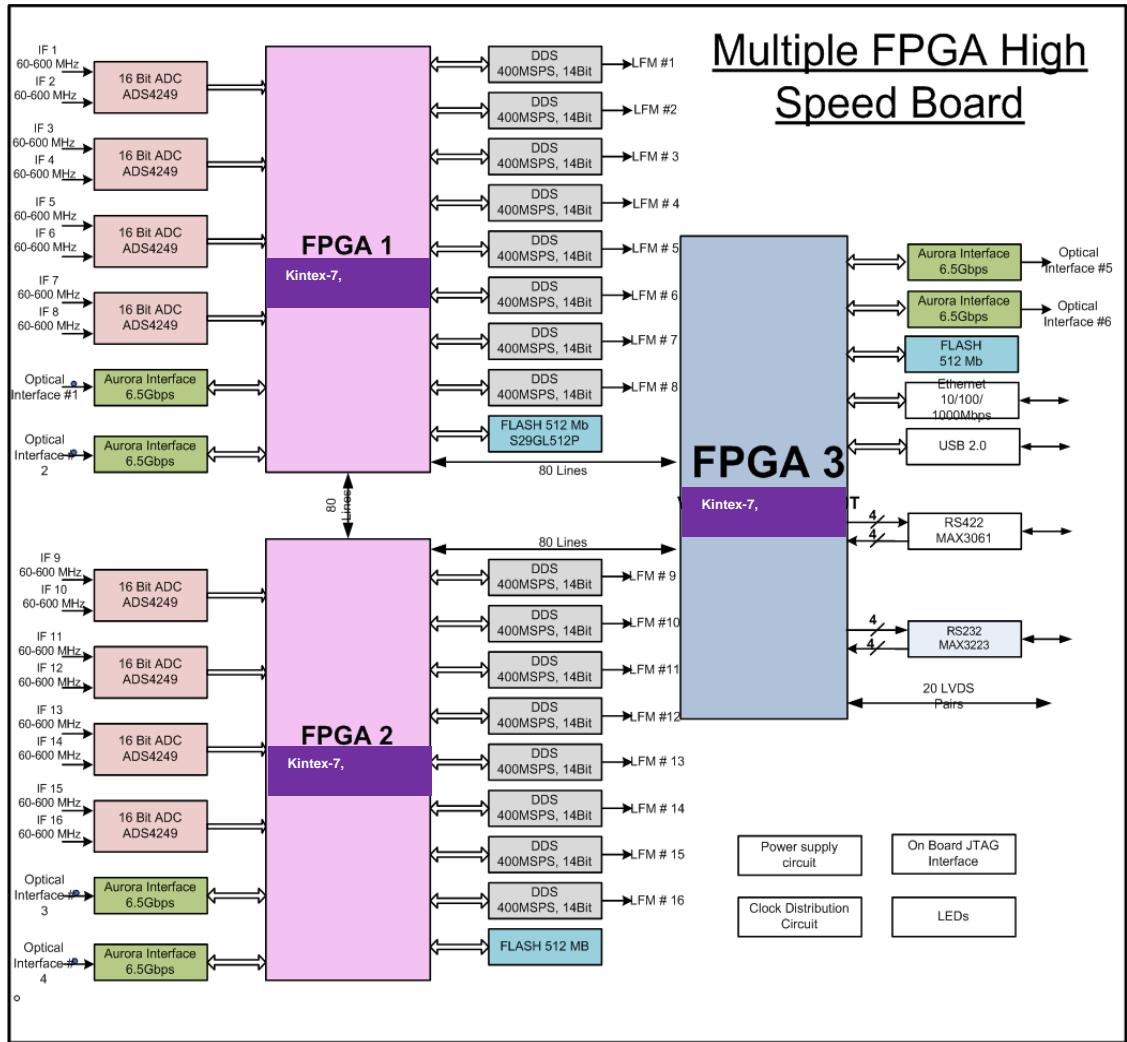

| Figure 6-16: Block diagram of Hardware for Adaptive Beam Former VLSI Architecture.....                                                                                 | 90  |

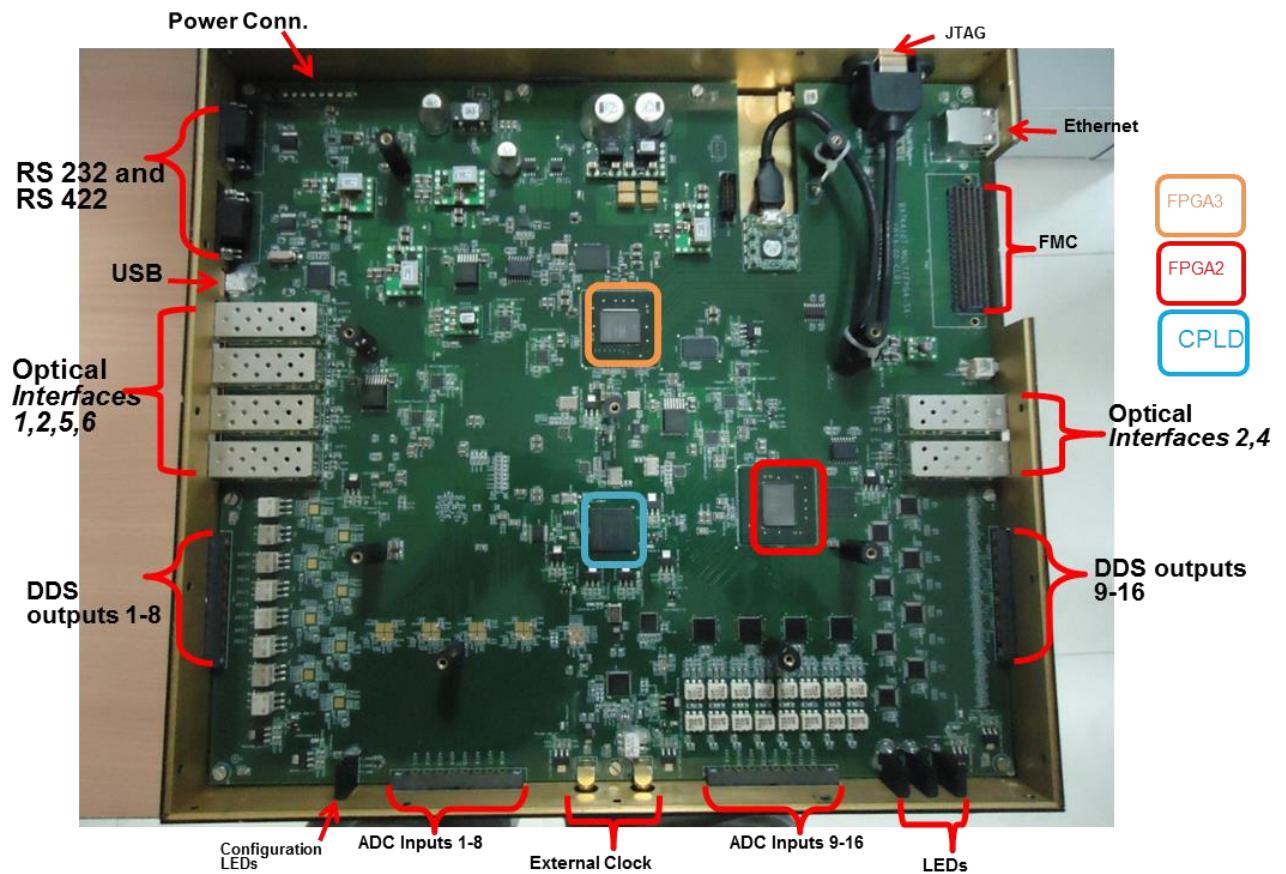

| Figure 6-17: Hardware for Adaptive Beam Former VLSI Architecture .....                                                                                                 | 91  |

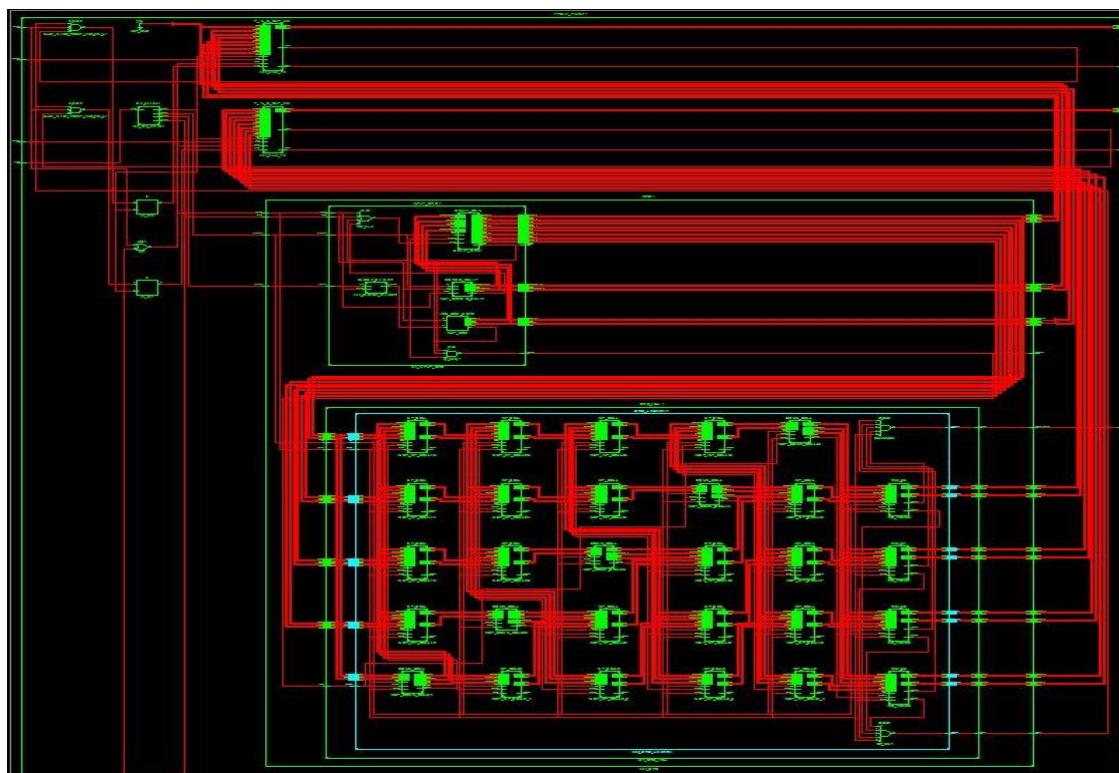

| Figure 6-18: RTL view of four element IQRD RLS weight computation. ....                                                                                                | 91  |

| Figure 6-19: RTL view of eight element partial beam formation. ....                                                                                                    | 92  |

| Figure 6-20: Hardware test set up for Adaptive Beam Formation. ....                                                                                                    | 92  |

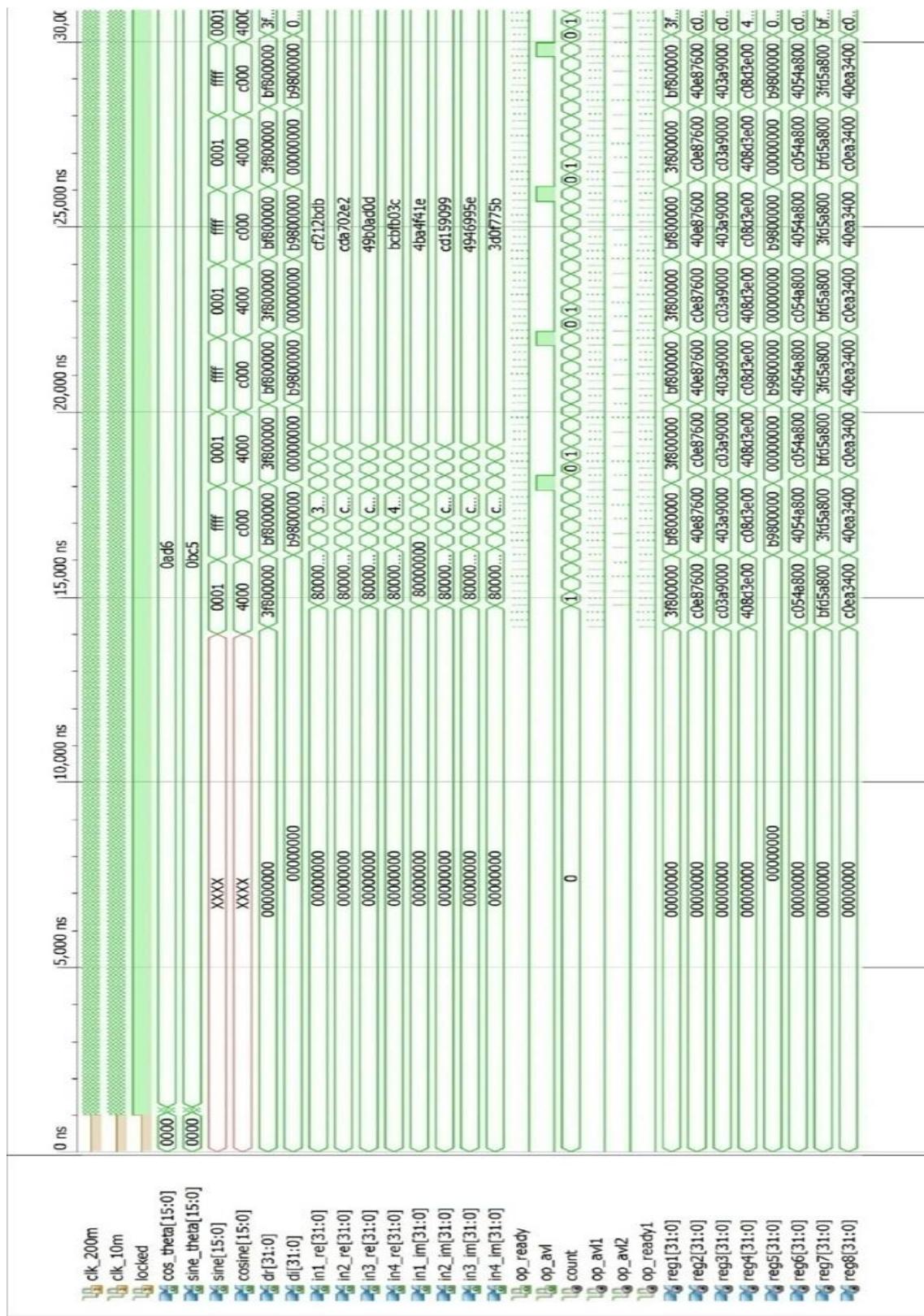

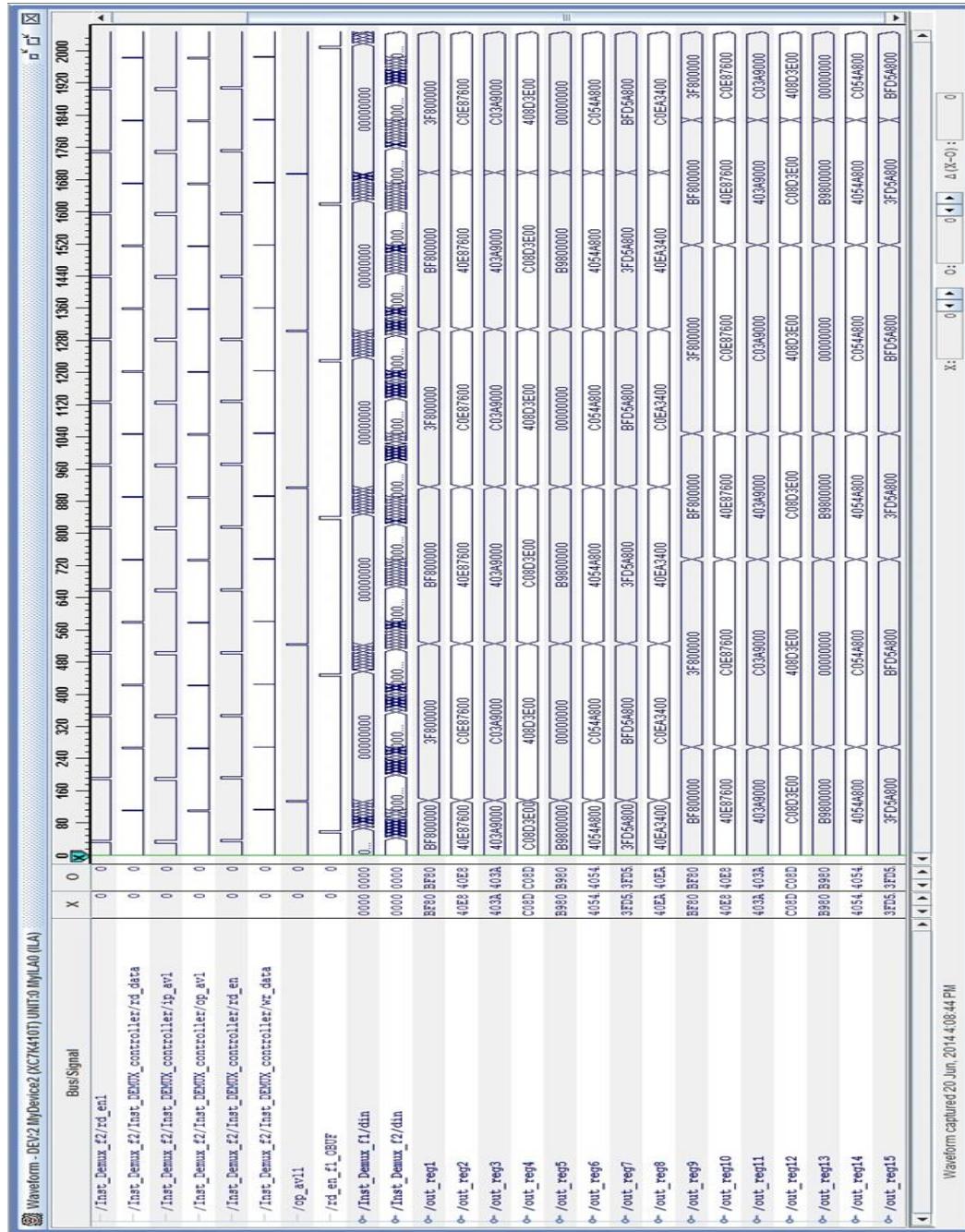

| Figure 7-1: Calculation of Adaptive Weights for 16 Element Array at timing simulation. ....                                                                            | 99  |

| Figure 7-2: Adaptive Weight calculation for 16 Element Array at Chip level.....                                                                                        | 100 |

| Figure 7-3: Computation of Adaptive Weights for 16 Element Array functional simulations. ....                                                                          | 101 |

| Figure 7-4: Simulation of digital down converter and multiple beams .....                                                                                              | 102 |

| Figure 7-5: Real time data captured from the FPGA and plotted in chipscope tool.....                                                                                   | 103 |

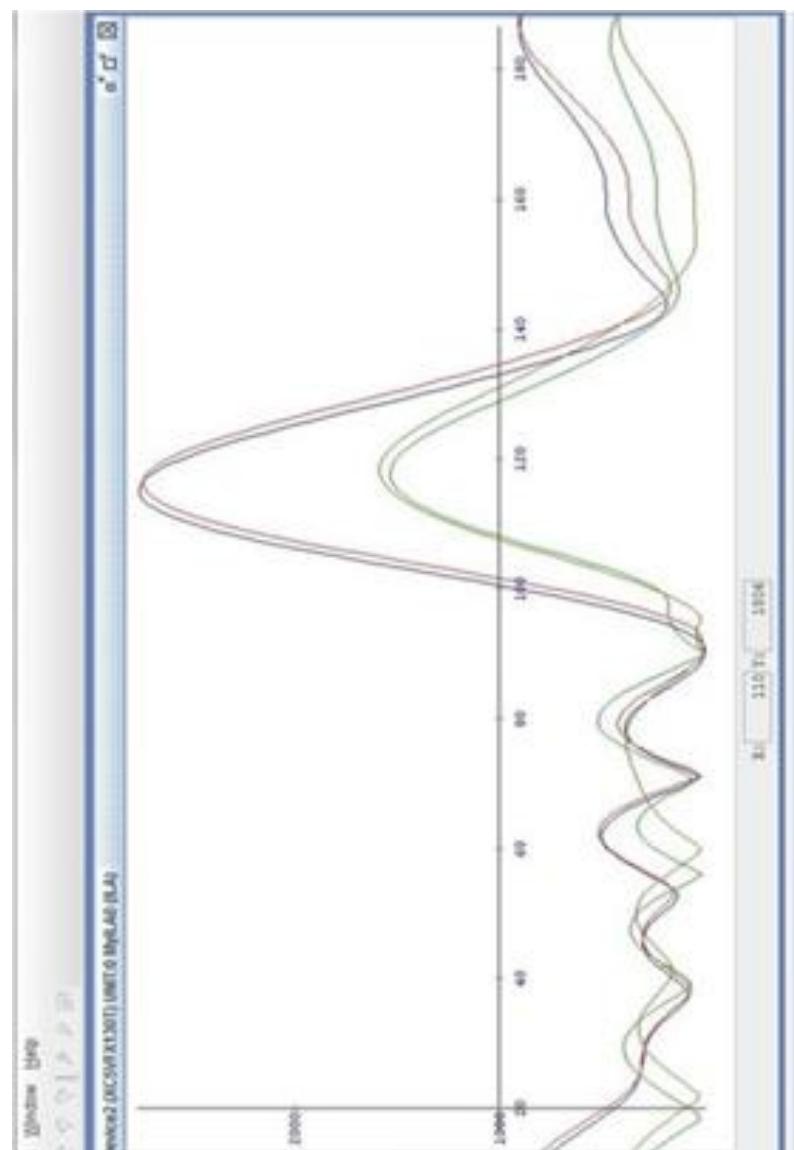

| Figure 7-6: The real time data is received from the prototype board and MATLAB is used to plot the multiple beams. ....                                                | 104 |

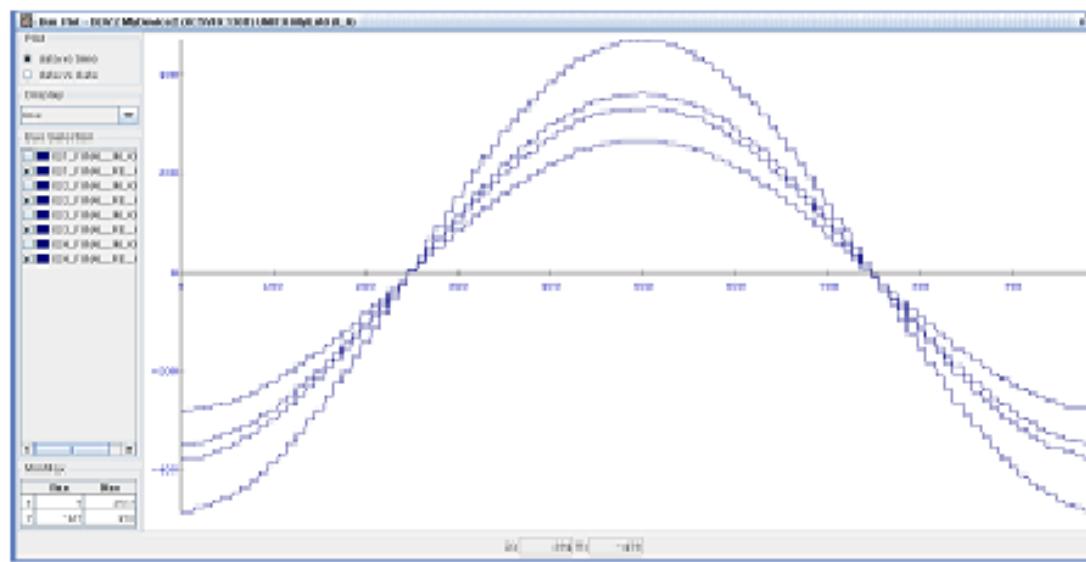

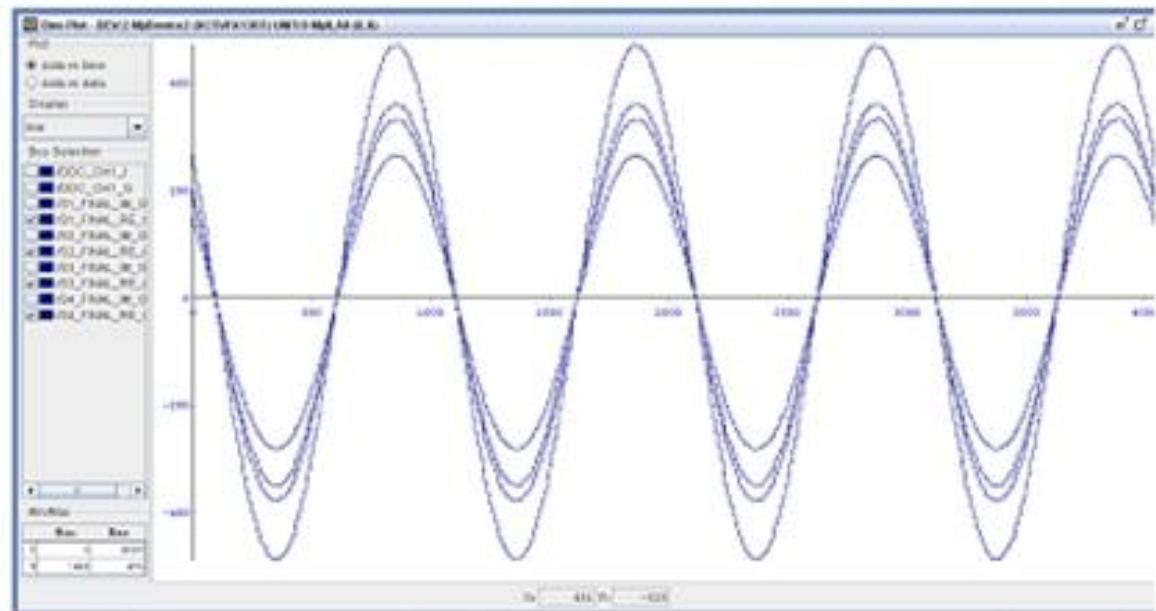

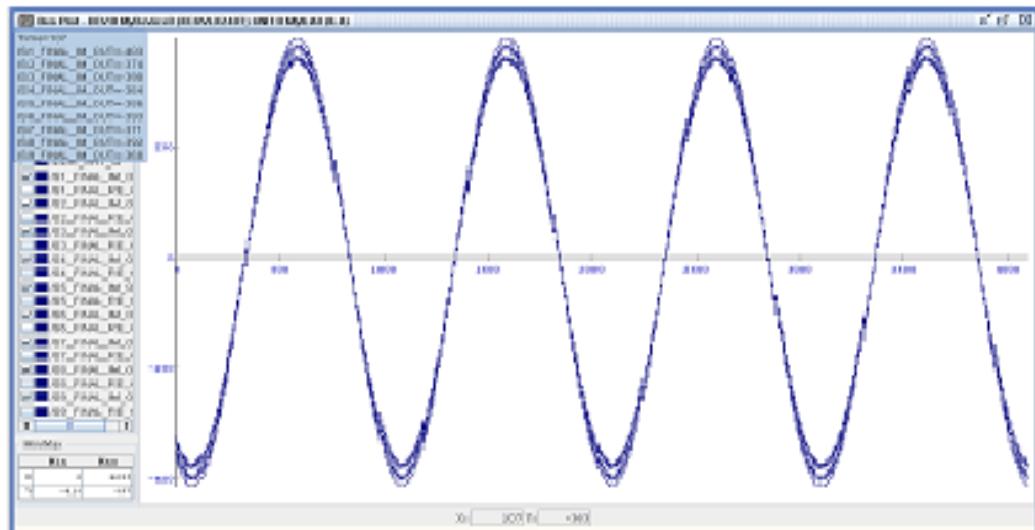

| Figure 7-7: The planar antenna array Inphase signal output indicating four digital beams in the chipscope...105                                                        | 105 |

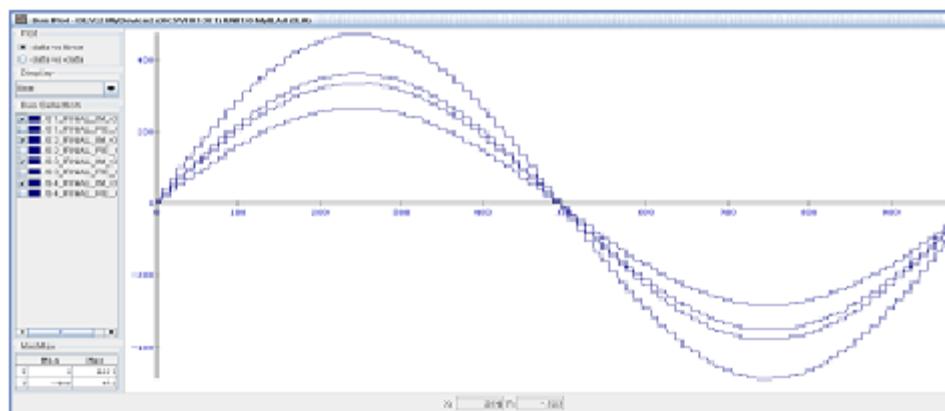

| Figure 7-8: The planar antenna array quadrature phase signal output indicating four digital beams in the chipscope.....105                                             | 105 |

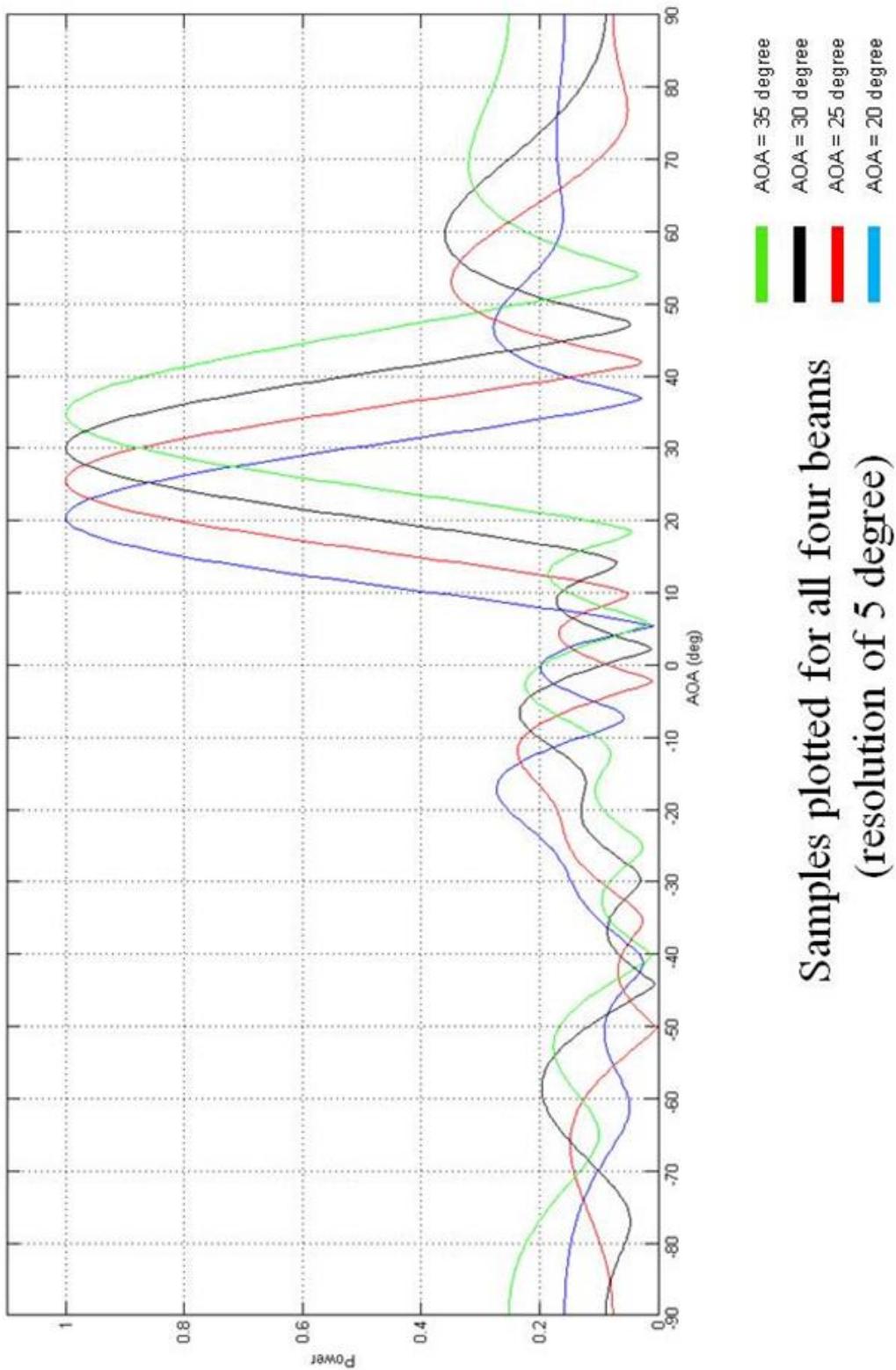

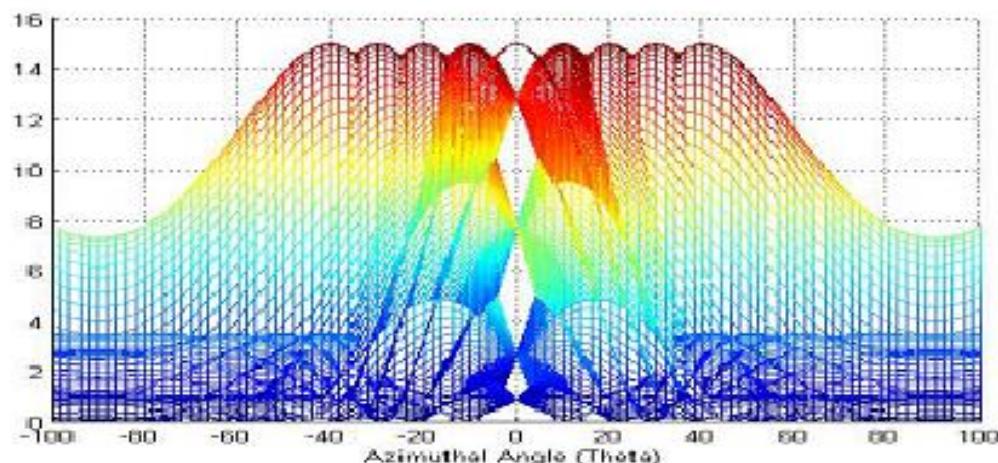

| Figure 7-9: Four digital beams plotted in MATLAB using the weight vectors stored inside FPGA in the desired direction at Azimuth zero deg and Elevation 20 deg.....106 | 106 |

| Figure 7-10: Planar Antenna array output in the receive mode showing four in phase signals corresponding to four beams.....107                                         | 107 |

| Figure 7-11: Planar Antenna array output in the receive mode showing four quadrature phase signals corresponding to four beams.....107                                 | 107 |

| Figure 7-12: Four beams plotted in MATLAB using the weight vectors stored inside FPGA in the direction of arrival at Azimuth 0 deg and Elevation 20 deg. ....108       | 108 |

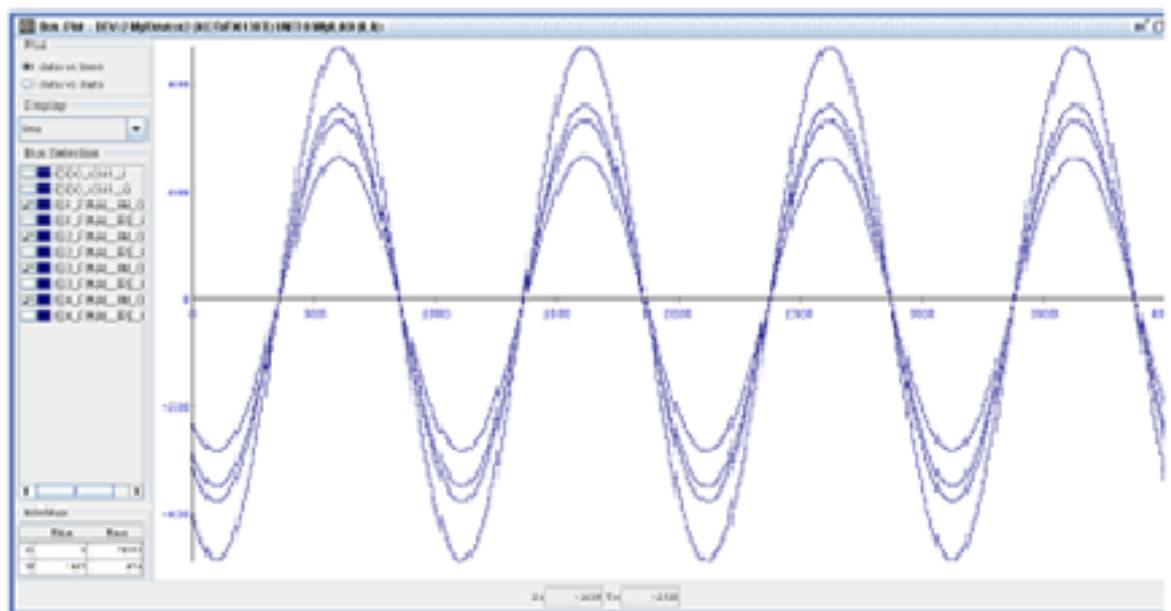

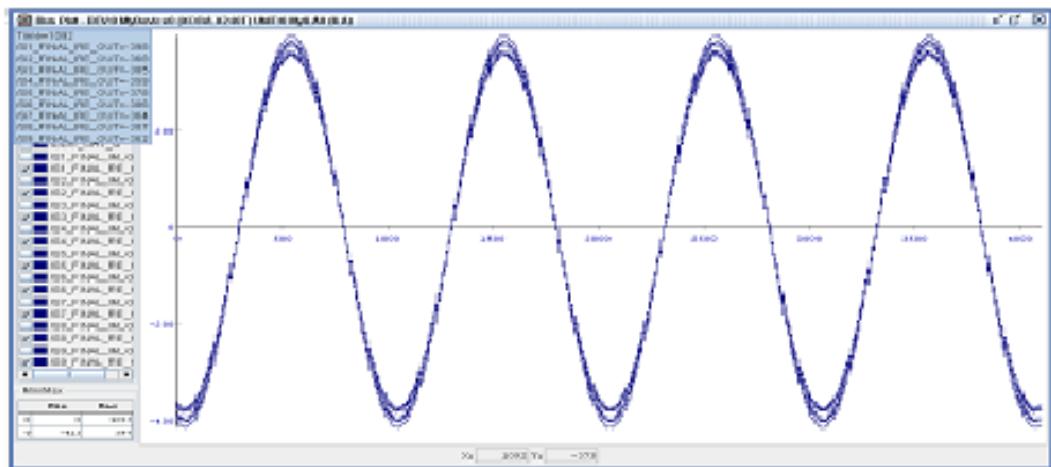

| Figure 7-13: Chipscope output showing nine in phase outputs corresponding to nine beams for 16 elements planar antenna array.....108                                   | 108 |

| Figure 7-14: Chipscope output showing nine quadrature phase outputs corresponding to nine beams for 16 element planar antenna array .....                              | 109 |

|                                                                                                                                                |     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7-15: Nine beams plotted in MATLAB using the weight vectors stored inside FPGA.....                                                     | 109 |

| Figure 7-16: Chipscope output showing nine in phase output corresponding to nine beams for 16 element planar antenna array.....                | 110 |

| Figure 7-17: Chipscope output showing nine quadrature phase outputs corresponding to nine beams for 16 element planar antenna array .....      | 110 |

| Figure 7-18: Nine beams plotted in MATLAB using the weight vectors stored inside FPGA.....                                                     | 111 |

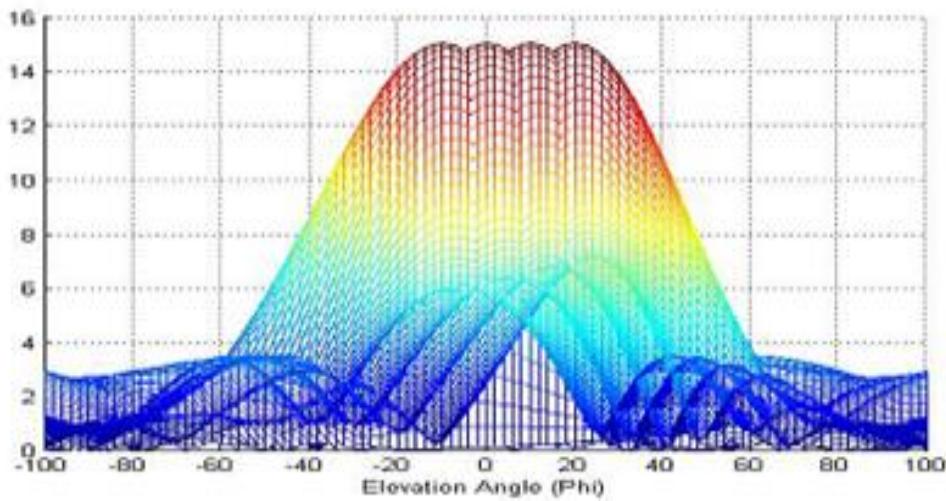

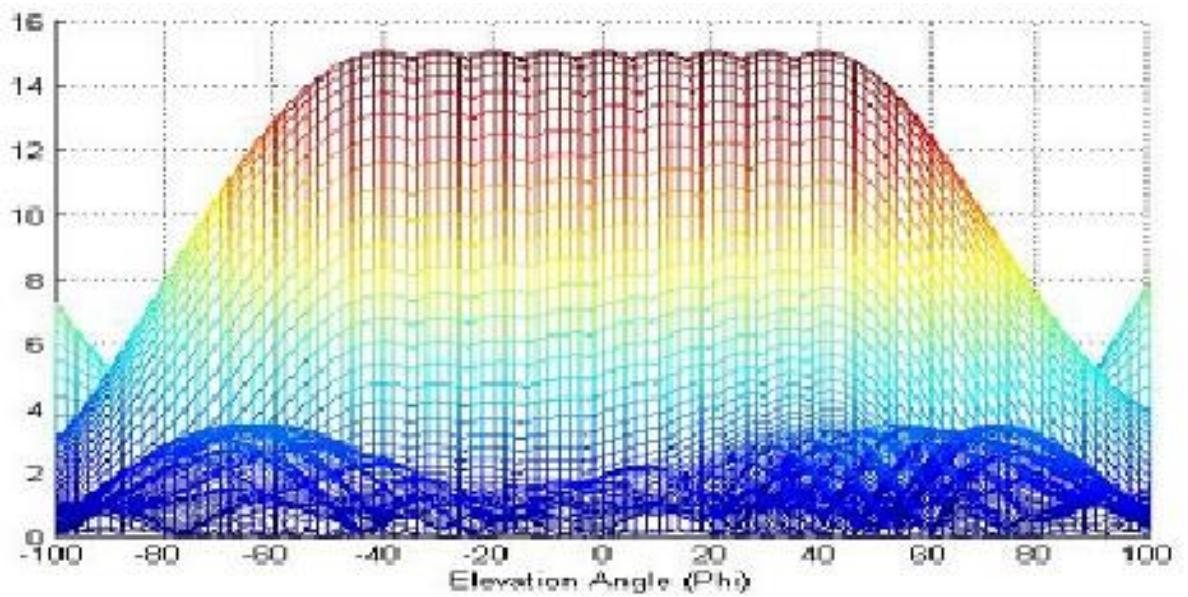

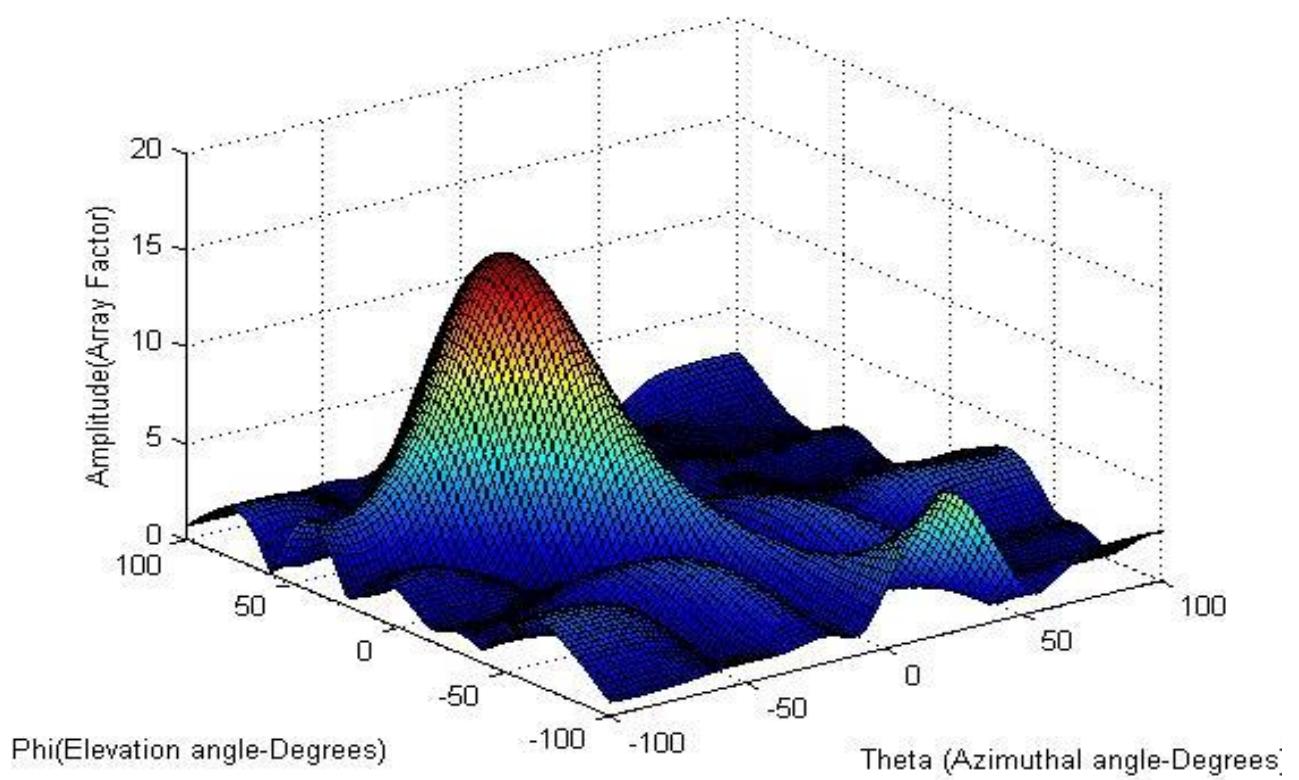

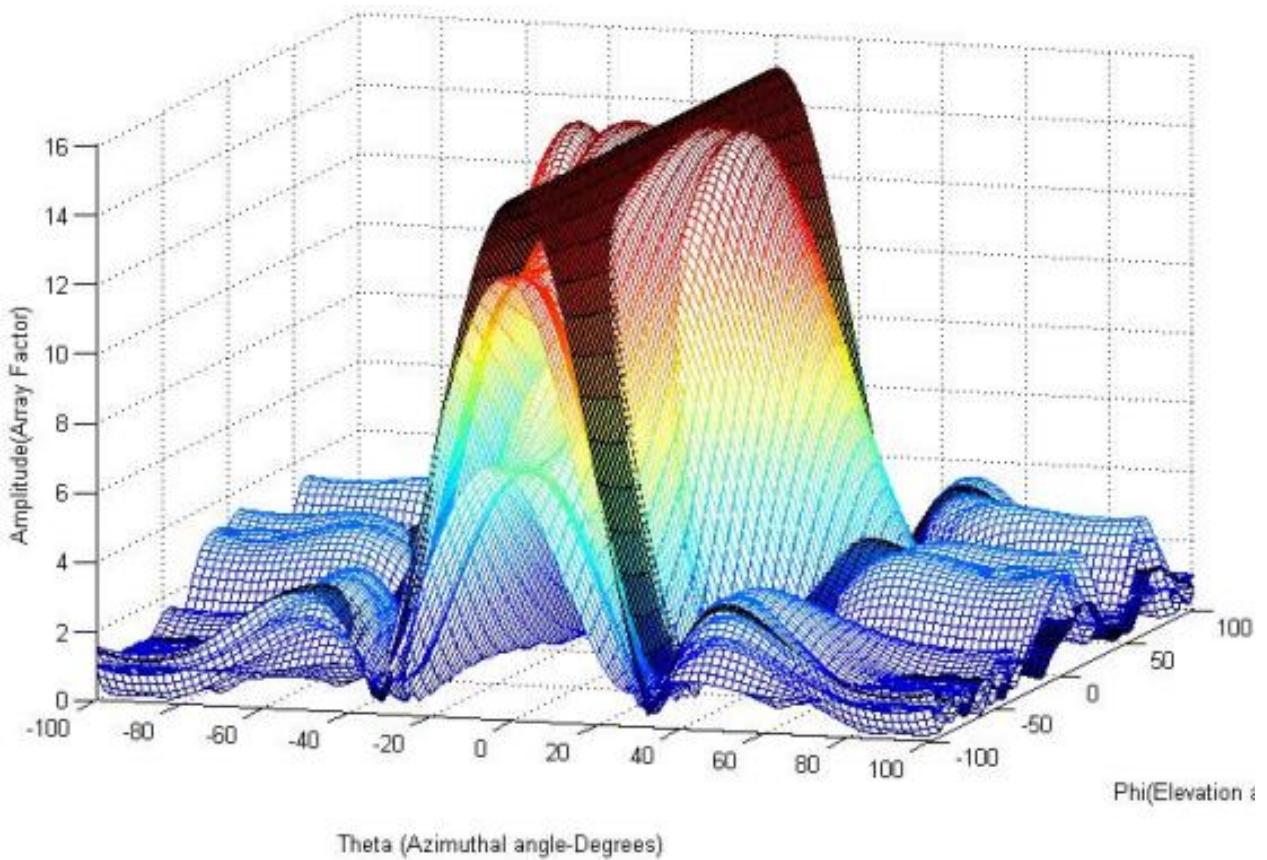

| Figure 7-19: One Adaptive digital Beam plot for sixteen element planar antenna array using weights generated by inverse QRD-RLS in MATLAB..... | 112 |

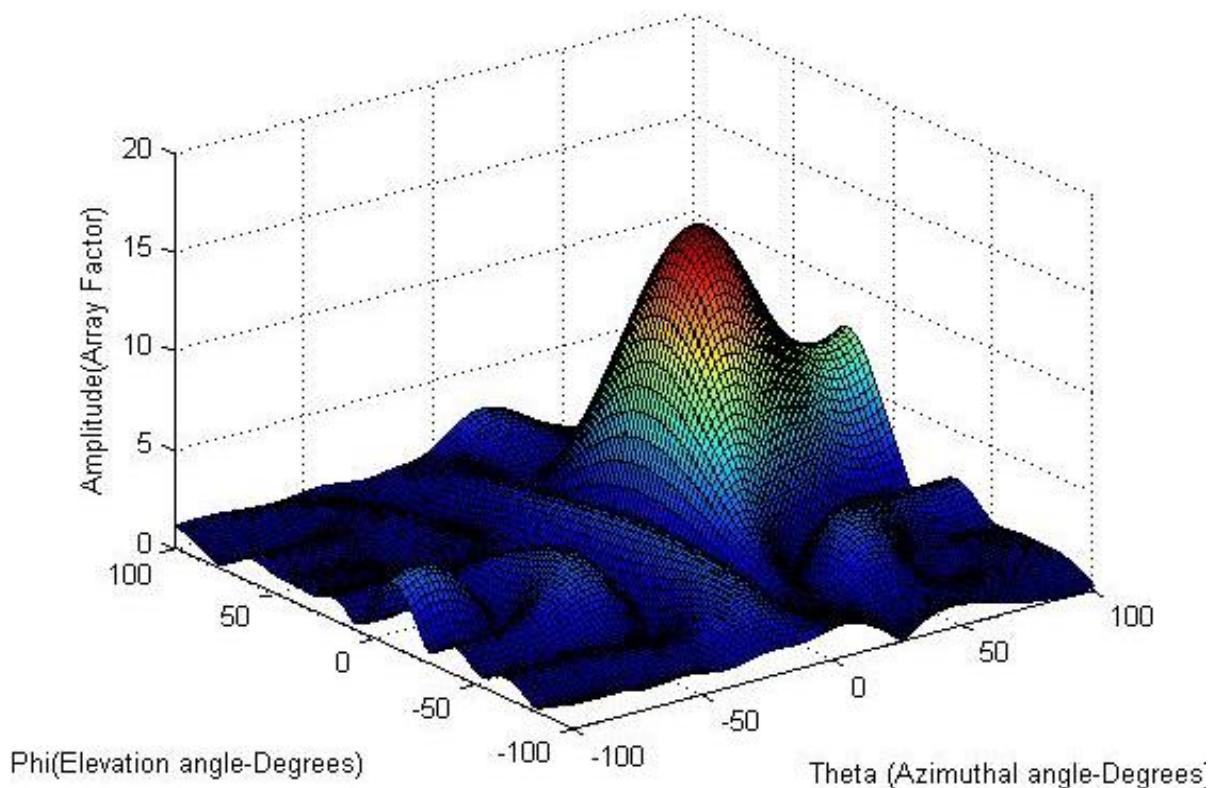

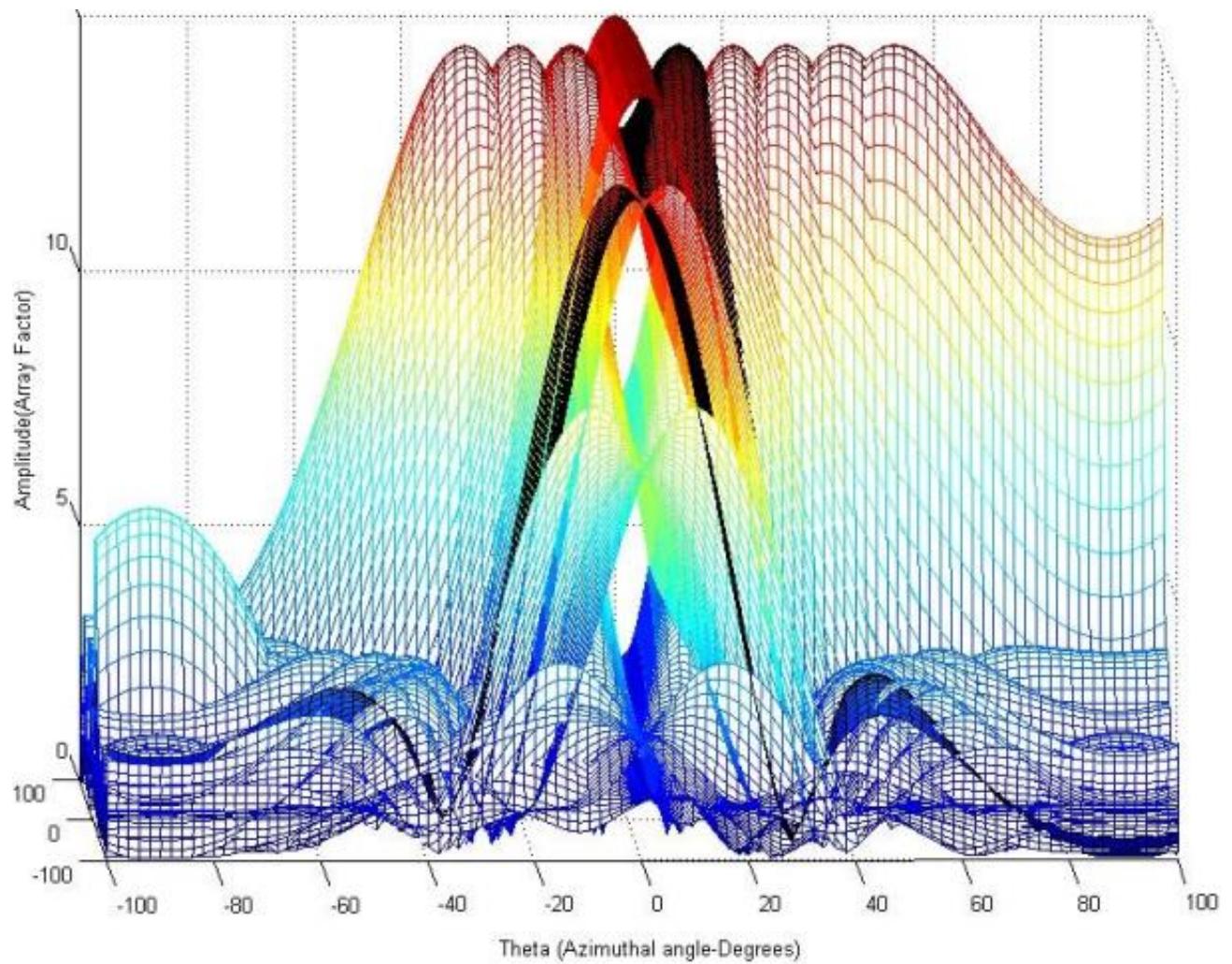

| Figure 7-20: Beam plot for the 16 element planar antenna array using weights generated by conventional QRD-RLS in MATLAB.....                  | 113 |

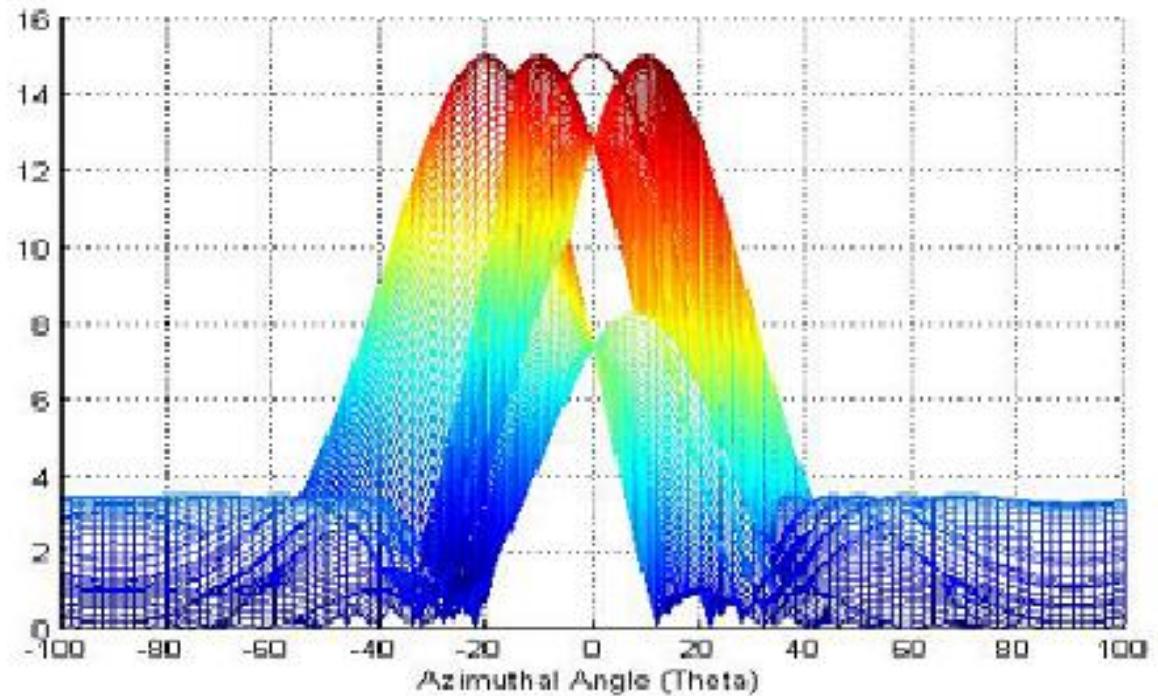

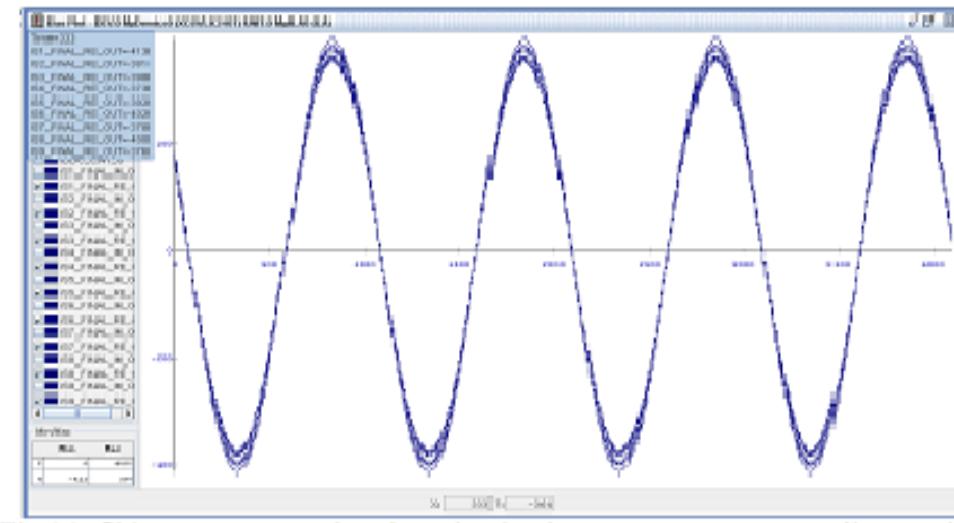

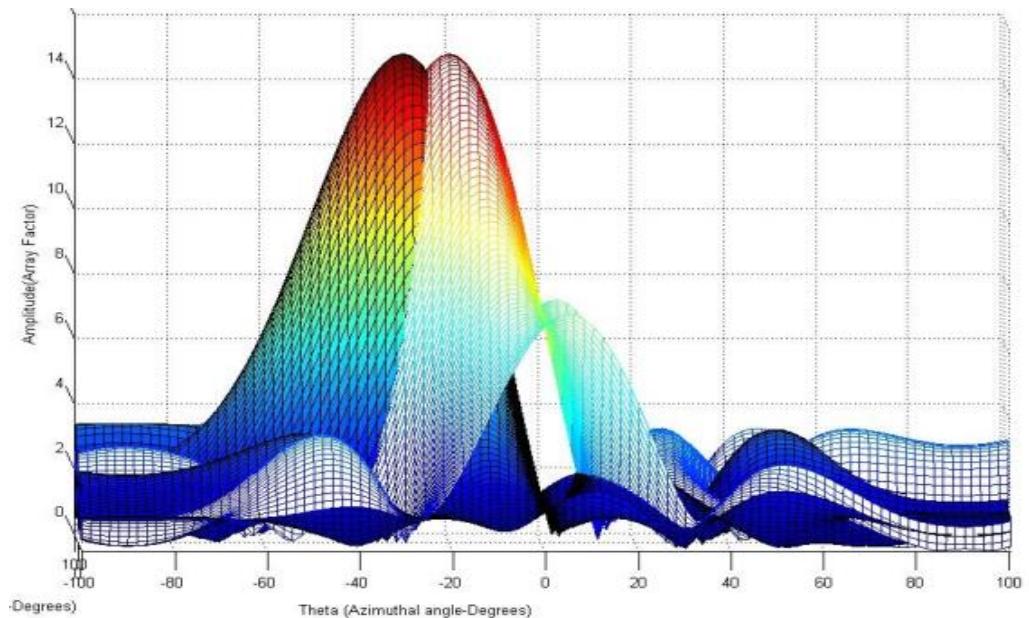

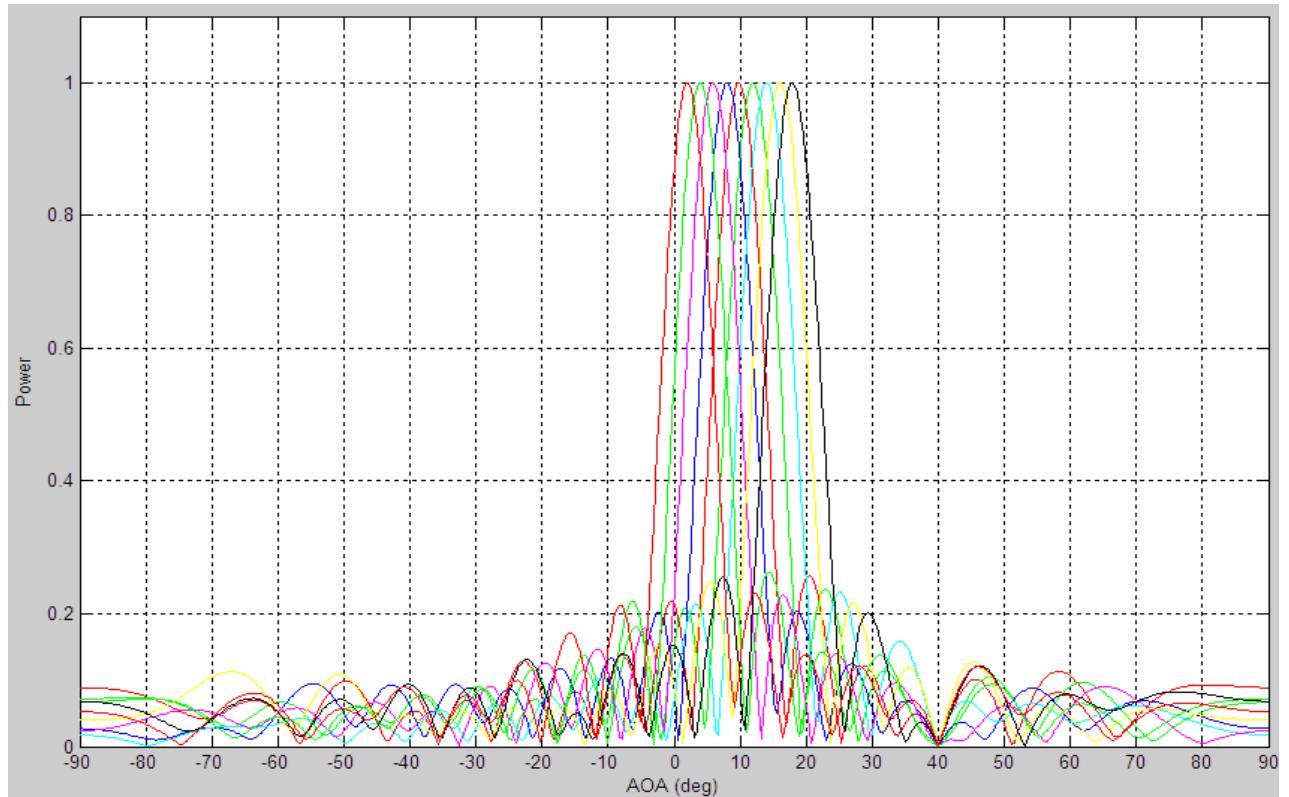

| Figure 7-21: Eight elements planar array to form two adaptive beams from the hardware in the direction of arrival.....                         | 114 |

| Figure 7-22: Multiple beams generated for sixteen elements planar array. ....                                                                  | 115 |

| Figure 7-23: Planar array of sixteen elements Nine adaptive beams. ....                                                                        | 116 |

| Figure 7-24: Linear array of sixteen elements Nine adaptive beams. ....                                                                        | 117 |

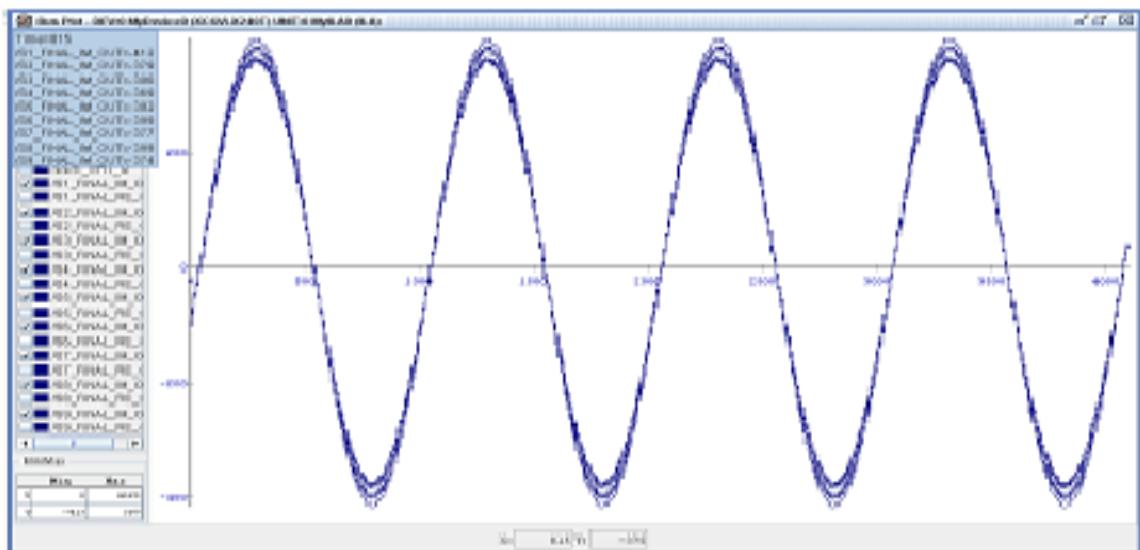

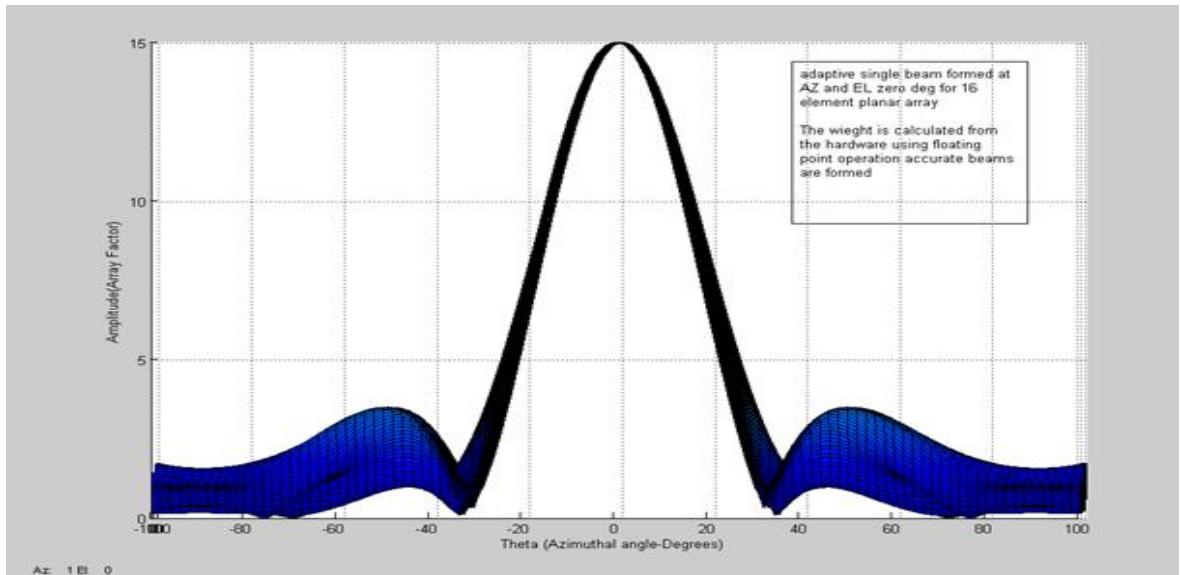

| Figure 7-25: Planar array of sixteen elements single adaptive beam. ....                                                                       | 118 |

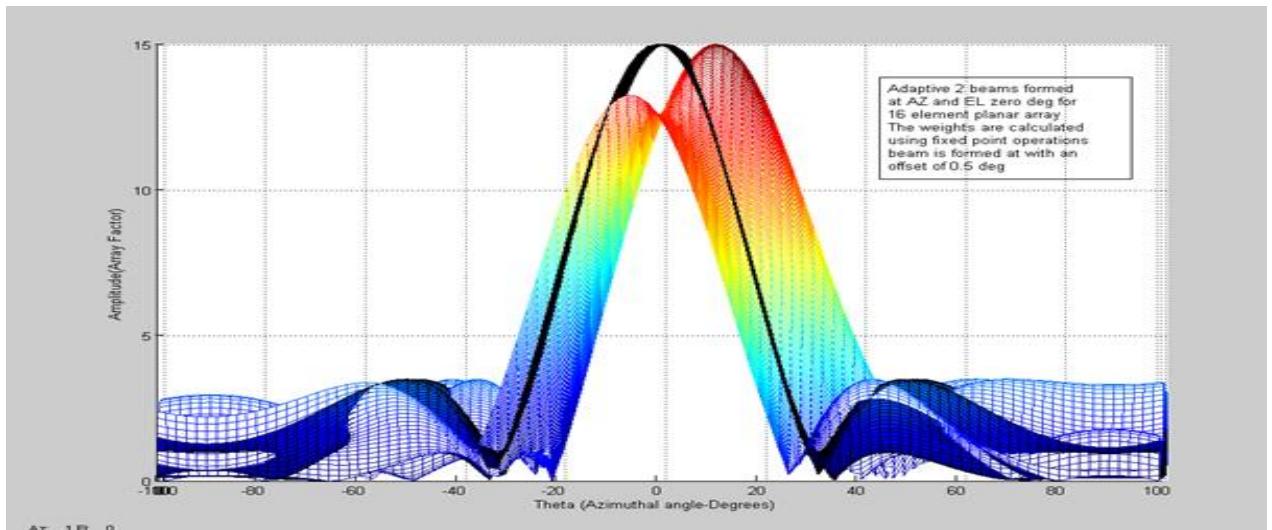

| Figure 7-26: Planar array of sixteen elements two adaptive beam. ....                                                                          | 118 |

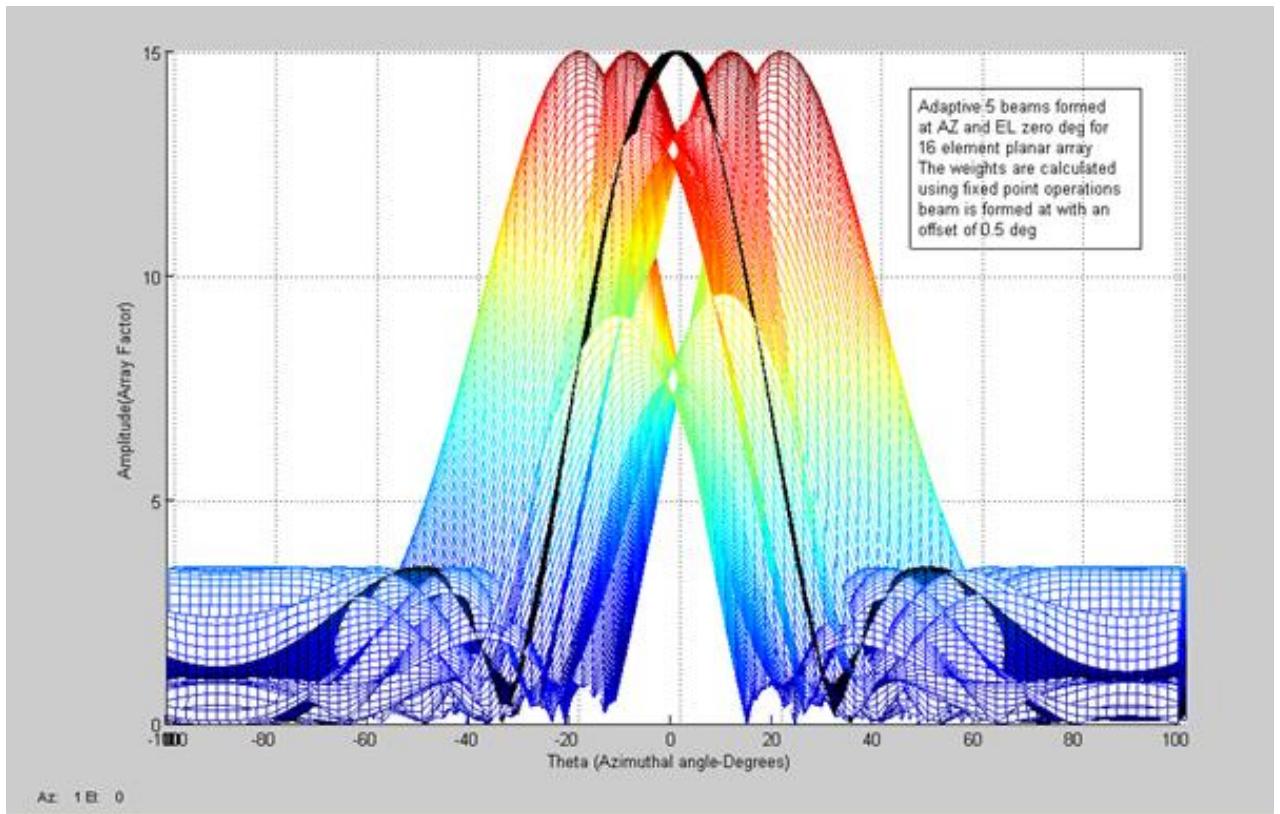

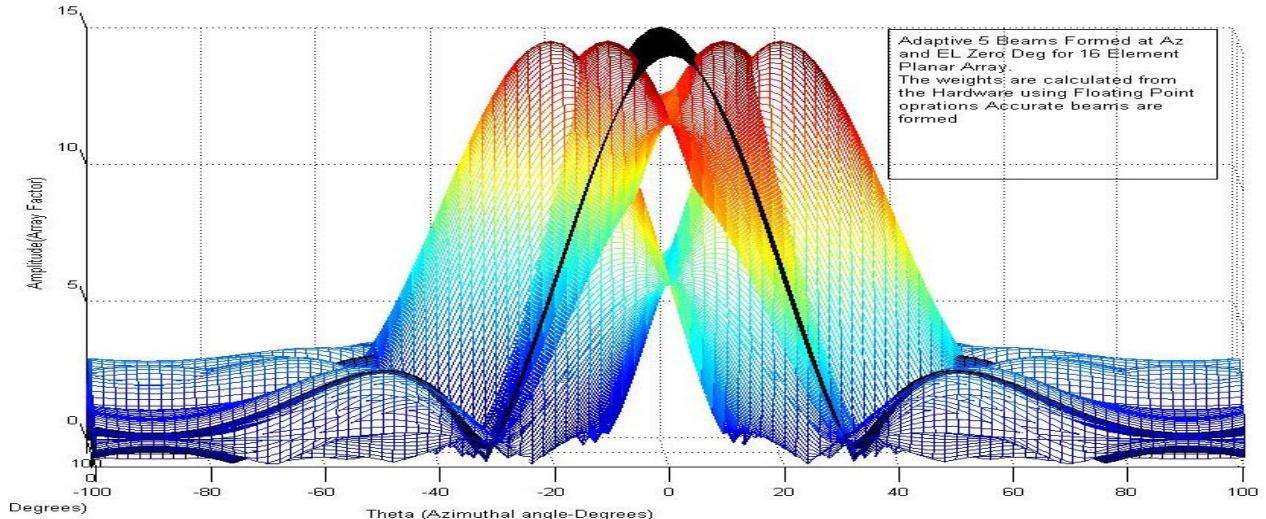

| Figure 7-27: Planar array of sixteen elements five adaptive beam.....                                                                          | 119 |

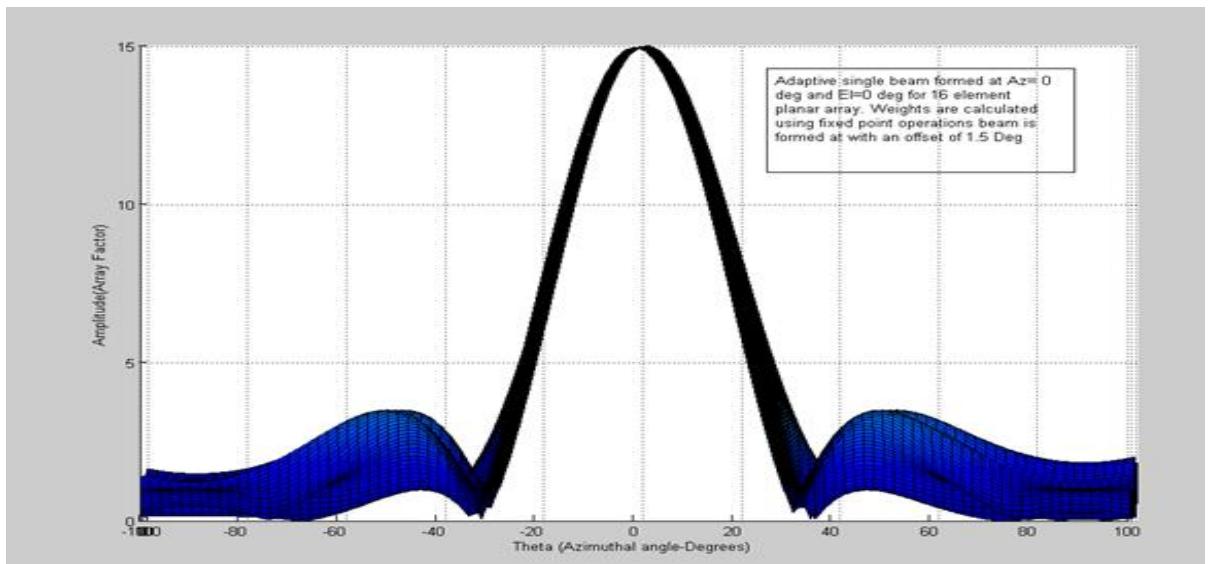

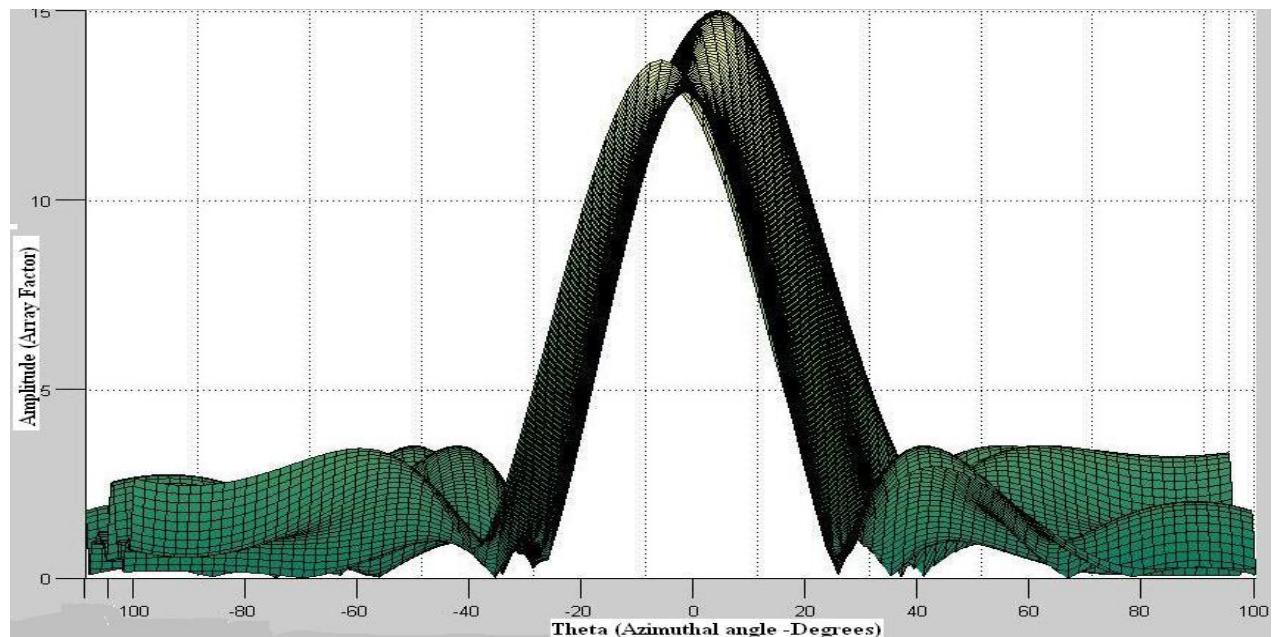

| Figure 7-28: Planar array of sixteen elements single adaptive beam. ....                                                                       | 120 |

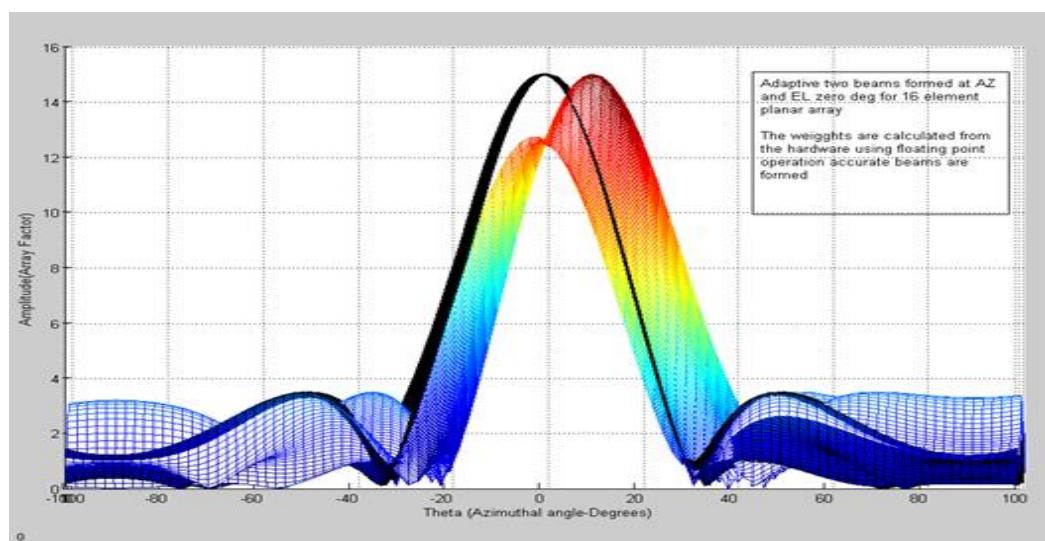

| Figure 7-29: Planar array of sixteen elements two adaptive beams. ....                                                                         | 120 |

| Figure 7-30: Planar array of sixteen elements five adaptive beams. ....                                                                        | 121 |

| Figure 7-31: Planar array of sixteen elements single beam.....                                                                                 | 121 |

| Figure 7-32: Planar array of sixteen elements four adaptive beams.....                                                                         | 122 |

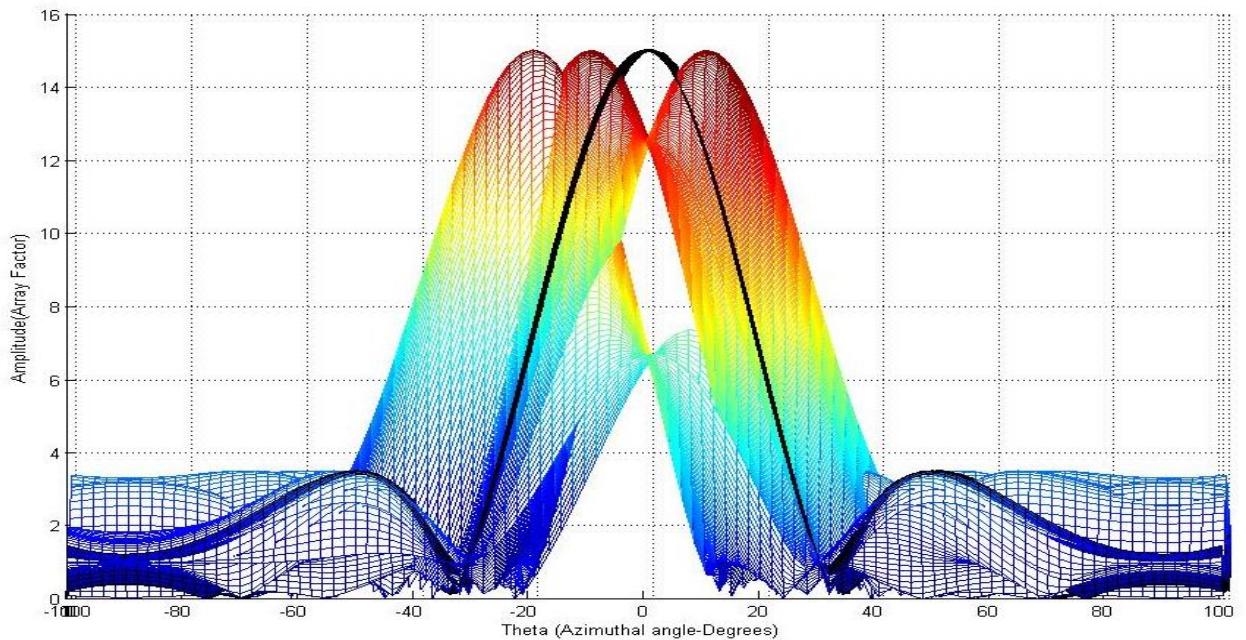

## **LIST OF TABLES**

|                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 6-1: Resource utilization of FPGA-I and FPGA II for implementation of Inverse QRD RLS for Adaptive beam former of 8 elements with Floating point operations..... | 93 |

| Table 6-2: Resource utilization of FPGA-III for implementation of Adaptive beam former for sixteen elements. (Floating point) .....                                    | 93 |

| Table 6-3: Resource utilization of FPGA-I and FPGA II for implementation of Inverse QRD RLS for Adaptive beam former of 8 elements with fixed point operations.....    | 94 |

| Table 6-4: Resource utilization of FPGA-III for implementation of Adaptive beam former for sixteen elements with fixed point operations. ....                          | 94 |

| Table 6-5: The Virtex-V FPGA resources utilization to form four beams.....                                                                                             | 95 |

| Table 6-6: The Virtex-VI FPGA resources utilization for four beam architecture .....                                                                                   | 95 |

| Table 6-7: Resource utilization Comparison for 32 bit Fixed and Floating point operations. ....                                                                        | 95 |

## LIST OF ABBREVIATIONS

|            |                                     |

|------------|-------------------------------------|

| RLS        | Recursive Least Squares             |

| QRD        | Q-R Decomposition                   |

| CRLS       | Constrained Recursive Least Squares |

| LMS        | Least Mean Square                   |

| FPGA       | Field Programmable Gate Array       |

| DDC        | Digital Down Conversion             |

| ADC        | Analog to Digital Converter         |

| NCO        | Numerically Controlled Oscillator   |

| DDS        | Direct Digital Synthesizers         |

| T/R Module | Transmit-Receive Module             |

| LUT        | Look-Up Table                       |

| IQRD       | Inverse QR Decomposition            |

| ADBF       | Adaptive Digital Beam Forming       |

# Chapter 1

## Introduction

# Chapter 1.

## Introduction

### 1.1 Beam Formation

Phased array antennas have played a crucial role in development of multifunction radars. There are numerous benefits of electronic scanning for multiple targets, search and track functions due to sufficient beam agility. The next generation of phased array antennas will offer improvements in radar functionality utilizing Digital Beam Forming (DBF) in place of its analog counterpart [112]. However, DBF requires higher computational throughput and more receivers to digitally perform the same operations that were formerly done with analog hardware. But due to advancement in the technology of digital computing it has become increasingly easier to accommodate the more demanding computing requirements.

A conventional analog phased array antenna sums the signals from the individual antenna elements through radio frequency combiner networks made up of one or more stages of phase shifter, attenuators, amplifiers and time delay networks. After the beams are formed in analog receivers, an ADC will be used to produce digital signals that are input to the radar signal and data processing computers. In a radar system with DBF architecture the receivers are placed prior to the final stage of combining so that some or all of the beam forming occurs in a digital computer. From an array of elements in the phased array configuration every element will have a low noise amplifier and then go directly into a receiver where the analog is converted to digital in phase and quadrature samples. The digital I and Q samples are then sent to a digital beam forming processor where the beam forming is done in a high speed computer.

A number of array signal processing techniques can be illustrated using the DBF architecture, including the following that can enhance the capability of radar systems,

1. For improved search occupancy by digital steering of beams on receive mode

2. Electromagnetic interference (EMI) mitigation and adaptive cancellation for jammer

3. Improved metric accuracy by high-resolution angle estimation of targets and jammers.

Also a significant amount of error due to costly analog time-delay units can be reduced by replacing them with infinite precision digital time delay wideband DBF array designs. As compared to a conventional analog array, where entire sum or monopulse difference beam is lost due to failures, a DBF array is more robust to receiver failures since only the part of the array feeding that receiver is lost.

Digital beam former design is an essential part of radar and information exchange architectures. There are numerous ways that beam forming is currently utilized [3][7]. The optimality of the system used in signal reception decreases due to sensitivity in SNR caused by unwanted signal which enters the system neither by the main lobe nor by the side lobes of the patterned beam. The processing of the signal is done by the signal processors for the signals which are received and then the beam is formed in the directions as specified [24][27].

Presently, efficient beam forming is employed in the filter algorithms which are adaptive and it can be utilized in the array system that comprises of the radar such that the intended signal is preserved in the occurrence of noise signal [25]. Due to the increase in radar traffic the interference suppression becomes more essential in those systems where adaptive beam forming has its major usage. The signals and interference properties are distinguished in the active phased planar array through beam forming where it comprises an array of sensors that are independent so that it gives the samples of signal which are received in space [22].

Hereby outputs from the sensor are modeled by a filter that can be transverse to produce output in the form of the beam. The basic aim of the modifying filter is to defend the target signal when the noise signal is cancelled. Moreover the modifying filter provides capacity to the system that consists of an array of antenna such that it can automatically capture the occurrence of the intruding signals to precisely suppress the noise signals which simultaneously enhance the referenced signal the QRD RLS algorithms are opted to be a better approach for those applications where convergence speed is paramount [27].

## 1.2 Phased Arrays

In a phased array antenna, the effective radiation pattern of the array is reinforced/suppressed in a desired/undesired direction by varying the relative phases of the respective signals feeding the antennas.

Multiple active antennas are grouped together and coupled to a common source to result into a directive radiation pattern in an antenna array. Normally the directivity of the antenna array is related to the spatial relationship of the individual antennas [5]. An "Active antennas" is one in which the signal input controls the source of energy. A multiband television antenna is one example of this nature [4].

The desired radiation pattern is achieved by changing the phase of the various elements. The limits are determined by:

- (a) The array configuration.

- (b) The array size.

- (c) The elements radiation pattern.

Phased Array main benefits are [32]

- A large structure need not be rotated to cover the entire space.

- The steering can be done in electronic mode hence faster steering in the desired direction.

- Solid-state transmitters are used in the entire phased array instead of a single RF sources. Hence warm-up time of the array is less, complex RF feed system not required, and single-point failure is removed.

- Capable to “zoom-in” in time

- System can run for long durations without any difficulty.

- Phased array can be assembled on an aircraft or a moving vehicle.

- The system can perform surveillance/tracking of thousands of targets in a given time.

- Remote operations are possible

- The great benefit is graceful degradation. Even some solid state amplifiers are failed in the active phased array, the radar system will work with degraded performance.

### 1.3 Adaptive Filter

An adaptive filter is a mathematically intensive algorithm that helps in modeling the relationship between two real time signals [11]. These filters can be realized by using arithmetical processing device like a DSP chip/microprocessor or by using field-programmable gate array (FPGA). They can also be realized using VLSI integrated circuits. The specific physical realization of the adaptive filter is independent of its basic operation.

The following characteristics define an adaptive filter:

- What are the signals that are processed.

- How the output signal is computed from input signal.

- How the filter's input-output relationship can be altered by changing different parameters within the structure.

- How the computational algorithm adjusts the parameters from one time instant to the next.

Different communication applications utilize the concept of adaptive weight calculation (AWC). Typical applications include multiple-input multiple-output (MIMO) systems, adaptive beam forming, pre-distortion and equalization [17]. In most of the applications, over-determined systems of equations is solved. The least squares approach is generally used for approximations. Some of these techniques are Normalized LMS (NLMS), Least Mean Squares (LMS) and Recursive Least Squares (RLS). For fast convergence rates and good numerical properties, the Recursive Least Squares is widely used. But this algorithm is not efficient in hardware implementation and terms of precision as, it requires matrix inversion. More accurate results and efficient architectures can be obtained by the technique of QR decomposition (QRD) based on RLS. [17].

An alternative method to implement the RLS technique is application of QR decomposition and triangularize the input data matrix. When quantization effects are considered, the RLS algorithm based on QR decomposition offers improved numerical behavior that can be used in implementation of systolic arrays [18].

RLS algorithms proposed earlier were based on the QRD technique [6] and mainly focused on information matrix triangularization to avoid the use of inversion of matrix. Due to multiplications for every output sample being of the order of  $[N^2]$ , the computational requirement was very high. Subsequently, variations of QR-RLS techniques have been

proposed with a condensed complexity of computation which is of the order  $[N]$ . The fast QR-RLS algorithms are related to the tapped delay line FIR filter realization. Implementation of the algorithms for inverse QRD-RLS algorithm is carried out in Xilinx FPGA.

## 1.4 Motivation

- The work carried out by the various researchers in this area is having certain limitations. As per the literature survey it is found that most of the work was carried out to address two important issues.

- Optimized QRD RLS for adaptive weight calculation in terms of area.

- Optimized processing time.

- The major issue has not been addressed by researchers is that, the complete adaptive beam former VLSI architecture to form multiple receive beams for a phased array radar applications.

- Various researchers have addressed individual module level performance factors and in totality the complete architecture to support for 16 element phased array has not been considered and architecture is not developed which will be suitable for a phased array radar.

- Due to the above reasons it is essential to develop VLSI architecture to support sixteen element phased array radar. The present day requirement of radar is adaptive nulling to be formed in the direction of the jammers i.e. angle of interference.

- It is required to design a scalable architecture which can be extended to a larger number of phased array antennas. This will be a great advantage for futuristic radars to work efficiently in the electronic war scenario. The architecture should be modular and scalable in nature.

## 1.5 Objectives and Contributions

### 1.5.1. Thesis Objectives

- **Objective-1**

Design and Realization of a Generic, Modular and scalable VLSI architecture of Adaptive Beam Formation for Sixteen element Phased Array.

- **Objective-2**

The designed architecture should be optimized in terms of speed. The total computation time for one beam should be less than 5  $\mu$ sec.

- **Objective-3**

The designed architecture should be optimized in terms of Area and should utilize maximum number of DSP slices to handle all the arithmetic operations. The state of the art technology FPGA's should be used to develop the architecture.

- **Objective-4**

The designed VLSI architecture should be validated on the hardware and should meet the timing, functional and interface requirements.

### 1.5.2. Thesis Contributions – A Summary

- The VLSI architecture of Adaptive Beam Formation for Sixteen element Phased Array is designed which is Generic, Modular and scalable in nature. This architecture is developed in various stages. First the beam formation architecture is designed using the weights which are calculated offline and are stored in a separate memory. Multiple receive beams are formed in the fixed directions around the transmit beams. Q-R Decomposition based RLS algorithm is used for optimal weight calculation. The simulation is carried out in MATLAB to demonstrate multiple receive beams. Second, the modified architecture is designed consisting of digital down conversion, complex multipliers and Inverse Q-R Decomposition RLS module to calculate the weights online. The architecture is simulated in MATLAB and multiple beams have been validated in various look angles in the phased Array Configuration.

- A pipelined and parallel architecture is developed using a systolic array method for optimal weight calculation. The algorithm is mapped in a pipelined sequence of basic computation cells such as Angle processor, Rotation processor, and Weight

processor. These basic cells perform their task in parallel, such that in each clock period all the cells are activated.

- The Angle processor takes the input data from the input vector matrix and computes the rotation angles. Cosine and sine calculations are carried out and given to the rotation processor to perform the rotation and obtain the new set of values. Angle processor stores the rotated data in its internal memory and uses whenever new data is available.

- The Rotation processor performs the given rotation on the input data by multiplying it with the cosine and sine from the angle processor to generate the rotated data and stores in its internal memory and passes the output to the cell of next row.

- Weight processor receives data from rotation processors in its previous row and cosine & sine of the rotation angle from angle processor in its row.

- The initial architecture was designed using the QRD RLS adaptive algorithm. But this algorithm needs back substitution method which will take double the time to arrive at optimal weights. Hence the architecture is modified for Inverse QRD RLS Adaptive algorithm to generate the optimal weights. The architecture is optimized for 4x4 matrix size considering 16 element planar phased array configurations. The optimal time for adaptive weight computation and beam formation achieved is 4.6 u sec.

- The pipelined architecture of IQRD-RLS algorithm implemented for 4x4 matrix size array using multiple FPGA's. Three FPGA's are used to form the complete architecture. FPGA1 and FPGA2 architectures remain identical in nature. Each one is interfaced with eight ADC channels for receiving the antenna element data. Total sixteen channel data will arrive simultaneously. It take input from the ADC, and then DDC will make two signals from the ADC input by multiplying the ADC output with the NCO (Numerically Controlled Oscillator) output which is sine and cosine waves, producing two frequency translated signals, one in phase with the input signal and the other is quadrature signal. The DDC is used as a frequency translator. Once the input data matrix is available, based on that Adaptive weight computation using systolic array method, optimal weight will be calculated for each one of the element in the phased array configuration. The optimal weight will be multiplied with the input signal for respective element data in the phased array to form the beam in the desired direction and a null in the interference direction.

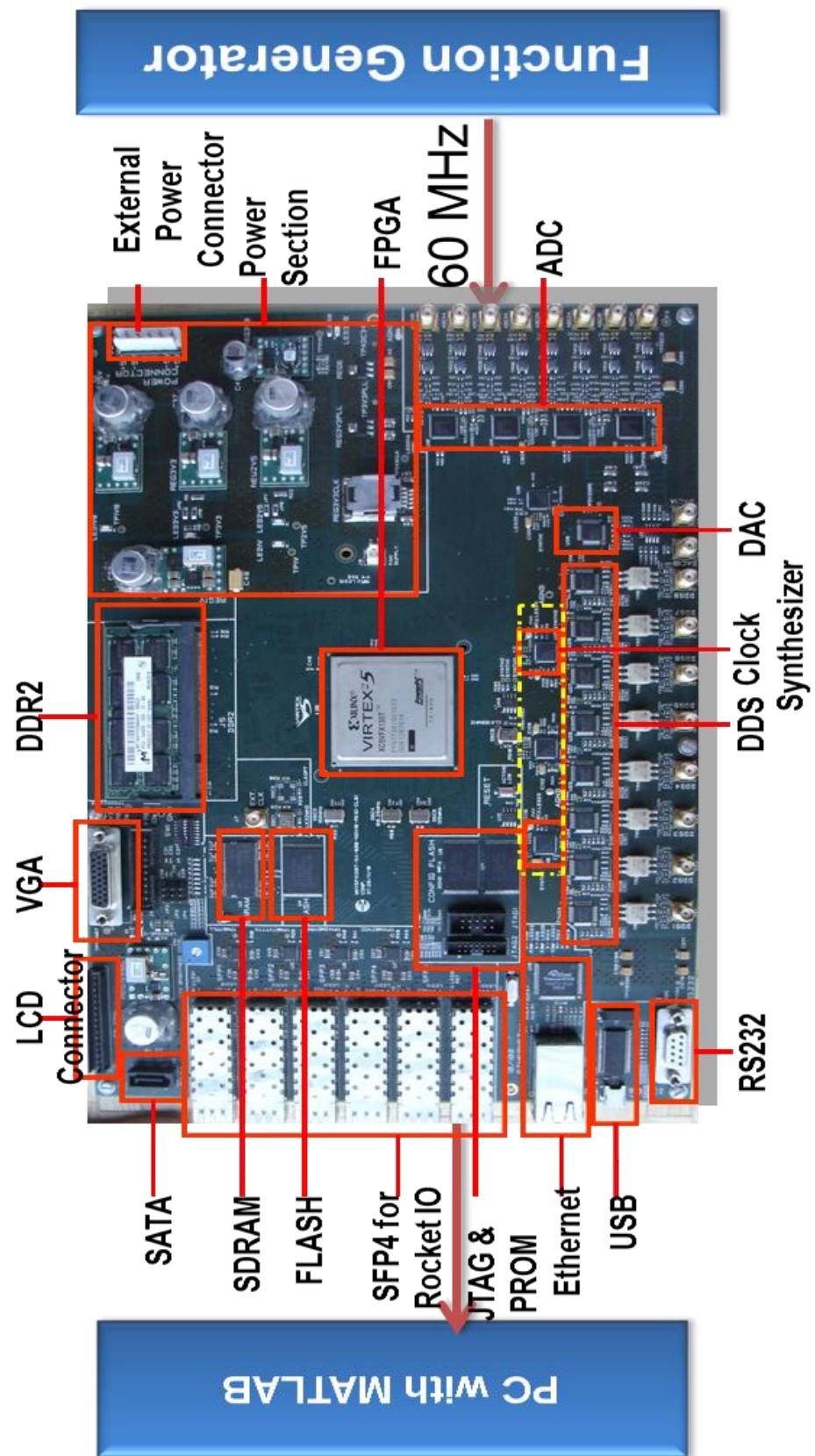

- The architecture is optimized to use more number of DSP slices instead of slice registers and slice LUTs. This has resulted in the area optimization of the Adaptive beam formation Architecture. To validate this architecture a proto hardware is used which is having three FPGA's along with sixteen channel ADC's on board. A test set up was developed; commands and controls were given from the Remote PC. Real time data captured from the FPGA's, plotted in MATLAB and validated with the simulated results. The designed architecture has met the functional, timing and interface requirements to form multiple Adaptive Receive beams in the desired direction.

## 1.6 Thesis Organization

Chapter 1 presents a brief introduction to the Beam formation in phased array Radar. The motivation behind this research work and the thesis objectives and contributions are also mentioned. At the end, organization of the thesis is elaborated.

Chapter 2 describes an elaborated literature survey, carried out by referring various international journals and international conferences. The detailed study has been covered in this chapter.

Chapter 3 explains various algorithms for computation of adaptive weights. The most suitable algorithms are QRD and IQRD RLS for optimal weight calculation. The details of these algorithms are covered.

Chapter 4 includes architecture development for 16 elements Phased Array with MATLAB functional Simulation results.

Chapter 5 covers the realizable and optimized VLSI architecture for 16 element array to form one beam within the given time.

Chapter 6 elucidates beam formation using fixed weights and beam formation with adaptive weights architecture development and Implementation on the hardware.

Chapter 7 reveals the results of functional simulation, fixed weight beam formation and adaptive weight beam formation. Comparison of the results using floating point arithmetic and fixed point arithmetic and operations in computing the weights and beam formation architecture.

Chapter 8 presents the conclusion of the research work.

## 1.7 **Summary**

In this chapter brief introduction of beam formation for phased array Radar is explained along with the benefits and limitations of phased arrays. The working principle of adaptive filter and various applications of adaptive filters are covered. Particularly for phased array radar application the role of adaptive filter is explained along with various adaptive algorithms. The requirement of optimized adaptive weight computation in terms of processing time and area is covered.

Further the motivation to carry out this novel method of adaptive beam former is explained. The resources optimization and time for the computation of weights are two important parameters are briefed. The thesis objectives are listed and the main contribution is hardware realization of a planar array adaptive beam formation for phased array radar is covered in detail. At the end of the chapter thesis organization is covered mentioning the design challenges, experimental results and conclusion.

In the next chapter a detailed literature survey is covered, mentioning the research work carried out till now and limitations of the same in this area. Many researchers have focused on simulation study of adaptive filters alone but the architecture required for phased array application was not considered. The literature study shows that small section of the entire architecture developed in this thesis was illustrated. Significant information on processing time for complete architecture to form multiple adaptive beams was not illustrated in the literature.

# **Chapter 2**

# **Literature Review**

## Literature Review

### 2.1 Phased Array Radar

There are thousands of radiating antenna elements in a modern day active phased radar that makes it a very complex system. Each antenna element consists of dedicated transmitters and receivers. Cluster of sub array transmitters and receiver are spread across the antenna elements. There are dedicated digital communication links that connects all the subsystems. The RF energy will be distributed in the antenna frame with a limited space in the array.

In a Planar Phased array antenna, there is an array of radiating elements on a regular lattice or rectangular grid or triangular grid structure. Several thousand elements will be used to make phased array antenna. In phased-array radars the waveform diversity of MIMO radar is compromised. However, phased-array radar has better performance in terms of side lobe suppression level, computational complexity, and signal-to-noise ratio (SNR) loss with the objective of range and doppler side lobe suppression. This simplifies the design of large scale radar systems.

A good amount of research work has been carried out in this area and observed that various techniques have been identified to reduce the side lobe suppression and to form pencil beam with wider antenna structure. But the adaptive beam formation for larger array dimension is not addressed efficiently by the researchers. The architectures were not developed to meet the present day requirements of the phased array radar.

### 2.2 Digital Beam formation in phased array Radar

With recent advancements in VLSI technology it has become possible to accommodate several complex DSP algorithms into efficient architectures and realize small high performance Application Specific Integrated Circuits (ASICs) or Field Programmable Gate Array (FPGA) devices. In Digital Beam Forming (DBF) technology antenna technology and digital technology are combined together. There are multiple advantages of

using digital methods for beam forming in Radar systems and can achieve high degree of flexibility in performance of the radar by “Beam Pattern Management”. Coherent processing of data collected with an array of sensors enhances coherent wave front, measurement of a propagating wave front relative to ambient background noise and spatially localized interferences in conventional beam former. To achieve this, weighted sensor data are time delayed and summed. The weighted sum of the sensor signals of beam formers is given as output in receive mode due to which, signal dimensions reduce from the number of elements to one. There are various advantages of DBF in receive and transmit ends like high gain, closely placed multiple beam low side lobe levels adaptive nulling, flexible radar power and time management. In a digital beam former system the RF signal is converted into I and Q Channels two streams of binary base band signals representing from each antenna element. Using these I and Q two digital base band signals amplitudes and phases of the signals received at each element of the array can be recovered. Multi-byte A/D converters are available to receive data from antenna, carry out the sampling and provide the output data in digital domain. Faster processing speed and computation power have enabled, the computation of multiple beams digitally using VLSI instead of RF domain. Therefore the deciding factors for number of simultaneous beams are mainly the processor speed and its processing capacity and speed of A/D conversion and its resolution which is ADC number of bits. Input samples are weighted by a complex weighting function adding together to form the desired output. A set of beams that are differently oriented in space are formed as end product of this process with each beam giving access to a number of range and Doppler cells. DBF mainly involves the following key tasks : a) Analog signal is translated into digital domain accurately with the help of high speed ADCs b) Digital mixing, down converting digital filtering is carried out on these high speed samples by DSP methods c) Beams are sent for further processing and plotting using high speed data communication. Researchers have carried out the work on the fixed weight beam formation for communication application and not for radar application. There is a need to develop the VLSI architecture for active phased array application which will greatly help in carrying out the adaptive nulling in the direction of jammers.

### **2.3 QR decomposition**

QR decomposition (QRD) has applications in smart antennas, sonar systems, phased-array radars, adaptive beamforming, channel equalization and, 3G wireless communication, de-noising, echo cancellation and WiMAX. In QR Decomposition a  $m \times n$  real matrix A

as:  $A=Q \times R$ , where  $Q$  is an  $m \times m$  orthogonal matrix such that  $Q \times Q^T = I$  where  $I$  is an identity matrix, and  $R$  is an  $m \times n$  upper triangular matrix. An orthogonal transform of a vector  $X = [x_1, \dots, x_n]^T$  can be defined by the orthogonal matrix  $Q$  as:  $Y = Q^T X$ .

The vector's length:  $Y = X$  is not changed in the orthogonal transform. Computational stability and fast convergence are characteristic features of QRD. Many algorithms are available for solving the QRD problem. Some of them are the Givens rotations method, Gram-Schmidt method, Householder transformations, and modified Gram-Schmidt algorithms. Most of the algorithms implementations support a linear i.e one dimension systolic array. Researchers have developed a full two-dimensional (2D) systolic array [114] which is implemented in this work. Unlike all previous work, in Givens a rotation does not avoid divide and square root operations for implementation of QRD. The dynamic range of the input matrix data is accommodated by carrying out all operations floating-point arithmetic. Further, any bit width exponent and mantissa and any size floating-point format, is supported, including standard formats of IEEE. Whereas other work that support only square matrices or tall matrices, QR implementation works for input matrix of any size: short, tall or square matrices. Subject to available hardware resources, the input matrix size can be configured at compile time to virtually any size. As compared to a one dimension systolic array implementation, where latency increases quadratically, latency of two dimension systolic array implementation linearly increases. High throughput and fast clock rate are achieved in QR implementation due to fully pipelined architecture. Also it is easy to scale up the design over multiple FPGAs and future FPGAs.

The main limitations are computational complexity in arriving the optimal weights are not addressed. The speed of operation is an essential factor to be considered for an efficient architecture which has lacked in the previous work done by the researchers. Large size of channel matrix suffers large latencies and low throughput in conventional QR Decomposition hardware.

## 2.4 Adaptive Phased Array

Target Detection and tracking are specific applications of a radar system. Scanning and tracking or guiding objects is one such crucial application. There are various important requirements of future phased array radar systems which includes high SNR, high sample rate, large size array. To meet this radar system requirement generally seven GHz to thirteen GHz range of RF frequencies will be used for realizing systems. At any given time in the

space multiple targets will be available in order to track all the targets simultaneously multiple independent beams are required.

Present day radar systems are using phased array beam forming techniques. Primary concern for design of such systems is functional requirements such as resolution; sensitivity, response time and secondary concern are non-functional requirements such as cost, power consumption [115]. Due to this, it is difficult to find phased array systems that are low-cost and low-power. However, phased array antennas have been very promising in areas like software defined radio and satellite receivers, but their large scale realization cost is very high. Here development of a low-cost, low-power phased array receiver platform is our goal. A scalable architecture can be used for realizing this which is highly flexible and can support a number of applications, in such a way that multiple requirements can be met using same architecture. High performance can be realized using reconfigurable Multiprocessor System-on-Chip (MPSoC) based system architectures. These architectures enable efficient reuse of hardware by reconfiguring parts of an application. As compared to reconfigurable hardware, central processing hardware is used in conventional phased array receivers, that makes the system non scalable less power efficient [116].

## 2.5 Phased Array Systems and Applications in Radar

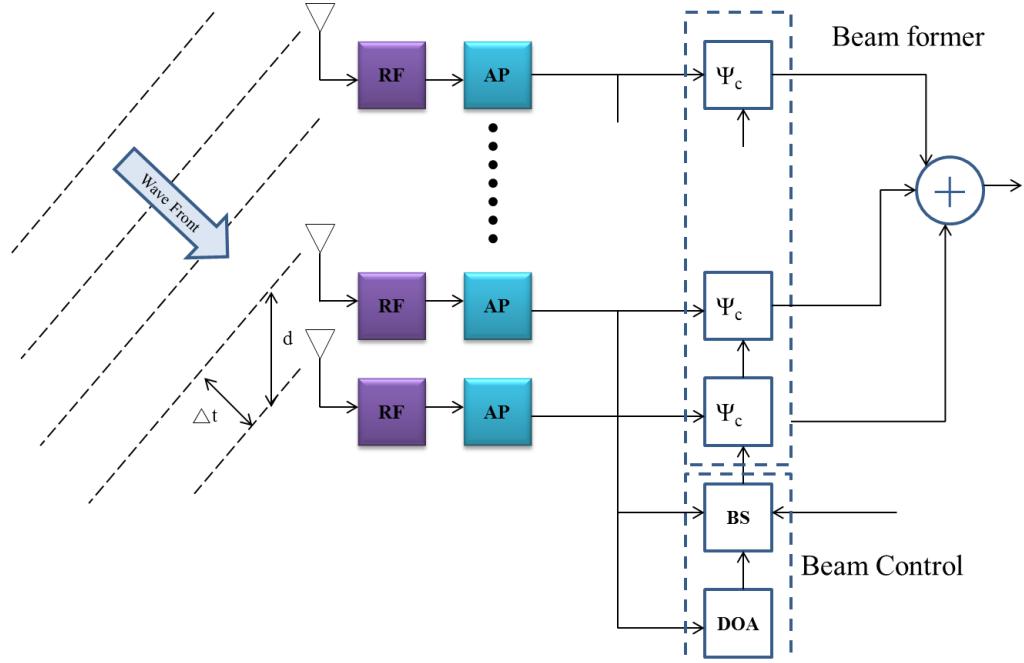

Figure 2.1 show radar system modules of a generic phased array system. Signals are received at multiple antennas in a phased array receiver. Antenna Processing (AP) is applied for calibration or equalization purposes after the Radio Frequency (RF) front end for each antenna. By use of equalization process electrical or mechanical distortions are improved for the front-end and the wireless channels. The beam forming unit then combines the signals and creates a resulting signal with maximum sensitivity in desired direction and a minimum sensitivity or a null in other directions. By changing the shape and direction of formed beam that is achieved by changing the delay and gain and the antenna signals before summation is referred as beam steering process. Let's say a wave front arrives at an angle of incident to the array in a phased array that consists of antennas placed at a distance  $d$  apart.

Figure 2-1: Generic Phased Array Receiver

If a time delay  $t = l/c$  is observed between the signals where  $c$  is the propagation speed of radio waves. The wave front traveling a distance  $l = d \sin(\psi)$  further to the next antenna, then a phase shift  $(\psi t)$  would happen if the signal is a narrowband signal, due to this time delay giving rise to the term ‘phased array’. By correcting the delay [1], the direction of maximum sensitivity steering is achieved.

Fixed array configuration used in traditional adaptive array beam forming can lead to significant performance loss and inefficiencies under different scenarios. A reconfigurable adaptive antenna array strategy becomes particularly important to achieve high signal to noise and interference ratio using fewer antennas as antennas become smaller and cheaper relative to front-ends. Spatial Correlation Coefficient (SCC) can be minimized between the desired signal and the interference and this objective can be achieved.

## 2.6 Fixed point operations and floating point operations

The VLSI architectures can be designed using either fixed point arithmetic or floating point arithmetic operations. The architecture based on fixed point operations design needs less FPGA resources and computation time is much faster. This also brings the limitations in terms of rounding and truncation errors.

The floating-point arithmetic permits us to symbolize broad range of numbers with constant precision. Finite-point arithmetic symbolizes a decreased range of numbers with appropriate precision absolute. Employing floating precision arithmetic is highly expensive

when considered in terms of hardware and results in inefficient architecture, particularly when implemented using FPGA. Alternatively the fixed precision arithmetic representation leads to hardware design that is efficient and also introduces a small amount of error. Here the design employs two's compliment method and the representation of finite precision arithmetic comprise of the sign bit, integer part along with the fractional part. Quantities that find occurrence in the algorithm are characterized with  $m_n$  bits designed for the integer along with  $m$  bits which are employed for the representation of the fractional bits. Finally, representing a finite precision illustration would entail  $m_n+m+1$  bit, were one bit is utilized as a sign bit representation [80].

QR decomposition needs the usage of arithmetic operations, the calculations required finds an expansion when there is growth in the dimension of the matrix. Large number of calculations is observed during the matrix decomposition process where the orthogonal matrix and upper triangular matrix are obtained. Calculations employed for the decomposition process are the basic arithmetic computation which is a direct approach; complicated computations significantly alter the precision of the entity likely producing the inefficient values during the implementation in the FPGA. Finite-precision arithmetic reduces the obtained precision and thereby introducing two different types of errors which are coined as the round-off and the truncate error. Round-off error [129] makes its presence when the additional bits are required in the outcome than the bits that are reserved usually after the arithmetic computations.

## 2.7 Papers Referred

- 1) Researchers have carried out the work on “*A low-complexity high speed QR decomposition implementation for MIMO receivers, published in IEEE Symposium in 2009. In this research a hybrid QRD scheme that uses a combination of multi-dimensional Givens rotations, Householder transformations and the conventional two-dimensional (2D) Givens rotations to both reduce the overall computational complexity and achieve higher execution parallelism. To prove the effectiveness of the proposed QRD scheme, a novel pipelined architecture is presented that uses un-rolled pipelined CORDIC processors iteratively to maximize throughput and resource utilization, while minimizing the gate count. The proposed design achieves the lowest processing time and the highest throughput reported to-date for the same framework. The proposed scheme reduces the overall computational complexity and allows*

*higher execution parallelism, and is proved to have the same BER performance as the conventional scheme through simulations. The major limitations of this approach are huge amount FPGA resource utilization”.*

- 2) Various researchers have thought of “*Optimal implementation of QR decomposition. A work published in 2011 on Fixed-point CORDIC-based QR decomposition by givens rotations on FPGA, Givens rotations algorithm based QR decomposition systolic array a parallel architecture implemented on FPGA. The proposed architecture adopts a direct mapping by 21 fixed-point CORDIC-based process units that can compute the QR decomposition for a 4×4 real matrix. In order to achieve a comprehensive resource and performance evaluation, the computational error analysis, the resource utilized, and speed achieved on Virtex V Field Programmable Gate Arrays, are evaluated with different precision of the intermediate word lengths. The limitations are 32 bit word lengths are not worked out and time and area are not optimized for beam forming application*”.

- 3) Further Researchers have developed “*FPGA implementation of fast QR decomposition based on givens rotation, in 2012 this work was published in fifty fifth IEEE International Midwest Symposium on Circuits and Systems. In this work an enhanced fixed-point hardware design of QR decomposition, particularly optimized for Xilinx FPGAs is evaluated. Givens Rotation method implementation on FPGA is presented. The feedback loop problem is addressed, and a very high throughout is achieved. Further work is expected on large matrix size decomposition as well as using dynamic reconfigurable technology to optimize size and area. The main limitations are it is not a generic architecture for beam formation; uses large number of Resources and computation is also not efficient*”.

- 4) Researchers have worked on “*FPGA based architectures for high performance adaptive FIR filter systems which is published in IEEE International Instrumentation and Measurement Technology Conference in 2013. This work presents a high performance adaptive FIR filter hardware architecture. In particular, the RLS (Recursive Least Square) algorithm for adaptive signal processing is explored based on QR decomposition, which is accomplished by using the Givens Rotation algorithm. The Givens Rotation algorithm is implemented using a systolic array and LUT-based Newton’s method. This*

*architecture is suitable for high-speed FPGAs or ASIC designs. It also solves the trade-off between throughput and latency issues. As a case study, this QR design is tested using Xilinx XC5VLX110T FPGA. The findings show that the system is capable of running the QR decomposition at up to 200MHz with 56 clock cycles latency. The main limitation of this approach is that, it addresses only the local issue of QR decomposition. This work is not focused on Adaptive beam formation”.*

- 5) Researcher have worked on “*Low complexity QR-decomposition architecture using the logarithmic number system, and published in EDA Consortium, 2013. In this work, they have proposed a QR-decomposition hardware implementation that processes complex calculations in the logarithmic number system. The proposed algorithm is simulated with several different configurations in a downlink pre-coding environment for 4x4 and 8x8 multi-antenna wireless communication systems. In addition, the results are compared with the CORDIC-based architectures. In a second step, HDL implementation as well as logical and physical CMOS synthesis are performed. The comparison to actual references highlight this approach as highly efficient in terms of hardware complexity and accuracy. The limitations are, they used wireless communication for data transfer, by using this type of communication the data loss is more and communication speed is very less and it will affect very badly the accuracy of the system”.*

- 6) Researchers have developed on “*FPGA Implementation of Beam forming Algorithm for Terrestrial Radar Application, and published in 2014. Here Beamformer algorithm is developed using LMS algorithm was simulated and implemented hardware using Altera FPGA. Here focus, is to implement adaptive beamforming algorithm known Least Mean Square Algorithm in FPGA. The limitations are, they use LMS algorithm which has very low convergence speed and sample matrix inversion is not possible in this algorithm”.*

- 7) Researchers have simulated on “*FPGA Methodology for Power Analysis of Embedded Adaptive Beamforming IEEE 2015. In this work, they proposed an FPGA-based methodology for the analysis, modeling and prediction of power dissipation in embedded array signal processing systems containing adaptive beamforming components. This FPGA-based methodology enables the*

*exploration of the adaptive beamforming design space in terms of power, timing, overhead, arithmetic precision and computational resources. A distinct feature of this methodology is that it enables such design-space exploration in real-time and on actual received waveforms. They describe a specific implementation of this methodology using a hardware prototype based on Xilinx's Virtex 7 FPGA. They use this prototype to explore the design space of a four-channel Least-Mean-Squares (LMS) beamformer. The main result of this exploration is the selection of an adaptive algorithm design point that represents the best tradeoff between parameter convergence, machine precision and energy-efficiency for the embedded array signal processor. The Limitations are, they used LMS algorithm, this algorithm convergence speed is very low compare to QRD RLS and Sample matrix inversion is not possible in this algorithm”.*

- 8) Researchers have developed “*a high performance adaptive FIR filter hardware architecture. In particular, the RLS (Recursive Least Square) algorithm for adaptive signal processing is explored based on QR decomposition, which is accomplished by using the Givens Rotation algorithm. The Givens Rotation algorithm is implemented using a systolic array and LUT-based Newton's method. This architecture is suitable for high-speed FPGAs or ASIC designs. It also solves the tradeoff between throughput and latency issues. As a case study, this QR design is tested using Xilinx XC5VLX110T FPGA. The findings show that the system is capable of running the QR decomposition at up to 200MHz with 56 clock cycles latency*”.

## 2.8 Summary

In this chapter a detailed literature survey is covered, mentioning the research work carried out till now and limitations of the same in this area. Many researchers have focused on simulation study of adaptive filters alone but the architecture required for phased array application was not considered. The literature study shows that small section of the entire architecture developed in this thesis was illustrated. Significant information on processing time for complete architecture to form multiple adaptive beams was not illustrated in the literature.

In the next chapter adaptive filter multiple algorithms were covered along with the detailed structure of adaptive filter, convergence rate and computational aspects. The recursive least square (RLS) is mentioned along with conventional QRD-RLS and Inverse QRD-RLS mathematical model.

# Chapter 3

## Adaptive Filter Algorithms

## Adaptive Filter Algorithms

### 3.1 Introduction

The Research area of advanced signal processing and specifically adaptive signal processing has seen a vast development in the last few decades, because of advancement in the technology for realization of the advanced algorithms on the hardware. Large numbers of problems have been solved using these algorithms. These problems include noise cancellation, echo cancellation, signal prediction, channel equalization and adaptive arrays.

There is a close relationship of Adaptive filtering algorithms with regulating mechanism for the filter coefficients with the traditional optimization techniques [69]. However, in the classical approach, all computations are carried out in an off-line method. Due to its real-time dynamic characteristic, an adaptive filter tracks the optimum behavior of a slowly varying environment. There are wide varieties of adaptive algorithms which can be compared based on, following aspects.

- **Computational aspects:** Computational complexity is an important factor for the adaptive filter performance. Dynamically the weight vector needs to be calculated in the real time scenario. The weight vectors should be obtained with minimum number of operations and should be optimal in nature. Also the errors generated during the computation should be as small as possible.

- **Filter structure:** The transfer function gives the relationship between input and output of the adaptive filter. The delay line filter is easy for implementation, simple and efficient. The computational complexity and speed of adaptation with respect changing environment is an important aspect of the adaptive filter.

- **Rate of convergence, tracking and maladjustment:** The weight vectors of a filter will converge in a faster way if the environment is noiseless other way the convergence will be slower if the environment is very noise. The weights will be near to optimum value, but they are how close to the optimum will define the maladjustment. The algorithm convergence speed in non-stationary environment is related to the adaptive filter tracking ability.

In designing adaptive filters for radar applications, recursive least squares (RLS) and constrained recursive least squares (CRLS) [10, 4] algorithms were the promising methods compared to least mean squares (LMS) algorithm due to their fast convergence rate. CRLS and RLS algorithm uses direct inversion input data matrix. It has two major disadvantages. One is that this method has undesirable numerical characteristics when complex covariance matrix is ill conditioned. Another disadvantage is that the RLS and CRLS algorithms cannot be implemented as parallel and pipelined array processors for real time signal processing applications [12].

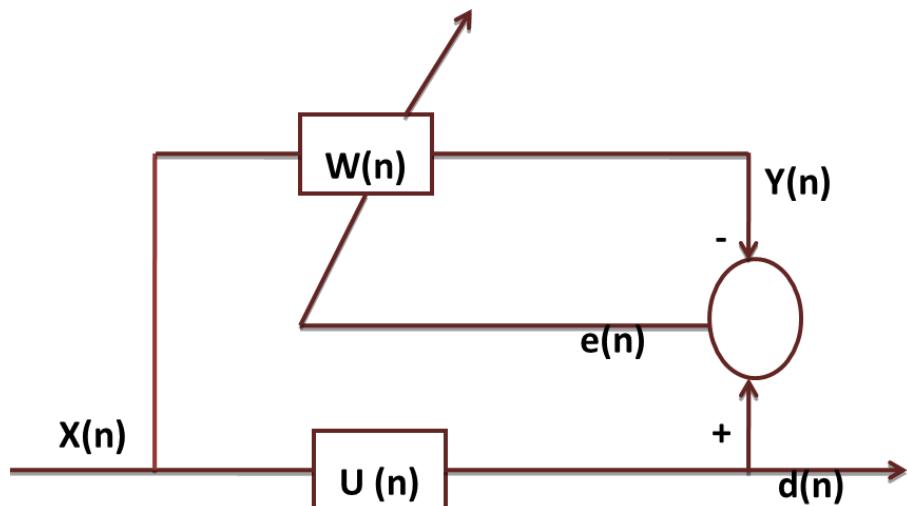

The adaptive filter has wide range of applications like system identification, channel identification, plant identification, echo cancellation, acoustic echo cancellation, and adaptive noise cancellation. This adaptive filter is used for channel identification where a beam is formed for phased array radar application. All adaptive filters have the same general parts; an input  $x(n)$ , a desired result  $d(n)$ , an output  $y(n)$ , an adaptive transfer function  $w(n)$ , and an error signal  $e(n)$  which is the difference between the desired output  $u(n)$  and the actual output  $y(n)$  as shown in Figure 3.1. In addition to these parts, the system identification and the inverse system configurations have an unknown linear system  $u(n)$  that can receive an input and give a linear output to the given input.

Figure 3-1: Basic adaptive filter structure

### 3.2 Recursive Least Squares approach

The adaptive filter operates on recursive manner and optimizes the weighted sum of the squared estimation errors; hence it is known as recursive least-squares (RLS) adaptive filters [12]. The RLS finds the precise solution for every iteration [2]. Let us consider the exponentially-weighted RLS adaptive filter [19] and derive the optimal solution.

Let  $\mathbf{W}(n)$  denote the coefficient vector of the adaptive filter at time  $n$ . Even though we have not yet formulated the problem, assume that  $\mathbf{W}(n)$  is the optimal solution of the problem[62]. Let the estimation error at time  $k$  due to the coefficient vector  $\mathbf{W}(n)$  be  $e_n(k)$ , *i.e.*,

$$\mathbf{e}_n(\mathbf{k}) = \mathbf{d}(\mathbf{k}) - \mathbf{W}^T(\mathbf{n})\mathbf{X}(\mathbf{k}) \quad (3-1)$$

The exponentially-weighted RLS adaptive filter selects the coefficient vector  $\mathbf{W}(n)$  so as to minimize the exponentially-weighted sum of the squared errors given by

$$J(\mathbf{n}) = \sum_{k=1}^n \lambda^{n-k} e_n^2(k) \quad (3-2)$$

Finding the optimal solution is an easy proposition. Substituting “Eq.(3.1)” for  $e_n$  into “Eq.(3-2)” and expanding gives

$$J(\mathbf{n}) = \sum_{k=1}^n \lambda^{n-k} \mathbf{d}^2(k) + \mathbf{W}^T(\mathbf{n}) \{ \lambda^{n-k} \mathbf{X}(\mathbf{k}) \mathbf{X}^T(\mathbf{k}) \} \mathbf{W}(\mathbf{n}) - 2 \{ \lambda^{n-k} \mathbf{d}(\mathbf{k}) \mathbf{X}^T(\mathbf{k}) \} \mathbf{W}(\mathbf{n}) \quad (3-3)$$

$J(n)$  is a quadratic function of the coefficients, it has a unique minimum whenever the matrix within brackets in the second term on the right-hand-side of “Eq.(3.3)” is positive definite. In most cases, the matrix

$$\sum_{k=1}^n \lambda^{n-k} \mathbf{X}(\mathbf{k}) \mathbf{X}^T(\mathbf{k}) \quad (3-4)$$

is positive definite1 for  $n > L$ . The optimal coefficient vector can be determined from “Eq.(3-4)” by differentiating  $J(n)$  with respect to  $\mathbf{W}(n)$  and setting the resulting vector equal to the zero vector. This operation gives

$$2\hat{\mathbf{R}}_{xx}(\mathbf{n})\mathbf{W}(\mathbf{n}) = \hat{\mathbf{P}}_{xd}(\mathbf{n}) \quad (3-3)$$