# **Analytical modeling and simulation of gate material and channel engineering of DG Strained-Si MOSFET with interface charges**

*Submitted in partial fulfillment of the requirements

for the award of the degree of

DOCTOR OF PHILOSOPHY*

*by*

**SUDDAPALLI SUBBA RAO**

(Roll No: 717028)

Supervisor:

**Prof. N. Bheema Rao**

Professor

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

TELANGANA STATE-506004, INDIA

2021

# Approval Sheet

This thesis entitled "**The analytical modeling and simulation of gate material and channel engineering of DG Strained-Si MOSFET with interface charges**" by **SUDDAPALLI SUBBA RAO** is approved for the degree of Doctor of Philosophy.

---

---

---

Examiners

---

---

---

Supervisor (s)

---

Chairman

Date: \_\_\_\_\_

# DECLARATION

This is to certify that the work presented in the thesis entitled "**The analytical modeling and simulation of gate material and channel engineering of DG Strained-Si MOSFET with interface charges**" is a bonafide work done by me under the supervision of **Prof. N. Bheema Rao**, Professor, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

Suddapalli Subba Rao

(Roll No: 717028)

Date: .....

**DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**TELANGANA STATE-506004, INDIA**

## **CERTIFICATE**

This is to certify that the thesis entitled "**The analytical modeling and simulation of gate material and channel engineering of DG Strained-Si MOSFET with interface charges**", which is being submitted by **Mr. Suddapalli Subba Rao (Roll No: 717028)**, in partial fulfillment for the award of the degree of Doctor of Philosophy to the Department of Electronics and Communication Engineering of National Institute of Technology Warangal, is a record of bonafide research work carried out by him under my supervision and has not been submitted elsewhere for any degree.

Prof. N. Bheema Rao

(Supervisor)

Professor

Department of E.C.E.

N.I.T. Warangal

Warangal - 506004, India

## ACKNOWLEDGEMENTS

First of all, I would like to express my sincere gratitude to my supervisor Prof. N. Bheema Rao for his guidance and support. His extreme energy, encouragement, and immense knowledge that resolved all my queries have always been a constant source of motivation throughout my Ph.D. study and research. His passion and enthusiasm for teaching, sharing his knowledge and motivating students have not only inspired me, but has also made every individual an ardent academic disciple who has been taught by him. Being student-responsive and an effective mentor, his guidance helped me throughout thick and thin periods of my research, for which I am honestly indebted and thankful throughout my career and lifetime.

I am also grateful to Prof. L. Anjaneyulu, Head of the department, Department of Electronics and Communication Engineering, NIT Warangal for his valuable suggestions and support that he shared during my research tenure.

Besides my supervisor, I take this privilege to thank Doctoral Scrutiny Committee members, Dr. T.V.K. Hanumantha Rao, Associate professor, Department of Electronics and Communication Engineering, NIT Warangal, Dr. P. Sree Hari Rao, Associate Professor, Department of Electronics and Communication Engineering, NIT Warangal and Prof. N. Vishwanathan, Professor, Department of Electrical Engineering, NIT Warangal for their continuous support, suggestions and advices during my research period whenever required.

It is my pleasure to show my indebtedness to my co-scholars at NIT like R Shashank, T Sunil Kumar, M A Mushahhid Majeed, D Srikar, P Raveendra, Ch Vijaya Durga, and B J Rani Deepika for their help during the course of this work.

I find no words inadequate to express any form of acknowledgment to my father, mother, wife, daughter, brother and sister for their love, support and patience for making my dream come true.

Finally, I thank God, for filling me every day with new hopes, strength, purpose and faith.

# ABSTRACT

Non-conventional field effect transistor have captivated researchers' attention for upcoming ULSI applications as channel length of MOSFETs reached physical limit. Out of the nonconventional MOS devices that are presently being followed for the next generation ULSI, double gate (DG) strained-Silicon (s-Si) MOSFET is an important contender as the DG s-Si MOSFETs have a few unique characteristics, such as improved higher driving capability, low subthreshold current, and adaptability with CMOS technology. However, due to the high electric field in the nano-scaled device, interface charges are introduced at s-Si/SiO<sub>2</sub> interface. As a result, the electrical characteristics of the DG s-Si MOSFETs deteriorate due to the hot carrier effects (HCEs). Moreover, channel potential, position of minimum threshold voltage, channel potential, and subthreshold characteristics of the DG s-Si MOSFET are altered because of interface traps at s-Si/SiO<sub>2</sub> interface. To reduce this HCEs problem, the gate material engineering, such as dual metal gate and triple metal gate structures are incorporated into the DG s-Si MOSFET. Moreover, the lateral electric field at drain side decreases, thereby decreasing the interface charges at s-Si/SiO<sub>2</sub> interface. To further reduce HCEs, the channel engineering is employed into the DG s-Si MOSFET. The main objective of the thesis is to introduce with the analytical simulation and modeling of the graded channel dual material (GC-DM) DG s-Si MOSFET with interface charges with the help of the two-dimensional Poisson's equation. Moreover, analytical models are developed with the help of center potential based natural length to evaluate the exact short-channel characteristics of the MOSFET.

In this thesis, the analog/RF performance of GC-DMDG s-Si MOSFET with interface charges is presented. Besides, the analog/RF figures of merit of the proposed s-Si GC-DMDG MOSFET, including the intrinsic voltage gain, transconductance generation factor, early voltage, unity-current gain frequency, transconductance frequency product, gain $\times$ frequency product, and gain transconductance frequency product, are evaluated for different values of device parameters. Also, the analog/RF performance of the proposed GCGS-TMDG s-Si MOSFET is further improved by employing the gate stack with high-k dielectric material and triple material gate engineering. Furthermore, variability analysis of GC-DMDG s-Si MOSFET with fixed charges is thoroughly analyzed. By varying the different device parameters, the variability analysis of the proposed GCDM-DG s-Si MOSFET is performed with respect to variations in threshold voltage and drain current while considering the line edge roughness and fluctuations in random dopant, contact resistance, and oxide thickness. And also, the performance of CMOS inverter using GC-DMDG s-Si MOSFET is evaluated for different device parameters. It is investigated that the proposed GC-DMDG s-Si MOSFET has better noise margin than GC-DG

s-Si MOSFET. The proposed analytical models are verified against numerical results obtained from TCAD simulations obtained from Sentaurus, which is a device simulator from Synopsys.

# Contents

|                                            |              |

|--------------------------------------------|--------------|

| <b>Approval Sheet</b>                      | <b>i</b>     |

| <b>Certificate</b>                         | <b>iii</b>   |

| <b>Acknowledgements</b>                    | <b>iv</b>    |

| <b>Abstract</b>                            | <b>v</b>     |

| <b>List of Figures</b>                     | <b>x</b>     |

| <b>List of Tables</b>                      | <b>xvi</b>   |

| <b>List of Abbreviations</b>               | <b>xvii</b>  |

| <b>List of Symbols</b>                     | <b>xviii</b> |

| <b>1 Introduction</b>                      | <b>1</b>     |

| 1.1 Overview . . . . .                     | 1            |

| 1.2 History of Transistors . . . . .       | 2            |

| 1.3 MOSFET Scaling . . . . .               | 3            |

| 1.4 CMOS boosters . . . . .                | 4            |

| 1.4.1 Strained-silicon material . . . . .  | 4            |

| 1.4.2 Gate material engineering . . . . .  | 5            |

| 1.4.3 Graded channel engineering . . . . . | 5            |

| 1.4.4 High-k insulating material . . . . . | 5            |

| 1.4.5 Non-conventional MOSFETs . . . . .   | 6            |

| 1.5 Motivation . . . . .                   | 6            |

| 1.6 Problem statement . . . . .            | 7            |

| 1.7 Objectives . . . . .                   | 7            |

| 1.8 Organization of Work . . . . .         | 7            |

|                                                                                                                           |           |

|---------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>2 Literature Survey</b>                                                                                                | <b>8</b>  |

| 2.1 Introduction . . . . .                                                                                                | 8         |

| 2.2 Review on strained-silicon MOSFETs . . . . .                                                                          | 9         |

| 2.2.1 Review on s-Si MOSFETs with interface charges . . . . .                                                             | 10        |

| 2.2.2 Review on gate stack and gate engineering of s-Si MOSFETs . . . . .                                                 | 11        |

| 2.2.3 Review on channel engineering of s-Si MOSFETs . . . . .                                                             | 12        |

| 2.3 Review on DG MOSFETs . . . . .                                                                                        | 13        |

| 2.4 Review on multiple gate MOSFETs . . . . .                                                                             | 14        |

| 2.5 Review on subthreshold characteristics models of DG s-Si MOSFETs . . . . .                                            | 15        |

| 2.5.1 Review on threshold voltage models of DG s-Si MOSFETs . . . . .                                                     | 16        |

| 2.5.2 Review on subthreshold current models of DG s-Si MOSFETs . . . . .                                                  | 16        |

| 2.5.3 Review on subthreshold swing models of DG s-Si MOSFETs . . . . .                                                    | 17        |

| 2.5.4 Review on analog/RF performance of DG s-Si MOSFETs . . . . .                                                        | 18        |

| 2.5.5 Review on variability analysis of DG s-Si MOSFETs . . . . .                                                         | 19        |

| 2.6 Summary . . . . .                                                                                                     | 20        |

| <b>3 Analytical simulation and modeling of subthreshold characteristics of GC-DMDG s-Si MOSFET with interface charges</b> | <b>21</b> |

| 3.1 Introduction . . . . .                                                                                                | 21        |

| 3.2 Device structure and simulation setup . . . . .                                                                       | 22        |

| 3.3 Analytical modeling . . . . .                                                                                         | 25        |

| 3.3.1 Effect of strain on silicon energy band and flat-band voltage . . . . .                                             | 25        |

| 3.3.2 Center potential modeling . . . . .                                                                                 | 26        |

| 3.3.3 Electric field modeling . . . . .                                                                                   | 28        |

| 3.3.4 Threshold voltage modeling . . . . .                                                                                | 28        |

| 3.3.5 Subthreshold current modeling . . . . .                                                                             | 29        |

| 3.3.6 Modeling of effective conductive path . . . . .                                                                     | 31        |

| 3.3.7 Subthreshold swing modeling . . . . .                                                                               | 32        |

| 3.4 Result Analysis . . . . .                                                                                             | 33        |

|                                                                                                           |            |

|-----------------------------------------------------------------------------------------------------------|------------|

| 3.5 Conclusion . . . . .                                                                                  | 46         |

| <b>4 Analog/RF performance of GC-DMDG and GCGS-TMDG s-Si MOSFETs with interface charges</b>               | <b>48</b>  |

| 4.1 Introduction . . . . .                                                                                | 48         |

| 4.2 Analog/RF performance of GC-DMDG s-Si MOSFET with interface charges .                                 | 49         |

| 4.2.1 Results and discussion . . . . .                                                                    | 49         |

| 4.3 Analog/RF performance of GCGS-TMDG s-Si MOSFET with interface charges.                                | 61         |

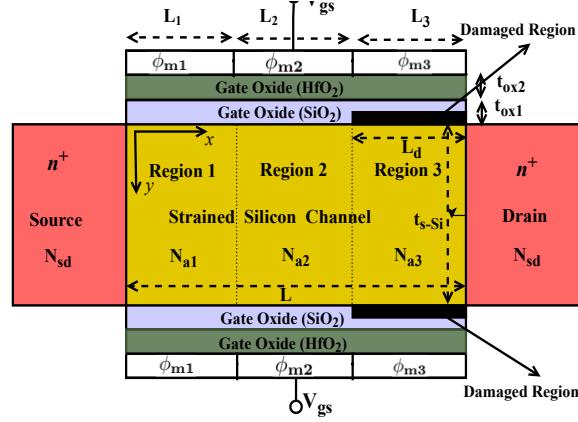

| 4.3.1 Proposed device structure . . . . .                                                                 | 62         |

| 4.3.2 Results and discussion . . . . .                                                                    | 63         |

| 4.4 Summary and Conclusions . . . . .                                                                     | 75         |

| <b>5 Variability analysis of GC-DMDG s-Si MOSFET with interface charges and CMOS inverter performance</b> | <b>76</b>  |

| 5.1 Introduction . . . . .                                                                                | 76         |

| 5.2 Variability analysis of GC-DMDG s-Si MOSFET with interface charges . .                                | 78         |

| 5.2.1 Result analysis . . . . .                                                                           | 78         |

| 5.3 Performance evaluation of CMOS inverter using GC-DMDG s-Si MOSFET with interface charges . . . . .    | 85         |

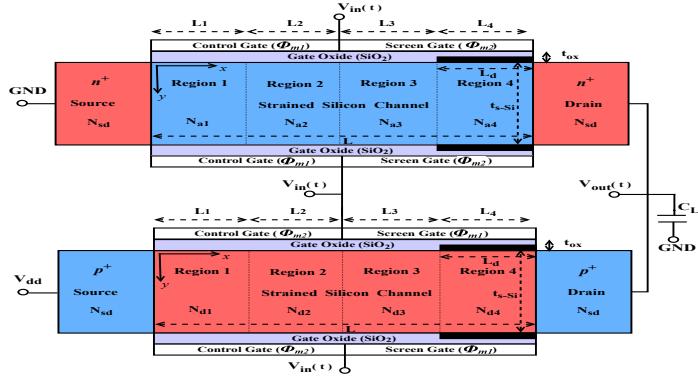

| 5.3.1 Proposed CMOS Inverter diagram . . . . .                                                            | 85         |

| 5.3.2 Result analysis . . . . .                                                                           | 86         |

| 5.4 Summary and Conclusions . . . . .                                                                     | 90         |

| <b>6 Conclusions and Future Scope</b>                                                                     | <b>91</b>  |

| 6.1 Conclusions . . . . .                                                                                 | 91         |

| 6.2 Future Scope . . . . .                                                                                | 92         |

| <b>References</b>                                                                                         | <b>94</b>  |

| <b>List of Publications</b>                                                                               | <b>105</b> |

# List of Figures

|      |                                                                                                                                                                                                                                      |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | A brief time line of the important events in the advancement of Semiconductor technology . . . . .                                                                                                                                   | 2  |

| 1.2  | Lattice structure of relaxed silicon, relaxed SiGe, and s-Si on relaxed SiGe . . . . .                                                                                                                                               | 4  |

| 1.3  | 2-D diagram of DMG structure of MOSFET. . . . .                                                                                                                                                                                      | 5  |

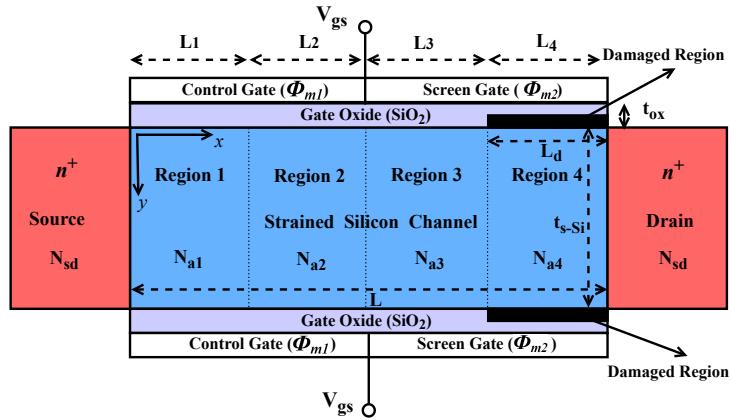

| 3.1  | Structure of symmetrical GC-DMDG s-Si MOSFET with interface charges. . . . .                                                                                                                                                         | 22 |

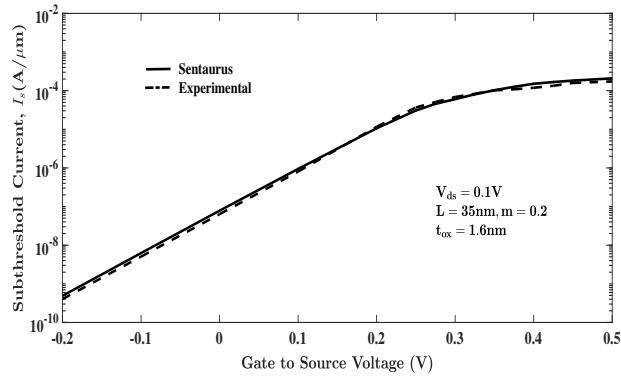

| 3.2  | Calibration of s-Si MOSFET against experimental data of [93]. . . . .                                                                                                                                                                | 22 |

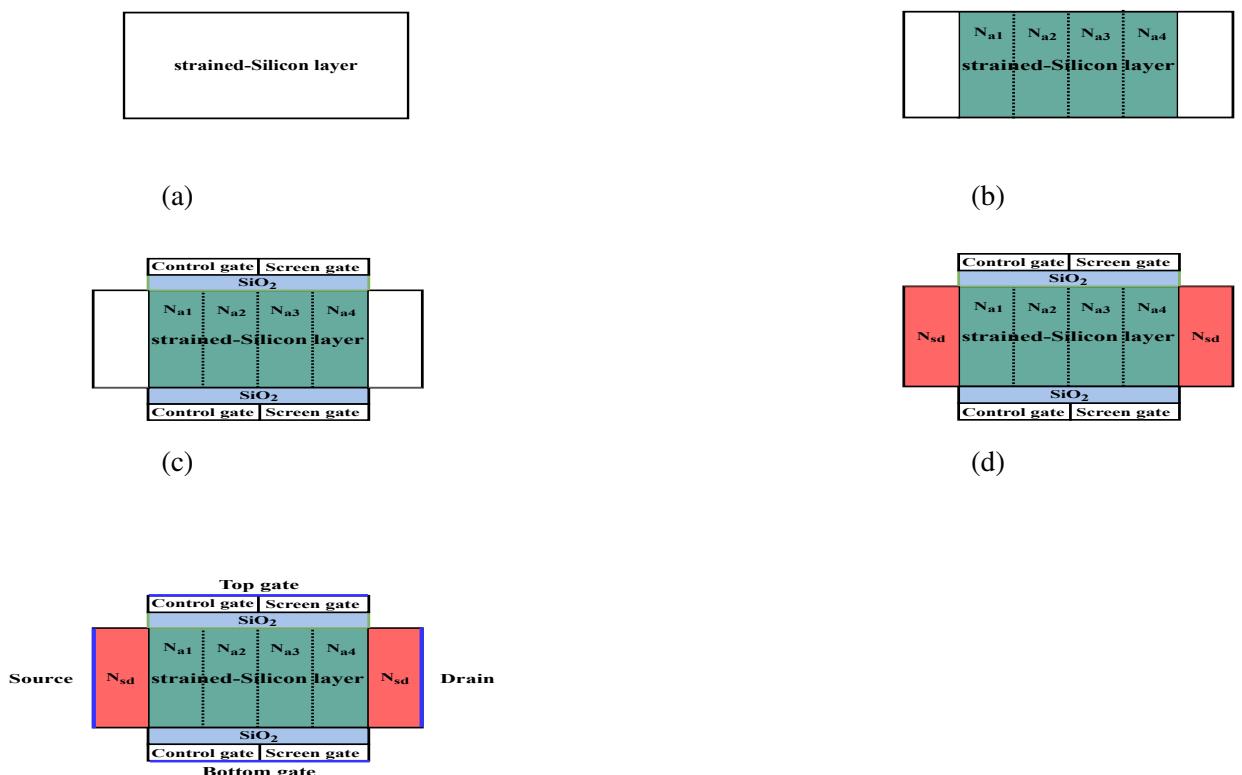

| 3.3  | Fabrication flow of the proposed s-Si GC-DMDG MOSFET, a. strained-Si layer, b. Graded channel ion implantation, c. Top and bottom gate stack deposition, d. Source/Drain ion implantation, and e. Metal contacts formation . . . . . | 23 |

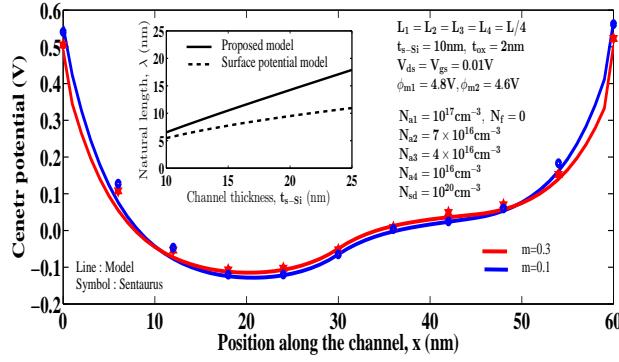

| 3.4  | Variation of center potential of the GC-DMDG s-Si MOSFET with $m= 0.1$ and $0.3$ for $L= 60$ nm. Inset: Variation of natural length of GC-DMDG s-Si MOSFET for different values of s-Si thickness. . . . .                           | 33 |

| 3.5  | Variation of center and surface potentials of GC-DMDG and GC-DG s-Si MOSFETs for $L= 20$ nm, $L= 60$ nm and $L= 100$ nm. . . . .                                                                                                     | 34 |

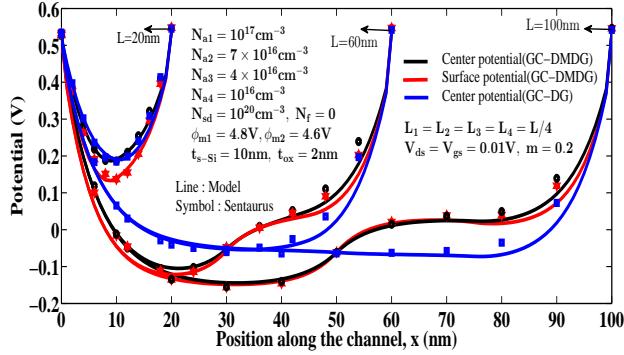

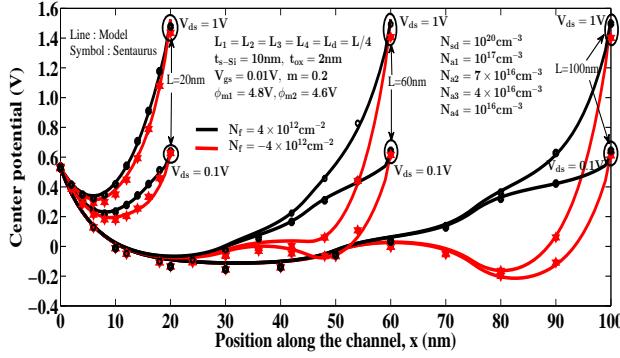

| 3.6  | Variation of center potential of the GC-DMDG s-Si MOSFET with damaged length, $L_d = L/4$ for different channel lengths. . . . .                                                                                                     | 35 |

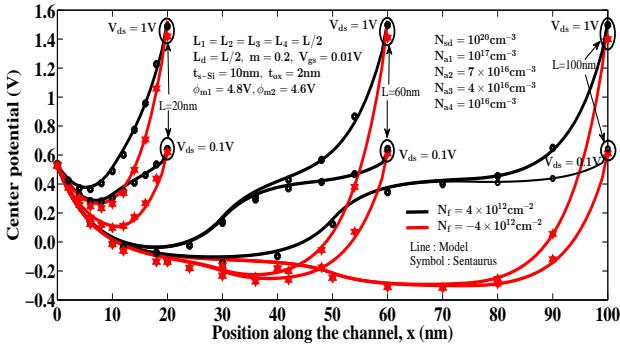

| 3.7  | Variation of center potential of the GC-DMDG s-Si MOSFET with damaged length, $L_d = L/2$ for different channel lengths. . . . .                                                                                                     | 35 |

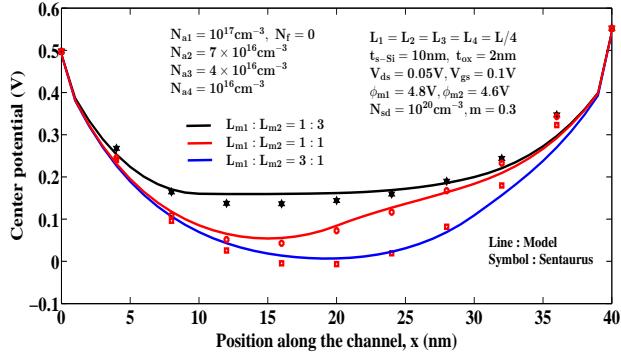

| 3.8  | Variation of center potential of the GC-DMDG s-Si MOSFET for different gate length ratios of control/screen. . . . .                                                                                                                 | 36 |

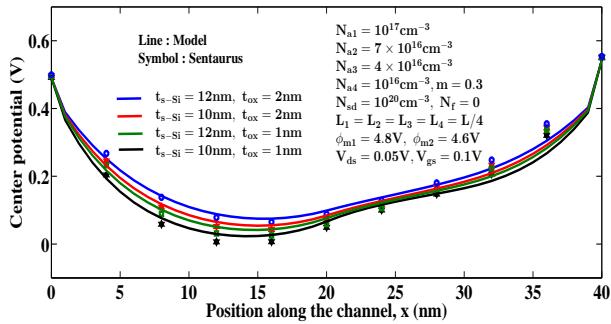

| 3.9  | Variation of center potential of the GC-DMDG s-Si MOSFET for different values of $t_{ox}$ and $t_{s-Si}$ . . . . .                                                                                                                   | 36 |

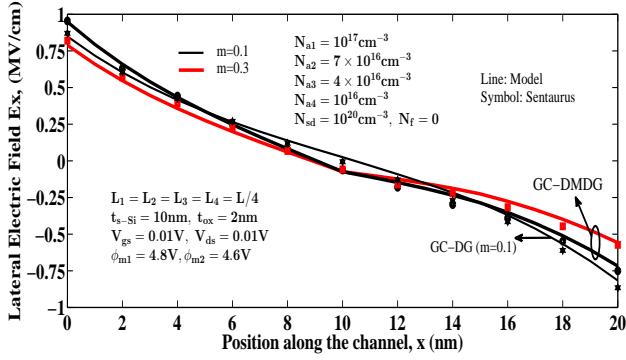

| 3.10 | Variation of lateral electric field along the channel length of GC-DMDG and GC-DG s-Si MOSFETs with $m= 0.1$ and $0.3$ . . . . .                                                                                                     | 37 |

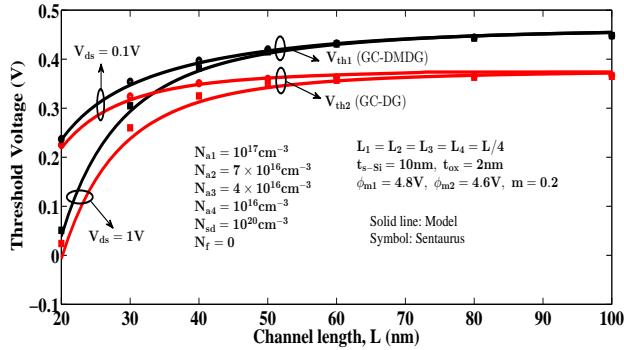

| 3.11 | Variation of threshold voltage along channel length of the GC-DMDG and GC-DG s-Si MOSFETs for different values of $V_{ds}$ . . . . .                                                                                                 | 38 |

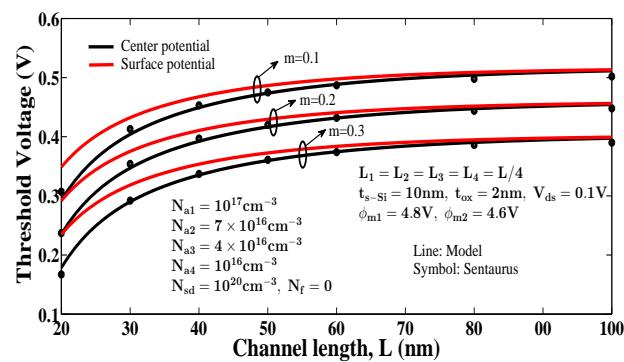

| 3.12 | Variation of $\psi_{cr}$ and $\psi_{sr}$ based threshold voltage along channel length of the GC-DMDG s-Si MOSFET for different Ge mole fractions. . . . .                                                                            | 38 |

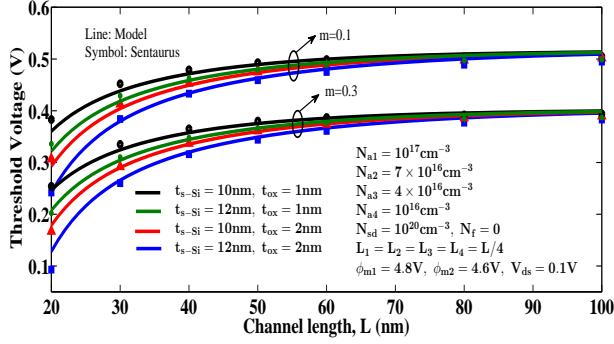

| 3.13 | Variation of threshold voltage along channel length of the GC-DMDG s-Si MOSFET for different values of $t_{ox}$ and $t_{s-Si}$ . . . . .                                                                                             | 39 |

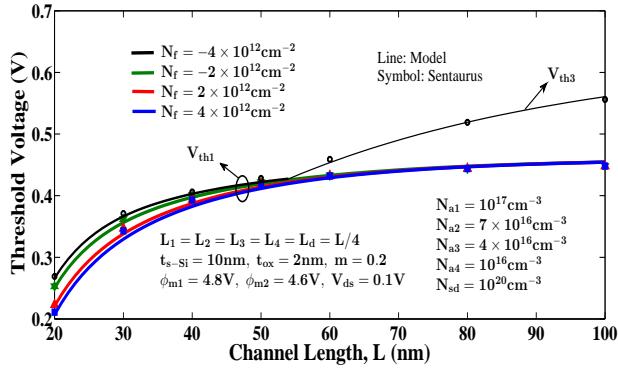

| 3.14 | Variation of threshold voltage along channel length of the GC-DMDG s-Si MOSFET for interface charge density with $L_d = L/4$ . . . . .                                                                                               | 39 |

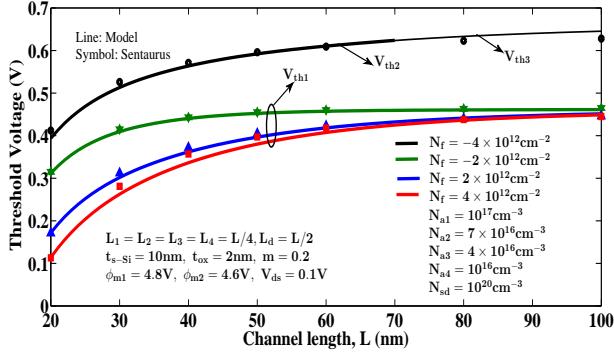

|                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 Variation of threshold voltage along channel length of the GC-DMDG s-Si MOSFET for interface charge density with $L_d = L/2$ . . . . .               | 40 |

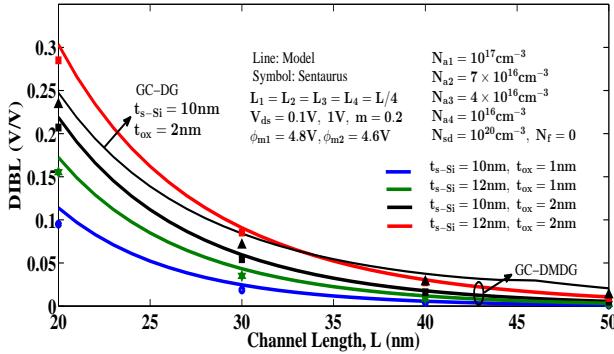

| 3.16 Variation of DIBL along channel length of GC-DMDG and GC-DG s-Si MOSFETs with $m= 0.2$ . . . . .                                                     | 40 |

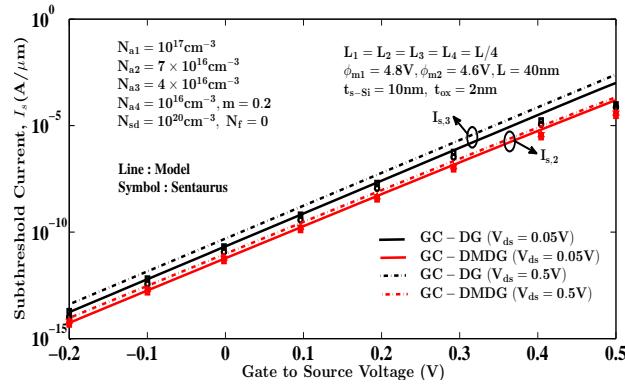

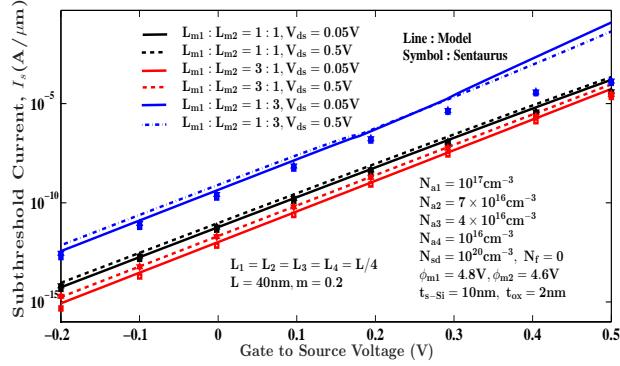

| 3.17 Variation of SC of GC-DG and GC-DMDG s-Si devices with $L= 40$ nm for different values of $V_{ds}$ . . . . .                                         | 41 |

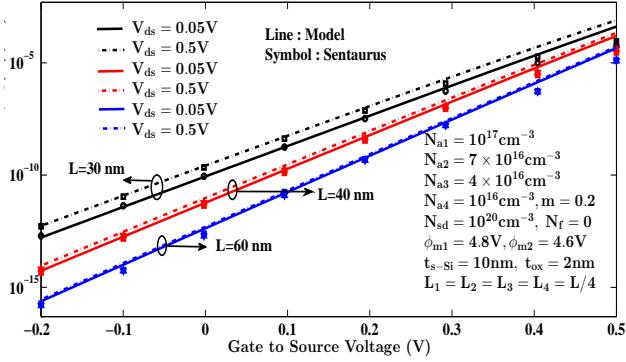

| 3.18 Variation of $V_{ds}$ on subthreshold current of the GC-DMDG s-Si MOSFET for different channel lengths. . . . .                                      | 42 |

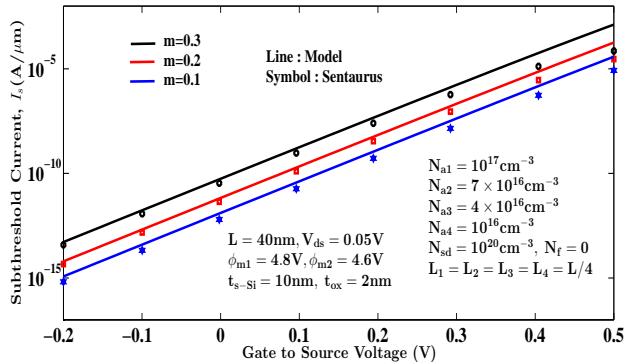

| 3.19 Variation of on SC of the GC-DMDG s-Si MOSFET with $L= 40$ nm for different Ge mole fractions. . . . .                                               | 42 |

| 3.20 Variation of $V_{ds}$ on subthreshold current of the GC-DMDG s-Si MOSFET with $L= 40$ nm for different gate length ratios of control/screen. . . . . | 43 |

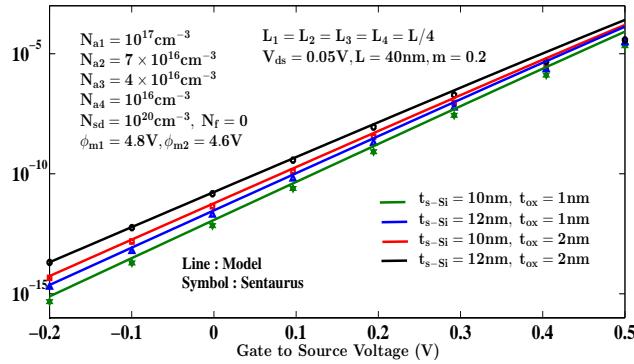

| 3.21 Variation of subthreshold current of GC-DMDG s-Si MOSFET with $L= 40$ nm for different $t_{ox}$ and $t_{si}$ values. . . . .                         | 43 |

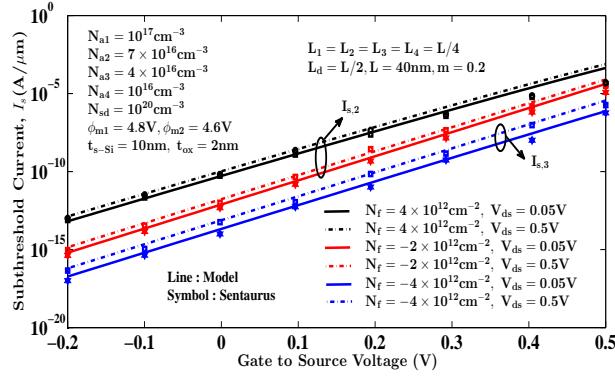

| 3.22 Variation of fixed charges on SC of the GC-DMDG s-Si device with $L= 40$ nm for $V_{ds}= 0.05$ and $0.5$ V. . . . .                                  | 44 |

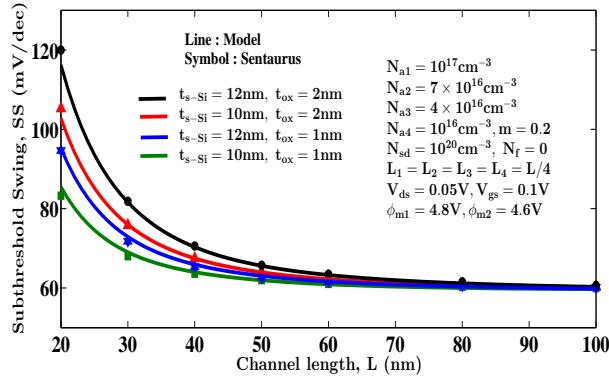

| 3.23 Variation of subthreshold swing of GC-DMDG s-Si MOSFET for different $t_{ox}$ and $t_{si}$ values. . . . .                                           | 44 |

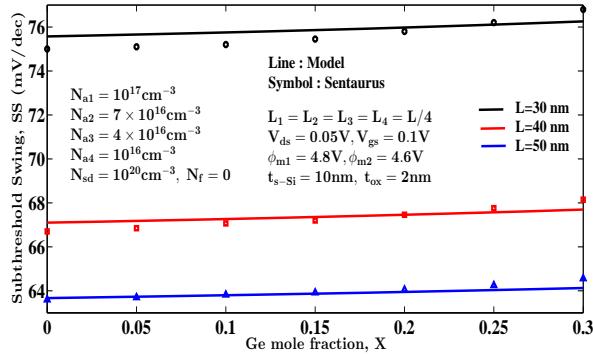

| 3.24 Variation of subthreshold swing of the GC-DMDG s-Si MOSFET for different Ge mole fractions. . . . .                                                  | 45 |

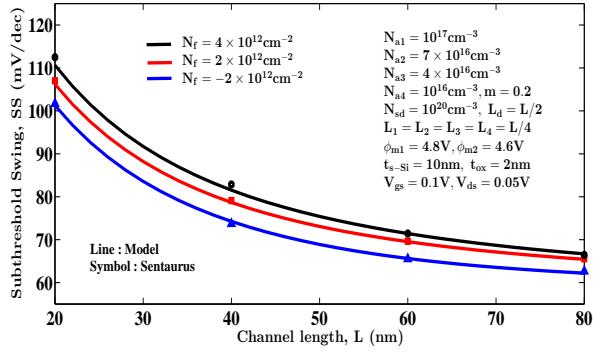

| 3.25 Variation of charge density on subthreshold swing of the GC-DMDG s-Si MOSFET with damaged length, $L_d = L/2$ . . . . .                              | 46 |

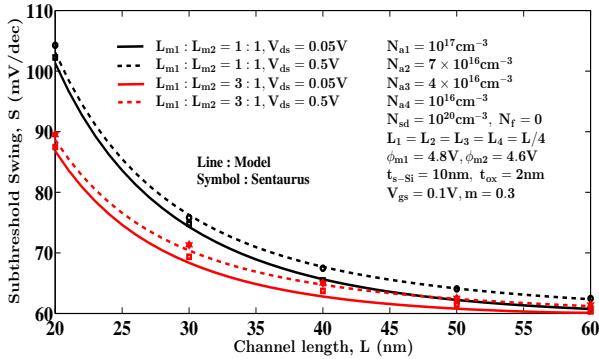

| 3.26 Variation of $V_{ds}$ on SS of the GC-DMDG s-Si MOSFET for different gate length ratios of control/screen. . . . .                                   | 46 |

| <br>                                                                                                                                                      |    |

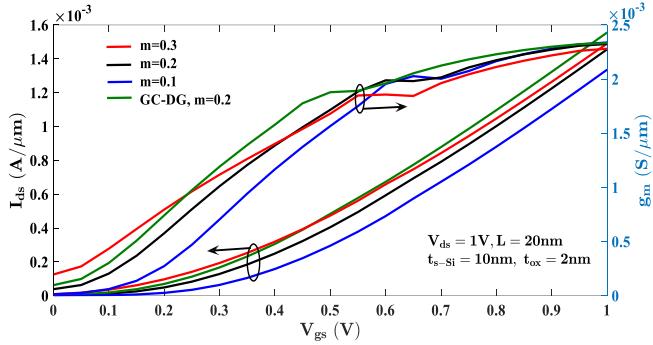

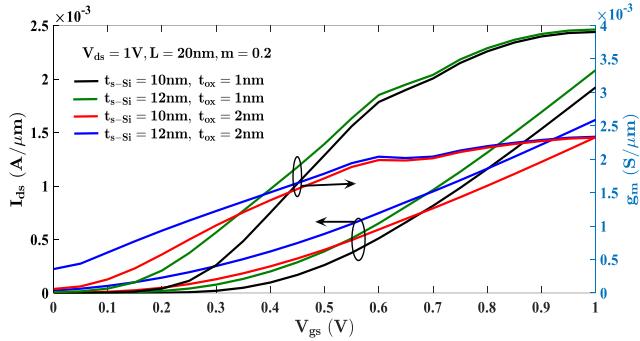

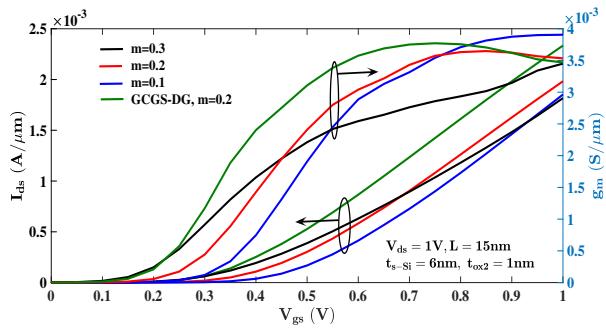

| 4.1 Effect of strain on transfer characteristics and $g_m$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                                                | 50 |

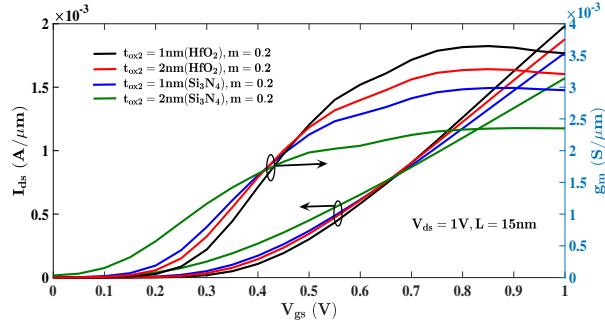

| 4.2 Effects of $t_{ox}$ and $t_{s-Si}$ on transfer characteristics and $g_m$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                              | 50 |

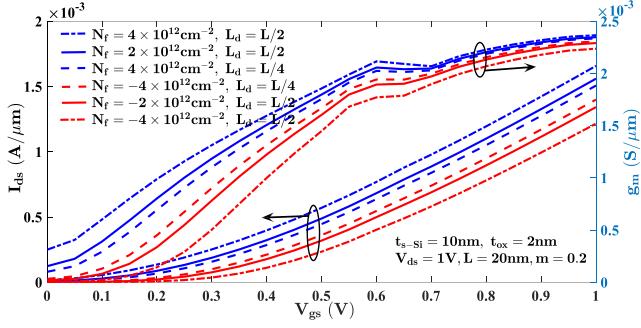

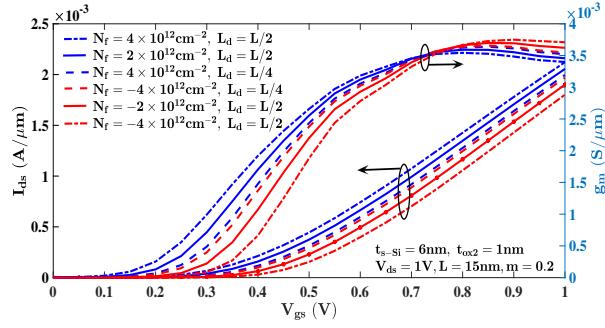

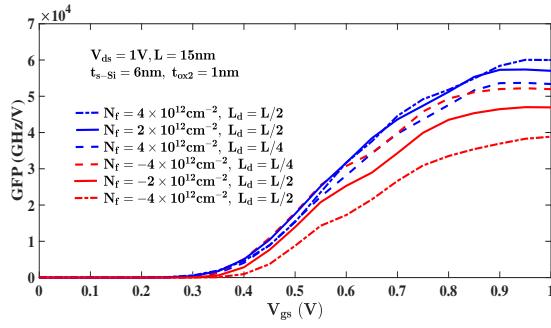

| 4.3 Effect of $N_f$ with $L_d$ on transfer characteristics and $g_m$ of GC-DMDG s-Si MOSFET for $L= 20$ nm. . . . .                                       | 51 |

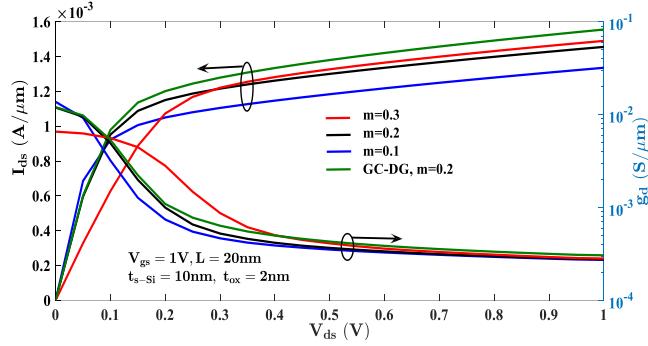

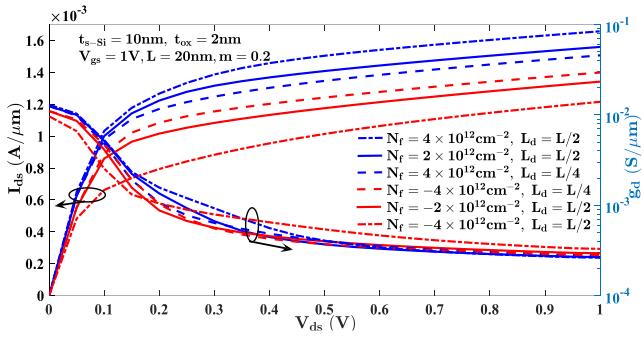

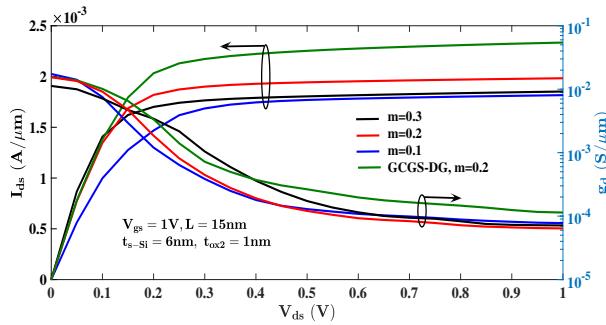

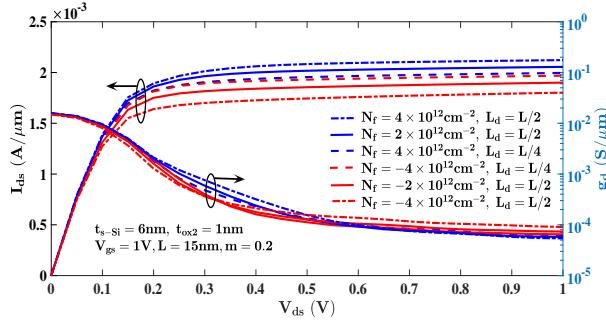

| 4.4 Effect of strain on drain characteristics and $g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                                                   | 51 |

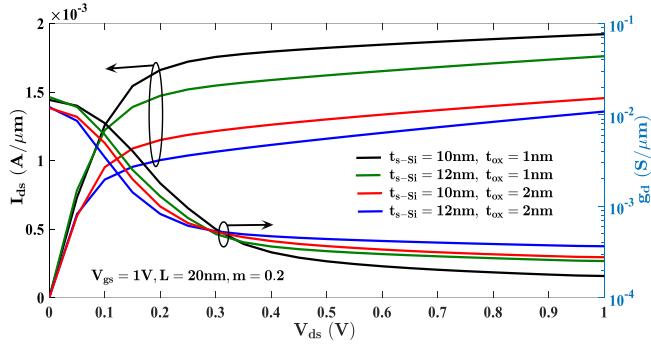

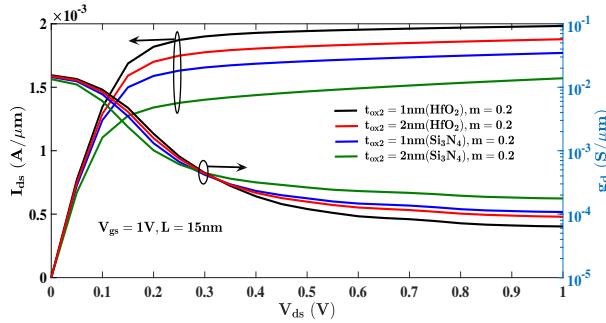

| 4.5 Effects of $t_{ox}$ and $t_{s-Si}$ on drain characteristics and $g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                                 | 52 |

| 4.6 Effect of interface charge density with $L_d$ on drain characteristics and $g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                      | 52 |

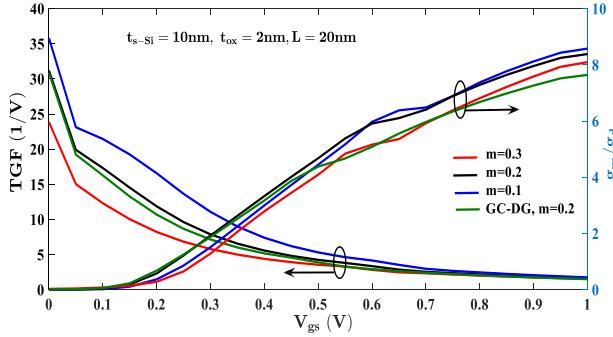

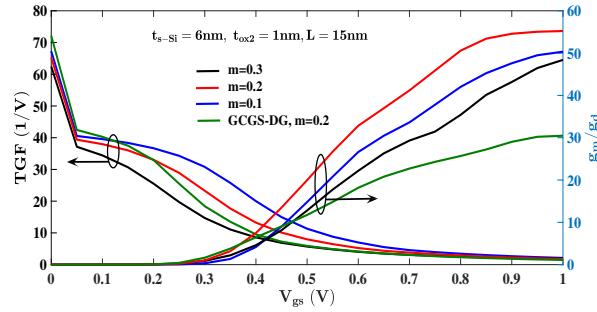

| 4.7 Effect of strain on TGF and $g_m/g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm.                                                                         | 53 |

|      |                                                                                                                            |    |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

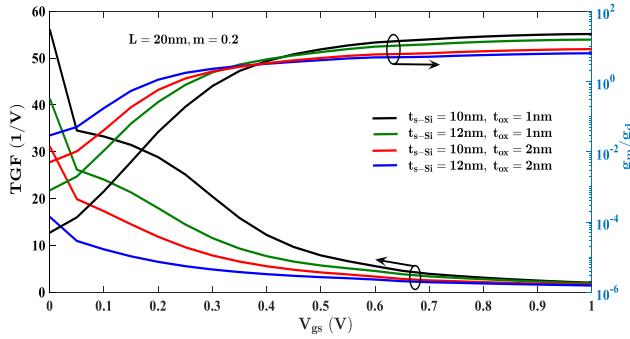

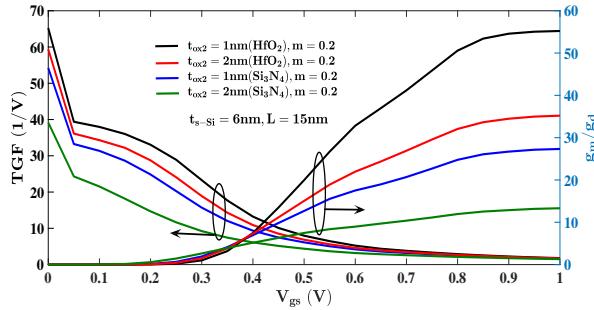

| 4.8  | Effects of $t_{ox}$ and $t_{s-Si}$ on TGF and $g_m/g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                    | 53 |

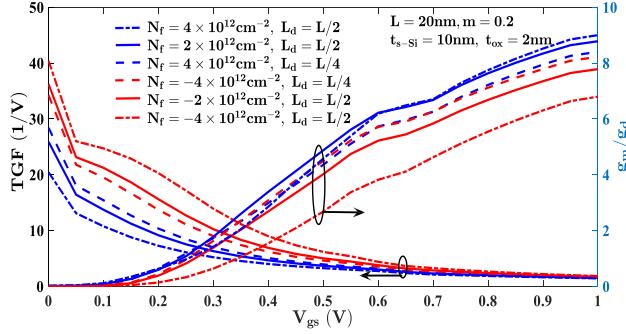

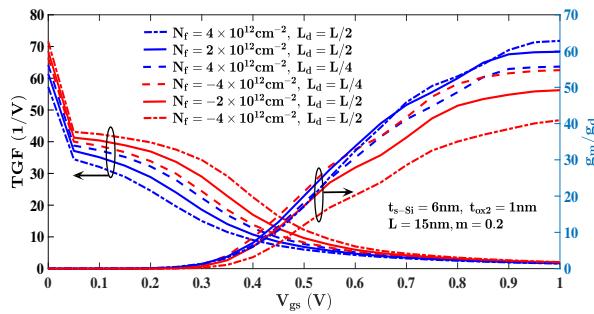

| 4.9  | Effect of interface charge density with $L_d$ on TGF and $g_m/g_d$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .         | 54 |

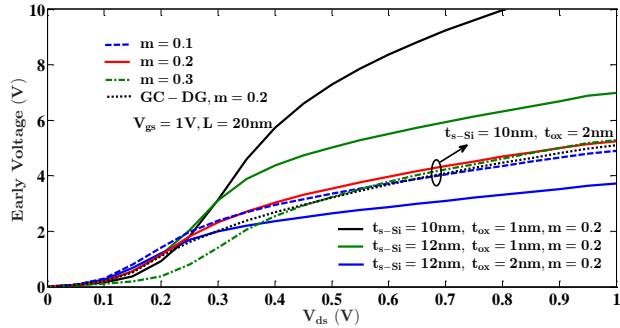

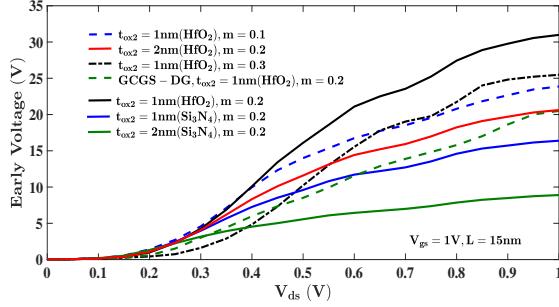

| 4.10 | Effects of strain, $t_{ox}$ , and $t_{s-Si}$ on early voltage of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .              | 54 |

| 4.11 | Effect of interface charge density with $L_d$ on early voltage of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .             | 55 |

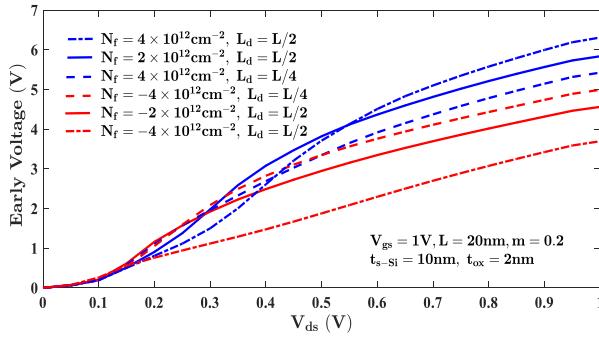

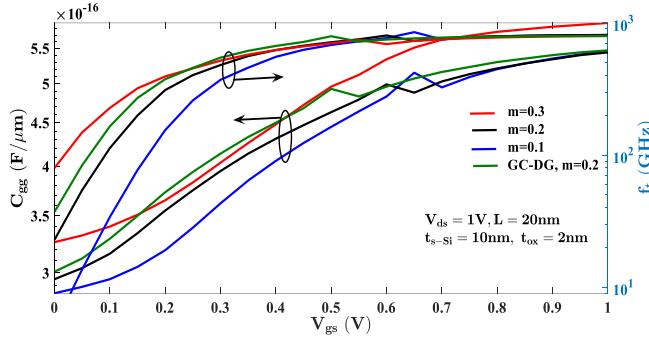

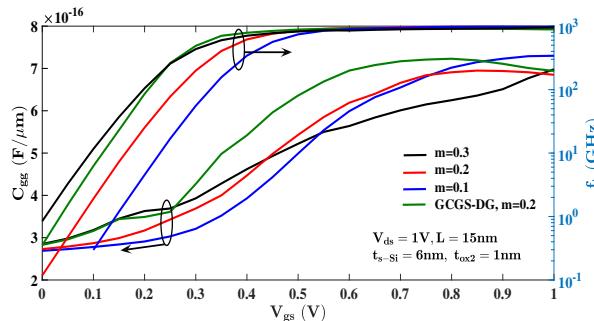

| 4.12 | Effect of strain on $C_{gg}$ and $f_t$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                                     | 55 |

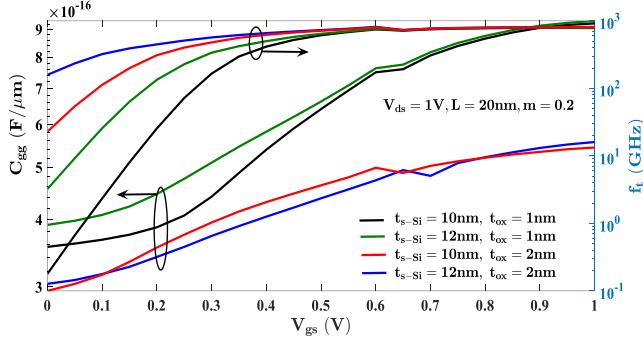

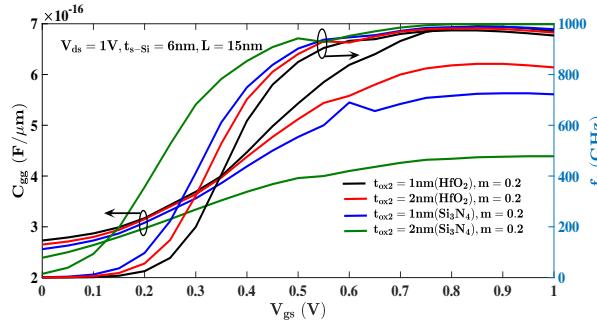

| 4.13 | Effects of $t_{ox}$ and $t_{s-Si}$ on $C_{gg}$ and $f_t$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                   | 56 |

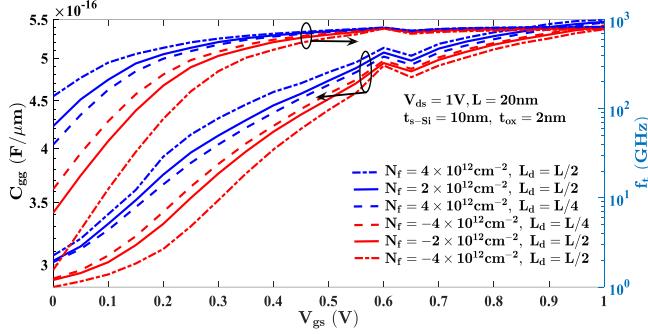

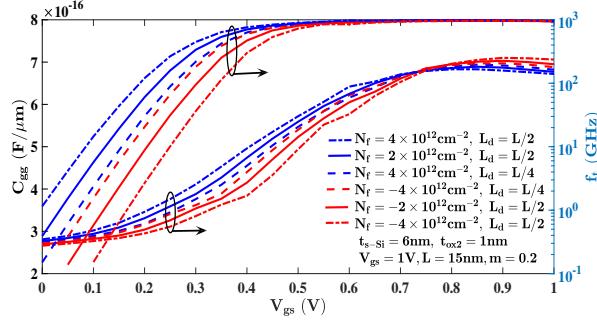

| 4.14 | Effect of interface charge density with $L_d$ on $C_{gg}$ and $f_t$ of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .        | 56 |

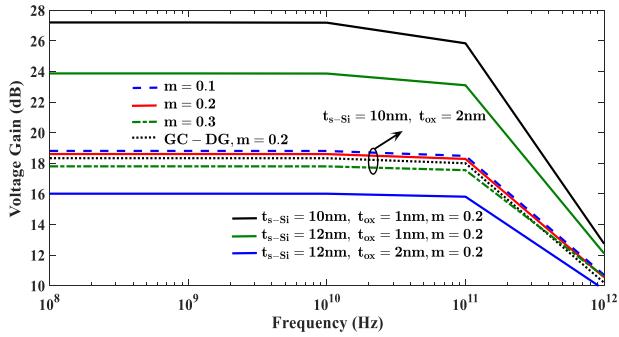

| 4.15 | Effects of strain, $t_{ox}$ and $t_{s-Si}$ on voltage gain of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                 | 57 |

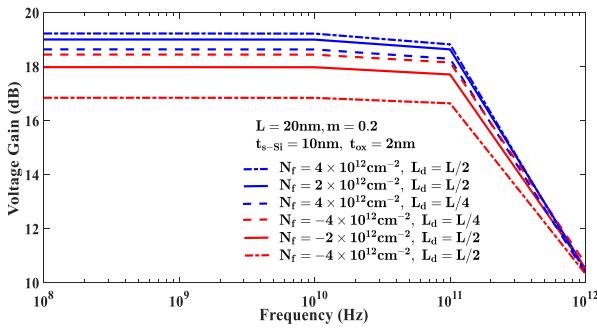

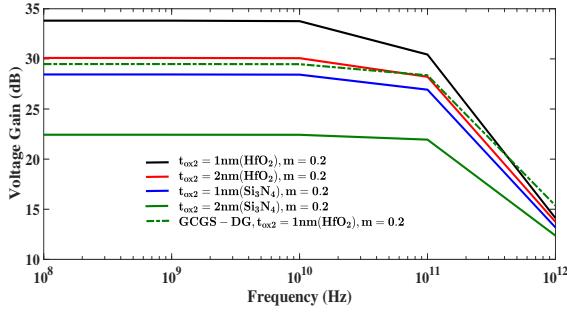

| 4.16 | Effect of interface charge density with $L_d$ on voltage gain of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .              | 57 |

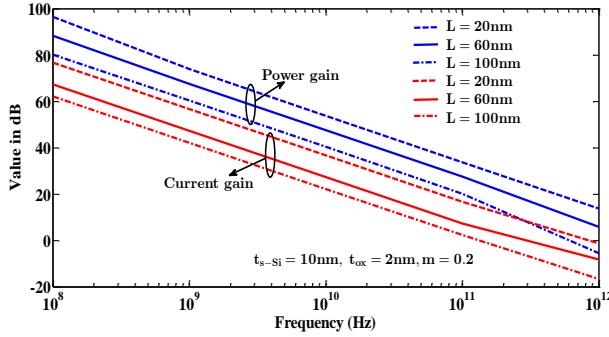

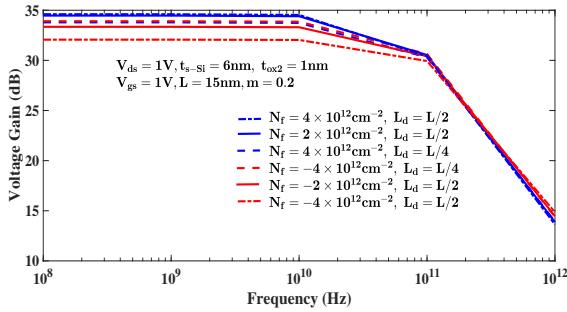

| 4.17 | Current and Power gains of GC-DMDG s-Si MOSFET for different channel lengths. . . . .                                      | 58 |

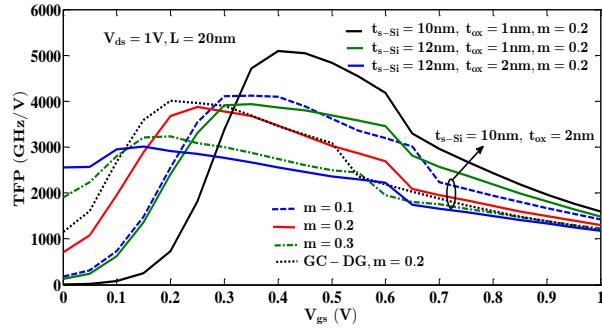

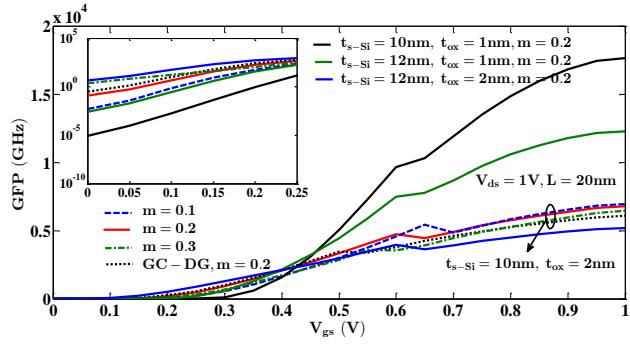

| 4.18 | Effects of strain, $t_{ox}$ , and $t_{s-Si}$ on TFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                        | 58 |

| 4.19 | Effect of interface charge density with $L_d$ on TFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                       | 59 |

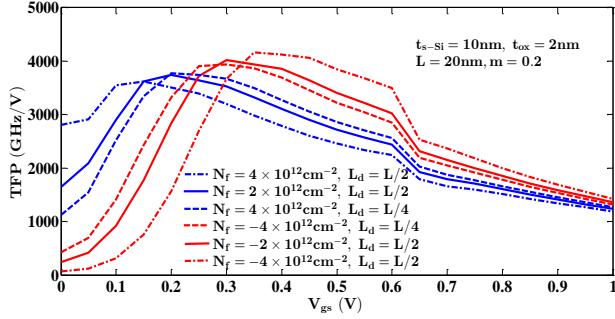

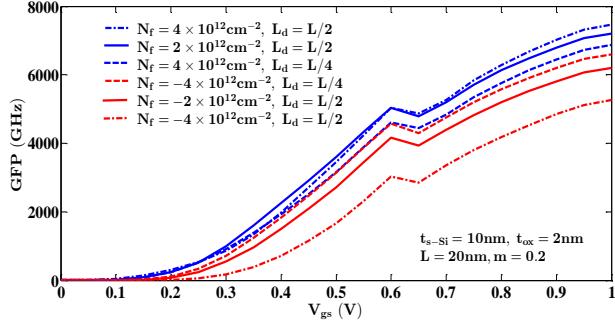

| 4.20 | Effects of strain, $t_{ox}$ , and $t_{s-Si}$ on GFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                        | 59 |

| 4.21 | Effect of interface charge density with $L_d$ on GFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                       | 60 |

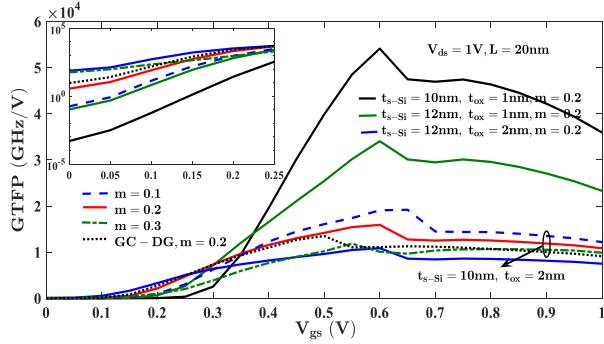

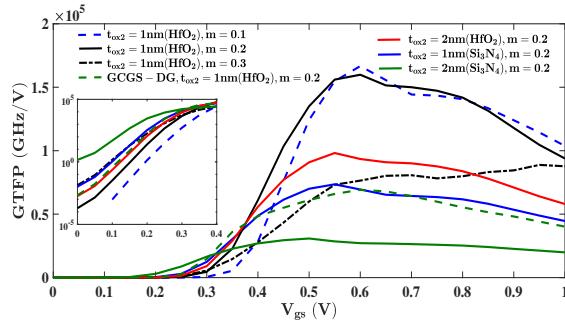

| 4.22 | Effects of strain, $t_{ox}$ , and $t_{s-Si}$ on GTFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                       | 60 |

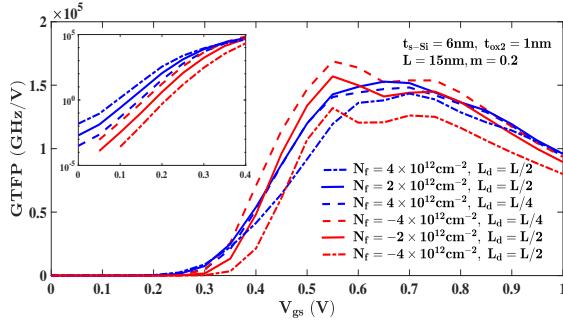

| 4.23 | Effect of interface charge density with $L_d$ on GTFP of GC-DMDG s-Si MOSFET when $L= 20$ nm. . . . .                      | 61 |

| 4.24 | Structure of symmetrical GCGS-TMDG s-Si MOSFET with interface charges. .                                                   | 62 |

| 4.25 | Variation of strain on transfer characteristics and $g_m$ of GCGS-TMDG s-Si MOSFET when $L= 15$ nm. . . . .                | 63 |

| 4.26 | Effect of $t_{ox2}$ on transfer characteristics and $g_m$ of GCGS-TMDG s-Si MOSFET for different gate stacks. . . . .      | 64 |

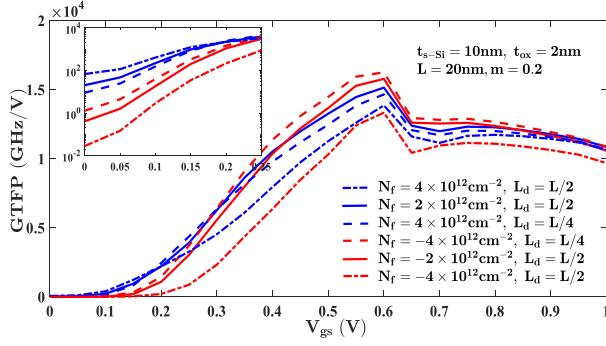

| 4.27 | Effect of $N_f$ with damaged length on transfer characteristics and $g_m$ of GCGS-TMDG s-Si MOSFET for $L= 15$ nm. . . . . | 64 |

|                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.28 Variation of strain on output characteristics and $g_d$ of GCGS-TMDG s-Si MOSFET when $L= 15$ nm. . . . .                                  | 65 |

| 4.29 Effect of $t_{ox2}$ on output characteristics and $g_d$ of GCGS-TMDG s-Si MOSFET for different gate stacks. . . . .                        | 65 |

| 4.30 Effect of $N_f$ with damaged length on output characteristics and $g_d$ of GCGS-TMDG s-Si MOSFET for $L= 15$ nm. . . . .                   | 66 |

| 4.31 Variation of strain on TGF and intrinsic gain of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                            | 66 |

| 4.32 Effect of $t_{ox2}$ on TGF and intrinsic gain of GCGS-TMDG s-Si MOSFET for different gate stacks. . . . .                                  | 67 |

| 4.33 Effect of fixed charge density for different $L_d$ on TGF and intrinsic gain of GCGS-TMDG s-Si MOSFET for $L= 15$ nm. . . . .              | 67 |

| 4.34 Effects of strain and $t_{ox2}$ on early voltage of GCGS-TMDG s-Si MOSFET when $L= 15$ nm. . . . .                                         | 68 |

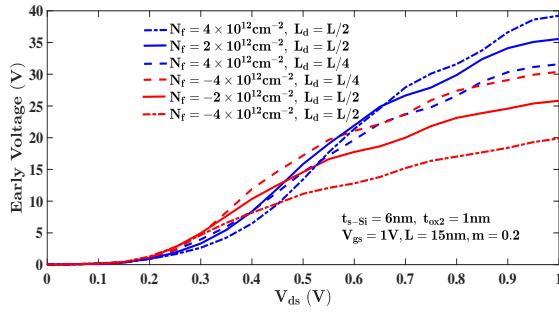

| 4.35 Effect of fixed charge density for different $L_d$ on early voltage of GCGS-TMDG s-Si device when $L= 15$ nm. . . . .                      | 68 |

| 4.36 Variation of strain on $C_{gg}$ and $f_t$ of GCGS-TMDG s-Si device when $L= 15$ nm. . . . .                                                | 68 |

| 4.37 Effect of $t_{ox2}$ on $C_{gg}$ and $f_t$ of GCGS-TMDG s-Si MOSFET for different gate stacks. . . . .                                      | 69 |

| 4.38 The effect of fixed charge density for various values of $L_d$ on the $C_{gg}$ and $f_t$ of GCGS-TMDG s-Si MOSFET when $L= 15$ nm. . . . . | 69 |

| 4.39 Effect of $t_{ox2}$ on voltage gain of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                                      | 70 |

| 4.40 Effect of fixed charge density for different $L_d$ on the voltage gain of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                   | 70 |

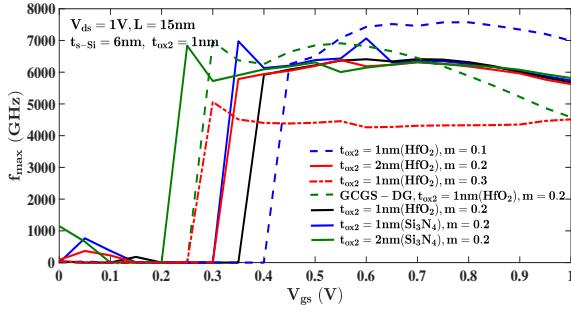

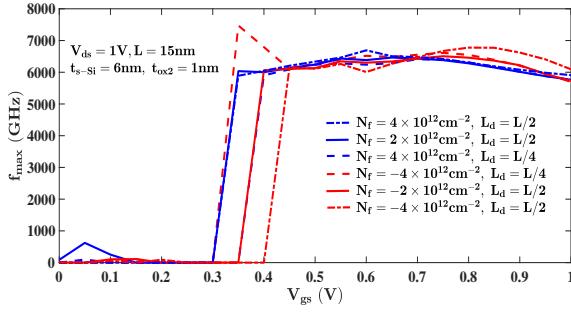

| 4.41 Effects of strain and $t_{ox2}$ on $f_{max}$ of GCGS-TMDG s-Si MOSFET for different gate stacks. . . . .                                   | 71 |

| 4.42 Effect of fixed charge density with damaged length on $f_{max}$ of GCGS-TMDG s-Si MOSFET. . . . .                                          | 71 |

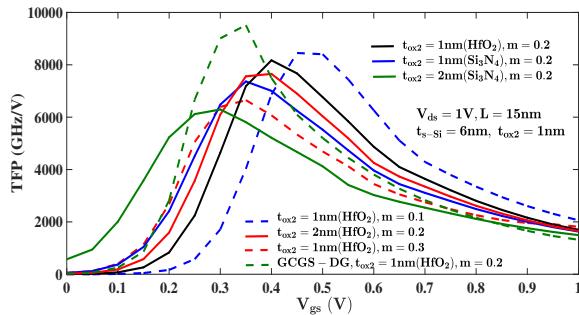

| 4.43 Effects of strain and $t_{ox2}$ on TFP of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                                   | 71 |

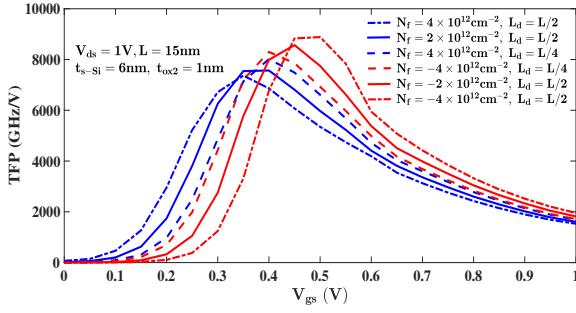

| 4.44 Effect of fixed charge density with damaged length on TFP of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                | 72 |

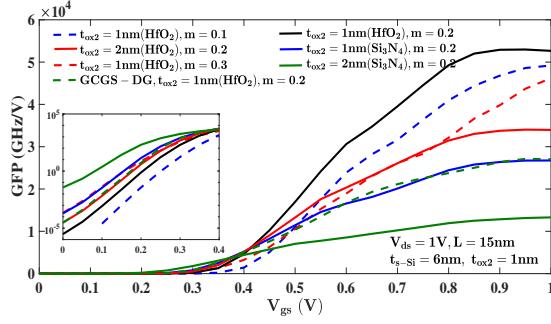

| 4.45 Effects of strain and $t_{ox2}$ on GFP of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                                   | 72 |

| 4.46 Effect of fixed charge density with damaged length on TFP of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                | 73 |

| 4.47 Effects of strain and $t_{ox2}$ on GTFP of GCGS-TMDG s-Si MOSFET with $L= 15$ nm. . . . .                                                  | 73 |

|      |                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.48 | Effect of fixed charge density with damaged length on GTFP of GCGS-TMDG s-Si MOSFET with $L = 15$ nm. . . . .                                    | 74 |

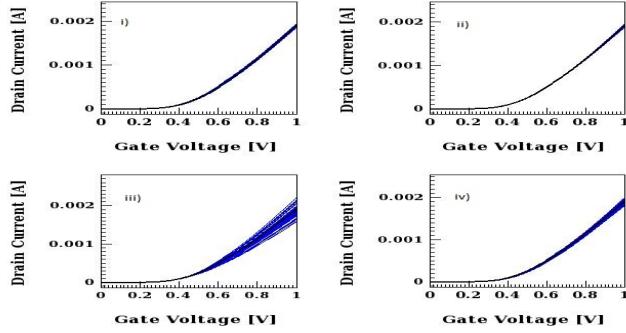

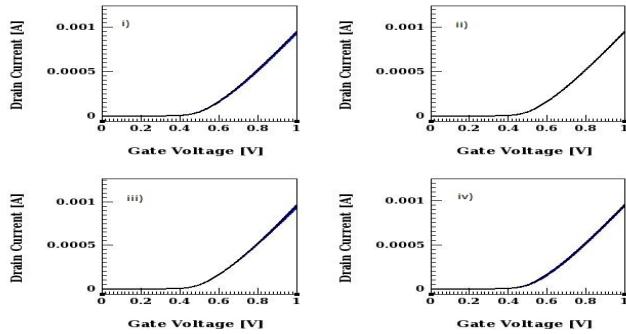

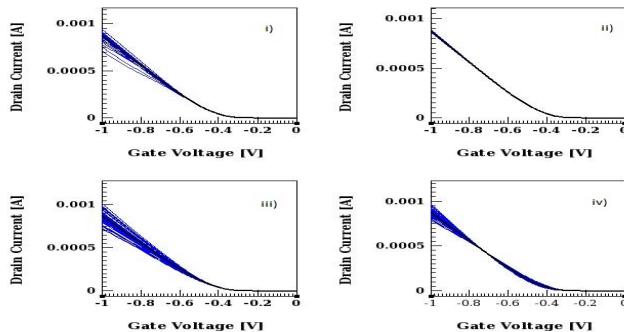

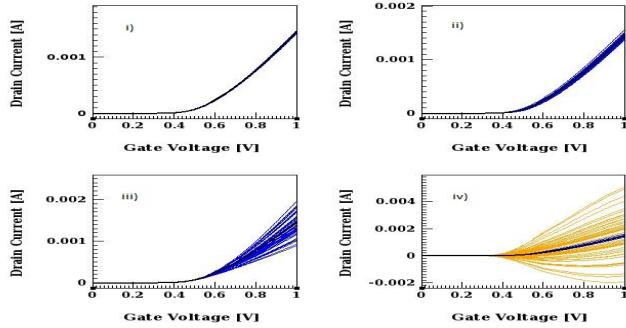

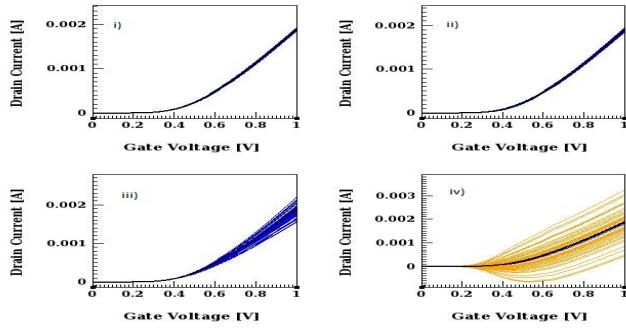

| 5.1  | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $L = 20$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .               | 78 |

| 5.2  | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $L = 40$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .               | 79 |

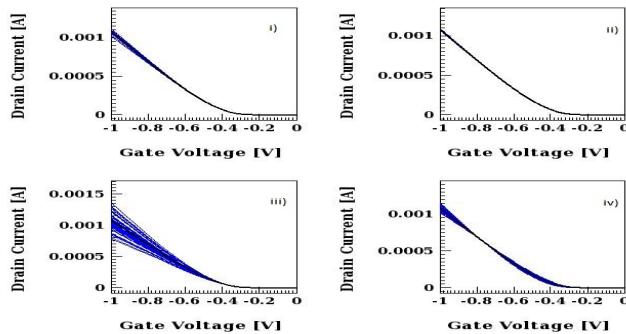

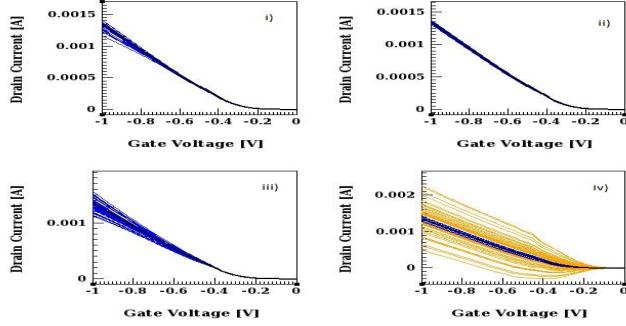

| 5.3  | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $L = 20$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .               | 79 |

| 5.4  | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $L = 40$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .               | 80 |

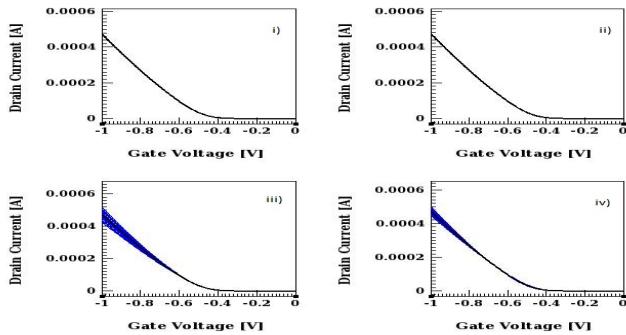

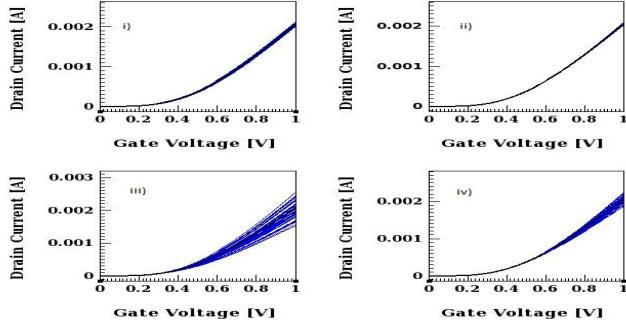

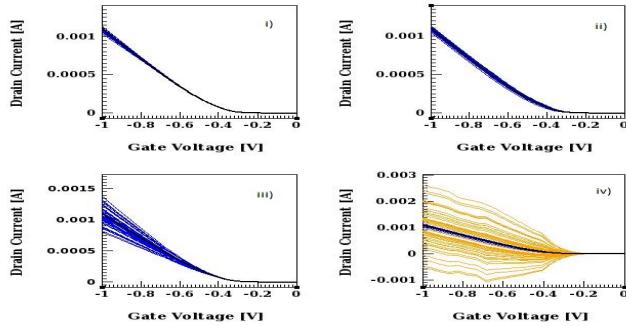

| 5.5  | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $m = 0.3$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .                 | 81 |

| 5.6  | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $m = 0.3$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .                 | 81 |

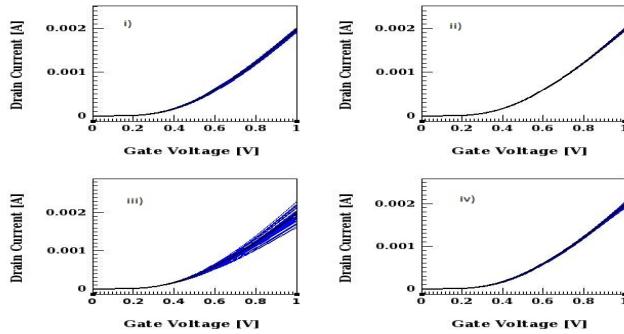

| 5.7  | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $t_{ox} = 2$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .           | 82 |

| 5.8  | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $t_{ox} = 2$ nm due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .           | 82 |

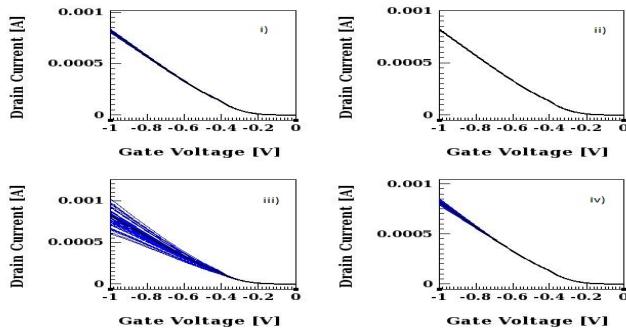

| 5.9  | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $N_f = -4 \times 10^{12}$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . . | 83 |

| 5.10 | Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with $N_f = 4 \times 10^{12}$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .  | 83 |

| 5.11 | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $N_f = -4 \times 10^{12}$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . . | 84 |

| 5.12 | Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with $N_f = 4 \times 10^{12}$ due to i) RDF, ii) OTF, iii) CRF, iv) LER. . . . .  | 84 |

| 5.13 | Circuit diagram of CMOS inverter using GC-DMDG s-Si MOSFET with interface charges. . . . .                                                       | 86 |

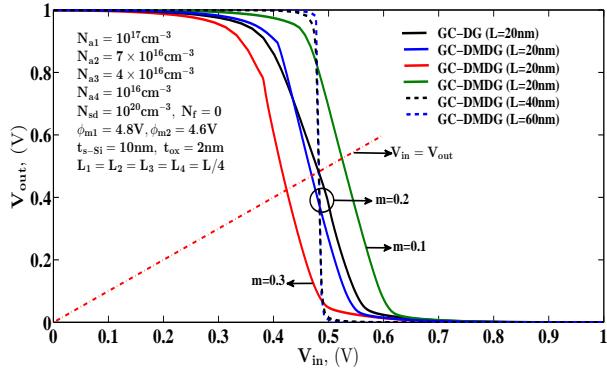

| 5.14 | VTC of CMOS inverter using GC-DMDG s-Si MOSFET for different values of $m$ and $L$ . . . . .                                                     | 86 |

| 5.15 | VTC of CMOS inverter using GC-DMDG s-Si MOSFET for different values of $N_f$ , $t_{ox}$ and $t_{s-Si}$ . . . . .                                 | 87 |

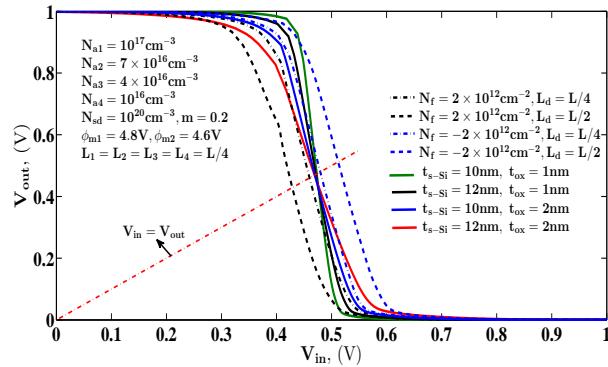

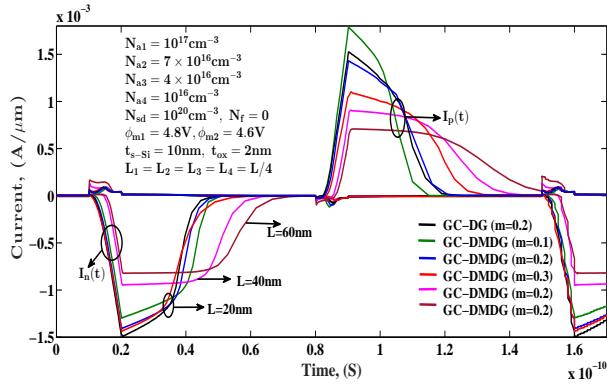

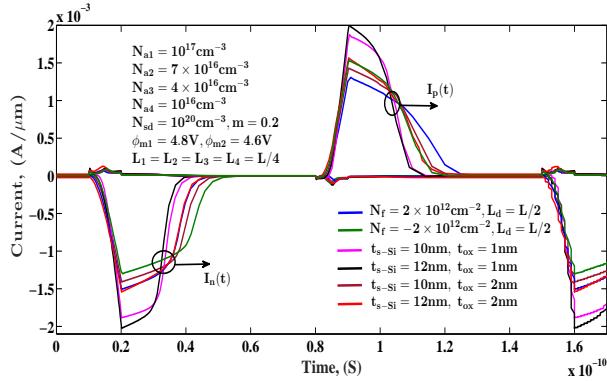

| 5.16 | Transient response of currents ( $I_n(t)$ and $I_p(t)$ ) in CMOS inverter for various values of $m$ and $L$ . . . . .                            | 88 |

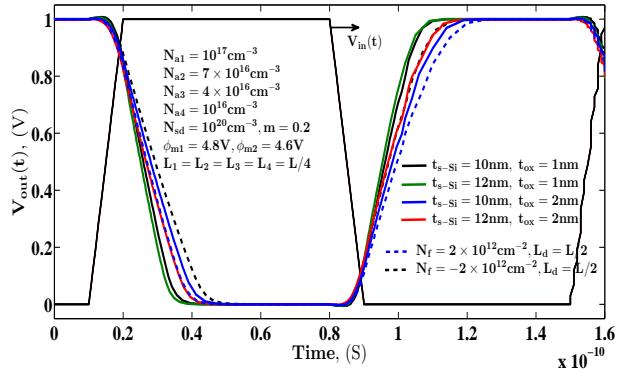

| 5.17 | Transient response of currents ( $I_n(t)$ and $I_p(t)$ ) in CMOS inverter for various values of $N_f$ , $t_{ox}$ and $t_{s-Si}$ . . . . .        | 88 |

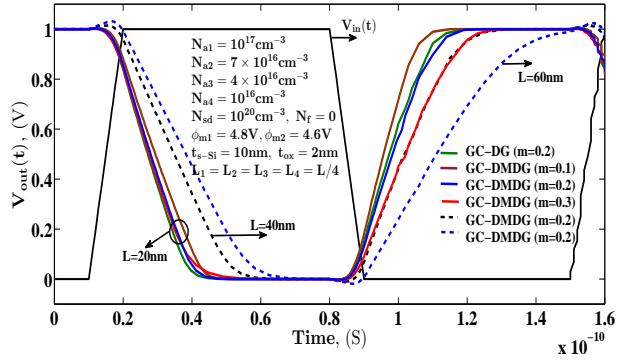

| 5.18 | Transient response ( $V_{out}(t)$ ) of CMOS inverter for various values of $m$ and $L$ . . . . .                                                 | 89 |

# List of Tables

|     |                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------|----|

| 3.1 | Dimensions and parameters used in simulation of GC-DMDG s-Si MOSFET . . . . .             | 24 |

| 3.2 | Performance comparison of the proposed GC s-Si MOSFET with the previous works . . . . .   | 46 |

| 4.1 | Performance evaluation of the proposed GC s-Si MOSFET with the literature. . . . .        | 61 |

| 4.2 | Parameters and dimensions considered in simulation of GCGS-TMDG s-Si device . . . . .     | 62 |

| 4.3 | The performance evaluation of proposed GCGS-TMDG s-Si device with previous works. . . . . | 74 |

| 5.1 | Variability analysis of proposed GCDM-DG s-Si n-MOSFET with $V_{ds} = 0.05$ V . . . . .   | 80 |

| 5.2 | Variability analysis of proposed GCDM-DG s-Si p-MOSFET with $V_{ds} = 0.05$ V . . . . .   | 81 |

| 5.3 | Variability analysis of proposed GCDM-DG s-Si n-MOSFET with $V_{ds} = 0.9$ V . . . . .    | 84 |

| 5.4 | Variability analysis of proposed GCDM-DG s-Si p-MOSFET with $V_{ds} = 0.9$ V . . . . .    | 85 |

| 5.5 | Noise margin of CMOS inverter using GC-DMDG s-Si MOSFET . . . . .                         | 87 |

# List of Abbreviations

|                |                                                     |

|----------------|-----------------------------------------------------|

| <b>2D</b>      | Two Dimensional                                     |

| <b>BJT</b>     | Bipolar junction transistor                         |

| <b>CMOS</b>    | Complementary Metal Oxide Semiconductor             |

| <b>CPU</b>     | Central processing Unit                             |

| <b>DIBL</b>    | Drain-induced barrier-lowering                      |

| <b>DMG</b>     | Dual-metal-gate                                     |

| <b>FD</b>      | Fully-depleted                                      |

| <b>FOM</b>     | Figure of merit                                     |

| <b>Ge</b>      | Germanium                                           |

| <b>HCEs</b>    | Hot-carrier effects                                 |

| <b>IC</b>      | Integrated Circuit                                  |

| <b>ITRS</b>    | International Technology Roadmap for Semiconductors |

| <b>MOSFET</b>  | Metal Oxide Semiconductor Field Effect Transistor   |

| <b>MuGFETs</b> | Multi-gate field effect transistors                 |

| <b>nMOSFET</b> | n-channel MOSFET                                    |

| <b>pMOSFET</b> | p-channel MOSFET                                    |

| <b>PD</b>      | Partially-depleted                                  |

| <b>QMEs</b>    | Quantum mechanical effects                          |

| <b>RF</b>      | Radio Frequency                                     |

| <b>SCEs</b>    | Short-channel effects                               |

| <b>Si</b>      | Silicon                                             |

| <b>SOI</b>     | Silicon-on-insulator                                |

| <b>s-Si</b>    | Strained-silicon                                    |

| <b>SoC</b>     | System On-Chip                                      |

| <b>VLSI</b>    | Very large scale integration                        |

| <b>ULSI</b>    | Ultra-large scale integration                       |

| <b>UTB</b>     | Ultra-thin body                                     |

# List of Symbols

|                 |                                                                                   |

|-----------------|-----------------------------------------------------------------------------------|

| $\epsilon_{Si}$ | Permittivity of Si (F cm <sup>-1</sup> )                                          |

| $\epsilon_{ox}$ | Permittivity of SiO <sub>2</sub> (F cm <sup>-1</sup> )                            |

| $t_{s-Si}$      | Strained-Silicon channel thickness (nm)                                           |

| $t_{ox}$        | Oxide thickness (nm)                                                              |

| $L$             | Channel length (nm)                                                               |

| $q$             | Charge of electron (1.6e <sup>-19</sup> C)                                        |

| $N_A$           | Acceptor doping concentration of channel (cm <sup>-3</sup> )                      |

| $N_{sd}$        | Source/drain doping concentration (cm <sup>-3</sup> )                             |

| $V_{fb}$        | Flat-band voltage (V)                                                             |

| $\chi_{Si}$     | Electron affinity of Si (eV)                                                      |

| $E_g$           | Silicon energy band gap (eV)                                                      |

| $N_{V,s-Si}$    | Density of states in the valence band of s-Si                                     |

| $m_{h,s-Si}^*$  | Hole effective masses of s-Si                                                     |

| $V_T$           | Thermal voltage (V)                                                               |

| $n_i$           | Intrinsic carrier density (cm <sup>-3</sup> )                                     |

| $\psi_{cr}(x))$ | Center channel potential (V)                                                      |

| $m$             | Ge mole fraction                                                                  |

| $V_{GS}$        | Gate to source voltage (V)                                                        |

| $V_{DS}$        | Drain to source voltage (V)                                                       |

| $N_f$           | Interface charge density (cm <sup>-2</sup> )                                      |

| $V_{bi,s-Si}$   | Built in voltage of s-Si (V)                                                      |

| $k$             | Boltzmann's constant (1.38e <sup>-23</sup> JK <sup>-1</sup> )                     |

| $T$             | Temperature (300K)                                                                |

| $C_{gg}$        | Total gate capacitance (fF)                                                       |

| $V_{th}$        | Threshold voltage (V)                                                             |

| $x_{min}$       | Minimum channel potential (V)                                                     |

| $E$             | Electric field (V cm <sup>-3</sup> )                                              |

| $SS$            | Subthreshold swing (mV/Dec.)                                                      |

| $\mu$           | Mobility of the free carrier (cm <sup>2</sup> V <sup>-1</sup> sec <sup>-1</sup> ) |

| $\lambda$       | Natural length                                                                    |

| $V_{th}$        | Threshold Voltage                                                                 |

| $J_n(y)$        | Current density (A/μm)                                                            |

# Chapter 1

## Introduction

### 1.1 Overview

The semiconductor manufacturing company has been playing a major role in digital world since 1970 and is one of the world's big companies. The development of semiconductor company has not been uniform but has a enormous influence on other companies such as smart homes, communication, security, transportation, surveillance, health care, etc. Such a remarkable growth was not at all seen earlier in any industry in the past. World semiconductor commerce census predict its worldwide semiconductor trading as \$440 billion in 2020, which is 6.8% more than the sales in 2019. Semiconductor materials, which have electrical conductivity that lies in between conductivity of conductors and insulators, are categorized into extrinsic (impure) and intrinsic (pure) semiconductors. Moreover, a few pure elements and various compounds show semiconductor characteristics of germanium, silicon, and compounds of gallium, which are most frequently utilized in electronic components. Besides, based on type of impurity, impure materials are classified into p-type and n-type semiconductors. Applications of semiconductors have been growing gradually from radio to almost each electronic component that has controlled switch. Semiconductor components are extensively studied to achieve better performance in terms of low power consumption, high speed, high efficiency, and small area with good functionality. The continual requirement of performance enhancement has the inspiring drive behind the investigation of advanced semiconductor MOSFETs and drive this area truly interesting also difficult.

## 1.2 History of Transistors

In 1940s, the transistor was invented and is a semiconductor component it can switch or strengthen the electrical signals [1]. The vacuum tubes transformed the domain of electronic components and give rise to portable and cost effective computers, calculators, and radios. The concept of field-effect component was demonstrated in 1926 [2]. In 1952, junction field-effect transistor was proposed based on the unipolar concept with three electrodes by Shockley [3]. In 1960, the most essential unipolar component, which was called as the metal oxide semiconductor field effect transistor (MOSFET) has four electrodes adding a body to handle the electrical characteristics more effective manner[4]. However, for most of the analog circuits, the BJT has been transistor of choice even after the invention of MOSFET, since it has better driving capability and ease of process flow.

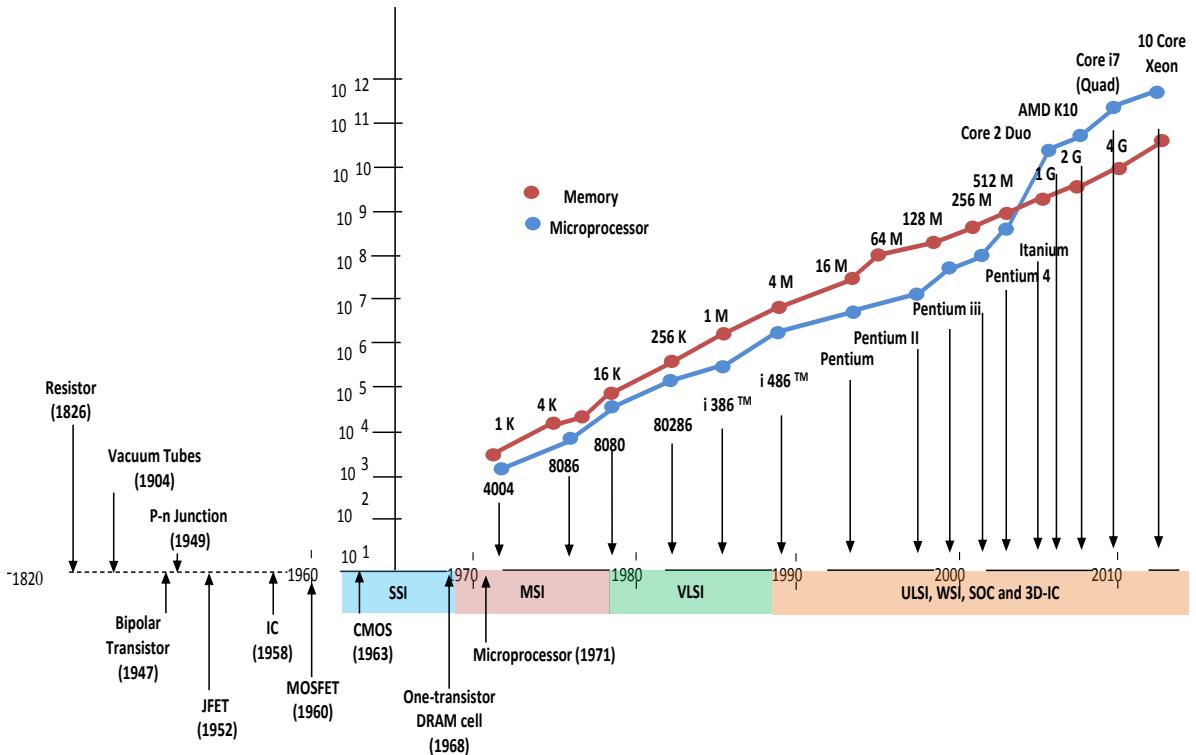

Figure 1.1: A brief time line of the important events in the advancement of Semiconductor technology

In 1957, proposed an integrated circuit (IC) that comprises of resistors, capacitors, and transistors [5]. The major milestone in the enhancement of integration onto the semiconductor chip, which is a complementary metal oxide semiconductor (CMOS) technology, was marked in 1963. With the help of CMOS process, researchers have capable to integrate thousands of billions of devices on a substrate. Nowadays, the CMOS technology has become the most used technology in semiconductor industry and is used for the fabrication of micro-controllers,

memories, and other analog (digital) circuits due to high packing density. Fig. 1.1 shows the important milestones in the development of semiconductor industry. Moore's law states that number of devices per square inch on the IC double in each 18 months [6]. In semiconductor industry, two major milestones are noticed in 1989 and 2005. In 1989, the million and billion devices were integrated onto a semiconductor wafer. In 2005, ultra large scale integration (ULSI) was possible due to the MOSFET scaling and advanced semiconductor manufacturing process.

### 1.3 MOSFET Scaling

The electronic industry has been extremely benefiting from scaling down the dimensions of MOSFET for the last four decades. The shrinking of MOSFETs to sub-nano meter scale enables integration of the billions of the components on a small substrate area. Initially, the constant electric field scaling theory was introduced in 1974 [7]. In this theory, the scaling was done to the dimensions and voltage of the device with same scaling factor  $S$  while keeping electric field constant. Hence, the speed of device increases by a factor  $S$  and the power dissipation of the device decreases by a factor of  $S^2$ . The other major scaling is constant voltage scaling. In this theory, the operating voltage of the device is unchanged and scaling is applied to all other parameters of the device.

In 2015, International Technology Roadmap for Semiconductors (ITRS) presented that the scaling of the MOSFET more Moore beyond CMOS technology node could be a challenging task since the planar MOSFET has already reached its scaling limit [8]. Moreover, more Moore beyond CMOS Further continuing the scaling of MOSFETs leads to high hot carrier effects (HCEs) and short channel effects (SCEs) such as subthreshold swing, drain induced barrier lowering (DIBL), threshold voltage roll-off, and interface charges [9]. Hence, the performance of MOSFET deteriorates in terms of leakage current, non ideal switching characteristics, and power dissipation. Therefore, the elimination of HCEs and SCEs till allowable amount is of importance in device scaling. To further continue the MOSFET scaling in sub 30 nm, we need to come up with novel device structures and new materials (i.e., CMOS technology boosters).

## 1.4 CMOS boosters

As explained in preceding section, a major challenging task in nano-scaled CMOS scaling is eliminating the SCEs and HCEs. To suppress SCEs and HCEs, CMOS boosters are incorporated into the nano-scaled device. They are strained-silicon (s-Si), channel engineering, gate material engineering, high-k dielectric material, non-conventional MOSFET structures, etc. Some of them are illustrated below.

### 1.4.1 Strained-silicon material

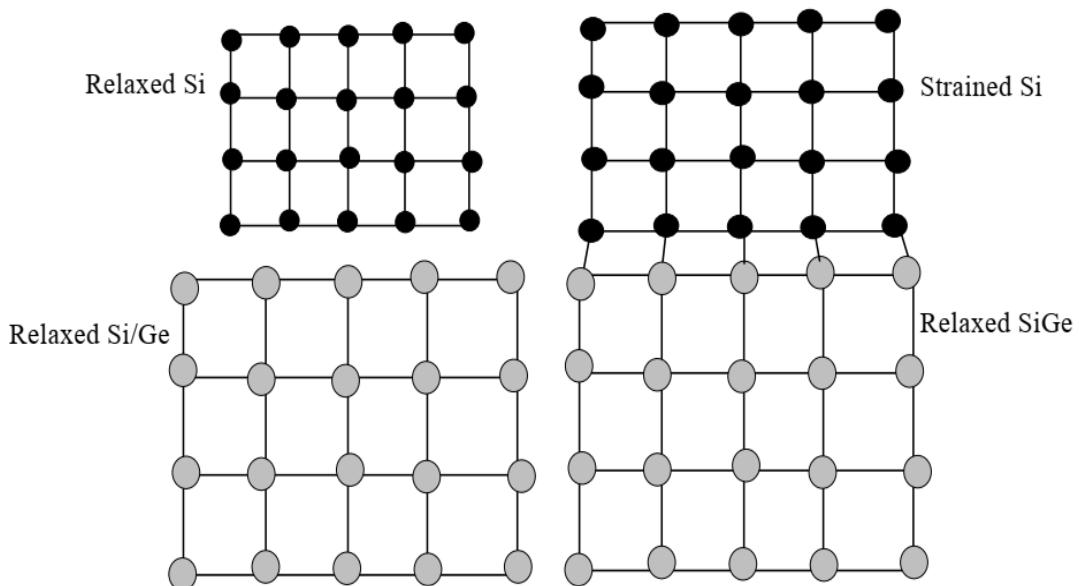

Traditionally, s-Si layer is included for its advantageous characteristics such as enhanced carrier mobility, overshoot of carrier velocity, and high ON current [10]-[12]. With the help of layer transfer technique [13], biaxial-tensile strain is induced in Silicon material by developing the Silicon material over a  $\text{Si}_{1-X}\text{Ge}_X$  buffer material with bigger in plane lattice constant than the Silicon material, which is grown on silicon on insulator (SOI) body. Later, by selective etching process, the s-Si layer is transferred on the surface of the SOI substrate by removing the  $\text{Si}_{1-X}\text{Ge}_X$  layer. However, the removal of  $\text{Si}_{1-X}\text{Ge}_X$  layer does not change the amount of strain in Silicon material [14]. Consequentially, the strain in Silicon material turns out to be a function of  $X$  ( $X$  is a Germanium mole fraction in Silicon material) of the relaxed  $\text{Si}_{1-X}\text{Ge}_X$ , as observed in the Silicon material that is directly grown on the  $\text{Si}_{1-X}\text{Ge}_X$  interface.

Figure 1.2: Lattice structure of relaxed silicon, relaxed SiGe, and s-Si on relaxed SiGe

### 1.4.2 Gate material engineering

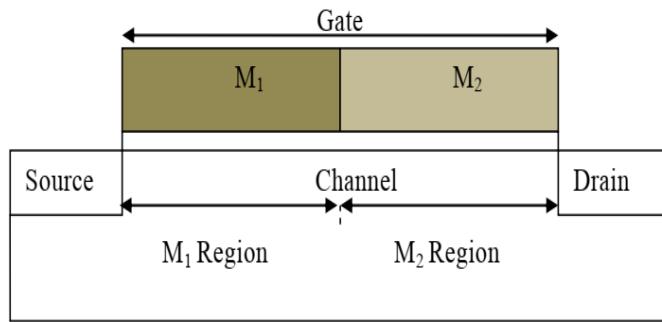

Dual-Metal-Gate (DMG) structure, which is one of the notable CMOS technology boosters, was proposed by Long et al. [15]. The gate material of the DMG MOSFET consists of control gate work function is  $\phi_{m1}$  and screen gate work function is  $\phi_{m2}$ .  $\phi_{m1} > \phi_{m2}$  for n-type device, and vice versa for p-type device. Consequently, the step-equivalent curve is attained in the channel potential. When device operates in the saturation region, the channel region under control gate layer is screened from a drain to source voltage ( $V_{ds}$ ) as the channel region under screening gate layer absorbs any excess  $V_{ds}$ . Therefore, the SCEs and HCEs of the MOSFET are suppressed by employing DMG structure.

Figure 1.3: 2-D diagram of DMG structure of MOSFET.

### 1.4.3 Graded channel engineering

If the doping profile in the Silicon channel decreases uniformly in a stepwise manner from the source/channel interface to the drain/channel interface then it is considered as graded-channel (GC) structure [16]. By employing GC structure in the MOSFET, high threshold voltages and low SCEs are obtained. Moreover, the HCEs are also reduced due to the lower built-in potential at the drain/channel interface.

### 1.4.4 High-k insulating material

In a process of scaling CMOS devices, the thickness of the dielectric material has reached 10 Angstrom. With the reduction of channel length below 32 nm, the gate dielectric thickness has to be scaled down to an ultra-thin size (i.e., less than 1 nm approximately, which is equivalent to five atomic layers). This very thin dielectric layer results in a huge amount of OFF current, thereby increasing the standby power consumption. Therefore, a need of thick dielectric material is required in order to prevent electrons tunneling through gate oxide [17],

i.e., the physical thickness of the dielectric material has to be high, whereas its electrical thickness has to be low. Hence, high-k dielectric materials could be one of the best solutions for the issues discussed. The effective oxide thickness of the high-k dielectric material is given as  $t_{eff} = t_{high-k} \frac{\epsilon_{SiO_2}}{\epsilon_{high-k}}$ , where  $\epsilon_{SiO_2}$  and  $\epsilon_{high-k}$  are permittivities of silicon dioxide material and high-k dielectric layer, respectively.  $t_{high-k}$  is thickness of high-k dielectric layer. Researchers have found a few suitable high-k dielectric materials, such as  $HfO_2$ ,  $ZrO_2$ , and  $Ta_2O_5$  to suppress the SCEs and gate tunneling current simultaneously.

#### 1.4.5 Non-conventional MOSFETs

The multiple-gate (MuG) MOSFETs are categorized as the double gate (DG) conventional SOI MOSFET, DG non-conventional FinFET, Tri-gate MOSFET, Quadruple Gate MOSFET, surrounding gate MOSFET, and Nanowire MOSFET. The MuG-MOSFET structures can have high gate control over the silicon channel [18]. Consequently, reduction of leakage current and SCEs of the device can be attained. Nevertheless, several process flow issues of MuG-MOSFETs must be resolved before using the MuG-MOSFETs in VLSI systems. Moreover, MuG-MOSFETs require modern fabrication methods such as enhanced etching accuracy, corner effects, reliability, and ultra-thin fin effects, etc.

### 1.5 Motivation

In nano-scaled regime, DG s-Si MOSFETs suffer from SCEs and HCEs. To suppress SCEs and HCEs, both DMG with GC engineering and gate stack structure are employed in DG s-Si MOSFET. In the light of above discussion, an effort is done to investigate the subthreshold performance of DG s-Si MOSFET. Therefore, theoretical models of the subthreshold characteristics are developed for DG s-Si MOSFET. Moreover, the effect of various device parameters on the subthreshold characteristics of DG s-Si MOSFET is investigated using the derived theoretical models. Besides, CMOS technology boosters like DMG with GC engineering and high-k dielectric material help to enhance ON current of DG s-Si MOSFET. Therefore, these techniques are employed in the DG s-Si MOSFET to examine their effects on subthreshold behavior of the MOSFET.

## 1.6 Problem statement

The aim of this thesis is to introduce a comprehensive simulation and modeling based investigation on subthreshold performance of DG s-Si MOSFET with interface charges, including the CMOS technology boosters such as DMG with GC engineering and high-k dielectric material.

## 1.7 Objectives

- Modeling of center potential and threshold voltage of GC-DMDG s-Si MOSFET with interface charges

- Modeling of sub-threshold current and swing of GC-DMDG s-Si MOSFET with interface charges

- Analog/RF performance of GC-DMDG s-Si MOSFET with interface charges

- Variability analysis of GC-DMDG s-Si MOSFET with interface charges

- Analog/RF performance of GCGS-TMDG s-Si MOSFET with interface charges

## 1.8 Organization of Work

The main aim of this thesis is to demonstrate a exhaustive modeling and the simulation based analysis of the subthreshold performance of DG s-Si MOSFET with interface charges including the CMOS technology boosters. The thesis comprises six chapters containing the present Chapter. The contents of other chapters of the thesis are outlined as follows:

**Chapter 2** reviews the notable amount of most updated literature of the modeling and simulation of DG MOSFET and DG s-Si MOSFET with interface charges in detail.

**Chapter 3** deals with the analytical simulation and modeling of subthreshold characteristics of GC-DMDG s-Si MOSFET with interface charges.

**Chapter 4** presents a detailed analysis of analog/RF performance evaluation of GC-DMDG s-Si MOSFET and GCGS-TMDG s-Si MOSFET with interface charges.

**Chapter 5** presents a detailed study of variability analysis of GC-DMDG s-Si MOSFET with interface charges and CMOS inverter's performance.

**Chapter 6** review the work done in thesis and provides some direction for the upcoming work.

# Chapter 2

## Literature Survey

### 2.1 Introduction

MOSFET miniaturization has several advantages, such as high switching speed, high density, good functionality and low cost of microprocessors. However, the problems related with miniaturization of the planar MOS transistors increase as the transistor density in ICs increases. The CMOS boosters, which have already been discussed in Chapter 1, are extremely helpful to address the issues related with miniaturization. Also, double gate s-Si device is one of the MOSFETs that are scaled down to the higher degree compared to the conventional device due to their reduced SCEs. However, when DG s-Si MOSFET is scaled down to nano-scaled regime, it still exhibits HCEs and SCEs. In order to reduce these effects, gate and channel engineering techniques are applied to DG s-Si MOSFET.

The objective of this thesis is to carry out the two dimensional (2-D) modeling and simulation of sub-threshold analysis of proposed DG s-Si device structures. As the upcoming research methods in any domain could be estimated with the help of detailed study of the up to date research in a specific domain of interest, this chapter is devoted to describe a thorough review of the up to date work on different features of DG s-Si MOSFETs and gate and channel engineering of DG s-Si MOSFETs to verify the scope of thesis mentioned in previous chapter.

## 2.2 Review on strained-silicon MOSFETs

strained-silicon MOSFETs have been reported by many researchers due to their better performance over conventional Si MOSFETs [19]-[26].

In [27], utilizing the exact solution of 2-D Poisson's equation, surface potential, subthreshold current, threshold voltage, and subthreshold swing have been modeled for gate stack DG s-Si MOSFETs. In addition this, it not only provides the physical perspective into MOSFET physics but also offers the simple designing method of further immunity of SCEs of CMOS based MOSFET in the nanoscale regime.

In [28], with the help of 2-D simulation, the effect of the strain in the conduction path of cylindrical s-Si MOSFETs was demonstrated. For low values of the strain, the conduction path is created in center of the cylindrical SiGe pillar and there is no conduction path at s-Si layer surface. However, for large values of strain, the conduction path obtains in s-Si layer, thereby enabling the benefit of mobility improvement of carriers in MOSFET operation.

In [29], ultralow on-resistance s-Si-on-insulator lateral double-diffused MOSFET with silicon-germanium and trench gate was presented. In OFF state, both trench gate and P-top layer help in depleting N-drift region, which turns to an allowable heavily doped N-type drift region. Furthermore, the improved electric field in trench oxide increases the breakdown voltage.

In [30], the BSIM3 model was developed for biaxially strained p-MOSFETs with the help of a suitable parameter extraction technique. The obtained model parameters were calibrated by comparing the results with numerical TCAD simulations and a basic analytical model. The mean error in the alternating current and direct current characteristics of a model were predicted to be less than 1.5%.

In [31], the impact of uniaxial-strain on energy band structure, mobility of a carrier, effective masses of carrier, density of states, and high-field saturation on the ON current, leakage current and switching speed in nano-scale, Silicon and Germanium, DG p-MOSFETs were exhaustively investigated.

### 2.2.1 Review on s-Si MOSFETs with interface charges

The electric field in nano-scaled MOSFET introduces trap charges at the Si/SiO<sub>2</sub> region, which degrade the electrical behavior of s-Si MOSFET due to HCEs. Thereby, the damaged region at Si/SiO<sub>2</sub> interface of the DG MOSFET is expanded from drain end to source end with interface charges owing to HCEs. Until now, so many researchers have explored HCEs in the DG MOSFETs [32], [33], which are attributed to the electron type (acceptor) or hole type (donor) trap generation at Si/SiO<sub>2</sub> region can be transformed into the corresponding interface trap charges (positive or negative localized charges).

In [34], a surface potential model was presented for s-Si on Silicon-Germanium MOSFET with interface charges. The 2-D Poisson's equation was solved in damaged and undamaged s-Si regions to get the surface potential of the channel. The impacts of different values of damaged length and interface charges on channel potential were presented in detail. The channel potential dependency on the effect of strain was also investigated.

In [35], a surface potential based threshold voltage model for performance analysis of gate stack dual-metal-insulated-gate source-engineered fully-depleted (FD) SOI MOSFET was demonstrated. Also, the parametric investigation was done to optimize the MOSFET dimensions for enhanced nanoscaled MOS design. Furthermore, a six transistor SRAM cell was developed using gate stack dual-metal-insulated-gate source-engineered FD SOI MOSFET and static noise margin was calculated.

In [36], the effects of oxide charges induced by various SOI thicknesses on the performance and reliability of a strained SOI device with SiN-capped contact etch stop layer were presented. Compared to thick thickness of SOI MOSFET, the thin thickness of SOI MOSFET with high strain contact etch stop layer possesses higher interface trap density, thereby degrading the MOSFET performance.

In [37], the border trap characterization of TaN/HfO<sub>2</sub>/Si and TaN/HfO<sub>2</sub>/s-Si/Si<sub>0.8</sub>Ge<sub>0.2</sub> MOSFET was illustrated. Drain current hysteresis technique was used to obtain the border traps. It is noticed that border traps are greater in the case of high-k films on s-Si/Si<sub>0.8</sub>Ge<sub>0.2</sub>.

In [38], the impacts of silicon back trap state density between silicon channel and buried oxide layer on memory characteristics were presented. The back trap states of FD strained SOI substrate were deliberately obtained by varying the temperature of rapid thermal annealing method and the value of back trap was estimated with the help of back gated MOSFET method.

In [39], a 2-D threshold voltage analytical model of a DMG FD strained SOI MOSFET was developed by employing the interface charge effects. The presented threshold voltage model includes both positive and negative trap charges. Finally, the analytical model was validated with 2-D numerical device simulator.

### 2.2.2 Review on gate stack and gate engineering of s-Si MOSFETs

The dual metal gate structure was introduced in DG MOSFETs to suppress the HCEs and to further increase the immunity against SCEs [40]-[42]. Which has the control gate (source end) having greater work-function than at the screening gate (drain end). Consequently, the step-equivalent curve is attained in the channel potential. After the saturation region, the channel region under control gate layer is screened from the  $V_{ds}$  as the channel region under screening gate layer absorbs any excess  $V_{ds}$ . Therefore, the SCEs of DG MOSFET are suppressed by employing DMG structure [43]. Moreover, this gate engineering increases the average electric field in the channel due to the reduced peak electric field at the drain end in turn reducing the HCEs.

The triple material gate (TMG) engineering is incorporated by few authors in DG MOSFET to reduce the HCEs and SCEs [44]-[45]. Where TMG structure has three different work functions used for control and screen gates. Hence, a step profile in the channel potential is attained and the improved average electric field in the channel.

In [46], the impact of strain on a linearly graded work-function engineered surrounding gate MOSFET was demonstrated. From the result analysis, it is noticed that the inclusion of strain shifts the minimum channel potential toward the source side, which in-turn gives a shielding to the drain voltage. Moreover, it is observed that linearly graded gate has better performance compared to the single metal gate in low power applications.

High-k dielectric with  $\text{SiO}_2$  used as gate stack (GS) is employed in DG MOSFET, so enhanced sub-threshold characteristics are attained due to the reduction in the gate leakage current of DG MOSFET. In [47], the transconductance of the s-Si p-MOSFETs with high-k dielectric material as gate oxide was estimated. Moreover, transconductance improvement factors of 2.73 and 2.97 are noticed for s-Si p-type MOSFETs in comparison with conventional Si p-type MOSFETs with high-k and  $\text{SiO}_2$  dielectric materials, respectively. The transconductance of s-Si MOSFET at low temperature was also simulated.

In [48], a theoretical model to present the s-Si nanoscale DG MOSFET along with high-k dielectric material was proposed. By including the effects of s-Si and high-k dielectrics in devices, alteration of energy band diagram and increase in conduction band offset are noticed. The mobility can also be enhanced while maintaining the effective gate control.

In [49], SCEs of high-k GS dual material tri-gate s-Si-on-nothing MOSFET with dual material bottom gate were demonstrated. Moreover, the channel potential of the MOSFET was derived along with its electric field and threshold voltage. The effect of the MOSFET performance owing to the varying of various MOSFET parameters was also discussed.

In [50], the 2-D analytical modeling of high-k triple material gate stack DG s-Si on nothing MOSFET with a ion-implanted doping profile was proposed. The surface potential was developed by using the 2-D Poisson's equation and including the parabolic channel potential approximation. The threshold voltage and electric field were also derived for the device. Besides, comprehensive studies of the MOSFET response regarding the different SCEs were also presented.

In [51], strained SiGe p-MOSFETs with high-k dielectric were fabricated and characterized. The s-Si/s-Si<sub>0.5</sub>Ge<sub>0.5</sub>/strained SOI heterostructure MOSFETs offer good transfer and output characteristics with an ON and OFF current ratios of 105. The obtained hole mobility exhibits an improvement of about 2.5 times over Silicon hole mobility and no deterioration in hole mobility compared to SiO<sub>2</sub> or even HfO<sub>2</sub> gate dielectric MOSFETs.

### 2.2.3 Review on channel engineering of s-Si MOSFETs

Lateral graded channel engineering have been used in DG MOSFETs to achieve higher threshold voltage and decreased SCEs [52]-[54]. In GC structure, doping profile in the Silicon channel decreases from the source/channel interface to drain/channel interface. Besides, the peak electric field at drain side is reduced due to the lower built-in potential at drain/channel interface, thereby reducing the HCEs through lateral GC engineering.

In [55], an asymmetric DG single halo doped SOI MOSFET were investigated theoretically and compared with an asymmetric DG SOI MOSFET. The 2-D simulation studies illustrate that the inclusion of single halo in the DG structure results in reduced DIBL, threshold voltage roll-up, kink free in output characteristics, high output resistance and higher breakdown voltage when compared to simple DG structure. Moreover, the incorporation of single halo in

DG MOSFET results in step like potential profile, which screens the channel potential at source side from the drain voltage.

## 2.3 Review on DG MOSFETs

So far, many analytical models have been reported on DG MOSFETs with high transconductance and double drive current. Here, a higher degree of gate control over channel than drain reduces the SCEs [56, 57].

In [56], a 2-D analytical model for electrostatic potential was developed for undoped DG MOSFETs. The threshold voltage roll-off, subthreshold current and swing of DG MOSFETs are in good agreement with the TCAD simulation results. Besides, this model not only provides useful physics related to SCEs but is also used as basis for compact modeling of the DG MOSFETs.

In [57], an analytical model of threshold voltage for DG MOSFETs with fixed charges was developed. With the aid of 2-D Poisson's equation and parabolic potential approximation, threshold voltage model for device was derived. Moreover, it can be helpful to estimate hot carrier induced MOSFET deterioration for different MOSFET dimensions.

In [58], deterioration in the performance of the device due to HCEs in nano-scale DG MOSFETs was noticed. Besides, the hot carrier degradation effects on threshold voltage, surface potential, and DIBL of DG MOSFETs were also investigated. It is also observed that the deterioration in the performance of device becomes severe when the channel length decreases and the position of minimum channel potential is affected by the localized charge density.

In [59], a surface potential model of DMG MOSFETs by considering a channel depletion layer and depletion layers around the source (drain) junctions was developed. It can also be used in current models to estimate the subthreshold current.

In [60], based on the 2-D Poisson's equation, a subthreshold model consists of channel potential, threshold voltage, and subthreshold swing for the short-channel asymmetrical DMDG MOSFETs was presented. To reduce the SCEs, the MOSFET parameters such as thin substrate, thin oxide, and high ratio of control to screen gate are preferred.

## 2.4 Review on multiple gate MOSFETs

The electrostatic control of double and triple-gate devices can be enhanced by expanding the sidewall regions of the gate terminal to some level in buried oxide and bottom channel region. From an electrostatic perspective, the triple-gate and omega-gate MOSFETs comprise three and four gates, respectively. Furthermore, the electrostatic control can be improved by the surrounding-gate device. The surrounding-gate MOSFET was fabricated by wrapping a gate terminal around a silicon substrate [61].

In [62], multiple-gate (MG) MOSFETs with short channel length are evaluated using device Monte Carlo simulation. From the result analysis, the DG MOSFET has higher current drive capability and less leakage current than non-planar devices. However, source and drain regions have to be cautiously scaled to get optimal values of resistance and fringe capacitance.

In [63], the analytical modeling and simulation of output characteristics, transconductance, and output conductance of dual metal quadruple gate MOSFET were presented by changing the ratios of gate length and work function. Moreover, it is noticed that the better performance of a fixed channel length device can be attained by maintaining the length of control gate higher than the screen gate.

In [64], analytical model for the capacitance-voltage (C-V) characteristics of s-Si gate all around MOSFETs for different operating regions was developed. The effects of MOSFET dimensions, doping concentration, fixed charges, and strain on C-V characteristics of S-Si gate all around (GAA) MOSFETs were investigated. It is noticed that the proposed device performance becomes better by employing high-k dielectrics.

In [65], the authors presented the electrothermal characterization of various nanoscale MG MOSFETs, such as quadruple-gate,  $\pi$ -gate, and  $\omega$ -gate MOSFETs. Moreover, the temperature profile of a  $\omega$ -gate device with GC width was also investigated. Finite difference method was used to solve the 3-D time-dependent heat conduction equations. Besides, the transient temperature characteristics of MG MOSFETs were also studied.

## 2.5 Review on subthreshold characteristics models of DG s-Si MOSFETs

Till now, so many researchers have developed the different models to attain subthreshold performance of SOI and DG MOSFETs [66]-[68].

[69], a 2-D surface potential model for a FD DG s-Si MOSFET with interface charges was developed. The interface charges in the damage region owing to the HCE is a common phenomenon in short-channel MOSFETs. The developed analytical model contains effect of both negative and positive fixed charges. The effects of fixed charge density with damaged length and strain on the surface potential were examined comprehensively.

[70], a threshold voltage model of undoped DG MOSFET interface charges near the drain end was illustrated. In subthreshold region, the analytical model was developed based on solution of the potential distribution in the channel. Moreover, both the surface potential and threshold voltage models are in good agreement with the Atlas simulation results for different interface charge density with damaged lengths.

In [68], the substrate bias voltage dependent three dimensional subthreshold models of threshold voltage, channel potential, DIBL, current, and subthreshold swing of tri-gate SOI MOSFETs were developed. Moreover, a three dimensional approach had been used to derive the minimum of potential, which was later used to derive models of various device parameters.

In [52], the GC GS DG MOSFET was examined in view of improving device characteristics and immunity to SCEs. The MOSFET has a advantage of enhanced gate-oxide reliability, reduced parasitic bipolar-effect, improved cut off frequency and lower DIBL.

In [71], a 2-D subthreshold model was presented for a GC DG FD-SOI MOSFET, including the gate misalignment effect. The conformal mapping conversion method was used to give an accurate estimation of electric field, surface potential, and subthreshold behavior of the MOSFET by employing the gate misalignment effects on both drain and source side.

### 2.5.1 Review on threshold voltage models of DG s-Si MOSFETs

In [72], a analytical model for threshold voltage of nano-scale s-Si on insulator and s-Si on SiGe on insulator MOSFETs was presented. Moreover, this model considers the effects of strain and different device parameters. It can also be used to estimate the DIBL effects.

To model the threshold voltage for s-Si MOSFETs analytically, the authors developed a surface potential based the threshold voltage model of single-layer FD s-Si on insulator MOSFETs [73]. In this model, the effects of MOSFET parameters such as strain, SCEs, gate work function, s-Si thin film doping and thickness on threshold voltage were demonstrated. This model offers reduction in threshold voltage by increasing the strain and s-Si thickness.

In [74], the authors presented surface potential based analytical model of the threshold voltage for s-Si on Si-Ge On-Insulator MOSFET with localized charges using 2-D Poisson's equation. Moreover, the effects of strain and positive/negative interface charge on surface potential and threshold voltage were demonstrated. Besides, deterioration in the performance of the device due to hot carriers was discussed for different device dimensions and charge profiles.

In [75], the surface potential based threshold voltage model of s-Si dual material DG MOSFETs with vertical-gaussian doped channel was developed. The effects of strain and gaussian profile parameters on surface potential, threshold voltage, and lateral electric field were presented.

In [16], the authors proposed the surface potential based threshold voltage model for graded channel-dual material DG (GC-DMDG) MOSFET. Moreover, SCEs of the device were analyzed using the surface potential based natural length. Further, in [16], although the model provided effective results, it failed to estimate short channel behavior of the device accurately. In fact for short channel symmetrical DG MOSFET, the leakage path is created early at the center rather than surface of the channel [76]. Thus, SCEs are accurately estimated by center potential based natural length than surface potential.

### 2.5.2 Review on subthreshold current models of DG s-Si MOSFETs

In [66], surface potential based models of subthreshold current (SC) and subthreshold swing (SS) of the s-Si on silicon germanium on insulator MOSFETs were developed. The subthreshold performance was evaluated by varying the different device parameters.

In [67], a physics based compact SC model of nano-scale DG MOSFETs was demonstrated. The channel potential was developed with the help of conformal mapping method and parabolic approximations. In the proposed model, the electrostatics are influenced by capacitive coupling between the body electrodes that are considered in subthreshold region.

In [77], the authors presented a 2-D analytical model of asymmetric 4T and 3T DG MOSFETs to evaluate the subthreshold performance. In the proposed model, it is observed that there is a change in position of charge centroid with respect to a difference in the front/back gate bias. The subthreshold behavior with asymmetry in the gate voltage, oxide thickness, and work function was presented. Also, a model for the subthreshold characteristics of 3T DG MOSFETs was demonstrated.

In [78], 2-D analytical models of the SC and SS of gaussian doped s-Si double-material double-gate (DMDG) MOSFET were presented. The SS and SC of device were optimized by selecting the projected range/straggle parameter value. Moreover, Gaussian doping profile offers an advantage of gaining better control on the subthreshold performance of the MOSFET with out altering the geometry of device.

In [79], a subthreshold current model of FD asymmetrical DG MOSFETs was developed. Moreover, the variations in subthreshold performance owing to structure's asymmetry such as difference in oxide thickness or bias voltage between front and back gate were presented.

### 2.5.3 Review on subthreshold swing models of DG s-Si MOSFETs

In [80], the authors presented a 2-D analytical model to analyze the channel conductance and subthreshold swing of a channel and gate engineered DG MOSFET. Here, the diffusion equation was considered to derive the drain to source current of the MOSFET in subthreshold region. Variations in subthreshold swing of the MOSFET for different materials, and oxide layer thickness were also presented.

In [81], physics based models of threshold voltage with the DIBL and subthreshold swing of undoped DG MOSFETs were developed. These models were obtained from a solution of 2-D Poisson's equation by considering a electron concentration.

In [82], the subthreshold characteristics of GC-DMDG MOSFET were analyzed with the help of analytical models of SC and SS. The variations in SS against various MOSFET parameters were observed with the aid of effective-conduction path parameter. The SC and SS of the

GC-DMDG MOSFET offers better performance when compared to a dual-material double-gate and GC DG MOSFETs.

In [45], analytical models of SC and SS of triple material DG MOSFET were presented. Both diffusion and drift components of current densities were included for modeling of SC. Virtual cathode idea of DG MOSFETs was employed to model a SS of triple material DG MOSFETs. The dependencies of SC and SS on various device dimensions were explored.