# **Design and Analysis of High-Performance Multilayer Differential Inductors for RFIC and MMIC Applications**

*Submitted in partial fulfillment of the requirements

for the award of the degree of

**DOCTOR OF PHILOSOPHY***

*by*

**SUNIL KUMAR TUMMA**

(Roll No: 701622)

Supervisor:

**Prof. N. Bheema Rao**

Professor

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

TELANGANA STATE-506004, INDIA

2021

**Dedicated to**

*My family & Teachers*

# Approval Sheet

This thesis entitled **“Design and Analysis of High-Performance Multilayer Differential Inductors for RFIC and MMIC Applications”** by **Sunil Kumar Tumma** is approved for the degree of Doctor of Philosophy.

## Examiners

---

Dr. Anand Bulusu

Professor

Department of ECE

IIT Roorke

## Supervisor

---

Dr. N. Bheema Rao

Professor

Department of ECE

NIT Warangal

## Chairman

---

Dr. L. Anjaneyulu

Professor & HOD

Department of ECE

NIT Warangal

Date: \_\_\_\_\_

# DECLARATION

This is to certify that the work presented in the thesis entitled "**Design and Analysis of High-Performance Multilayer Differential Inductors for RFIC and MMIC Applications**" is a bonafide work done by me under the supervision of **Prof. N. Bheema Rao**, Professor, Department of Electronics and Communication Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea / data / fact / source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

Sunil Kumar Tumma

(Roll No: 701622)

Date: .....

**DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

**NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**TELANGANA STATE-506004, INDIA**

## **CERTIFICATE**

This is to certify that the thesis entitled "**Design and Analysis of High-Performance Multi-layer Differential Inductors for RFIC and MMIC Applications**", which is being submitted by **Mr. Sunil Kumar Tumma (Roll No: 701622)**, in partial fulfillment for the award of the degree of Doctor of Philosophy to the Department of Electronics and Communication Engineering of National Institute of Technology Warangal, is a record of bonafide research work carried out by him under my supervision and has not been submitted elsewhere for any degree.

Prof. N. Bheema Rao

(Supervisor)

Professor

Department of E.C.E.

N.I.T. Warangal

Warangal - 506004, India

## ACKNOWLEDGEMENTS

Firstly, I would like to express my sincere gratitude to my supervisor Prof. N. Bheema Rao for the continuous support of my Ph.D study and related research, for his patience, motivation, and guidance. My sincere thanks to him for providing me an opportunity to join the institute as a Ph.D research scholar and giving me access to the research facilities. I find words inadequate to thank them for enabling me to complete this work in spite of all obstacles. The thesis would not have seen the light of the day without his insistent support and cooperation.

I am also grateful to Prof. L. Anjaneyulu, Head of the department, Department of Electronics and Communication Engineering, NIT Warangal for his valuable suggestions and support that he shared during my research tenure.

Besides my supervisor, I take this privilege to thank Doctoral Scrutiny Committee members, Dr. P. Sree Hari Rao, Associate professor, Department of Electronics and Communication Engineering, NIT Warangal, Dr. T.V.K. Hanumanth Rao, Associate professor, Department of Electronics and Communication Engineering, NIT Warangal, Prof. N. Vishwanathan, Department of Electrical Engineering, NIT Warangal for their continuous support, suggestions, and advices during my research period whenever required.

It is my pleasure to show my indebtedness to my co-scholars at NIT like Dr. P. Akhendra Kumar, Dr. R. Shashank, Dr. M.A. Mushahid Majid, S Subba Rao, Siva Rama Krishna, Jail Singh Bhookya, Santosh Kumar Veeramalla, Roshan Bodile, Prathap Soma, and Ravi Shankar Puppala for their help during the course of this work. I find no words inadequate to express any form of acknowledgement to my father, mother, wife, brothers for their love, support and patience for making my dream come true.

Finally, I thank God, for filling me every day with new hopes, strength, purpose and faith.

# ABSTRACT

Integrated inductors are one of the most basic passive elements used in the design of Radio Frequency Integrated Circuits (RFICs) and Monolithic Microwave Integrated Circuits (MMICs) to implement the circuits like Voltage Controlled Oscillators (VCO), Low Noise Amplifiers (LNA), impedance matching networks, filters, and power amplifiers. In realization of these circuits, high performance, as well as miniaturized on-chip inductors, are desirable to increase the reliability and to reduce the fabrication cost. The spiral inductors are considered to be a good choice, however, it produces moderate-quality factor (Q). Differential excitation of the symmetric spiral inductor known as the differential inductor is used to obtain high-quality factors over a wide range of frequencies. Fractal curves are used in the realization of inductors to increases the inductance density compared to the spiral inductors for the equivalent on-chip area. The multilayer implementation of the symmetrical spiral inductor and fractal inductor with differential excitation improves the figure-of-merit such as inductance, quality factor, and self-resonance frequency ( $f_{SR}$ ) over the conventional differential inductors.

Initially, in this thesis, several multilayer differential spiral inductors using variable width and multipath techniques have been proposed. Initially, the variable width series stacked differential spiral inductor has been proposed. The variable width of the metal decreases the series resistance and series stacking increases the metal trace length. Thus, it attains high Q and inductance over the conventional planar differential inductor. Furthermore, a variable multipath width multilayer differential inductor has been proposed. The variation in multipath width reduces the skin and proximity effects and up-down series stacking reduces the parasitic capacitance. Therefore, it attains high Q and self-resonance frequency over conventional planar differential inductor and planar multipath differential inductor. Later, series stacked non-parallel multipath differential inductor has been proposed that reduces the parasitic capacitance among the adjoining metal layers and also reduces the conductor's current crowding effects at high frequencies, leading to higher quality factor and self-resonance frequency over conventional series stacked multipath inductor occupying the equivalent on-chip area.

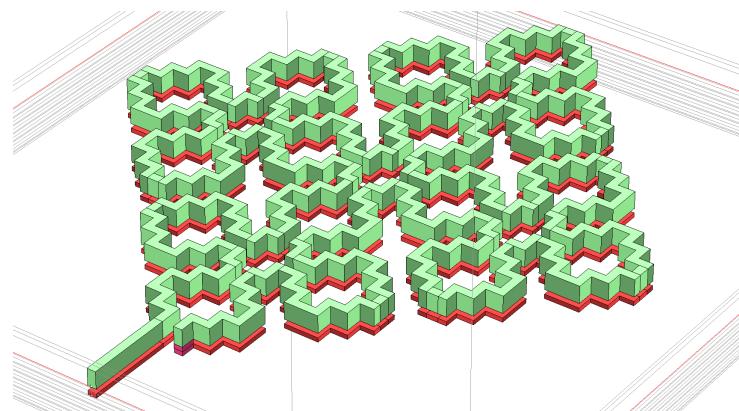

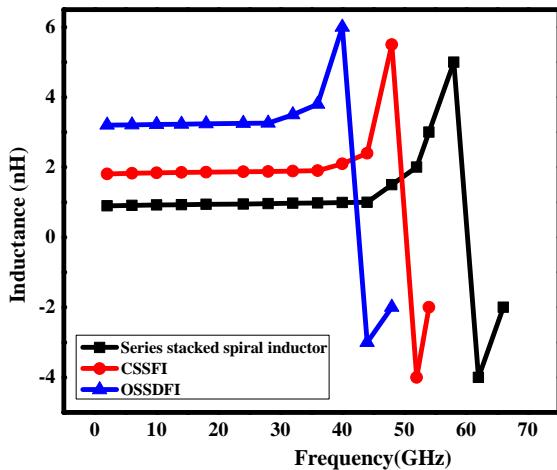

The conventional series stacked fractal inductor (CSSFI) achieves higher inductance due to longer trace lengths for the minimal on-chip area. However, it suffers from low Q and  $f_{SR}$  due to parasitic capacitance between the adjacent metal layers. To overcome this drawback a novel hybrid series stacked differential fractal inductor using Hilbert and Sierpinski fractal curves is proposed with two different layers connected in series using vias. The proposed inductor reduces the parasitic capacitance and negative mutual inductance between the adjacent layers

that attain significant improvement in overall inductance, quality factor, and self-resonance frequency when compared with CSSFI.

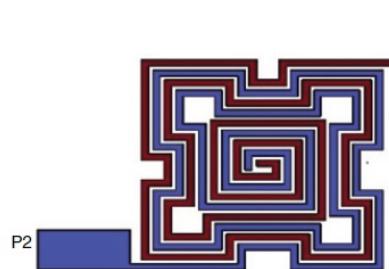

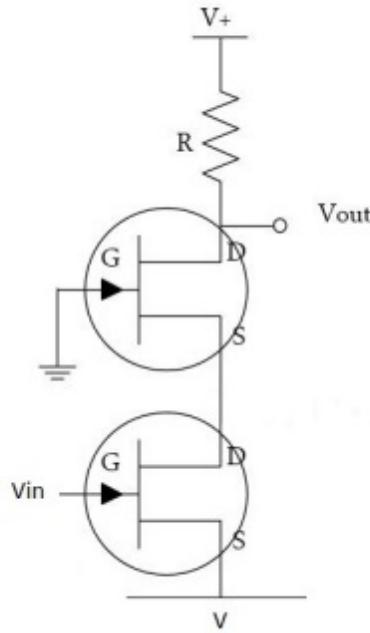

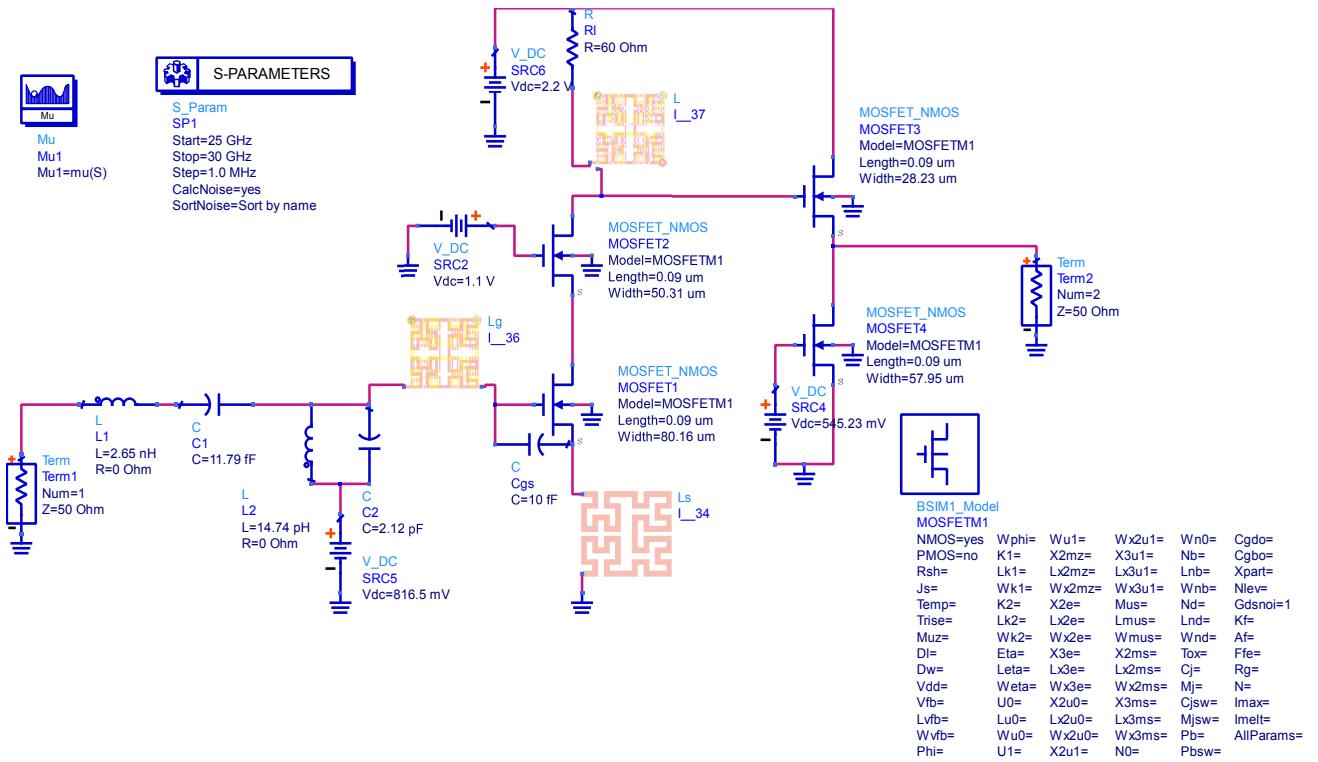

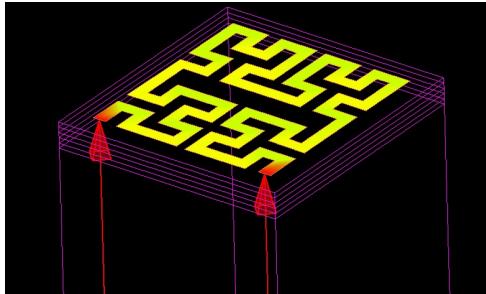

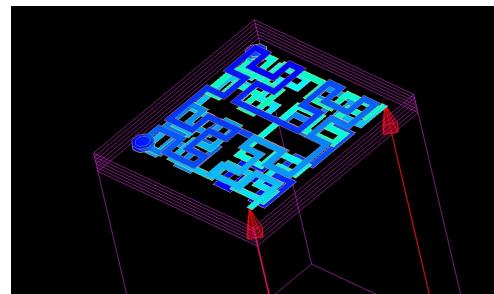

An Orthogonal Series Stacked Differential Fractal Inductor (OSSDFI) is proposed in which the consecutive metal layers have 90 degrees phase shift with one another. This kind of arrangement reduces the negative mutual inductance and parasitic capacitance between the adjacent metal layers to a larger extent. Thus, OSSDFI attains a 2-fold improvement in inductance and more than 50% improvement in Q when compared with CSSFI. A narrow band LNA using cascode topology with inductive source degeneration is designed and simulated for 5G band (27-30 GHz) applications in 90 nm CMOS technology using the tool Advanced Design System. The inductors in the LNA are replaced with the proposed high Q OSSDFI contributes to high gain, better input matching, and low noise figure compared to the state-of-the-art LNAs.

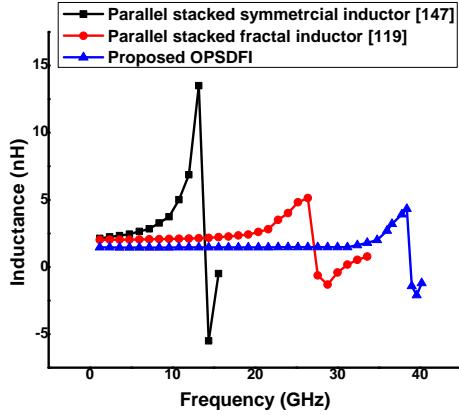

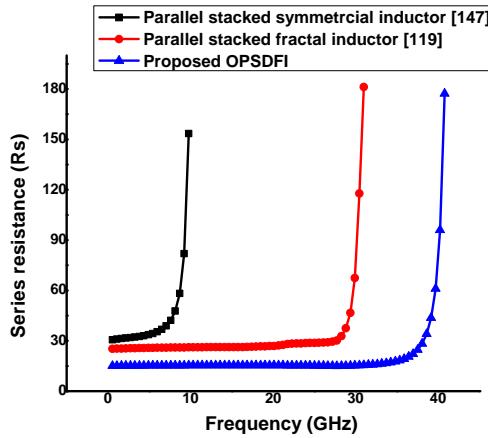

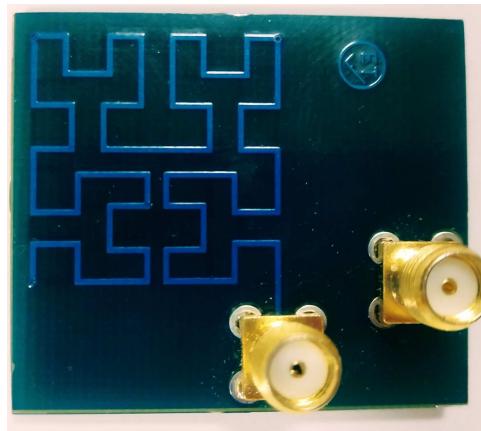

The conventional parallel stacked fractal inductor attains high Q but it suffers from low self-resonance frequency values owing to huge parasitic capacitance resultant from the adjacent metal layers. To overcome this, an orthogonal parallel stacked differential fractal inductor (OPSDFI) is proposed. Similar to OSSDFI, the OPSDFI also has the orthogonal arrangement of metal layers which reduces the adjacent layer parasitic capacitance. The metal layers in the OPSDFI are interconnected together on the four corners using vias from the top layer to the bottom layer. This kind of stacking increases the overall thickness of the inductor which in turn reduces the series resistance ( $R_s$ ). The combined effect of the decrease in series resistance and parasitic capacitance improves the Q of the proposed OPSDFI compared with the conventional parallel stacked fractal inductor.

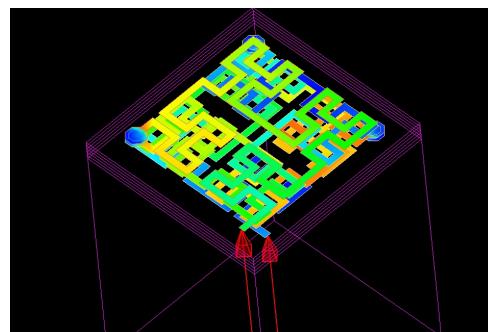

A multipath differential fractal inductor is proposed for wireless applications such as satellite, WLAN, Bluetooth, Microwave, Radar, and Cellular phone, etc. The multipath technique reduces the skin and proximity effects and improves the quality factor without any change in inductance and self-resonance frequency compared to the planar fractal inductor for the equal on-chip area.

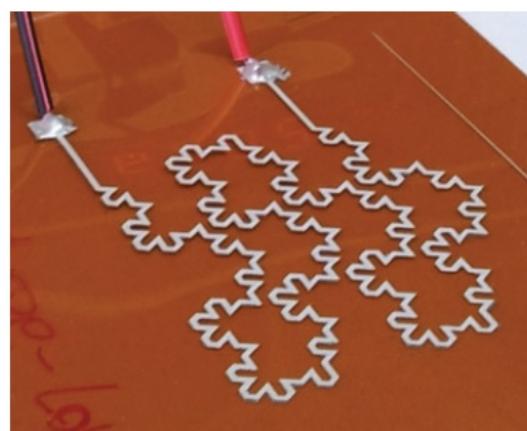

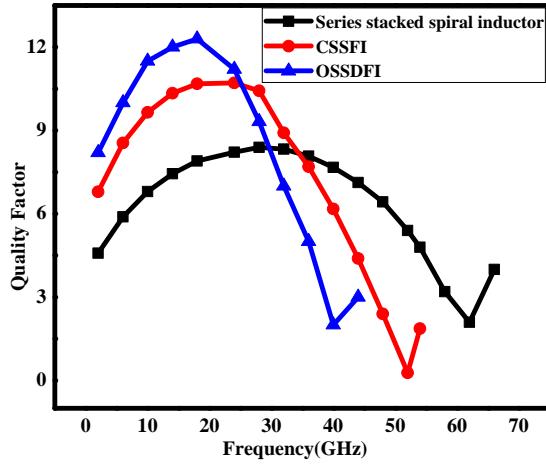

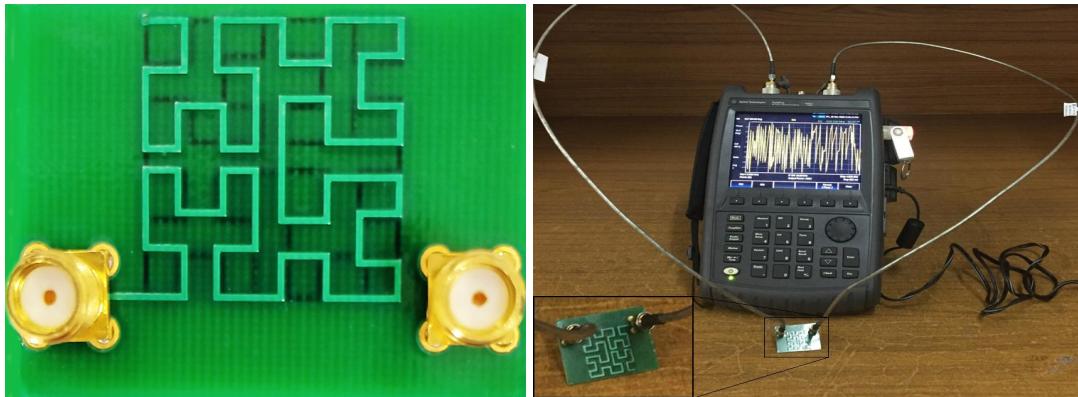

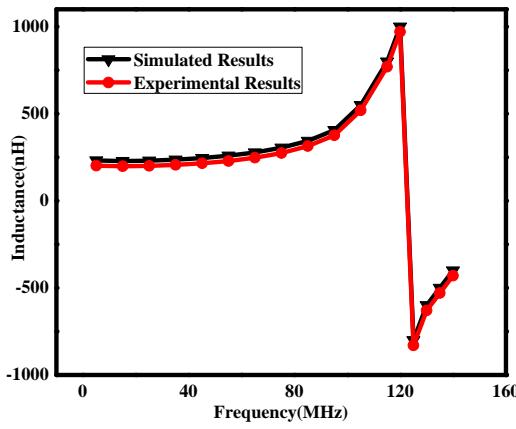

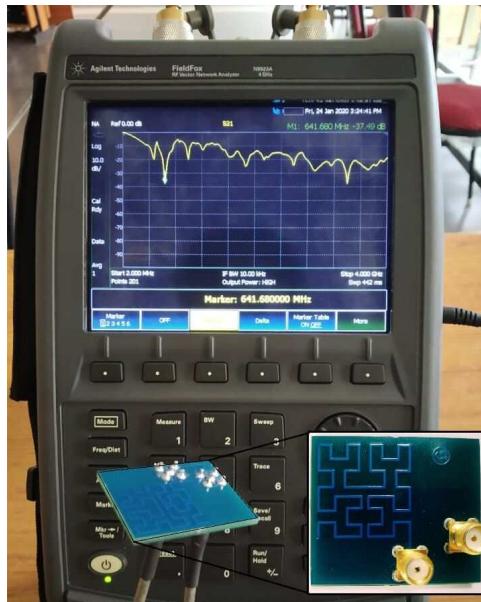

Due to the unavailability of fabrication of inductors on Silicon substrate, most of the proposed inductors are scaled down to lower frequencies (scaled up to micrometer to millimeter scale) and are fabricated on FR-4 substrate. The proposed inductors are validated experimentally using Vector Network Analyzer (VNA-N9923A) of the frequency range from 0.01GHz to 1GHz. For all the fabricated inductors, the experimental results are in good agreement with the simulated results demonstrate the robustness of the design.

# Contents

|                                                                             |              |

|-----------------------------------------------------------------------------|--------------|

| <b>Approval Sheet</b>                                                       | <b>ii</b>    |

| <b>Certificate</b>                                                          | <b>iv</b>    |

| <b>Acknowledgements</b>                                                     | <b>v</b>     |

| <b>Abstract</b>                                                             | <b>vi</b>    |

| <b>List of Figures</b>                                                      | <b>xii</b>   |

| <b>List of Tables</b>                                                       | <b>xvi</b>   |

| <b>List of Abbreviations</b>                                                | <b>xvii</b>  |

| <b>List of Symbols</b>                                                      | <b>xviii</b> |

| <b>1 Introduction</b>                                                       | <b>1</b>     |

| 1.1 Overview . . . . .                                                      | 1            |

| 1.2 On-chip inductors . . . . .                                             | 5            |

| 1.2.1 Active inductor . . . . .                                             | 5            |

| 1.2.2 Bondwire inductor . . . . .                                           | 5            |

| 1.2.3 Spiral inductor . . . . .                                             | 6            |

| 1.2.4 Impact of parasitics on the performance of on-chip inductor . . . . . | 8            |

| 1.2.5 Losses in spiral inductor . . . . .                                   | 10           |

| 1.2.6 Differential inductor . . . . .                                       | 12           |

| 1.3 On-chip capacitors . . . . .                                            | 17           |

| 1.4 Fractal curves . . . . .                                                | 19           |

| 1.4.1 Applications of fractal geometry . . . . .                            | 19           |

| 1.5 Low noise amplifier . . . . .                                           | 22           |

| 1.6 Design tool and Measurement setup . . . . .                             | 23           |

|          |                                                                              |           |

|----------|------------------------------------------------------------------------------|-----------|

| 1.7      | Motivation . . . . .                                                         | 24        |

| 1.8      | Problem statement . . . . .                                                  | 24        |

| 1.9      | Objectives . . . . .                                                         | 24        |

| 1.10     | Organization of Work . . . . .                                               | 25        |

| <b>2</b> | <b>Literature Survey</b>                                                     | <b>26</b> |

| 2.1      | Introduction . . . . .                                                       | 26        |

| 2.2      | Review on On-Chip Inductor Design . . . . .                                  | 26        |

| 2.2.1    | Conventional planar on-chip spiral inductors . . . . .                       | 27        |

| 2.2.2    | Multilayer on-chip spiral inductors . . . . .                                | 30        |

| 2.2.3    | Symmetrical planar and multilayer on-chip spiral inductors . . . . .         | 33        |

| 2.2.4    | Planar and multilayer Fractal inductors . . . . .                            | 34        |

| 2.3      | Summary . . . . .                                                            | 36        |

| <b>3</b> | <b>Multilayer spiral differential inductors</b>                              | <b>37</b> |

| 3.1      | Introduction . . . . .                                                       | 37        |

| 3.2      | Variable width series stacked differential spiral inductor . . . . .         | 37        |

| 3.2.1    | Simulation results and discussion . . . . .                                  | 38        |

| 3.3      | Variable multipath width multilayer differential inductor . . . . .          | 41        |

| 3.3.1    | Simulation results of the inductor . . . . .                                 | 42        |

| 3.4      | Series stacked non-parallel multipath differential inductor . . . . .        | 44        |

| 3.4.1    | Simulation results of the proposed inductor . . . . .                        | 45        |

| 3.5      | Summary . . . . .                                                            | 47        |

| <b>4</b> | <b>Hybrid series stacked differential fractal inductor</b>                   | <b>48</b> |

| 4.1      | Introduction . . . . .                                                       | 48        |

| 4.2      | Hilbert and Sierpinski curves . . . . .                                      | 49        |

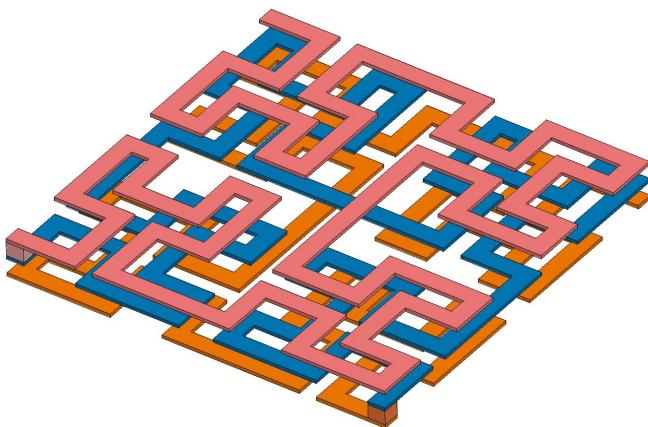

| 4.3      | Hybrid series stacked differential fractal inductor . . . . .                | 50        |

| 4.3.1    | Design and simulation of hybrid series stacked differential fractal inductor | 52        |

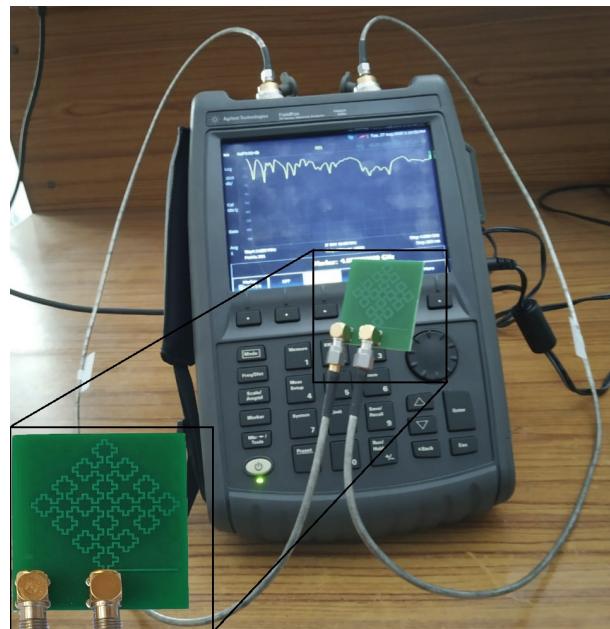

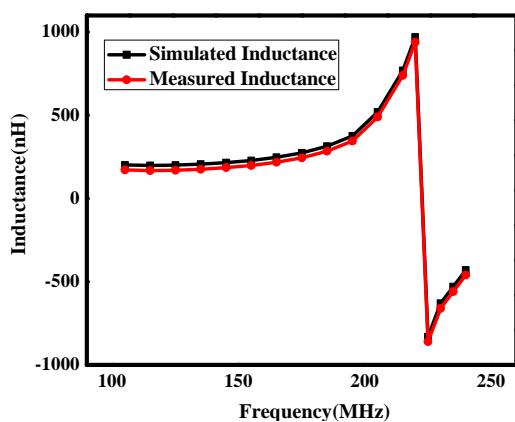

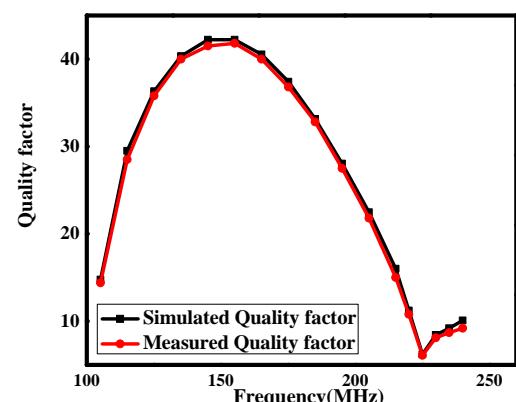

| 4.3.2    | Fabrication and Measurement results . . . . .                                | 57        |

|          |                                                                                     |           |

|----------|-------------------------------------------------------------------------------------|-----------|

| 4.4      | Summary                                                                             | 59        |

| <b>5</b> | <b>Multilayer stacked differential fractal inductors and its application in LNA</b> | <b>60</b> |

| 5.1      | Introduction                                                                        | 60        |

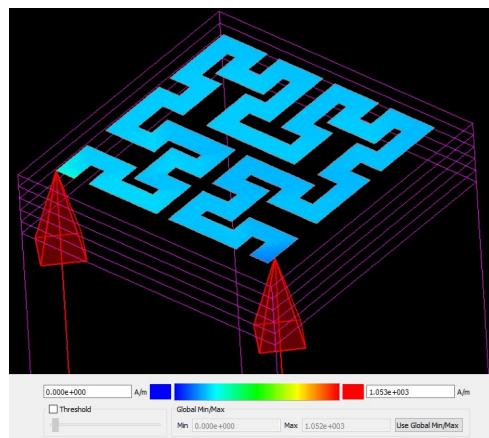

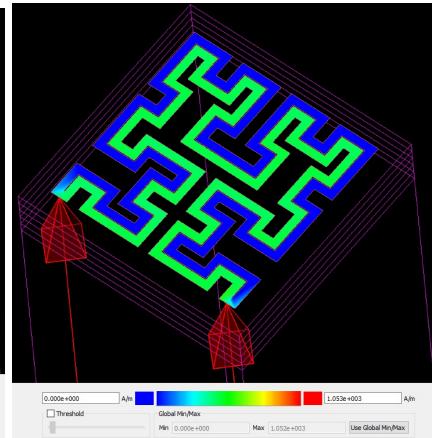

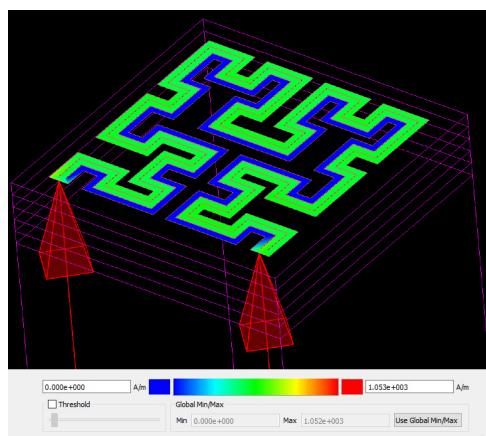

| 5.2      | Orthogonal series stacked differential fractal inductor (OSSDFI)                    | 61        |

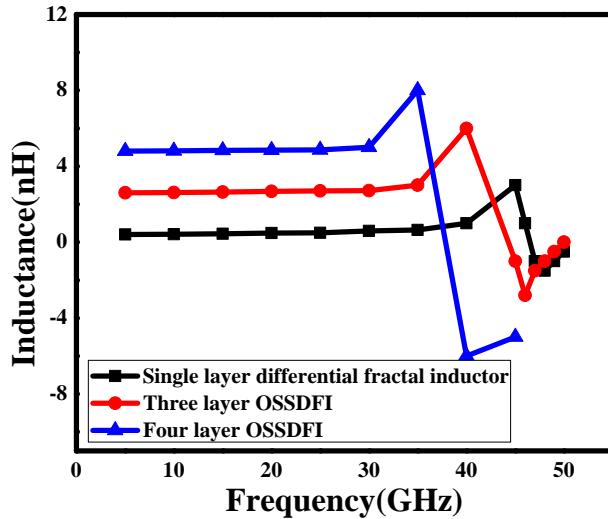

| 5.2.1    | Simulation results of the proposed OSSDFI                                           | 62        |

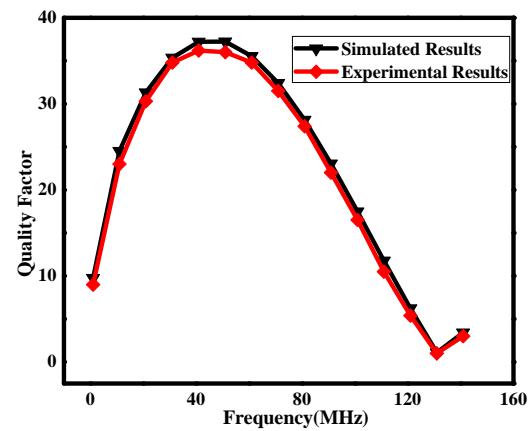

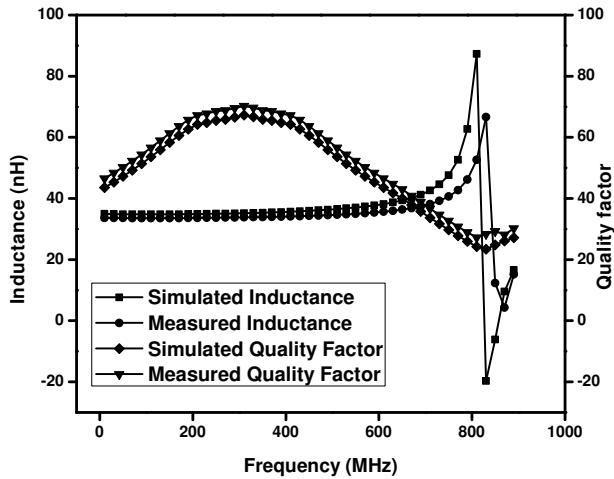

| 5.2.2    | Measurement results of the fabricated OSSDFI                                        | 63        |

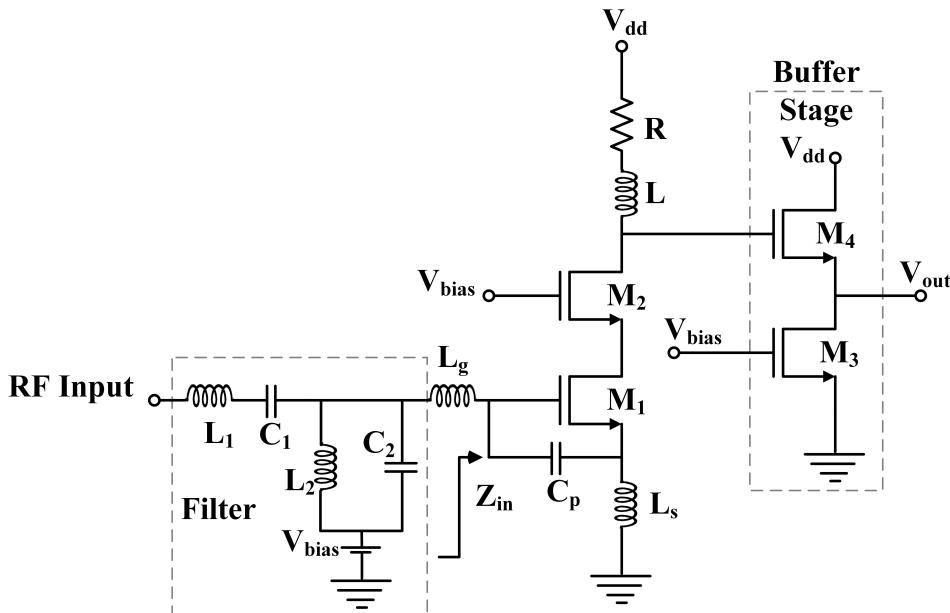

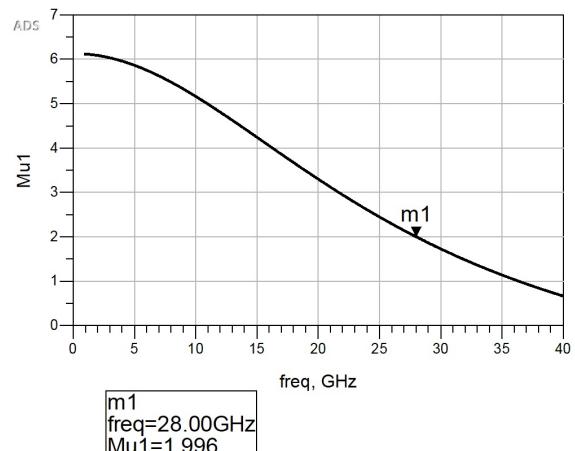

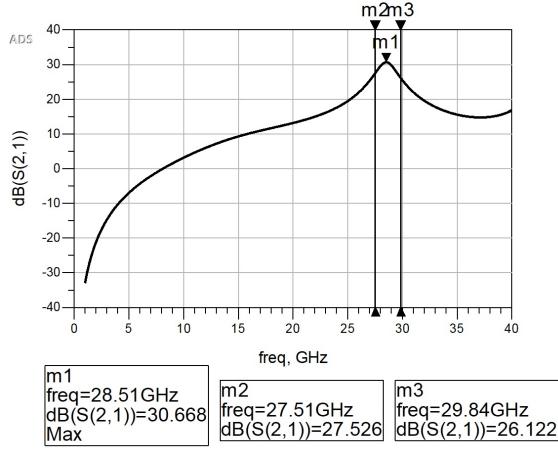

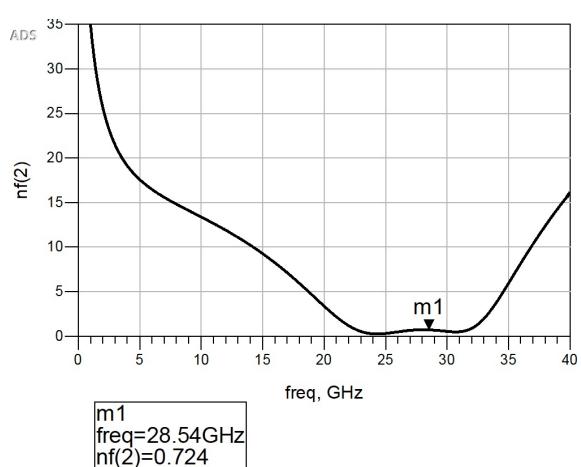

| 5.3      | Design and simulation of the LNA                                                    | 65        |

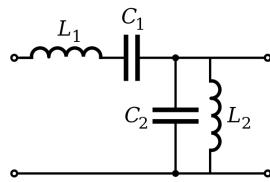

| 5.3.1    | Design of bandpass filter                                                           | 65        |

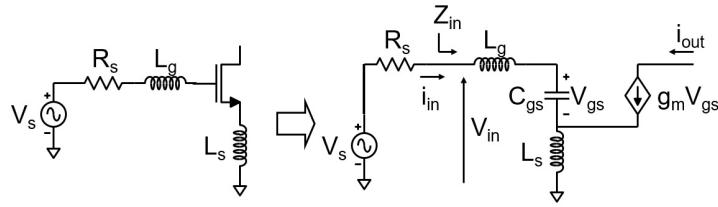

| 5.3.2    | Design of $L_s$ , $L_g$ and $C_{gs}$                                                | 66        |

| 5.3.3    | Gain of the LNA                                                                     | 68        |

| 5.3.4    | Calculation of noise figure                                                         | 68        |

| 5.3.5    | Stability                                                                           | 69        |

| 5.3.6    | Calculation of optimal width of the transistors                                     | 70        |

| 5.3.7    | Calculation of power dissipation                                                    | 70        |

| 5.3.8    | Simulation results of the LNA using OSSDFI                                          | 71        |

| 5.4      | Orthogonal parallel stacked differential fractal inductor (OPSDFI)                  | 75        |

| 5.4.1    | Simulation results and performance analysis of the proposed OPSDFI                  | 76        |

| 5.4.2    | Measurement results of the fabricated OPSDFI                                        | 78        |

| 5.5      | Summary                                                                             | 80        |

| <b>6</b> | <b>Multipath differential fractal inductor for wireless applications</b>            | <b>81</b> |

| 6.1      | Introduction                                                                        | 81        |

| 6.2      | Design and simulation of the proposed multipath differential fractal inductor       | 82        |

| 6.3      | Fabrication and measurement of results on PCB                                       | 86        |

| 6.4      | Summary                                                                             | 86        |

| <b>7</b> | <b>Conclusions And Future Scope</b>                                                 | <b>88</b> |

| 7.1      | Conclusions                                                                         | 88        |

| 7.2      | Future Scope                                                                        | 89        |

|                             |            |

|-----------------------------|------------|

| <b>References</b>           | <b>90</b>  |

| <b>List of Publications</b> | <b>104</b> |

# List of Figures

|      |                                                                                 |    |

|------|---------------------------------------------------------------------------------|----|

| 1.1  | Typical cellular phone RF front end circuit (Source-BOSCH) . . . . .            | 3  |

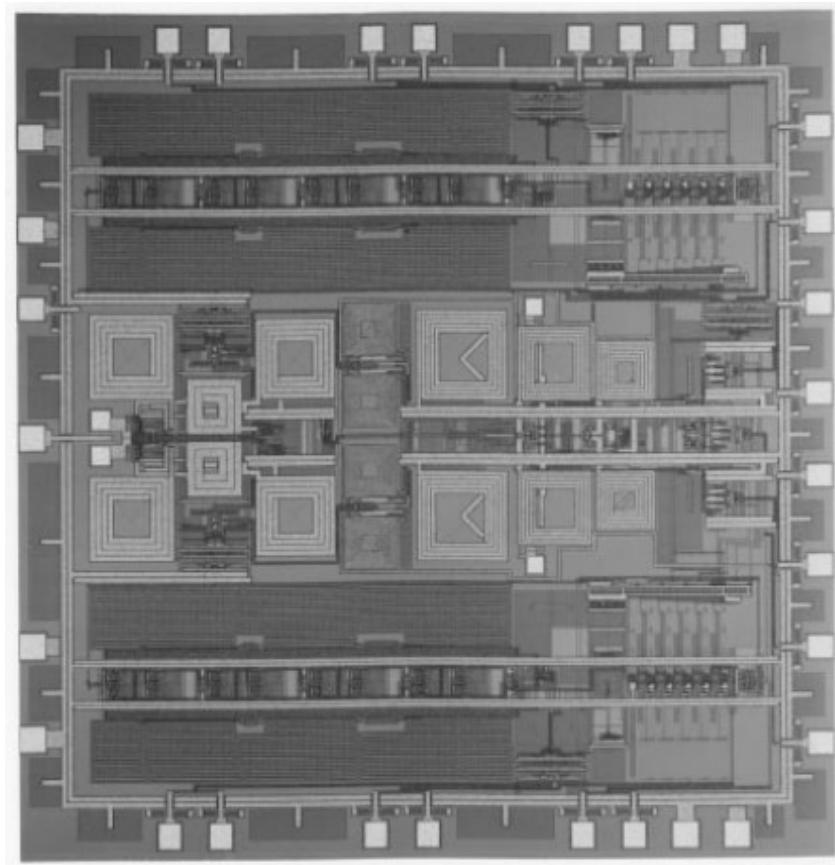

| 1.2  | A single-chip GPS receiver (Maxim Inc.) . . . . .                               | 4  |

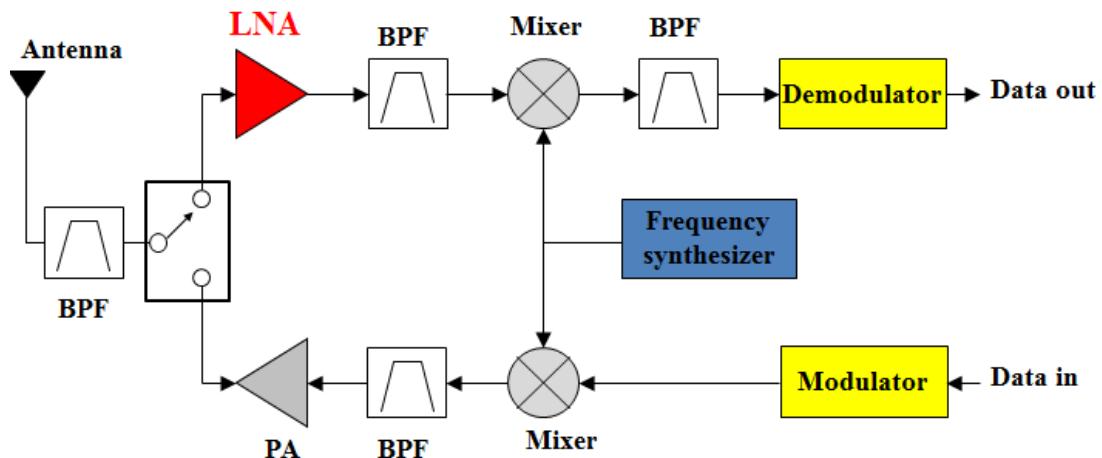

| 1.3  | RF transceiver composed of different building blocks . . . . .                  | 4  |

| 1.4  | Gyrator-C based active inductor . . . . .                                       | 5  |

| 1.5  | Interconnection of metal leads and packaged IC chip through bondwires . . . . . | 6  |

| 1.6  | Bond wire and its equivalent circuit . . . . .                                  | 6  |

| 1.7  | Performance metrics of on-chip inductor . . . . .                               | 7  |

| 1.8  | Different shapes and lateral parameters of planar spiral inductor . . . . .     | 7  |

| 1.9  | Typical $\pi$ -equivalent model of spiral inductor . . . . .                    | 8  |

| 1.10 | Substrate losses in spiral . . . . .                                            | 11 |

| 1.11 | Variation of skin and proximity effects with frequency . . . . .                | 11 |

| 1.12 | Multiple metal stacking of the inductor . . . . .                               | 13 |

| 1.13 | Asymmetrical spiral inductor . . . . .                                          | 14 |

| 1.14 | Symmetric spiral inductor using two asymmetrical spiral inductors . . . . .     | 14 |

| 1.15 | Symmetric spiral inductor . . . . .                                             | 14 |

| 1.16 | Excitation of symmetric spiral inductor . . . . .                               | 15 |

| 1.17 | Lumped equivalent circuits for different excitations . . . . .                  | 15 |

| 1.18 | Performance metrics of on-chip capacitor . . . . .                              | 17 |

| 1.19 | MIM capacitor . . . . .                                                         | 18 |

| 1.20 | MEMS capacitor . . . . .                                                        | 18 |

| 1.21 | Natural fractal curves . . . . .                                                | 20 |

| 1.22 | Mathematical fractal curves . . . . .                                           | 21 |

| 1.23 | Fractal inductor . . . . .                                                      | 21 |

| 1.24 | Fractal capacitor . . . . .                                                     | 21 |

|      |                                                                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

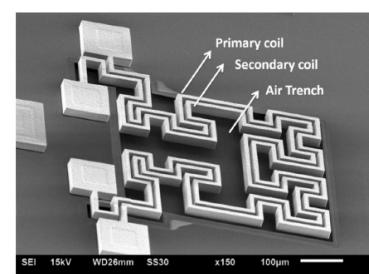

| 1.25 | Fractal transformer                                                                                                          | 21 |

| 1.26 | Block diagram of LNA                                                                                                         | 23 |

| 1.27 | Common source                                                                                                                | 23 |

| 1.28 | Common gate                                                                                                                  | 23 |

| 1.29 | Cascode LNA                                                                                                                  | 24 |

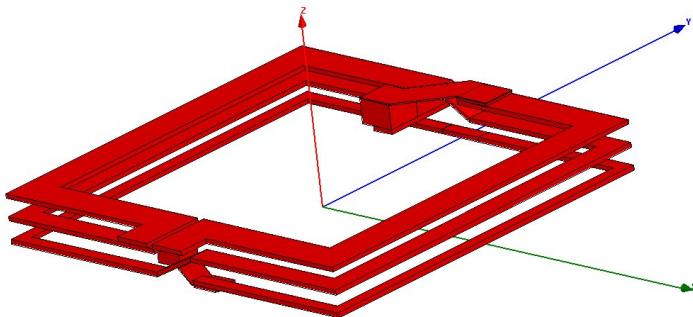

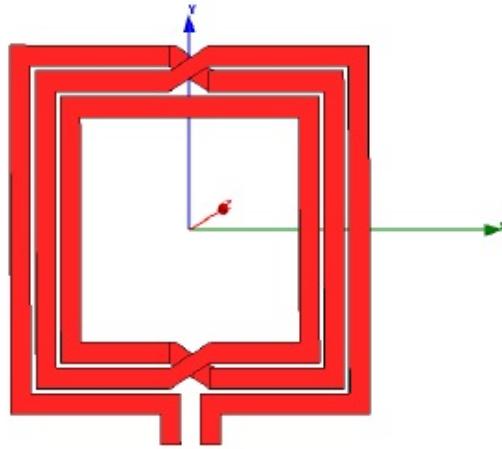

| 3.1  | Proposed variable width series stacked differential inductor                                                                 | 38 |

| 3.2  | Standard planar differential inductor                                                                                        | 39 |

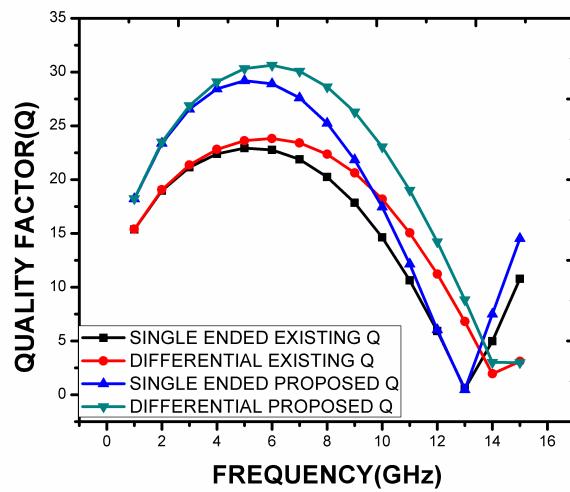

| 3.3  | Comparison of Q for single-ended and differential excitation for the existing planar and proposed differential inductors     | 39 |

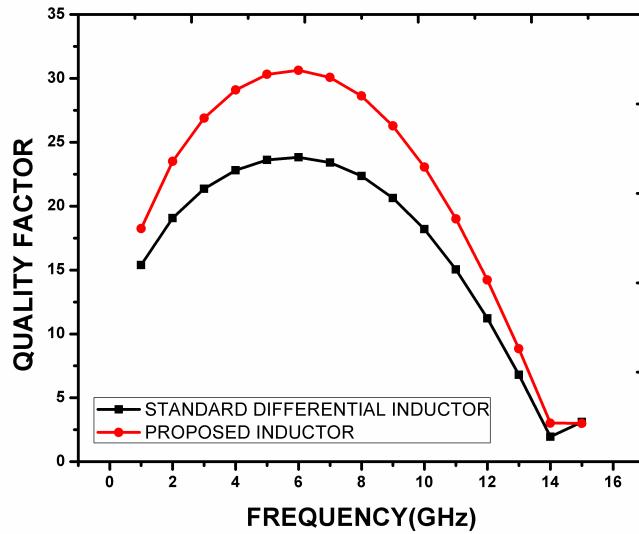

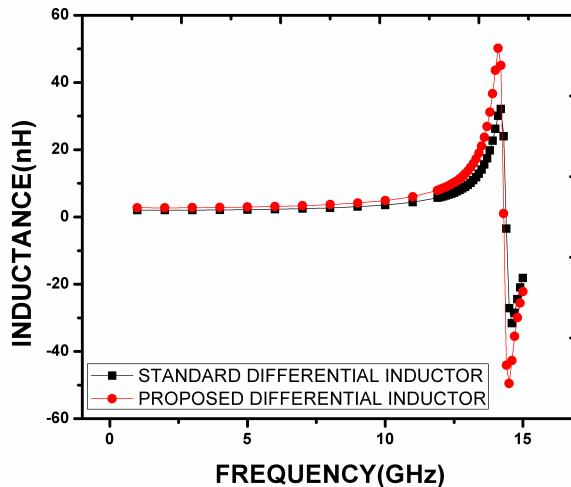

| 3.4  | Comparison of Q for the planar and proposed differential inductors                                                           | 40 |

| 3.5  | Comparison of inductance for the planar and proposed differential inductors                                                  | 40 |

| 3.6  | Proposed variable multipath width multilayer differential inductor                                                           | 42 |

| 3.7  | Comparison of Q                                                                                                              | 43 |

| 3.8  | Comparison of self-resonance frequency                                                                                       | 44 |

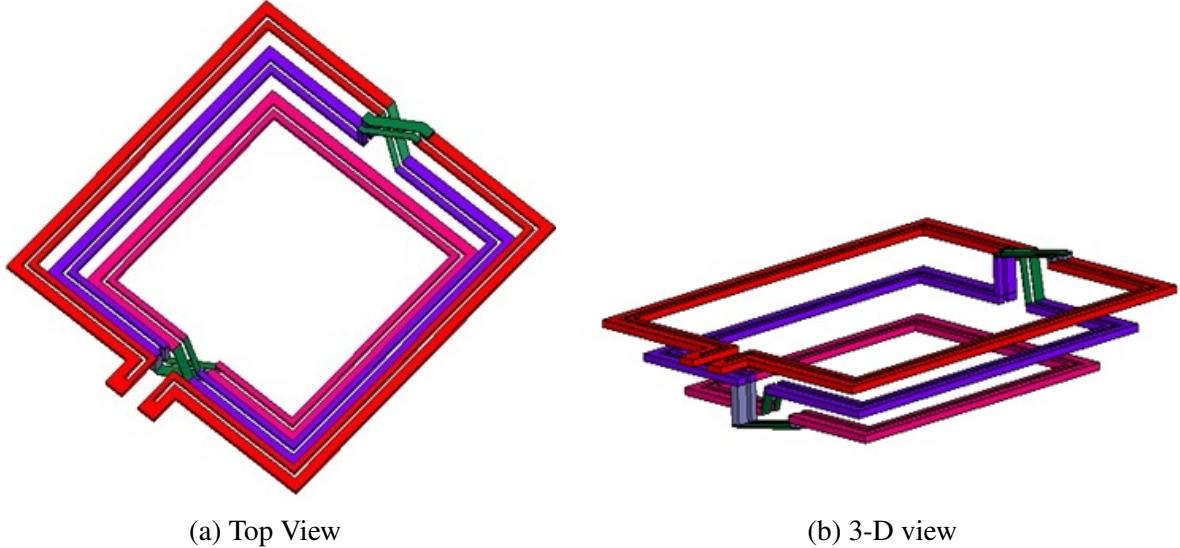

| 3.9  | Proposed series stacked non parallel multipath differential inductor                                                         | 45 |

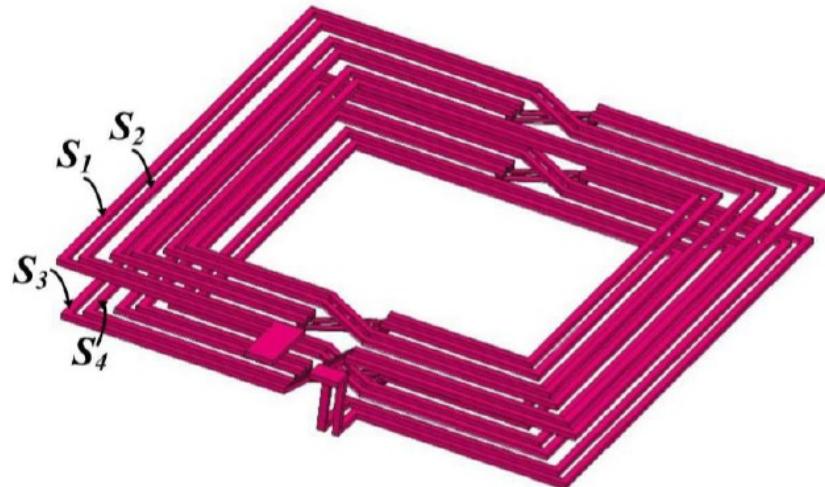

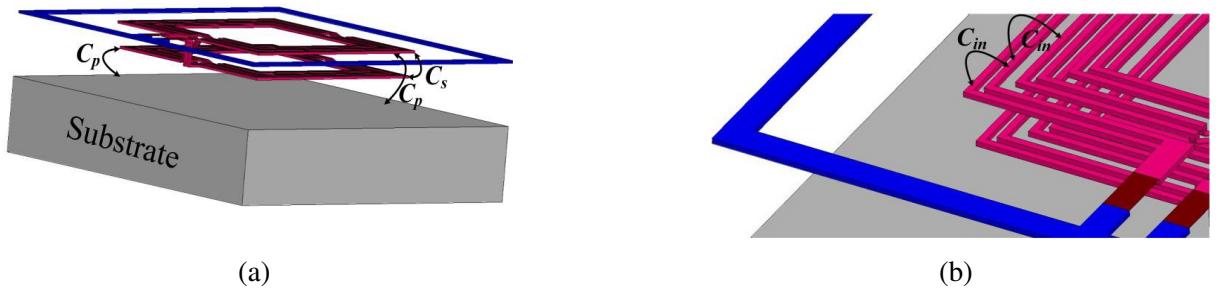

| 3.10 | (a) Partition of conductor width (b) Non parallel metal layers                                                               | 45 |

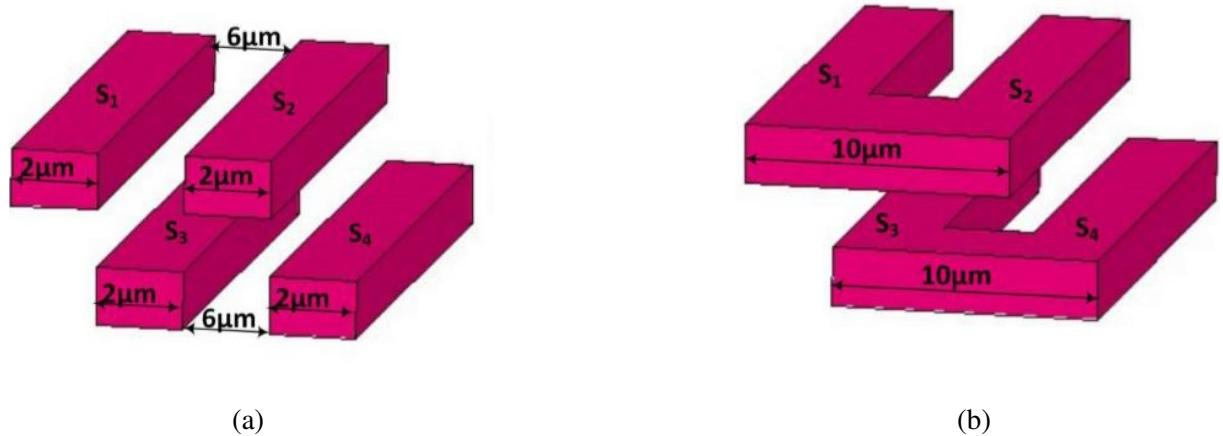

| 3.11 | (a) interlayer capacitance ( $C_s$ ) and metal to substrate capacitance ( $C_p$ ) (b) inter-winding capacitance ( $C_{in}$ ) | 46 |

| 3.12 | Comparison of Q                                                                                                              | 46 |

| 3.13 | Comparison of inductance                                                                                                     | 46 |

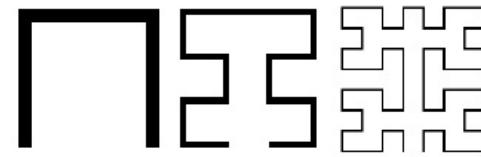

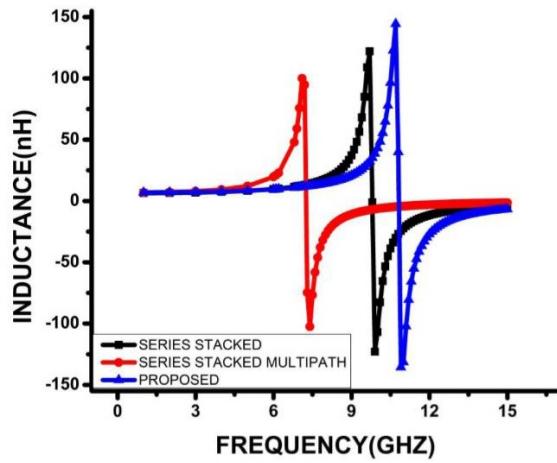

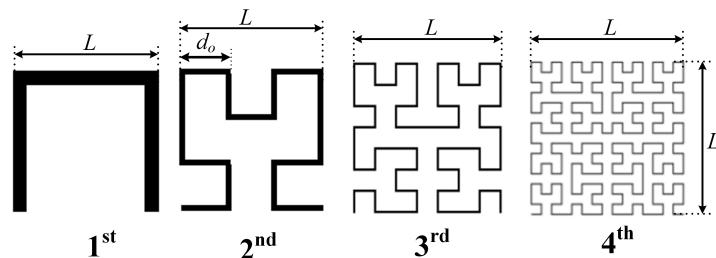

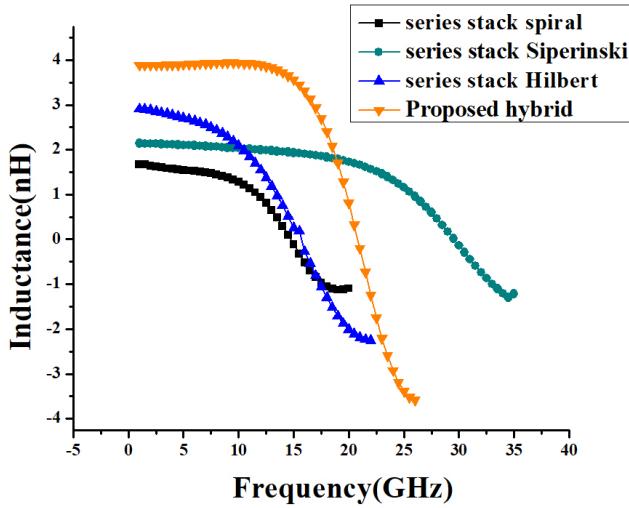

| 4.1  | Order of the Hilbert curves                                                                                                  | 49 |

| 4.2  | Order of the Sierpinski curves                                                                                               | 50 |

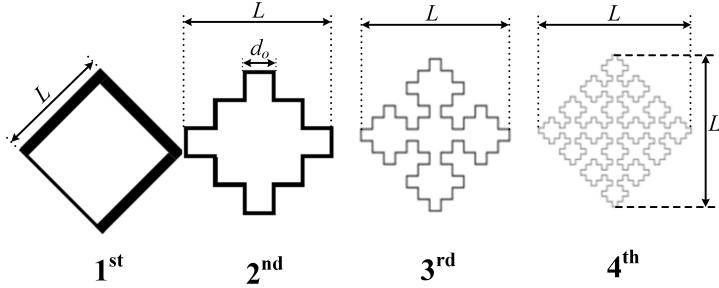

| 4.3  | Series stacked fractal inductor using Sierpinski curve                                                                       | 51 |

| 4.4  | Series stacked fractal inductor using Hilbert curve                                                                          | 51 |

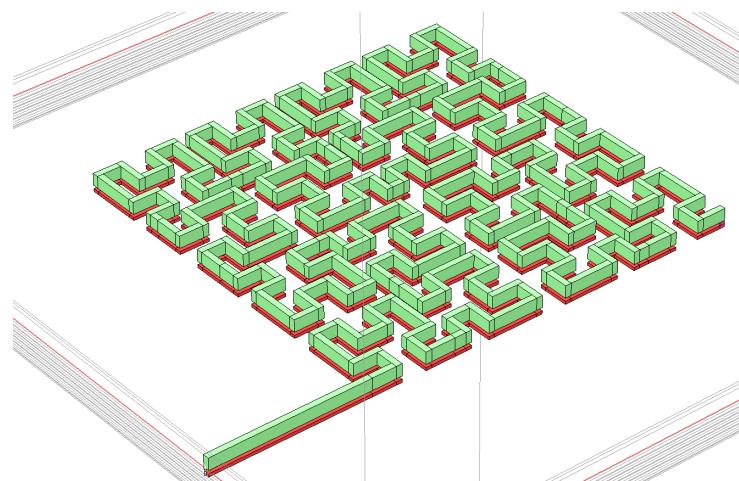

| 4.5  | Proposed hybrid series stacked differential fractal inductor                                                                 | 51 |

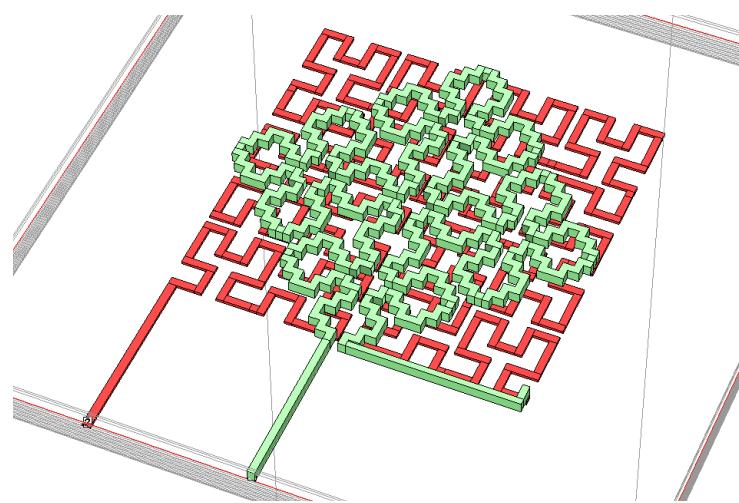

| 4.6  | Technology parameters and metal stack for 180 nm process                                                                     | 53 |

| 4.7  | $2^{nd}$ IO (IF=200 $\mu$ m, ID=66 $\mu$ m ).                                                                                | 53 |

|      |                                                                            |    |

|------|----------------------------------------------------------------------------|----|

| 4.8  | $3^{rd}$ IO (IF=200 $\mu$ m, ID=28 $\mu$ m ) . . . . .                     | 53 |

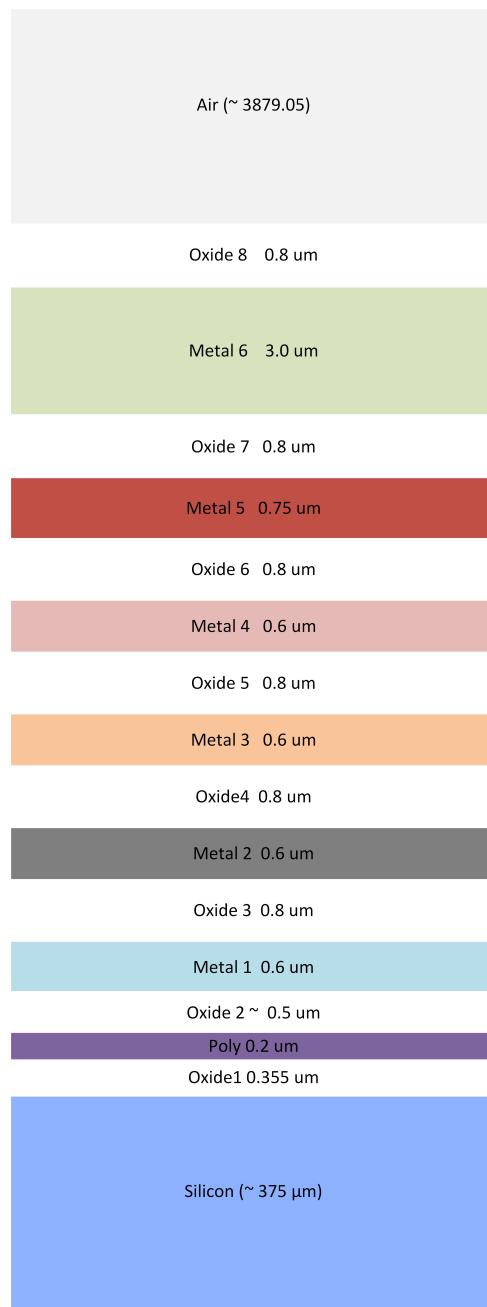

| 4.9  | Comparison of inductance . . . . .                                         | 54 |

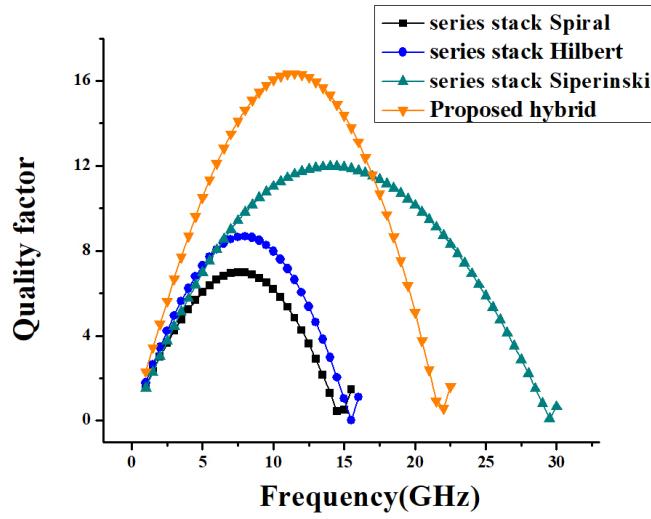

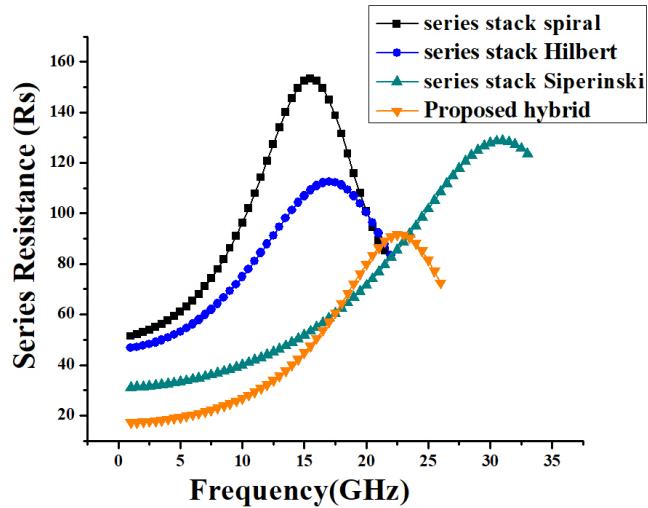

| 4.10 | Comparison of Q . . . . .                                                  | 55 |

| 4.11 | Comparison of series resistance . . . . .                                  | 55 |

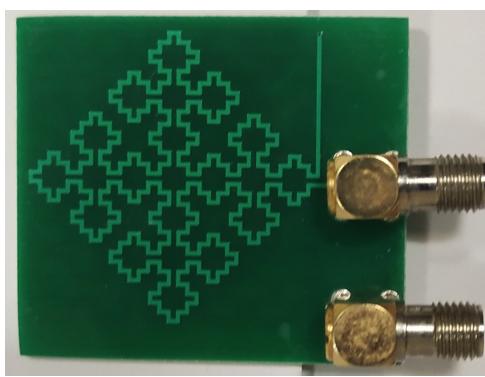

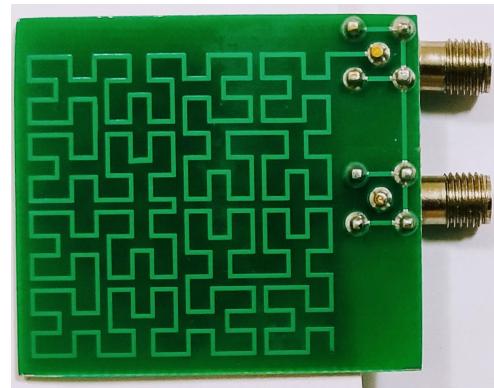

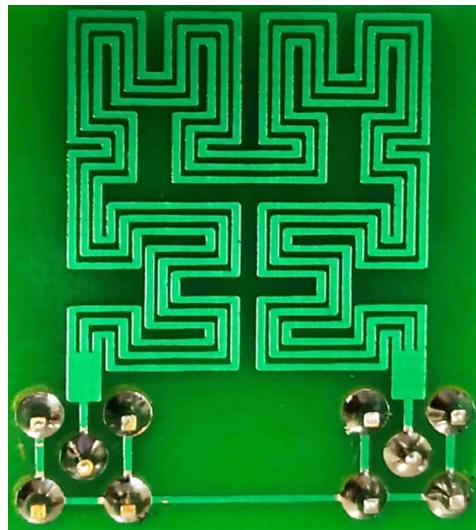

| 4.12 | Fabricated inductor top view . . . . .                                     | 58 |

| 4.13 | Fabricated inductor bottom view . . . . .                                  | 58 |

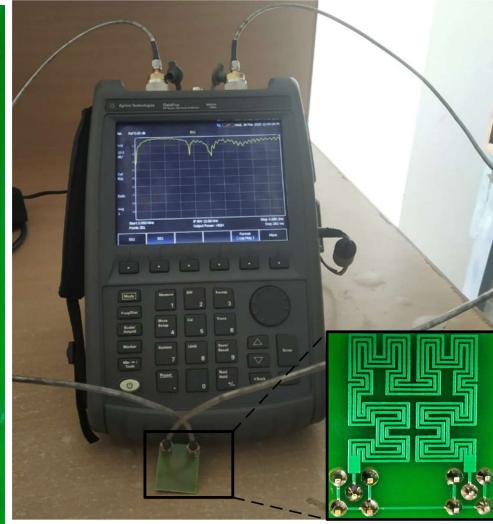

| 4.14 | Measurement of results using network analyzer . . . . .                    | 58 |

| 4.15 | Simulated and measured L (nH) . . . . .                                    | 58 |

| 4.16 | Simulated and measured Q . . . . .                                         | 58 |

| 5.1  | Proposed orthogonal series stacked differential fractal inductor . . . . . | 61 |

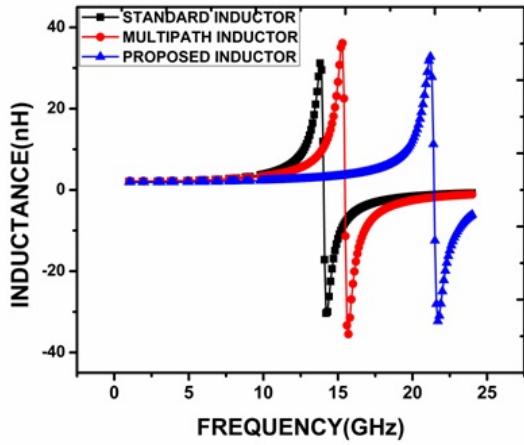

| 5.2  | Comparison of inductance . . . . .                                         | 62 |

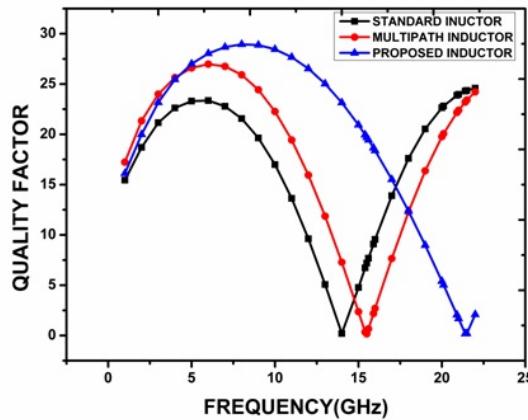

| 5.3  | Comparison of quality factor . . . . .                                     | 63 |

| 5.4  | OSSDFI fabricated on Multilayer PCB . . . . .                              | 64 |

| 5.5  | Experimentation using Network Analyzer . . . . .                           | 64 |

| 5.6  | Simulated and measured inductance . . . . .                                | 64 |

| 5.7  | Simulated and measured Q . . . . .                                         | 64 |

| 5.8  | Cascode LNA with inductive source degeneration . . . . .                   | 65 |

| 5.9  | LC band pass filter . . . . .                                              | 66 |

| 5.10 | Input equivalent circuit of inductive degeneration architecture . . . . .  | 67 |

| 5.11 | Inductive source degeneration LNA using proposed OSSDFI . . . . .          | 72 |

| 5.12 | Single layer ( $L_s$ ) . . . . .                                           | 72 |

| 5.13 | Three layer ( $L_g$ ) . . . . .                                            | 72 |

| 5.14 | Four layer L . . . . .                                                     | 72 |

| 5.15 | Simulated inductances for multilayer OSSDFI . . . . .                      | 73 |

| 5.16 | Input matching . . . . .                                                   | 74 |

| 5.17 | Noise figure . . . . .                                                     | 74 |

|      |                                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 5.18 | Gain                                                                                                      | 74 |

| 5.19 | Stability factor                                                                                          | 74 |

| 5.20 | Orthogonal parallel stacked differential fractal inductor                                                 | 76 |

| 5.21 | Simulation of the proposed OPSDFI (On-chip area= $200\text{ }\mu\text{m} \times 200\text{ }\mu\text{m}$ ) | 77 |

| 5.22 | Q plots                                                                                                   | 77 |

| 5.23 | Inductance plots                                                                                          | 78 |

| 5.24 | Series resistance plots                                                                                   | 78 |

| 5.25 | Fabricated OPSDFI on multilayer PCB                                                                       | 79 |

| 5.26 | Measurement of results using VNA                                                                          | 79 |

| 5.27 | Comparison of measured and simulated results                                                              | 80 |

| 6.1  | Conventional fractal                                                                                      | 82 |

| 6.2  | 2-path inductor                                                                                           | 82 |

| 6.3  | 3-path inductor                                                                                           | 82 |

| 6.4  | 4-path inductor                                                                                           | 82 |

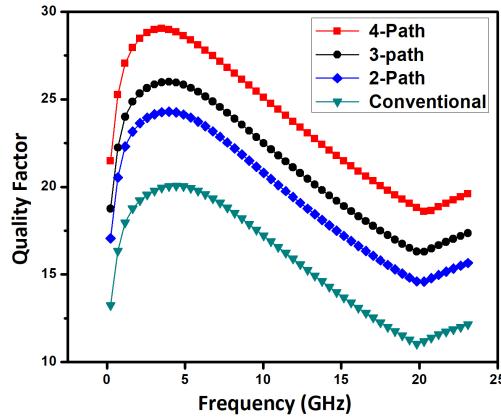

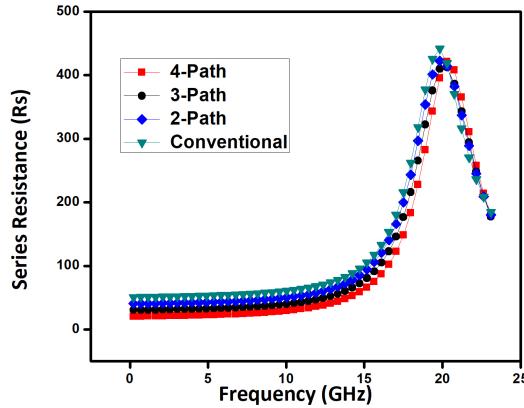

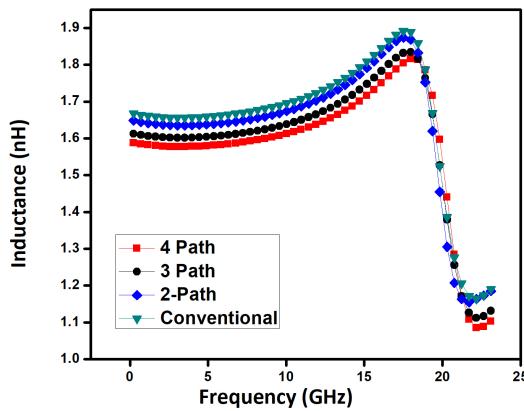

| 6.5  | Relation between quality factor and multiple paths                                                        | 84 |

| 6.6  | Relation between series resistance and multiple paths                                                     | 84 |

| 6.7  | Relation between inductance and multiple paths                                                            | 84 |

| 6.8  | Fabricated inductor                                                                                       | 87 |

| 6.9  | Measurement of results                                                                                    | 87 |

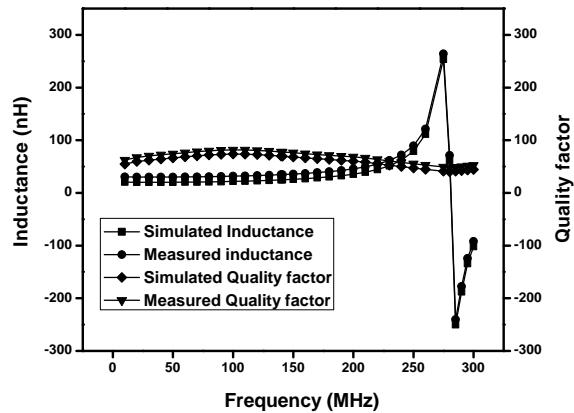

| 6.10 | Comparison of simulated and measured results                                                              | 87 |

# List of Tables

|     |                                                                                       |    |

|-----|---------------------------------------------------------------------------------------|----|

| 3.1 | Comparison of simulated values for the proposed and planar differential inductors     | 41 |

| 3.2 | Comparison of simulated values for the proposed and planar differential inductors     | 43 |

| 3.3 | Comparison of simulated values for the proposed and planar differential inductors     | 47 |

| 4.1 | Illustration of length of the curve                                                   | 50 |

| 4.2 | Performance metrics for proposed inductor with different iteration orders             | 52 |

| 4.3 | Performance comparison of the proposed inductor with existing state-of-the-art        | 57 |

| 4.4 | Simulated results vs Measured results                                                 | 57 |

| 5.1 | Performance comparison of the proposed inductor with existing state-of-the-art        | 63 |

| 5.2 | Simulated results vs Measured results                                                 | 64 |

| 5.3 | Design specifications of LNA                                                          | 66 |

| 5.4 | Designed component values of LNA operating at center frequency                        | 71 |

| 5.5 | Comparison of designed and simulated inductances                                      | 73 |

| 5.6 | Performance summary and comparison of the proposed LNA with state-of-the-art LNAs     | 75 |

| 5.7 | State-of-the-art comparison of the proposed inductor                                  | 78 |

| 5.8 | Measured results vs Simulated results                                                 | 80 |

| 6.1 | Comparison of the proposed multipath fractal inductor with state-of-the-art inductors | 85 |

| 6.2 | Measured results vs Simulated results                                                 | 86 |

# List of Abbreviations

|              |                                                        |

|--------------|--------------------------------------------------------|

| <b>3D</b>    | Three Dimensional                                      |

| <b>AMS</b>   | Analog/mixed signal                                    |

| <b>ADS</b>   | Advanced Design System                                 |

| <b>BPF</b>   | Band Pass Filter                                       |

| <b>CMOS</b>  | Complementary Metal Oxide Semiconductor                |

| <b>EM</b>    | Electro Magnetic                                       |

| <b>FOM</b>   | Figure of merit                                        |

| <b>IC</b>    | Integrated Circuit                                     |

| <b>LNA</b>   | Low Noise Amplifier                                    |

| <b>MIM</b>   | Metal Insulator Metal                                  |

| <b>MOM</b>   | Metal Oxide Metal                                      |

| <b>PCB</b>   | Printed Circuit Board                                  |

| <b>PGS</b>   | Patterned Ground Shield                                |

| <b>PBG</b>   | Photonic Band Gap                                      |

| <b>RF</b>    | Radio Frequency                                        |

| <b>SoC</b>   | System On Chip                                         |

| <b>SDSSI</b> | Symmetrical Trace Differential Stacked Spiral Inductor |

| <b>VCO</b>   | Voltage Controlled Oscillator                          |

| <b>VNA</b>   | Vector Network Analyzer                                |

| <b>WLAN</b>  | Wireless Local Area Network                            |

# List of Symbols

$\mu\text{m}$  Micro Meter

$nH$  Nano Henry

$pF$  Pico Farad

$Q$  Quality Factor

$\varepsilon$  Epsilon

$\eta$  Eta

# Chapter 1

## Introduction

### 1.1 Overview

The rapid evolution of wireless and mobile communication demands a low cost, high integration level, small volume on-chip passive components in the implementation of the receiver and transmitter. The on-chip passive components were first proposed in the 1990s, a significant amount of research was published in the literature [1, 2]. These passive components are listed as capacitors, inductors, and resistors. Most of the wireless applications necessitate the integration of multiple functions like a personal digital assistant, video game, phone, web browser, email, digital camera, etc. This has motivated the researchers to integrate digital, analog/mixed-signal (AMS) modules on a single chip to realize the Radio Frequency (RF)/mixed-signal system-on-chip (SoC) [3, 4]. The main obstacle is the integration of passive components in the realization of an SoC. Applying Moore's law active components (CMOS transistors) are successfully scaled-down to increase the component density that reduce the die size. However, the passive components cannot be scaled down as fast as the active components due to specific capacitance, resistance, and impedance levels necessary to process the analog signal.

Passive components are chosen depending on the frequency of operation of the circuit and the type of connection. For low frequency of operation, passive devices can be connected externally. As frequency increases, the parasitic effect on devices will degrade the characteristics of passive components [5]. When the frequency of operation of an RF circuits increases, the values of inductances in it needs to be reduced and it's not possible to have such small inductance value by externally connected inductors [6]. For example, to design a voltage-controlled

oscillator (VCO) of 10 MHz an inductance of several  $\mu\text{H}$ , is needed. However, a 10 GHz VCO needs an inductance in the order of 1 nH. It is quite difficult to design such small inductance externally since the package pin and bond wire associated inductance can exceed 1nH. As a result, on-chip passive components that offer small inductance values are commonly used in RF and mm-wave applications.

In a typical PCB (Printed Circuit Board) of the RF front end, the passive components count is higher than the active components. For example, in an Ericson cell phone board active to passive component ratio is 1 : 21 [7]. The RF-front end WLAN (Wireless Local Area Network) transceiver developed by Maxim Integrated Products (MAX2820) for IEEE 802.11b applications has a passive component count of 33 capacitors, 4 resistors, and 4 inductors [8]. In a typical cell phone, RF front end as shown in Fig.1.1, the 85% of the passive component count occupies 70% of board area with 60% of board cost [9]. A single GPS (Global Positioning System) receiver developed by Maxim Integrated Products (MAX 2742) as shown in Fig.1.2 has more than 10 inductors which occupy about 25% of the board area [10]. Thus, the board area occupied by the passive components should be minimized to reduce the board cost and also to improve the frequency of operation. The passive component count will be reduced with the advancement in fabrication technology, time to market, and domain of the application. Thus, the realization of low cost and high-performance RF systems depends on the integration of passive components.

High-quality passive components are vital in the implementation of transceivers aimed for mm-wave communication as shown in Fig.1.3, for implementation of critical building blocks such as filters, transformers, low-noise amplifiers, power amplifiers, and oscillators. The on-chip inductor is the important passive component amongst the on-chip passive components [11]. The on-chip inductor's performance is determined based on quality factor (Q), self-resonance frequency ( $f_{SR}$ ), inductance (L), and on-chip area. In the present scenario due to advancements in RF-VLSI technology, the demand for high-performance inductors in terms of high Q, high  $f_{SR}$ , and optimal inductance with a small on-chip area is increased.

Depending on the design technology on-chip inductors are mainly classified into three types which are active inductors, bond wire inductors, and spiral inductors. Bond wire inductors have an exceptionally high-quality factor (typically, 20–50), but they are not unsuitable for RF applications due to unwanted coupling with the other devices [12]. The active inductors are formed using transistors and other active components [13]. The advantages of active inductors are high-quality factor, high frequency of operation, better tuning capability, ease of fabrication,

Figure 1.1: Typical cellular phone RF front end circuit (Source-BOSCH)

and occupies the small on-chip area. The drawbacks of active inductors are limitations on coupling, high power consumption, and high noise interference.

Planar inductors are highly compatible with the IC interconnect scheme. Some of the planar inductors structures are loop [14], meander [15], and spiral [16]. The spiral inductor is considered to be the best choice due to its large positive mutual inductance, robustness, and ease of design. The performance of spiral inductors is degraded owing to substrate losses and metal losses. These losses limit the  $Q$  of the spiral inductor. Symmetrical spiral inductor with differential excitation known as differential inductor [17] improves the  $Q$  and  $f_{SR}$  as they are less affected by substrate parasitics. Differential inductors exhibit better noise rejection and robustness, which is vital in transceivers. Application of fractal curves in the implementation of inductor achieves higher inductance for the miniaturized on-chip area [18]. The thesis focuses on improving the performance of the multilayer differential spiral inductors as well as differentially excited multilayer fractal inductors which will be useful for RF and mm-wave applications.

Figure 1.2: A single-chip GPS receiver (Maxim Inc.)

Figure 1.3: RF transceiver composed of different building blocks

## 1.2 On-chip inductors

### 1.2.1 Active inductor

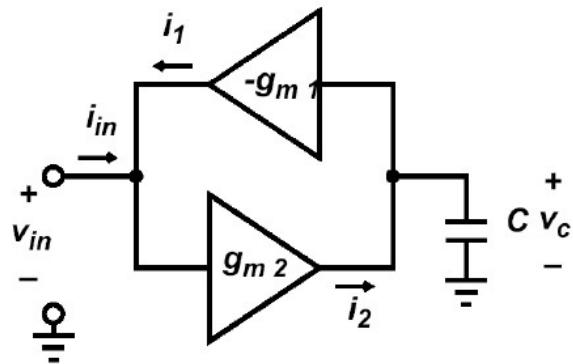

Active inductors were designed using an operational amplifier (Op-Amp) and Gyrator-C based techniques. The Op-Amp based active inductor operates at low frequencies (up to 100 MHz), and it utilizes a large on-chip area and experiences non-linearity problems [19]. In contrast to this Gyrator-C based active inductor shown in Fig.1.4 operates at sub GHz to few GHz frequency range, and it occupies the small on-chip area, provides good linearity with high tunability [20]. The drawbacks of an active inductor are poor noise performance and high power consumption. The effective inductance ( $L_{eff}$ ) of an active inductor is expressed using Eq.1.1

$$L_{eff} = \frac{C}{g_{m1}g_{m2}} \quad (1.1)$$

Where  $g_m$  is the transconductance of gain blocks and 'C' is the capacitance of the passive capacitor.

Figure 1.4: Gyrator-C based active inductor

### 1.2.2 Bondwire inductor

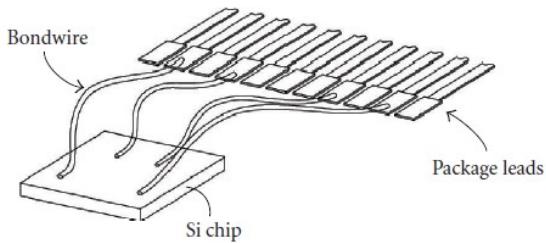

In 1995, Craninckx and Steyaert first explored on-chip bond wire inductors in RF integrated circuits [21]. Bond wires are used to make connections between a chip and an IC package has shown in Fig.1.5, and typically it offers an inductance of several nH and a resistance of several to several tens of mΩ. In general, bond wires are made of gold with a diameter of

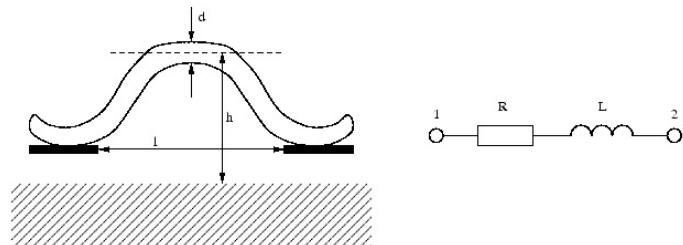

about 25 to 250  $\mu\text{m}$  and typical length of 2-5 mm. The series resistance of the bondwire inductors is very small, therefore it offers high quality factor typically 30 to 60. The performance of the bondwire inductor depends on length of the wire ( $l$ ), diameter ( $d$ ), height of the substrate ( $h$ ), and frequency of operation. The physical dimensions and equivalent circuit of bondwire inductor has shown in Fig.1.6,

Figure 1.5: Interconnection of metal leads and packaged IC chip through bondwires

Figure 1.6: Bond wire and its equivalent circuit

The size of the bond wire is typically  $100 \mu\text{m} \times 100 \mu\text{m}$ , which introduce considerable parasitic capacitance and resistance due to underpass oxide layer and silicon. Due to these constraints bond wire inductors operation at higher-order frequencies is limited in terms of the quality factor, inductance, and self-resonance frequency.

### 1.2.3 Spiral inductor

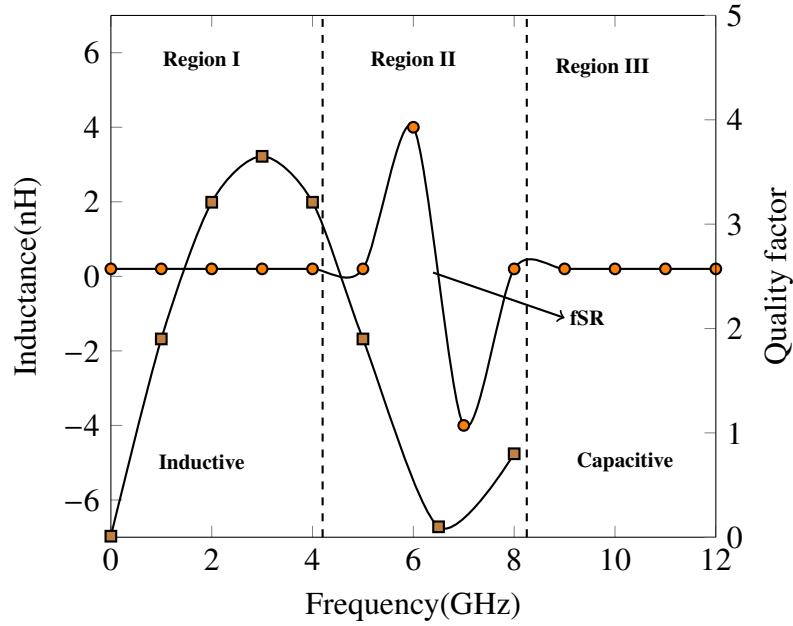

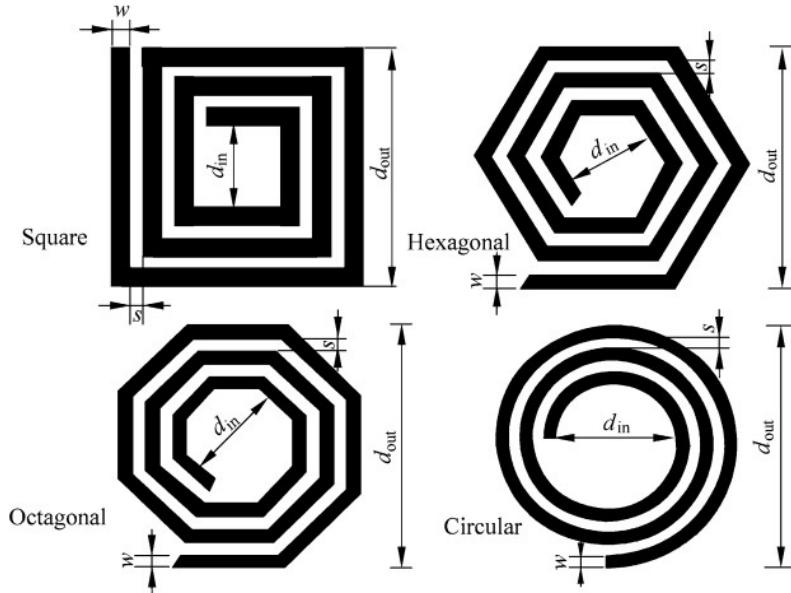

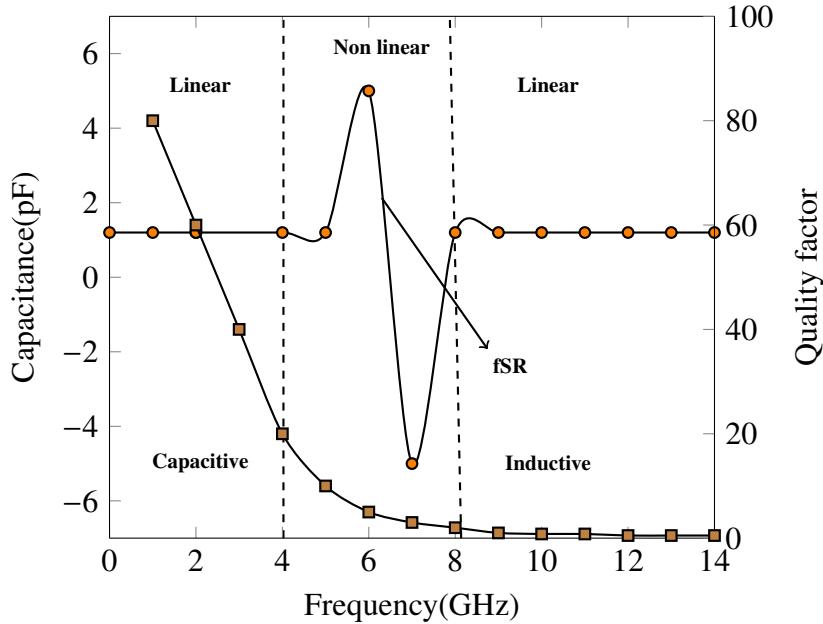

The spiral inductor design shapes are circular, octagonal, hexagonal, and square. Among them, square, rectangle, and octagonal inductors are used most frequently in the circuits due to high Q and effective utilization of the on-chip area. The performance metrics such as inductance, quality factor, and self-resonance frequency are shown in Fig. 1.7. From Fig. 1.7, region I is considered as an inductive region. The frequency at which the Q value becomes '0' is known as self-resonance frequency ( $f_{SR}$ ) of the inductor, after the ( $f_{SR}$ ), the inductor behaves like a capacitor. The Q, L, and  $f_{SR}$  greatly affected by many parameters. Those parameters are classified into design-controlled parameters and process-controlled parameters. The design controlled parameters of the spiral inductor are also known as lateral parameters which are

Figure 1.7: Performance metrics of on-chip inductor

known as inner diameter ( $d_{in}$ ), outer diameter ( $d_{out}$ ), the width of the conductor ( $w$ ), the spacing between the adjacent conductors ( $s$ ), and the number of turns ( $n$ ). Different shapes of planar spiral inductors and the lateral parameters are shown in Fig.1.8.

Figure 1.8: Different shapes and lateral parameters of planar spiral inductor

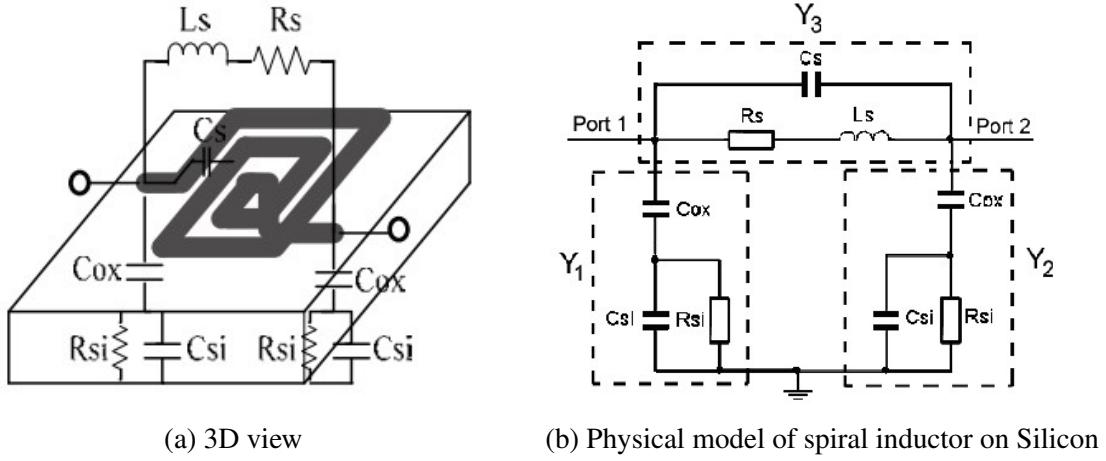

Process-controlled parameters are also known as ‘vertical’ parameters. They are metal resistivity, substrate resistivity, oxide thickness, metal thickness, and the number of metal layers. These parameters are used to define the inductance, capacitance, quality factor, and other parasitic elements of the inductor such as series resistance ( $R_s$ ), oxide capacitance ( $C_{ox}$ ), sub-

strate capacitance ( $C_{si}$ ), substrate resistance ( $R_{si}$ ), and spiral capacitance ( $C_s$ ). Based on these parameters the physical model ( $\pi$ -model) of spiral inductor [22] is derived and it is shown in Fig.1.9.

Figure 1.9: Typical  $\pi$ -equivalent model of spiral inductor

#### 1.2.4 Impact of parasitics on the performance of on-chip inductor

The inductor is designed to store magnetic energy, but its inherent resistance and capacitance are counter-productive and are referred to as parasitic resistance and capacitance. The physical model shown in Fig.1.9, illustrates the parasitic resistance and capacitances associated with the on-chip inductor. This model is used to investigate the performance of the on-chip inductor at low frequencies of a few MHz and high frequencies of several gigahertz.

The  $Q$  of an inductor is the amount of energy stored to the amount of energy dissipated in one cycle of the excitation. The expression for the quality factor of on-chip inductor taking magnetic energy and electrical energy into consideration is given in Eq.1.2.

$$Q = 2\pi \left( \frac{\text{Peak Magnetic Energy} - \text{Peak Electrical Energy}}{\text{Energy loss in one oscillation cycle}} \right) \quad (1.2)$$

The  $Q$  of the on-chip inductor mounted on a silicon substrate, which is derived from the physical model is given in Eq.1.3 [22].

$$Q = \underbrace{\frac{\omega L}{R_s}}_{\text{ohmic loss}} \cdot \underbrace{\frac{R_p}{(R_p + [(\omega L/R_s)^2 + 1]R_s)}}_{\text{substrate loss}} \cdot \underbrace{\left[ 1 - \frac{R_s^2(C_s + C_p)}{L} - \omega^2 L(C_s + C_p) \right]}_{\text{self-resonance factor}} \quad (1.3)$$

$$R_p = \frac{1}{\omega^2 C_{ox} R_{Si}} + \frac{R_{Si}(C_{ox} + C_{Si})^2}{C_{ox}^2} \quad (1.4)$$

$$C_p = C_{ox} \cdot \frac{1 + \omega^2(C_{ox} + C_{Si})C_{Si}R_{Si}^2}{1 + \omega^2(C_{ox} + C_{Si})^2R_{Si}^2} \quad (1.5)$$

The inductor's self-resonance frequency ( $f_{SR}$ ) is represented in Eq.1.6.

$$f_{SR} = \frac{1}{2\pi \sqrt{LC_{eq}}}. \quad (1.6)$$

In Eq.1.3,  $\omega$  is known as the angular frequency at which stored energy is measured,  $R_s$  is the series resistance of the inductor,  $L$  is the total inductance,  $C_{ox}$  is the oxide capacitance between the spiral and substrate,  $C_s$  is the capacitance between metal traces,  $C_{Si}$  is the substrate capacitance, and  $R_{Si}$  is the substrate resistance. In Eq.1.4 and Eq.1.5,  $R_p$  and  $C_p$  are the total parasitic resistance and capacitances, respectively, which are the resultant of the oxide capacitance ( $C_{ox}$ ), substrate capacitance ( $C_{Si}$ ), and substrate resistance ( $R_{Si}$ ) [22]. In Eq.1.6,  $C_{eq}$  is the parasitic capacitance resultant of  $C_s$  and  $C_p$  [23].

In Eq.1.3, the first term  $\frac{\omega L}{R_s}$  accounts for the stored magnetic energy and the ohmic loss in the series resistance. At a low-frequency regime, the Q of the inductor is dependent on series resistance, and it is well described by  $\frac{\omega L}{R_s}$ .

The second term in Eq.1.3, represents the substrate loss factor. At high frequencies (Giga Hertz Range) the Q factor decreases and it is due to the combined effect of substrate loss and self-resonance. Physically, the substrate loss is due to penetration of electrically induced displacement current from metal-to-substrate and it is modeled by a substrate RC network comprised of  $C_{ox}$ ,  $R_{Si}$ , and  $C_{Si}$  shown in Fig. 1.9. For typical on-chip inductors, the substrate loss factor causes 10 to 40% reduction in Q [22].

The last term in Eq.1.3, represents the self-resonance factor. The self-resonance factor describes the decrease in Q owing to the increase in the peak electric energy with frequency and the vanishing of Q at the self-resonance frequency.

In addition to Q, the total inductance (L) of the inductor is also affected at high frequencies. The substrate loss due to the magnetic field can be modeled as the mutual inductance between the metal and substrate [11]. The magnetically induced eddy currents will flow in a direction opposite to that of the current in the spiral. This mechanism increases the negative mutual inductance of the spiral and thus reduces the total inductance and hence Q. At gigahertz frequencies, the current crowding in the conductor reduces the skin depth and increases the resistance. The increase in series resistance causes a decrease in the Q [22]. The performance of the multilayer inductors and multilayer multipath inductors at high frequencies is well described using the multilayer physical model which is derived from the single layer physical model [100, 103, 106]. The performance of the inductor is deteriorated after the peak Q frequency ( $f_{Q_{max}}$ ) due to high substrate losses and current crowding effects.

The Y-parameters of the  $\pi$ -model for inductors can be directly determined from the  $\pi$  network series and shunt impedances [23]. The inductance, quality factor, and series resistance are determined from Y-parameters using Eq.1.7, Eq.1.8, and Eq.1.9 [24], respectively.

$$L = \text{Im}\left(\frac{-1}{2\pi f Y_{11}}\right) \quad (1.7)$$

$$Q = \frac{\text{Im}(Y_{11})}{\text{Re}(Y_{11})} \quad (1.8)$$

$$R_s = \frac{1}{\text{Re}(Y_{12})}. \quad (1.9)$$

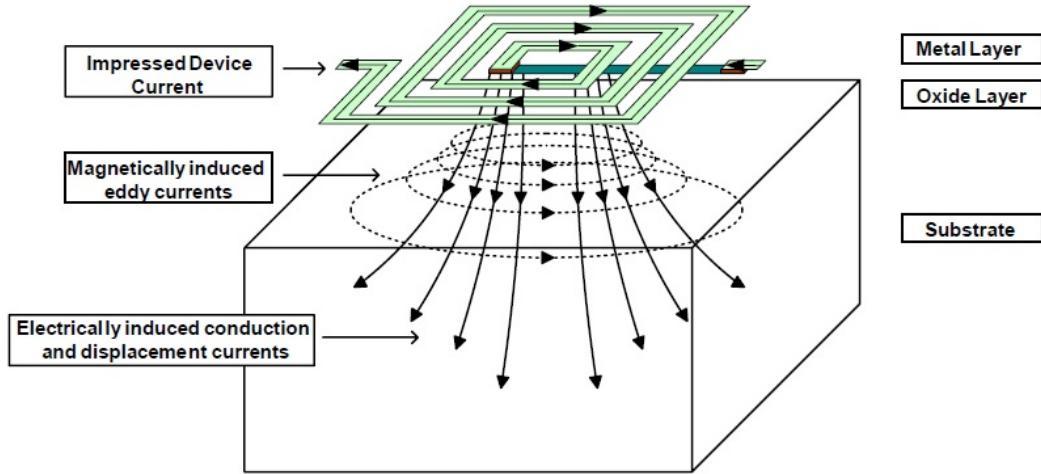

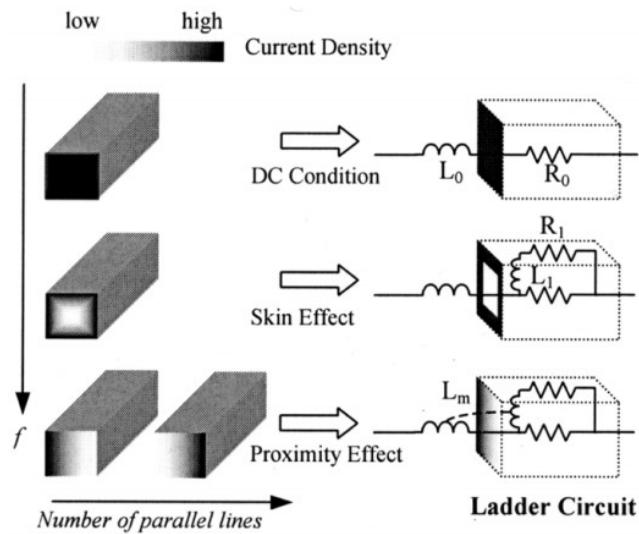

### 1.2.5 Losses in spiral inductor

The spiral inductor's performance at high frequencies was degraded owing to substrate losses and ohmic losses [25]. The substrate losses are due to the penetration of Electric and Magnetic fields into the substrate, which is shown in Fig.1.10. The ohmic losses or metal losses are due to non-uniform current distribution within the metal arisen from skin effect and proximity effect [26].

Figure 1.10: Substrate losses in spiral

Skin effect is defined as at any given frequency the magnetic field penetration through the metal line produces current flowing near the surface of the metal. Skin effect loss is dependent on skin depth ( $\delta$ ). The magnetic field generated from the adjacent metal lines induces the eddy currents and causes non-uniform current distribution in the metal. This phenomenon is called the proximity effect. The skin and proximity effects increase the effective resistance of the metal trace, which is shown in Fig.1.11. Thus, at a high frequency of operation increase in skin and proximity effects increases the series resistance of the inductor which in turn decreases the Q.

Figure 1.11: Variation of skin and proximity effects with frequency

To enhance the performance of spiral inductors in terms of figures-of merit (such as quality factor, inductance) different techniques were proposed. Substrate etching [27] as well as

utilization of patterned ground shield [28] beneath the inductor and utilization of high resistivity substrate [29] had reduced the substrate losses and increased the  $Q$  at the expense of low  $f_{SR}$ . However, these techniques had an unusual and expensive fabrication process and not compatible with other active MOS devices. Differential inductors were proposed in the literature to increase the  $Q$  of the inductor without altering the fabrication process.

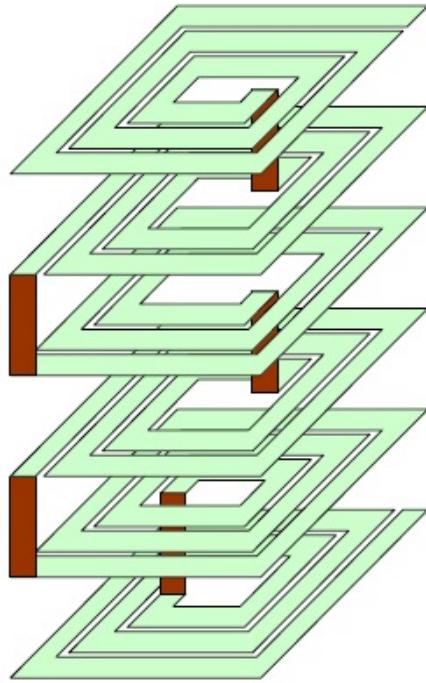

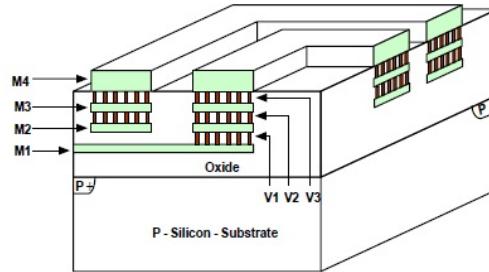

The performance of the spiral inductors was further improved by implementing them in multiple layers. In multilayer inductors, spirals are connected either connected in series or parallel in different metal layers. The spirals connected in series increases the total inductance and occupies the same on-chip area as compared with planar inductor [30]. The parallel connection of metal layers [31] increases the effective thickness of the metal which in turn decreases the series resistance and improves the  $Q$ . The series stacked and parallel stacked inductors are shown in Fig.1.12.

### 1.2.6 Differential inductor

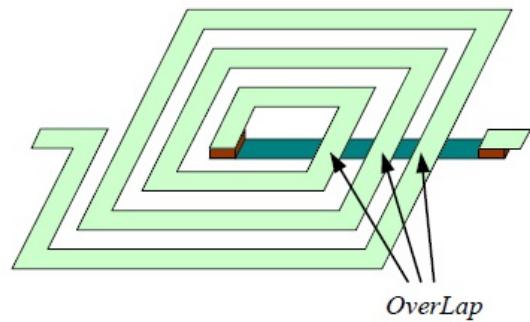

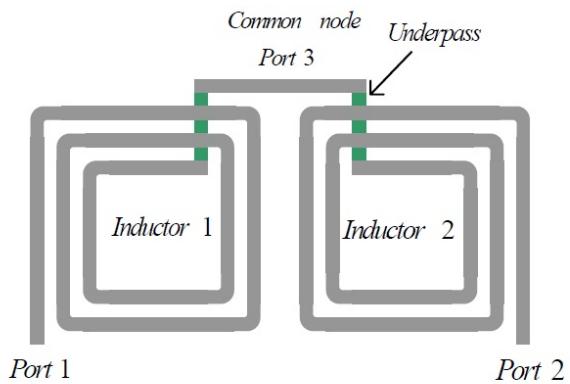

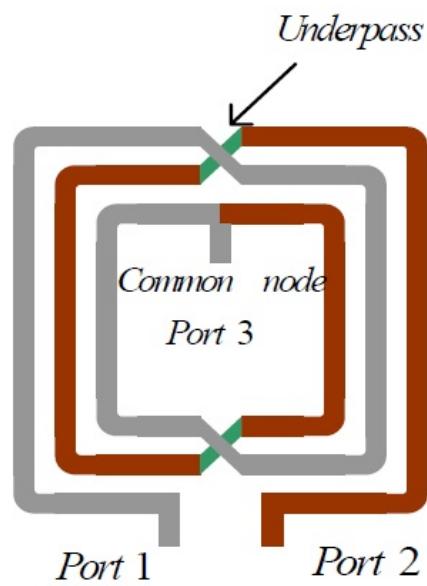

The spiral inductors are classified into symmetrical and asymmetrical inductors based on the arrangement of ports. In the asymmetrical spiral inductor (conventional spiral inductor) as shown in Fig.1.13, the ports are on the opposite side of the structure, whereas in the symmetrical spiral inductor the ports are on the same side of the structure. The asymmetrical inductor is realized using a pair of asymmetrical spiral inductors shown in Fig.1.14 occupies a large on-chip area. A fully symmetrical inductor as shown in Fig.1.15 is realized by joining two separate spirals with a single spiral from one side of an axis of symmetry to the other using a number of cross-over and cross-under connections occupy a small on-chip area [17]. This winding style was first reported by Rabjohn [32] to connect both primary and secondary coils of the monolithic transformers.

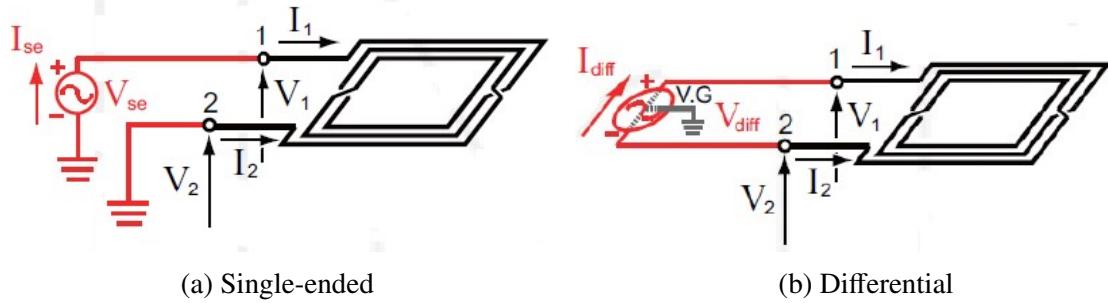

The inductor can be excited in two possible ways, one is a single-ended (single port) mode and the other is differential (two/dual) mode. In single-ended excitation, one port is connected to the source and the other port is grounded. In differential excitation, the two ports are connected to the source (i.e. voltages and currents on the two ports are 180 degrees out of phase). The difference between single-ended and differential excitation is shown in Fig.1.16. The symmetrical inductor with differential excitation is referred to as the differential inductor. In differential excitation the two voltages  $V_1$  and  $V_2$  are in anti-phase, however, the currents  $I_1$  and  $I_2$  are in the same direction. This strengthens the magnetic field produced by the parallel conductor's groups and increases the overall inductance per unit area. The differential inductor

(a) Series stacked inductor

(b) Parallel stacked spiral using vias

Figure 1.12: Multiple metal stacking of the inductor

is best suited for the connection of the active devices as the input ports are on the same side of the structure.

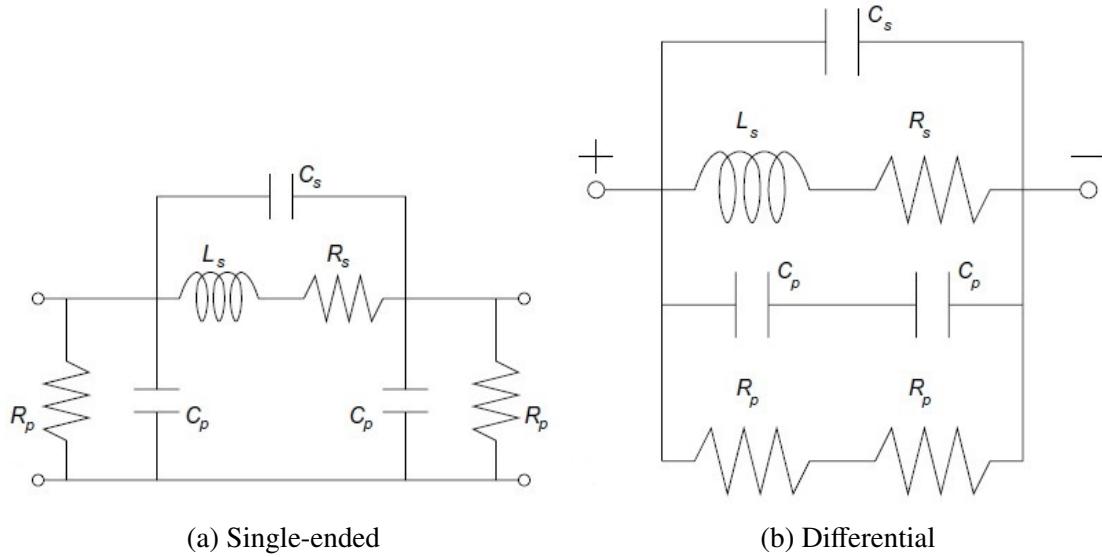

The equivalent circuits derived from the  $\pi$ -model of the spiral inductor is shown in Fig.1.17 for the single-ended and differential excitation. The quality factor for both single-ended ( $Q_{se}$ ) and differential excitations ( $Q_{diff}$ ) are given in Eq.1.11 and Eq.1.12 [33].  $Q_o$  is known as the quality factor corresponding to ohmic losses given in Eq.1.10. From Fig.1.17, it is evident that in differential excitation the substrate parasitic resistance  $R_p$  was doubled and  $C_p$  reduced to half [33]. This implies a huge reduction in substrate losses. Thus, the Q of the inductor had

Figure 1.13: Asymmetrical spiral inductor

Figure 1.14: Symmetric spiral inductor using two asymmetrical spiral inductors

Figure 1.15: Symmetric spiral inductor

Figure 1.16: Excitation of symmetric spiral inductor

Figure 1.17: Lumped equivalent circuits for different excitations

greatly improved when driven differentially without altering the fabrication process. The  $f_{SR}$  had increased owing to decrease in effective parasitic capacitance from  $C_p + C_o$  to  $C_p/2 + C_o$ .

$$Q_o = \frac{\omega L_s}{R_s} \quad (1.10)$$

$$Q_{se} = Q_o \cdot \frac{1 - \left( \frac{R_s^2}{L_s} - \omega^2 L_s \right) (C_p + C_s)}{1 + \frac{R_s}{R_p} \left[ 1 + \left( \frac{\omega L_s}{R_s} \right)^2 \right]} \quad (1.11)$$

$$Q_{diff} = Q_o \cdot \frac{1 - \left( \frac{R_s^2}{L_s} - \omega^2 L_s \right) \left( \frac{C_p}{2} + C_s \right)}{1 + \frac{R_s}{2R_p} \left[ 1 + \left( \frac{\omega L_s}{R_s} \right)^2 \right]} \quad (1.12)$$

The inductance, quality factor, and series resistance are calculated from the S-parameters obtained from the EM simulator or the vector network analyzer (VNA). Initially, S-parameters are converted into Y-parameters and the input impedance for the single-ended and differential excitation are calculated using Eq.1.13 and Eq.1.14 [33, 34]:

$$Z_{se} = 0.5 * \left( \frac{1}{Y_{11}} + \frac{1}{Y_{22}} \right) \quad (1.13)$$

$$Z_{diff} = \frac{(Y_{11} + Y_{12} + Y_{21} + Y_{22})}{(Y_{11}Y_{22} - Y_{12}Y_{21})} \quad (1.14)$$

Where,  $Y_{11}$  denotes the short circuit input admittance,  $Y_{22}$  denotes the short circuit output admittance,  $Y_{12}$  denotes the short circuit reverse transfer admittance, and  $Y_{21}$  denotes the short circuit forward transfer admittance.

The quality factor, inductance, and series resistance for single-ended and differential excitation are calculated using following equations [33, 34]:

$$Q_{se} = \frac{Imag(Z_{se})}{Real(Z_{se})} \quad (1.15)$$

$$Q_{diff} = \frac{Imag(Z_{diff})}{Real(Z_{diff})} \quad (1.16)$$

$$L_{se} = \frac{Imag(Z_{se})}{\omega} \quad (1.17)$$

$$L_{diff} = \frac{Imag(Z_{diff})}{\omega} \quad (1.18)$$

$$R_{se} = \frac{1}{Real(Y_{11})} \quad (1.19)$$

$$R_{diff} = Real(Z_{diff}) \quad (1.20)$$

### 1.3 On-chip capacitors

The capacitor is an important passive component in wireless RF applications. Types of on-chip capacitors available are MOS capacitors, MIM capacitors, MEMS capacitors, and passive capacitors. Capacitors are often used in impedance matching networks, RF oscillators, tuned resonators, and dc blocking circuits. In these circuits, area-efficient capacitors are highly desirable as capacitor occupies larger space in the die. The design of low leakage and high-performance capacitors is challenging in IC fabrication. The performance of the on-chip capacitor is measured in terms of capacitance per unit area, quality factor, and self-resonance frequency which are shown in Fig.1.18. The calculation of capacitance and quality factor values are given by Eq.1.21 and Eq.1.22 [24].

Figure 1.18: Performance metrics of on-chip capacitor

$$Capacitance = \frac{-Im[Y_{21}]}{2\pi f} \quad (1.21)$$

$$Q \text{ factor} = \frac{Im[Y_{11}]}{Re[Y_{11}]} \quad (1.22)$$

MOS capacitors have been utilized for a long time because of the benefits of easy integration and native MOSFET fabrication [35, 36]. However, the MOS capacitor suffers from non-linear behavior, sensitivity, and poor quality factor that limits their application. Due to this, metal electrode parallel plate capacitors in nano-structure became popular, later it was termed

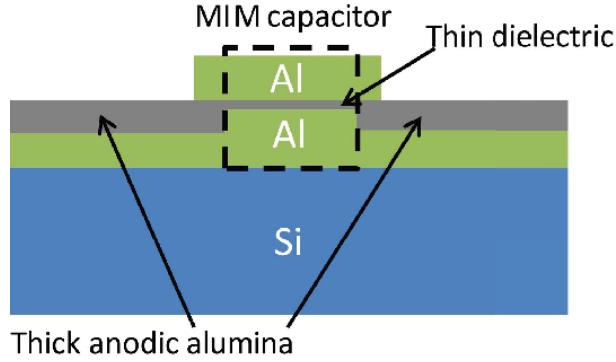

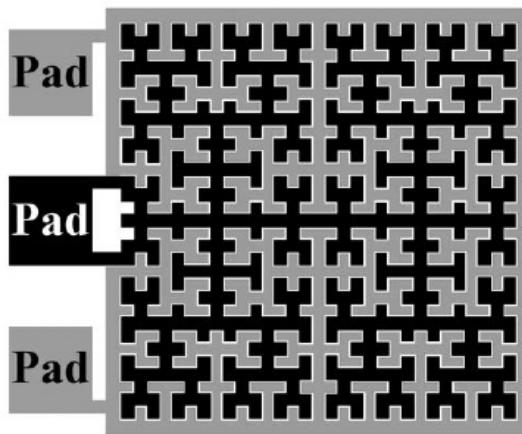

as Metal-Insulator-Metal (MIM) capacitors [37, 38]. These are constructed from a thin insulation film between two metal planes as shown in Fig. 1.19. The advantage of the MIM capacitor is insensitivity to a silicon substrate as the capacitor is formed by enclosing the electric field between the upper metal layers. However, as the capacitance is inversely proportional to the thickness of the insulator that does not scale with process technology, MIM capacitors do not follow technology scaling. Hence, the area of the capacitors relatively increases with progress in CMOS process technology. MEMS (Micro Electro Mechanical Systems) capacitor occupies a small on-chip area with high volume fabrication and it also attains high  $Q$  and  $f_{SR}$  with low power consumption [39, 40]. These are very much sensitive to the parasitic capacitive coupling between the substrate and metals and also suffer from inherent parasitic inductance. Fractal curves used in the implementation of capacitors increase the capacitance density and obtains high self-resonance frequency [41, 42]. The MEMS fractal capacitor is shown in Fig. 1.20.

Figure 1.19: MIM capacitor

Figure 1.20: MEMS capacitor

## 1.4 Fractal curves

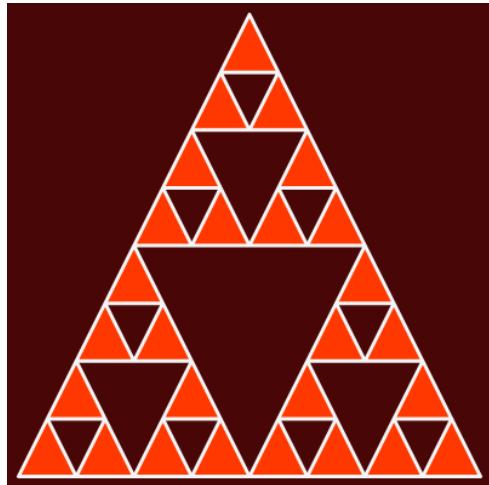

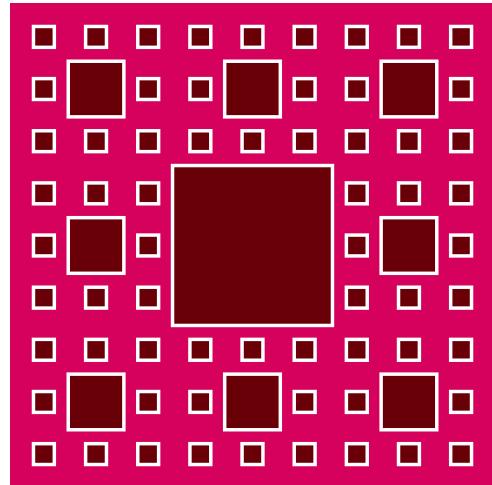

The French mathematician Mandelbrot discovered the term fractal which symbolizes broken or irregular fragments that fills every point in a bounded area [43]. Fractal has various properties like space-filling, recursive, infinite, and self-symmetry [44]. The fractal curves are typically defined by an iterative process. Some of the fractals are derived from mathematical formulas and some are derived from natural phenomena such as mountains, clouds, and trees. Generally, fractal curves are divided into two types, natural (random) and mathematical (deterministic). Nature fractals are all those that are available in nature-clouds, mountains, trees, leaves, valleys, and the human respiratory system. Fig. 1.21 shows examples of a few natural fractal curves. Mathematical fractals are developed using mathematical formulas and the concepts of iteration, recursion, etc. Widely known mathematical fractal curves are Hilbert, Sierpinski, Koch, Moore, Peano, etc [45, 46]. The mathematical space-filling curves are easily constructed using iterative algorithm [47]. Some of the well known mathematical space-filling curves are shown in Fig.1.22.

### 1.4.1 Applications of fractal geometry

The advancement in wireless communication systems has brought new challenges to the design and production of very good compact components. Such challenges encourage developers to find key solutions using different fractal geometries [48, 49]. Fractals are used in several branches of science and engineering disciplines such as image processing, microwave circuits, mechanics, forest and atmospheric sciences, and geology. One area of application that has impacted modern technology most is image compression using fractal image coding. Fractal image rendering and image compression schemes have led to a significant reduction in memory requirements and processing time. The self-similarity of the fractal geometry has been attributed to the dual-band nature of their frequency response.

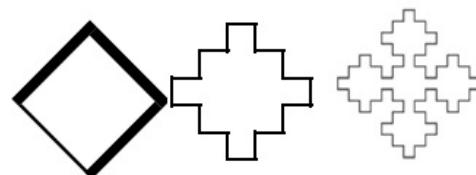

Integrated passive components such as capacitors, inductors, and resistors are the building blocks in MMICs to minimize the on-chip area. Fractal technology opens a new scope of opportunities in the miniaturization of passive RF and microwave components. Fractal-based electrical devices have been formerly demonstrated which includes fractal inductors, fractal capacitors, fractal sensors, fractal transformers, and fractal antennas. Fractal inductor attains large inductance value with miniaturized on-chip area compared to conventional planar spiral inductor [50, 51]. Fractal capacitors have high capacitance density in a single layer process

(a) Fern leaf-a natural fractal object

(b) Snow Flake

(c) Sierpinski Carpet

(d) Sierpinski Triangle

Figure 1.21: Natural fractal curves

[52, 53], fractal sensors have smart sensing and compact size [54], fractal antennas have useful multiband frequency behavior [55, 56], and fractal transformers have higher inductance and reduced micro-fabrication complexity [57]. Wireless communication systems are getting benefited from the implementation of fractal passive components along with the filter and antennas. Fractal based inductor, capacitor, and transformer are shown in Fig.1.23, Fig.1.24, and Fig.1.25, respectively.

(a) Construction of Hilbert curve

(b) Construction of Moore curve

(c) Construction of Sierpinski curve

Figure 1.22: Mathematical fractal curves

Figure 1.23: Fractal inductor

Figure 1.24: Fractal capacitor

Figure 1.25: Fractal transformer

## 1.5 Low noise amplifier

Low noise amplifiers are key building blocks of the receiver in a wireless communication system. The input signal to the LNA is very weak and the main function of the LNA is to provide sufficient gain to suppress the noise of subsequent stages while adding as little noise as possible. The performance metrics of the LNA are gain, noise figure (NF), input matching, power dissipation, linearity, and stability factor.

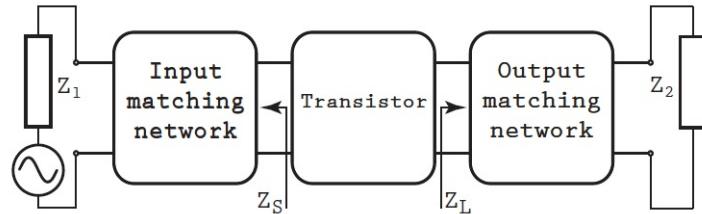

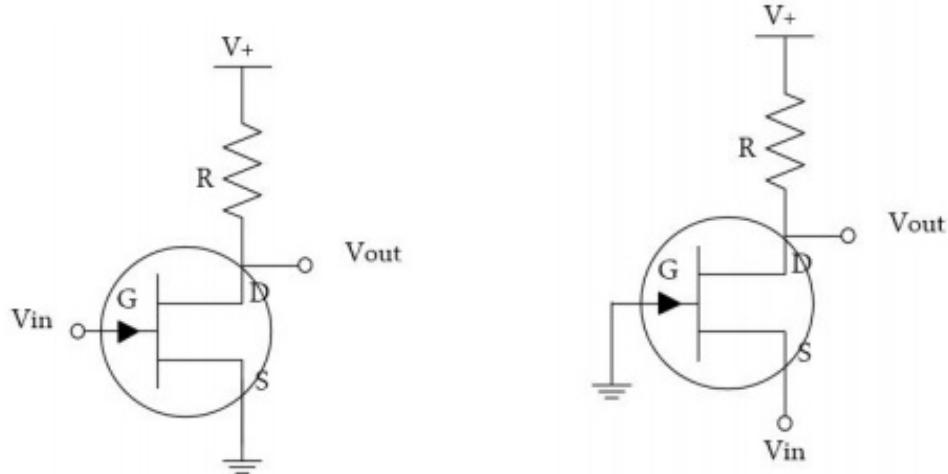

The universal topology of an LNA circuit can be consists of three stages as shown in Fig. 1.26. It has the input matching network, transistor amplifier, and finally output matching network. Several LNA topologies were proposed in the literature have their own merits and demerits. The CG (common gate) and CS (common source) are mostly used configurations in the design of CMOS LNA circuits. The CS LNA provides high gain and good noise performance [58]. However, the bandwidth of the CS amplifier is low due to the miller effect. Placing an inductor in the source of a CS stage the well-known inductive source degeneration topology is obtained. The common source LNA with inductive degeneration improves the gain and noise performance of the LNA and it is used to design narrowband LNA circuits [59]. The CG LNA configuration provides better input matching, better reverse isolation, good linearity, and large bandwidth. However, it has poor noise performance. Few techniques, such as capacitive cross-coupling, has been presented to improve the CG stage noise performance [60, 61, 62]. Wideband input matching is possible for CG configuration and hence this configuration is widely used in broadband LNA circuits [63, 64, 65].

Cascode LNA as shown in Fig. 1.29 provides superior noise performance, high power gain, low power consumption, and better reverse isolation [66, 67, 68]. Unfortunately, excellent noise and gain performance of cascode stage degrade at very high microwave frequencies. This is due to the increase in substrate parasitic admittance at the drain-source common node with the increase in frequency[69, 70]. Like a CS stage, the cascode stage is proper for narrowband applications, however using feedback techniques makes it possible using of cascode stage in multi-band and wideband applications [71, 72]. Another way to use cascode configuration in the wideband application is using complicated LC matching networks in the input [73].

The broadband input matching, high gain, and wide operation were obtained by distributed amplifiers (DA) [74] and multistage LNAs [75]. As the distributed amplifier and multistage LNAs are built from multiple cascading stages low power consumption and the minimal on-chip area would be difficult to obtain. The current-reuse LNA is exceptional for its ability to deliver high-performance in terms of low power dissipation, flat gain, low NF, good linearity,

and good input matching [76, 77]. Different noise cancellation techniques are proposed to improve the noise performance of the LNA [78, 79]. Multistage cascode LNAs have shown good performance in mm-wave frequency range [80, 81]. Likewise, various LNA topologies were proposed and still, research is going on optimize the performance of the LNA.

Figure 1.26: Block diagram of LNA

Figure 1.27: Common source

Figure 1.28: Common gate

## 1.6 Design tool and Measurement setup

Design, modeling, field distribution, and scattering parameters of the proposed on-chip inductors are carried out by EM simulators. The EM simulators used in most of the works in this thesis are High-Frequency Structural Simulator (HFSS), Sonnet, and ADS (Advanced Design System) Momentum. To verify the characteristics of fabricated devices Vector Network Analyzer (VNA) is used. In addition to device characteristics, circuit simulations are performed using ADS (Advanced Design System) circuit simulator.

Figure 1.29: Cascode LNA

## 1.7 Motivation

Most of the circuits like LNA and VCO in analog and mixed-signal RFICs and MMICs are typically operated in a differential signal mode. Differential inductors are considered to be the best choice for implementing the differential circuits due to superior noise rejection properties and miniaturized on-chip area. High-quality factor on-chip differential inductors are essential to enhance the performance of a conventional integrated circuit.

## 1.8 Problem statement

To design a high-performance differential inductor that can be used for RF and mm-wave applications to enhance the performance of the system.

## 1.9 Objectives

- To design multilayer differential spiral inductor using multipath technique.

- To design and implement multilayer series stacked, parallel stacked, and planar multipath differential fractal inductors.

- To fabricate the proposed inductors and validate the simulation results with the measured results.

- To implement Low Noise Amplifier using proposed differential fractal inductors for high frequency applications.

## 1.10 Organization of Work

The thesis presents a performance analysis of on-chip multilayer differential spiral inductors and differential fractal inductors to improve performance metrics of the components for the equivalent on-chip area. It also deals with the implementation of LNA using proposed inductors.

**Chapter 2** reviews the notable amount of most updated literature and a brief outline of the thesis is also presented.

**Chapter 3** deals with the design and simulation of multilayer differential spiral inductor using multipath and variable width techniques.

**Chapter 4** deals with the design and implementation of a novel hybrid series stacked differential fractal inductor for MMIC applications.

**Chapter 5** deals with the design and implementation of multilayer stacked differential fractal inductors. It also deals with the design of narrowband LNA using the proposed OSSDFI. Furthermore, the performance of the proposed inductor and LNA circuit is compared with the existing state-of-the-art.

**Chapter 6** deals with the design and implementation of multipath differential fractal inductor for wireless applications.

**Chapter 7**, conclusion of the thesis is summarized from the contributions and a brief discussion on the direction for future work is given.

# Chapter 2

## Literature Survey

### 2.1 Introduction

Development in wireless communication shows a keen interest in the design of radio transceivers. On-chip inductors integrated into RFIC's play a significant role in minimizing the size of radio transceivers. On-chip inductors play a fundamental role in RF circuits at a higher operating frequency, leading to different innovative structures over the years. In the subsequent sections, different on-chip inductors are reported and discussed according to the type of structure. These are not necessarily in the order of the year reported.

### 2.2 Review on On-Chip Inductor Design

The fabrication of inductor structures was investigated in the early 60s, but it was observed that inductors are the most difficult component to integrate because of their large on-chip area requirement and low-Q factor at GHz frequency practical applications. From conventional planar spiral inductors to several multilayer spiral inductors, the literature covers a wide range of on-chip inductors. The fractal curves were discovered to have symmetrical, space-filling, and recursive properties, which made them suitable for the development of on-chip inductors. We have included several types of fractal inductors in this literature, which offer few advantages over spiral inductors.

### 2.2.1 Conventional planar on-chip spiral inductors

This section describes several planar on-chip spiral inductors and their advantages and drawbacks.

In [82], E. Frlan, et al, designed and developed a lumped model for the first time to describe the characteristics of the square spiral inductor. The square spiral inductor was fabricated with  $265 \mu\text{m} \times 245 \mu\text{m}$  on-chip area on alumina substrate for the inner diameter of  $160 \mu\text{m}$ . The width and spacing between the conductors are  $20 \mu\text{m}$  and  $10 \mu\text{m}$ , respectively. The inductor has obtained an inductance of  $2 \text{ nH}$  for low frequencies. The inductance value was reduced to  $1.75 \text{ nH}$  at self-resonance frequency of  $20 \text{ GHz}$ .

In [83], N.M. Nguyen, et al, designed and fabricated two square spiral inductors on standard Si substrate. The inductors have an outer diameter of  $230 \mu\text{m}$  and  $115 \mu\text{m}$ , respectively. The large and small inductors has obtained inductance values of  $9.3 \text{ nH}$  and  $1.3 \text{ nH}$  with the self-resonance frequency of  $9.7$  and  $2.47 \text{ GHz}$ , respectively. Both inductors have obtained Q values in the range of 3 to 8. A low pass LC filter is realized utilizing these inductors has shown better performance in terms of input matching, linearity, and power gain. The authors have realized an RF bandpass amplifier for L band ( $1-2 \text{ GHz}$ ) using monolithic inductor having an inductance of  $4 \text{ nH}$  in Silicon Bipolar technology [84]. The amplifier has obtained a peak gain of  $8 \text{ dB}$ , Noise Figure (NF) of  $6.4 \text{ dB}$ , and matched input impedance.

In [85], J. Burgahartz, et al, realized a square spiral inductor with  $10 \mu\text{m}$  width  $3.5 \mu\text{m}$  spacing for an on-chip area of  $160 \times 160 \mu\text{m}^2$ . The inductor has obtained a peak Q value of  $9.7$ , inductance of  $2.45 \text{ nH}$ , and self-resonance frequency of  $5.3 \text{ GHz}$ . A bandpass filter (BPF), LNA, and VCO are implemented utilizing high Q square spiral inductor. Due to this, the insertion loss of BPF is improved by  $>5 \text{ dB}$ , the LNA has obtained low Noise Figure (NF), low power consumption, and high gain, and the VCO has obtained power saving and improvement in phase noise by  $7 \text{ dB}$ . After this, there has been enormous progress in design, modeling, and optimization of inductors for various millimeter and microwave applications.

In [86], C.P.Yue et.al., developed a physical model for an on-chip inductor on a silicon substrate. The developed physical model is based on copper losses, substrate losses, and parasitic losses. This model helps to optimize the performance of the inductor. Several innovative inductor structures are proposed in the later years.

In [87], J.Y.C. Chang et al., designed a spiral inductor to obtain a large inductance value of 100 nH with an outer diameter of 440  $\mu\text{m}$ . In this work, etching the substrate underneath the inductor reduces the substrate losses and improves the Q and self-resonance frequency of the inductor. The measurement results show that the removal of the substrate improves the self-resonance frequency to 3 GHz from 800 MHz. A balanced tuned amplifier has been implemented in a standard digital 2- $\mu\text{m}$  CMOS IC process using 100 nH proposed inductor attains a power gain of 14 dB at a center frequency of 770 MHz, NF of 6 dB, the power dissipation of 7 mW from a 3-V supply.

In [88], A. Eroglu, has implemented a rectangular spiral inductor for high-frequency ISM (Industrial, Scientific, and Medical) applications. The author proposed an analytical model and algorithm to determine the physical dimensions and self-resonance frequency for the desired inductance value. After this five spiral inductors are built on 100 mil thick Alumina ( $Al_2O_3$ ) substrate for different dimensions. The inductors have obtained inductance values ranging from 132 to 753 nH and self-resonance frequency values ranging from 38 to 81 MHz. The analytical results have shown better accuracy compared with simulated and measured results.

In [89], Jinglin Shi et.al, demonstrated the insertion of the patterned ground shield (PGS) beneath the inductor. The inductors and PGS were fabricated in 0.18  $\mu\text{m}$  and 0.35  $\mu\text{m}$  CMOS technology. The PGS provides good termination to the electric and magnetic field before it reaches the silicon substrate which reduces the substrate losses and improves the Q of the inductor to a greater extent. The authors have tested the performance of the inductor at different high temperatures and demonstrated that the use of PGS compensated for the decrease in Q. The authors have stated the effective way of separating PGS and top metal with an appropriate distance to enhance the Q for different high temperatures. The authors used metal PGS and poly strip PGS to analyze the performance of the inductor for the temperature range of 298 K to 358 K.

In [90], M.J. Chiang reported a complementary spiral-shaped electromagnetic bandgap (CSS-EBG) structure for spiral inductors and transmission line using 0.18  $\mu\text{m}$  CMOS technology. The CSS-EBG structure enhances the Slow Wave factor (SWF) and characteristic impedance of the transmission line compared to conventional thin-film microstrip (TFMS) transmission line for the same line width and material properties. For spiral inductor, the CSS-EBG structure provides effective shielding to terminate the substrate coupling. This reduces the substrate losses and improves the quality factor of the inductor compared to conventional spiral inductors without shielding. The inductor attains a peak Q of 10.5 at 37.8 GHz for an outer diameter of 110  $\mu\text{m}$ .

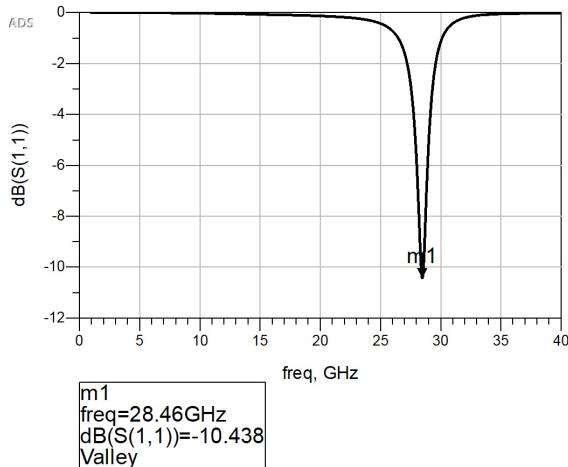

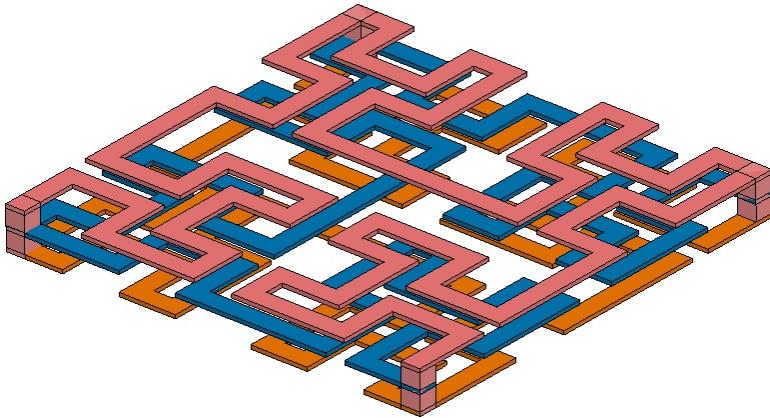

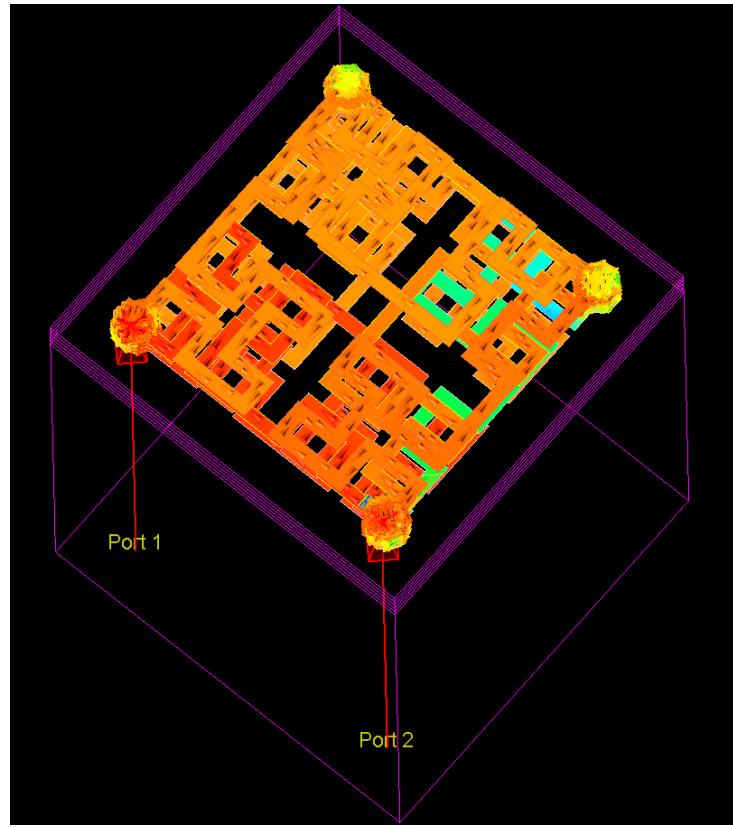

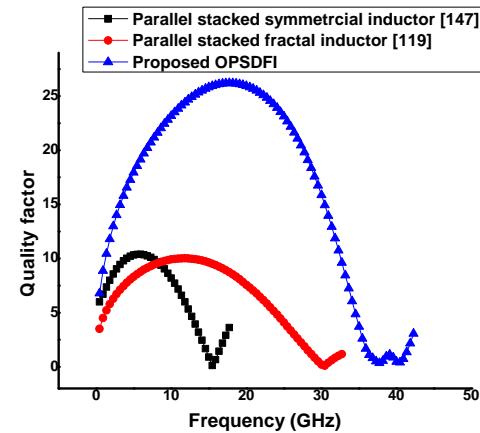

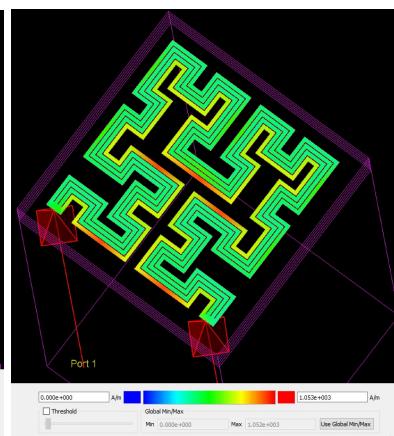

In [91], Hsien-Shun Wu et al, reported a spiral inductor incorporating a photonic bandgap (PBG) structure beneath the inductor as a ground plane substitute. The PBG ground plane is made of a thin, two-sided, printed-circuit board. The novel inductor configuration reduces the series resistance, increases the inductance, enhances the Q-factor and self-resonance frequency.