**INVESTIGATION ON SINGLE-PHASE VOLTAGE SOURCE BASED

INVERTER TOPOLOGIES FOR GRID-CONNECTED

PHOTOVOLTAIC POWER GENERATION SYSTEMS**

Submitted in partial fulfilment of the requirements

for the award of the degree of

**DOCTOR OF PHILOSOPHY

in

Electrical Engineering**

By

**Kuncham Sateesh Kumar**

**(Roll No. 716118)**

**Supervisor**

**Dr. A. Kirubakaran**

Assistant Professor

&

**Dr. N. Subrahmanyam**

Professor

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506004, TELANGANA STATE, INDIA

AUGUST-2020**

## **APPROVAL SHEET**

This Thesis entitled "**Investigation on Single-Phase Voltage Source based Inverter Topologies for Grid-Connected Photovoltaic Power Generation systems**" by **Kuncham. Sateesh Kumar** is approved for the degree of Doctor of Philosophy.

### **Examiners**

---

---

---

### **Supervisors**

**Dr. A. Kirubakaran**

Assistant Professor

EED, NIT Warangal

&

**Dr. N. Subrahmanyam**

Professor

EED, NIT Warangal

### **Chairman**

**Dr. M. Sailaja Kumari**

Professor & Head,

EED, NIT Warangal

**Date:** \_\_\_\_\_

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506 004, TELANGANA STATE, INDIA**

**CERTIFICATE**

This is to certify that the thesis entitled "**Investigation on Single-Phase Voltage Source based Inverter Topologies for Grid-Connected Photovoltaic Power Generation systems**", which is being submitted by **Mr. Kuncham Sateesh Kumar** (Roll No. 7161118), is a bonafide work submitted to National Institute of Technology, Warangal in partial fulfilment of the requirement for the award of the degree of **Doctor of Philosophy** in Department of Electrical Engineering. To the best of our knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. A. Kirubakaran**

(Supervisor)

Assistant Professor

Department of Electrical Engineering

National Institute of Technology

Warangal – 506004

Date:

Place: NIT Warangal

**Dr. N. Subrahmanyam**

(Co-Supervisor)

Professor

Department of Electrical Engineering

National Institute of Technology

Warangal – 506004

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Investigation on Single-Phase Voltage Source based Inverter Topologies for Grid-Connected Photovoltaic Power Generation systems**" is a bonafide work done by me under the supervision of **Dr. A. Kirubakaran, Assistant Professor, & Dr. N. Subrahmanyam, Professor**, Department of Electrical Engineering, National Institute of Technology Warangal, Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Kuncham Sateesh Kumar**

**(Roll No: 716118)**

Date:

Place: Warangal

## ACKNOWLEDGEMENTS

It gives me immense pleasure to express my deep sense of gratitude and thanks to my supervisor **Dr. A. Kirubakaran**, Assistant Professor, and **Dr. N. Subrahmanyam**, Professor, Department of Electrical Engineering, National Institute of Technology Warangal, for their invaluable guidance, support, and suggestions. Their knowledge, suggestions, and discussions helped me to become a capable researcher. They showed me the interesting side of this wonderful and potential research area. Their encouragement helped me to overcome the difficulties encountered in my research as well in my life.

I am very much thankful to **Prof. M. Sailaja Kumari** Head, Department of Electrical Engineering for his constant encouragement, support and cooperation.

I take this privilege to thank all my Doctoral Scrutiny Committee members, **Dr. V. T. Somasekhar**, Professor, Department of Electrical Engineering, **Dr. B. L. Narasimharaju**, Associate Professor, Department of Electrical Engineering and **Dr. P. Srihari Rao**, Associate Professor, Department of Electronics and communication Engineering for their detailed review, constructive suggestions and excellent advice during the progress of this research work.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal. They have always been encouraging and supportive.

I wish to express my sincere thanks to **Prof. N.V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

I convey my special thanks to my contemporary Research Scholars Mr. Jammy Ramesh Rahul, Mr. Abhilash T, Mr. Chinmay Kumar Das, Mr. Venu Sonti, Mr. Hema Sundhar K, Mr. Sathyakar VVK, Mr. Bhaskar, Mr. Ram Kumar, Mr. Gurappa, Mr. Anil Kumar B, Mr. Kalyan, Mr. Sachidananda Prasad, Mr. Eswar Gowd, Mr. Vishnu Prasad, Mr. Hareesh M, Mr. Suresh L, Mr. Ratna Rahul and also M Tech (Power Electronics) students Suneel B (2019), Punam (2020).

I acknowledge my gratitude to all my teachers and colleagues at various places for supporting me to complete the work.

I wish to express my gratitude to SERB for utilizing facilitates to carry out a part of the research work under EMR project grant 2016/007811.

My special, sincere acknowledgement, heartfelt gratitude and indebtedness are due to my parents **Shri. K. Srirama Murthy & Smt. Bharati**, my wife **K. Rama Devi**, my grandmother **K. Anasuryamma**, my sister **Ch. Sandhya**, my brother **K. Ashok Kumar**, my uncle **V. Srinivas**, my Aunt **V. Dhanalakshmi**, and other family members for their sincere prayers, blessings, constant encouragement, shouldering the responsibilities and moral support rendered to me throughout my life, without which my research work would not have been possible. I heartily acknowledge all my relatives for their love and affection towards me.

Above all, I express my deepest regards and gratitude to “**ALMIGHTY**” whose divine light and warmth showered upon me the perseverance, inspiration, faith and enough strength to keep the momentum of work high even at tough moments of research work.

**Kuncham Sateesh Kumar**

Ж

## ABSTRACT

---

---

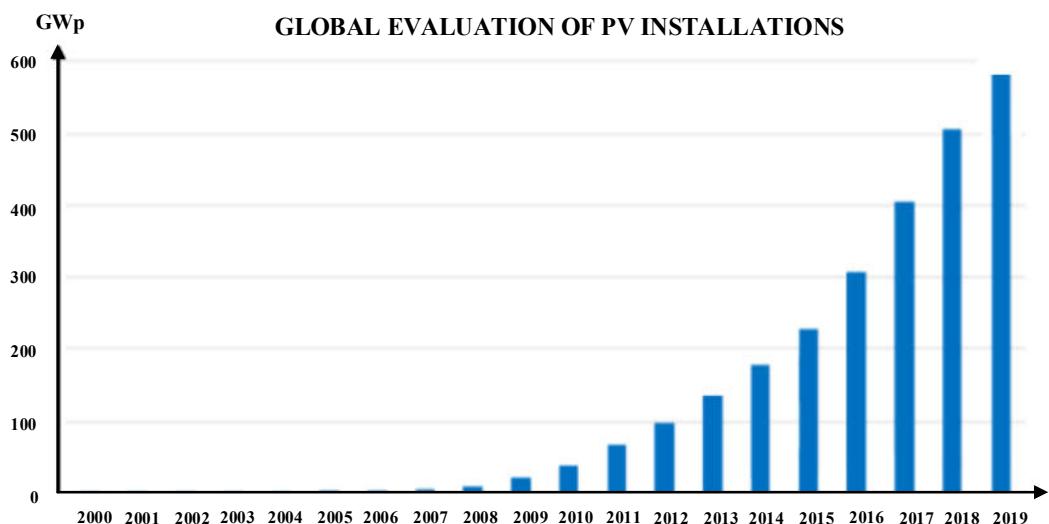

Emerging renewable power generations such as photovoltaic, wind, and fuel cells are getting much attention of the researchers in the present scenario due to dwindling conventional energy sources. As per the renewable global status report, the photovoltaic power generation systems (PVPGS) during the last decade has an exponential growth due to low price and deserves a prominent place with an overall global installation of 583.5 GW capacity by the end of 2019. Among those, the grid-connected PVPGS occupied 90% of the market share due to its simple structure, low cost, and longer life-time. Depends on the voltage and power rating of the PV source, each grid-connected PVPGS comprises a series, parallel, and both the combinations of PV modules, followed by inverter and filter circuit to feed the generated power into the AC grid.

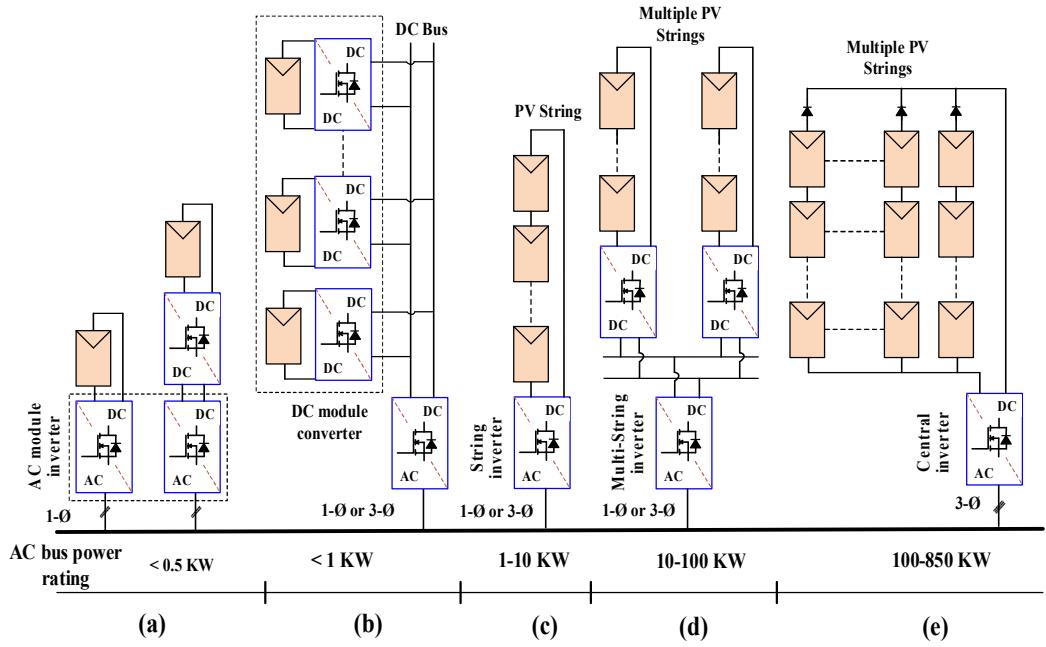

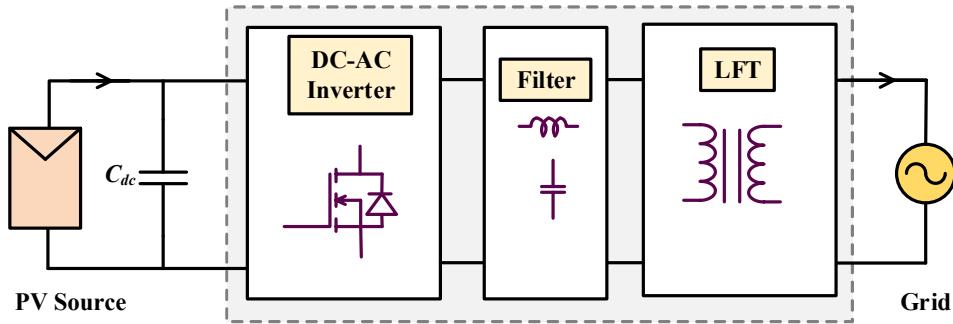

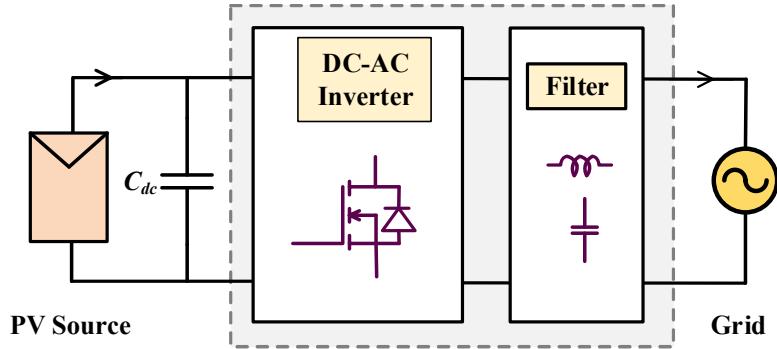

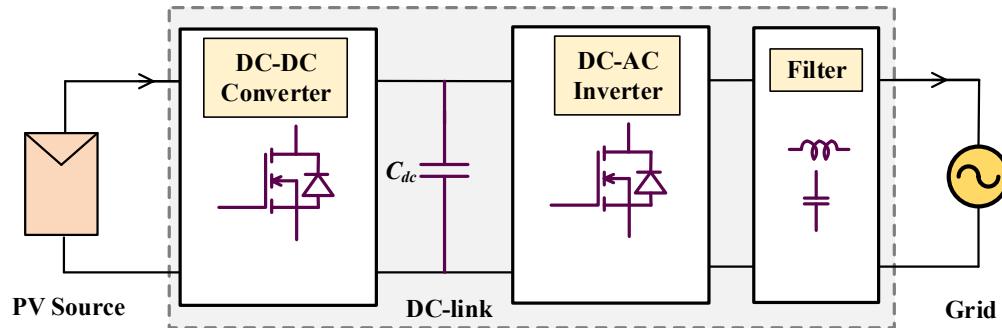

Based on the number of power processing stages, the inverters are classified into single-stage and two-stage systems. The applications such as central (100 kW to 850 kW) and string PVPGS (1 kW to 10 kW) require a single central inverter to interface with a whole PV array to the grid, known as single-stage inverter. Conversely, applications like module (<1 kW) and multi-string (10 kW to 100 kW) PVPGS utilize a front end DC-DC converter followed by an inverter for injecting PV power into the grid, known as two-stage inverter. Moreover, an additional DC-DC converter is used prior to the inverter for extracting maximum power from the PV source and for boosting the low PV voltage to higher DC voltage. The number of PV modules which are connected in series are less in two-stage inverter in comparison with the single-stage inverter to overcome the effects due to partial shading and module mismatch. Whereas, the two-stage inverter requires more number of passive components and power electronic devices for boosting and inversion operations, which results in increased component count and reduced efficiency. Since, both of the single-stage and two-stage inverters have their own merits and demerits; hence they will optimally selected based on the power generating capacity.

In both of the inverter configurations, galvanic isolation from the leakage current is a major challenge to solve the safety and reliability issues of grid-

connected PVPGS. To address this issue, both the single-stage and two-stage inverters are further categorized into isolated type and non-isolated type based on the placement of transformer in the power conversion stage. A bulky line frequency transformer (LFT) in the AC grid side or a compact high frequency transformer (HFT) in the DC source side is normally employed to provide the galvanic isolation between the PV source and the grid. Besides the galvanic isolation, it also steps up the low PV output voltage. However, the use of transformer make the system become heavy, expensive and reduces its overall efficiency.

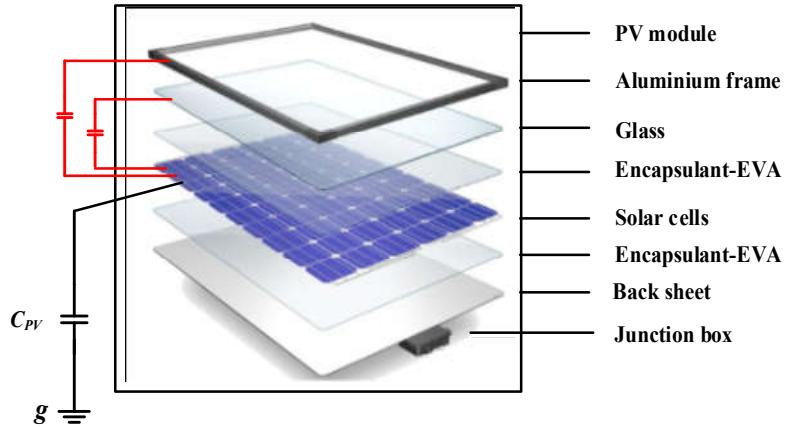

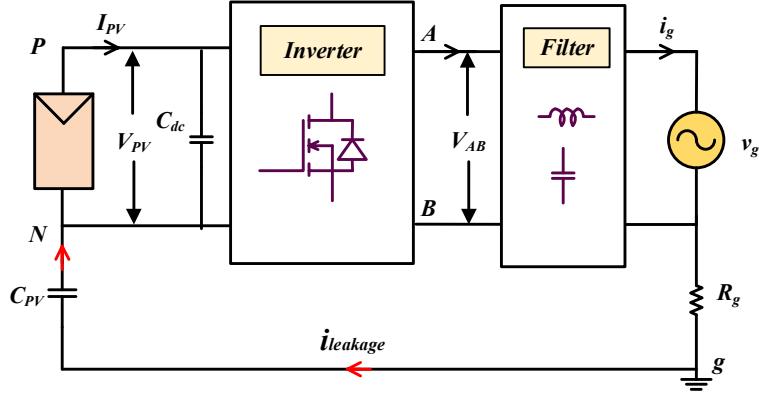

To alleviate the above drawbacks transformerless or non-isolated inverters becomes popular in the PVPGS. However, the removal of the transformer yields a direct connection between the inverter and PV module. In consequence, a resonant circuit is formed with the parasitic capacitances among PV module and ground, filter inductors and grid impedances. The common mode voltage (CMV) fluctuations produced by the inverter can excite this resonant circuit and causes the flow of leakage current from grid to PV module through PV parasitic capacitance ( $C_{PV}$ ). This increases electro-magnetic interference (EMI), total harmonic distortion (THD) and power losses, and also decreases the reliability and operational safety. Therefore, various topologies and different pulse width modulation (PWM) schemes have been proposed to reduce the leakage current and to enhance the overall system efficiency.

In contemporary, multilevel inverters (MLIs) are emerging in the area of grid-connected PVPGS because of its significant advantages like high quality of power output by lowering the THD, reduced losses with the reduction in voltage stress of the switches, reduced filter size with increased modularity. It is much more advantageous to have such benefits in non-isolated PV inverter topologies along with a reduction in leakage current. The popular MLI configurations are neutral point clamped (NPC), flying capacitor (FC) and cascaded H-bridge (CHB) inverters. The limitations of these MLIs are more component count, voltage balancing issues and control complexity for an increased number of output voltage levels. To overcome these drawbacks various other topologies are also developed in recent years. Most of these topologies utilizes the classical structures such as NPC, FC, CHB, and their variants. However, some of the

common limitations are stopping the usage of MLIs directly into grid-connected PVPGS such as higher leakage current, requirement of isolated DC sources, and increased component count.

Hence, there is a wide scope for further research in the area of single-phase inverter topologies for grid-connected PVPGS. Moreover, to address the aforesaid issues, namely, (i) operability with a single source, (ii) reduced switch count, (iii) leakage current reduction without the use of isolation transformer, (iv) reactive power capability, and (v) high efficiency, this research focuses on the development of different single-stage and two-stage inverter topologies for grid-connected PVPGS. In this context, four single-stage configurations and three two-stage configurations have been proposed in this thesis.

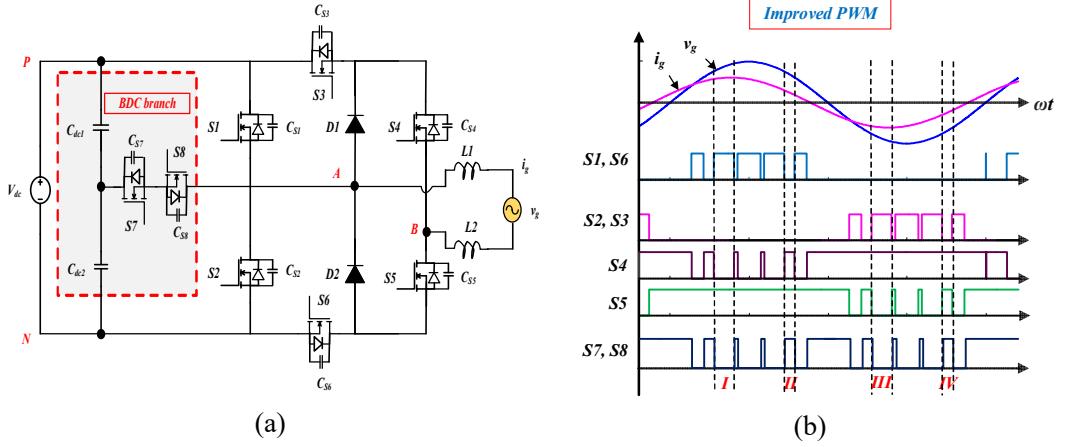

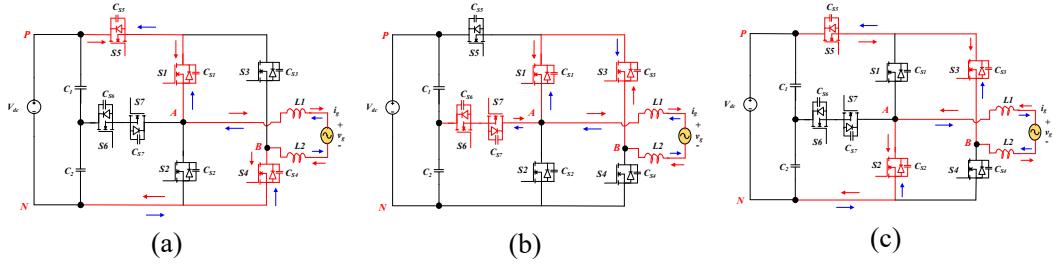

In the first proposal, a bi-directional clamping (BDC) based H5, Highly efficient reliable inverter concept (HERIC), and H6 TLI topologies are proposed with improved PWM schemes. BDC branch reduces the leakage current by clamping the inverter terminal voltages to half of the DC-link voltage during the freewheeling period and the improved PWM schemes ensure bi-directional current path while operating in negative power region. The common mode and differential characteristics of all the topologies are tested with MATLAB simulations and further justified with experimental results. Moreover, the performance characteristic comparisons of the proposed and traditional topologies are presented to highlight the merits of the proposed solution over the conventional.

In the second proposal, a novel two-stage power conditioner with the inherent benefits of boosting, generation of seven-level output voltage with minimum leakage current in a grid-connected PVPGS is proposed. The proposed power conditioner is an upgrade of a front-end multi output dc–dc boost converter and an asymmetrical seven-level inverter. A HFT employed in front-end converter produces balanced dc-link voltages to generate the seven-level output voltage. The leakage current caused by the parasitic capacitance of the PV panel is minimized by providing a common-mode conducting path to the inverter. This results in a reduction of the leakage current well below the grid standards. Furthermore, the proposed configuration utilizes a minimum number of devices

for every level generation, which reduces the control complexity and also improves the system efficiency.

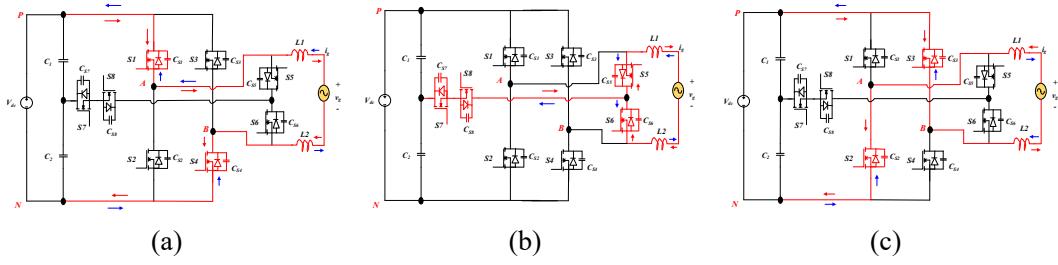

In the third proposal, a two-stage hybrid transformerless multilevel inverter for single-phase grid-connected PVPGS is presented. The proposed topology comprises a multilevel boost converter (MLBC) and a symmetrical hybrid MLI. MLBC combines the boosting and switched capacitor voltage functions to produce self-balanced multiple voltage levels. The proposed MLI is derived from a combination of bidirectional switches, a half bridge, and a diode-clamped branch, which can produce only two variations in the total common mode voltage and is capable of suppressing leakage current as per VDE 0126-1-1 grid standards. It offers the advantages of scalability, reactive power capability, reduced total harmonic distortion, and filter size.

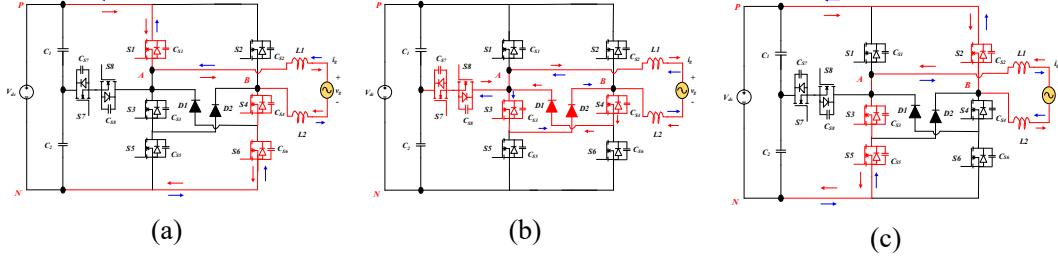

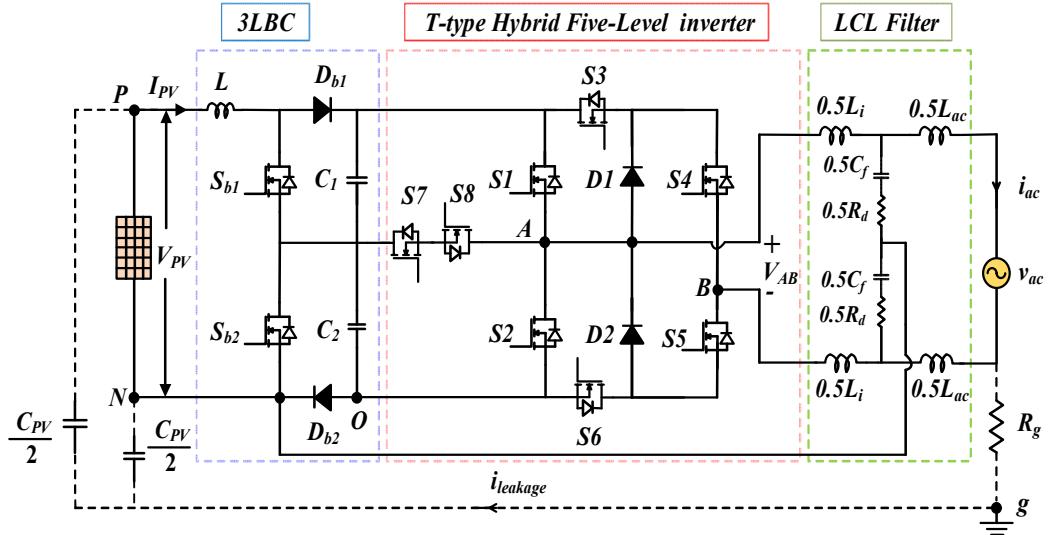

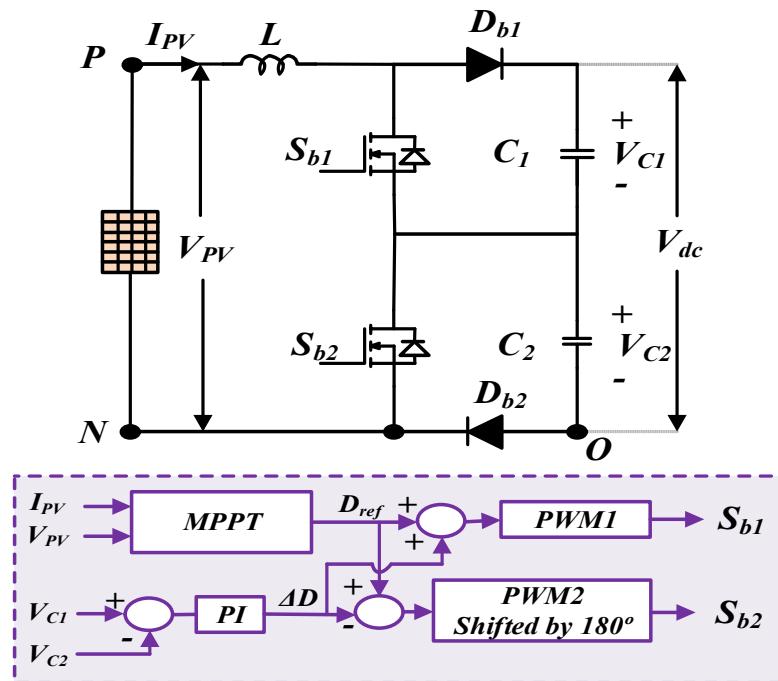

In the fourth proposal, a T-type hybrid five-level inverter and its level-shifted pulse width modulation scheme offers: (i) Reduced leakage current by eliminating the high frequency variations and sudden transitions in the voltage across PV parasitic capacitance, (ii) A path for the negative current in all the modes of operation under unity and non-unity power factor conditions of the grid without degrading the waveform quality. Moreover, the proposed inverter is integrated with a traditional three-level boost converter (3LBC) for boosting the PV output voltage and also to extract maximum power from the PV source. The 3LBC provides high efficiency and reduced input inductor size for the same power rating over the conventional boost converter.

In order to evolve steady state and dynamic performance of all the proposed topologies reported in the thesis, a thorough investigation of all the topologies has been achieved through both simulations and experiments. The simulations are performed in MATLAB/Simulink software and the proto type models are built using IRFP460 MOSFET modules and TLP250 opto coupler driver ICs. The control schemes are implemented in MATLAB Platform using Xilinx System Generator Blocks, Spartan 6 FPGA processor, and DSP TMS320F2812/28335 processor for real time operation. The grid-connected operation of the proposed topologies is verified using OPAL-RT OP4500 real-time modules. Moreover, in this study, an exhaustive comparison of various

topologies is shown based on component count, voltage stress across the semiconductor devices, common mode voltage behavior, and leakage current magnitude to demonstrate the merits of the proposed topologies. Finally, the performance of the proposed topologies is evaluated through Power Simulation (PSIM) thermal module and records maximum efficiency of 90-98%. This ensures that the proposed topologies are most opted for grid-connected PVPGS.

# TABLE OF CONTENTS

---

|                                                                                            |      |

|--------------------------------------------------------------------------------------------|------|

| <b>Acknowledgements</b> .....                                                              | ii   |

| <b>Abstract</b> .....                                                                      | iv   |

| <b>Table of Contents</b> .....                                                             | ix   |

| <b>List of Figures</b> .....                                                               | xiii |

| <b>List of Tables</b> .....                                                                | xxi  |

| <b>Abbreviations</b> .....                                                                 | xxii |

| <b>List of Symbols</b> .....                                                               | xxiv |

| <br>                                                                                       |      |

| <b>Chapter 1 Introduction</b> .....                                                        | 1    |

| 1.1. Background.....                                                                       | 2    |

| 1.2. PV Power Generation Systems.....                                                      | 3    |

| 1.2.1. Module Inverters.....                                                               | 3    |

| 1.2.2. String Inverters.....                                                               | 4    |

| 1.2.3. Multi-String Inverters.....                                                         | 4    |

| 1.2.4. Central Inverters.....                                                              | 6    |

| 1.3. Classification of PV Inverter Configurations.....                                     | 6    |

| 1.3.1. Single-Stage Isolated Inverter Configuration.....                                   | 7    |

| 1.3.2. Single-Stage Non-Isolated Inverter Configuration.....                               | 7    |

| 1.3.3. Two-Stage Isolated Inverter Configuration.....                                      | 8    |

| 1.3.4. Two-Stage Non-Isolated Inverter Configuration.....                                  | 9    |

| 1.4. Analysis of the Leakage Current in Non-Isolated Inverter<br>topologies                | 9    |

| 1.5. Multilevel Inverter Technology.....                                                   | 12   |

| 1.6. Important Standards Dealing with the Grid-Connected<br>PVPGS .....                    | 13   |

| 1.6.1. Leakage Current.....                                                                | 14   |

| 1.6.2. Total Harmonic Distortion.....                                                      | 14   |

| 1.6.3. Reactive Power Capability.....                                                      | 15   |

| 1.6.4. Standards and recommended practices for grid-<br>connected inverters in India ..... | 16   |

| 1.7. Summary.....                                                                          | 16   |

|                  |                                                                                         |    |

|------------------|-----------------------------------------------------------------------------------------|----|

| <b>Chapter 2</b> | <b>Literature Survey.....</b>                                                           | 17 |

| 2.1.             | Introduction.....                                                                       | 18 |

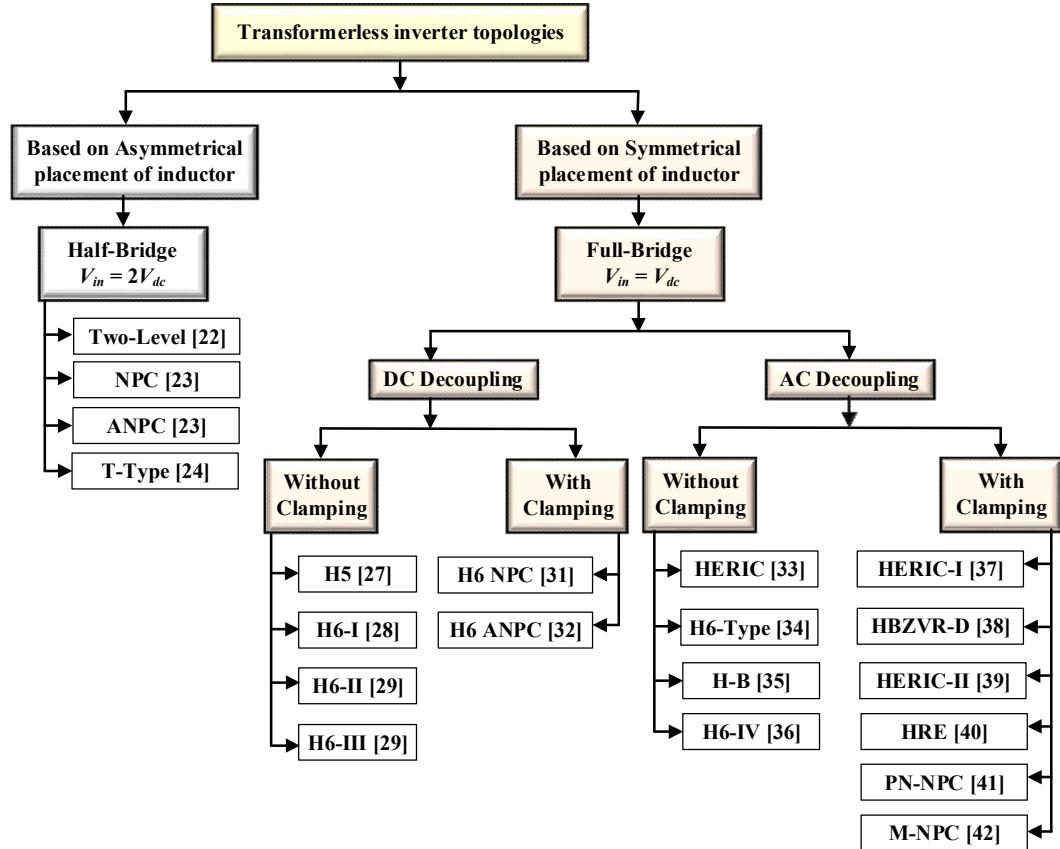

| 2.2.             | Classification of Single-Stage TLI Topologies.....                                      | 19 |

| 2.3.             | Classification of the Single-Stage Transformerless Multilevel<br>Topologies.....        | 32 |

| 2.4.             | Various types of Two-Stage Multilevel Inverter Topologies ...                           | 43 |

| 2.5.             | Problem Formulation.....                                                                | 49 |

| 2.6.             | Organization of the thesis.....                                                         | 49 |

| <b>Chapter 3</b> | <b>Bi-directional Transformerless Inverter Topologies .....</b>                         | 52 |

| 3.1.             | Introduction.....                                                                       | 53 |

| 3.2.             | Analysis of problems in H5, HERIC, H6, and Hybrid-Bridge<br>TLI topologies.....         | 54 |

| 3.2.1.           | Analysis of oscillations in the junction capacitance of<br>the switches.....            | 56 |

| 3.2.2.           | Analysis of the Bi-directional current path in the<br>traditional TLI topologies.....   | 58 |

| 3.3.             | Proposed BDC based H5, HERIC, H6, and Hybrid-Bridge<br>TLI topologies.....              | 60 |

| 3.3.1.           | Operating states.....                                                                   | 60 |

| 3.3.2.           | Improved PWM strategies.....                                                            | 63 |

| 3.4.             | Selection of passive components.....                                                    | 66 |

| 3.5.             | Simulation results.....                                                                 | 66 |

| 3.6.             | Experimental results.....                                                               | 70 |

| 3.6.1.           | Dynamic performance.....                                                                | 79 |

| 3.7.             | Evaluation of Efficiency using PSIM thermal module.....                                 | 81 |

| 3.8.             | Summary.....                                                                            | 83 |

| 3.9.             | Contributions.....                                                                      | 84 |

| 3.10.            | Papers Published.....                                                                   | 84 |

| <b>Chapter 4</b> | <b>A Two-Stage Seven-Level Power Conditioner for Photovoltaic<br/>Applications.....</b> | 85 |

| 4.1.             | Introduction.....                                                                       | 86 |

| 4.2.             | System configuration.....                                                               | 87 |

| 4.2.1.           | Front-end DC-DC boost converter.....                                                    | 87 |

|                                                                                           |            |

|-------------------------------------------------------------------------------------------|------------|

| 4.2.2. Asymmetrical seven-level inverter.....                                             | 89         |

| 4.2.3. Closed-loop control system.....                                                    | 89         |

| 4.3. Leakage current analysis.....                                                        | 94         |

| 4.4. Selection of passive filter components.....                                          | 97         |

| 4.5. Simulation and experimental results.....                                             | 97         |

| 4.5.1. Dynamic performance.....                                                           | 103        |

| 4.6. Evaluation of losses.....                                                            | 106        |

| 4.7. Comparison of the proposed inverter with the existing<br>two-stage PV inverters..... | 110        |

| 4.8. Summary.....                                                                         | 111        |

| 4.9. Contributions.....                                                                   | 111        |

| 4.10. Papers Published.....                                                               | 111        |

| <b>Chapter 5 A Two-Stage Hybrid Transformerless Multilevel<br/>Inverter.....</b>          | <b>112</b> |

| 5.1. Introduction.....                                                                    | 113        |

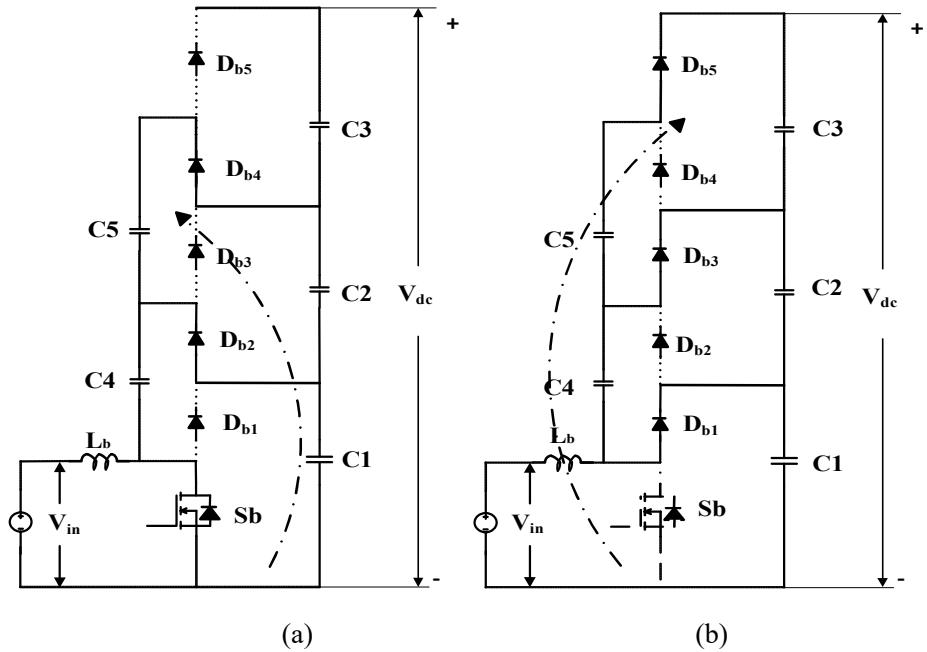

| 5.2. System description.....                                                              | 113        |

| 5.3. Operation of the multi-level boost converter.....                                    | 115        |

| 5.4. Proposed hybrid transformerless multilevel inverter.....                             | 116        |

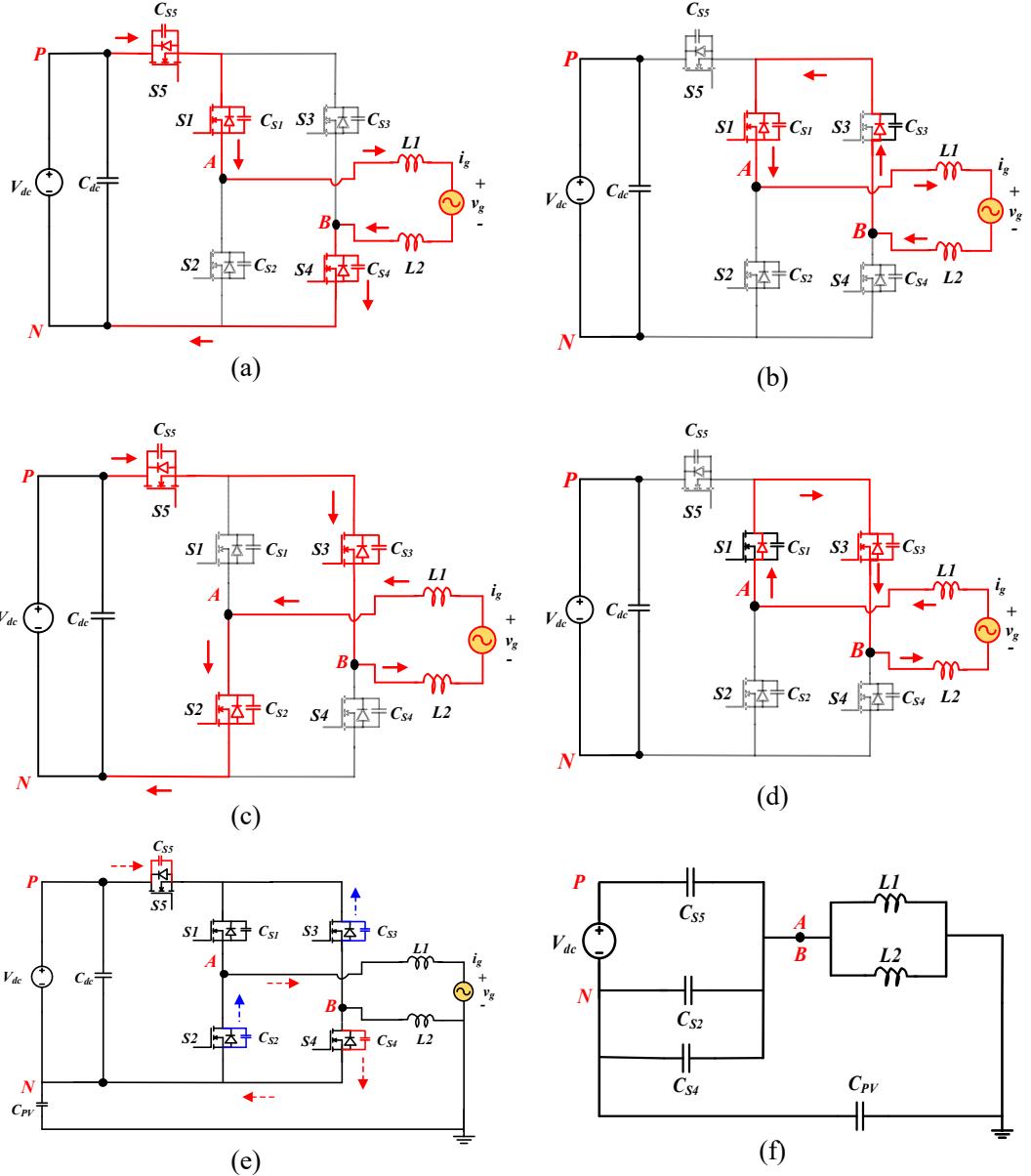

| 5.4.1. Operating states of the inverter in different modes.....                           | 116        |

| 5.5. Modified SLS-PWM technique with reactive power capability                            | 121        |

| 5.6. Common-mode voltage analysis.....                                                    | 124        |

| 5.7. Simulation results.....                                                              | 125        |

| 5.8. Experimental results.....                                                            | 131        |

| 5.9. Comparison with existing topologies.....                                             | 135        |

| 5.10. Efficiency calculation.....                                                         | 137        |

| 5.11. Summary.....                                                                        | 139        |

| 5.12. Contributions.....                                                                  | 140        |

| 5.13. Papers Published.....                                                               | 140        |

| <b>Chapter 6 A Two-Stage T-type Hybrid Five-Level Transformerless<br/>Inverter .....</b>  | <b>141</b> |

| 6.1. Introduction.....                                                                    | 142        |

| 6.2. System description.....                                                              | 143        |

| 6.2.1. Front-end 3LBC.....                                                                | 143        |

|                                                                                  |            |

|----------------------------------------------------------------------------------|------------|

| 6.3. Proposed T-Type Hybrid TLI.....                                             | 145        |

| 6.3.1. Circuit structure.....                                                    | 145        |

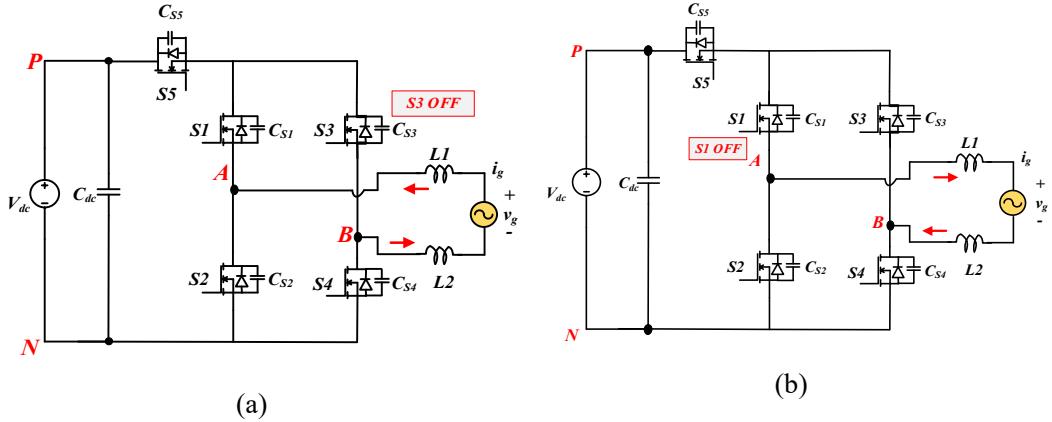

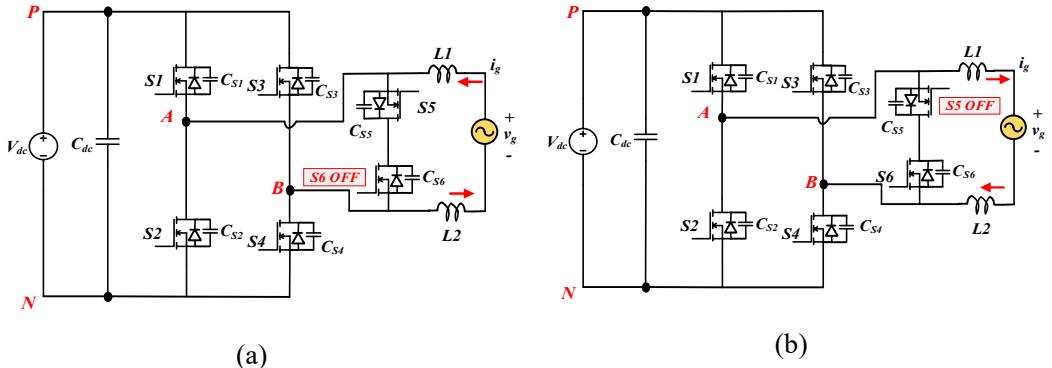

| 6.3.2. Operating states.....                                                     | 145        |

| 6.3.3. Closed-loop control.....                                                  | 149        |

| 6.4. Common-mode voltage analysis.....                                           | 150        |

| 6.5. Simulation results.....                                                     | 153        |

| 6.6. Experimental results.....                                                   | 156        |

| 6.7. Comparison of the proposed TLI with other Five-level TLI<br>Topologies..... | 160        |

| 6.8. Summary.....                                                                | 166        |

| 6.9. Contributions.....                                                          | 167        |

| 6.10. Papers Published.....                                                      | 167        |

| <b>Chapter 7 Conclusion and Future scope.....</b>                                | <b>168</b> |

| 7.1. Conclusion.....                                                             | 169        |

| 7.2. Author's contribution.....                                                  | 172        |

| 7.3. Future scope.....                                                           | 173        |

| <b>References.....</b>                                                           | <b>175</b> |

| <b>List of Publications.....</b>                                                 | <b>183</b> |

| <b>Bio-Data.....</b>                                                             | <b>185</b> |

## LIST OF FIGURES

---

---

|           |                                                                                                                                                                       |    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.1  | Global evaluation of PV installations.                                                                                                                                | 2  |

| Fig. 1.2  | Grid-connected PVPGS technologies: (a) AC module, (b) DC Optimizer, (c) String inverter, (d) Multi-String inverter, and (e) Central inverter.                         | 5  |

| Fig. 1.3  | Single-stage isolated inverter configuration.                                                                                                                         | 7  |

| Fig. 1.4  | Single-stage non-isolated inverter configuration.                                                                                                                     | 8  |

| Fig. 1.5  | Two-stage isolated inverter configuration with: (a) LFT and (b) HFT.                                                                                                  | 8  |

| Fig. 1.6  | Two-stage non-isolated inverter topology.                                                                                                                             | 9  |

| Fig. 1.7  | Parasitic capacitance of the PV module.                                                                                                                               | 10 |

| Fig. 1.8  | Typical structure of non-isolated inverter configuration with most significant stray elements.                                                                        | 11 |

| Fig. 1.9  | Classical multilevel inverter topologies: (a) Neutral-point clamped, (b) Flying capacitor and (c) Cascaded H-bridge.                                                  | 13 |

| Fig. 2.1  | Classification of single-stage TLI topologies based on inductor placement.                                                                                            | 20 |

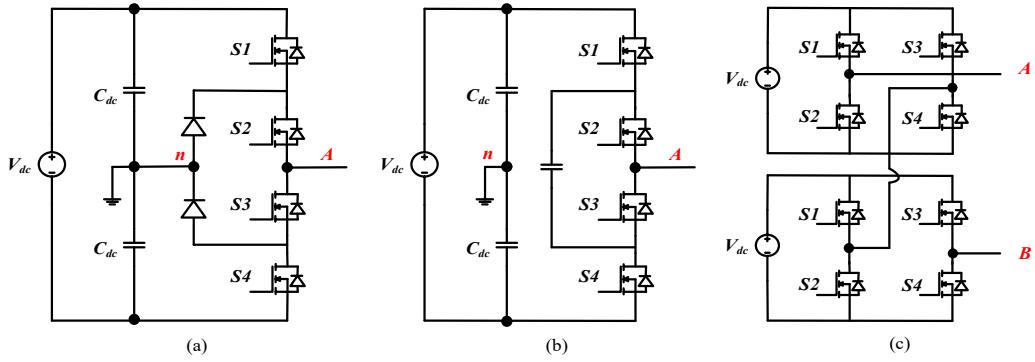

| Fig. 2.2  | Asymmetrical inductor based TLI topologies: (a) Two-level inverter, (b) Three-level NPC inverter, (c) Three-level ANPC inverter, and (d) Three-level T-Type inverter. | 21 |

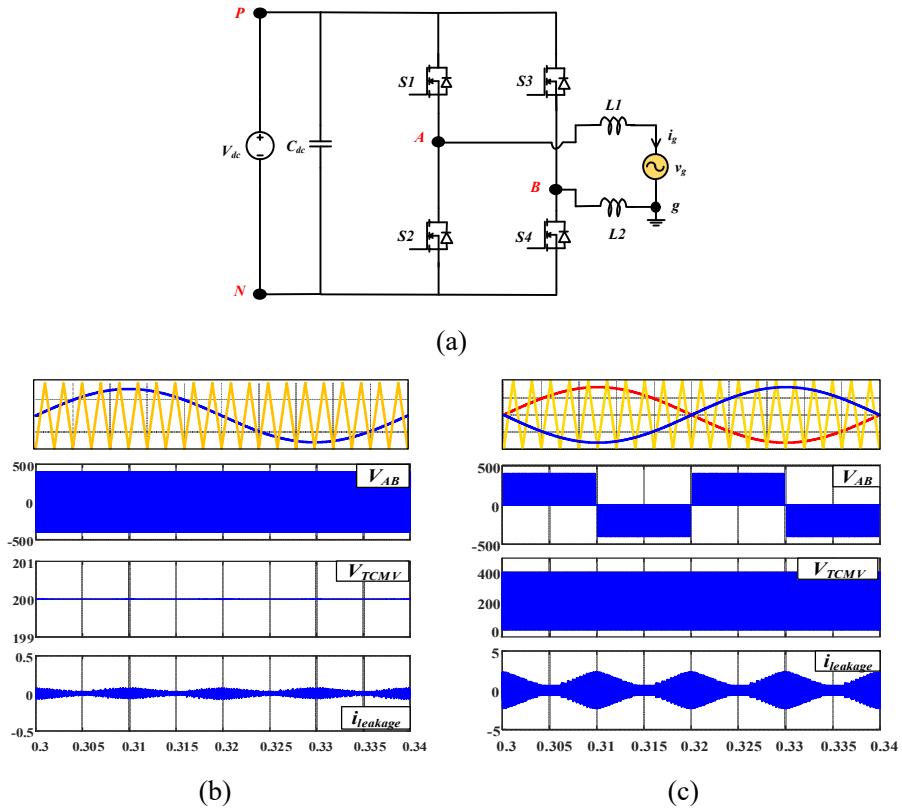

| Fig. 2.3  | (a) Full-bridge inverter, (b) Bipolar PWM, (c) Unipolar PWM.                                                                                                          | 22 |

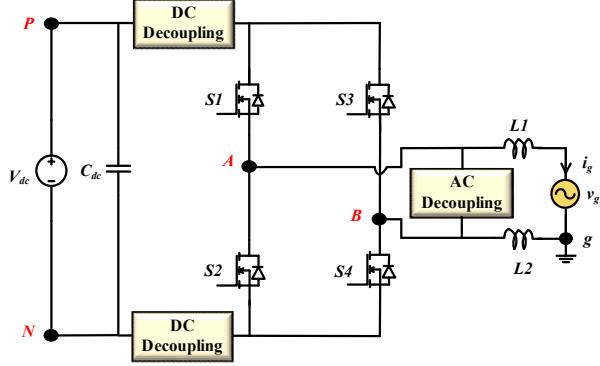

| Fig. 2.4  | Full-bridge inverter with decoupling network.                                                                                                                         | 23 |

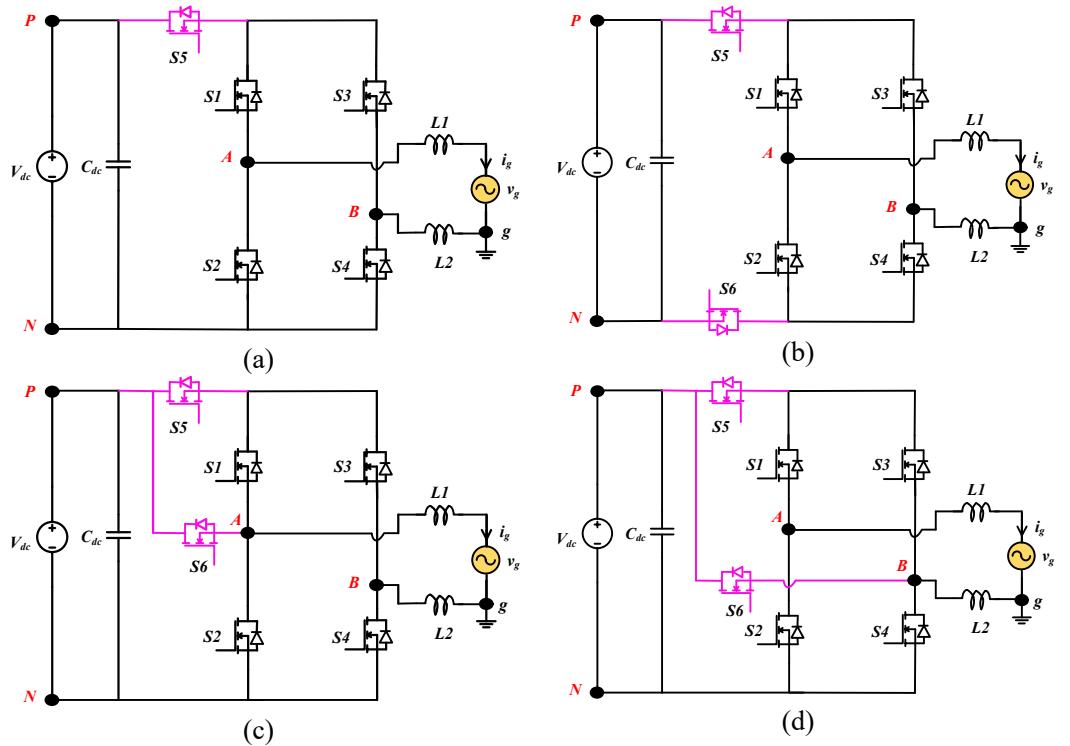

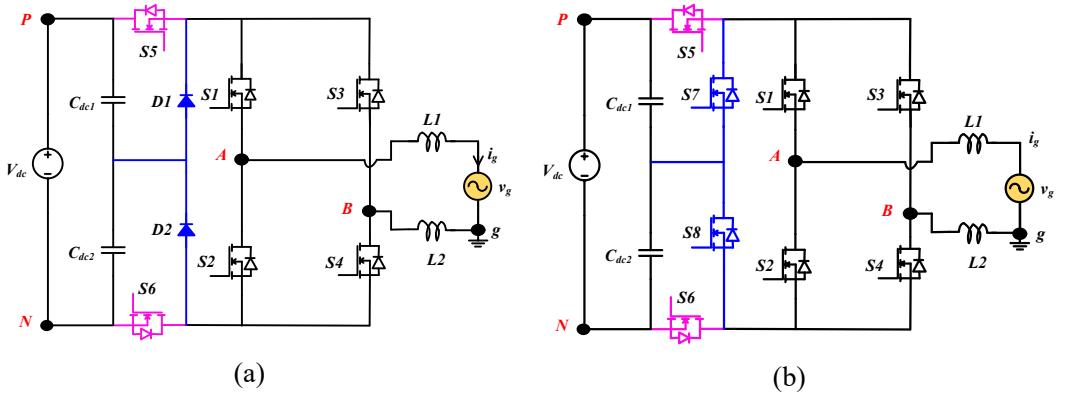

| Fig. 2.5  | DC decoupling based: (a) H5 inverter, (b) H6-I inverter, (c) H6-II inverter, and (d) H6-III inverter.                                                                 | 23 |

| Fig. 2.6  | DC decoupling based: (a) Passive clamped NPC H6 inverter, and (b) ANPC H6 inverter.                                                                                   | 24 |

| Fig. 2.7  | AC decoupling based: (a) HERIC, (b) H6-Type, (c) Hybrid-bridge, and (d) H6-IV.                                                                                        | 26 |

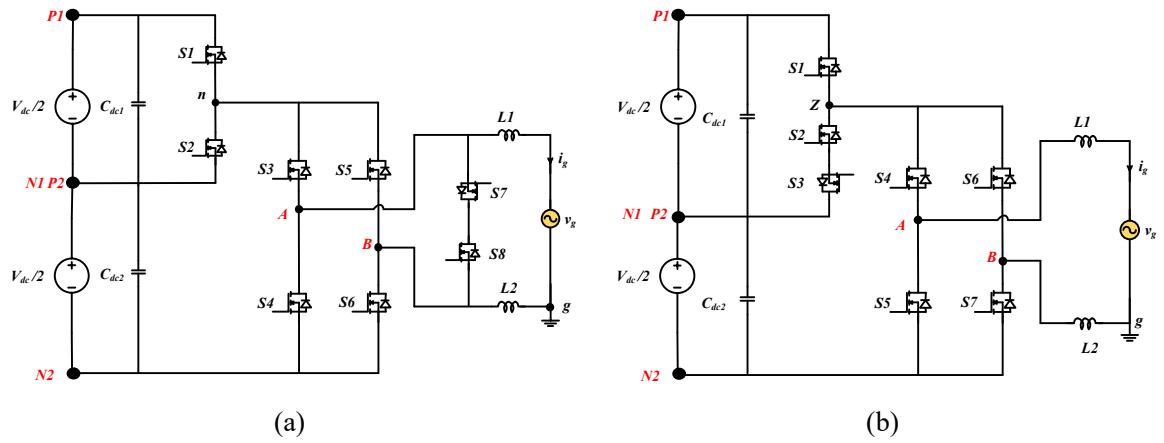

| Fig. 2.8  | AC decoupling based: (a) Passive clamped HERIC-I, (b) HBZVR-D, (c) Active clamped HERIC-II, (d) HRE, (e) PN-NPC, and (f) M-NPC.                                       | 27 |

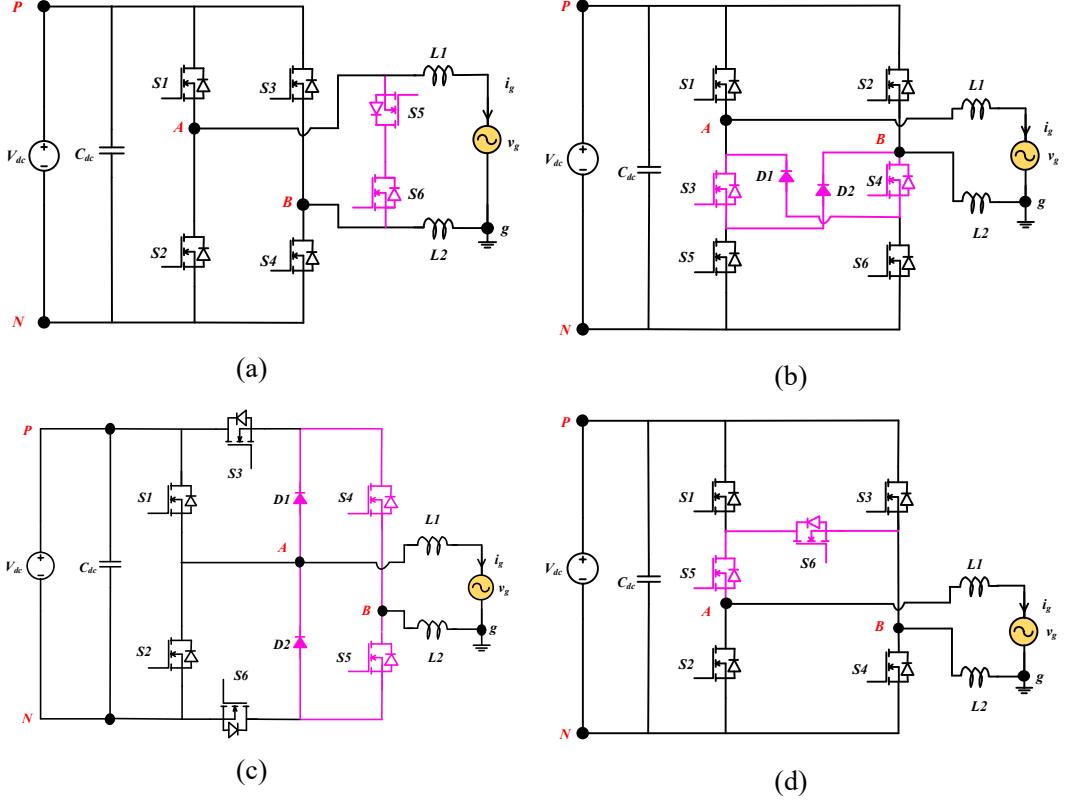

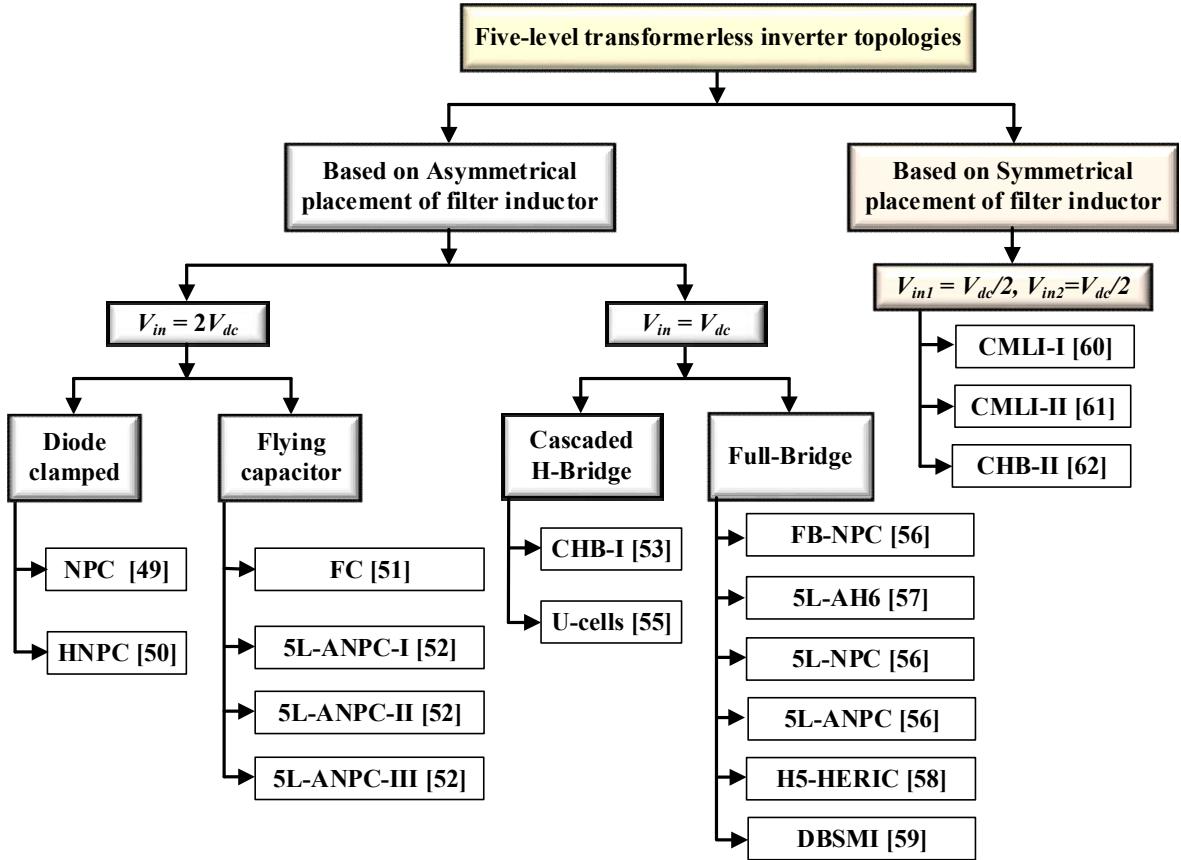

| Fig. 2.9  | Classification of the single-stage five-level TLI topologies based on inductor placement.                                                                             | 33 |

| Fig. 2.10 | (a) Diode clamped MLI, (b) HNPC MLI.                                                                                                                                  | 34 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.11 | (a) Flying capacitor MLI, (b) 5L-ANPC-I, (c) 5L-ANPC-II, and (d) 5L-ANPC-III.                                                                                                                                                                                                                                                                                                                                | 34 |

| Fig. 2.12 | Five-level (a) CHB-I inverter topology, (b) Packed U-cells inverter topology                                                                                                                                                                                                                                                                                                                                 | 35 |

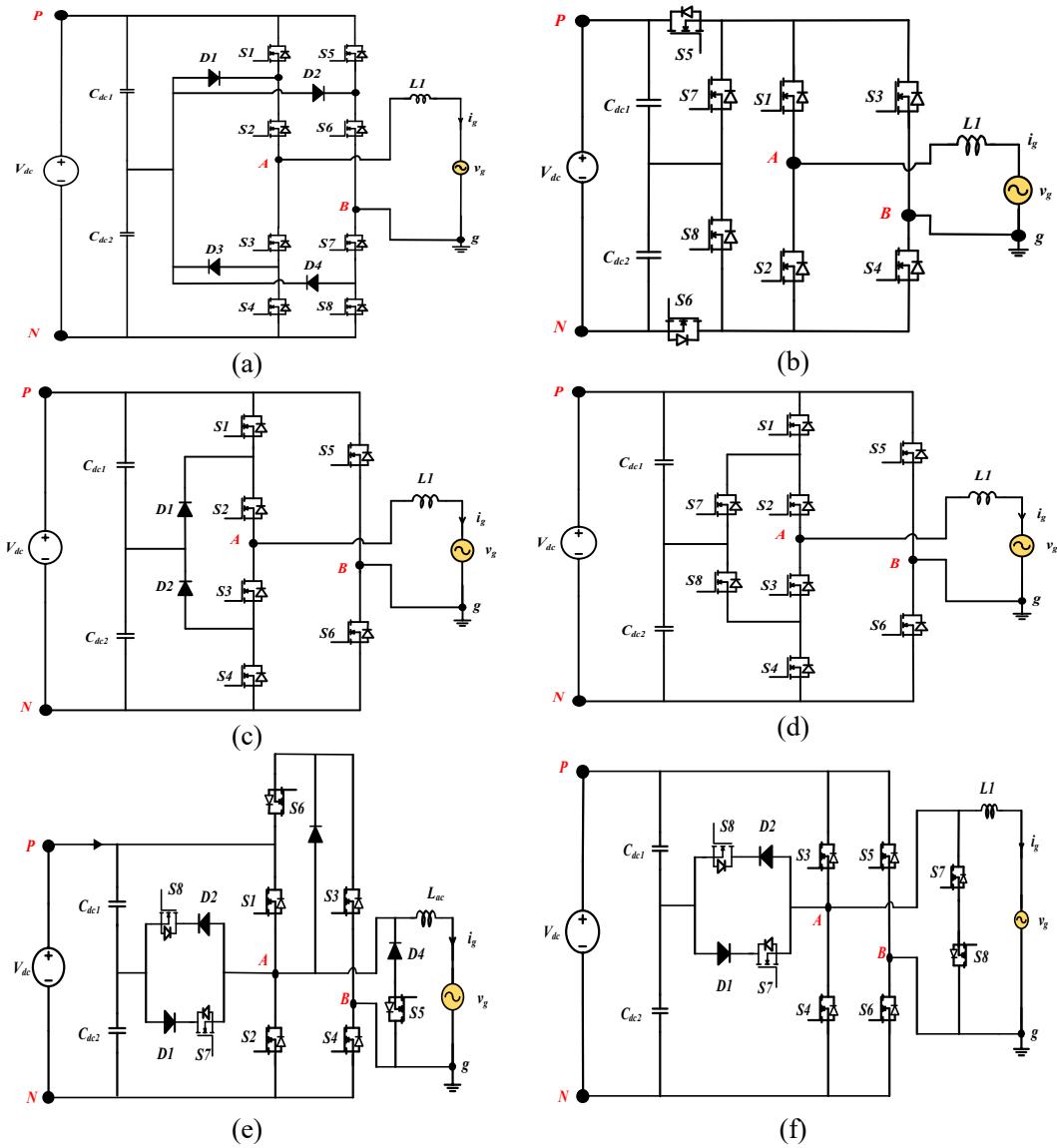

| Fig. 2.13 | F-B based five-level topologies: (a) FB-NPC, (b) 5L-AH6, (c) 5L-NPC, (d) 5L-ANPC, (e) H5-HERIC, and (f) DBSMI.                                                                                                                                                                                                                                                                                               | 37 |

| Fig. 2.14 | Symmetrical Five-Level TLI topologies: (a) Cascaded MLI (CMLI)-I, (b) CMLI-II, and (c) CHB-II.                                                                                                                                                                                                                                                                                                               | 39 |

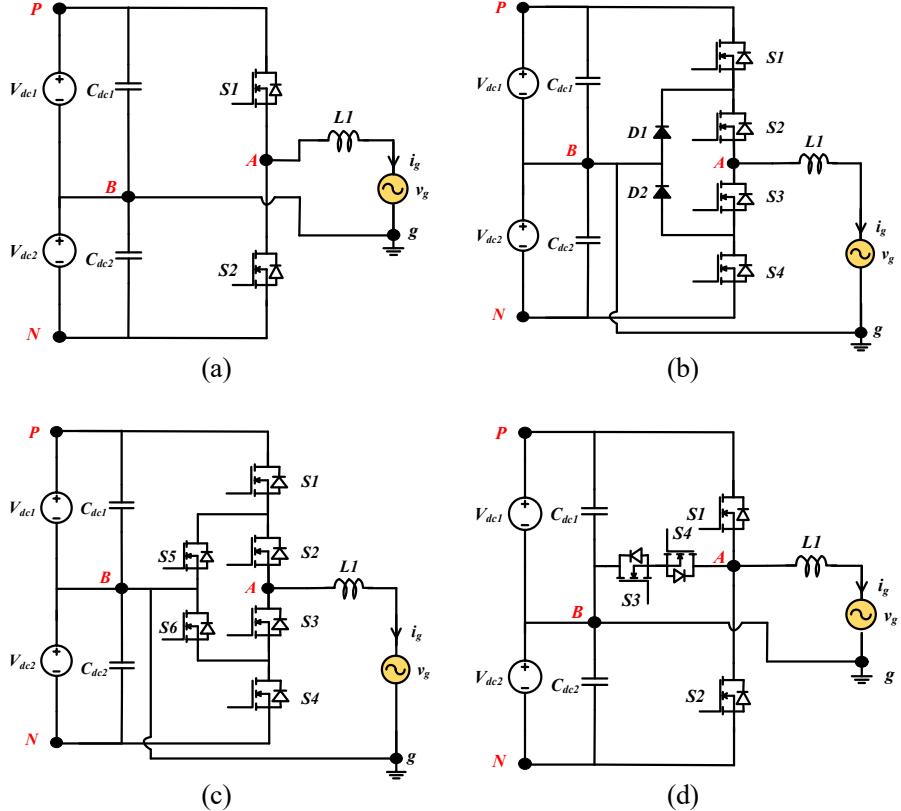

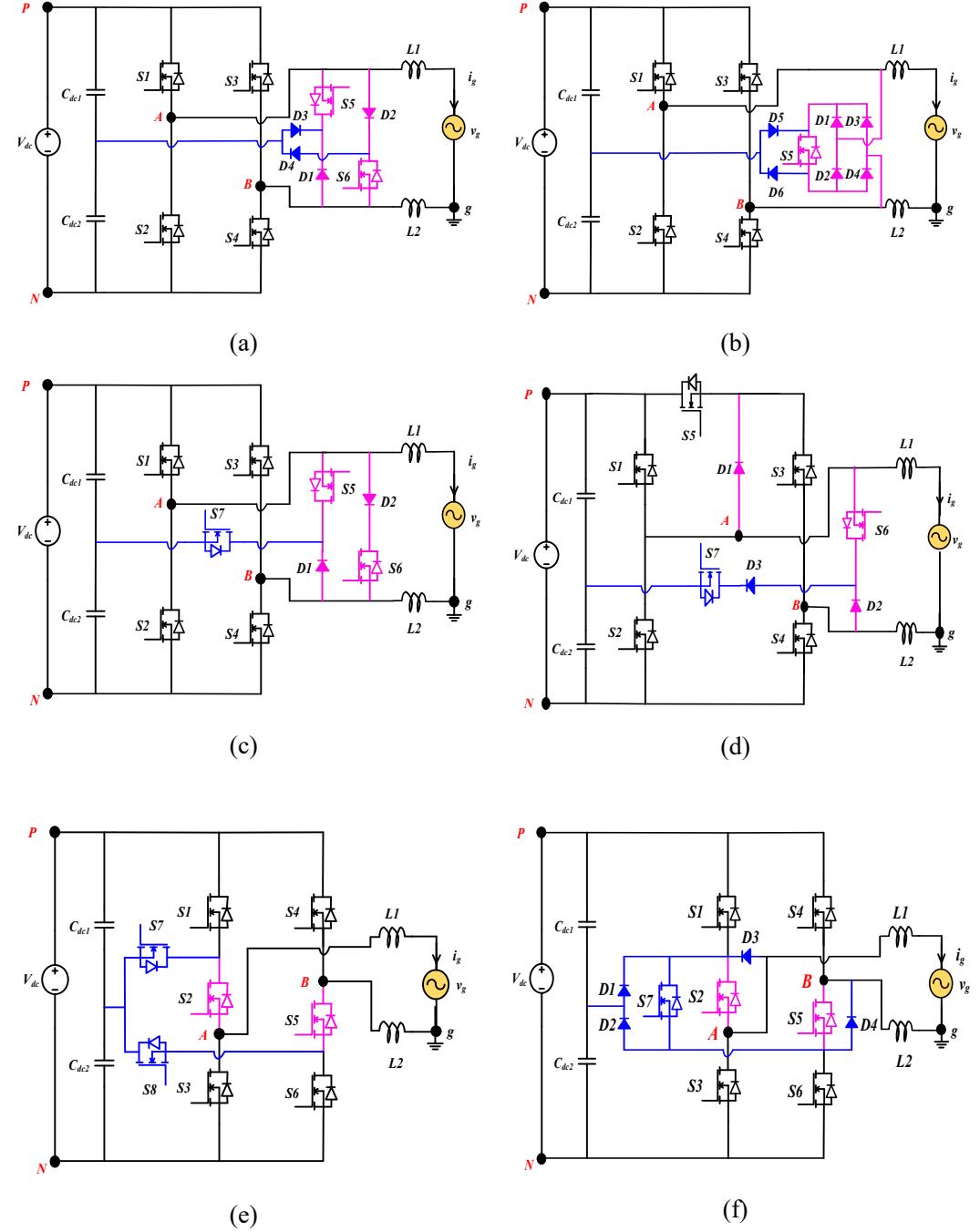

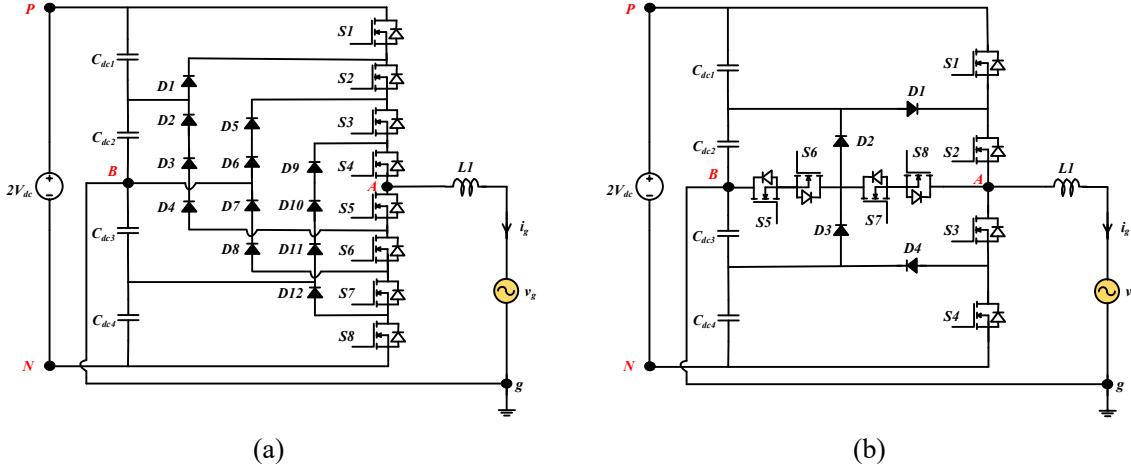

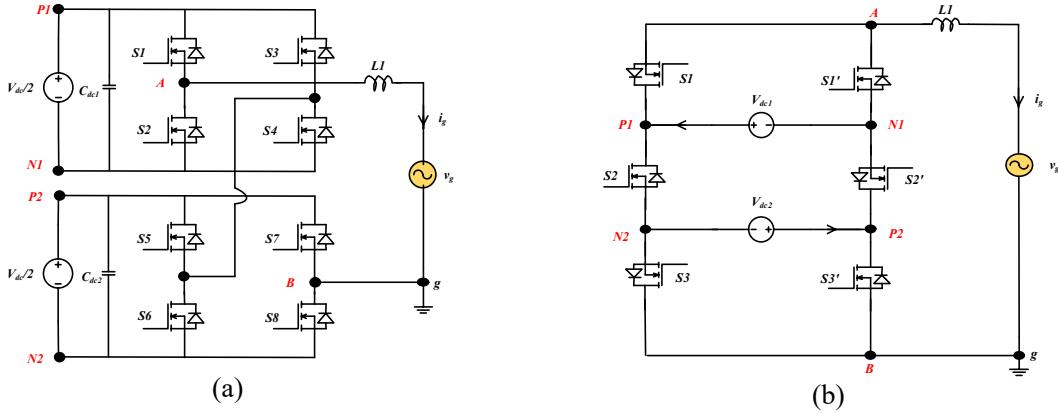

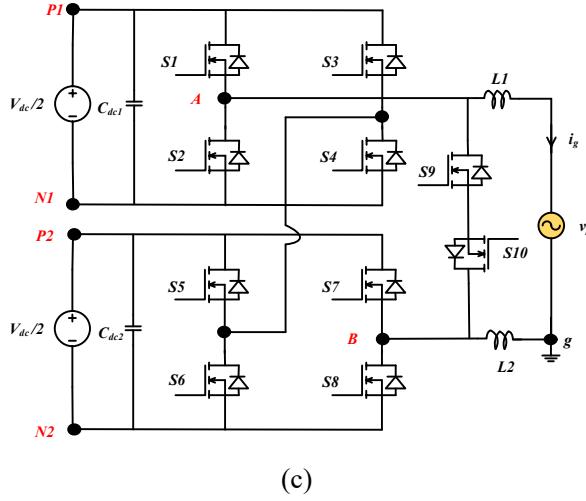

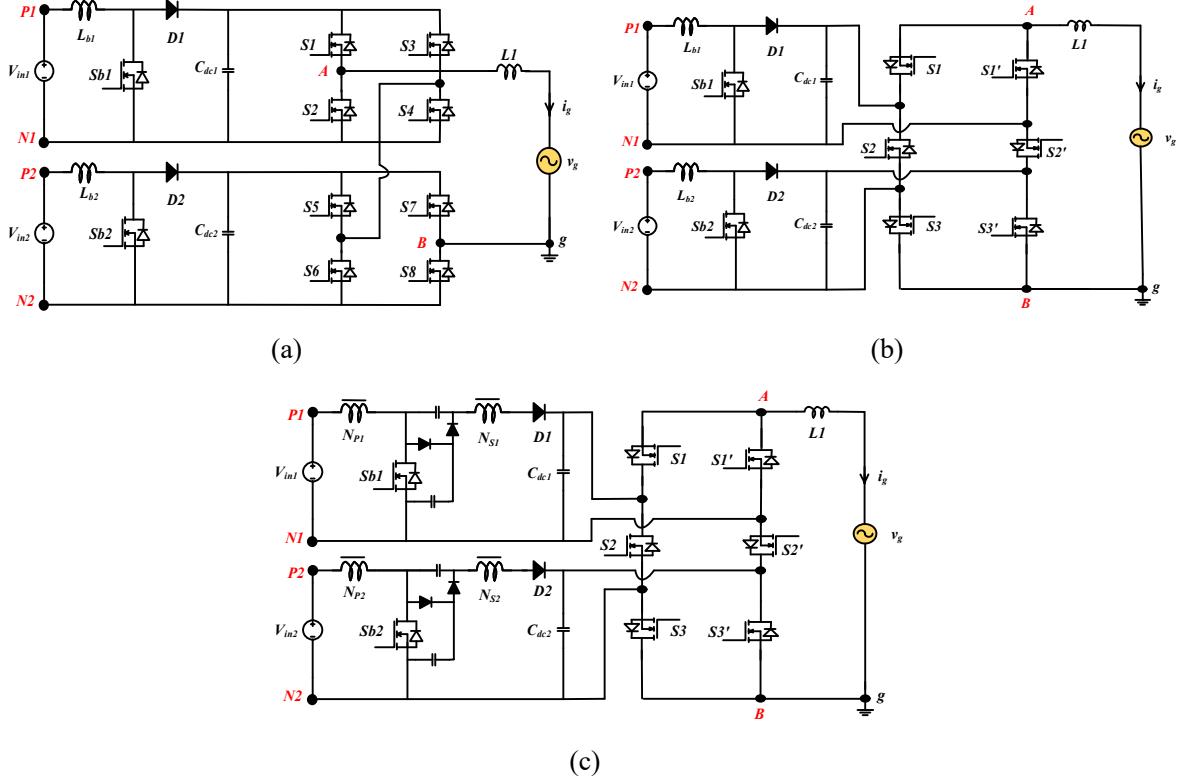

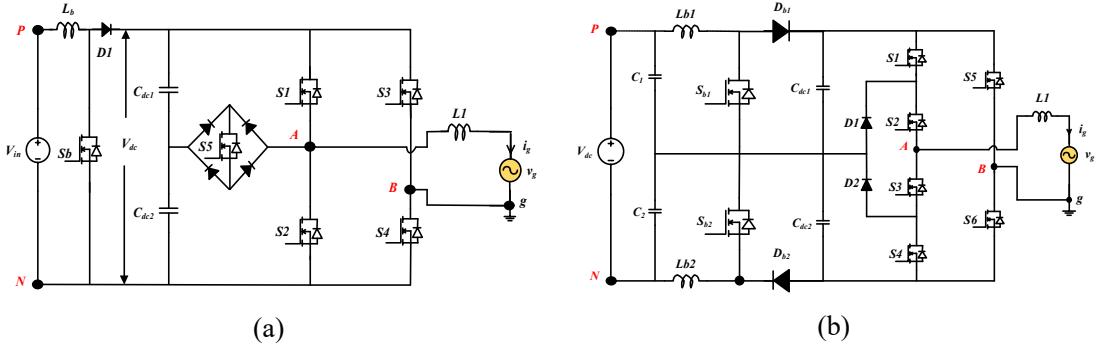

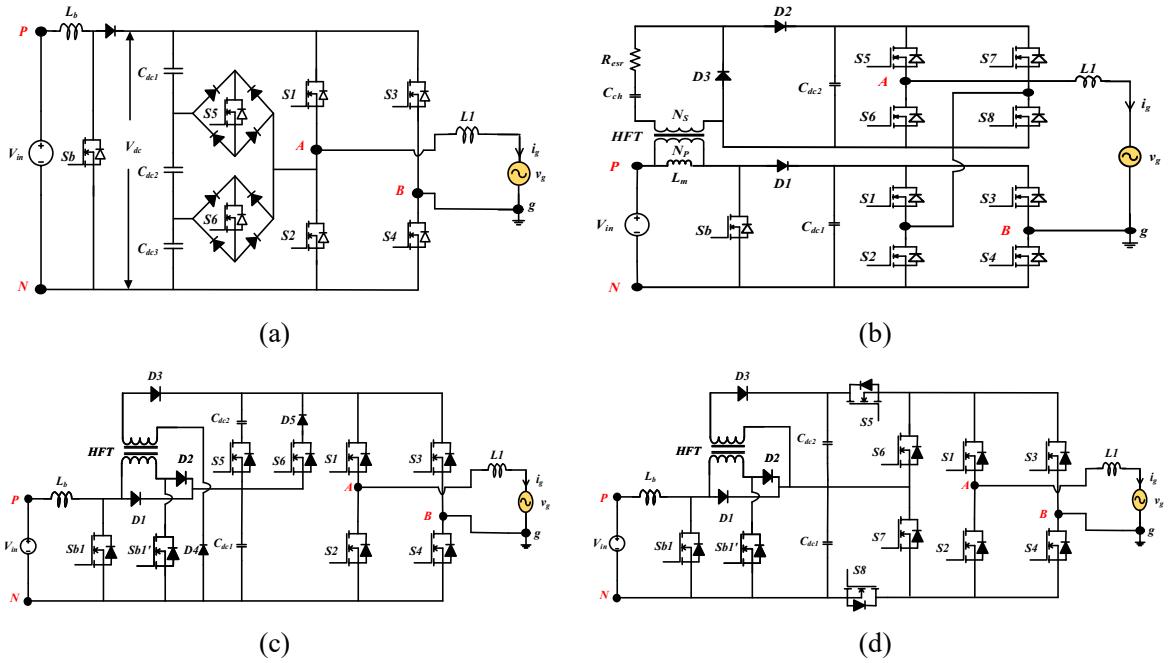

| Fig. 2.15 | Two-stage dual DC source based five-level inverter (a) Topology 1, (b) Topology 2, and (c) Topology 3.                                                                                                                                                                                                                                                                                                       | 44 |

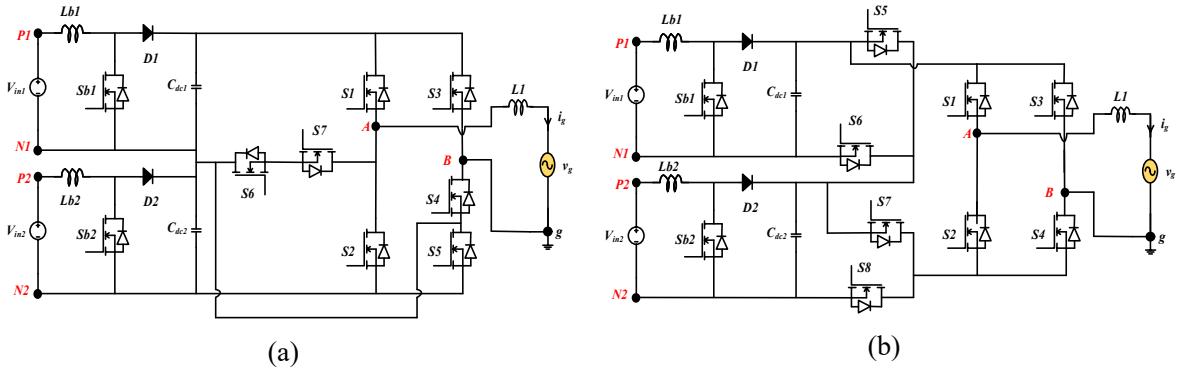

| Fig. 2.16 | Two-stage single DC source based five-level inverter (a) Topology 1, (b) Topology 2.                                                                                                                                                                                                                                                                                                                         | 45 |

| Fig. 2.17 | Two-stage dual DC source based seven-level inverter (a) Topology 1 (b) Topology 2.                                                                                                                                                                                                                                                                                                                           | 45 |

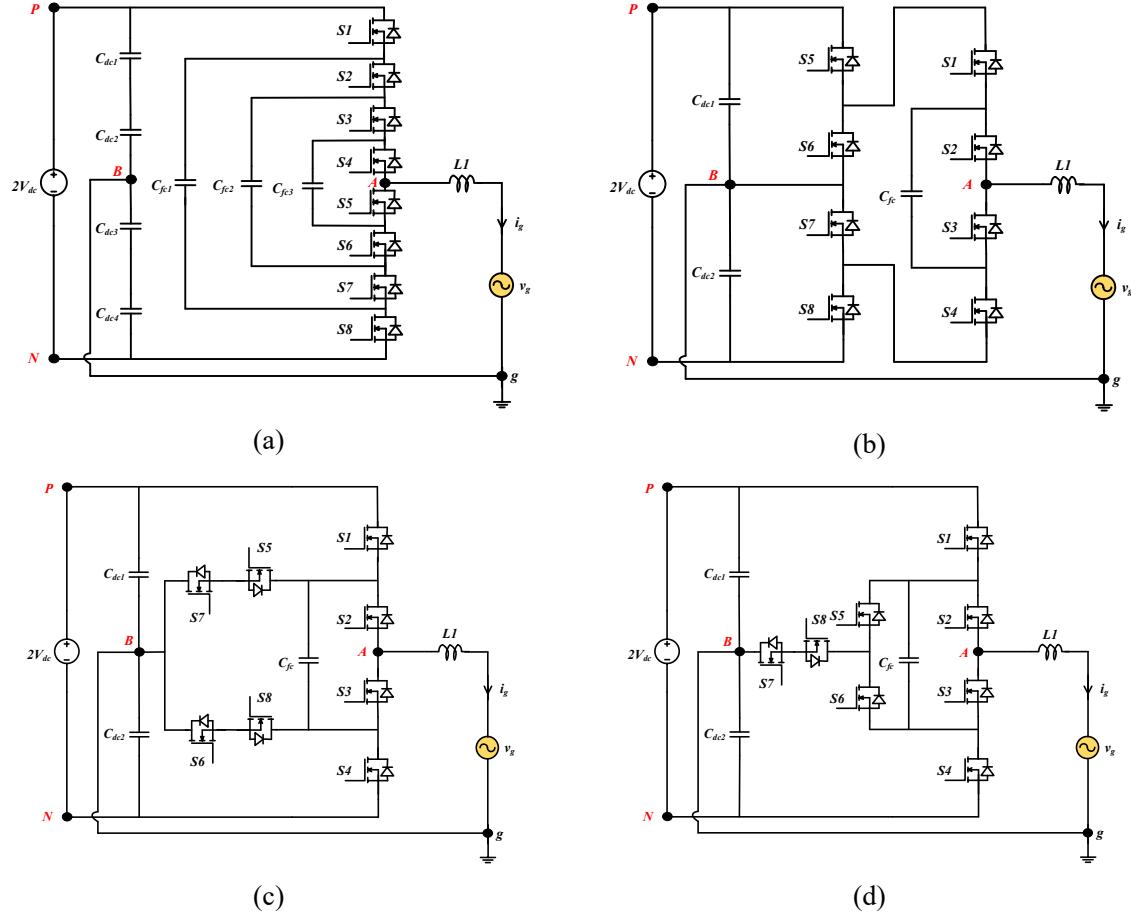

| Fig. 2.18 | Two-stage single DC source based seven-level inverter (a) Topology 1, (b) Topology 2, (c) Topology 3, (d) Topology 4.                                                                                                                                                                                                                                                                                        | 46 |

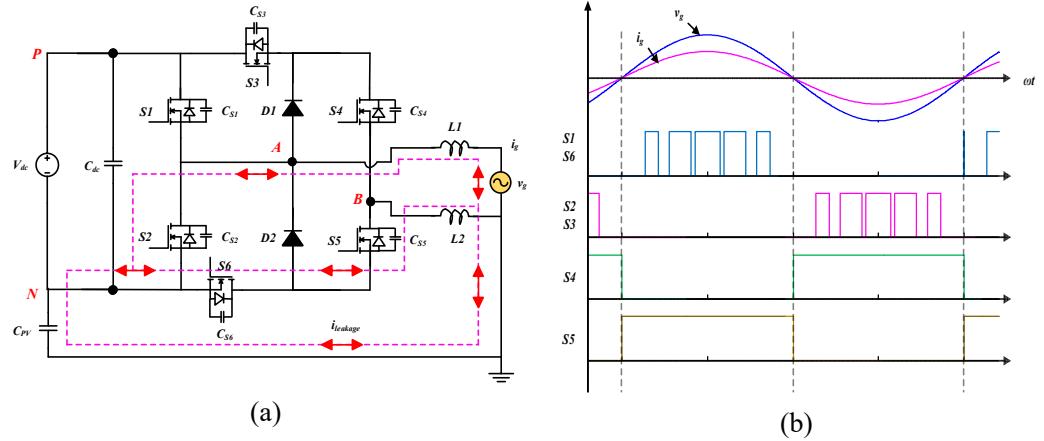

| Fig. 3.1  | H5 TLI: (a) circuit structure (b) gate pulses.                                                                                                                                                                                                                                                                                                                                                               | 54 |

| Fig. 3.2  | HERIC TLI: (a) circuit structure (b) gate pulses.                                                                                                                                                                                                                                                                                                                                                            | 54 |

| Fig. 3.3  | H6 TLI: (a) circuit structure (b) gate pulses.                                                                                                                                                                                                                                                                                                                                                               | 55 |

| Fig. 3.4  | H-B TLI: (a) circuit structure (b) gate pulses.                                                                                                                                                                                                                                                                                                                                                              | 55 |

| Fig. 3.5  | Operating states, charging and discharging of switch junction capacitances of H5 topology in positive power transferring mode: (a) Positive half cycle, (b) Freewheeling period during positive half cycle, (c) Negative half cycle, (d) Freewheeling period during negative half cycle, (e) Charging and discharging of switch junction capacitances during positive half cycle and (f) Simplified circuit. | 57 |

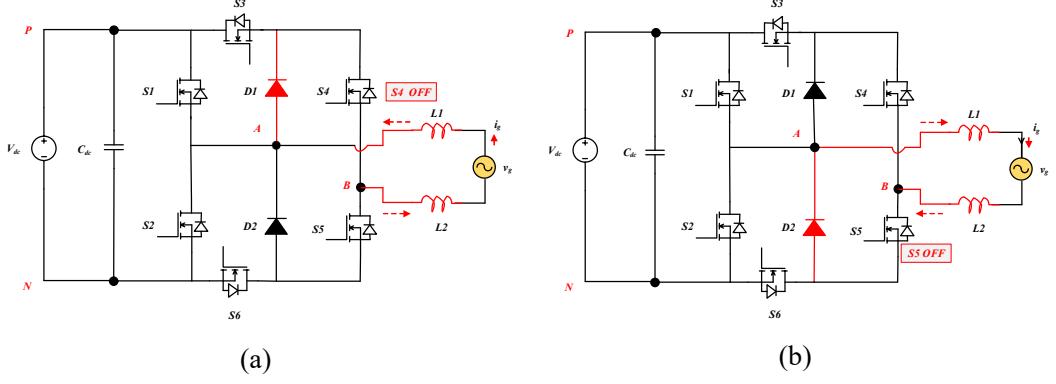

| Fig. 3.6  | H5 topology during negative power region; (a) positive $v_g$ and negative $i_g$ , (b) negative $v_g$ and positive $i_g$ .                                                                                                                                                                                                                                                                                    | 59 |

| Fig. 3.7  | HERIC topology during negative power region; (a) positive $v_g$ and negative $i_g$ , (b) negative $v_g$ and positive $i_g$ .                                                                                                                                                                                                                                                                                 | 59 |

| Fig. 3.8  | H6 topology during negative power region; (a) positive $v_g$ and negative $i_g$ , (b) negative $v_g$ and positive $i_g$ .                                                                                                                                                                                                                                                                                    | 59 |

|           |                                                                                                                                                  |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.9  | H-B topology during negative power region; (a) positive $v_g$ and negative $i_g$ , (b) negative $v_g$ and positive $i_g$ .                       | 60 |

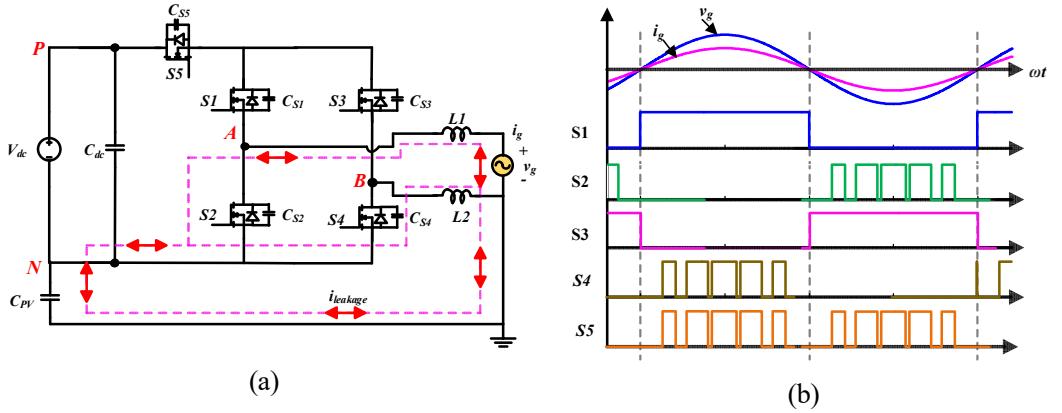

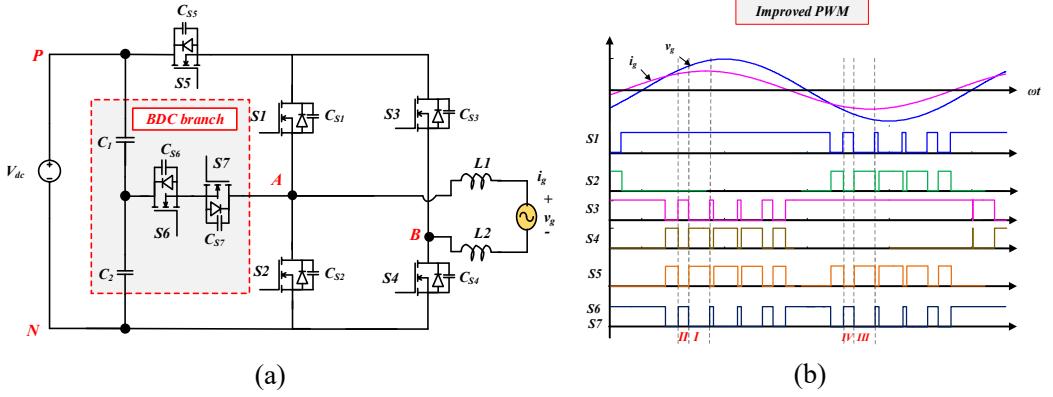

| Fig. 3.10 | BDC-H5 TLI: (a) Circuit diagram, (b) improved PWM.                                                                                               | 61 |

| Fig. 3.11 | BDC-HERIC TLI: (a) Circuit diagram, (b) improved PWM.                                                                                            | 61 |

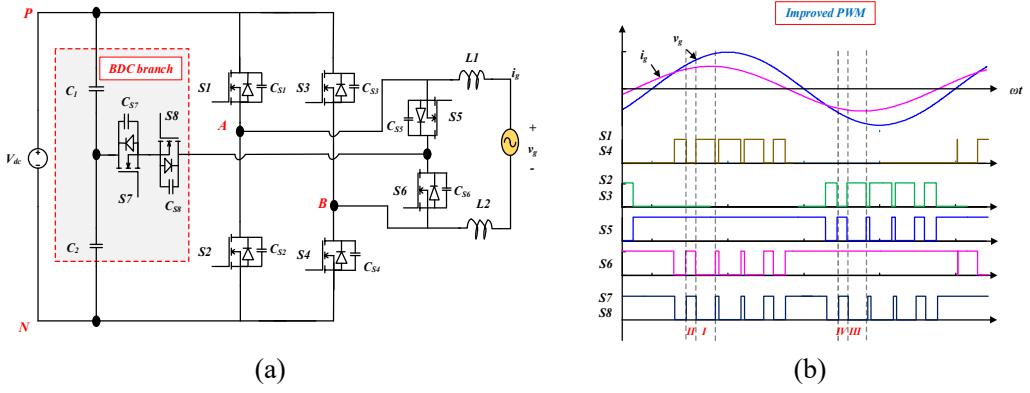

| Fig. 3.12 | BDC-H6 TLI: (a) Circuit diagram, (b) improved PWM.                                                                                               | 61 |

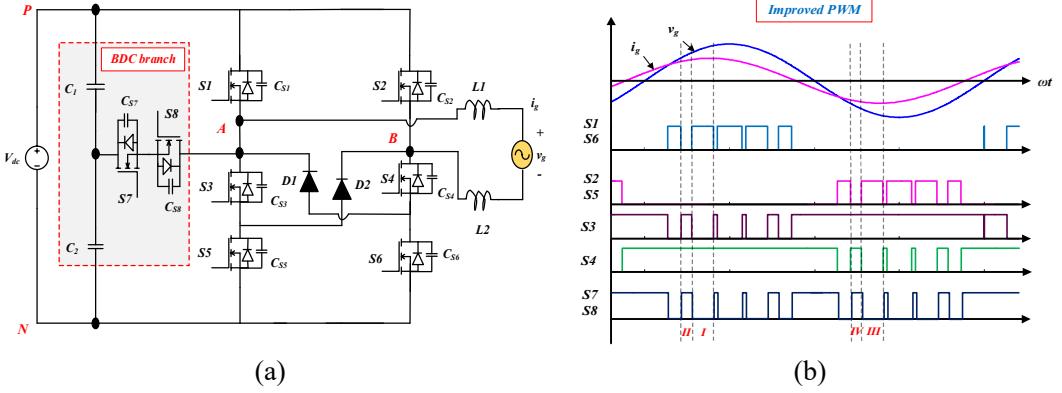

| Fig. 3.13 | BDC-H-B TLI: (a) Circuit diagram, (b) improved PWM.                                                                                              | 61 |

| Fig. 3.14 | Operating modes of the BDC-H5 inverter (a) $V_{AB} = V_{dc}$ , (b) $V_{AB} = 0$ , (c) $V_{AB} = -V_{dc}$ .                                       | 63 |

| Fig. 3.15 | Operating modes of the BDC-HERIC inverter (a) $V_{AB} = V_{dc}$ , (b) $V_{AB} = 0$ , (c) $V_{AB} = -V_{dc}$ .                                    | 63 |

| Fig. 3.16 | Operating modes of the BDC-H6 inverter (a) $V_{AB} = V_{dc}$ , (b) $V_{AB} = 0$ , (c) $V_{AB} = -V_{dc}$ .                                       | 63 |

| Fig. 3.17 | Operating modes of the BDC-H-B inverter (a) $V_{AB} = V_{dc}$ , (b) $V_{AB} = 0$ , (c) $V_{AB} = -V_{dc}$ .                                      | 63 |

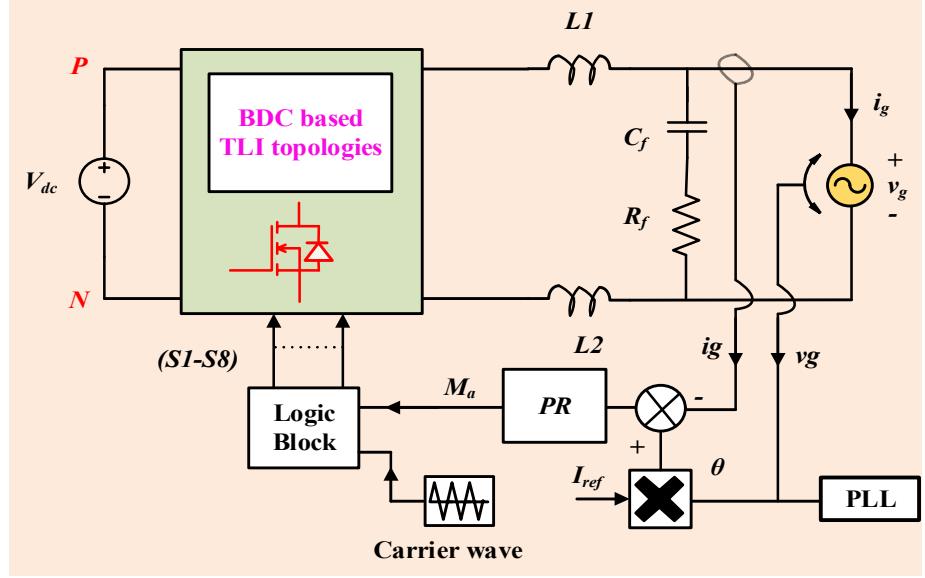

| Fig. 3.18 | Closed-loop control of BDC based topologies.                                                                                                     | 64 |

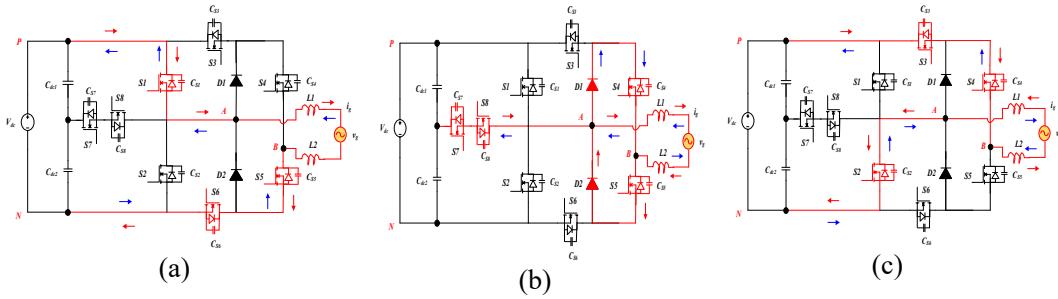

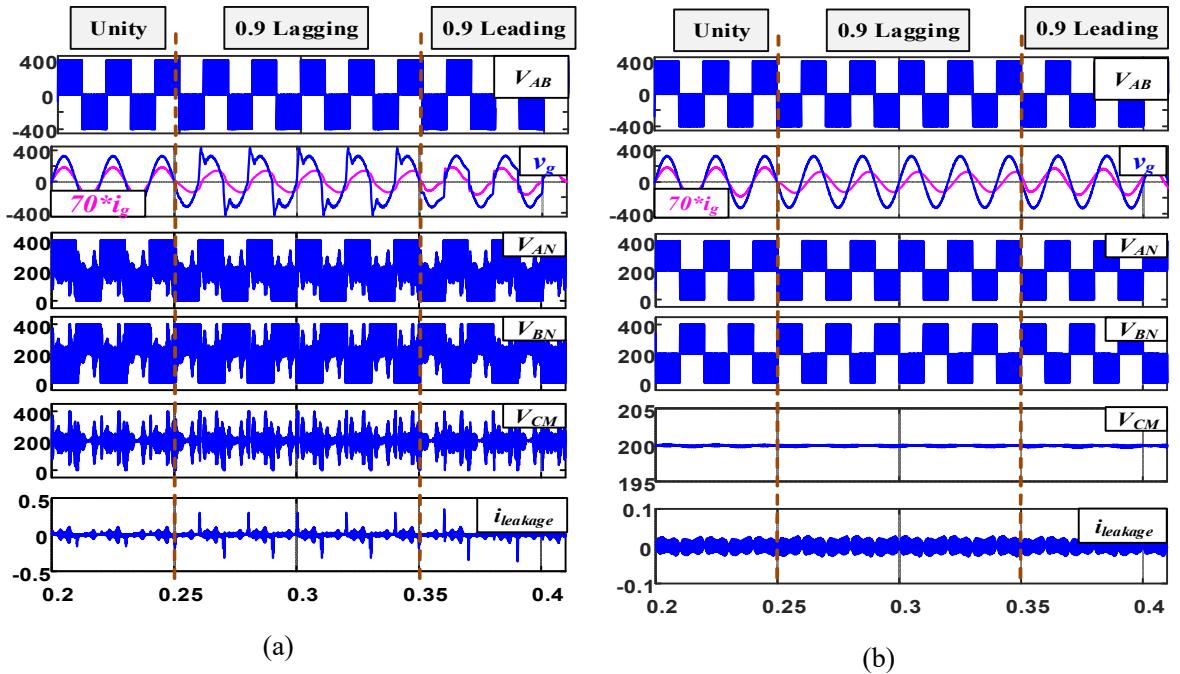

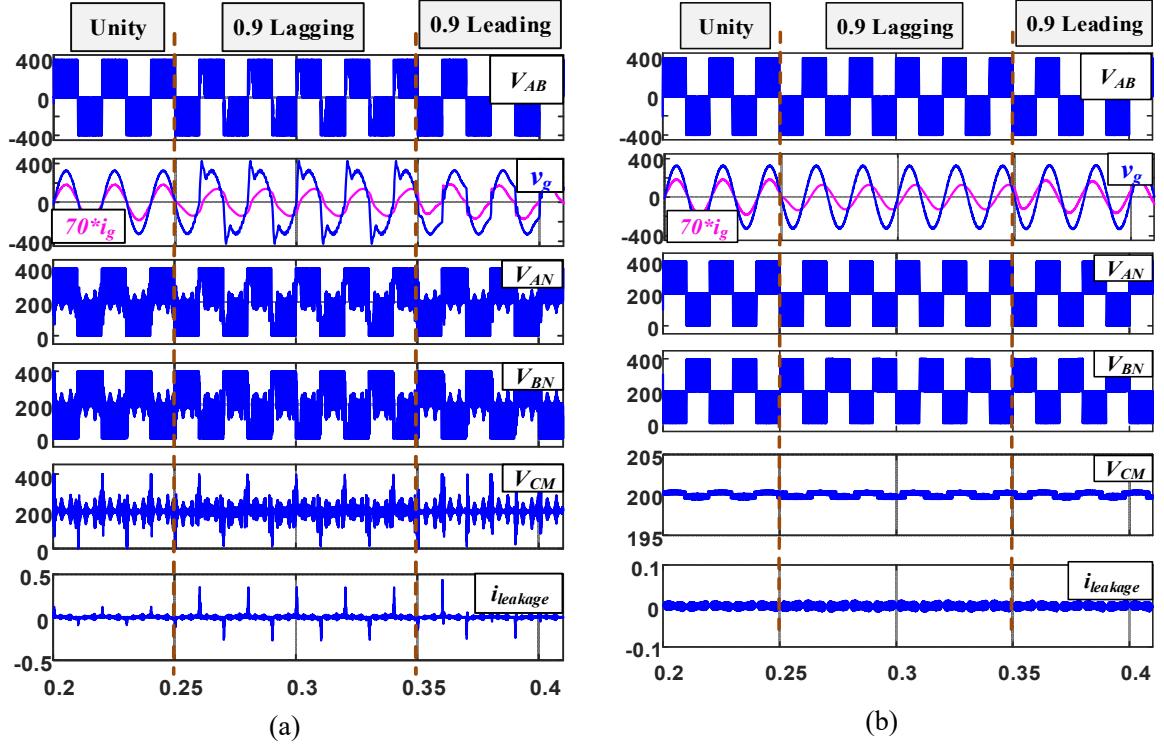

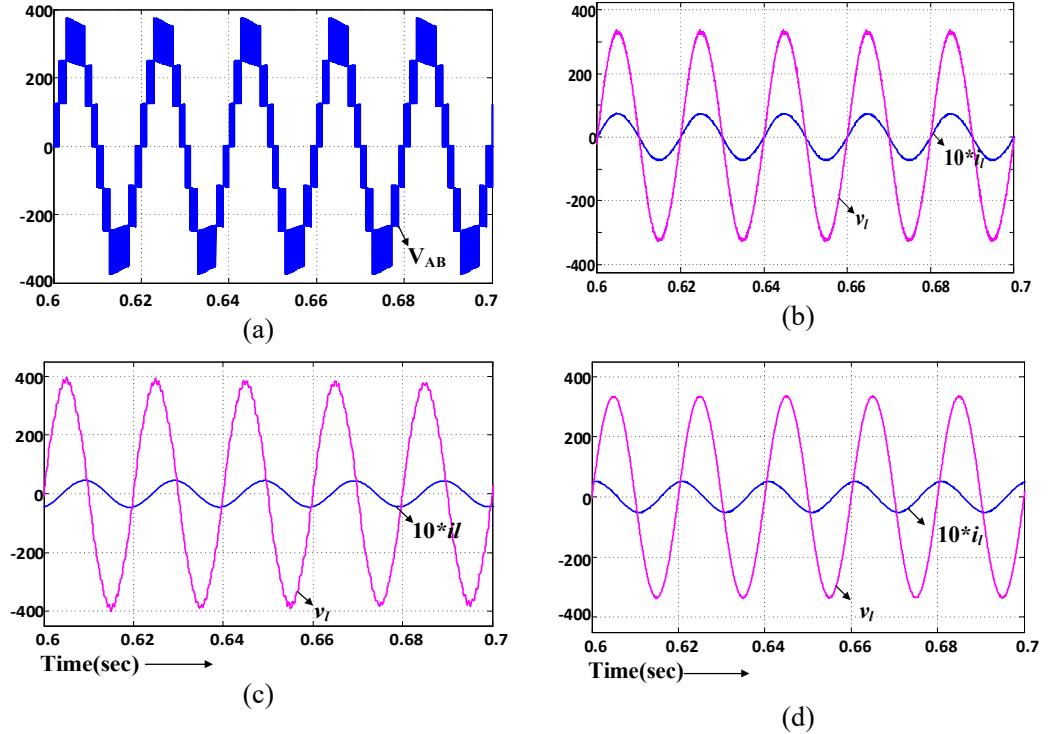

| Fig. 3.19 | Differential-mode and common-mode results; (a) H5, (b) BDC-H5 inverter.                                                                          | 67 |

| Fig. 3.20 | Differential-mode and common-mode results; (a) HERIC, (b) BDC-HERIC inverter.                                                                    | 68 |

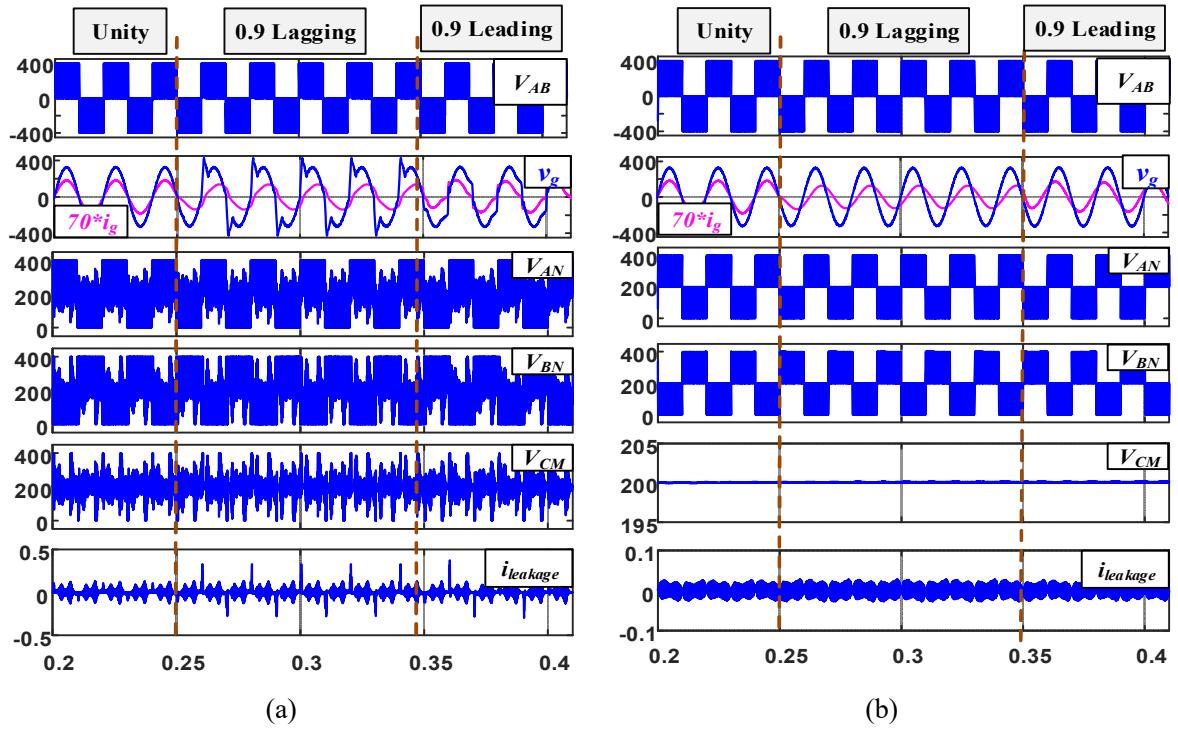

| Fig. 3.21 | Differential-mode and common-mode results; (a) H6, (b) BDC-H6 inverter.                                                                          | 68 |

| Fig. 3.22 | Differential-mode and common-mode results; (a) H-B, (b) BDC-H-B inverter.                                                                        | 69 |

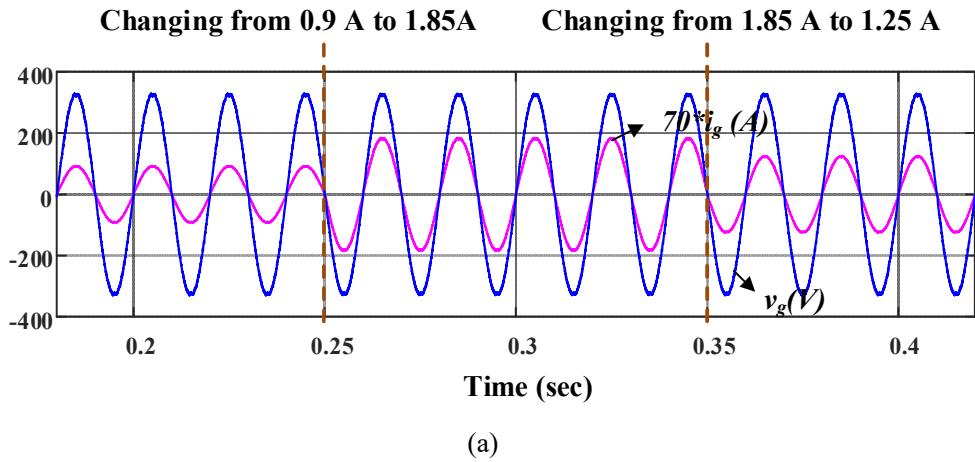

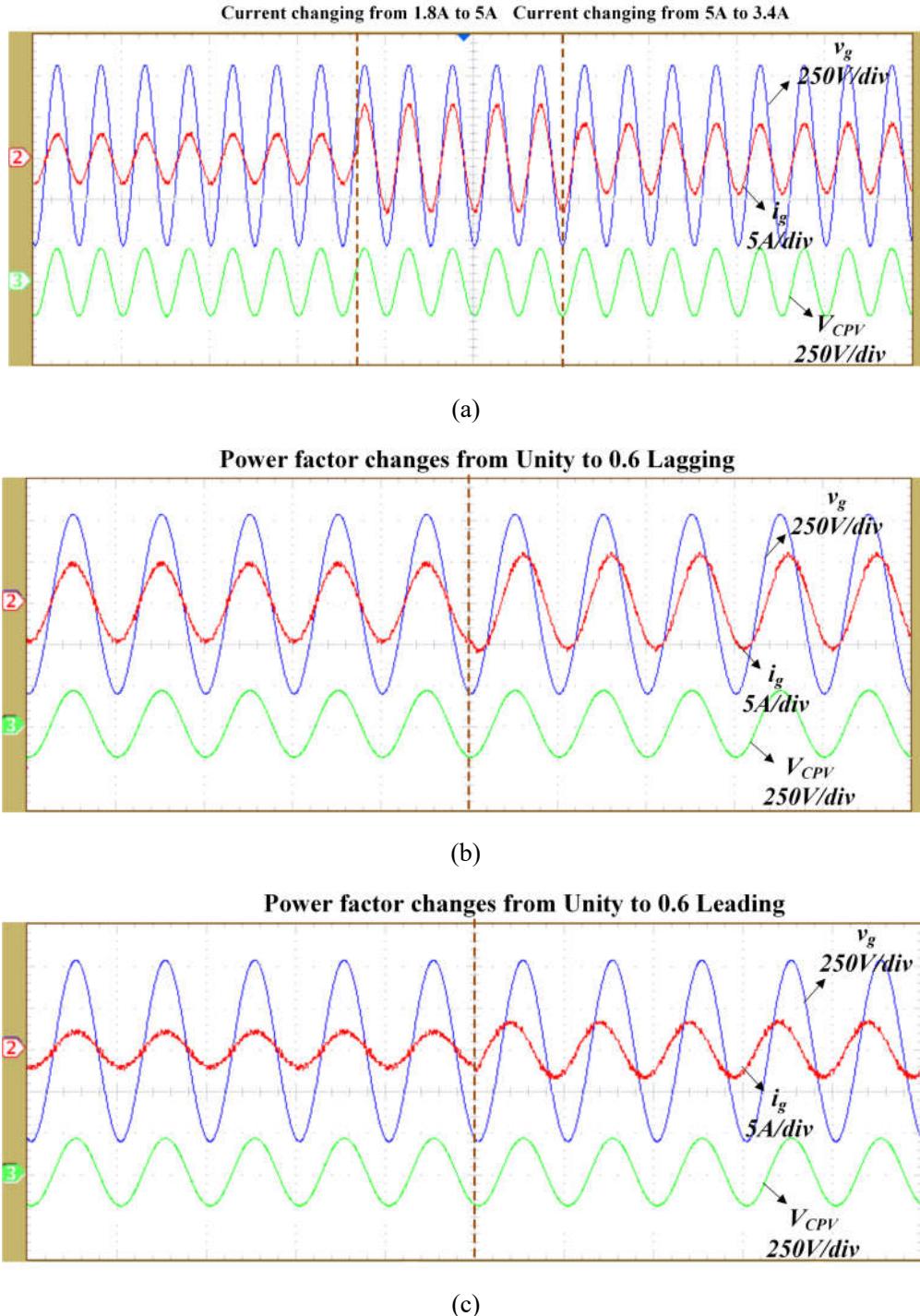

| Fig. 3.23 | Dynamic response of BDC-H5 topology: (a) step changes in grid current; power factor changes from: (b) unity to lagging and (c) unity to leading. | 70 |

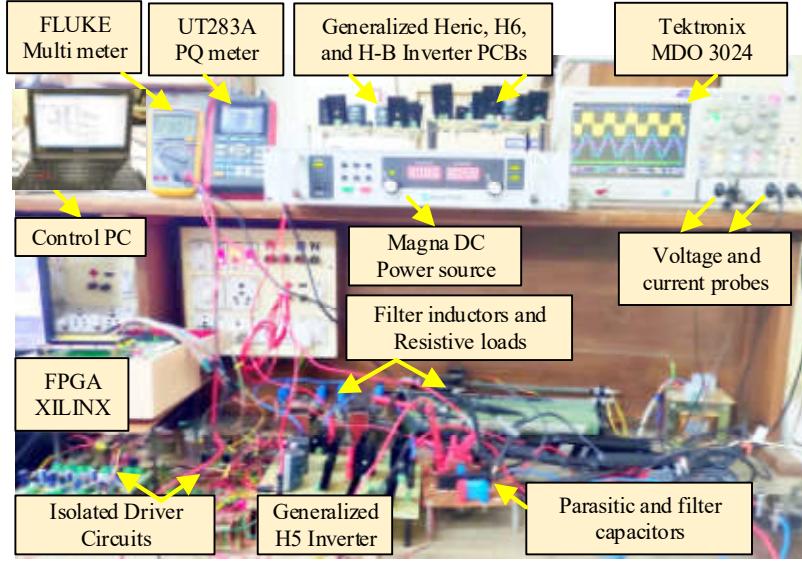

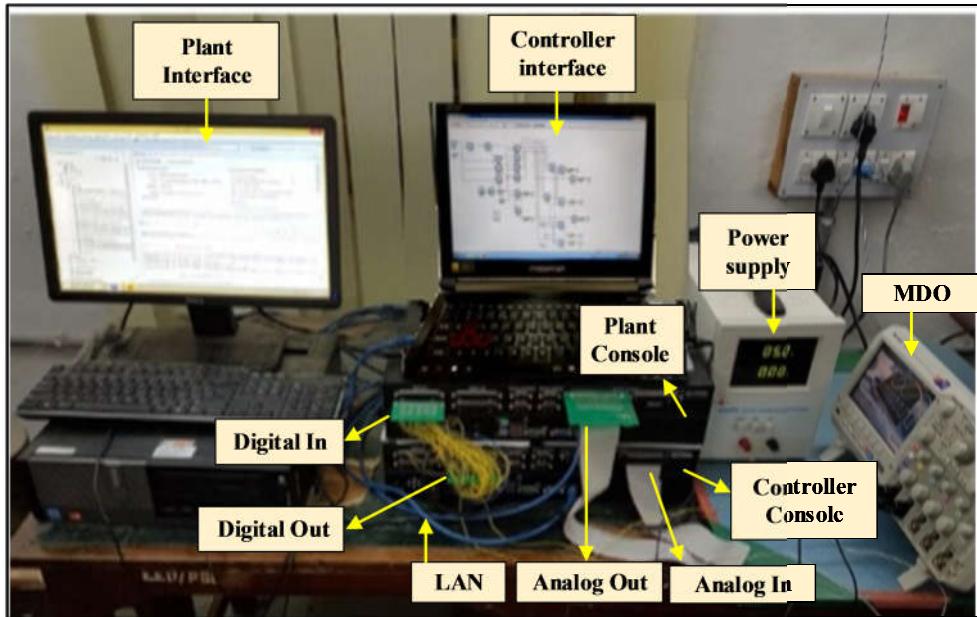

| Fig. 3.24 | Experimental test setup.                                                                                                                         | 71 |

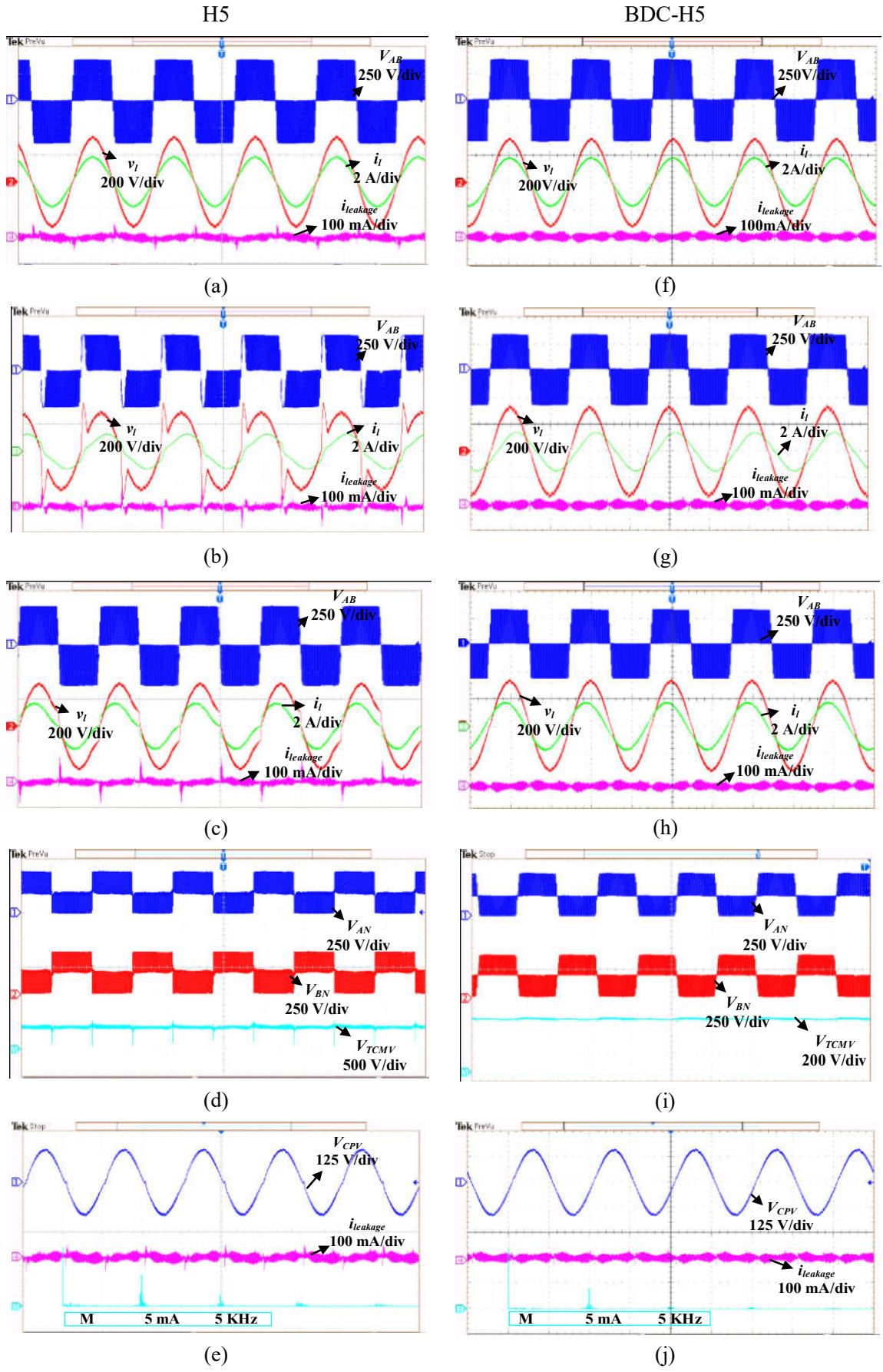

| Fig. 3.25 | Differential-mode and common-mode characteristics of H5 and BDC-H5 topologies.                                                                   | 72 |

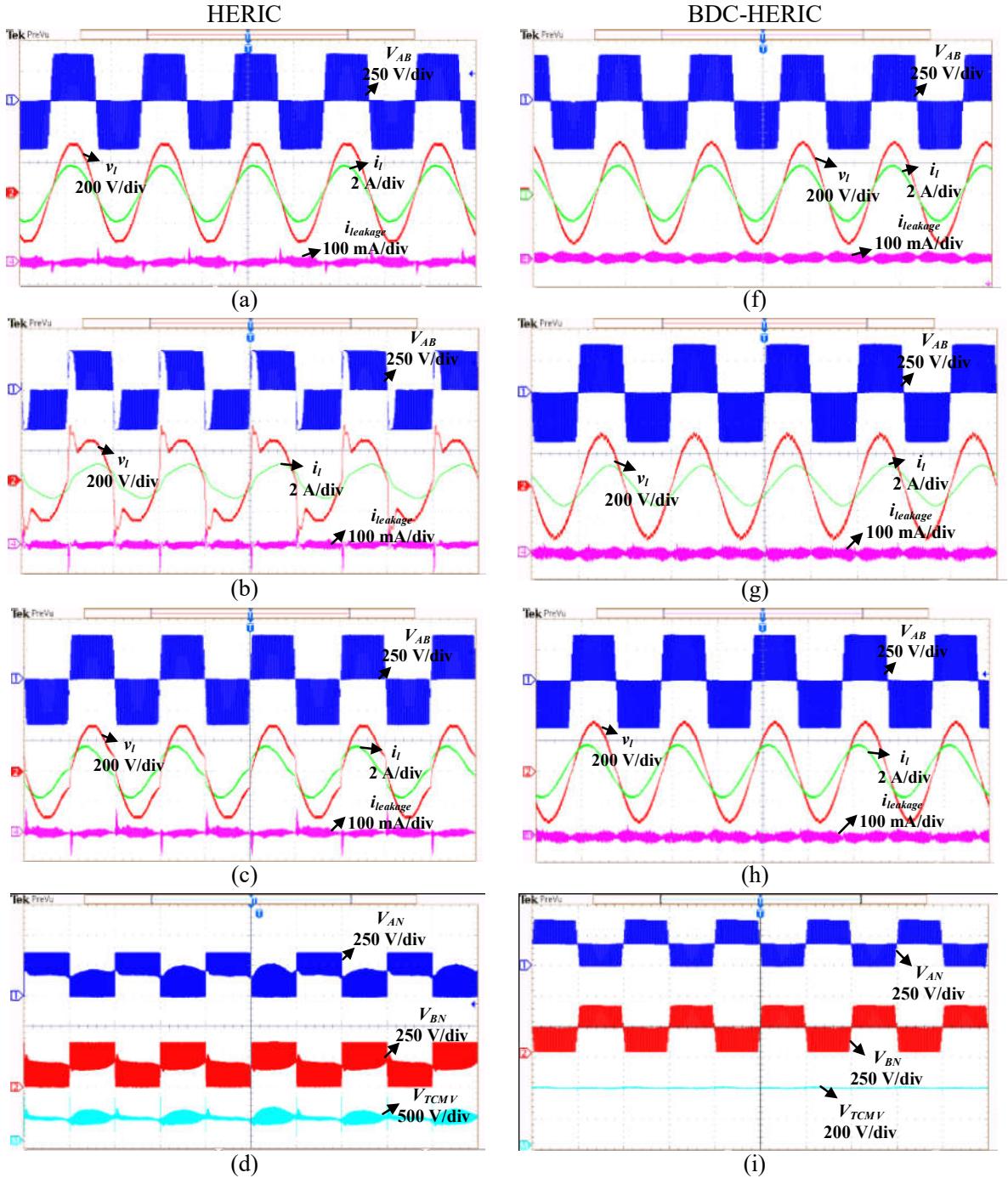

| Fig. 3.26 | Differential-mode and common-mode characteristics of HERIC and BDC-HERIC topologies.                                                             | 74 |

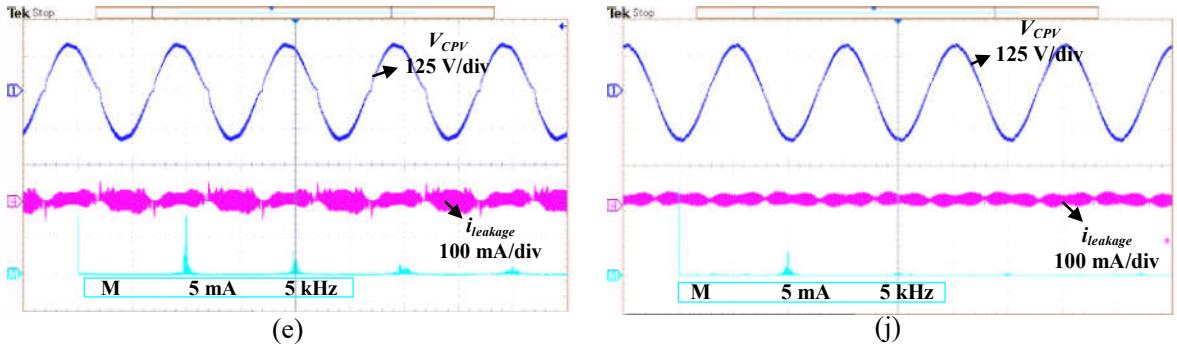

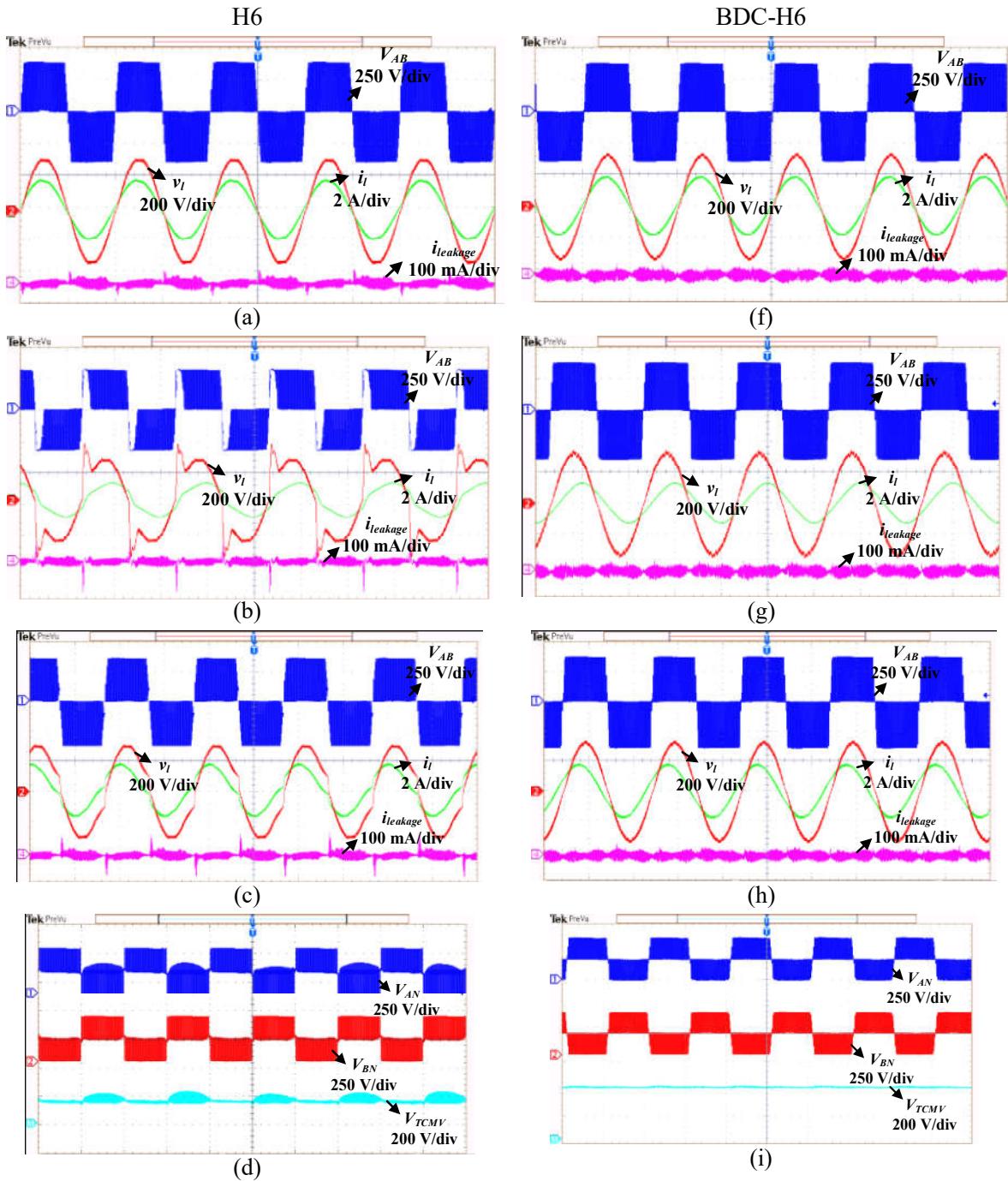

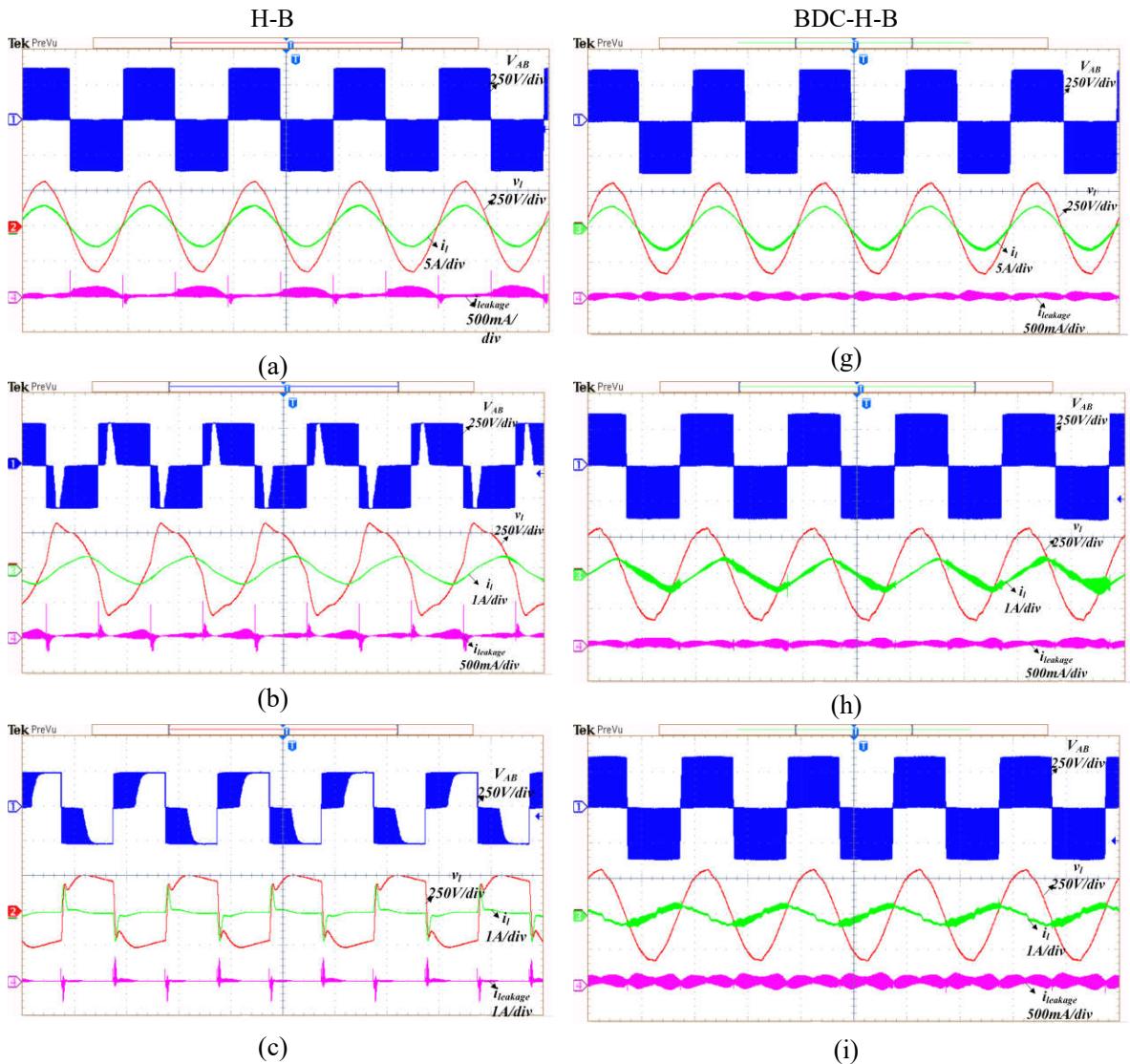

| Fig. 3.27 | Differential-mode and common-mode characteristics of H6 and BDC-H6 topologies.                                                                   | 75 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

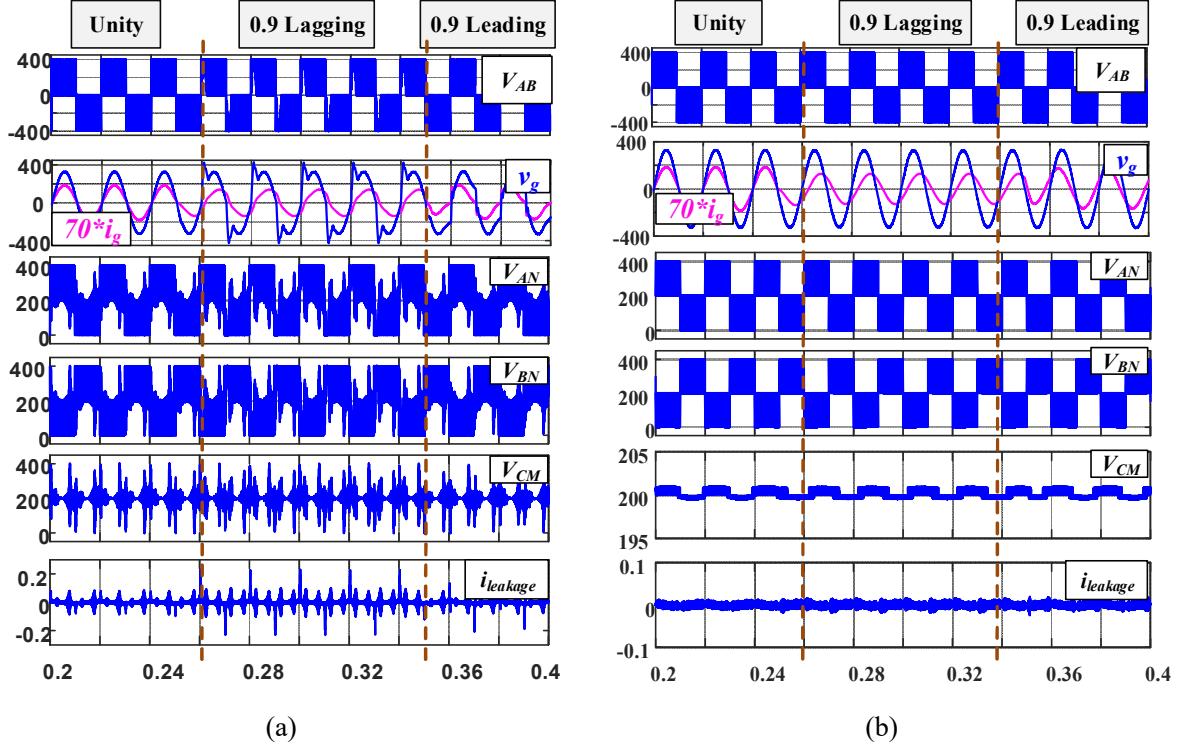

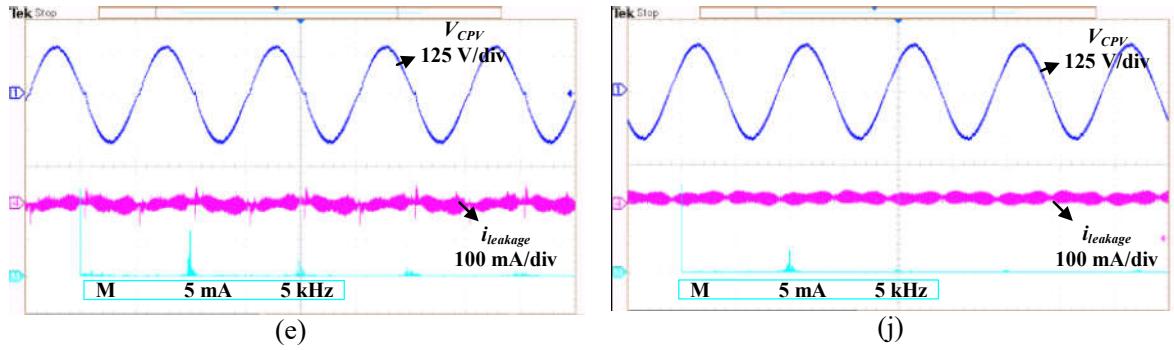

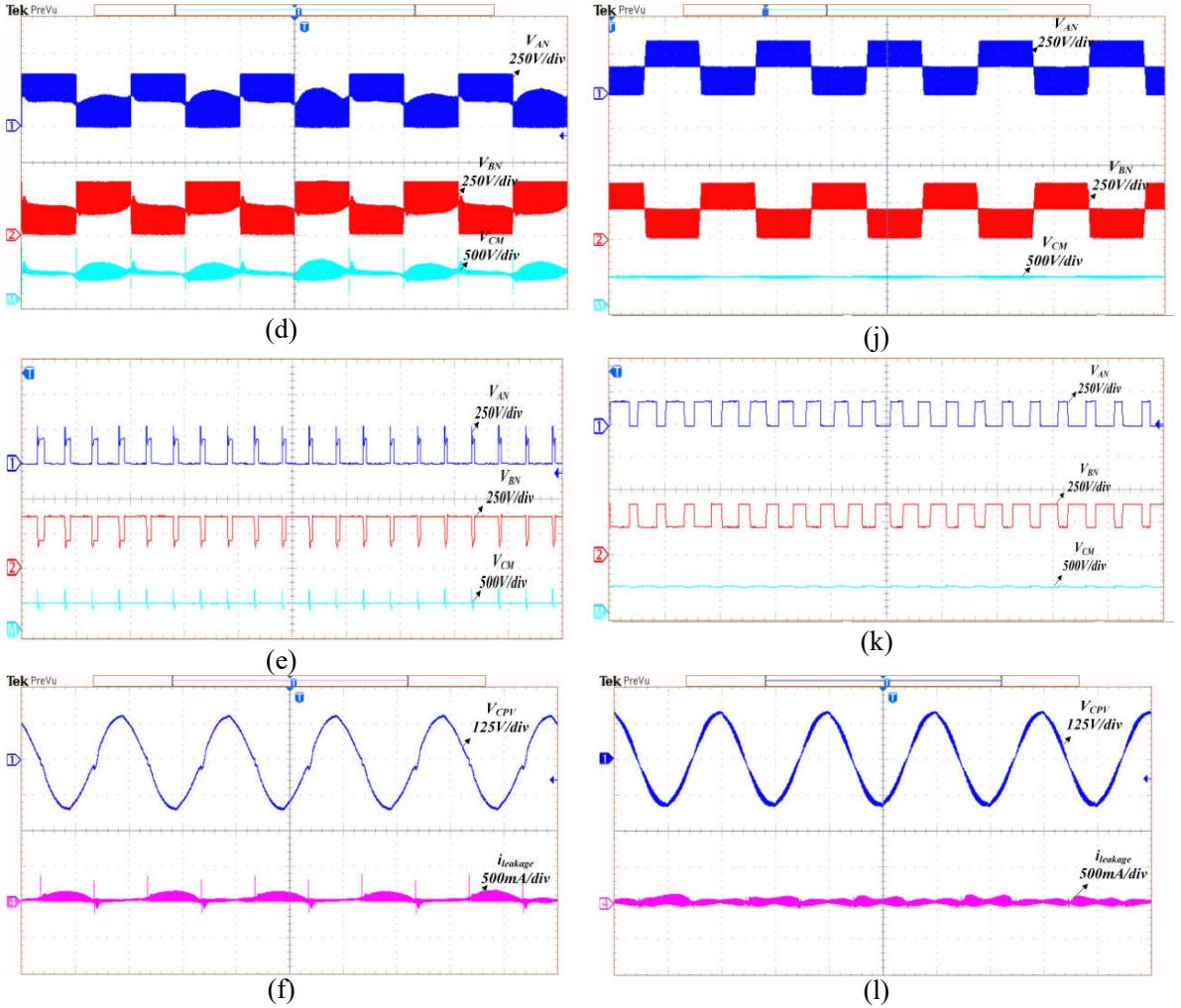

| Fig. 3.28 | Differential-mode and common-mode characteristics of H-B and BDC-H-B topologies.                                                                                                                                                                                                                                                                                                                                                              | 76  |

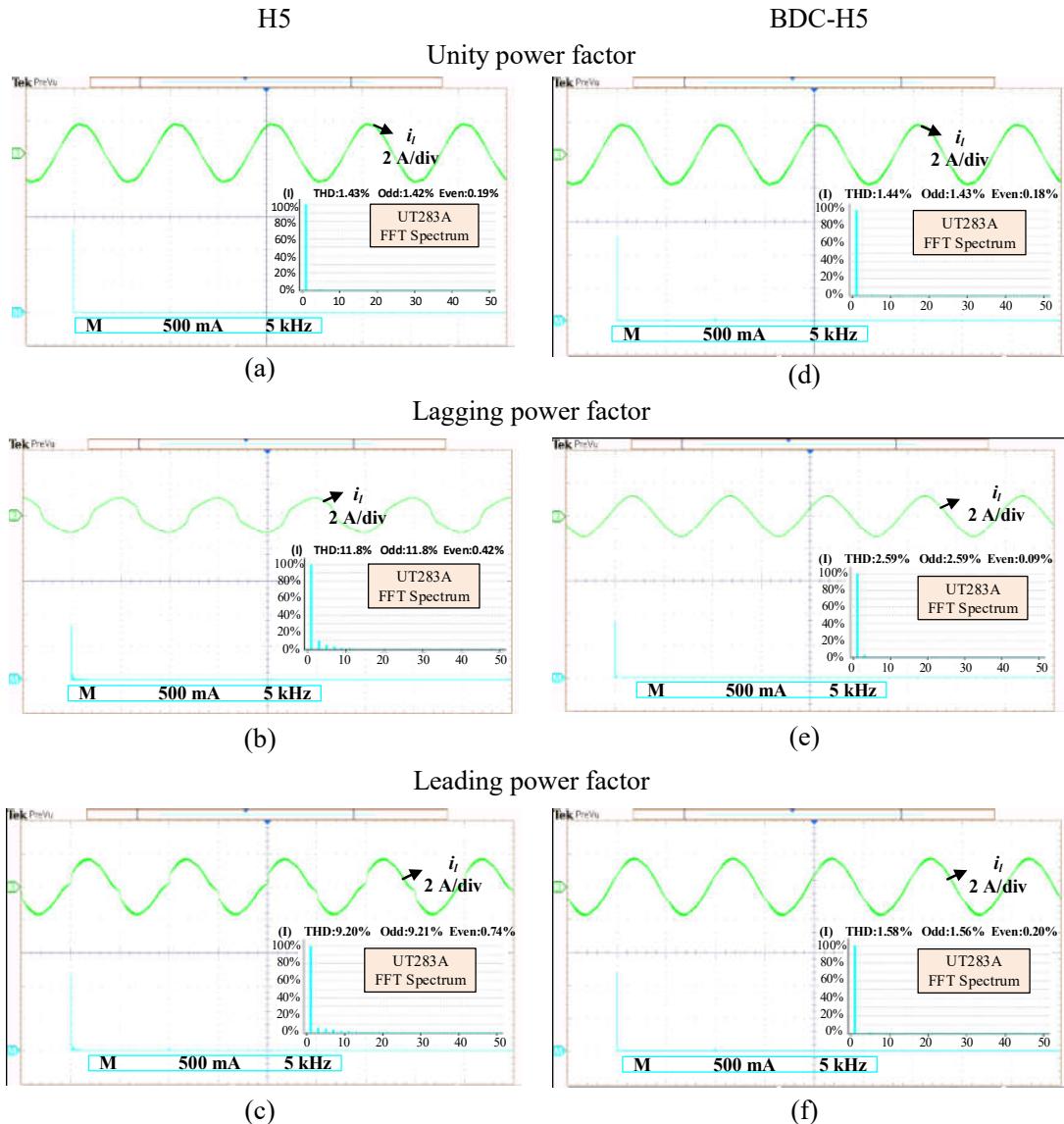

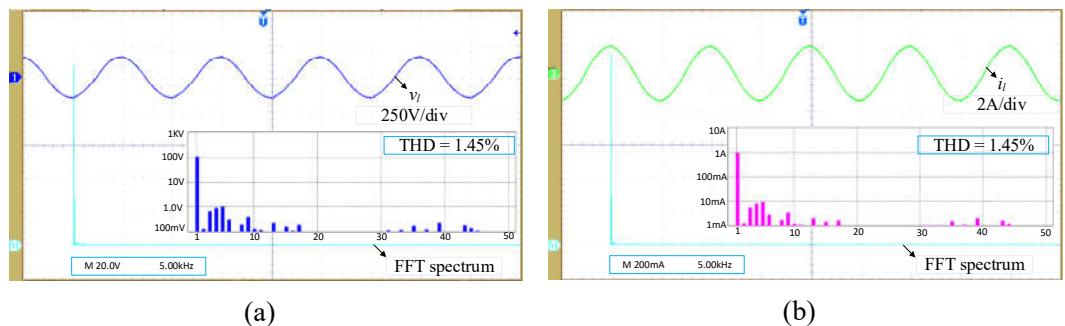

| Fig. 3.29 | THD Measurement of current waveforms for H5 and BDC-H5.                                                                                                                                                                                                                                                                                                                                                                                       | 77  |

| Fig. 3.30 | OPAL-RT real-time environmental setup                                                                                                                                                                                                                                                                                                                                                                                                         | 79  |

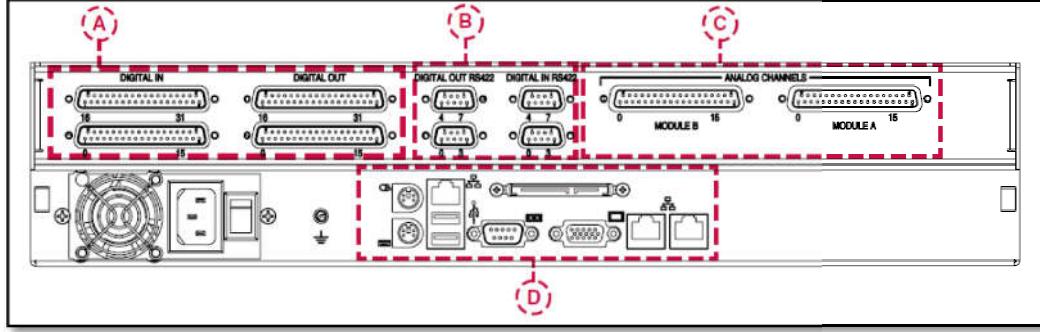

| Fig. 3.31 | Front view of OP4500 module.                                                                                                                                                                                                                                                                                                                                                                                                                  | 80  |

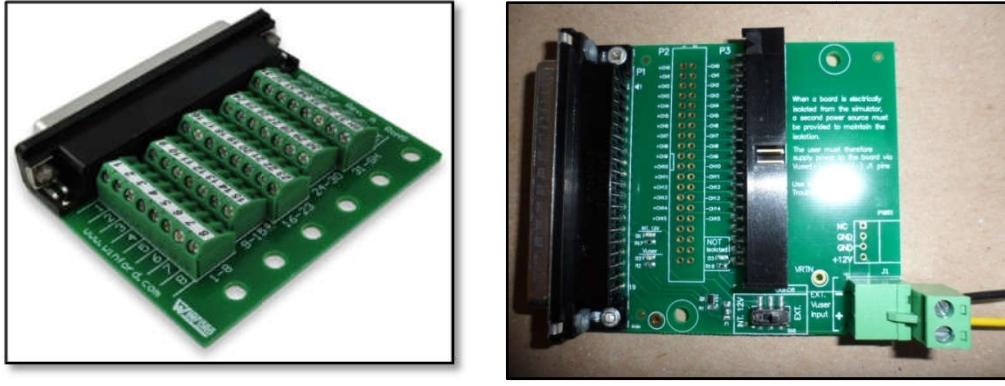

| Fig. 3.32 | DB 37; (a) Digital port, (b) Analog port.                                                                                                                                                                                                                                                                                                                                                                                                     | 80  |

| Fig. 3.33 | Dynamic response of the IH-B topology: (a) step change in the grid current, transient change in power factor from (b) unity to lagging and (c) unity to leading.                                                                                                                                                                                                                                                                              | 81  |

| Fig. 3.34 | PSIM thermal model for the traditional H5 inverter.                                                                                                                                                                                                                                                                                                                                                                                           | 82  |

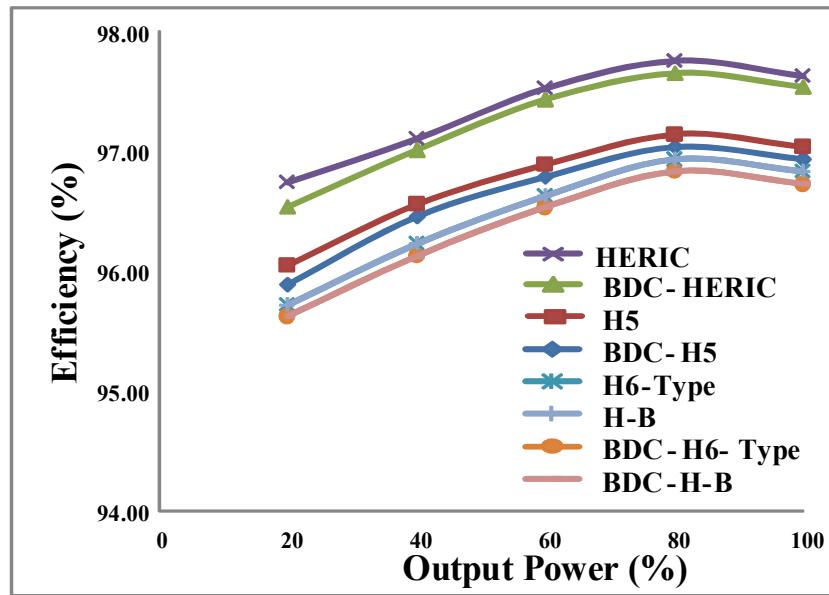

| Fig. 3.35 | Efficiency curves of the both traditional and BDC topologies.                                                                                                                                                                                                                                                                                                                                                                                 | 83  |

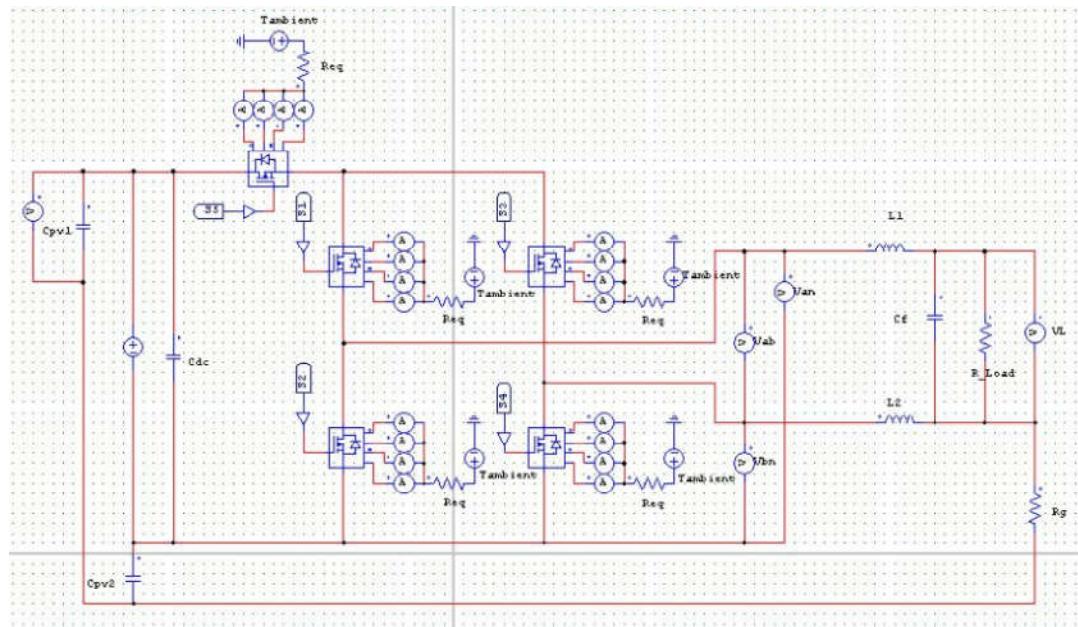

| Fig. 4.1  | Proposed single-phase two-stage power conditioner.                                                                                                                                                                                                                                                                                                                                                                                            | 87  |

| Fig. 4.2  | Operation forward boost converter (a) S1 is ON, (b) S1 is OFF.                                                                                                                                                                                                                                                                                                                                                                                | 88  |

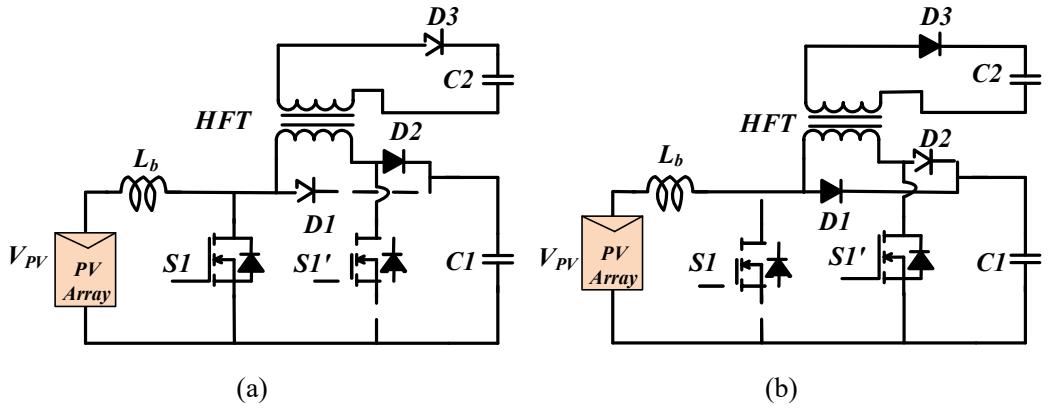

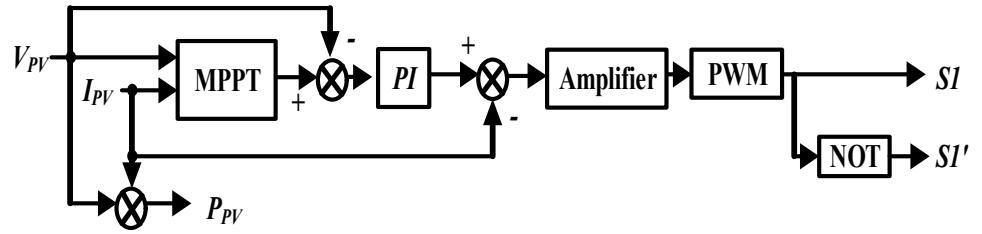

| Fig. 4.3  | MPPT control block.                                                                                                                                                                                                                                                                                                                                                                                                                           | 90  |

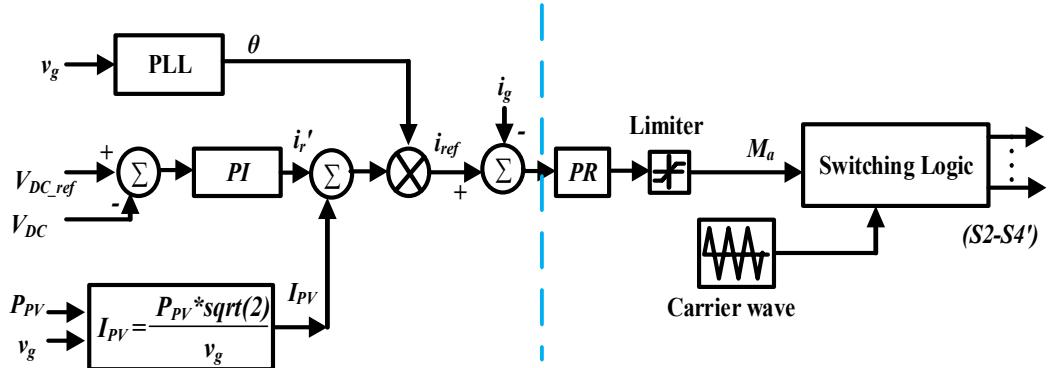

| Fig. 4.4  | Closed-loop control of inverter                                                                                                                                                                                                                                                                                                                                                                                                               | 90  |

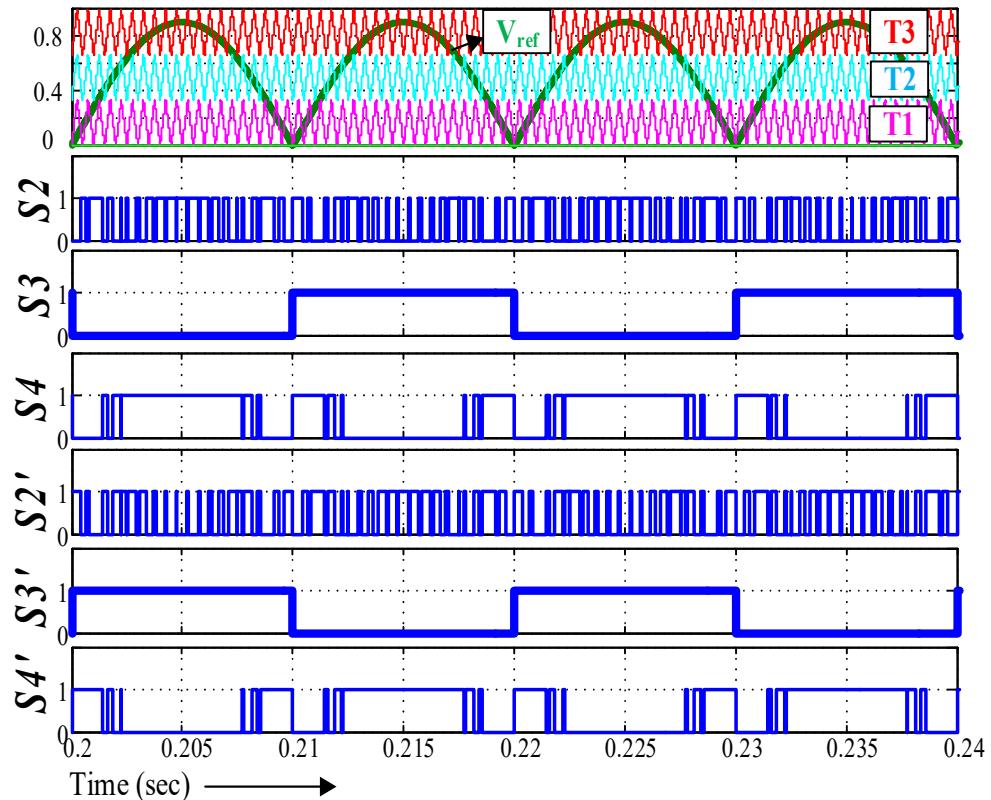

| Fig. 4.5  | Simulation waveforms of SLSPWM and corresponding gate pulses to the inverter switches                                                                                                                                                                                                                                                                                                                                                         | 91  |

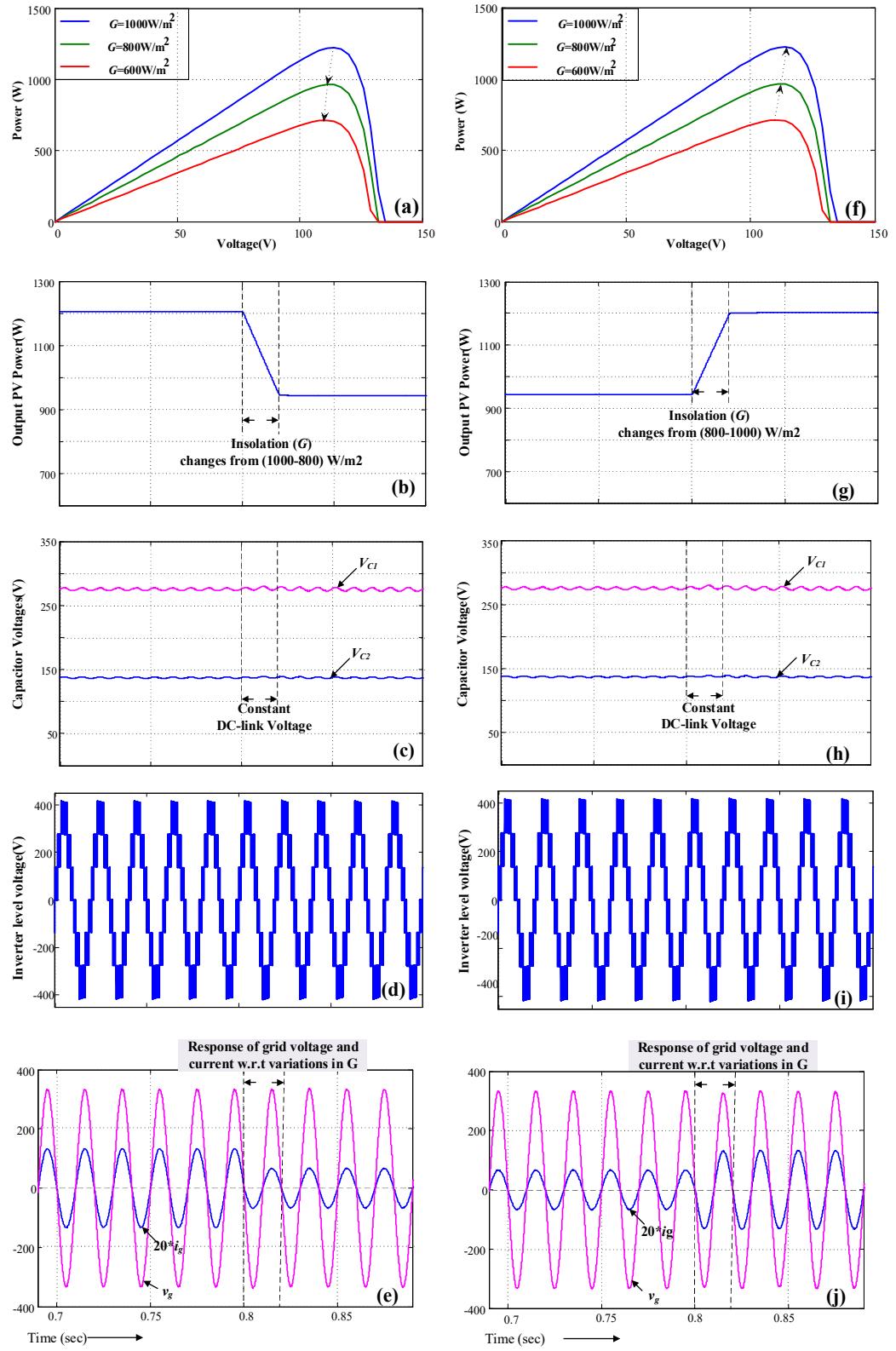

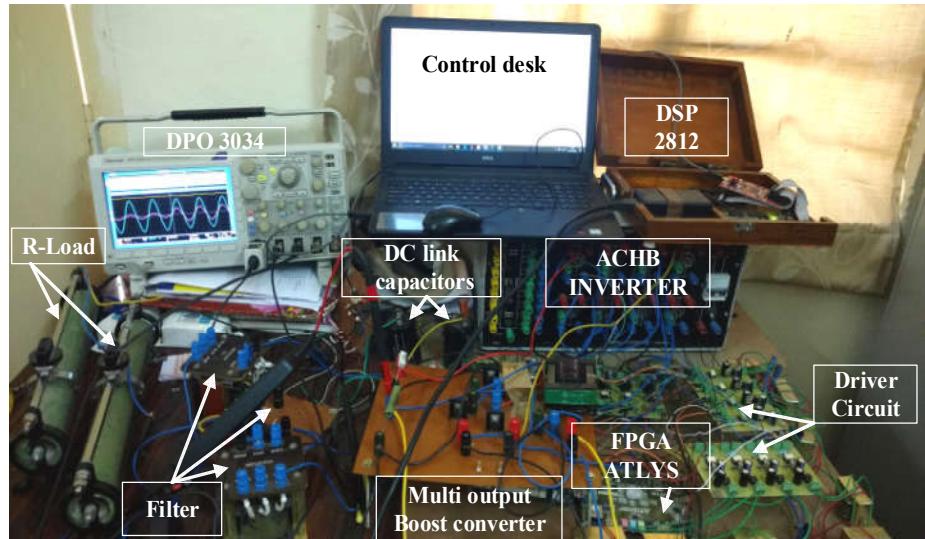

| Fig. 4.6  | Simulation results of the proposed power conditioner integrated with closed-loop control when input insolation varies from $1000 \text{ W/m}^2$ to $800 \text{ W/m}^2$ and vice versa. The subplot gives the waveforms of (a) and (f) PV characteristics; (b) and (g) Output PV power; (c) and (h) Balanced DC capacitor voltages; (d) and (i) seven-level output voltage of asymmetrical MLI; (e) and (j) grid voltage and injected current. | 93  |

| Fig. 4.7  | FFT spectrum of grid current.                                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

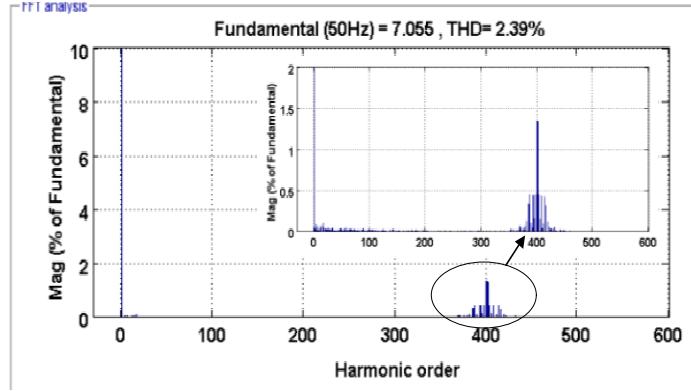

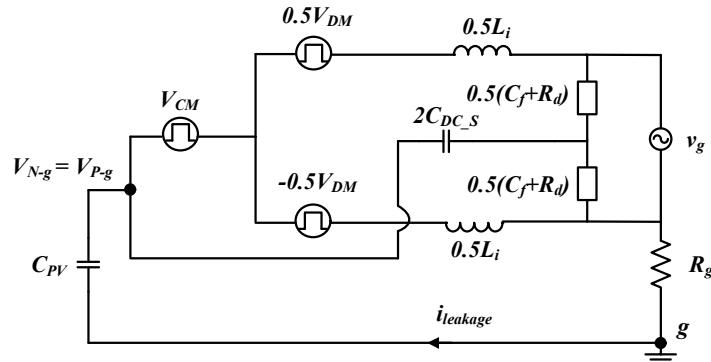

| Fig. 4.8  | (a) CM Equivalent circuit (b) Simplified CM equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                               | 95  |

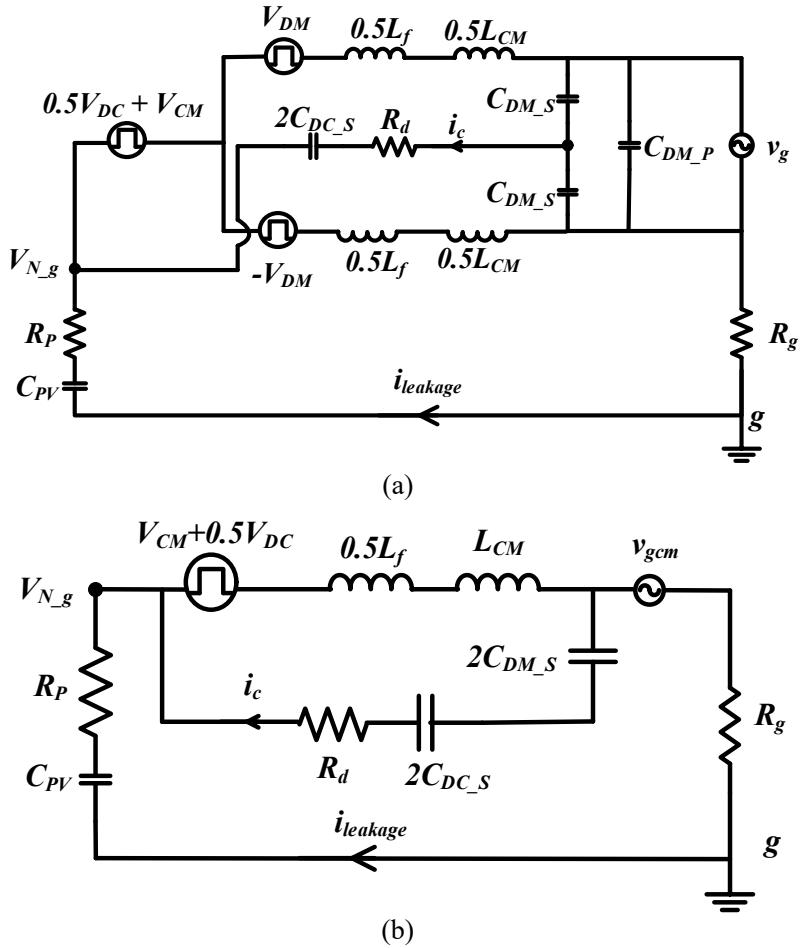

| Fig. 4.9  | Experimental prototype for the proposed power conditioner.                                                                                                                                                                                                                                                                                                                                                                                    | 98  |

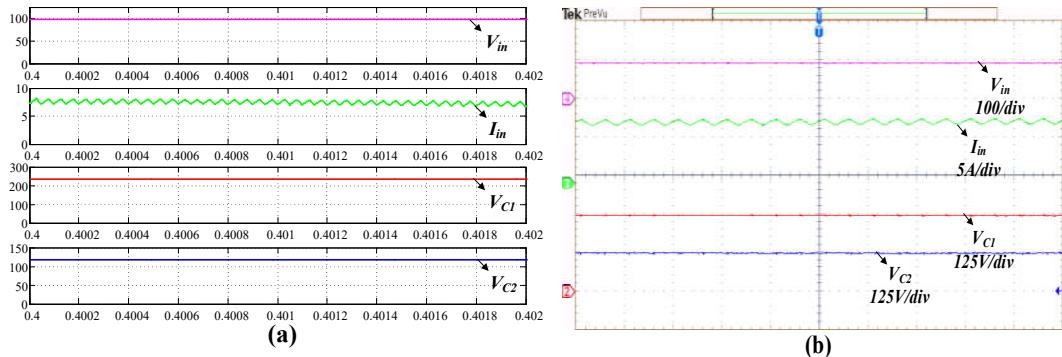

| Fig. 4.10 | Input voltage, current and DC-link voltage waveforms of (a) simulation and (b) experiment.                                                                                                                                                                                                                                                                                                                                                    | 99  |

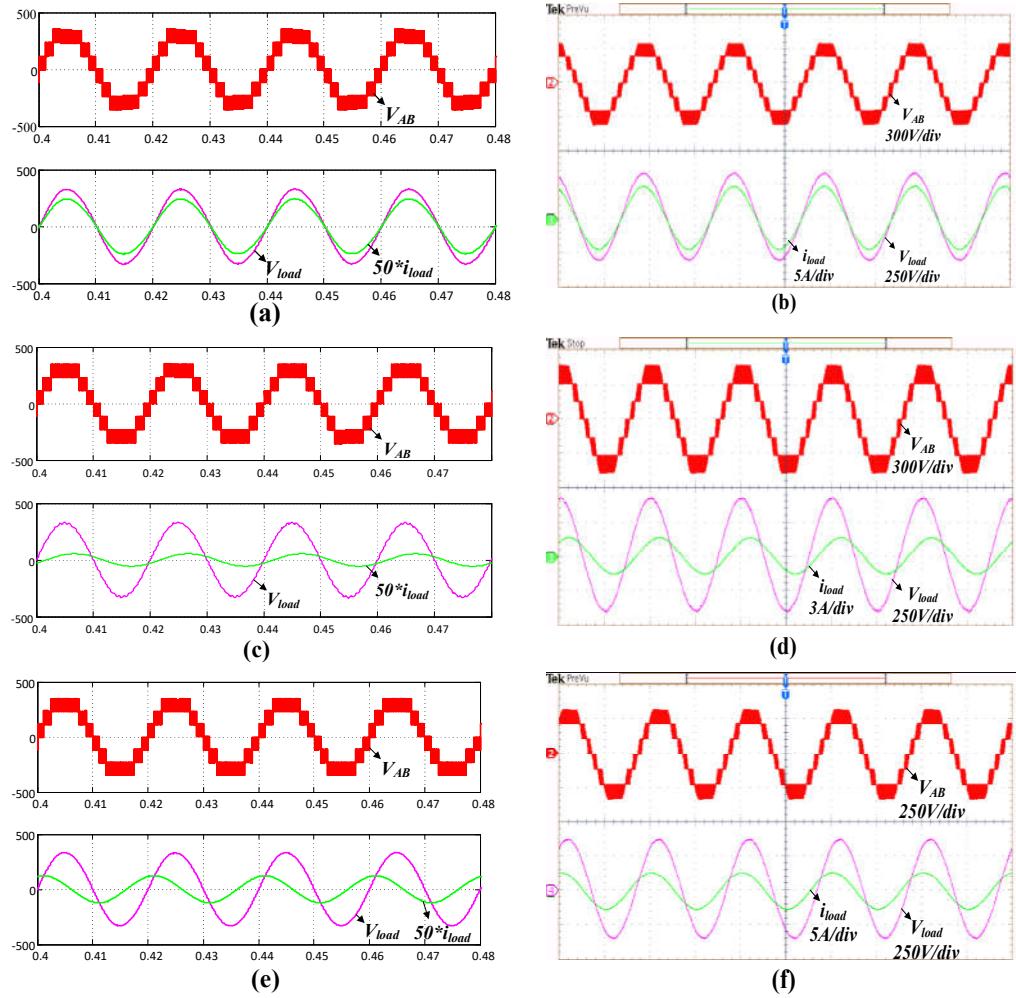

| Fig. 4.11 | Simulation and experimental results of seven-level voltage, load voltage and current (a) and (b) unity power factor; (c) and (d) (0.9) lagging power factor; (e) and (f) (0.9) leading power factor.                                                                                                                                                                                                                                          | 100 |

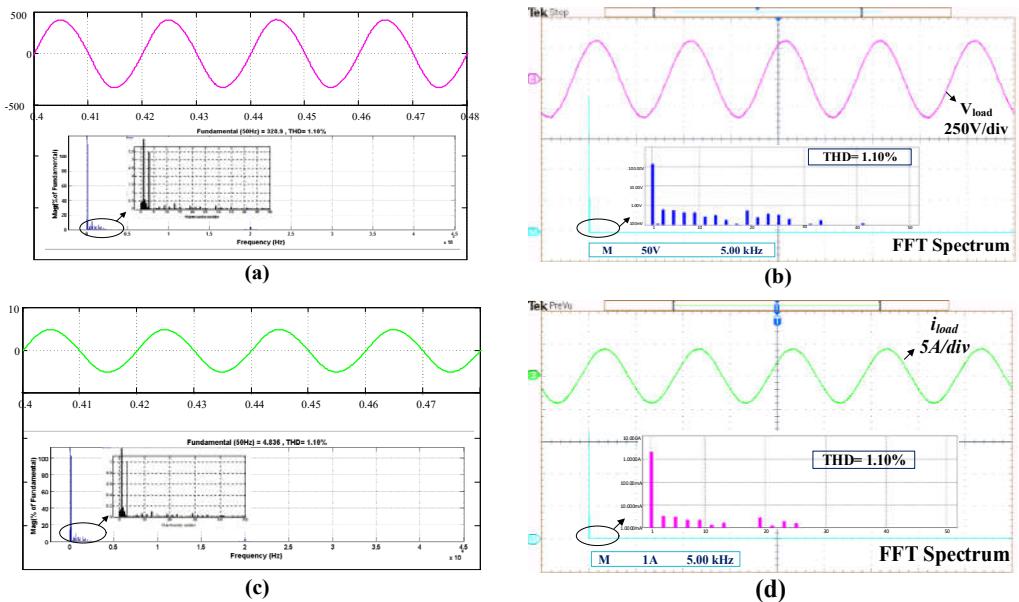

| Fig. 4.12 | Simulation and experimental FFT spectra for unity power factor operation (a) and (b) load voltage; (c) and (d) load current.                                                                                                                                                                                                                                                                                                                  | 100 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

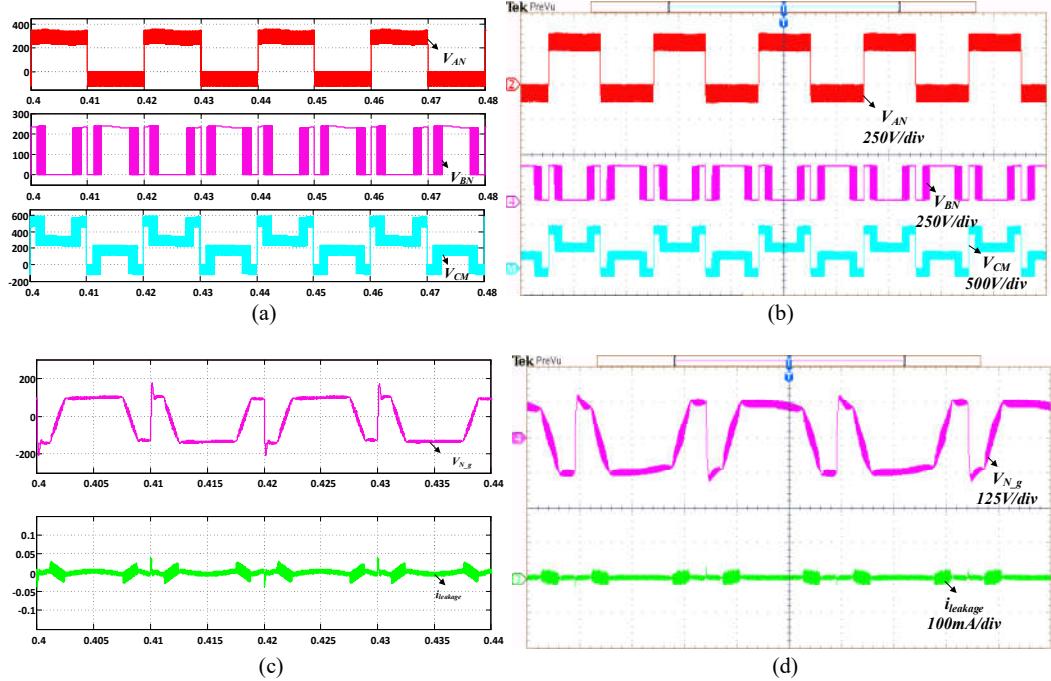

| Fig. 4.13 | Simulation and experimental waveforms of the (a) and (b) Terminal voltages $V_{AN}$ , $V_{BN}$ , and $V_{CM}$ ; (c) and (d) $V_{N-g}$ and leakage current.                                                                                                                                                                                                                                                                                                                              | 101 |

| Fig. 4.14 | Simulation results of $V_{N-g}$ and leakage current.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101 |

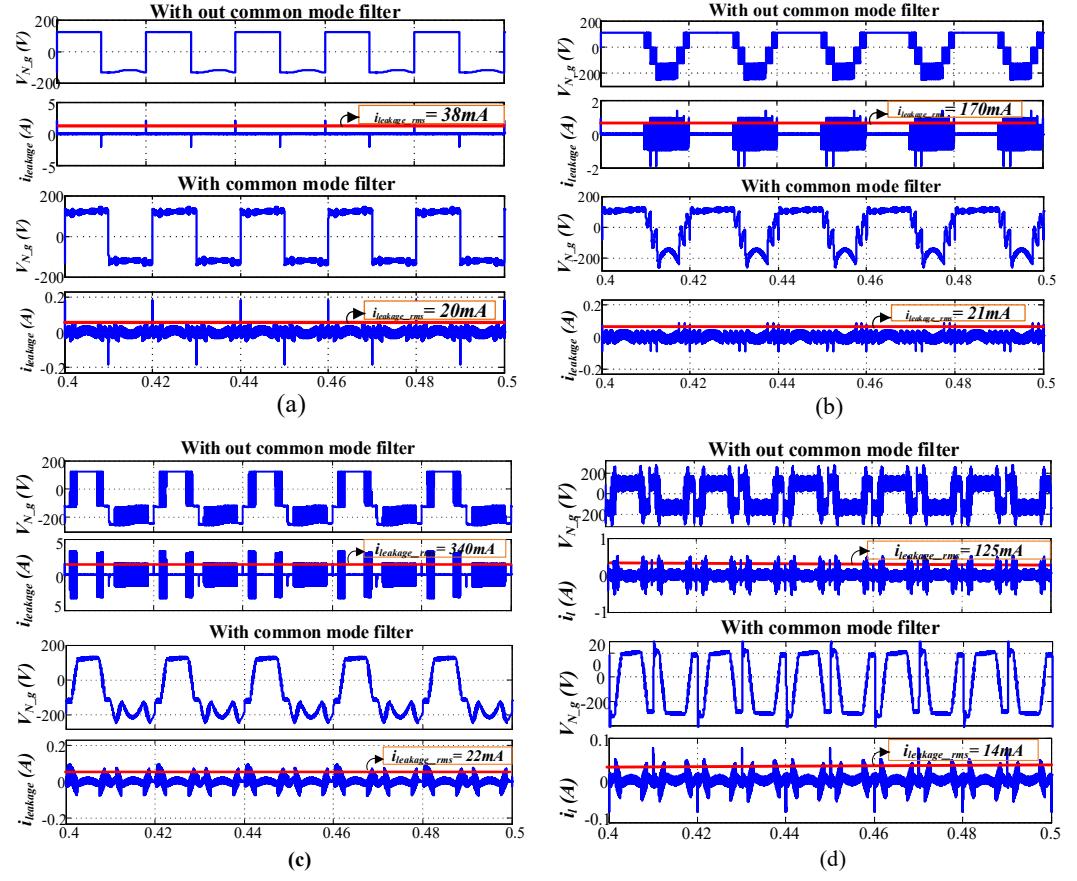

| Fig. 4.15 | Comparison of $V_{N-g}$ , leakage current $i_l$ and its RMS value without and with CM filter. (a) Ref []; (b) Ref []; (c) Ref []; (d) proposed topology.                                                                                                                                                                                                                                                                                                                                | 102 |

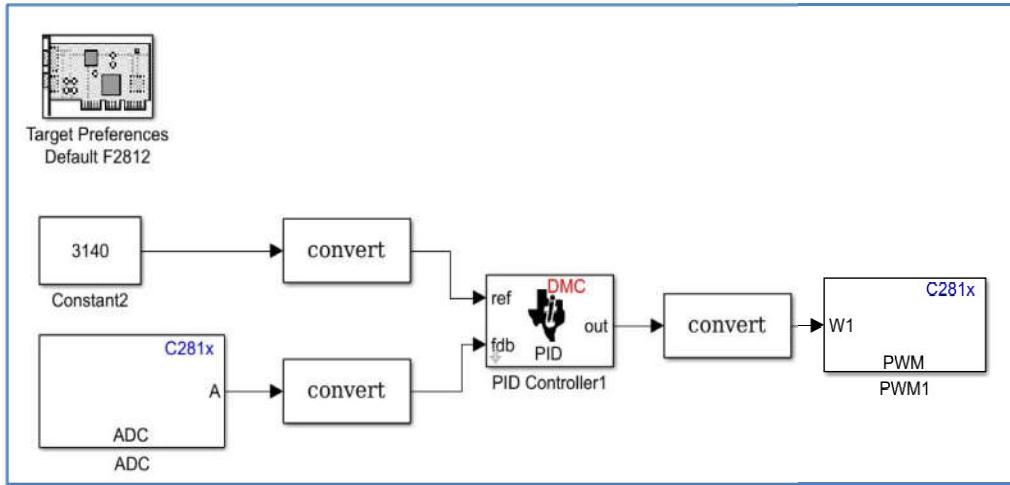

| Fig. 4.16 | Generation of the control pulses using DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 104 |

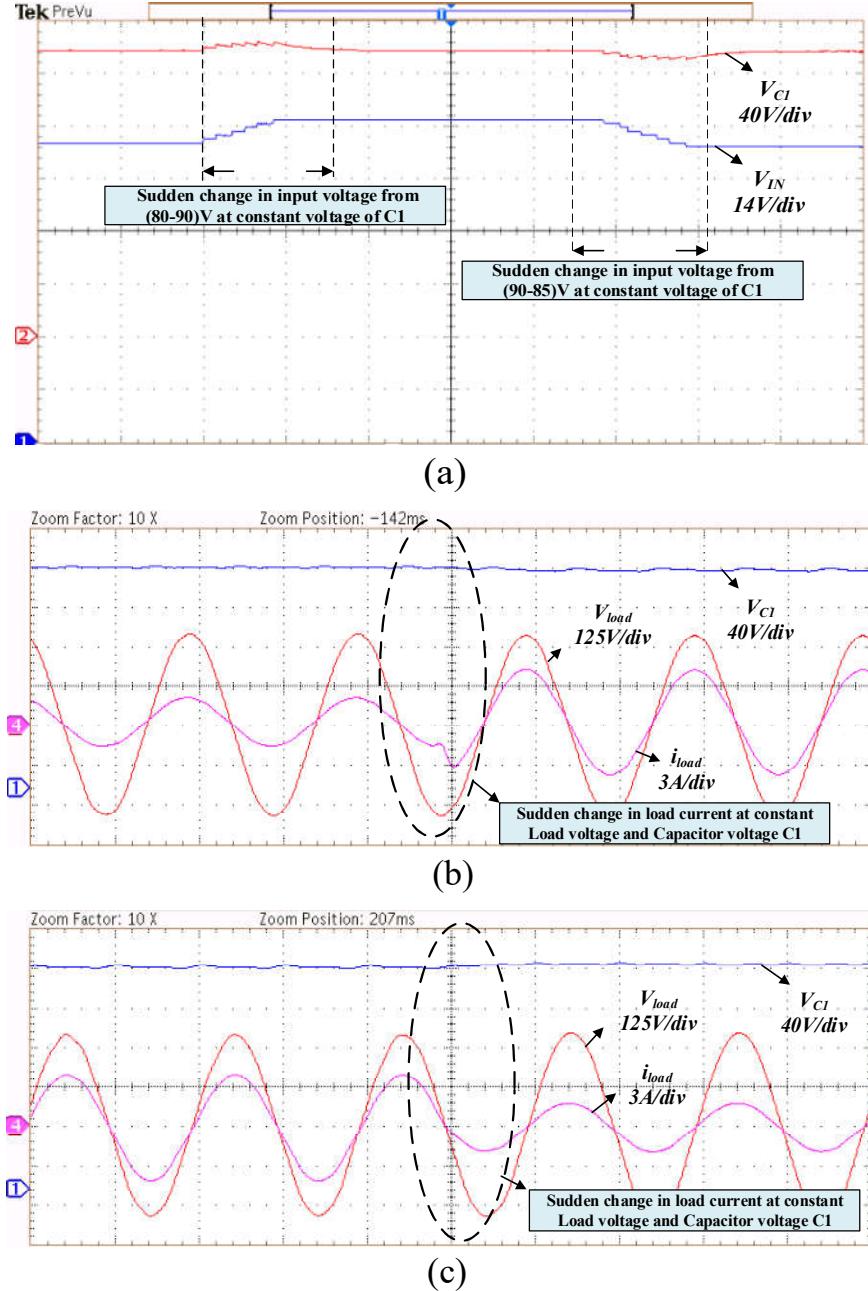

| Fig. 4.17 | Experimental waveforms of (a) capacitor voltage ( $V_{C1}$ ) with respect to changes in input voltage; (b) and (c) load voltage, capacitor voltage ( $V_{C1}$ ) response with respect to step change in load.                                                                                                                                                                                                                                                                           | 105 |

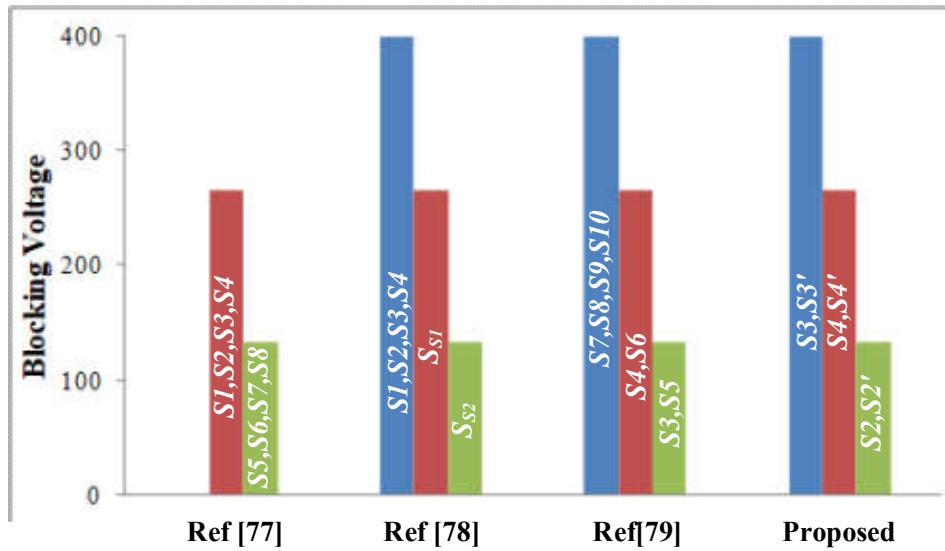

| Fig. 4.18 | Blocking voltages of the switches used in various MLI topologies.                                                                                                                                                                                                                                                                                                                                                                                                                       | 107 |

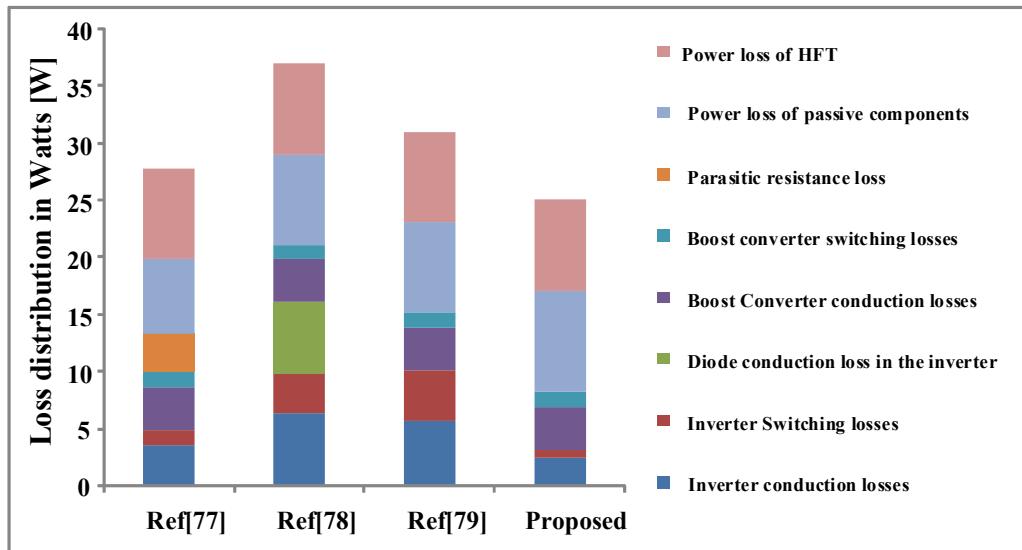

| Fig. 4.19 | Loss distribution in various topologies at 750 W of output power.                                                                                                                                                                                                                                                                                                                                                                                                                       | 109 |

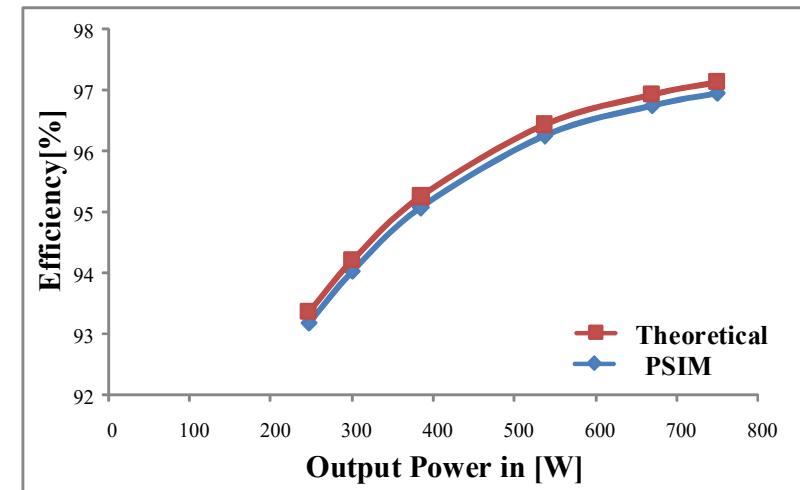

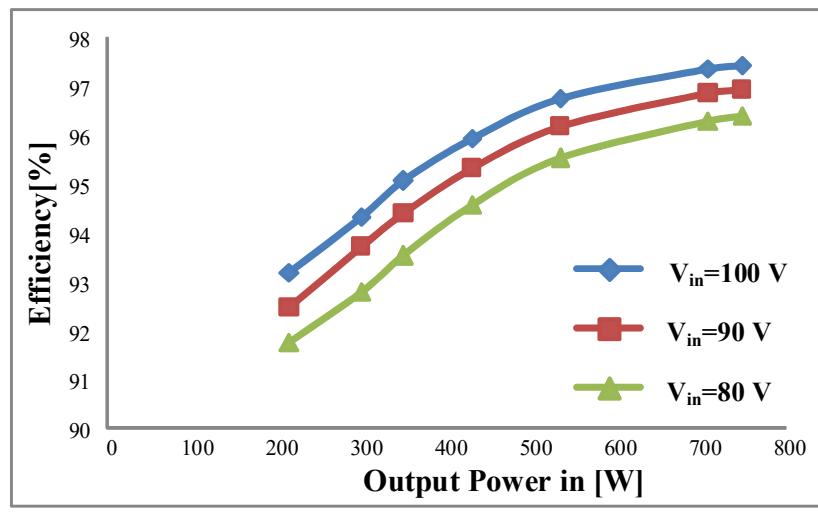

| Fig. 4.20 | Efficiency curves (a) Theoretical and PSIM, and (b) Different input voltages.                                                                                                                                                                                                                                                                                                                                                                                                           | 109 |

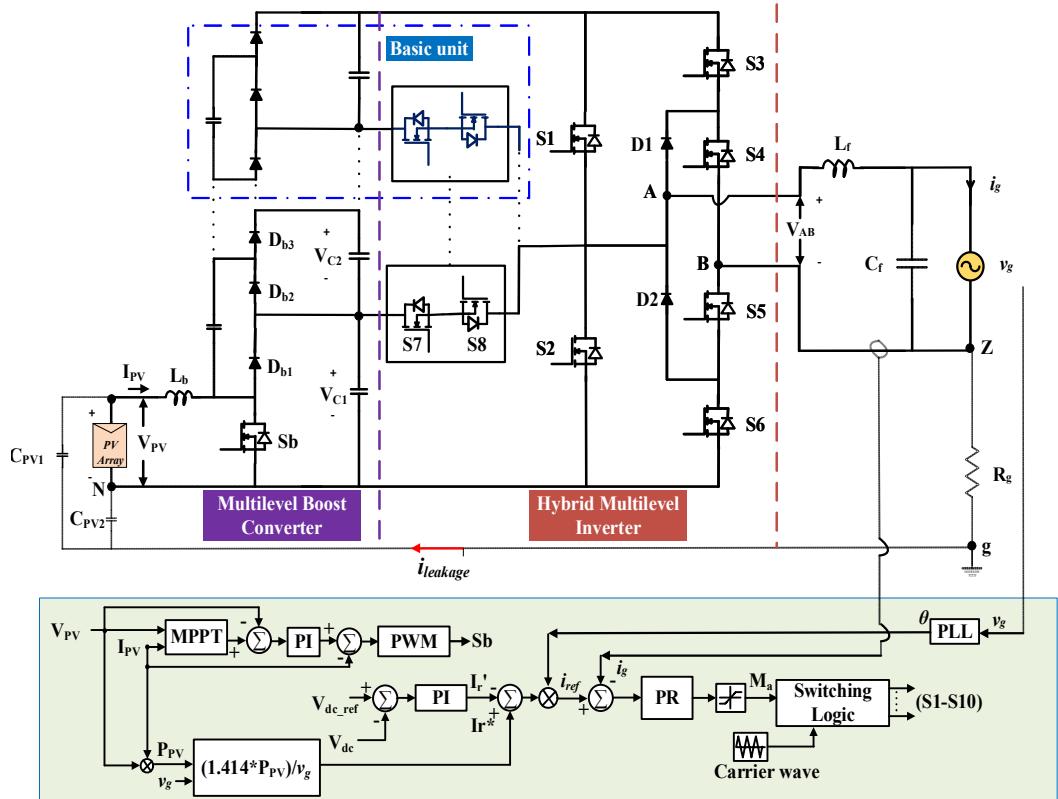

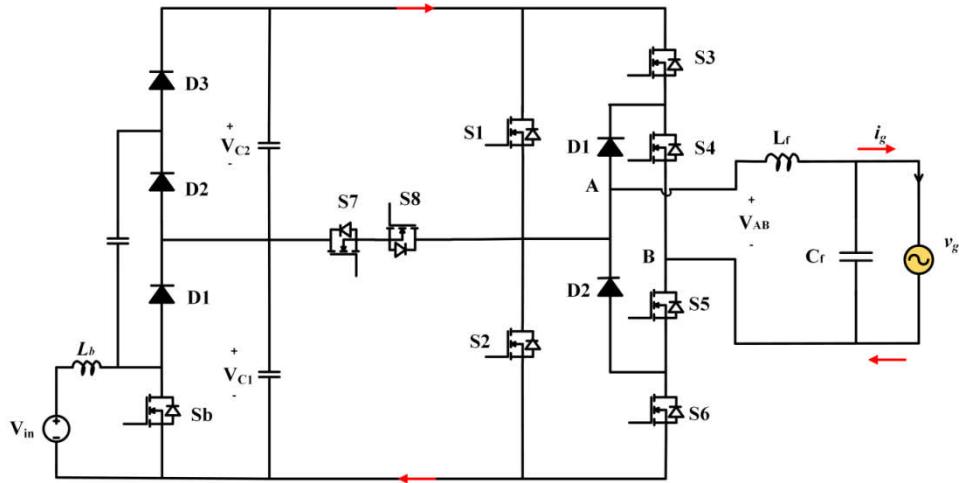

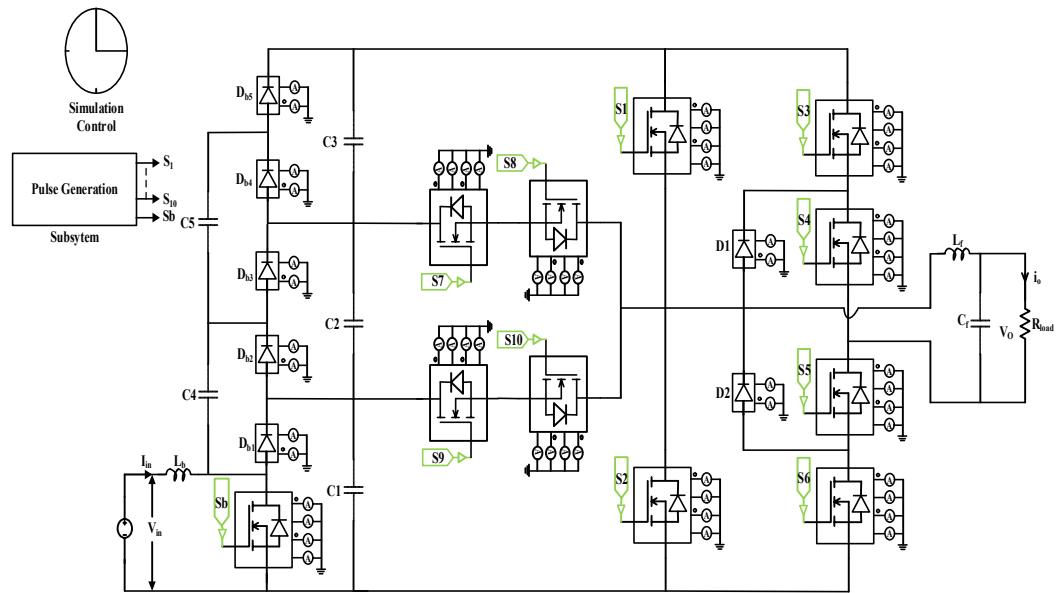

| Fig. 5.1  | Proposed two-stage grid-connected PV inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114 |

| Fig. 5.2  | Operating condition of the switch (a) on-state (b) off state.                                                                                                                                                                                                                                                                                                                                                                                                                           | 115 |

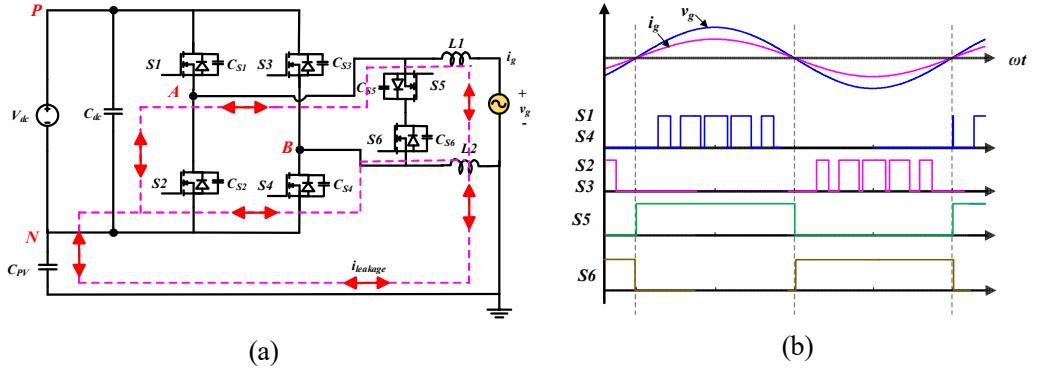

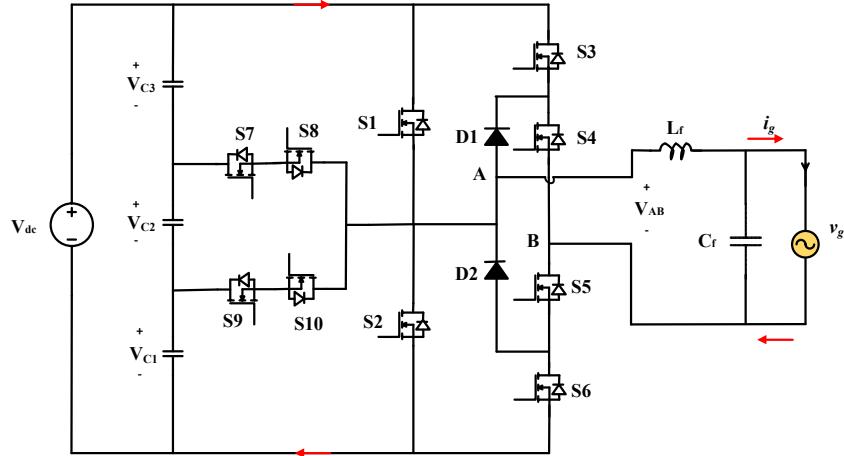

| Fig. 5.3  | Proposed hybrid seven-level inverter topology.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117 |

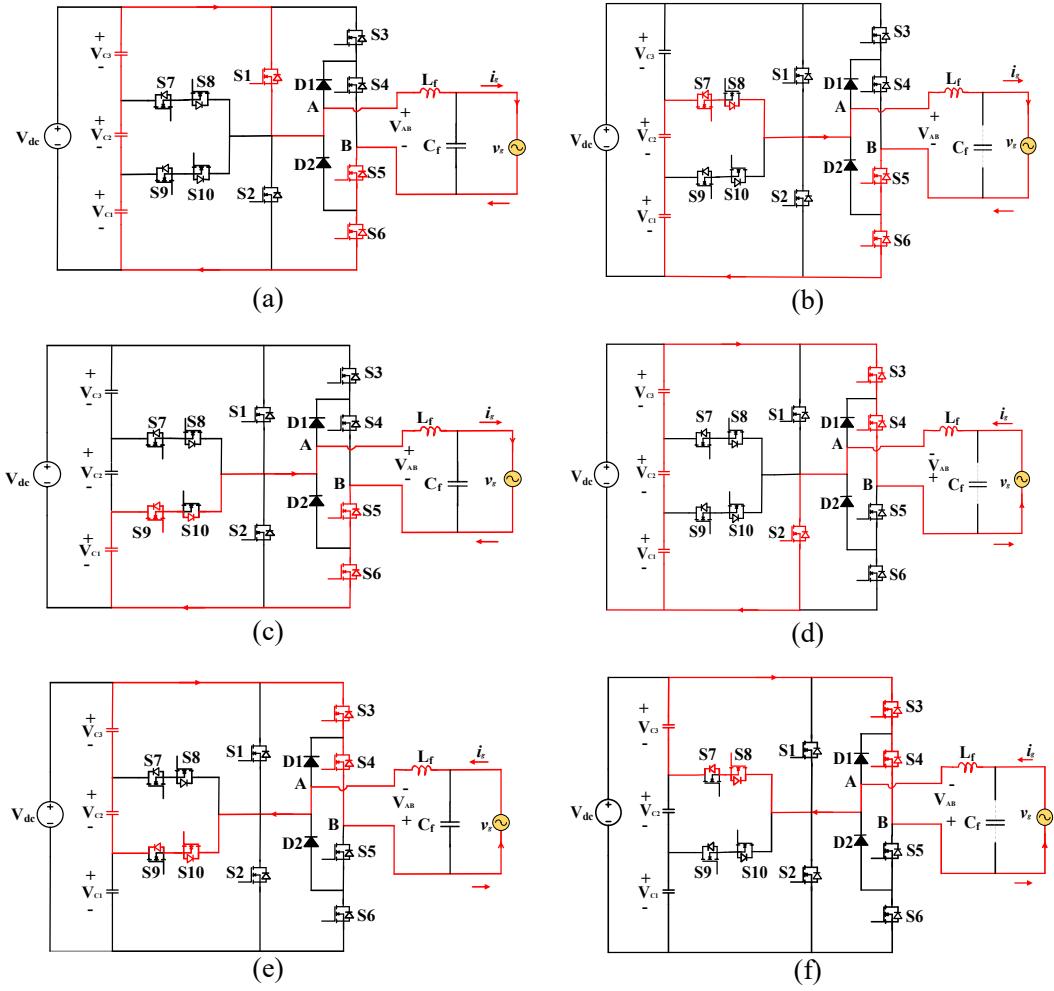

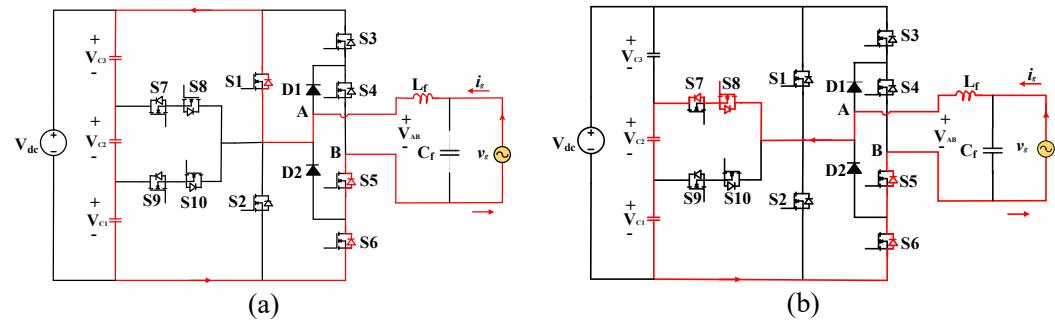

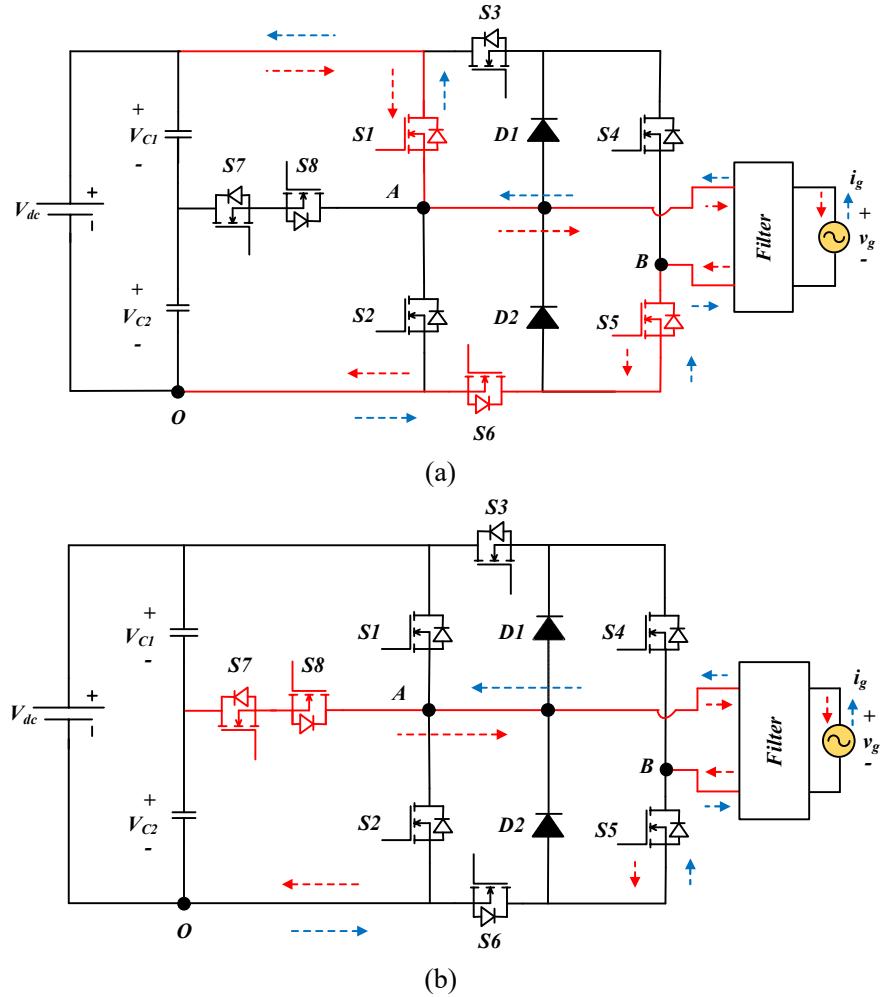

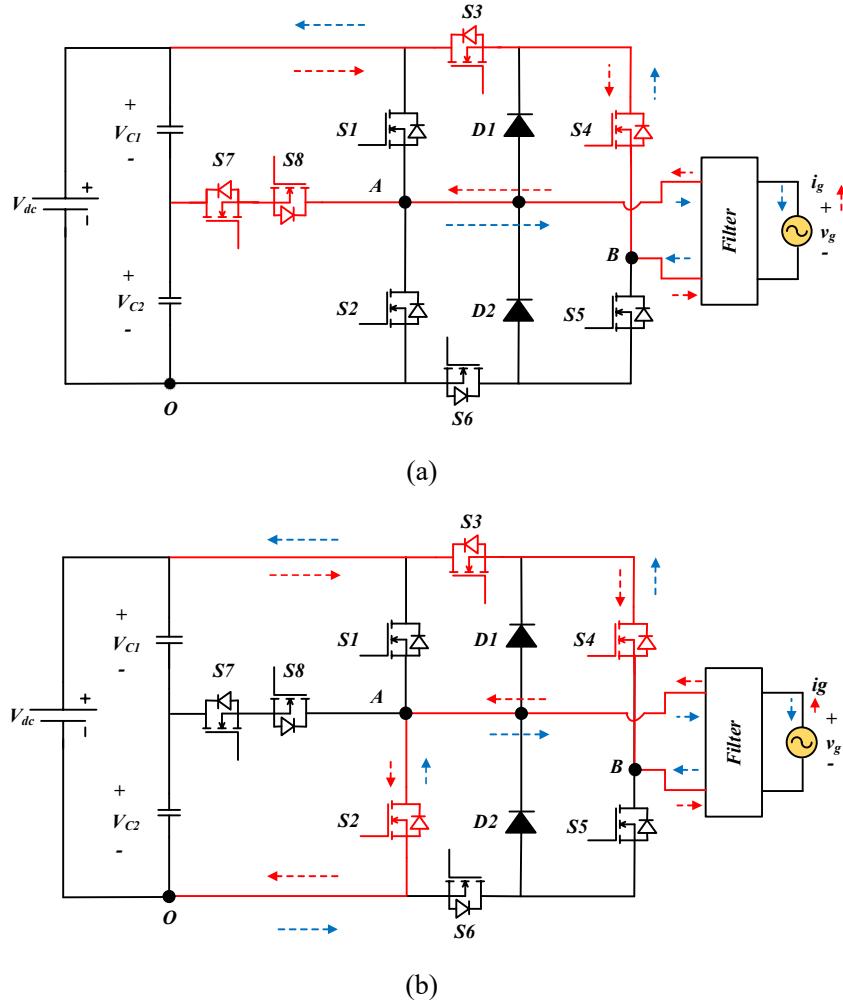

| Fig. 5.4  | Operating modes of the proposed topology when $v_g$ , $i_g$ are positive and $v_g$ , $i_g$ are negative respectively (a) $V_{AB} = (V_{C1} + V_{C2} + V_{C3})$ , (state 1 in table-5.1), (b) $V_{AB} = (V_{C1} + V_{C2})$ (state 2 in table-5.1), (c) $V_{AB} = V_{C1}$ (state 3 in table-5.1), (d) $V_{AB} = -(V_{C1} + V_{C2} + V_{C3})$ (state 6 in table-5.1), (e) $V_{AB} = -(V_{C2} + V_{C3})$ (state 7 in table-5.1), (f) $V_{AB} = -V_{C3}$ (state 8 in table-1).               | 118 |

| Fig. 5.5  | Operating modes of the proposed topology when $v_g$ positive and $i_g$ negative, $v_g$ negative and $i_g$ positive respectively. (a) $V_{AB} = (V_{C1} + V_{C2} + V_{C3})$ (state 1 in table-5.1), (b) $V_{AB} = (V_{C1} + V_{C2})$ (state 2 in table-5.1), (c) $V_{AB} = V_{C1}$ (state 3 in table-5.1), (d) $V_{AB} = -(V_{C1} + V_{C2} + V_{C3})$ (state 6 in table-5.1), (e) $V_{AB} = -(V_{C2} + V_{C3})$ (state 7 in table-5.1), (f) $V_{AB} = -(V_{C3})$ (state 8 in table-5.1). | 120 |

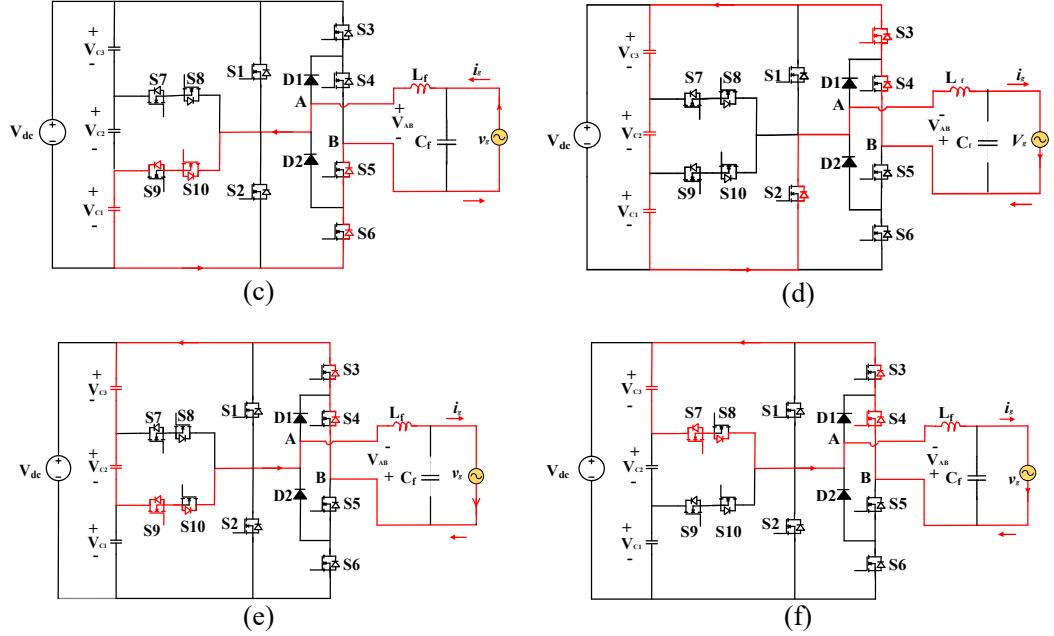

| Fig. 5.6  | Operating modes of the proposed topology in zero states ( $V_{AB}=0$ ); (a) state 4 in table 5.1, (b) state 5 in table 5.1.                                                                                                                                                                                                                                                                                                                                                             | 121 |

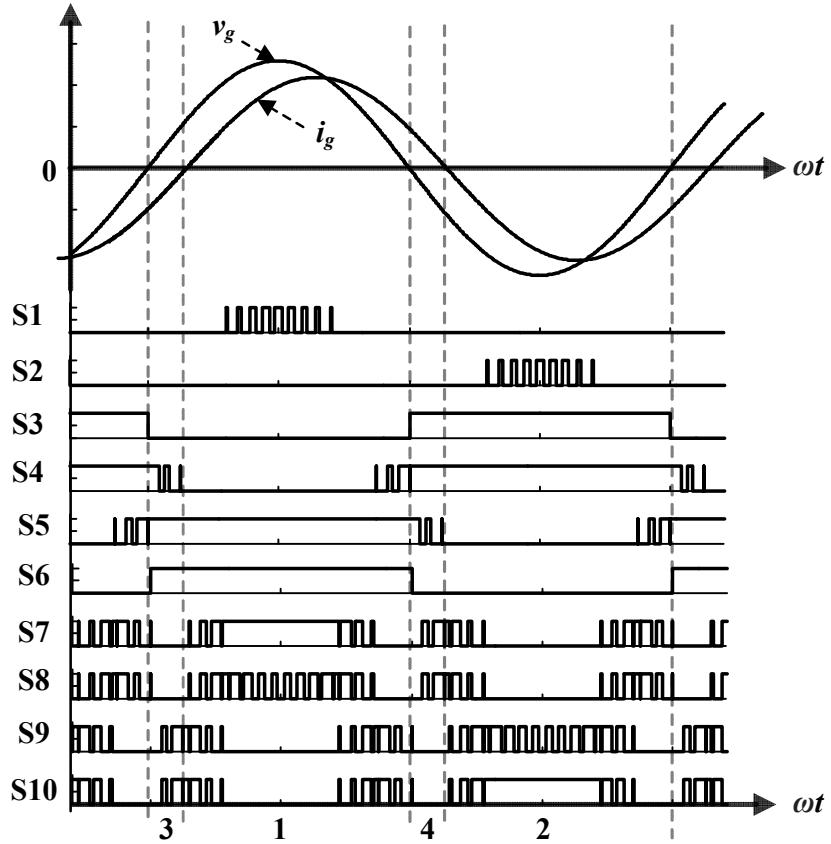

| Fig. 5.7  | Switching patterns for the inverter switches with reactive power capability.                                                                                                                                                                                                                                                                                                                                                                                                            | 122 |

|           |                                                                                                                                                                                                                                                   |     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

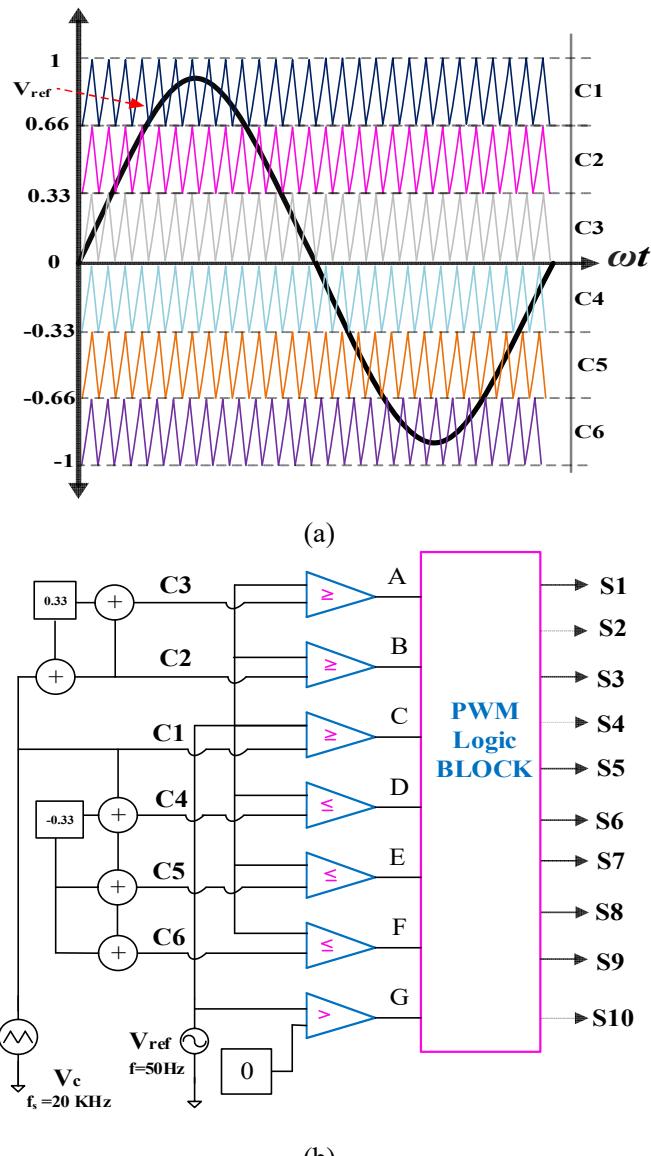

| Fig. 5.8  | (a) Seven-level SLS-PWM technique, (b) Implementation of SLS-PWM.                                                                                                                                                                                 | 123 |

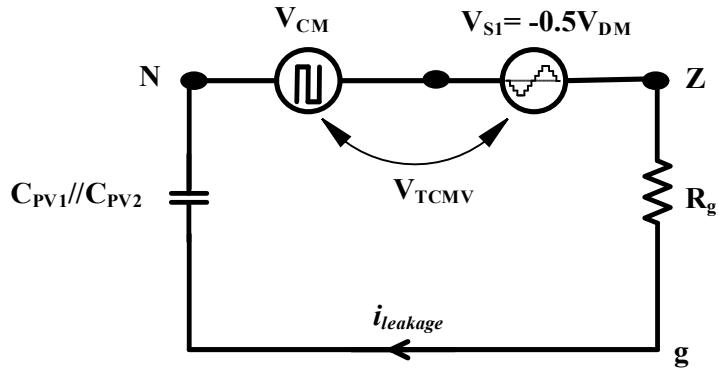

| Fig. 5.9  | Equivalent common-mode model for the proposed topology.                                                                                                                                                                                           | 124 |

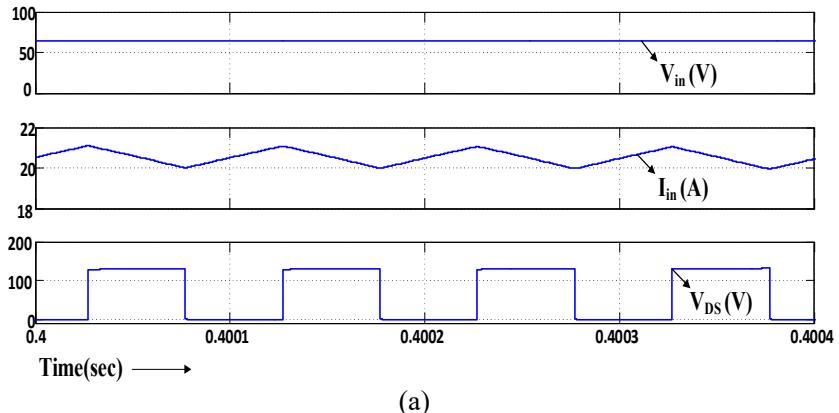

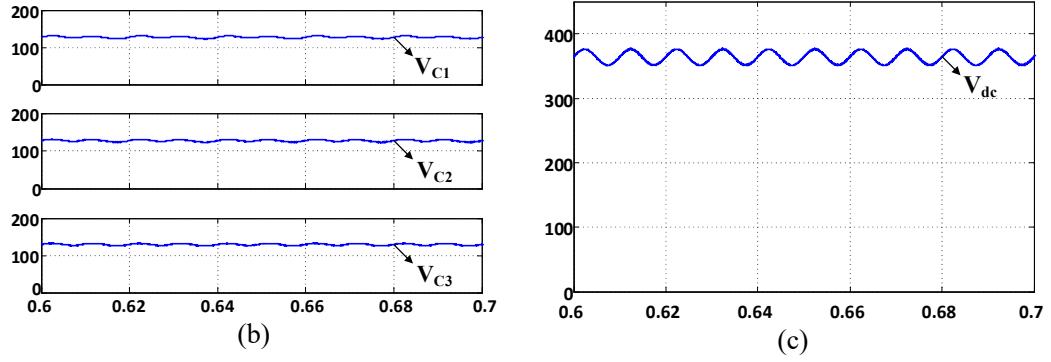

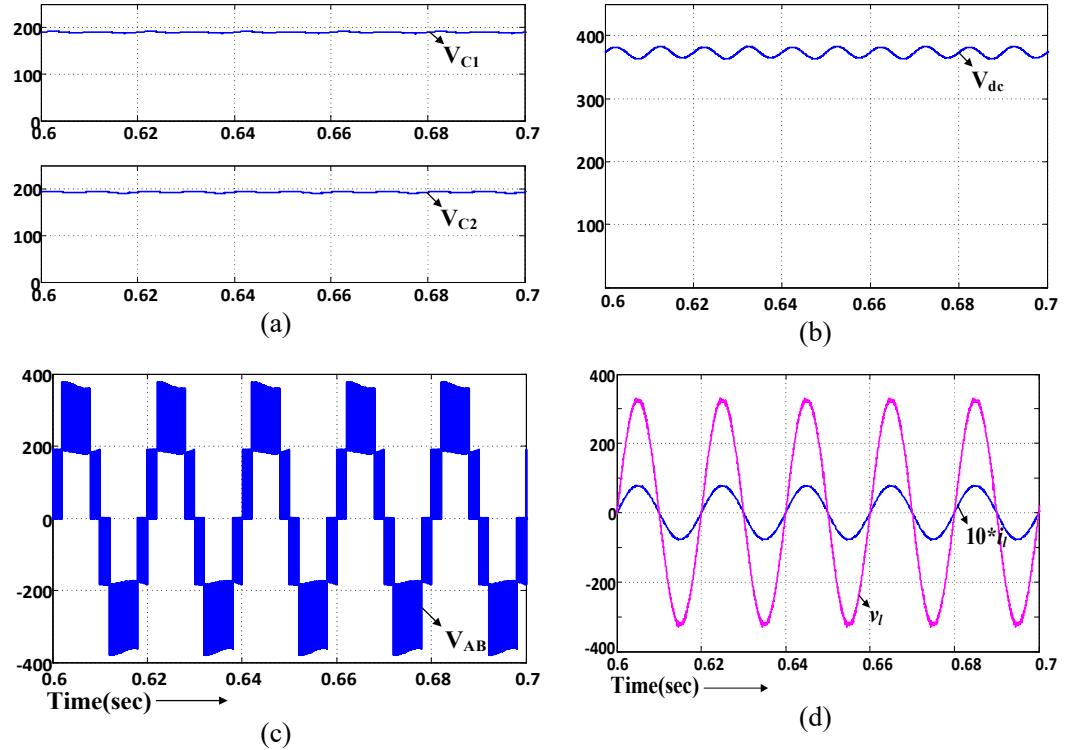

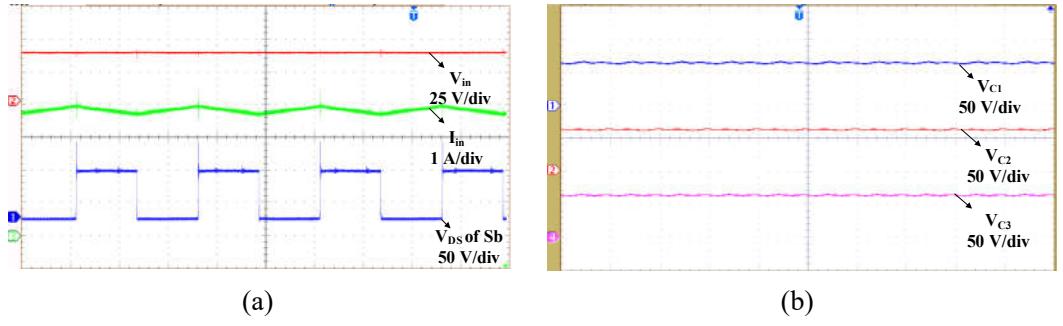

| Fig. 5.10 | Simulation results of MLBC; (a) input voltage, current and drain-source voltage of Sb, (b) balanced capacitor voltages (c) total DC-link voltage.                                                                                                 | 126 |

| Fig. 5.11 | Simulation results for the proposed seven-level inverter: (a) seven-level output voltage (b), (c) and (d) $v_l$ and $i_l$ at unity, lagging (0.58) and leading (0.58) power factor operations respectively.                                       | 126 |

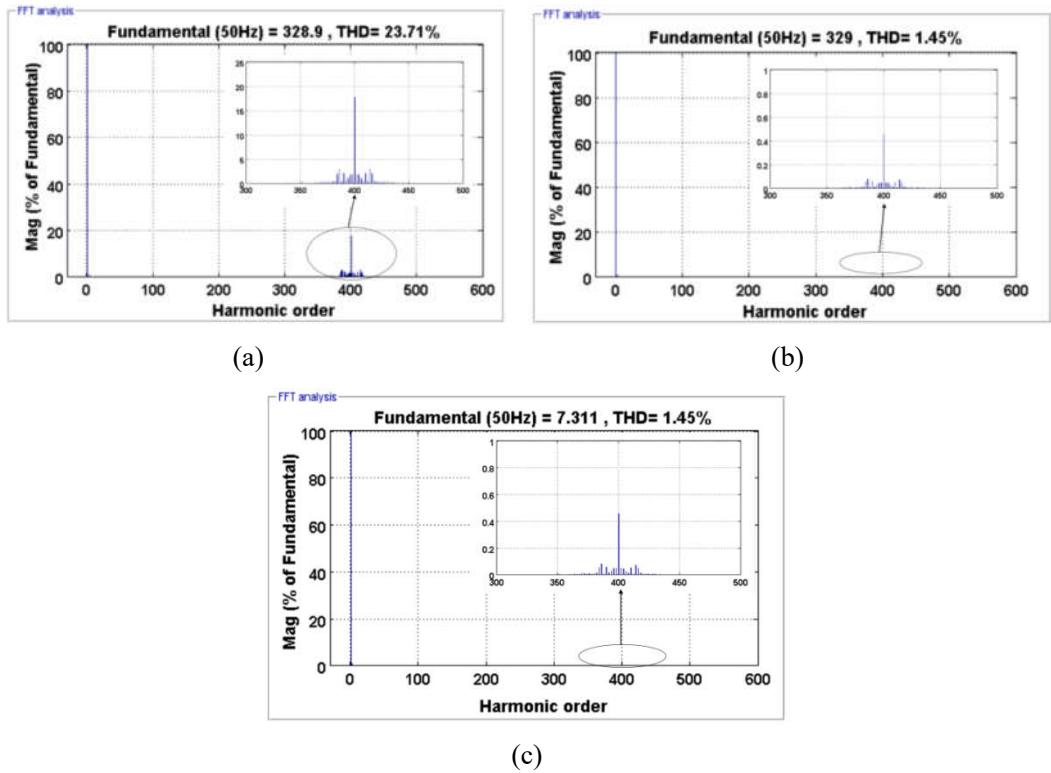

| Fig. 5.12 | THD spectrums of the seven-level MLI: (a) terminal voltage $V_{AB}$ and, (b) load voltage and, (c) load current with R load.                                                                                                                      | 127 |

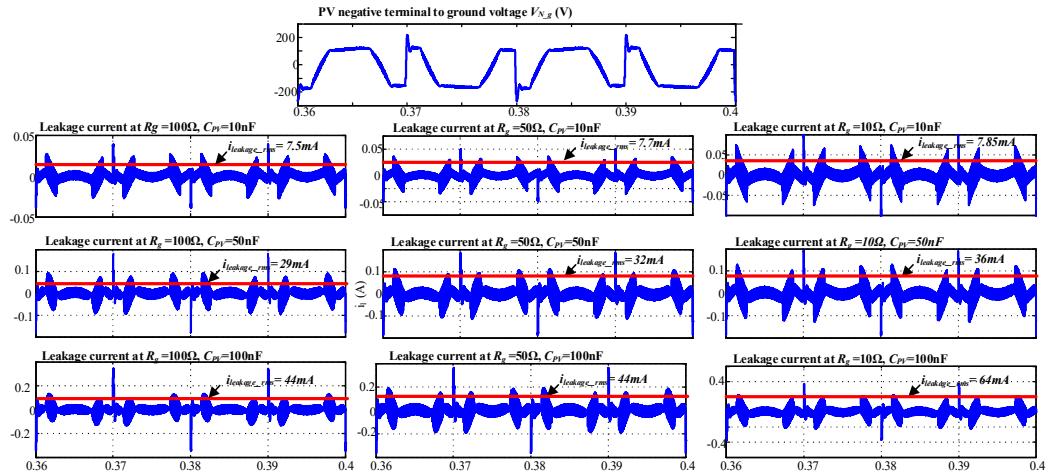

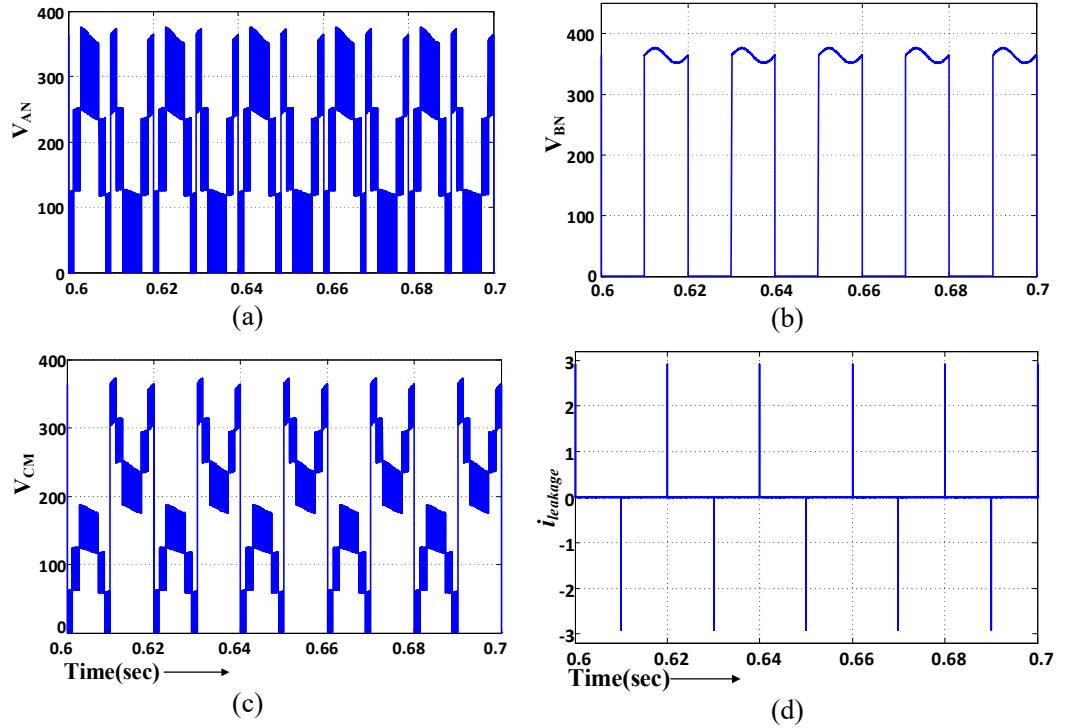

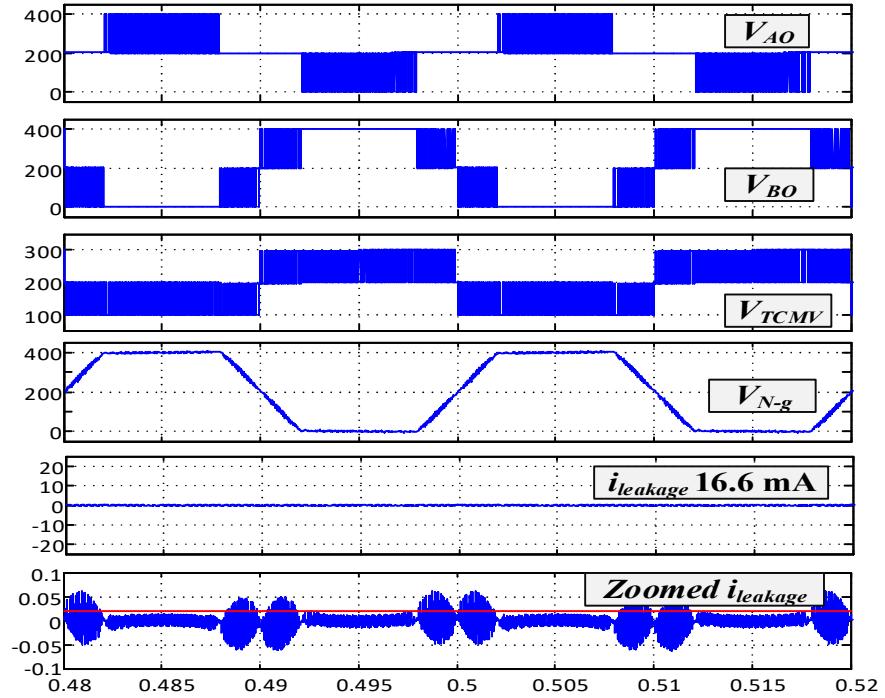

| Fig. 5.13 | Simulation results of seven-level inverter; (a) voltage $V_{AN}$ , (b) voltage $V_{TCMV}$ ( $=V_{BN}$ ), (c) CMV, and (d) Leakage current $i_{leakage}$ .                                                                                         | 128 |

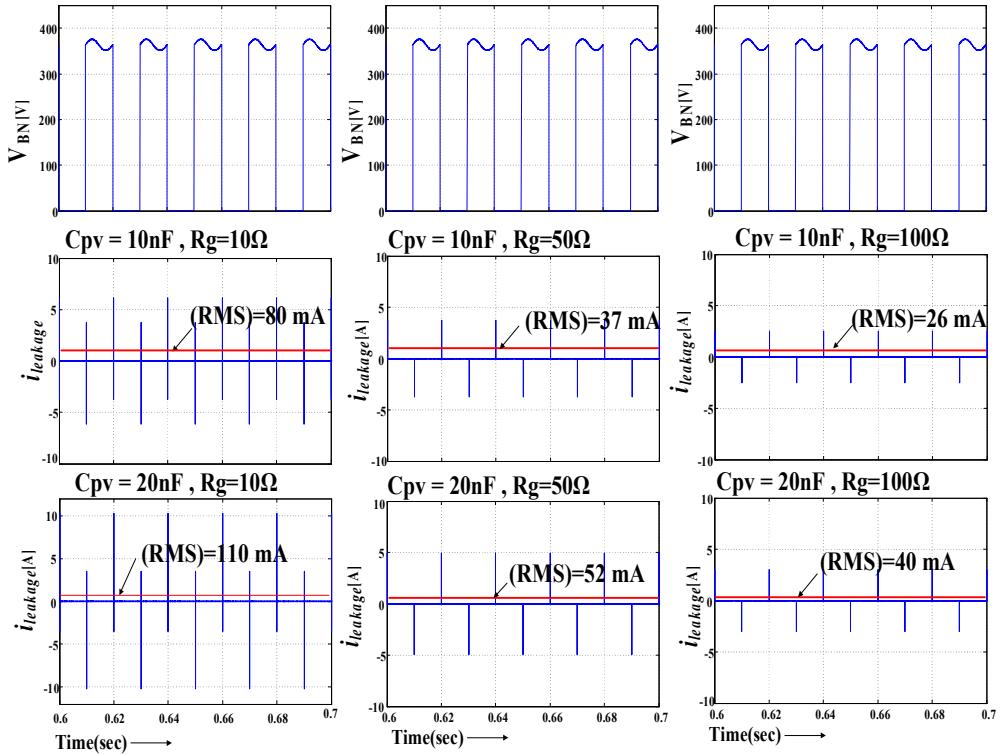

| Fig. 5.14 | Total common-mode voltage $V_{tcn}$ ( $=V_{BN}$ ) and leakage current ( $i_{leakage}$ ) at three different parasitic capacitance and ground resistance conditions.                                                                                | 128 |

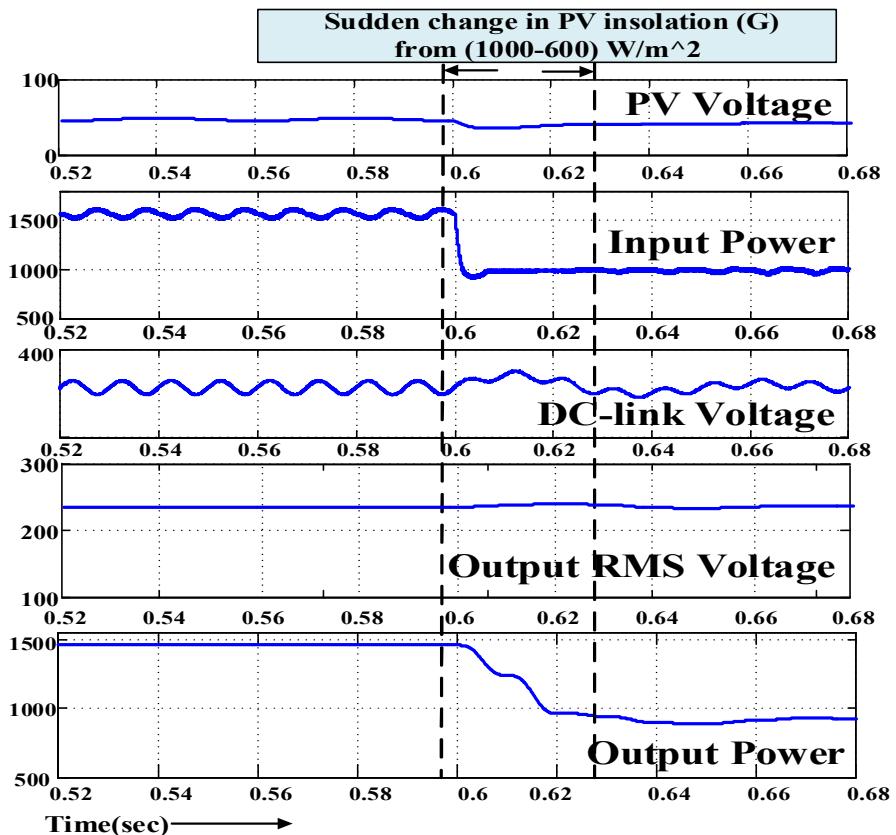

| Fig. 5.15 | Voltage and power results of grid-connected two-stage inverter when insolation changes from $1000 \text{ W/m}^2$ to $600 \text{ W/m}^2$                                                                                                           | 129 |

| Fig. 5.16 | Proposed two-stage five-level inverter.                                                                                                                                                                                                           | 130 |

| Fig. 5.17 | Simulation results of the proposed five-level inverter; (a) DC capacitor voltages, (b) DC-link voltage, (c) five-level inverter voltage and, (d) output load voltage and current after the LC filter.                                             | 130 |

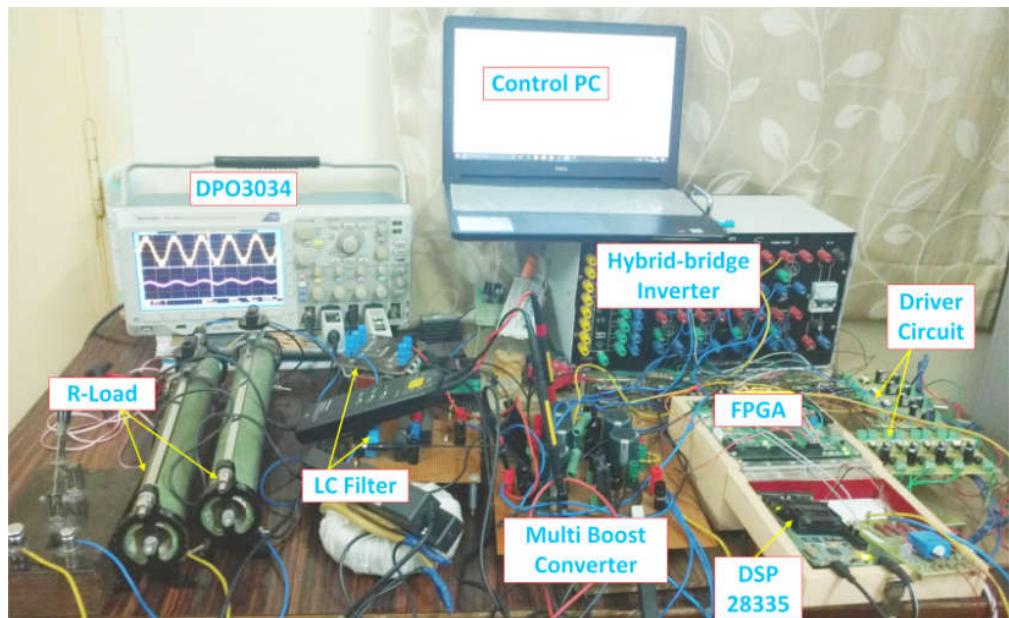

| Fig. 5.18 | Experimental setup.                                                                                                                                                                                                                               | 131 |

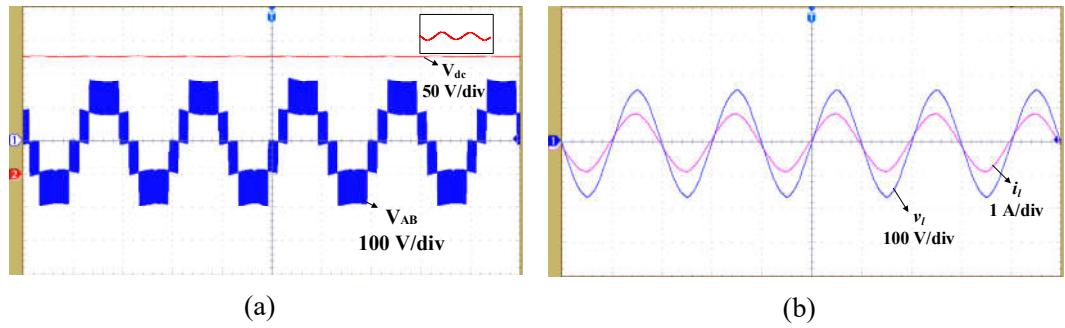

| Fig. 5.19 | Experimental results of the MLBC; (a) input voltage, current and drain-source voltage of Sb (b) balanced DC-link voltages.                                                                                                                        | 132 |

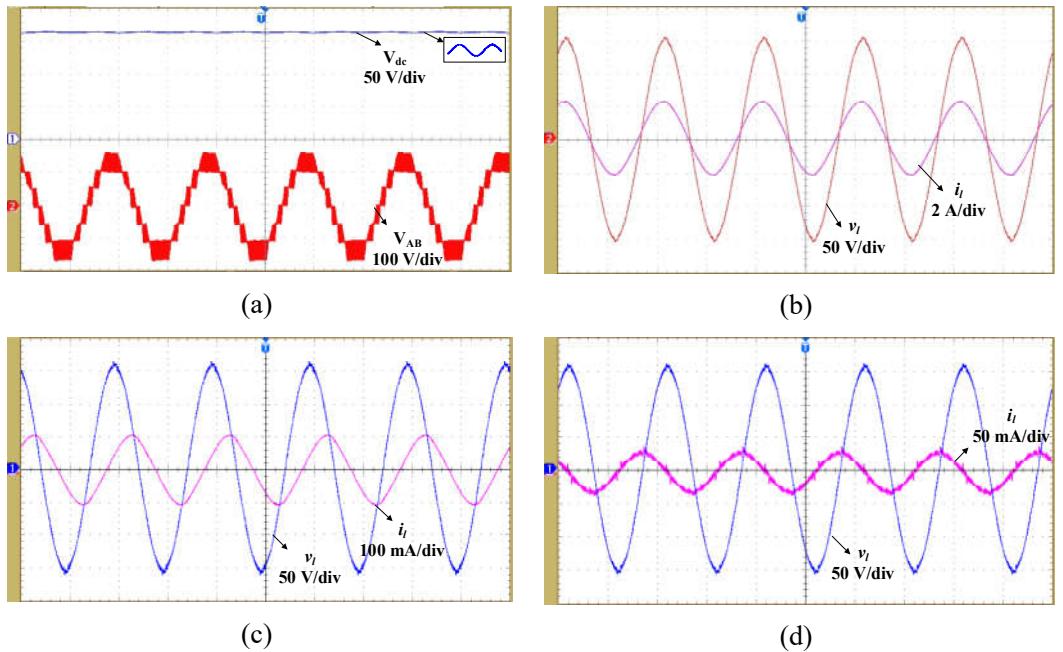

| Fig. 5.20 | Experimental results of the proposed topology (a) total DC-link voltage and seven-level voltage; load voltage and current under (b) UPF, (c) 0.58 lagging, and, (d) 0.58 leading conditions respectively.                                         | 132 |

| Fig. 5.21 | Experimental results of the proposed topology (a) and (b) step change in load current from high to low and low to high at constant output voltage, and (c) transient voltage variations in input voltage and their corresponding DC-link voltage. | 133 |

|           |                                                                                                                                                                                                                                                                                                              |     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

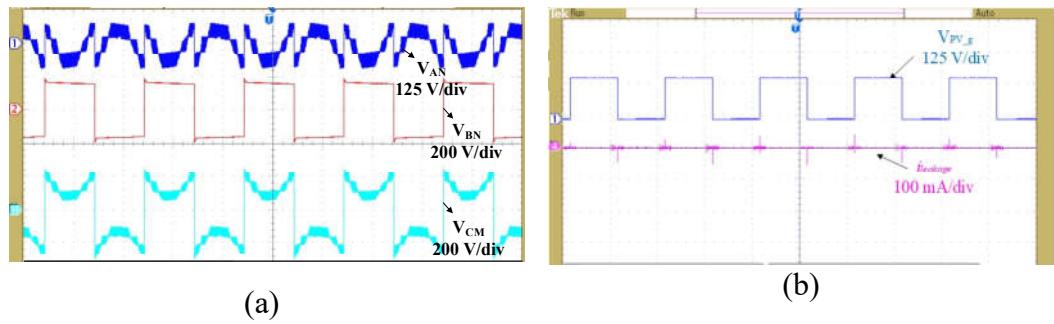

| Fig. 5.22 | Experimental results of the proposed topology (a) terminal voltages of $V_{AN}$ , $V_{BN}$ and $V_{CM}$ and (b) terminal voltage across DC source to ground $V_{Ng}$ and corresponding leakage current.                                                                                                      | 134 |

| Fig. 5.23 | Experimental FFT spectrums for the proposed seven-level MLI (a) load voltage, (b) load current.                                                                                                                                                                                                              | 134 |

| Fig. 5.24 | Experimental results of the proposed two-stage five-level inverter (a) DC-link and level voltage, (b) filtered output voltage and current waveforms under UPF.                                                                                                                                               | 135 |

| Fig. 5.25 | PSIM thermal module model for the proposed two-stage seven-level MLI.                                                                                                                                                                                                                                        | 138 |

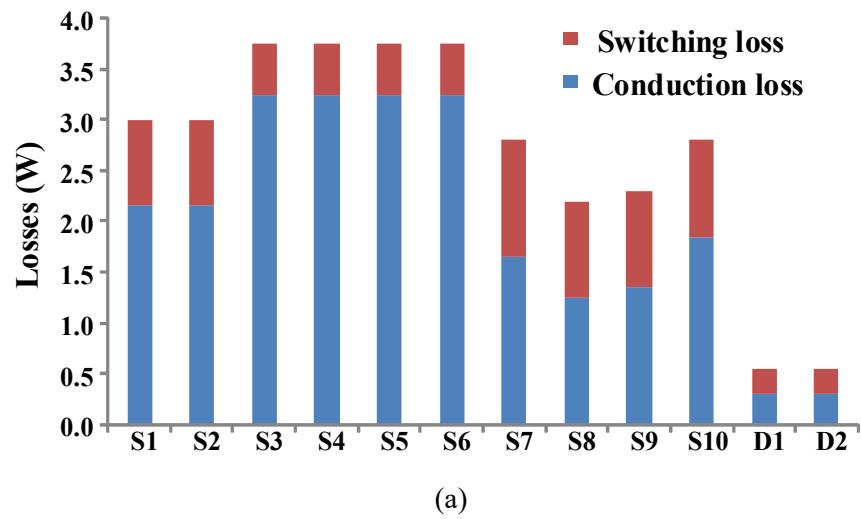

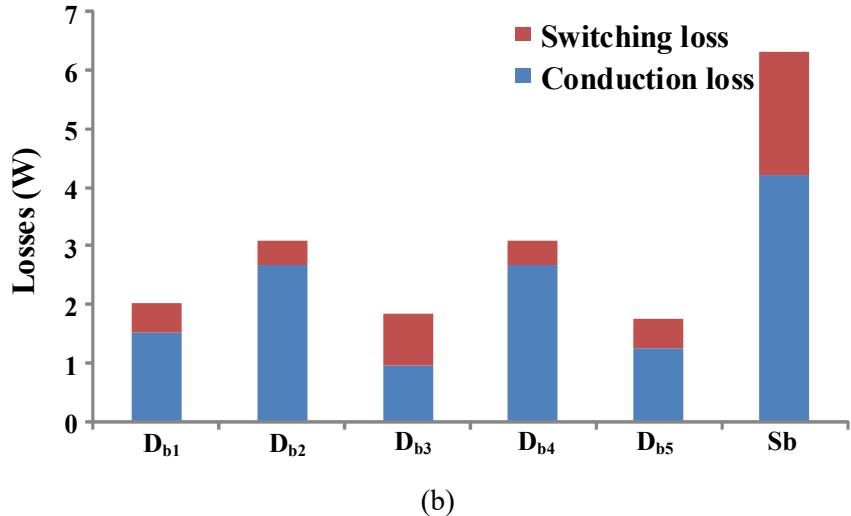

| Fig. 5.26 | Distribution of power losses in the semiconductor switches of (a) hybrid seven-level inverter (b) multilevel boost converter.                                                                                                                                                                                | 139 |

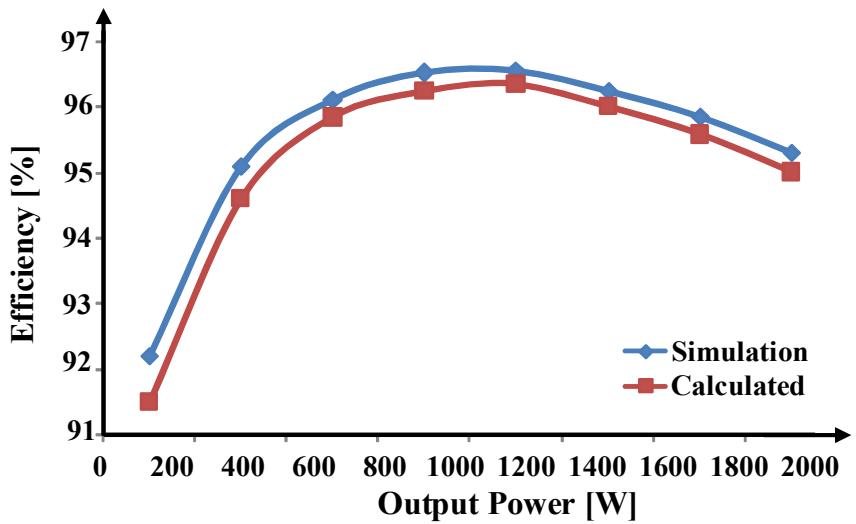

| Fig. 5.27 | Efficiency curve                                                                                                                                                                                                                                                                                             | 139 |

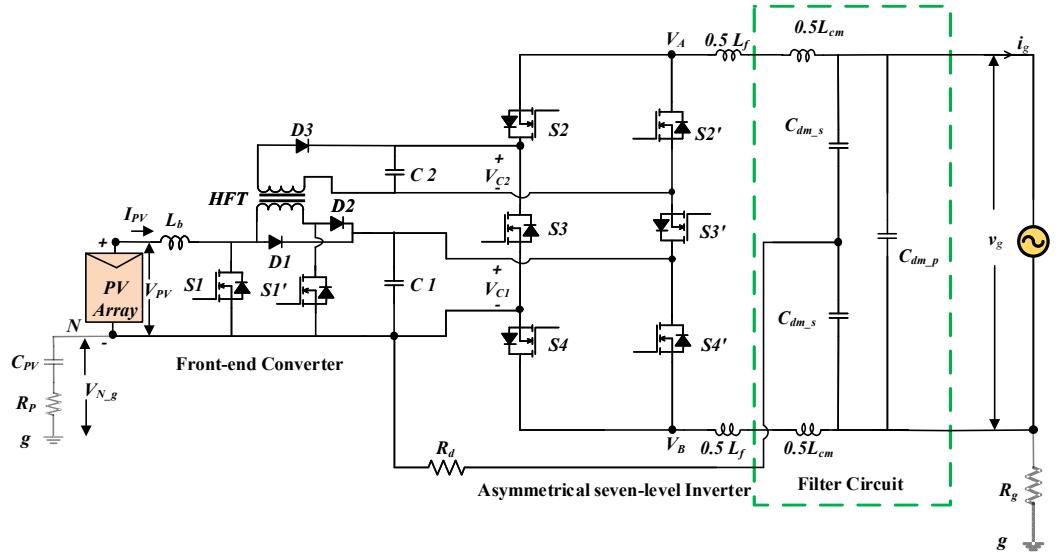

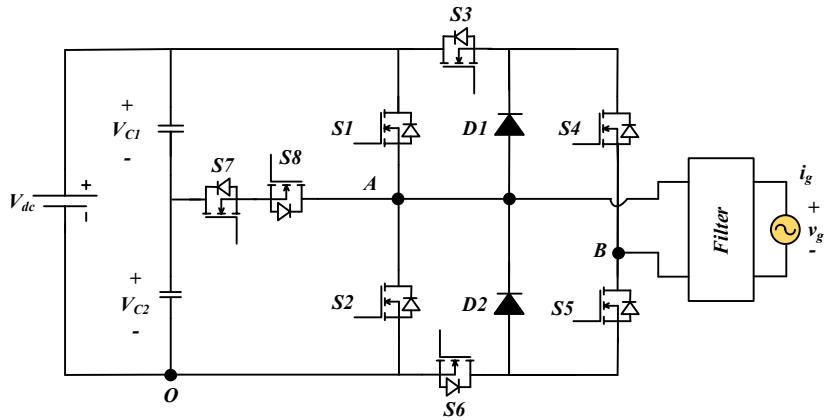

| Fig. 6.1  | Proposed two-stage T-type hybrid five-level TLI.                                                                                                                                                                                                                                                             | 143 |

| Fig. 6.2  | Block diagram of 3LBC with PI control.                                                                                                                                                                                                                                                                       | 144 |

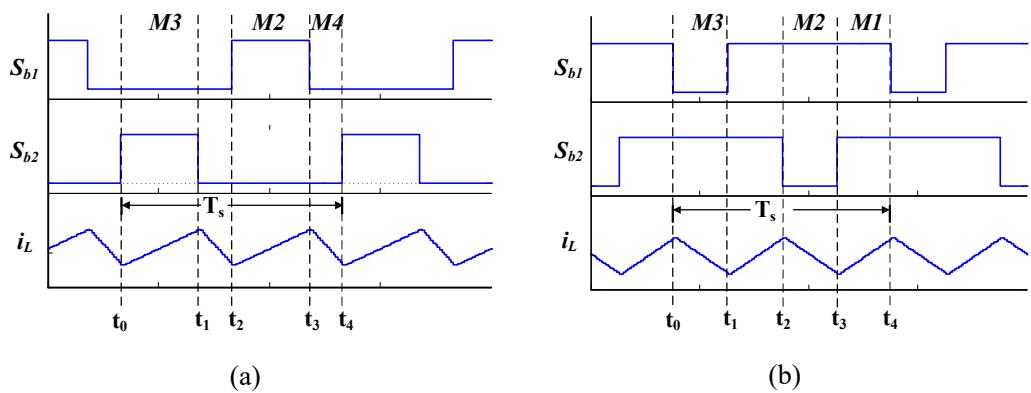

| Fig. 6.3  | Gate pulses and inductor current of 3LBC: (a) region 1, (b) region 2.                                                                                                                                                                                                                                        | 144 |

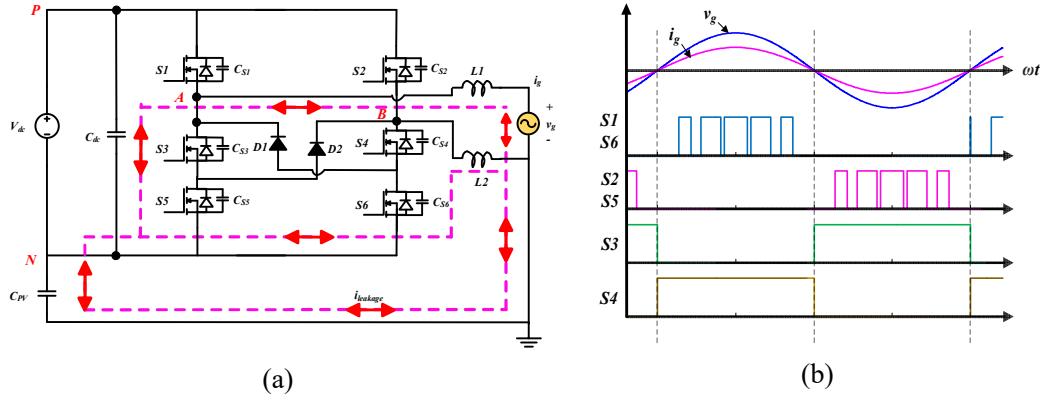

| Fig. 6.4  | Proposed T-Type Hybrid Five-level TLI.                                                                                                                                                                                                                                                                       | 145 |

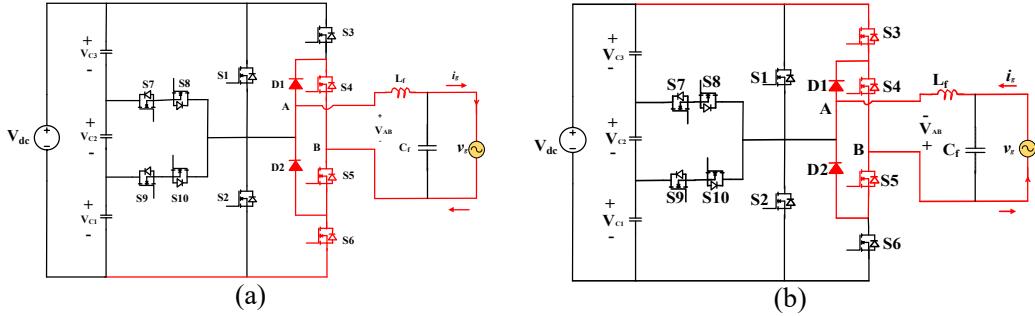

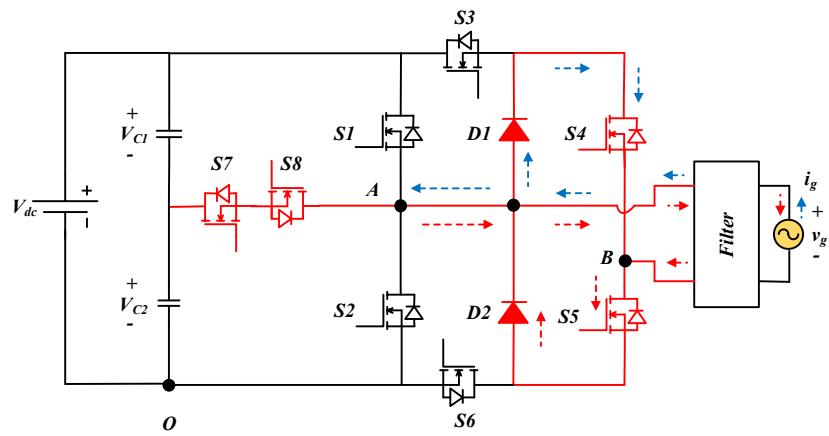

| Fig. 6.5  | Operating states of the inverter: (a) State 1 ( $V_{AB} = (V_{C1} + V_{C2})$ ), (b) State 2 ( $V_{AB} = V_{C2}$ )                                                                                                                                                                                            | 146 |

| Fig. 6.6  | Operation of the inverter during state 3 ( $V_{AB} = 0$ ).                                                                                                                                                                                                                                                   | 147 |

| Fig. 6.7  | Operating states of the inverter (a) State 4 ( $V_{AB} = -V_{C1}$ ), (b) State 5 ( $V_{AB} = -(V_{C1} + V_{C2})$ ).                                                                                                                                                                                          | 148 |

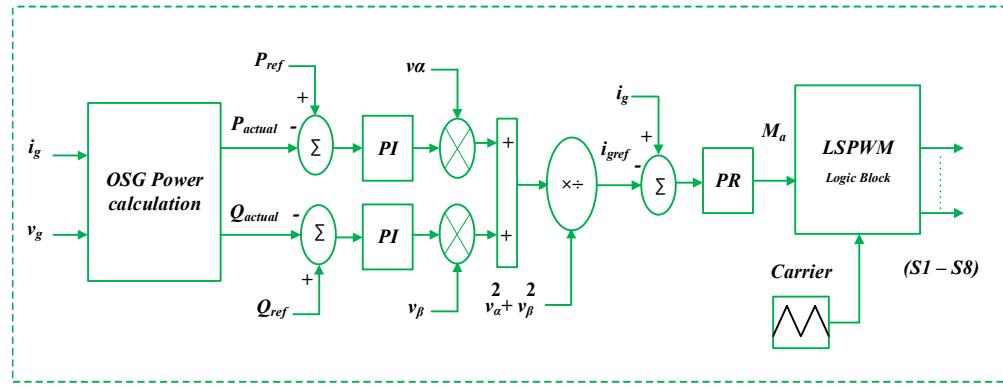

| Fig. 6.8  | Closed-loop control of the proposed inverter topology.                                                                                                                                                                                                                                                       | 149 |

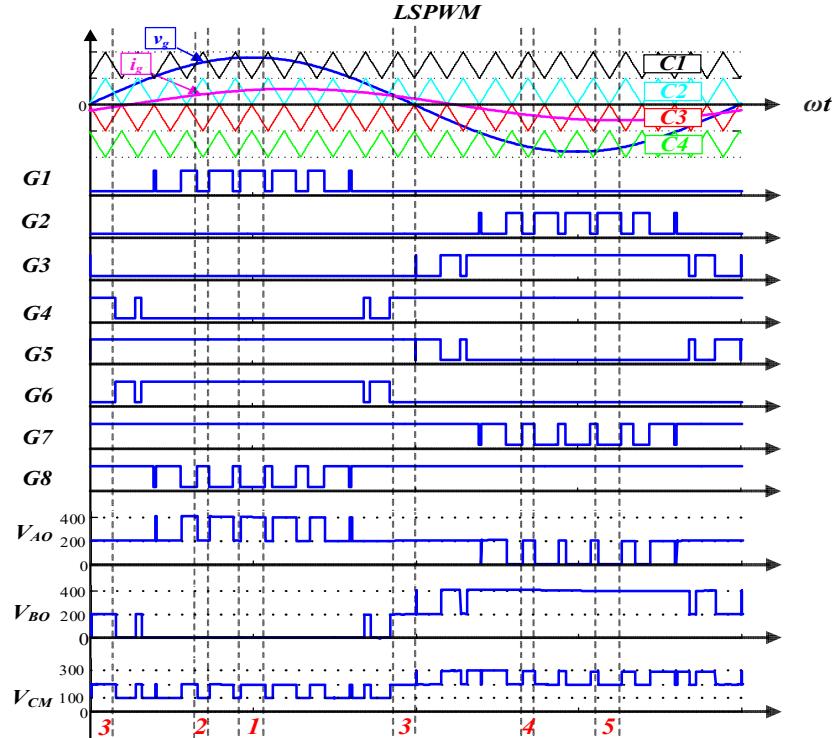

| Fig. 6.9  | Switching pulse generation corresponding to its operating states of the proposed inverter.                                                                                                                                                                                                                   | 149 |

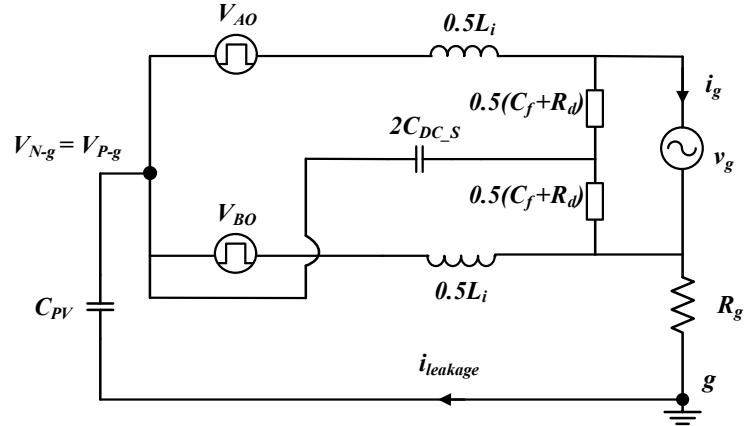

| Fig. 6.10 | (a). Common-mode equivalent circuit of the proposed TLI, (b) Equivalent circuit in terms of CMV and DMV and (c) Simplified circuit.                                                                                                                                                                          | 151 |

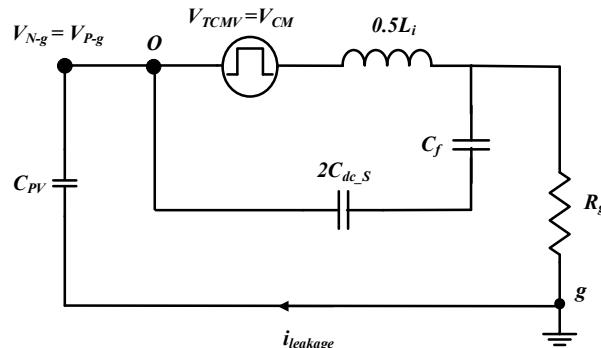

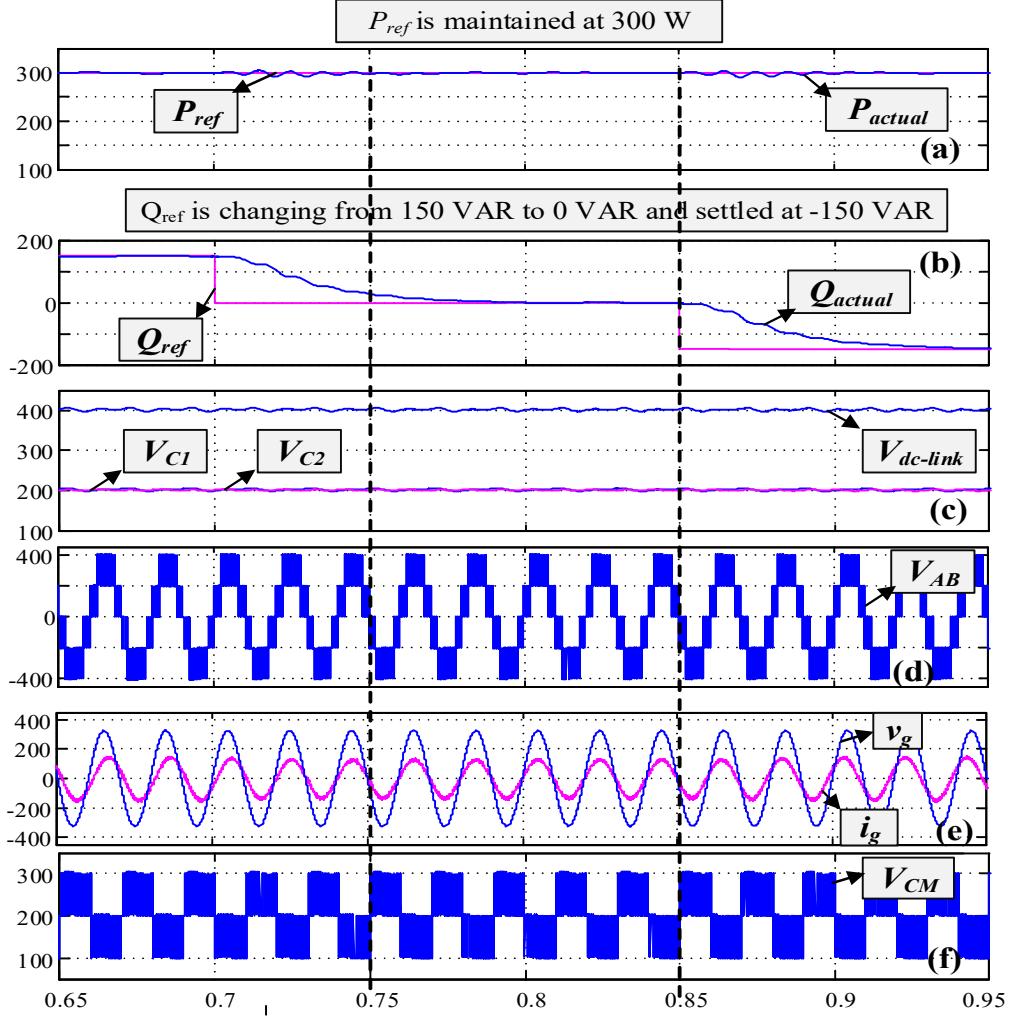

| Fig. 6.11 | Simulation results of the proposed two-stage system when $P_{ref}$ is changing from 500 W to 300 W and setteled at 400 W; (a) sudden changes in $P_{ref}$ , (b) constant $Q_{ref}$ , (c) total DC-link voltage and capacitor voltages $C1$ and $C2$ , (d) $V_{AB}$ , (e) $v_g$ and $70*i_g$ , (f) $V_{CM}$ . | 154 |

|           |                                                                                                                                                                                                                                                                     |     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

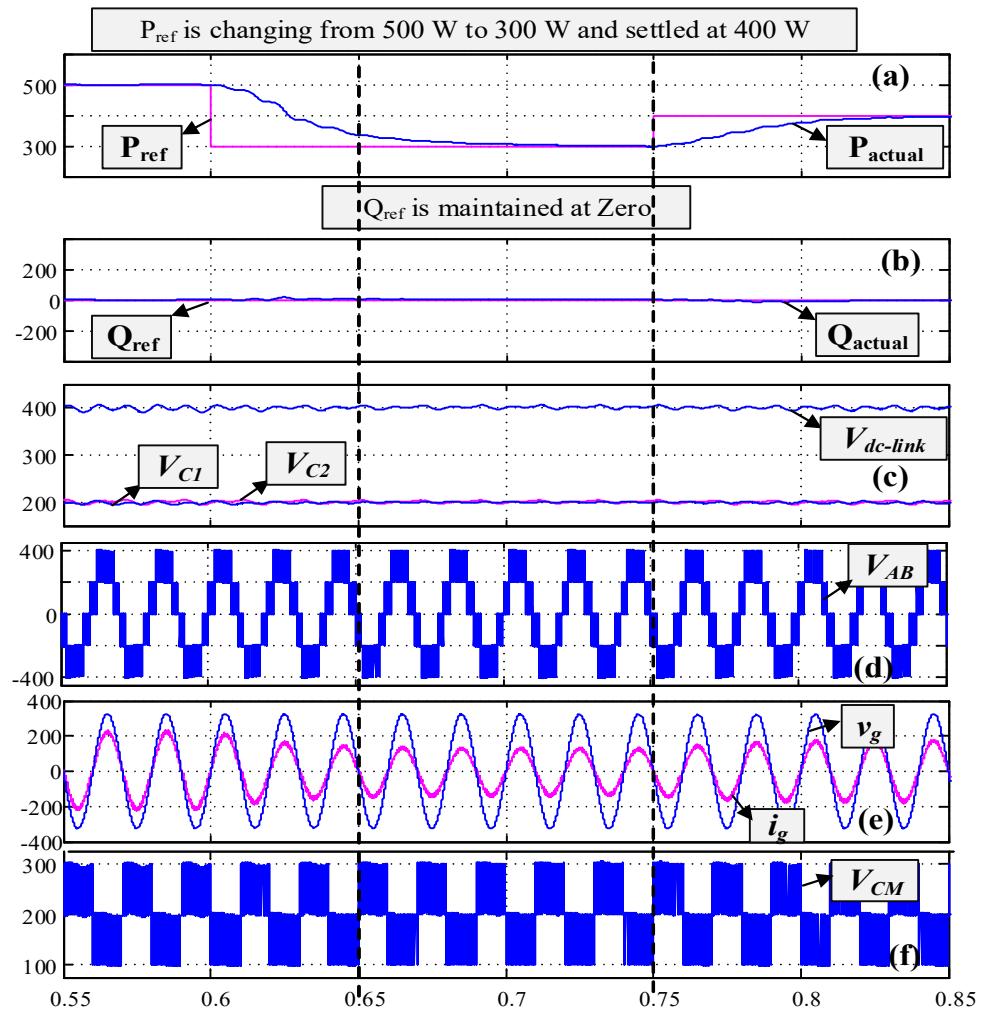

| Fig. 6.12 | Simulation results of the proposed two-stage system when $Q_{ref}$ is changing from 150 VAR to 0 VAR and setteled at -150 VAR;                                                                                                                                      | 155 |

|           | (a) constant $P_{ref}$ , (b) sudden changes in $Q_{ref}$ , (c) total DC-link voltage and capacitor voltages $C1$ and $C2$ , (d) $V_{AB}$ , (e) $v_g$ and $70*i_g$ , (f) $V_{CM}$ .                                                                                  |     |

| Fig. 6.13 | Common-mode characteristics of the proposed TLI topology.                                                                                                                                                                                                           | 156 |

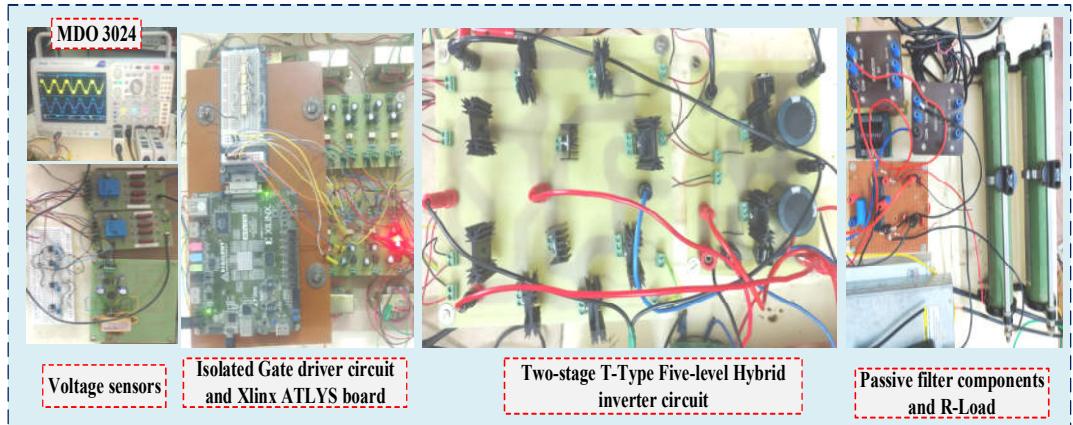

| Fig. 6.14 | Experimental prototype.                                                                                                                                                                                                                                             | 156 |

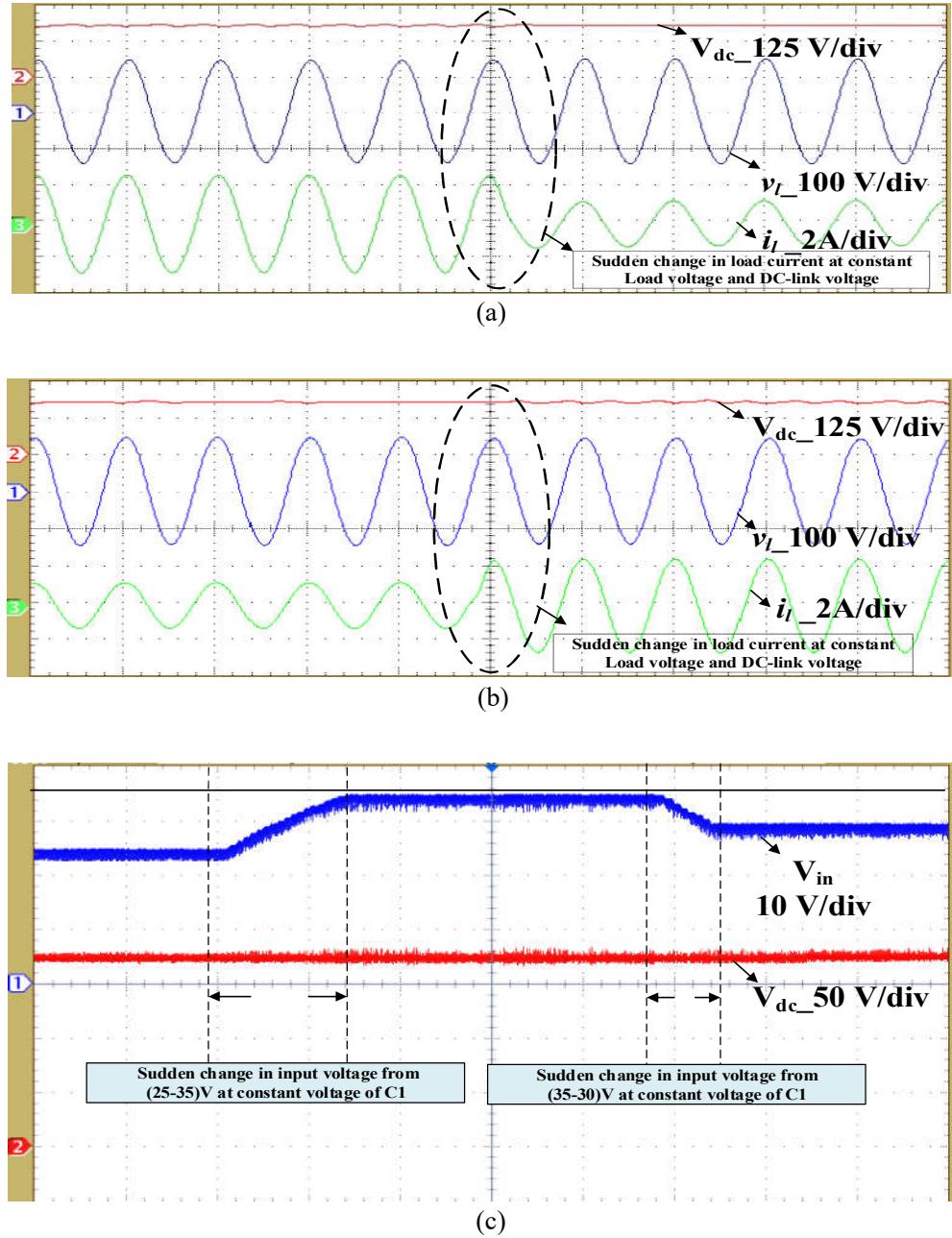

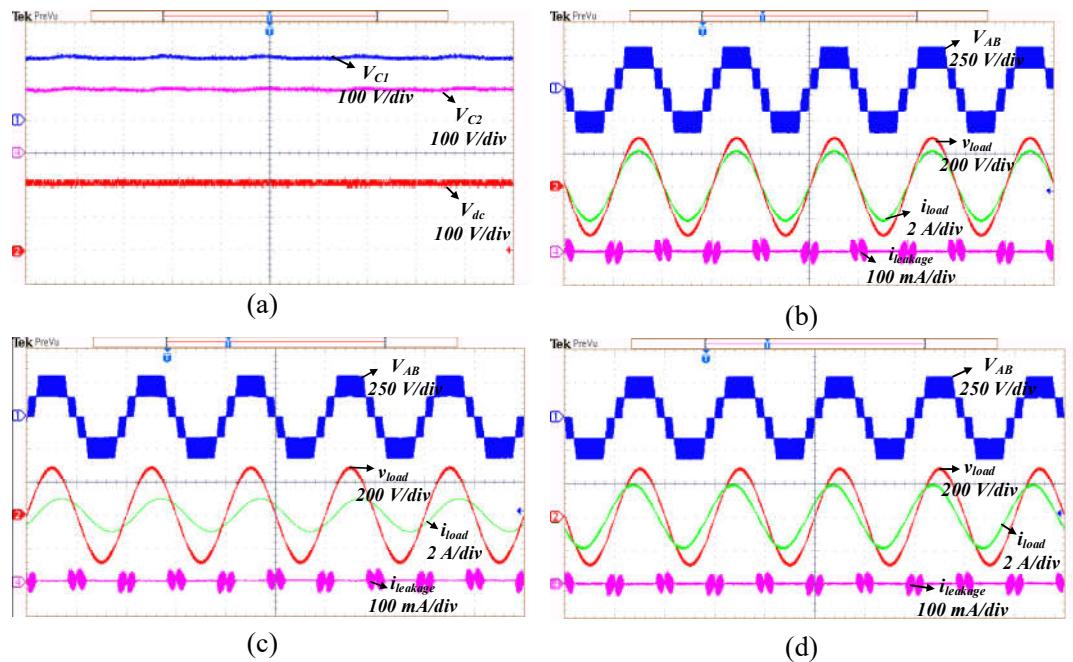

| Fig. 6.15 | (a) Input voltage, DC voltages waveforms of 3LBC; Five-level voltage ( $V_{AB}$ ), load voltage ( $V_{load}$ ), load current ( $i_{load}$ ) and leakage current ( $i_{leakage}$ ) under (b) Unity power factor, (c) Lagging power factor, (d) Leading power factor. | 157 |

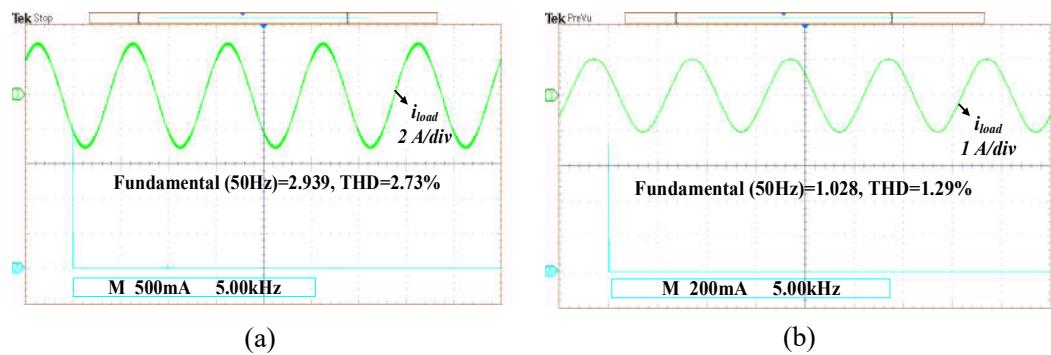

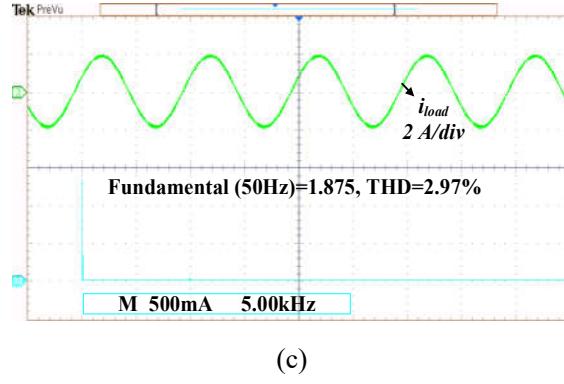

| Fig. 6.16 | FFT spectrums of load current under (a) Unity power factor, (b) Lagging power factor, (c) Leading power factor.                                                                                                                                                     | 158 |

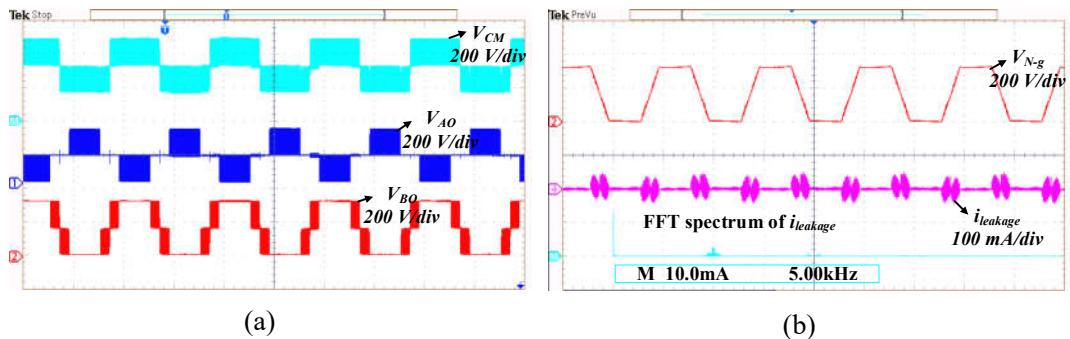

| Fig. 6.17 | (a) Inverter terminal voltages $V_{AO}$ , $V_{BO}$ , $V_{CM}$ , (b) PV negative terminal to ground voltage ( $V_{N\_g}$ ) and leakage current ( $i_{leakage}$ ).                                                                                                    | 158 |

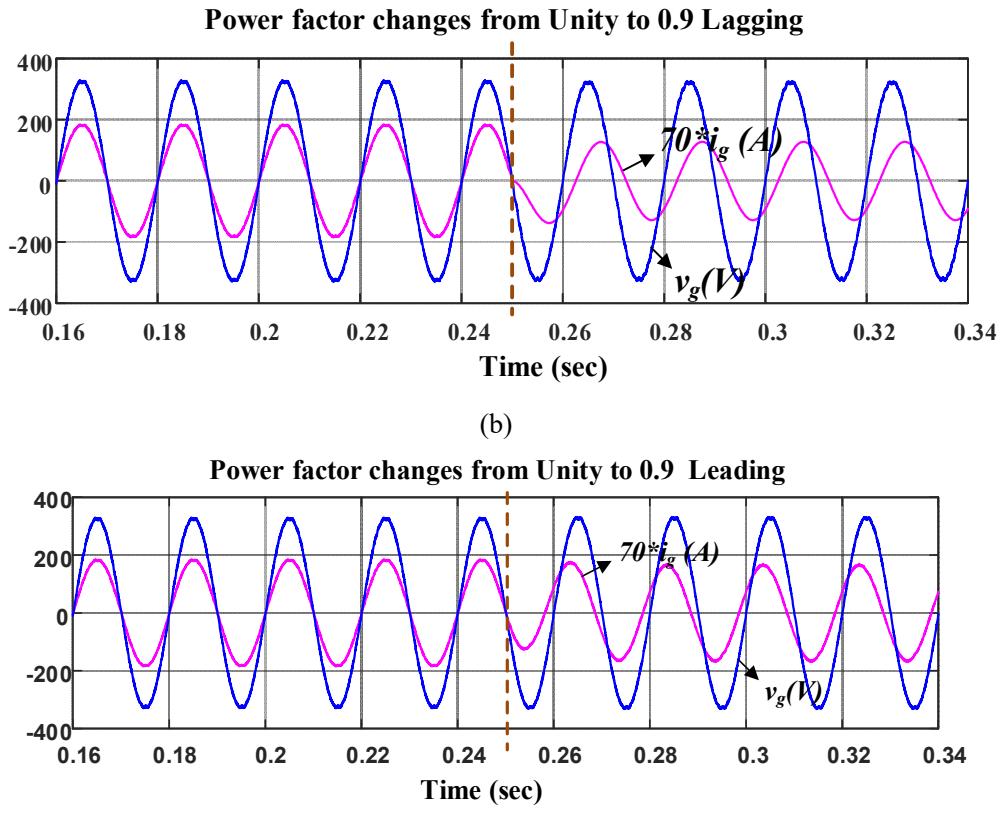

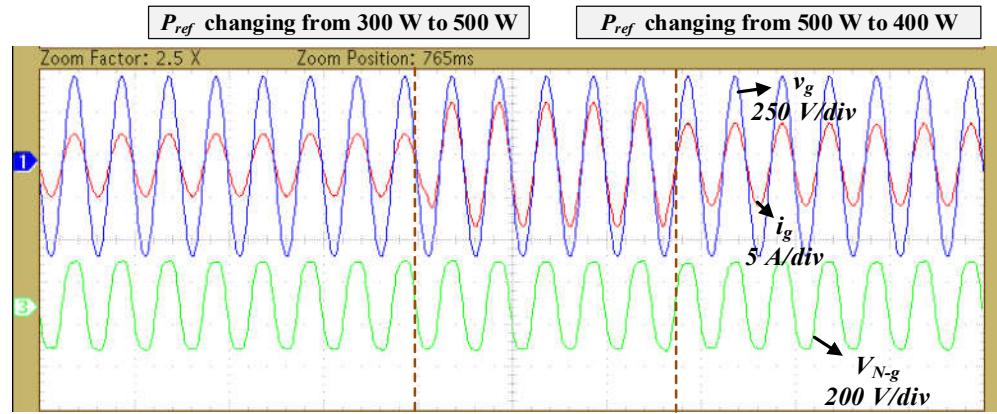

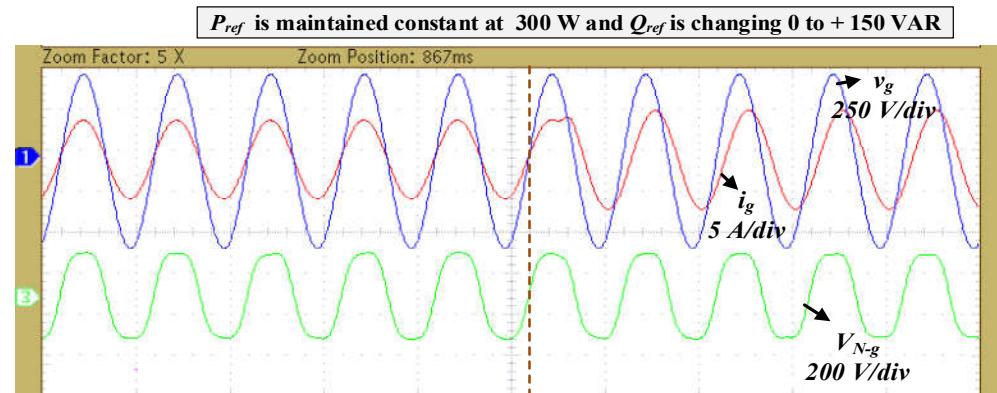

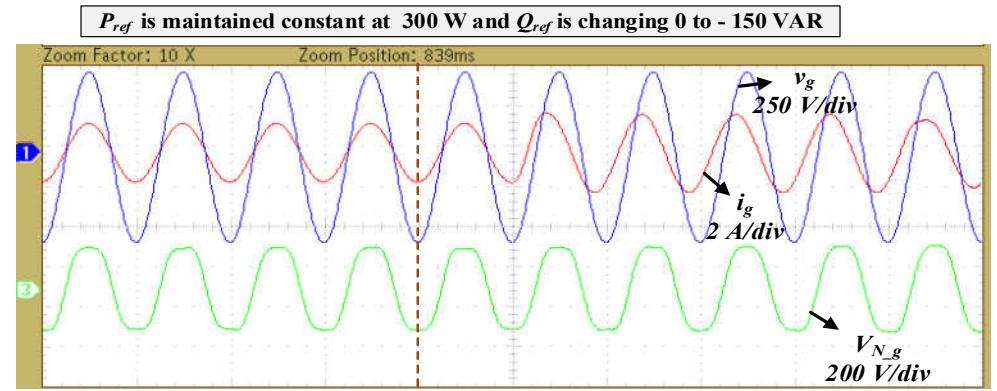

| Fig. 6.18 | (a) Dynamic performance of the proposed two-stage system (a) Step change in real power; Step change in reactive power (b) Lagging (c) Leading.                                                                                                                      | 159 |

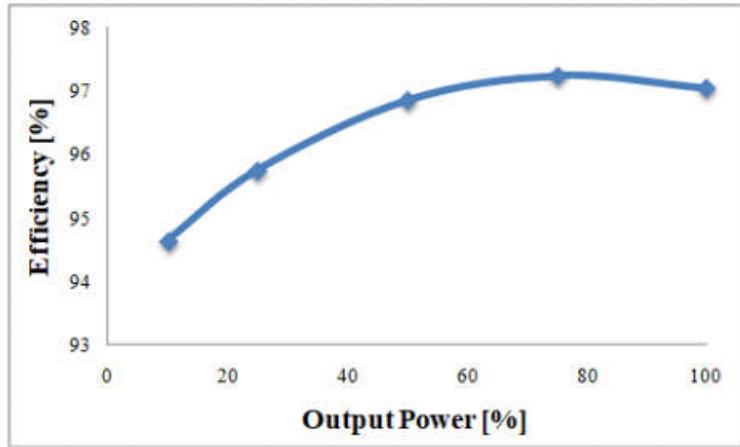

| Fig. 6.19 | Efficiency curve.                                                                                                                                                                                                                                                   | 160 |

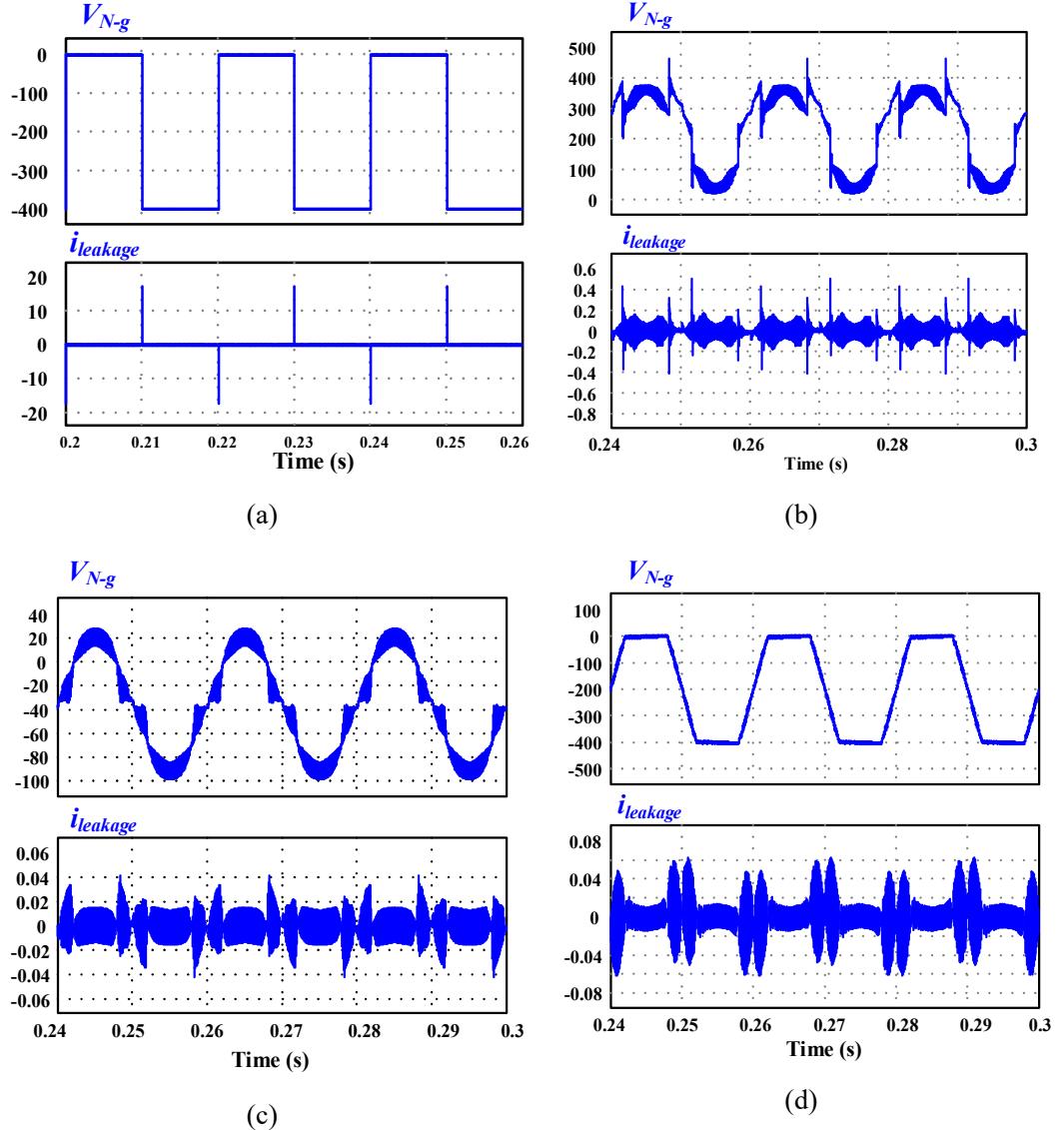

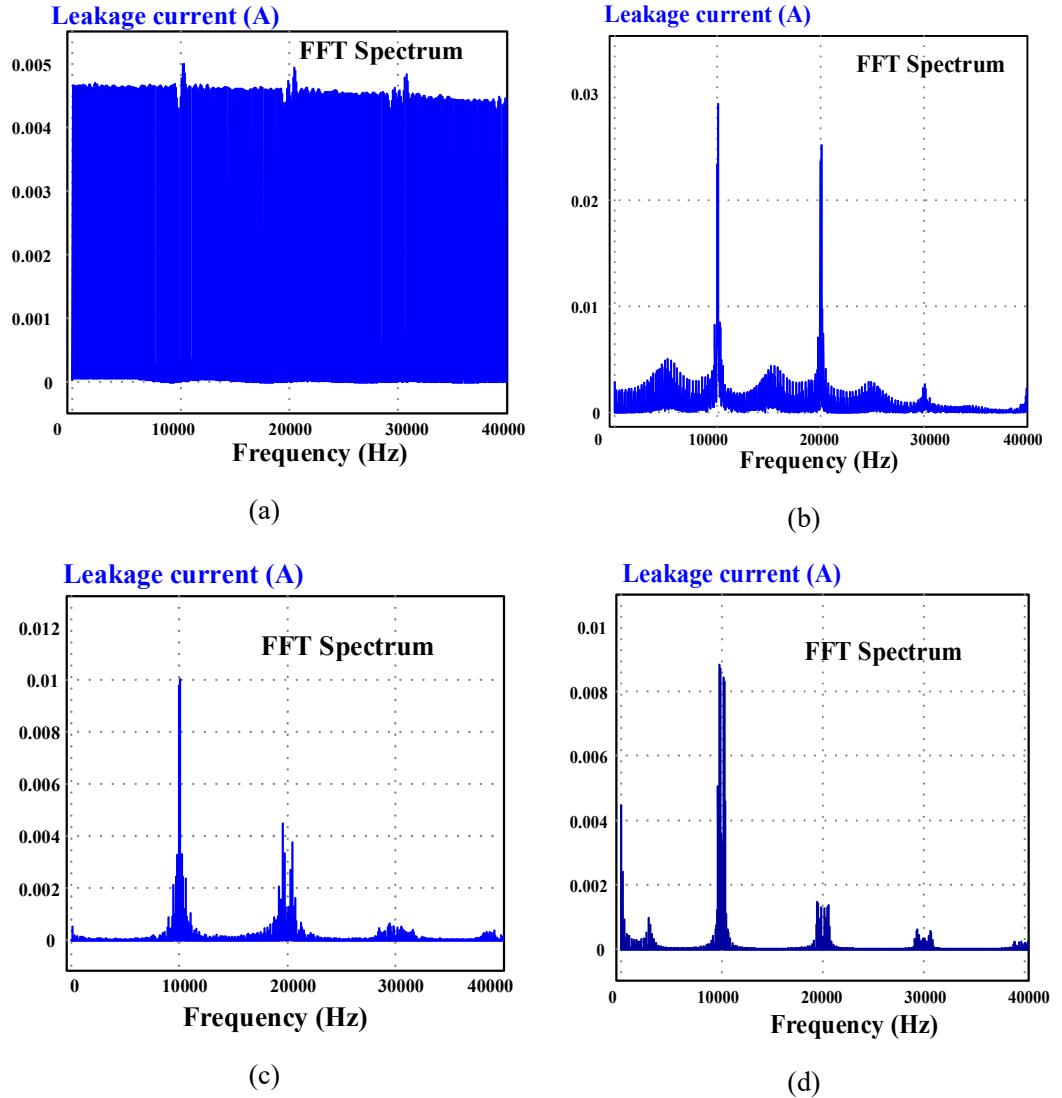

| Fig. 6.20 | Voltage across $C_{PV}$ and leakage current of the; (a) Topologies [9]-[11], (b) Topologies [12]-[13], (c) Topology [14] and (d) Proposed topology.                                                                                                                 | 161 |

| Fig. 6.21 | FFT spectrum of the; (a) Topologies [9]-[11], (b) Topologies [12]-[13] (c) Topology [14] and (d) Proposed topology.                                                                                                                                                 | 162 |

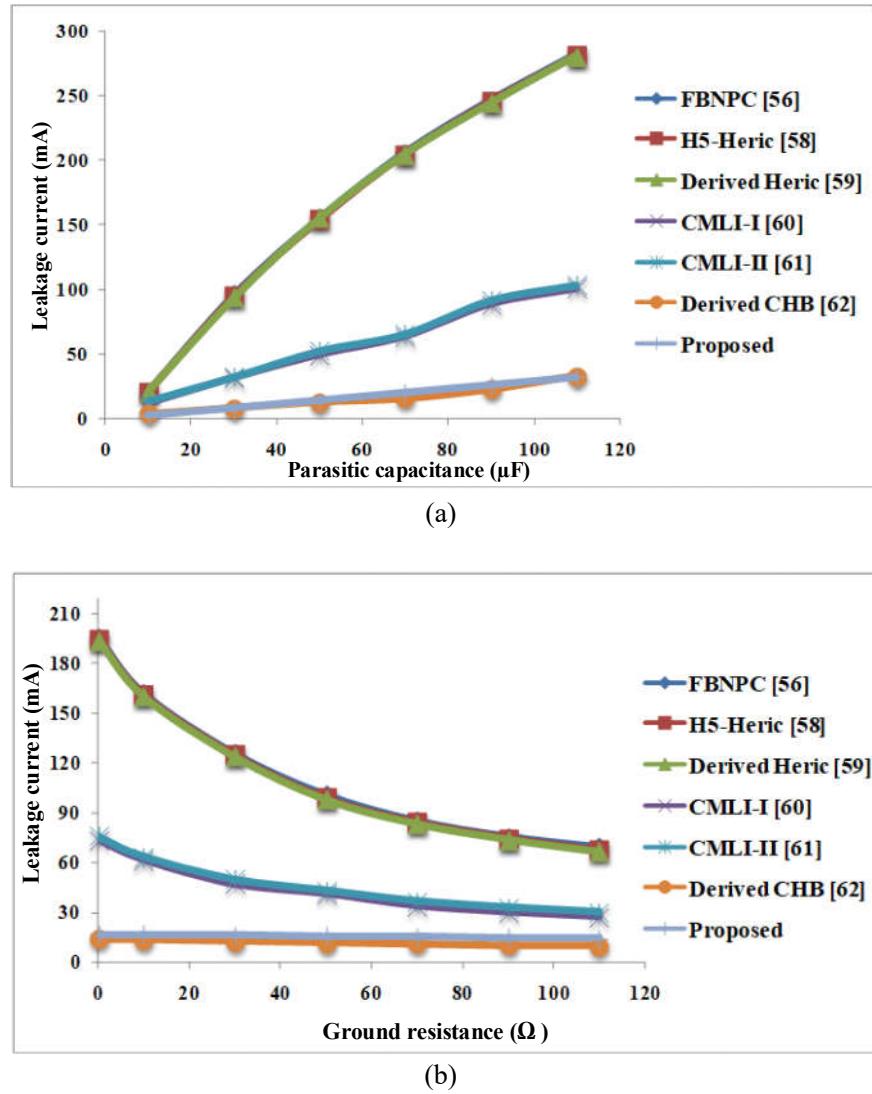

| Fig. 6.22 | (a) Parasitic capacitances versus leakage current curve, (b) Ground resistance versus leakage current.                                                                                                                                                              | 163 |

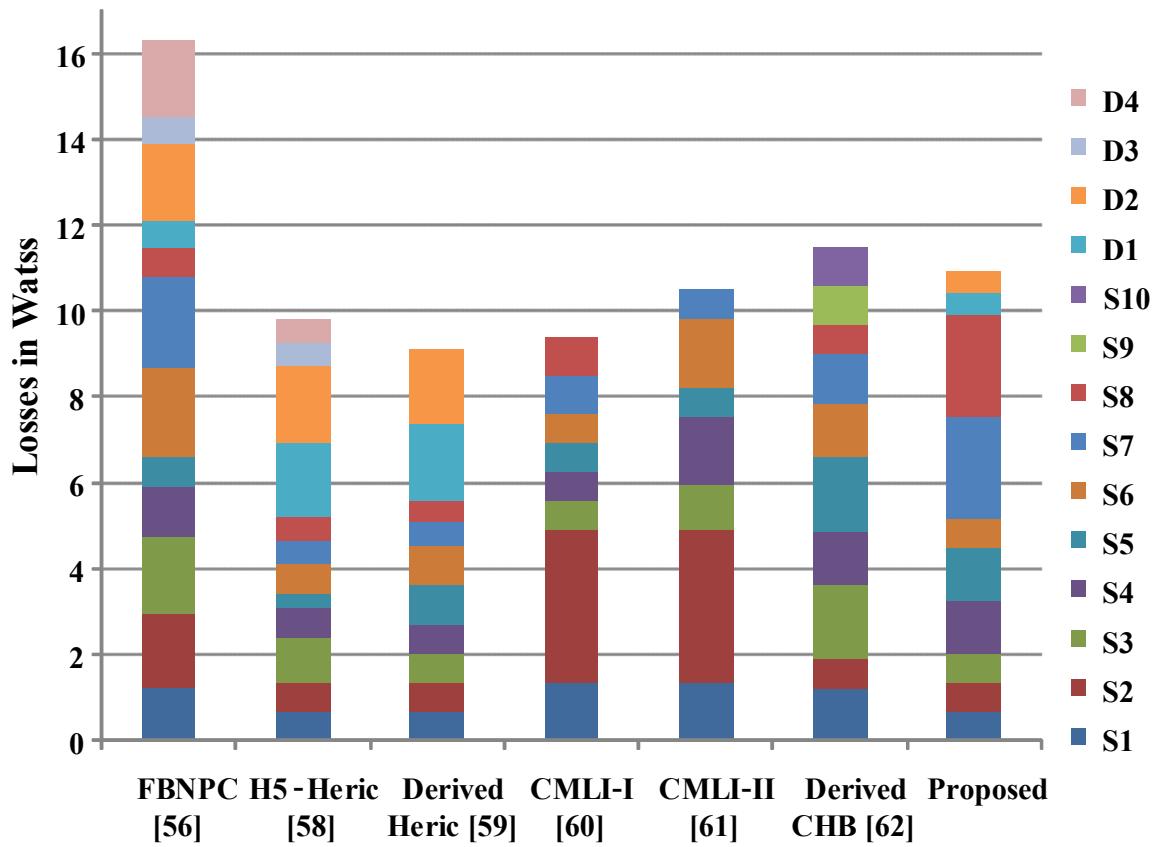

| Fig. 6.23 | Loss distribution of the various TLIs with proposed topology.                                                                                                                                                                                                       | 166 |

## LIST OF TABLES

---

|           |                                                                                                                |     |

|-----------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 1.1 | Overview of grid-connected PVPGS.                                                                              | 5   |

| Table 1.2 | IEEE 1547 THD standard for grid-connected PVPGS.                                                               | 15  |

| Table 1.3 | Table. 1.3 BIS / IEC standards for grid-connected PV inverters in India                                        | 15  |

| Table 2.1 | Comparative assessment of single-stage TLI topologies.                                                         | 29  |

| Table 2.2 | Comparative assessment of single-stage five-level TLI topologies.                                              | 40  |

| Table 2.3 | Comparative assessment of two-stage MLI topologies                                                             | 47  |

| Table 3.1 | Switching logic and CMV calculations of BDC based H5, HERIC, H6, and H-B TLI topologies                        | 65  |

| Table 3.2 | System parameters                                                                                              | 67  |

| Table 3.3 | Performance evaluation of the traditional and BDC based topologies                                             | 78  |

| Table 4.1 | Switching state of the asymmetrical seven-level inverter                                                       | 89  |

| Table 4.2 | System parameters                                                                                              | 99  |