**INVESTIGATIONS ON TOPOLOGIES AND CONTROL

ALGORITHMS OF DSTATCOM TO COMPENSATE

CURRENT RELATED POWER QUALITY ISSUES**

*Thesis submitted in partial fulfilment of the

requirements for the award of the

degree of*

**DOCTOR OF PHILOSOPHY**

*in*

**ELECTRICAL ENGINEERING**

*by*

**Alladi Pranay Kumar

(Roll No. 716011)**

Supervisor

**Dr. G. Siva Kumar**

Assistant Professor

Co-Supervisor

**Dr. D. Sreenivasarao**

Assistant Professor

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

WARANGAL – 506 004, TELANGANA STATE, INDIA**

**JULY-2020**

## **APPROVAL SHEET**

This Thesis entitled "**“Investigations on topologies and control algorithms of DSTATCOM to compensate current related power quality issues”** by **Mr. Alladi Pranay Kumar (Roll No. 716011)** is approved for the degree of Doctor of Philosophy.

### **Examiners**

|                          |                             |

|--------------------------|-----------------------------|

| Supervisor               | Co-Supervisor               |

| <b>Dr. G. Siva Kumar</b> | <b>Dr. D. Sreenivasarao</b> |

| Assistant Professor      | Assistant Professor         |

| EED, NIT WARANGAL        | EED, NIT WARANGAL           |

### **Chairman**

**Dr. S. Srinivasa Rao**

Professor & Head,

EED, NIT Warangal

Date: \_\_\_\_\_

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL

WARANGAL – 506 004**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**CERTIFICATE**

This is to certify that the thesis entitled "**Investigations on topologies and control algorithms of DSTATCOM to compensate current related power quality issues**", which is being submitted by **Mr. Alladi Pranay Kumar (Roll No. 716011)**, is a bona fide work submitted to National Institute of Technology Warangal in partial fulfilment of the requirement for the award of the degree of **Doctor of Philosophy** in Department of Electrical Engineering. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

**Dr. G. Siva Kumar**

(Supervisor)

Assistant Professor

Department of Electrical Engineering

National Institute of Technology Warangal

Warangal – 506004

**Dr. D. Sreenivasarao**

(Co-Supervisor)

Assistant Professor

Department of Electrical Engineering

National Institute of Technology Warangal

Warangal – 506004

Date:

Place: Warangal

## **DECLARATION**

This is to certify that the work presented in the thesis entitled "**Investigations on topologies and control algorithms of DSTATCOM to compensate current related power quality issues**" is a bona fide work done by me under the supervision of **Dr. G. Siva Kumar, and Dr. D. Sreenivasarao**, Assistant Professors, Department of Electrical Engineering, National Institute of Technology Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/date/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Alladi Pranay Kumar**

(Roll No: 716011)

Date:

Place: Warangal

## ACKNOWLEDGEMENT

I would like to express my deep gratitude towards **Dr. G. Siva Kumar** Assistant Professor and **Dr. D. Sreenivasarao** Assistant Professor, Electrical Engineering Department for their excellent guidance, support and constant reviewing throughout the course of research work. The interactions with them ensured right direction of this work and helped in completion of the thesis.

I am also thankful to **Prof. S Srinivasa Rao**, **Prof. N. Vishwanathan** and **Prof. V. T. Somasekhar**, Heads of the Electrical Department during the period of my research. I am sincerely grateful to **Prof. D V S S Siva Sarma**, **Dr. T Vinay Kumar** and **Prof. Sonawane Shirish Hari** who assessed my work and encouraged me as the members of my doctoral scrutiny committee. I would also like to thank **Dr. M. Raja Vishwanathan**, Assistant Professor, Department of Humanities & Social Science for the proof reading of thesis.

I wish to express my sincere thanks to **Prof. N.V. Ramana Rao**, Director, NIT Warangal for his official support and encouragement.

My sincere thanks to my colleagues especially Dr. Hareesh, Dr. Hari Priya, Dr. B. Anil Kumar , Dr. Ramanjaneya Reddy, Dr. Kiran, Dr. Vishnu Prasad, Mr. M Santhosh, Dr. Venu Sonti, Dr. Ratna Rahul, Dr. Kasi Rama Krishna Reddy, Dr. K V Praveen, Dr. Phani, Mr. G Eshwar Gowd, Dr. Durga Hari Kiran, Dr. Venkata Ramana, Ms Mounika, Mr. Ram Kumar, Mr. B Gurappa, Mr. Madu Babu, Mr. Rambabu, Mr. Bhaskar, Mr. Hema Sundar, Mr. M Sudhakar, Mr. Murali, Mr. Chandra Sai, Ms Madhuri, Mr. Chinna K, for answering all the questions and the support given by them whenever I was in need.

My sincere thanks to my dearest friends especially, Tinku, Mani, Anvesh, Avinash, Bharath, Chinni, Pradeep, Mahipal, Rajeev, Suma Rajeev, Divyateja, Vivek, Raviteja, Bharath, Durga Praveen, Mani Kiran, Ratna Raju, P Naresh, B Naresh, Ravi Chandra, Rajesh, Sai Tarun, Sudheer, Soujanya, Jyothi, Shravani, Ravi, Chittibabu, who encouraged me to choose this profession.

I also appreciate the encouragement from teaching, non-teaching members, and fraternity of Department of Electrical Engineering of NIT Warangal.

I also acknowledge my sincere gratitude to the Ministry of Human Resources Development (MHRD), Government of India for their financial support to carry out this research.

My heartily gratitude to my grand parents Rama Laxmi & Ballingam who are my inspiration, my parents Shri. Alladi Siddaramulu & Smt. Alladi Padma, my brother A Praveen Kumar, my aunt Smt. Lalitha finally my grand parents Balaveraiah & Kannamma.

Above all, I thank the almighty for giving me this learning opportunity and blessing me to finish my work successfully.

**Alladi Pranay Kumar**

## ABSTRACT

In modern distribution systems, the major power consumption has been in reactive and non-linear loads, such as motor drives, fans, pumps, and power electronic equipment. The consumption of excessive reactive power results into poor power factor at supply mains, poor voltage regulation, increased feeder losses and reduced the active power flow capability of the distribution system. Moreover, situation worsens in the presence of non-linear loads and raises power quality issues in distribution system. The operation of non-linear loads in distribution systems results into harmonic current burden and interrupts the normal operation of electrical and electronic equipment that are connected to the distribution system. At the same time, the power electronic equipment are typically designed with sophisticated microprocessor-based controllers which are quite sensitive to deviations in the voltage waveform. In recent years, with the advent of sophisticated electronic equipment, the electric power quality (PQ) has become an issue of concern and extensive research is being held to improve the power quality.

In the early days, synchronous condenser, mechanically switched capacitors and inductors have been used for reactive power compensation. However, due to their slow response and mechanical wear and tear, use of these devices is limited for the applications where fast compensation is not desirable. With the advent of first generation flexible alternating current transmission system (FACTS) devices, thyristor-controlled static var compensators (SVCs) made a significant advances in reactive power compensation. These devices are fast in operation and smooth control of reactive power compensation can be obtained. These SVC schemes are attractive due to their theoretical simplicity, however, practical disadvantages such as requirement of large inductor and capacitor banks, dependency of the reactive power compensation on operating voltage, hindered their popularity. With the significant progress of self-commutated semiconductor devices, attention has been focused on second generation FACTS devices which are based on voltage source and current source inverters. Among them, static synchronous compensator (STATCOM) has attracted the attention of researchers and power industries

for reactive power compensation and voltage regulation in transmission systems.

On the other hand, in the distribution system, harmonic regulation guidelines such as IEEE 519-1992 and IEC 61000 are applied to limit the current and voltage harmonics levels. To meet these requirements, the harmonics must be mitigated. Therefore, to eliminate harmonics and compensate reactive power, the FACTS technology can be extended further to distribution system. These devices solve power quality problems in the distribution system and they are popularly known as custom power devices (CPDs). The family of CPDs includes distribution static compensator (DSTATCOM), dynamic voltage restorer (DVR) and unified power quality conditioner (UPQC). Among them, DSTATCOM is a shunt connected device, which mitigates current related power quality problems, such as reactive power compensation, harmonic elimination, load balancing and neutral current elimination. In this thesis, an attempt has been made to develop and control various DSTATCOM topologies for power quality improvement in three-phase four-wire (3P4W) distribution system.

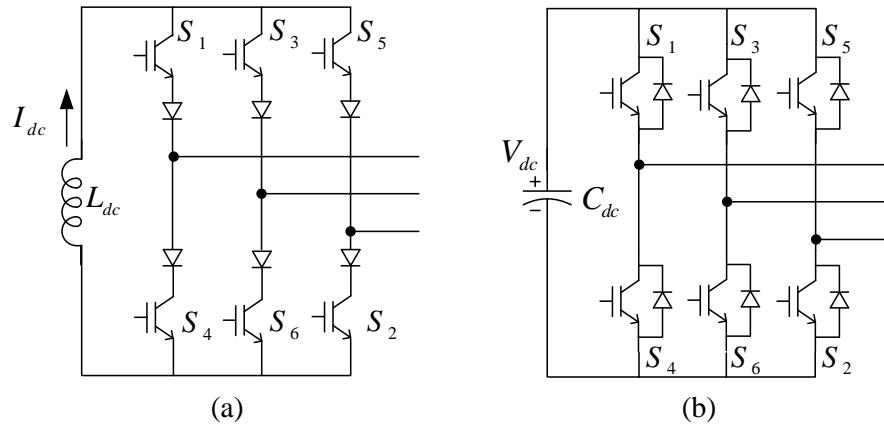

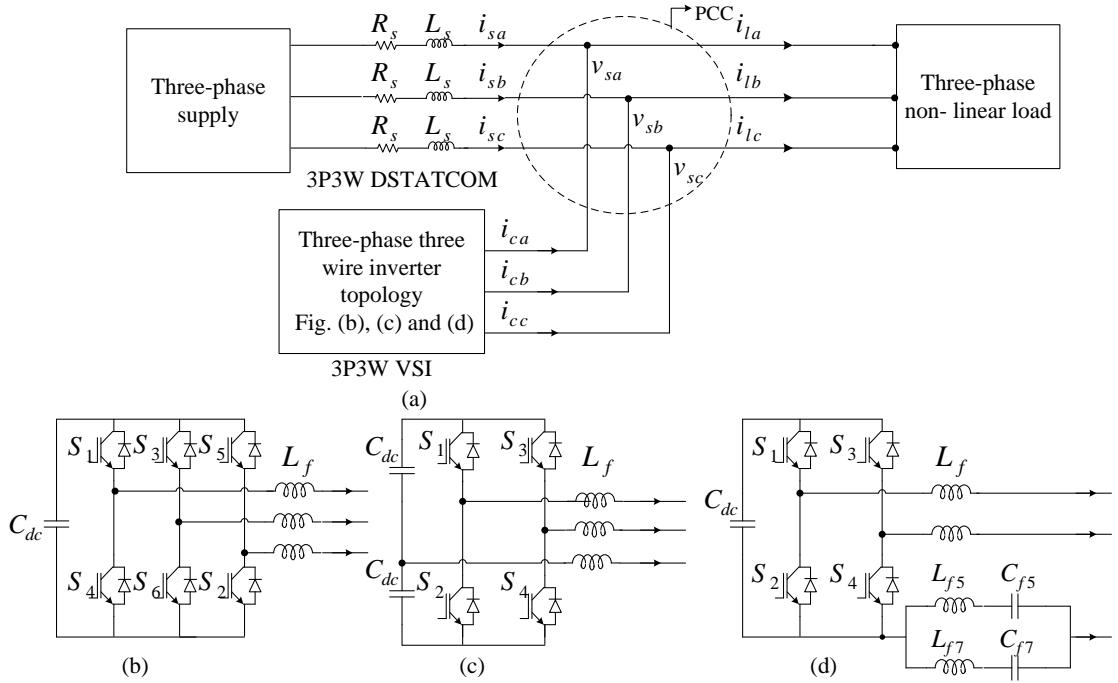

A cost-effective and high performance inverter is a prerequisite for the realization of a DSTATCOM. These inverters can be broadly categorized into two classes, namely, voltage source inverter (VSI) and current source inverter (CSI). In the present work, VSI has been considered as a power circuit for DSTATCOM, due to its higher market penetration and more noticeable development as compared to CSI topologies. The performance of any DSTATCOM topology depends on topology of VSI, reference current extraction technique and controller used to generate the switching pulses.

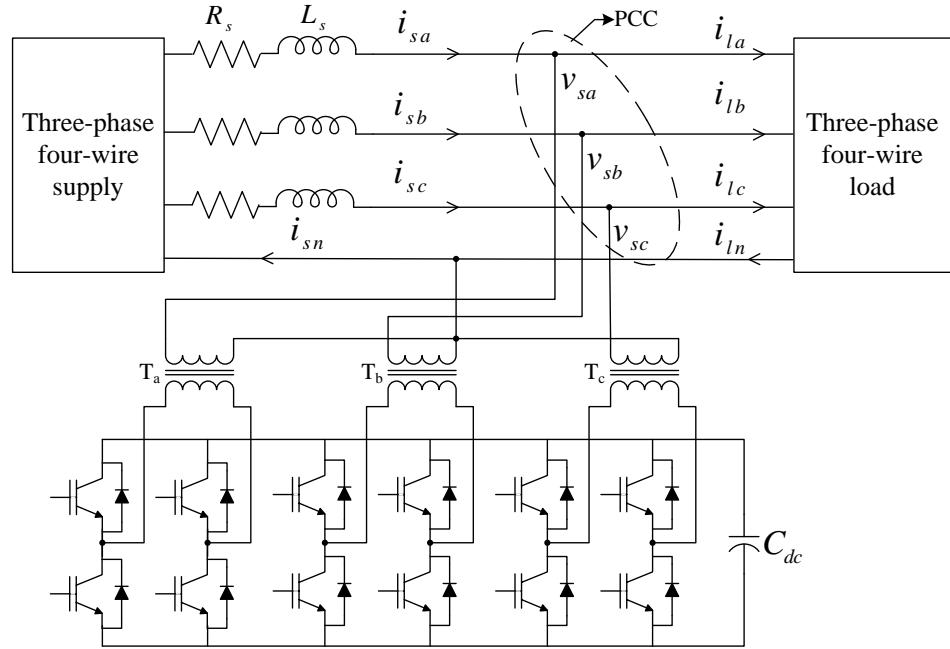

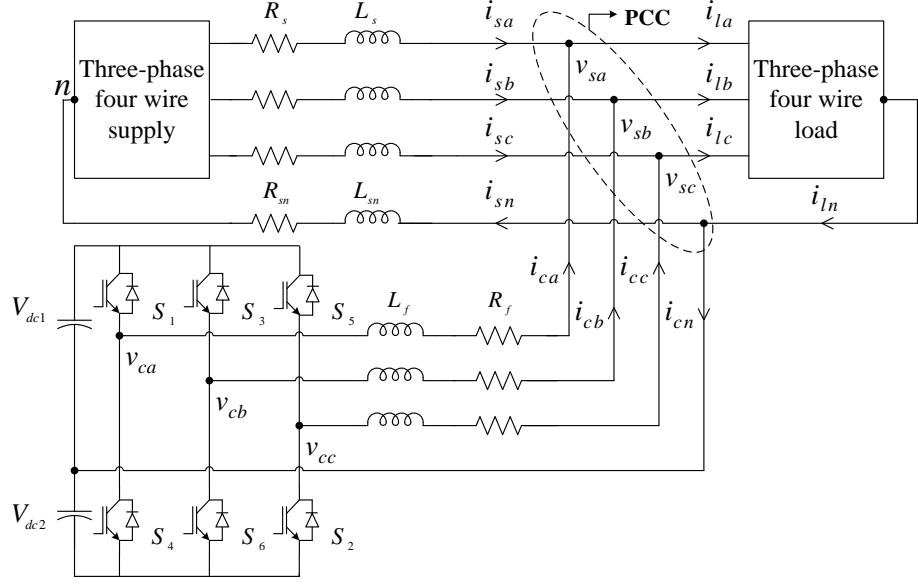

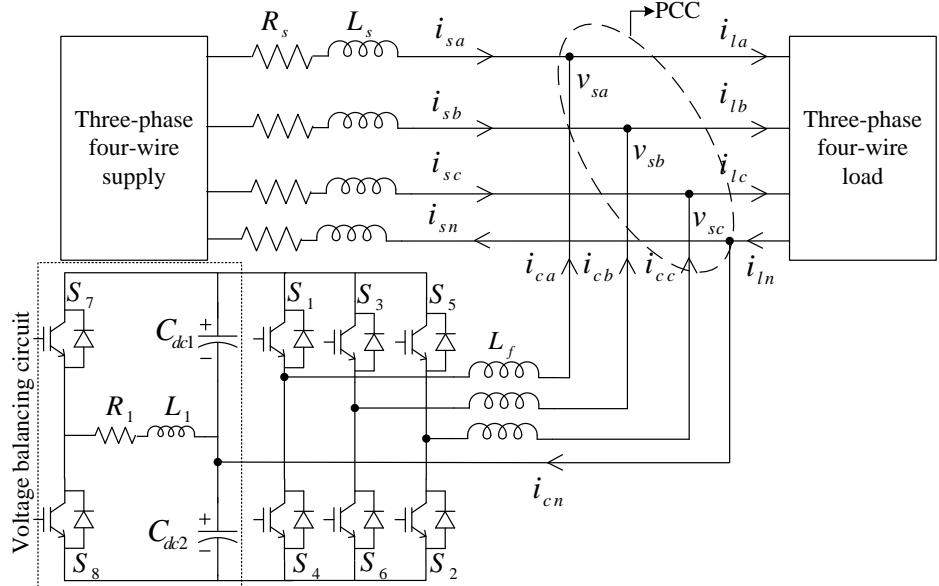

Among the available DSTATCOM topologies, three H-bridge (HB), three leg DSTATCOM, three-phase split-capacitor (TPSC) DSTATCOM and four leg DSTATCOM (FL-DSTATCOM) topologies are treated as traditional topologies. Three single phase H-bridge inverters are used to implement a three HB DSTATCOM, which can be applicable to both three-phase three-wire (3P3W) and 3P4W systems. However, the limitations of this topology are requirement of higher number of switching devices and coupling transformers, which will increase the size and cost of the DSTATCOM. A three leg VSI based DSTATCOM is having lesser number of switching devices and do not require any coupling transformers. However, this topology is not suitable for 3P4W systems. The structure of TPSC topology is same as three leg topology except the number of capacitors in its dc link. The dc link of three leg DSTATCOM consists of only one capacitor

whereas, the dc link of TPSC topology consists of two capacitors. The mid-point of the dc link is connected to the neutral conductor so that it is suitable for both 3P3W and 3P4W systems. The limitation of TPSC topology is, unequal voltage sharing of dc link capacitors during the transient operation of unbalanced and non-linear loads. FL-DSTATCOM require two additional switches compared to three leg and TPSC and it is suitable for both 3P3W and 3P4W systems. The advantages of this topology are better controllability, simple structure, easy control and the absence of capacitor voltage balancing problem unlike TPSC topology.

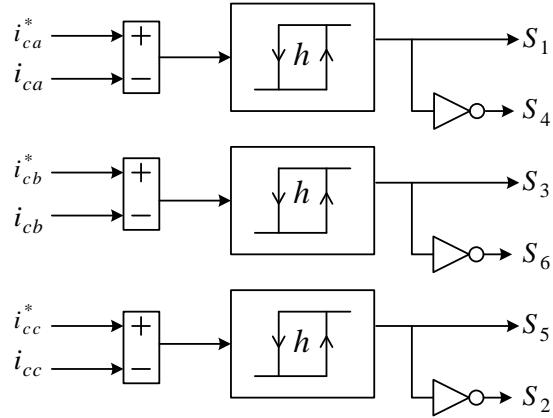

The conventional reference current extraction techniques are, unit template theory (UTT), instantaneous reactive power theory (IRPT), synchronous reference frame theory and instantaneous symmetrical component theory (ISCT). In recent years, model predictive control (MPC) has attracted researchers to replace, conventional pulse width modulation (PWM) and hysteresis controllers due to its versatile nature. The advantages of MPC are, simple addition and treatment of constraints, multi-variable case can be easily addressed, simple structure and good transient and steady state response. In MPC, the difference between the reference and actual value of a variable is considered as a cost function and evaluate the cost function for the available switching states. Among all the states, select a switching state, which minimizes the cost function and apply it for the upcoming instant. The additional constraints are included in the cost function using weighting factor and the weighting factor values are ranging from 0 to  $\infty$ . one of the considerable limitation of MPC is higher switching frequency.

In this thesis, an attempt has been made to overcome the capacitor voltage balancing problem in TPSC topology, by including an additional constraint in the cost function along with current control. Similarly, The higher switching frequency limitation of MPC is also reduced by including an additional constraint in the cost function. These two additional constraints are included using weighting factors and selection of weighting factor values has done using VlseKriterijumska Optimizacija I Kompromisno Re-senje (VIKOR) method.

To reduce the higher neutral leg switching frequency of FL-DSTATCOM, an additional constraint is included in the cost function using weighting factor and the Technique for Order Preference by Similarity to the Ideal Solution (TOPSIS) is applied to simplify the weighting factor tuning process. The reduction in neutral leg switching frequency will

reduce the phase leg switching frequency as they are dependent on each other.

Conventional MPC do not use any modulating signal, therefore it is a variable switching frequency control technique. This variable switching frequency further leads to uneven switching stress and also makes the filter design little complex. An attempt has been made in this thesis, to overcome the limitation and operate the VSI at constant switching frequency by using the concept of three dimensional space vector modulation (3DSVM).

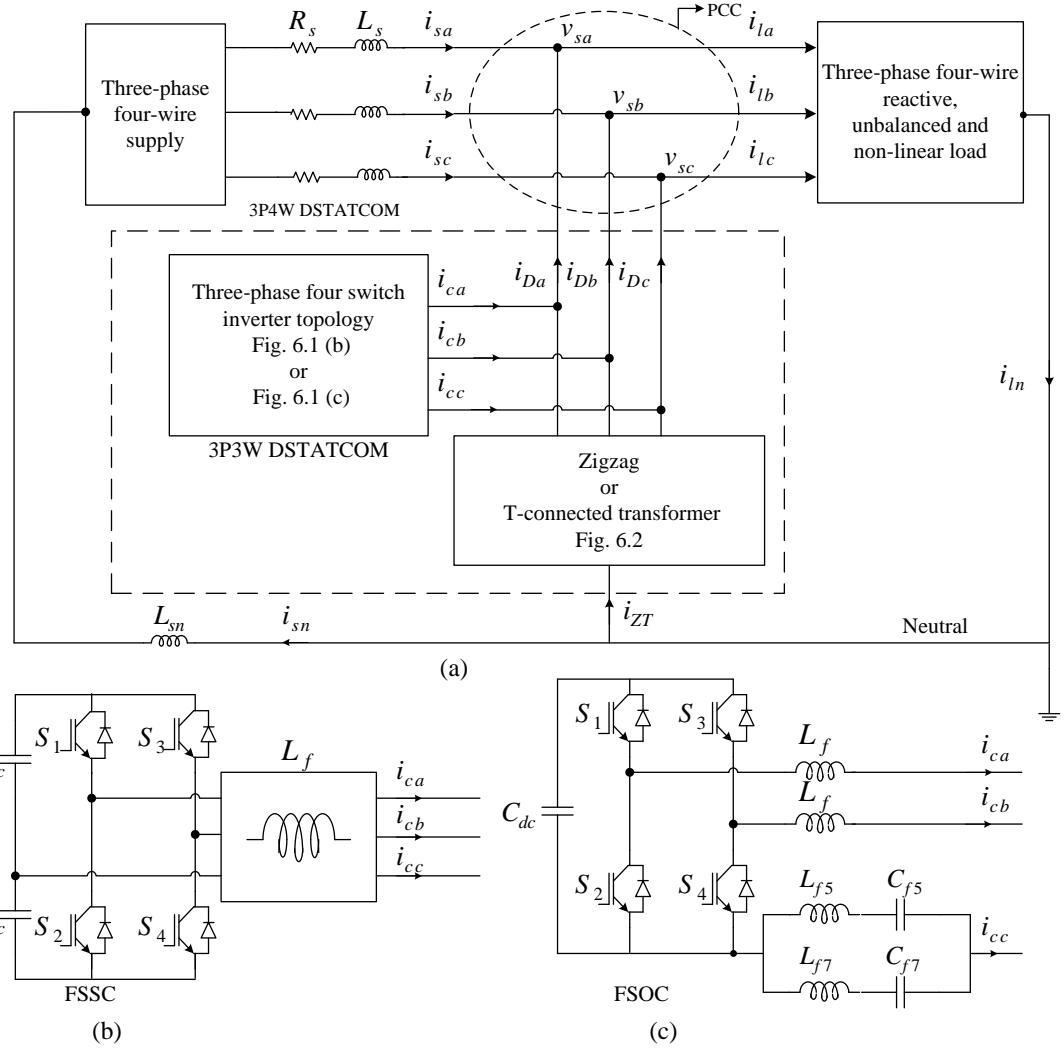

Four switch VSI based DSTATCOM topologies are cost effective solution compared to TPSC and FL-DSTATCOM topologies. However, the absence of fourth leg in these two topologies, restrict them for 3P4W systems. Therefore, in the present work, four different DSTATCOM topologies are formed by combining, two four switch VSI topologies with different transformer arrangements such as zigzag and T-connected transformer. This combination will reduce the cost of the DSTATCOM as well as compensate the current related power quality issues along with neutral current compensation.

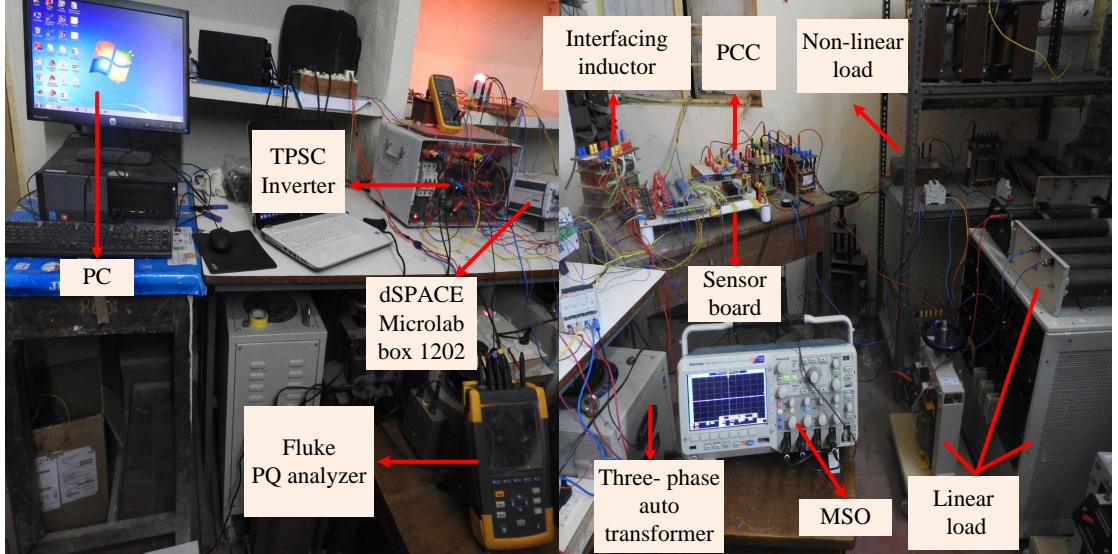

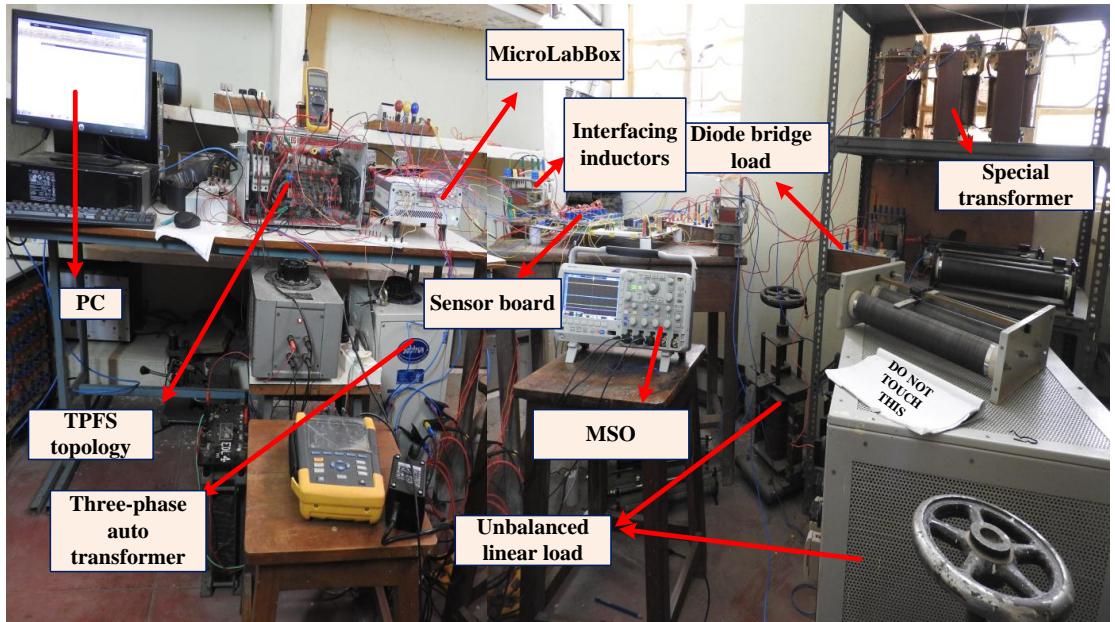

The control algorithms have been implemented on dSPACE MicroLabBox 1202 R&D controller, the topologies are implemented using an IGBT based inverter and LEM made voltage and current transducers are used to sense the voltage and current signals. The developed prototypes have been studied for reactive power compensation, harmonic elimination and neutral current compensation with different loading and utility conditions.

# TABLE OF CONTENTS

|                                                                         |              |

|-------------------------------------------------------------------------|--------------|

| <b>ACKNOWLEDGEMENT</b>                                                  | <b>i</b>     |

| <b>ABSTRACT</b>                                                         | <b>iii</b>   |

| <b>LIST OF TABLES</b>                                                   | <b>xi</b>    |

| <b>LIST OF FIGURES</b>                                                  | <b>xii</b>   |

| <b>ABBREVIATIONS</b>                                                    | <b>xvi</b>   |

| <b>NOTATIONS</b>                                                        | <b>xviii</b> |

| <b>1 Introduction</b>                                                   | <b>1</b>     |

| 1.1 Classification of power quality problems and their causes . . . . . | 1            |

| 1.2 Effects of power quality problems on end users . . . . .            | 4            |

| 1.2.1 Reactive power burden . . . . .                                   | 4            |

| 1.2.2 Influence of harmonic currents . . . . .                          | 5            |

| 1.2.3 Influence of excess neutral current . . . . .                     | 6            |

| 1.3 Power quality standards . . . . .                                   | 6            |

| 1.4 Solutions to power quality issues . . . . .                         | 7            |

| 1.4.1 Passive power filters . . . . .                                   | 8            |

| 1.4.2 Active power filters . . . . .                                    | 9            |

| 1.4.3 Hybrid power filters . . . . .                                    | 11           |

| 1.5 Objectives . . . . .                                                | 11           |

| 1.6 Organization of the thesis . . . . .                                | 13           |

| <b>2 Configurations and Control Algorithms of DSTATCOM</b>              | <b>15</b>    |

| 2.1 Classification of DSTATCOM configurations . . . . .                 | 15           |

| 2.1.1 Converter based classification . . . . .                          | 15           |

| 2.1.2 Supply based classification . . . . .                             | 16           |

| 2.2 Control algorithms to extract reference currents . . . . .          | 22           |

|          |                                                                                                                                              |           |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

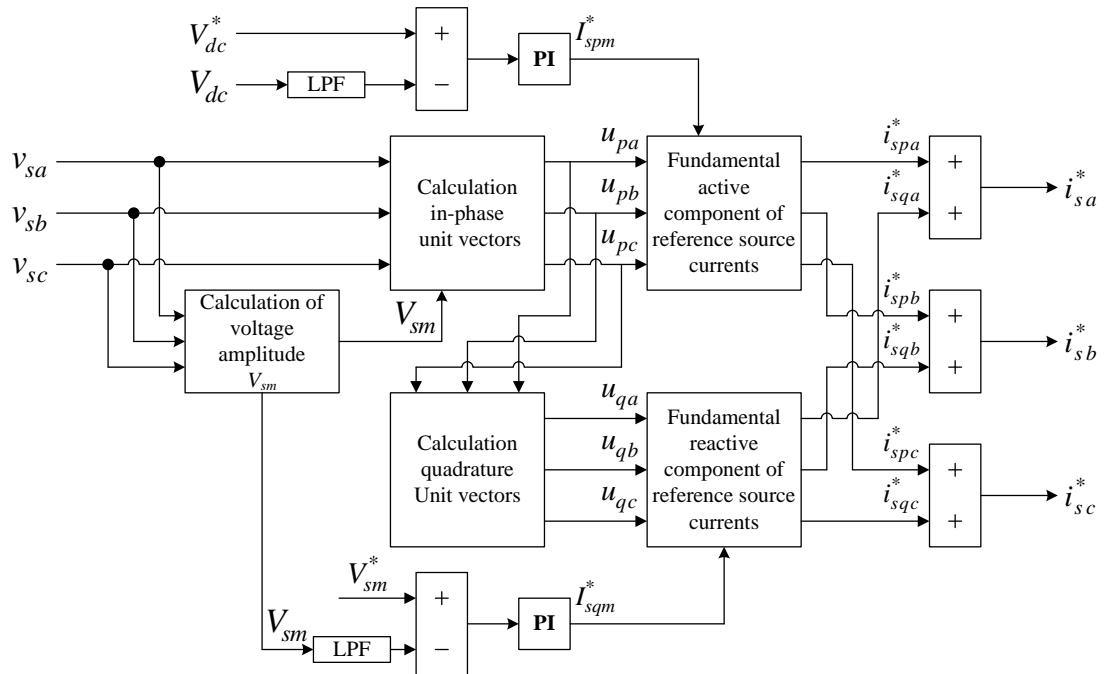

| 2.2.1    | Unit template technique (UTT) . . . . .                                                                                                      | 23        |

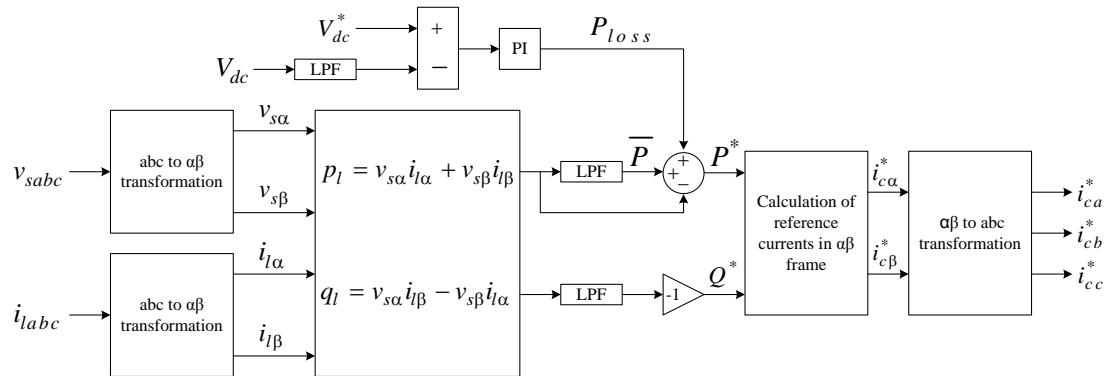

| 2.2.2    | Instantaneous reactive power theory (IRPT) . . . . .                                                                                         | 25        |

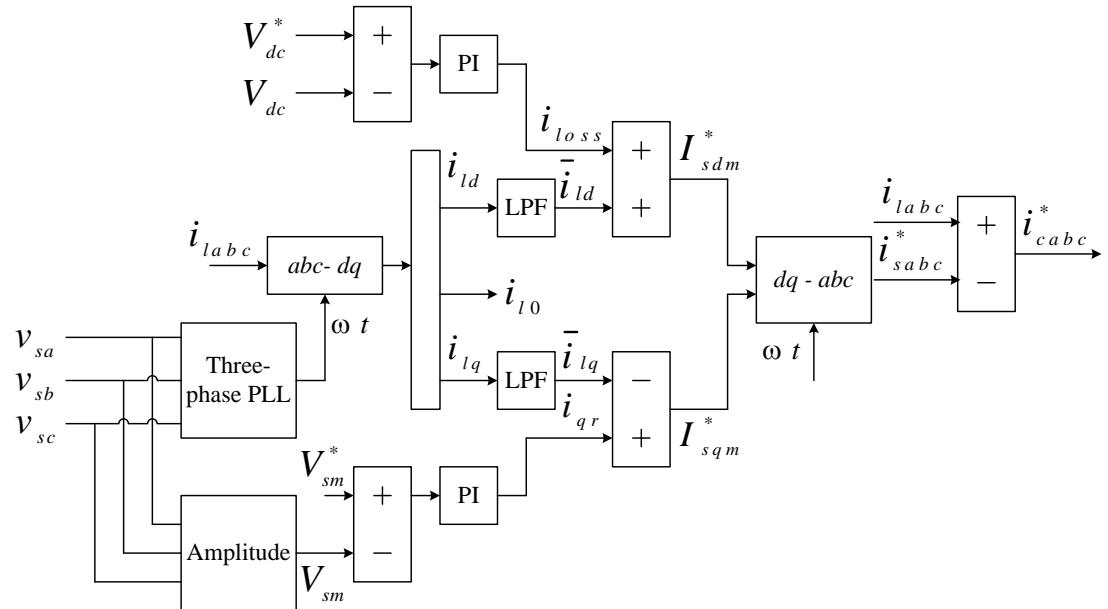

| 2.2.3    | Synchronous reference frame (SRF) theory . . . . .                                                                                           | 27        |

| 2.2.4    | Instantaneous symmetrical component theory (ISCT) . . . . .                                                                                  | 29        |

| 2.3      | Controllers to generate switching pulses . . . . .                                                                                           | 32        |

| 2.3.1    | Pulse width modulation (PWM) controller . . . . .                                                                                            | 32        |

| 2.3.2    | Hysteresis controller . . . . .                                                                                                              | 33        |

| 2.4      | Model predictive control (MPC) . . . . .                                                                                                     | 34        |

| 2.5      | Design of DSTATCOM parameters . . . . .                                                                                                      | 35        |

| 2.5.1    | DC-link voltage ( $V_{dc}$ ) . . . . .                                                                                                       | 35        |

| 2.5.2    | DC-link capacitor ( $C_{dc}$ ) . . . . .                                                                                                     | 36        |

| 2.5.3    | Interfacing inductor ( $L_f$ ) . . . . .                                                                                                     | 36        |

| 2.6      | Summary . . . . .                                                                                                                            | 38        |

| <b>3</b> | <b>Model Predictive Control of TPSC DSTATCOM with Simplified Weighting Factor Selection Using VIKOR Method for Power Quality Improvement</b> | <b>39</b> |

| 3.1      | Introduction . . . . .                                                                                                                       | 39        |

| 3.2      | Proposed MPC with VIKOR method . . . . .                                                                                                     | 40        |

| 3.2.1    | Reference current extraction using conductance factor method                                                                                 | 43        |

| 3.2.2    | Predictive model of TPSC DSTATCOM . . . . .                                                                                                  | 46        |

| 3.2.3    | Lagrange's extrapolation and cost function formation . . . . .                                                                               | 48        |

| 3.2.4    | Application of VIKOR method for selecting optimal switching state . . . . .                                                                  | 50        |

| 3.3      | Simulation studies . . . . .                                                                                                                 | 51        |

| 3.3.1    | Performance during compensation of non-linear and unbalanced loads . . . . .                                                                 | 52        |

| 3.3.2    | Performance with higher THD loads . . . . .                                                                                                  | 56        |

| 3.4      | Experimental studies . . . . .                                                                                                               | 58        |

| 3.4.1    | Simulation results for experimental parameters . . . . .                                                                                     | 65        |

| 3.5      | Summary . . . . .                                                                                                                            | 66        |

| <b>4</b> | <b>Model Predictive Control with TOPSIS Method for Four Leg DSTATCOM to Improve Power Quality and Reduce Switching Frequency</b>             | <b>67</b> |

| 4.1      | Introduction . . . . .                                                                                                                       | 67        |

|          |                                                                                                                                             |            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.2      | Proposed MPC with TOPSIS for FL-DSTATCOM . . . . .                                                                                          | 69         |

| 4.2.1    | Unit vector estimation using state observers from unbalanced and distorted supply voltages . . . . .                                        | 70         |

| 4.2.2    | Reference current extraction using conductance factor . . . . .                                                                             | 73         |

| 4.2.3    | Predictive model of FL-DSTATCOM and cost function formation . . . . .                                                                       | 77         |

| 4.2.4    | Weighting factor simplification and cost function minimization using TOPSIS based MPC . . . . .                                             | 79         |

| 4.3      | Simulation studies . . . . .                                                                                                                | 81         |

| 4.3.1    | Performance during case-1 . . . . .                                                                                                         | 81         |

| 4.3.2    | Performance during case-2 . . . . .                                                                                                         | 84         |

| 4.4      | Experimental studies . . . . .                                                                                                              | 86         |

| 4.5      | Summary . . . . .                                                                                                                           | 92         |

| <b>5</b> | <b>Model Predictive Control with Constant Switching Frequency for Four Leg DSTATCOM Using Three Dimensional Space Vector Modulation</b>     | <b>93</b>  |

| 5.1      | Introduction . . . . .                                                                                                                      | 93         |

| 5.2      | MPC algorithm with constant switching frequency . . . . .                                                                                   | 94         |

| 5.2.1    | Predictive model of FL-DSTATCOM . . . . .                                                                                                   | 95         |

| 5.2.2    | MPC with 3DSVM to achieve constant switching frequency                                                                                      | 98         |

| 5.3      | Simulation studies . . . . .                                                                                                                | 102        |

| 5.3.1    | Comparison of proposed method with conventional MPC and MPC with reduced switching frequency . . . . .                                      | 106        |

| 5.4      | Experimental studies . . . . .                                                                                                              | 106        |

| 5.5      | Summary . . . . .                                                                                                                           | 110        |

| <b>6</b> | <b>Three-Phase Four-Switch DSTATCOM Topologies with Special Transformers for Neutral Current Compensation and Power Quality Improvement</b> | <b>111</b> |

| 6.1      | Introduction . . . . .                                                                                                                      | 111        |

| 6.2      | Configuration of TPFS topologies with special transformers . . . . .                                                                        | 113        |

| 6.2.1    | FSSC topology . . . . .                                                                                                                     | 114        |

| 6.2.2    | FSOC topology . . . . .                                                                                                                     | 115        |

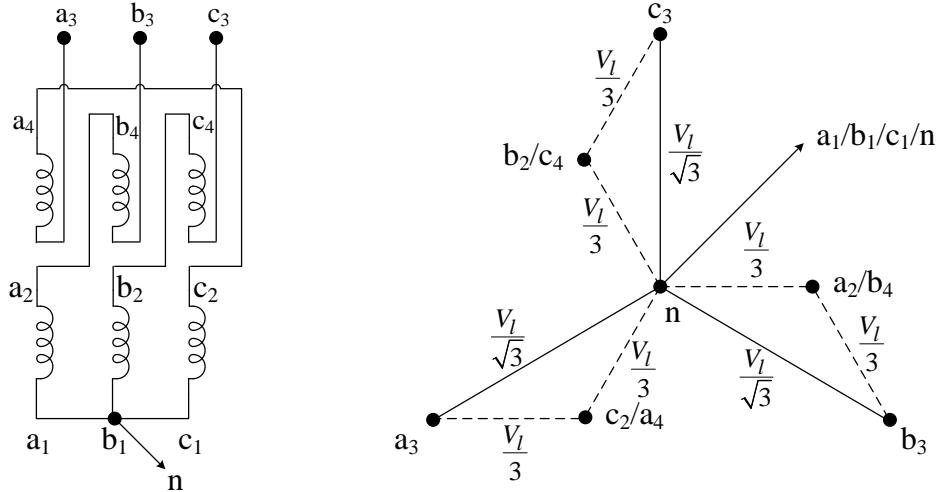

| 6.2.3    | Zigzag transformer . . . . .                                                                                                                | 115        |

| 6.2.4    | T-connected transformer . . . . .                                                                                                           | 116        |

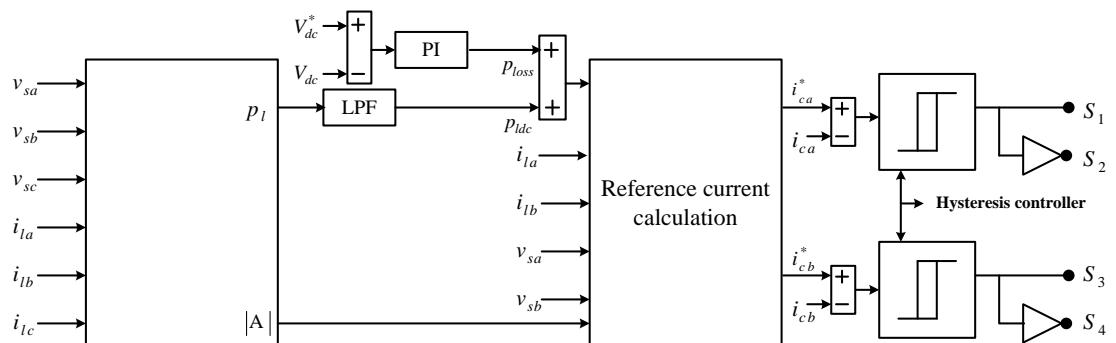

| 6.3      | Instantaneous symmetrical component theory (ISCT) . . . . .                                                                                 | 117        |

|                   |                                                                          |            |

|-------------------|--------------------------------------------------------------------------|------------|

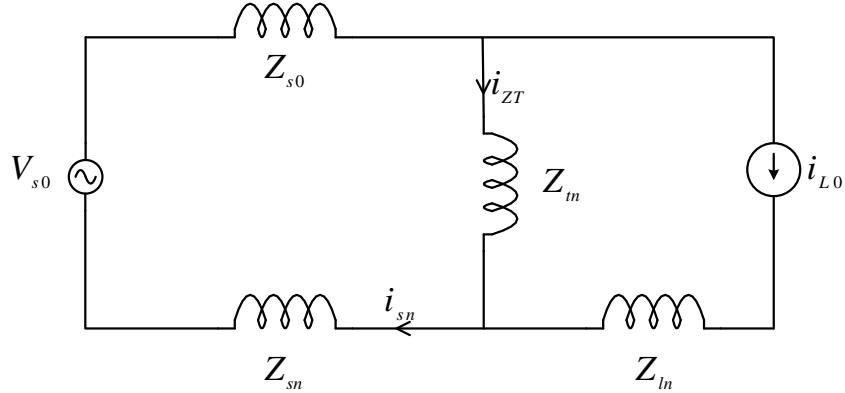

| 6.4               | Neutral current compensation . . . . .                                   | 118        |

| 6.5               | Simulation studies . . . . .                                             | 119        |

| 6.5.1             | Performance of FSOC with zigzag transformer . . . . .                    | 120        |

| 6.5.2             | Performance of FSOC with T-connected transformer . . . . .               | 121        |

| 6.5.3             | Performance of FSSC with zigzag transformer . . . . .                    | 122        |

| 6.5.4             | Performance of FSSC with T-connected transformer . . . . .               | 123        |

| 6.5.5             | Comparison of proposed topologies . . . . .                              | 124        |

| 6.6               | Experimental studies . . . . .                                           | 128        |

| 6.6.1             | Performance of FSOC inverter topology with special transformer           | 128        |

| 6.6.2             | Performance of FSSC inverter topology with special transformer . . . . . | 129        |

| 6.7               | Summary . . . . .                                                        | 131        |

| <b>7</b>          | <b>Conclusions and Future Scope of Research</b>                          | <b>132</b> |

| 7.1               | Conclusions . . . . .                                                    | 132        |

| 7.2               | Future scope of research . . . . .                                       | 134        |

| <b>A</b>          | <b>IMPORTANT DERIVATIONS</b>                                             | <b>136</b> |

| A.1               | Derivation of In-Phase and Quadrature Unit Vectors . . . . .             | 136        |

| A.2               | Derivation of Lagrange's Second Order Extrapolation . . . . .            | 137        |

| <b>REFERENCES</b> |                                                                          | <b>138</b> |

## LIST OF TABLES

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| 2.1 Comparison between three-phase DSTATCOM topologies . . . . .               | 21  |

| 3.1 Switching states with respective voltages of TPSC DSTATCOM . . . . .       | 47  |

| 3.2 <b>Selection of optimal switching state using <math>Q</math></b> . . . . . | 51  |

| 3.3 Simulation parameters . . . . .                                            | 52  |

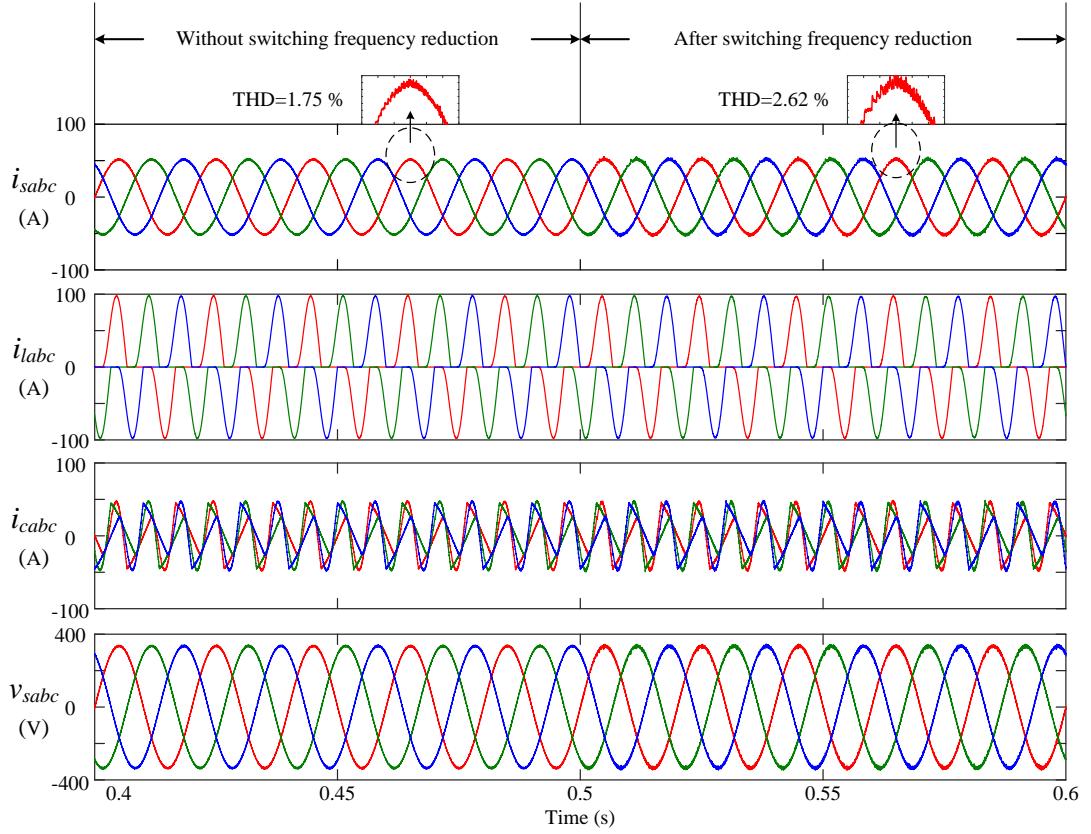

| 3.4 Comparison of THD and switching frequency . . . . .                        | 56  |

| 3.5 THD and switching frequency comparison for loads with higher THD           | 58  |

| 3.6 Experimental parameters . . . . .                                          | 59  |

| 3.7 THD and switching frequency during experimental studies . . . . .          | 62  |

| 4.1 Pole voltages and phase voltages of FL-DSTATCOM . . . . .                  | 78  |

| 4.2 Simulation parameters . . . . .                                            | 82  |

| 4.3 Parameters without and with additional constraint during case-1 . .        | 84  |

| 4.4 Parameters without and with additional constraint during case-2 . .        | 85  |

| 4.5 Experimental parameters . . . . .                                          | 87  |

| 5.1 Switching states and voltage vectors of FL-DSTATCOM . . . . .              | 97  |

| 5.2 Tetrahedrons and their associated voltage vectors of dodecahedron .        | 99  |

| 5.3 Example for tetrahedron selection using 3DSVM based MPC . . . . .          | 101 |

| 5.4 Simulation parameters . . . . .                                            | 102 |

| 5.5 THDs of load and source currents for load-1 and load-2 . . . . .           | 105 |

| 5.6 Comparison of proposed method with conventional methods . . . . .          | 107 |

| 5.7 Experimental parameters . . . . .                                          | 107 |

| 6.1 Simulation parameters . . . . .                                            | 120 |

| 6.2 Comparison of proposed topologies with conventional topologies . .         | 125 |

| 6.3 THD comparison of proposed four configurations . . . . .                   | 127 |

| 6.4 Comparison in terms of various components . . . . .                        | 127 |

| 6.5 Cost comparison of conventional and proposed topologies . . . . .          | 127 |

| 6.6 Experimental parameters . . . . .                                          | 128 |

## LIST OF FIGURES

|      |                                                                                                                                  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

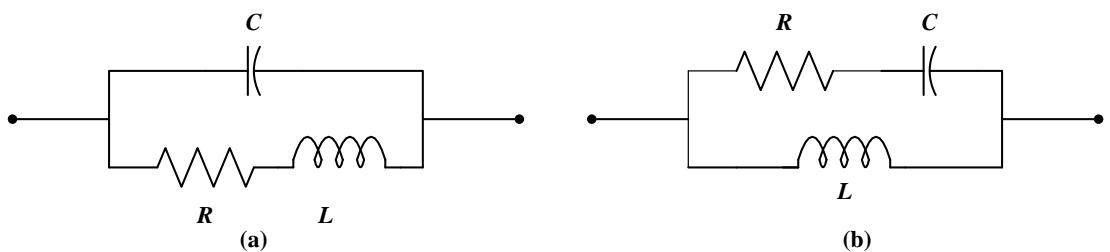

| 1.1  | Series passive power filters (a) Tuned filter, and (b) Damped filter. . . . .                                                    | 8  |

| 1.2  | Shunt passive power filters (a) Tuned filter, and (b) Damped filter. . . . .                                                     | 9  |

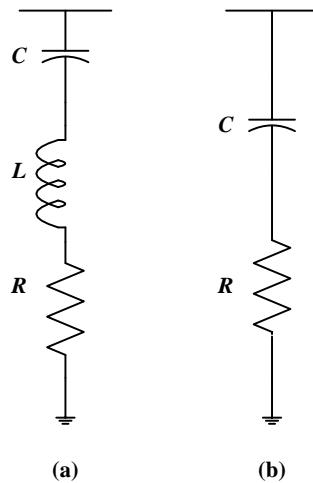

| 1.3  | Schematic diagram of DSTATCOM connected distribution system. . . . .                                                             | 10 |

| 1.4  | Schematic diagram of hybrid filter connected distribution system. . . . .                                                        | 11 |

| 2.1  | Connection diagram of (a) Current source inverter (b) Voltage source inverter. . . . .                                           | 16 |

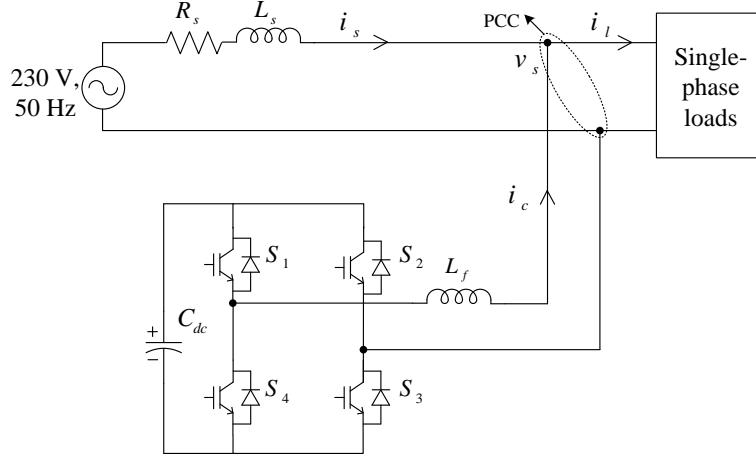

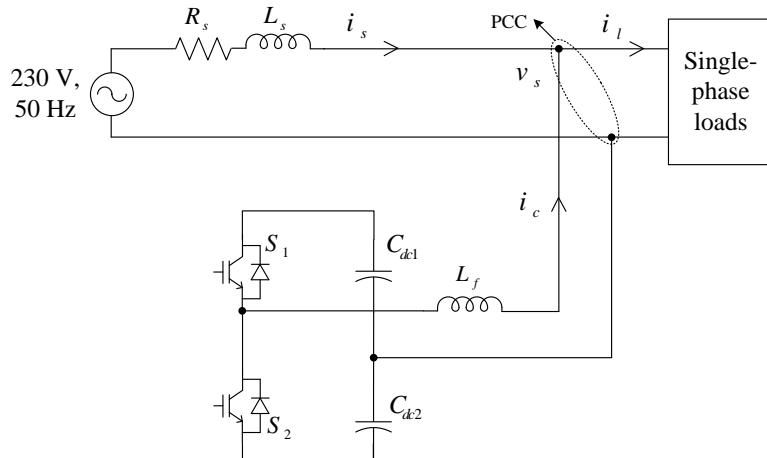

| 2.2  | Single-phase H-bridge DSTATCOM topology. . . . .                                                                                 | 17 |

| 2.3  | Single-phase split-capacitor DSTATCOM topology. . . . .                                                                          | 17 |

| 2.4  | (a) Schematic diagram of three-phase three-wire DSTATCOM topologies (b) Three leg DSTATCOM (c) FSSC, and (d) FSOC. . . . .       | 18 |

| 2.5  | Three H-bridge DSTATCOM topology in 3P4W distribution system. . . . .                                                            | 19 |

| 2.6  | Three-phase split-capacitor DSTATCOM topology in 3P4W distribution system. . . . .                                               | 20 |

| 2.7  | Three-leg split-capacitor DSTATCOM topology with voltage balancing circuit in 3P4W distribution system. . . . .                  | 20 |

| 2.8  | Four leg DSTATCOM topology for 3P4W distribution system. . . . .                                                                 | 21 |

| 2.9  | Unit template technique (UTT). . . . .                                                                                           | 23 |

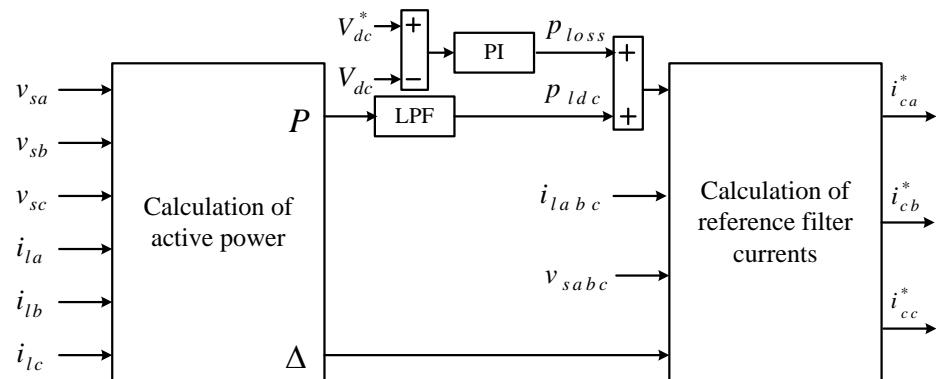

| 2.10 | Instantaneous reactive power theory (IRPT). . . . .                                                                              | 25 |

| 2.11 | Synchronous reference frame (SRF) theory. . . . .                                                                                | 27 |

| 2.12 | Instantaneous symmetrical component theory (ISCT). . . . .                                                                       | 29 |

| 2.13 | Pulse generation using PWM current controller. . . . .                                                                           | 33 |

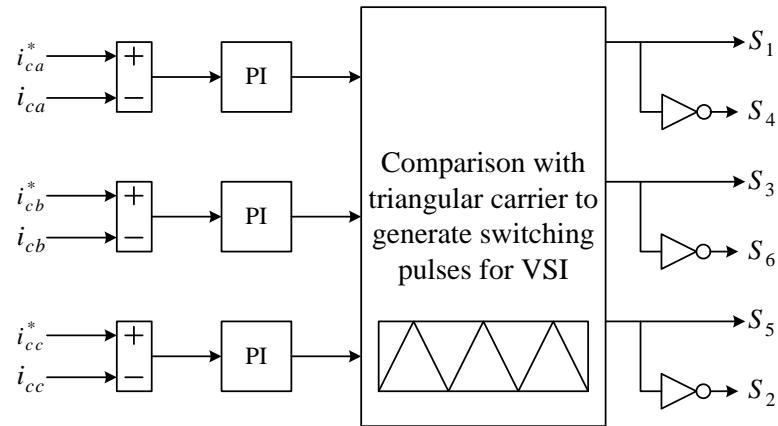

| 2.14 | Pulse generation using hysteresis current controller. . . . .                                                                    | 34 |

| 2.15 | Pulse generation using model predictive control. . . . .                                                                         | 35 |

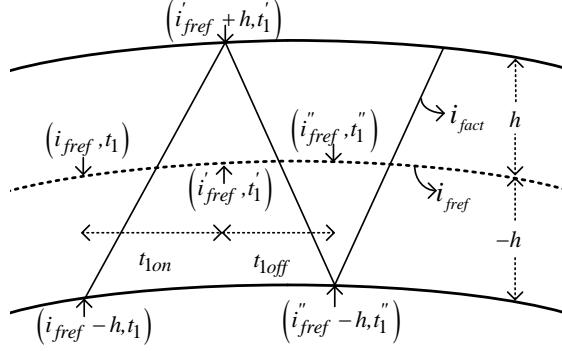

| 2.16 | Switching dynamics of hysteresis controller for $L$ -filter design. . . . .                                                      | 37 |

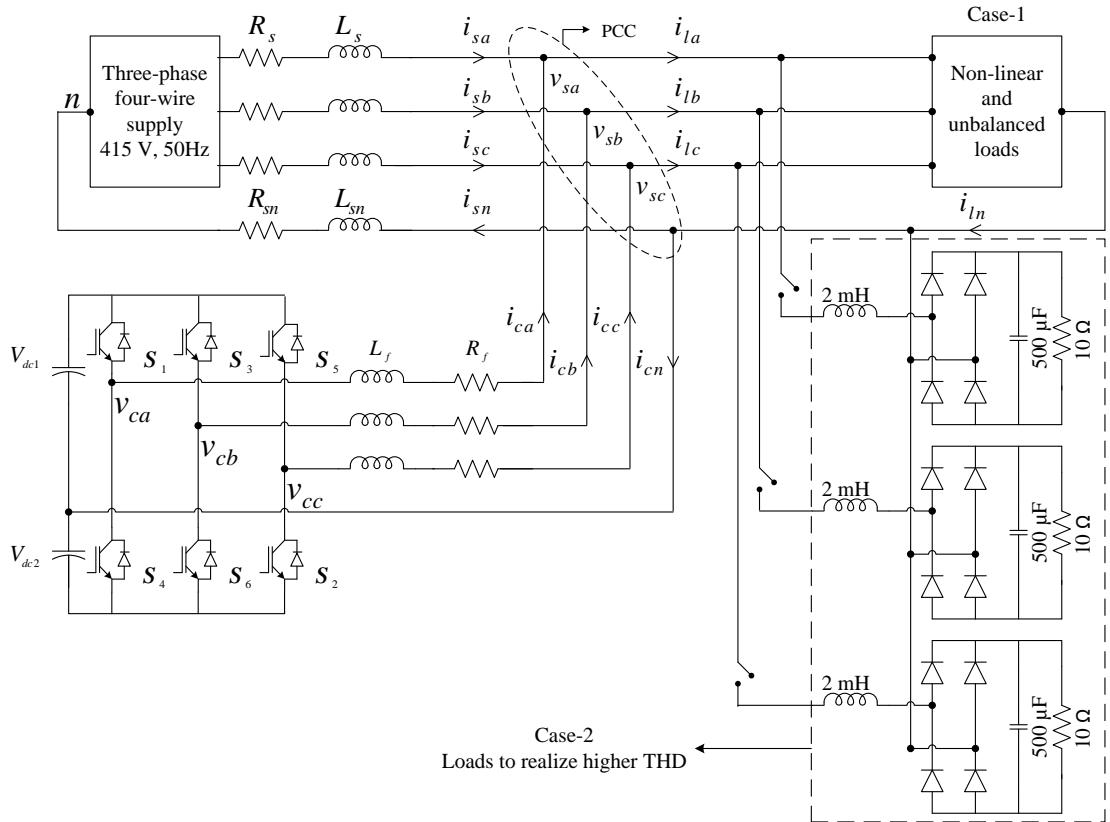

| 3.1  | Schematic diagram of DSTATCOM connected distribution system. . . . .                                                             | 41 |

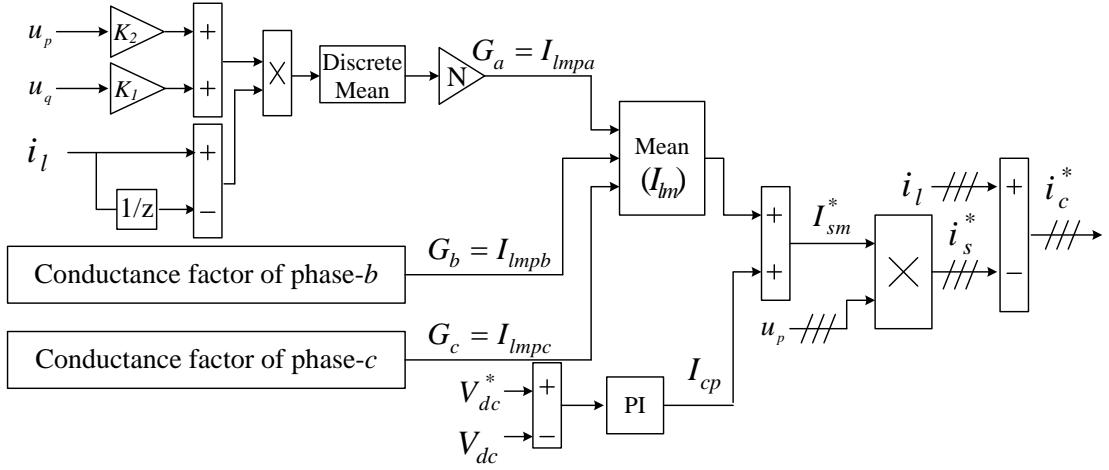

| 3.2  | Proposed MPC algorithm with VIKOR method. . . . .                                                                                | 43 |

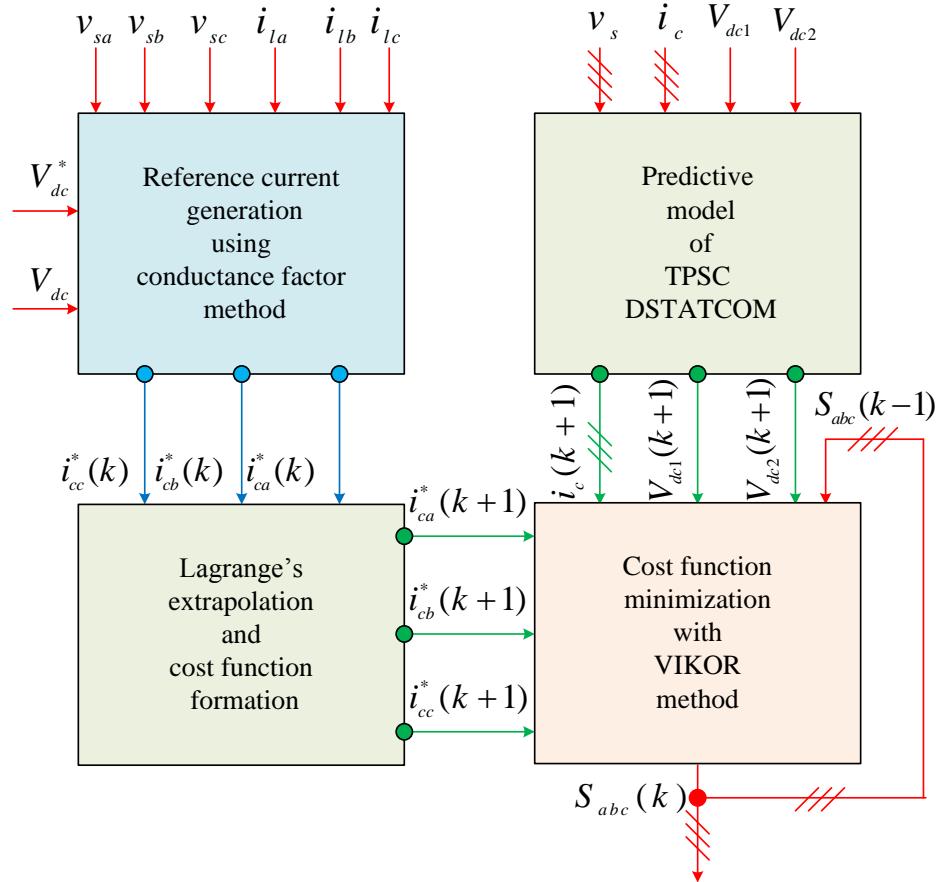

| 3.3  | Reference current extraction using conductance factor method. . . . .                                                            | 44 |

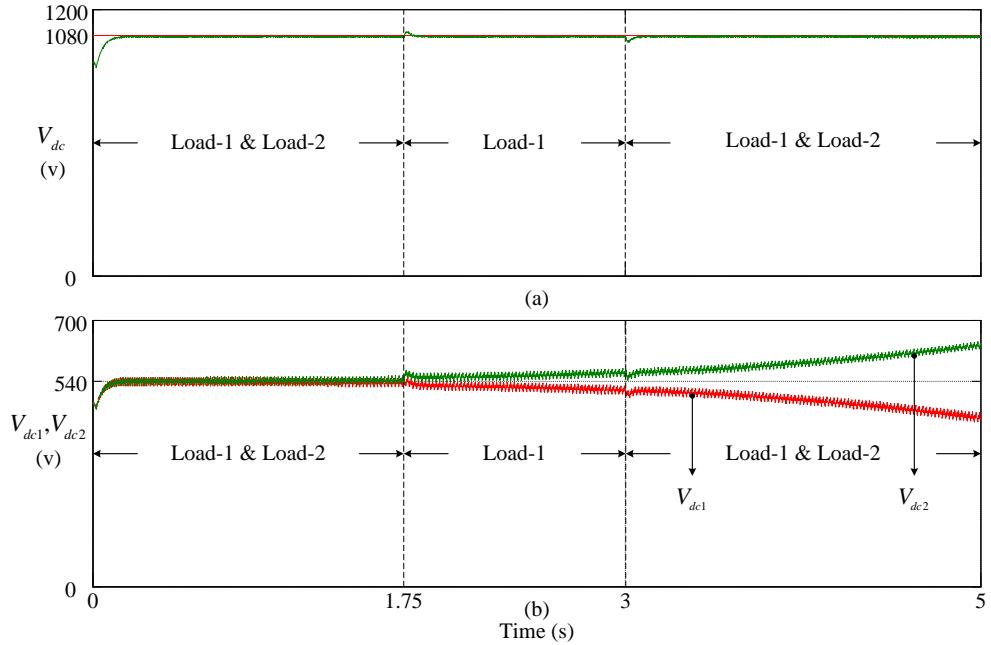

| 3.4  | Without adding additional constraints (a) Voltage across complete dc link, and (b) Voltage across individual capacitors. . . . . | 53 |

|      |                                                                                                                                                                                          |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

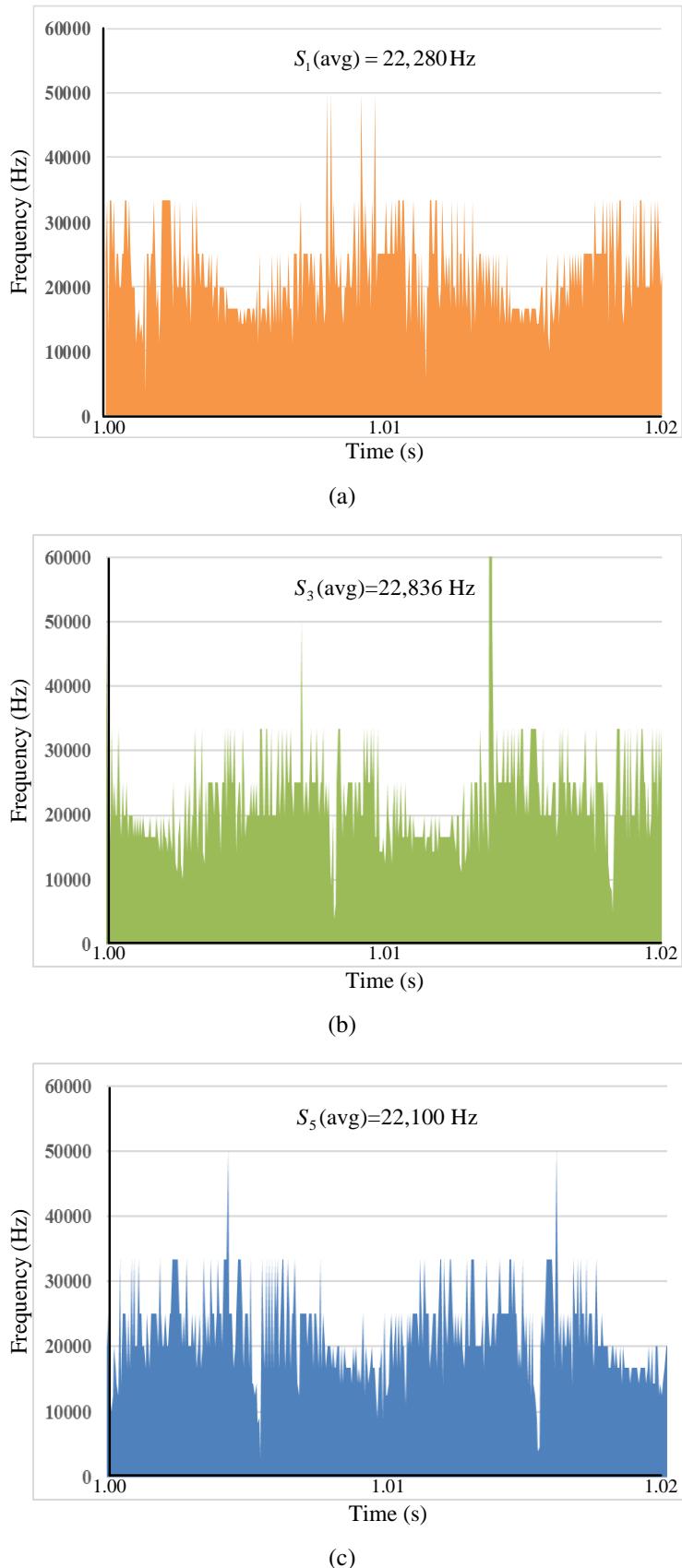

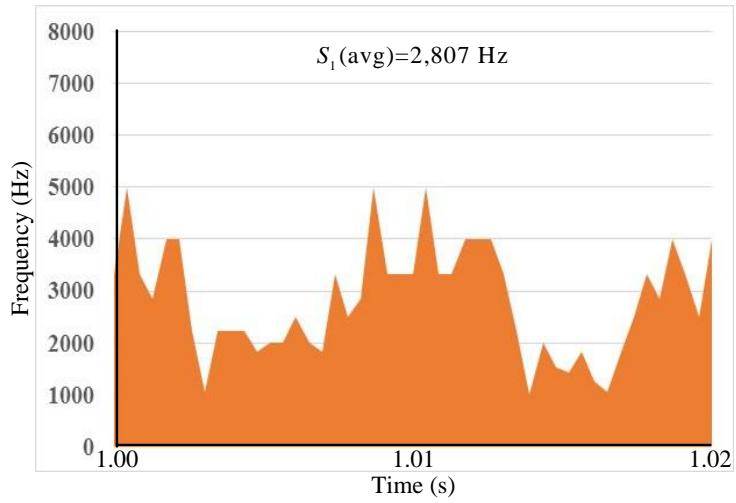

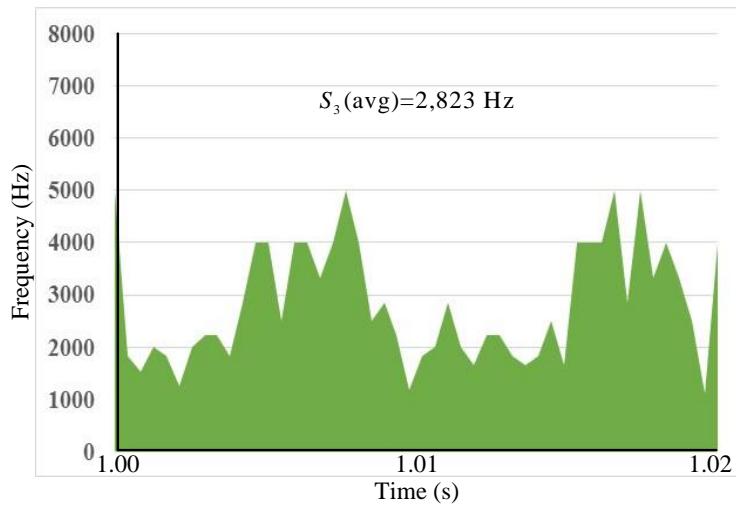

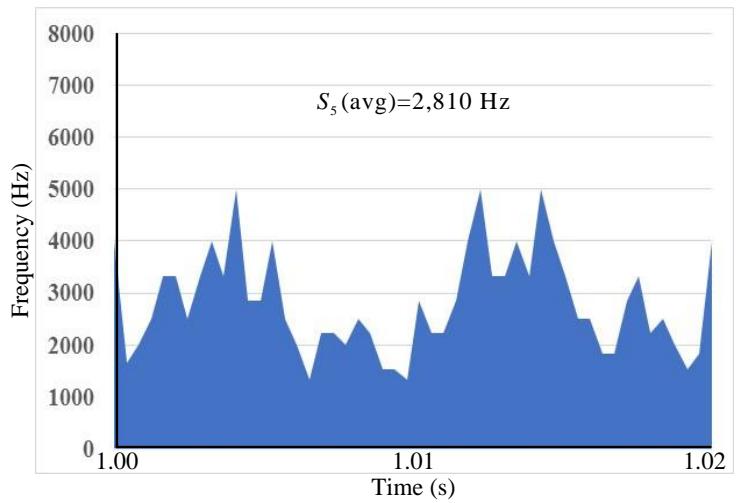

| 3.5  | Average switching frequency without adding additional constraints (a) $S_1$ (b) $S_3$ , and (c) $S_5$ . . . . .                                                                          | 54 |

| 3.6  | Simulation results using proposed control algorithm. . . . .                                                                                                                             | 55 |

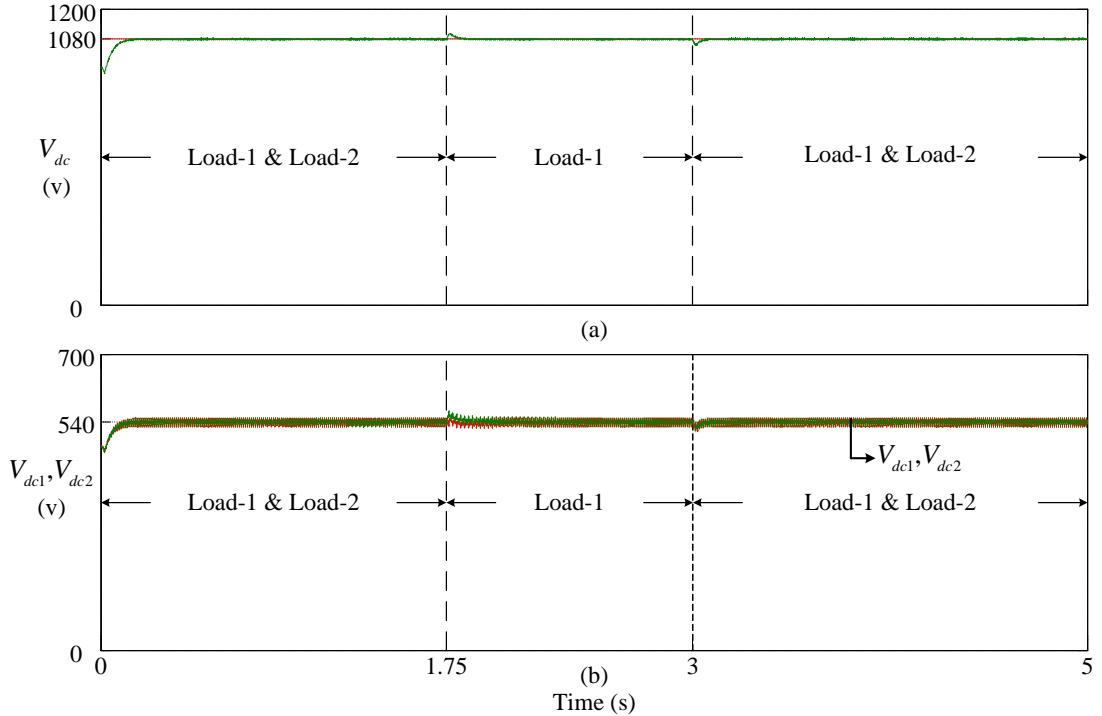

| 3.7  | After including additional constraints (a) Voltage across complete dc link, and (b) Voltage across individual capacitors. . . . .                                                        | 56 |

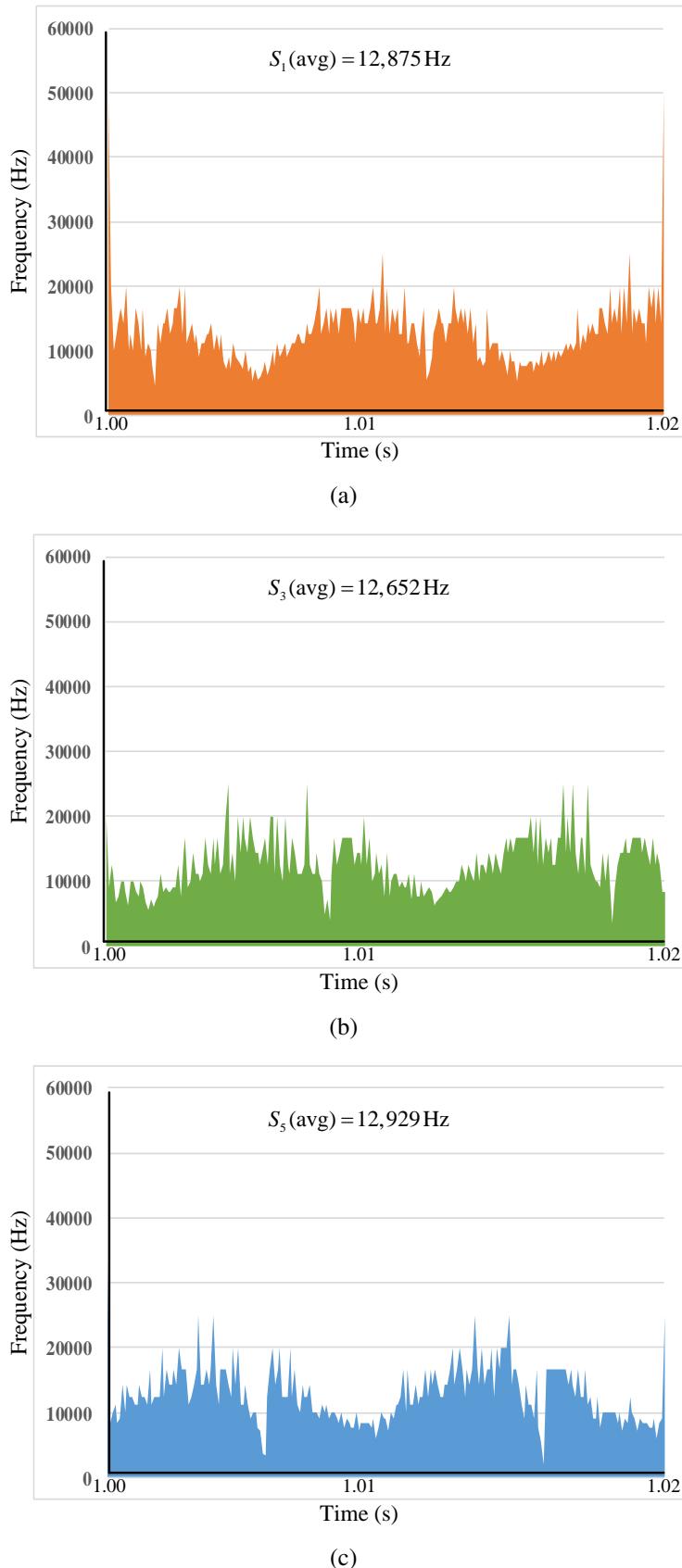

| 3.8  | Average switching frequency after adding additional constraints (a) $S_1$ (b) $S_3$ , and (c) $S_5$ . . . . .                                                                            | 57 |

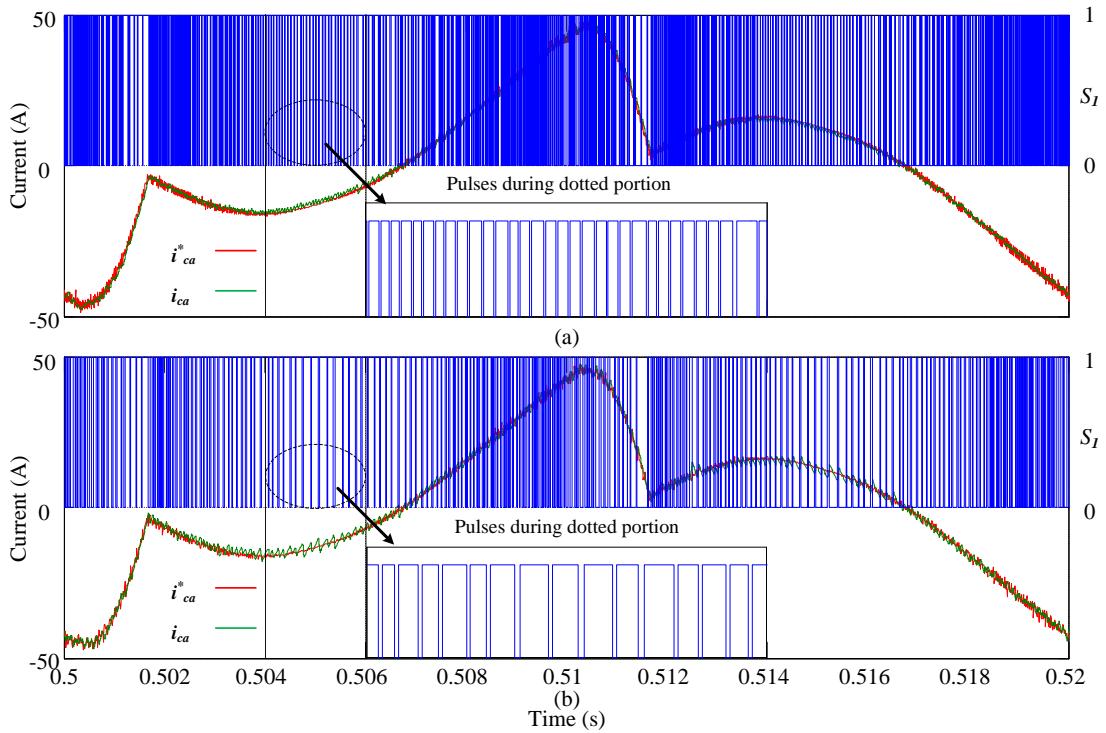

| 3.9  | Current tracking and switching pulses comparison (a) Without adding switching frequency constraint, and (b) After including switching frequency constraint in the cost function. . . . . | 58 |

| 3.10 | Voltages and currents without and with additional constraints during higher THD loads. . . . .                                                                                           | 59 |

| 3.11 | Photograph of the experimental setup. . . . .                                                                                                                                            | 60 |

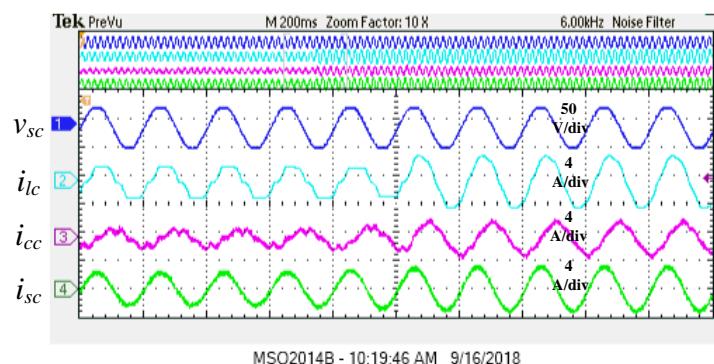

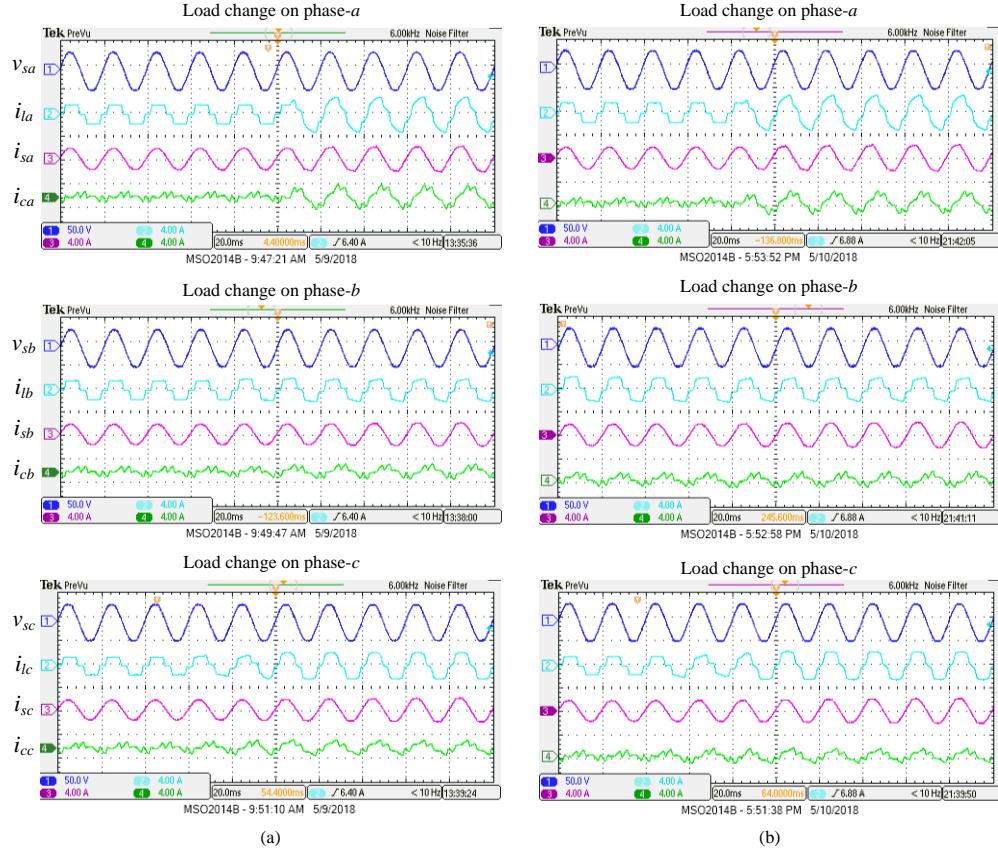

| 3.12 | Parameters during load variation (a) Phase- <i>a</i> (b) Phase- <i>b</i> , and (c) Phase- <i>c</i> . . . . .                                                                             | 61 |

| 3.13 | DC link voltage during load variation. . . . .                                                                                                                                           | 61 |

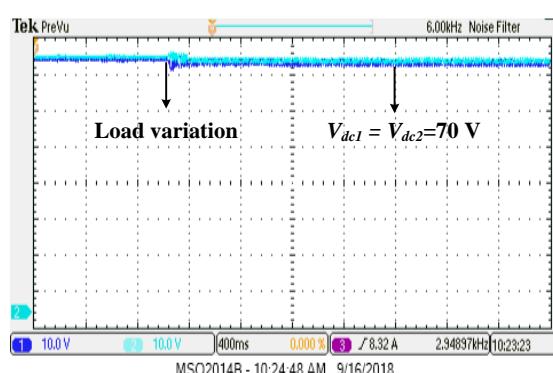

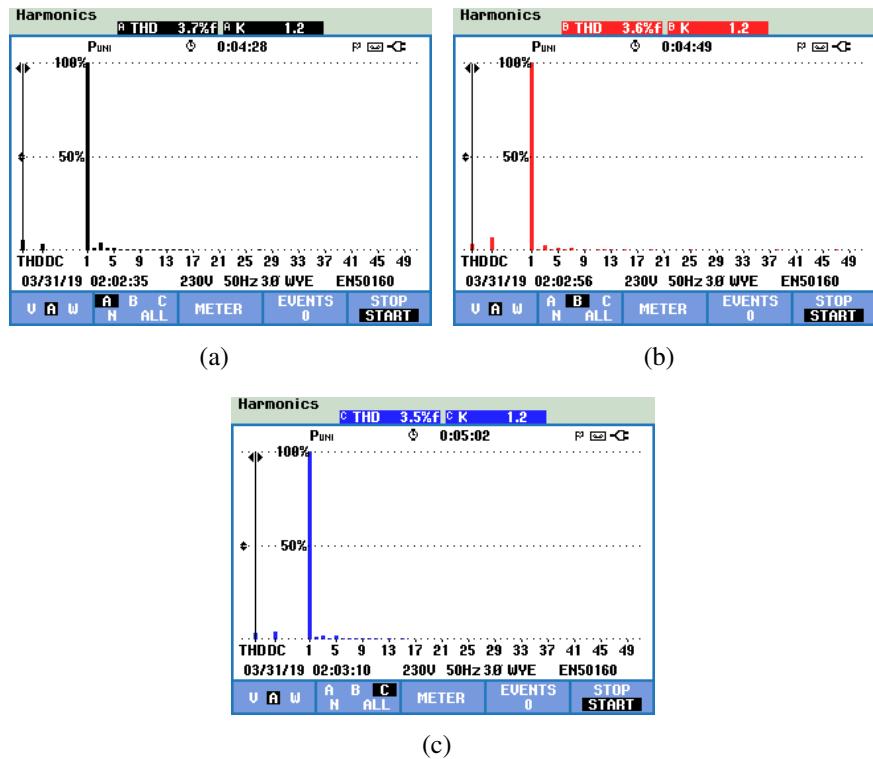

| 3.14 | THDs of source currents (a) Without additional constraints, and (b) With additional constraints. . . . .                                                                                 | 62 |

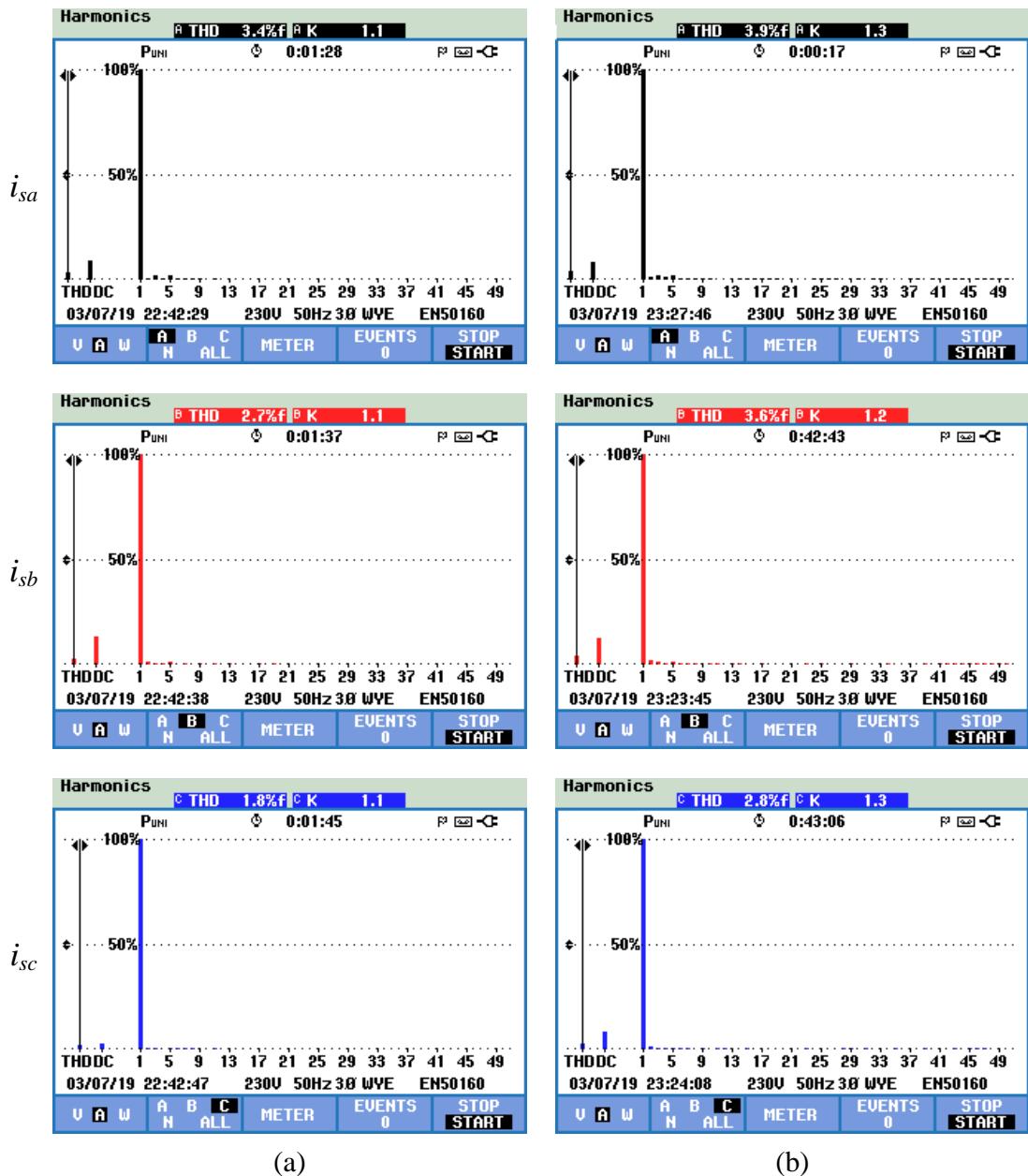

| 3.15 | Average switching frequency without adding additional constraints during experimental studies (a) $S_1$ (b) $S_3$ , and (c) $S_5$ . . . . .                                              | 63 |

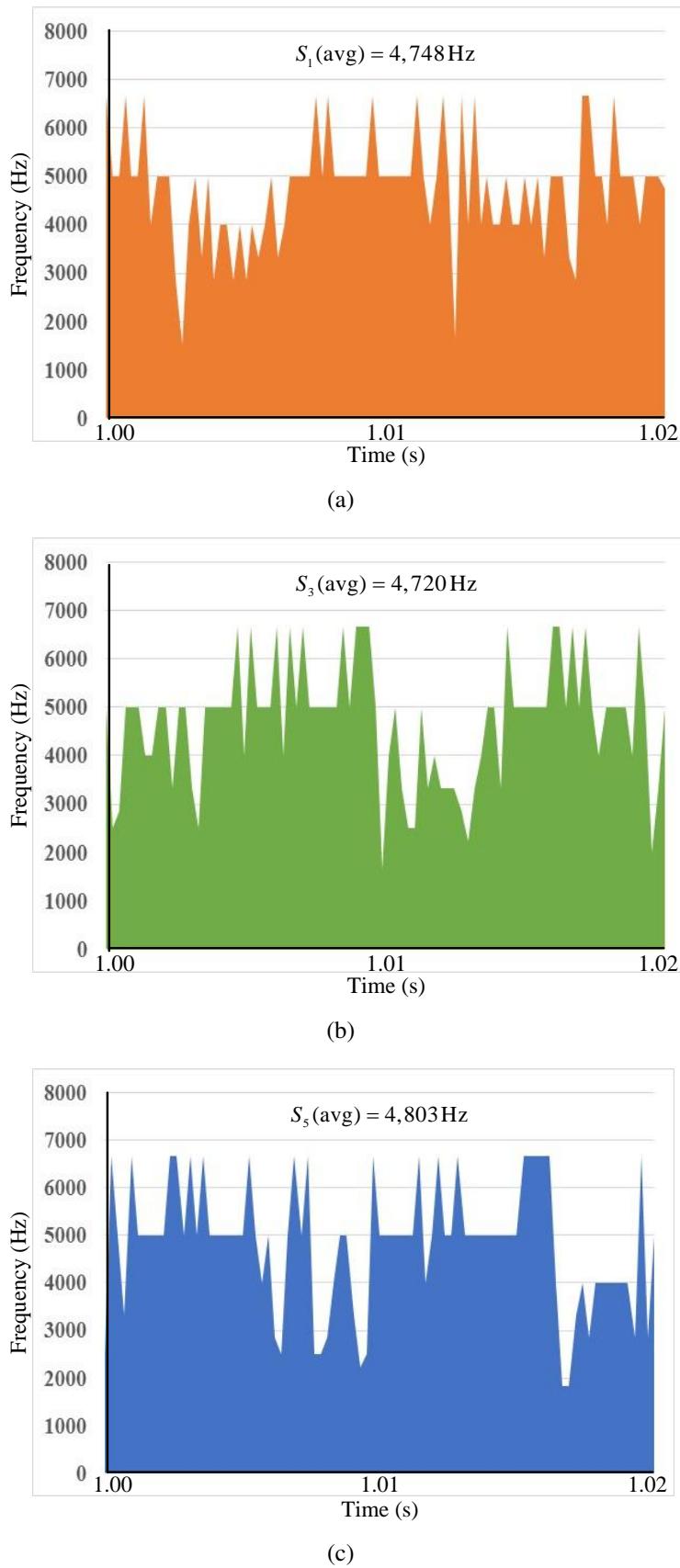

| 3.16 | Average switching frequency after adding additional constraints during experimental studies (a) $S_1$ (b) $S_3$ , and (c) $S_5$ . . . . .                                                | 64 |

| 3.17 | <b>Simulation results of voltages and currents with experimental parameters.</b> . . . . .                                                                                               | 65 |

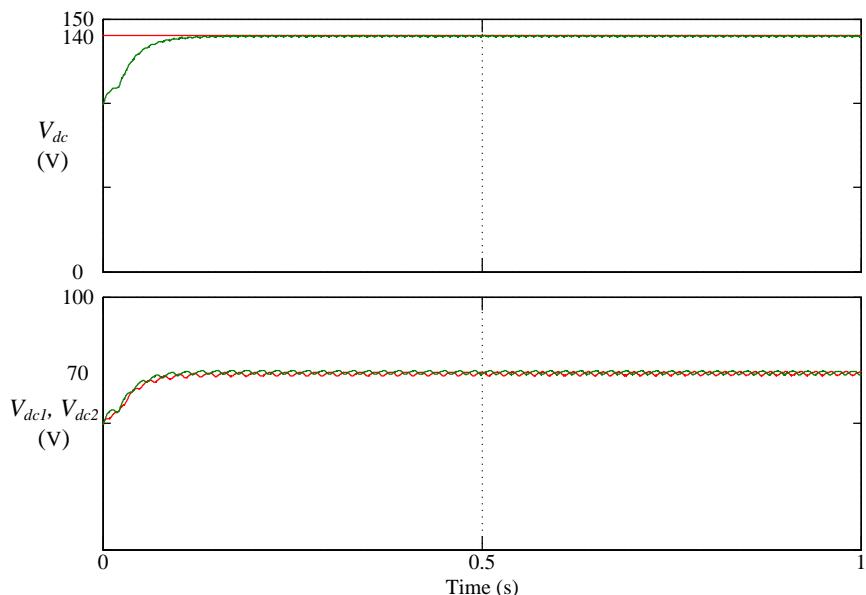

| 3.18 | <b>Complete dc link and individual capacitor voltages.</b> . . . . .                                                                                                                     | 65 |

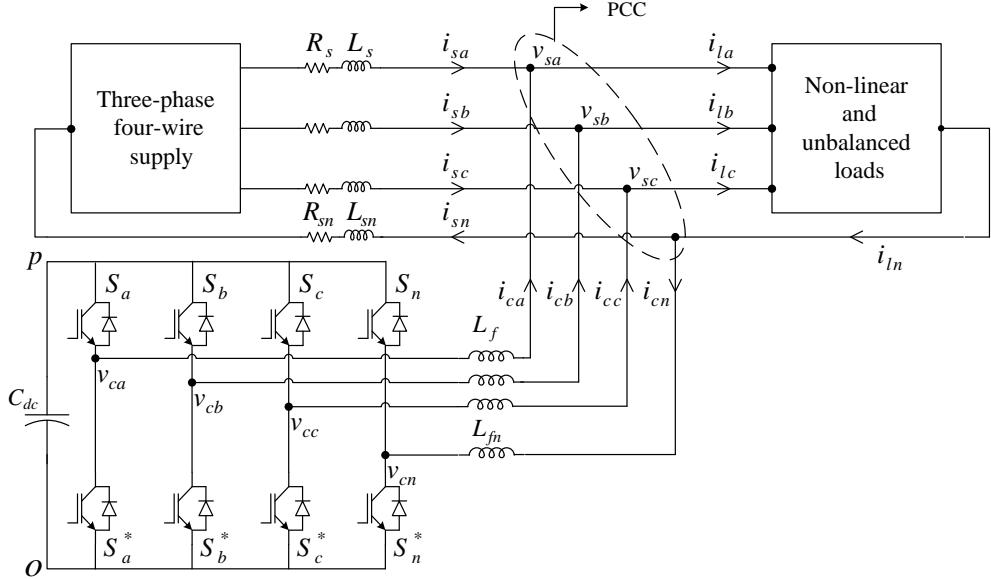

| 4.1  | Schematic diagram of a FL-DSTATCOM connected distribution system. . . . .                                                                                                                | 70 |

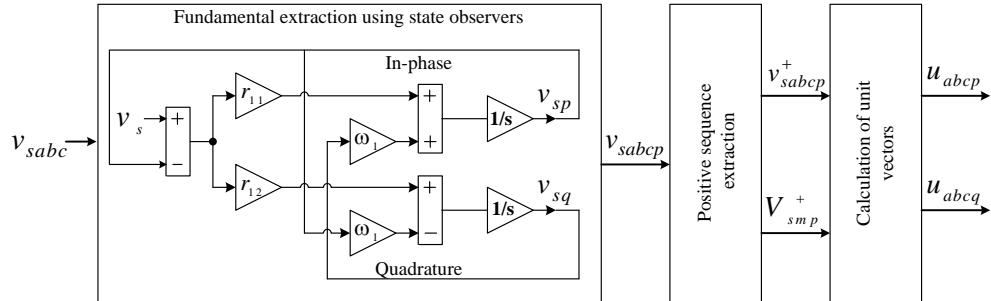

| 4.2  | Extraction of unit vectors using state observer and theory of symmetrical components [76]. . . . .                                                                                       | 71 |

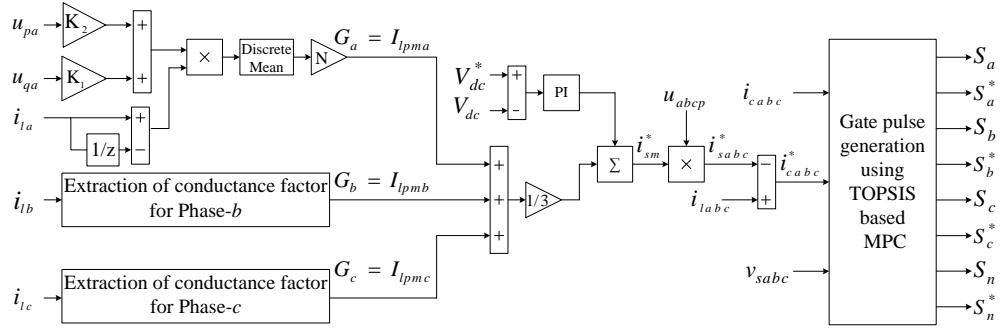

| 4.3  | Proposed conductance factor based control algorithm for FL-DSTATCOM. . . . .                                                                                                             | 74 |

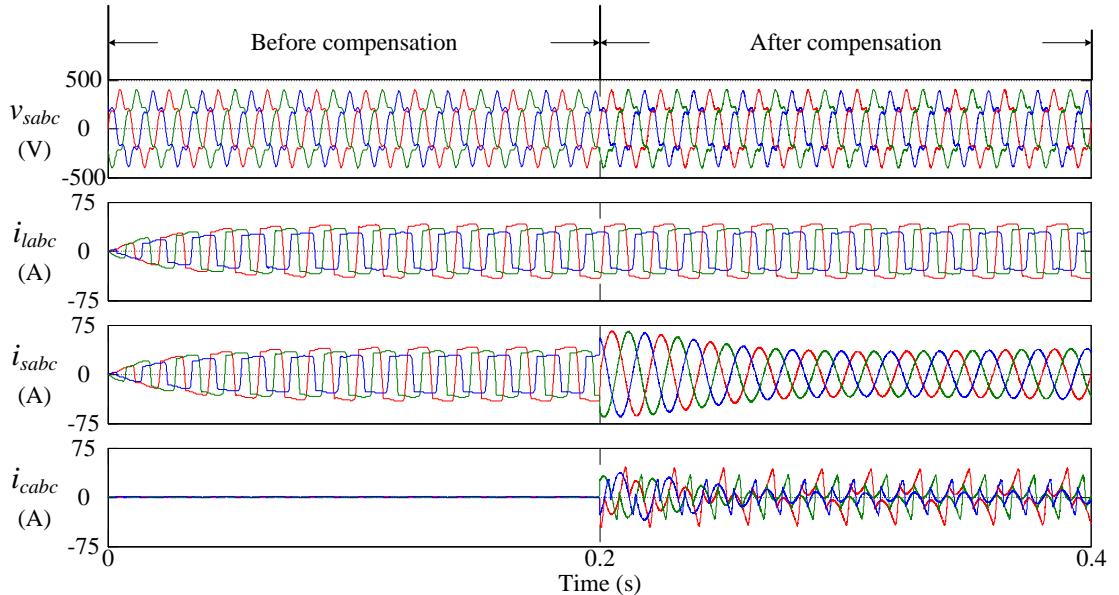

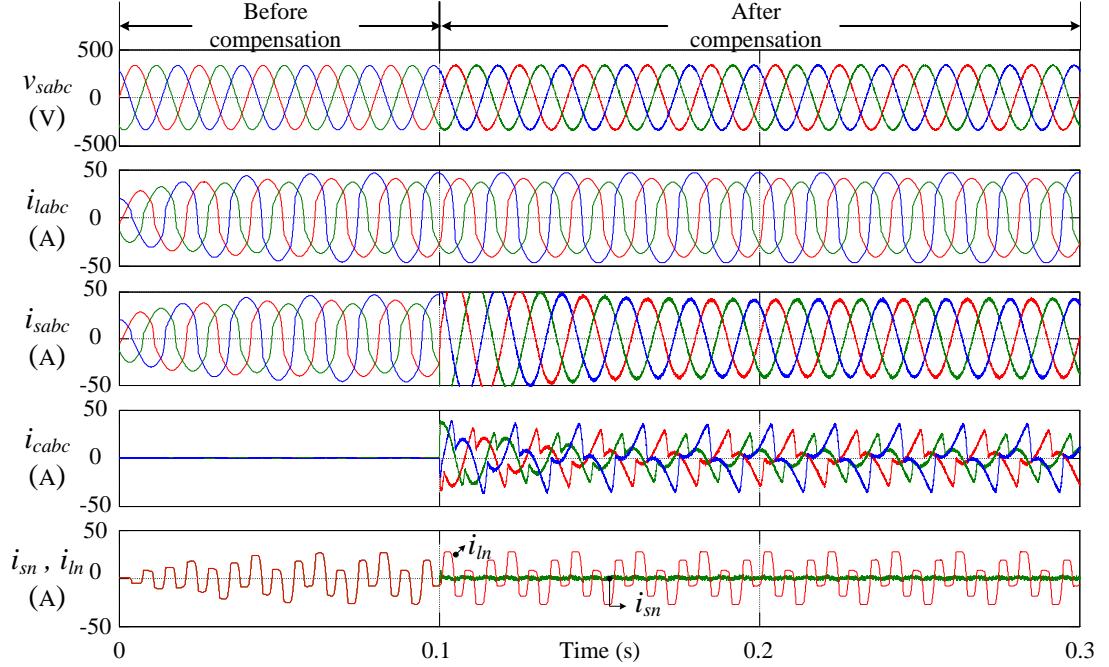

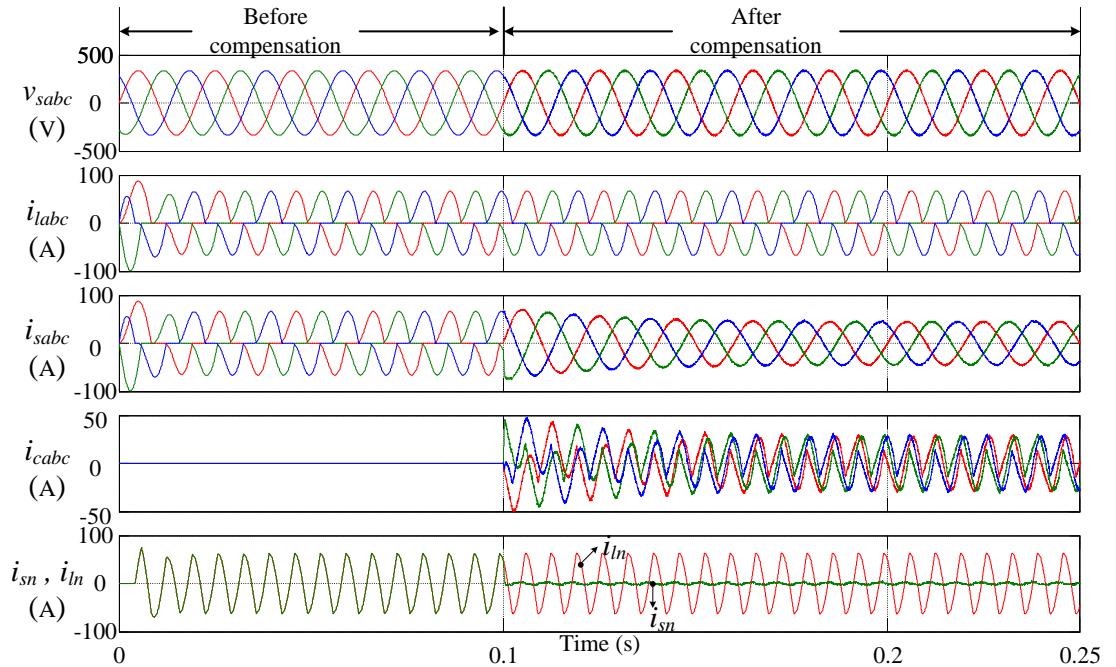

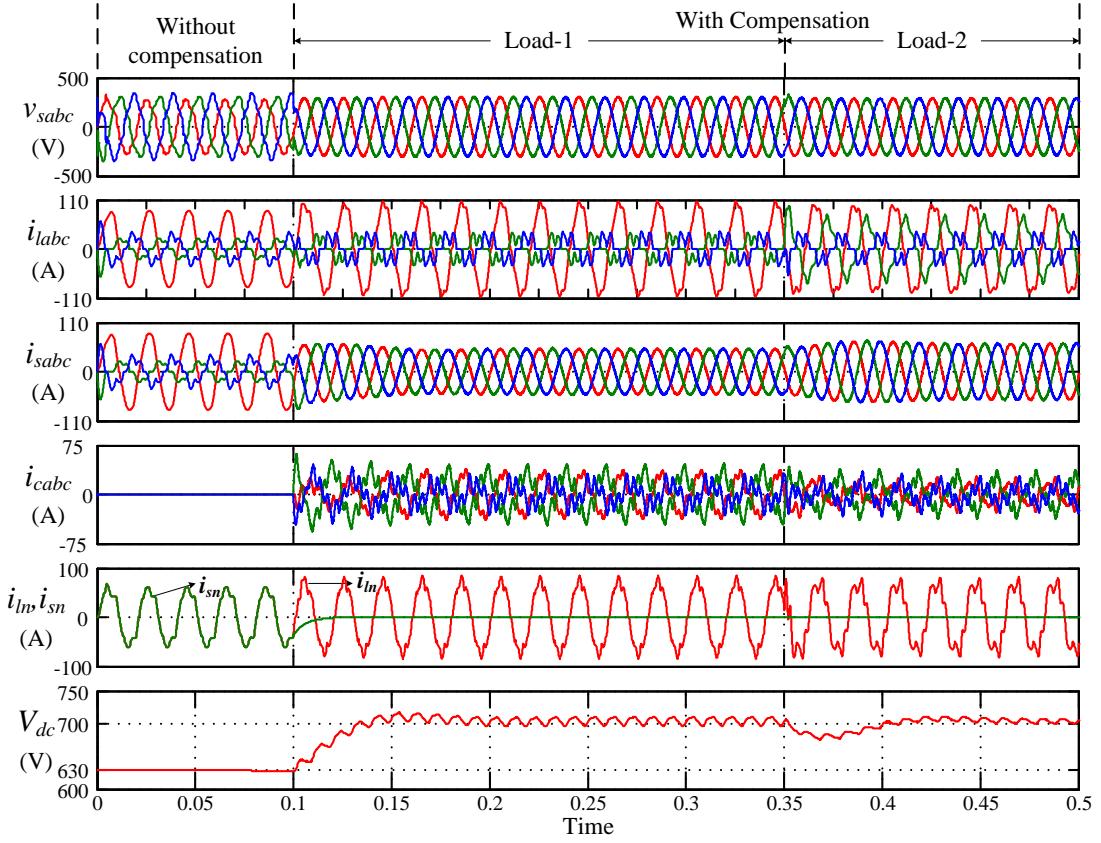

| 4.4  | Voltages and currents before and after connecting the FL-DSTATCOM. . . . .                                                                                                               | 82 |

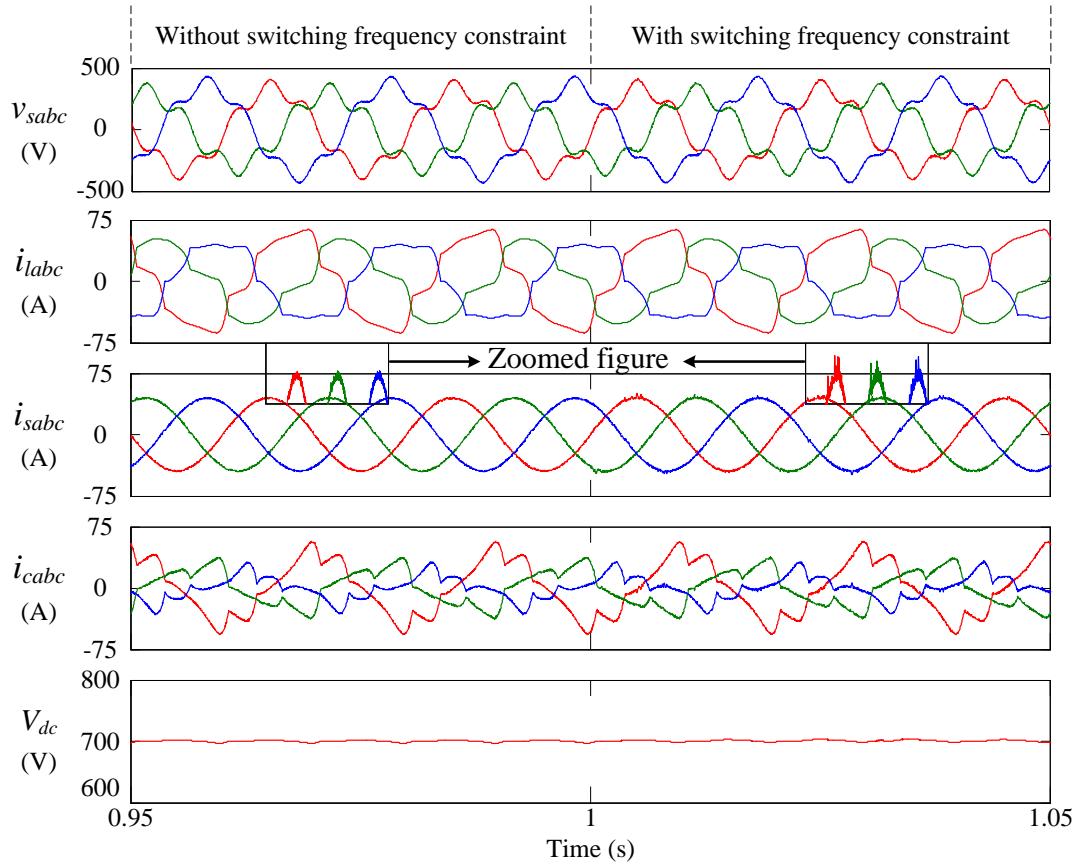

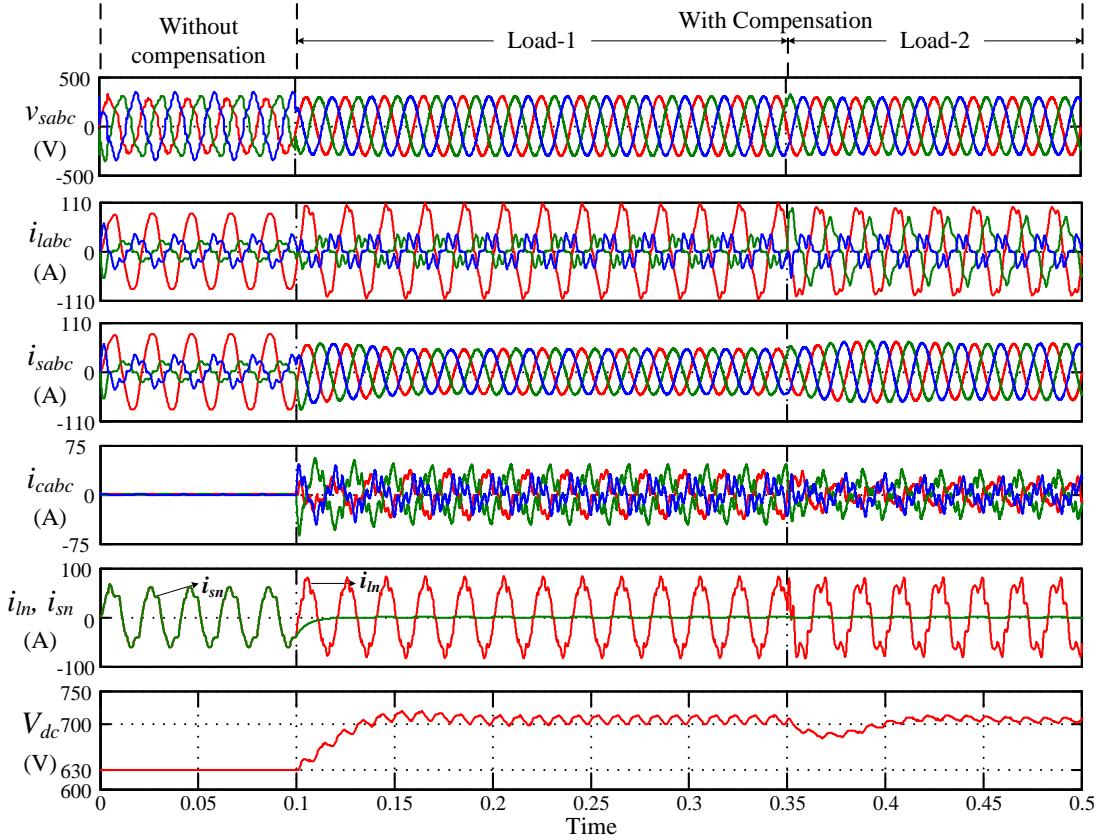

| 4.5  | Voltages and currents without and with additional constraint during case-1. . . . .                                                                                                      | 83 |

| 4.6  | Neutral currents without and with additional constraint during case-1. . . . .                                                                                                           | 84 |

| 4.7  | Neutral currents without and with additional constraint during case-2 . . . . .                                                                                                          | 85 |

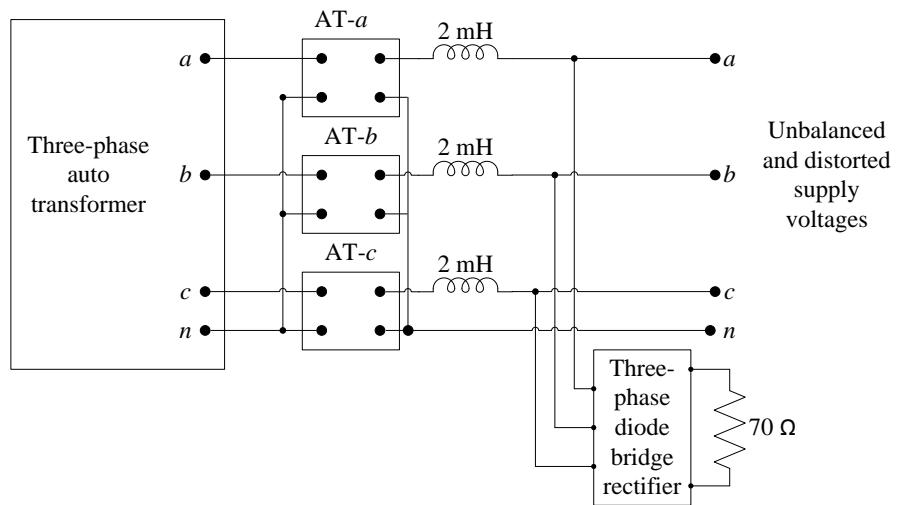

| 4.8  | Realization of three-phase unbalanced and distorted supply. . . . .                                                                                                                      | 86 |

|      |                                                                                                                                                                                                                  |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

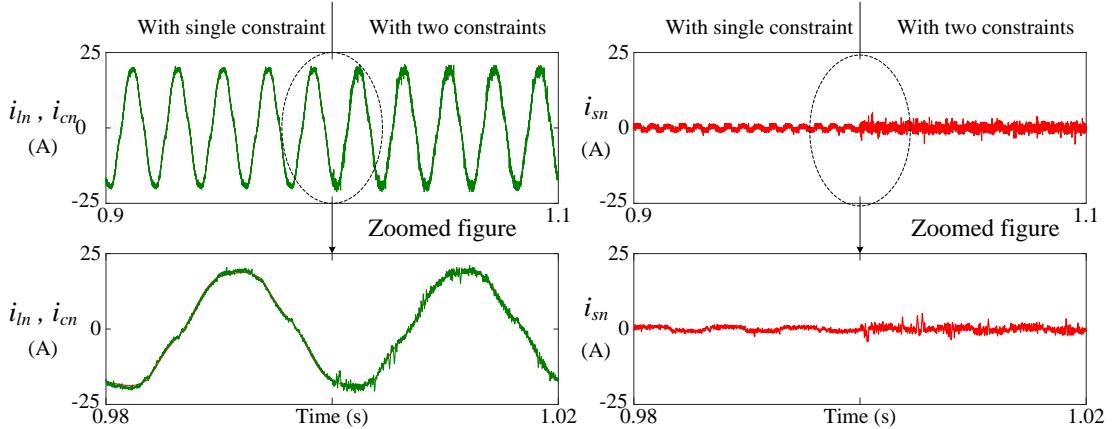

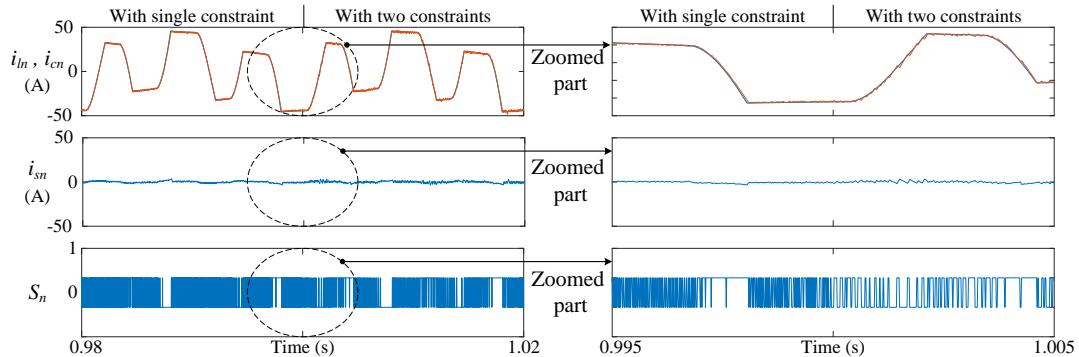

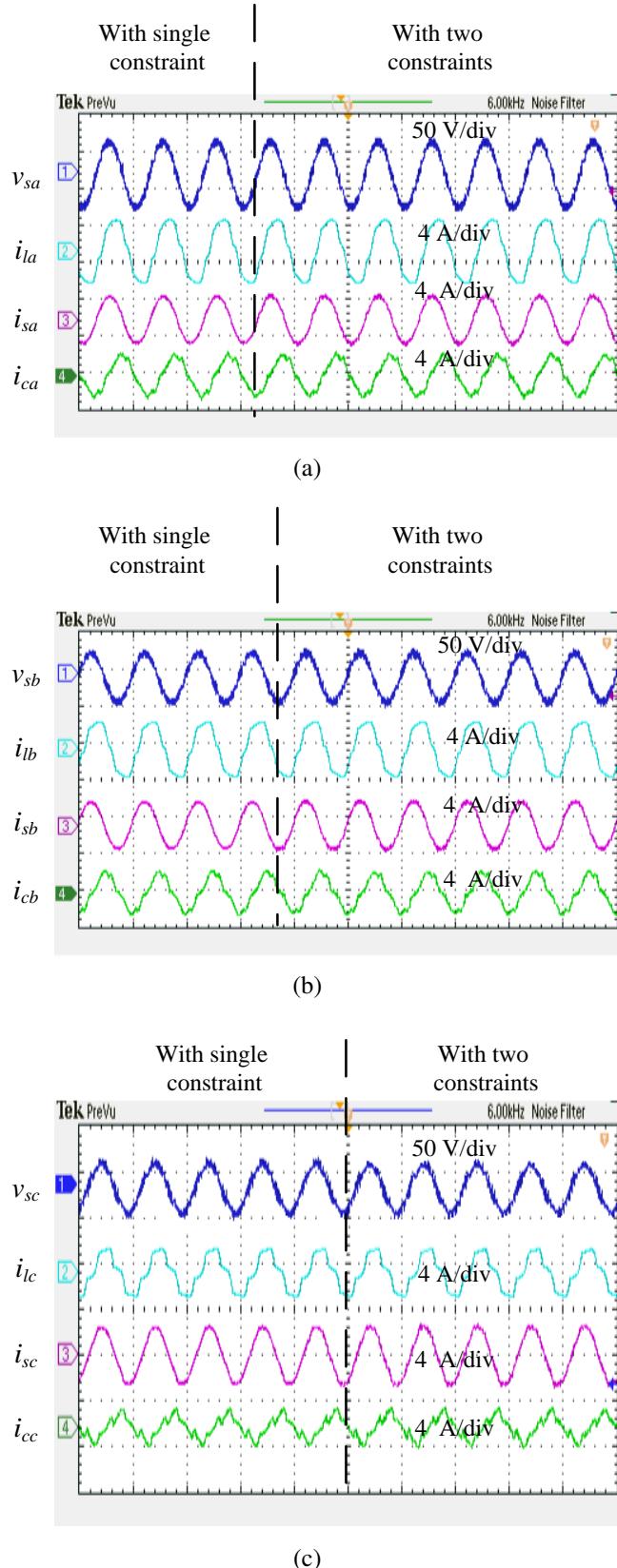

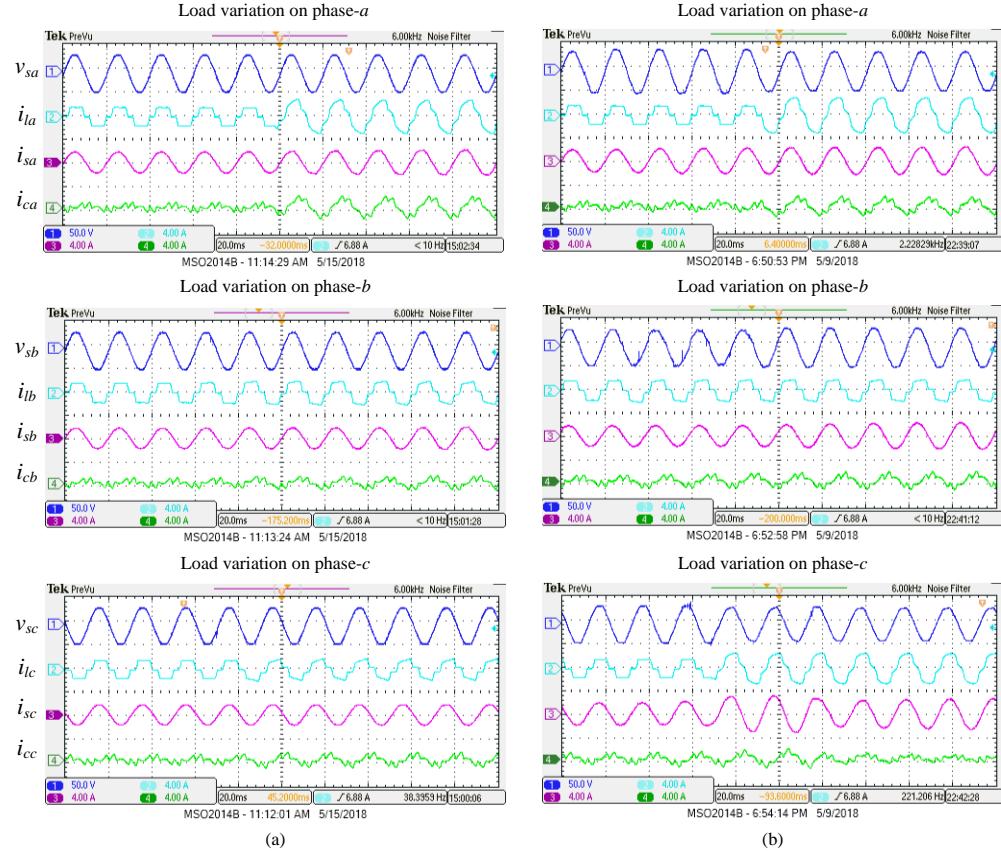

| 4.9  | Voltages and currents with single and two constraints of (a) Phase- <i>a</i> (b) Phase- <i>b</i> , and (c) Phase- <i>c</i> . . . . .                                                                             | 88  |

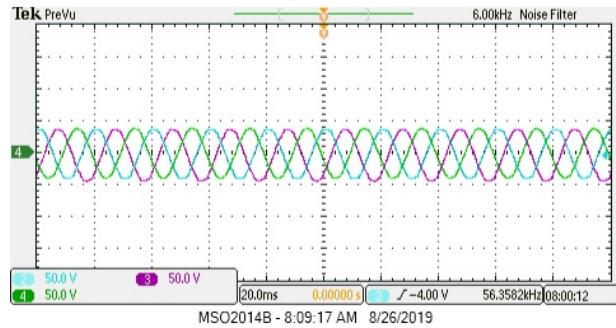

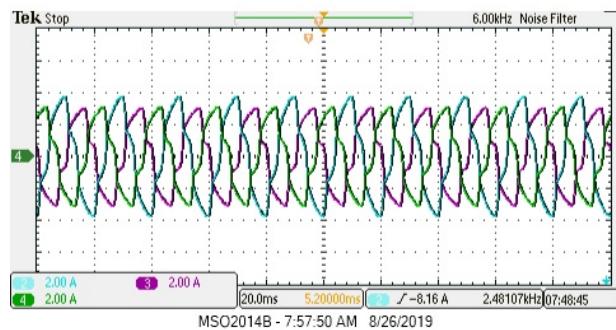

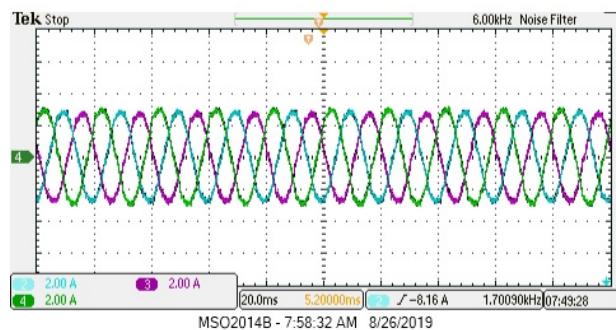

| 4.10 | Experimental waveforms of (a) Unbalanced and distorted PCC voltages (b) Unbalanced and distorted load currents, and (c) Balanced and sinusoidal source currents. . . . .                                         | 89  |

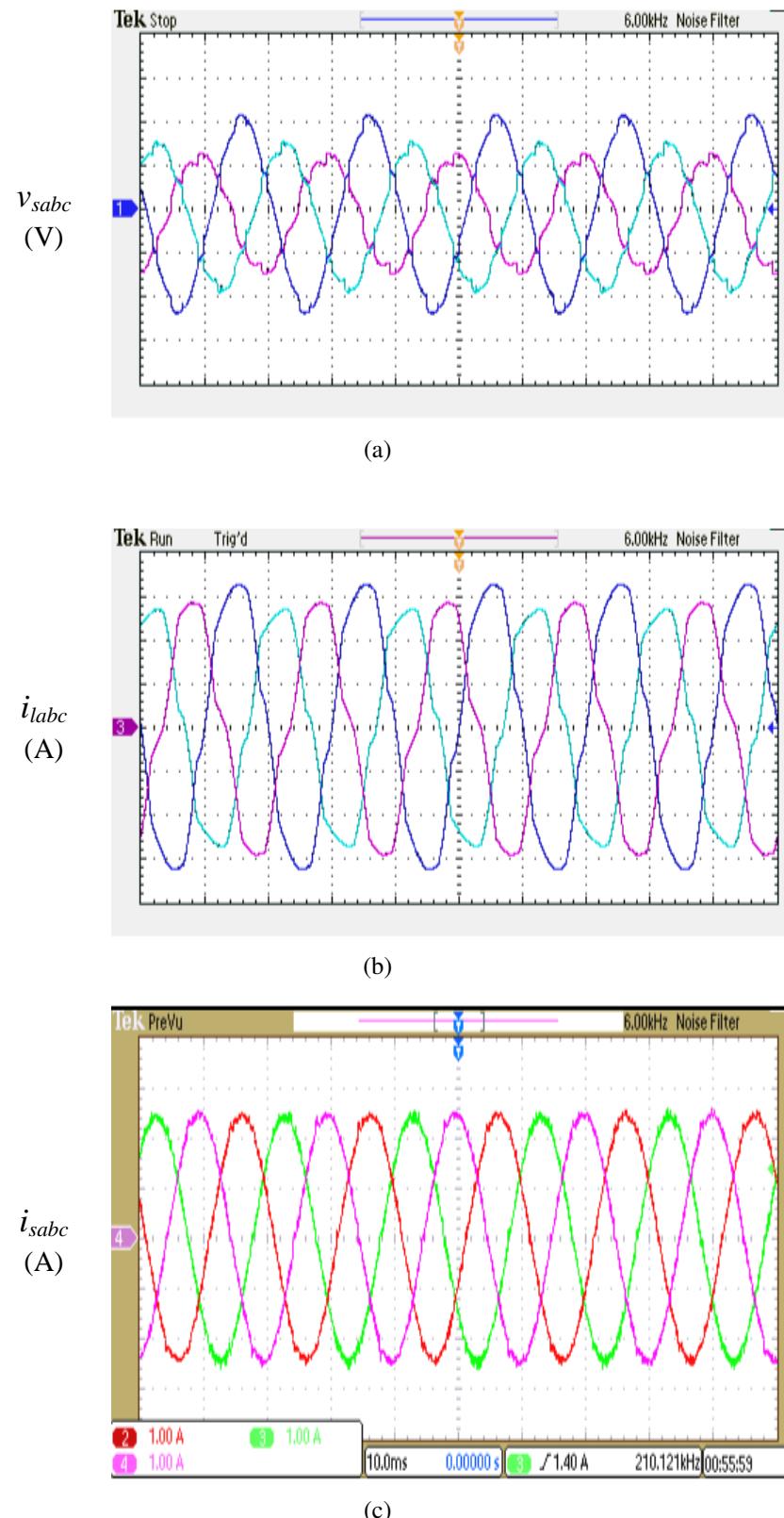

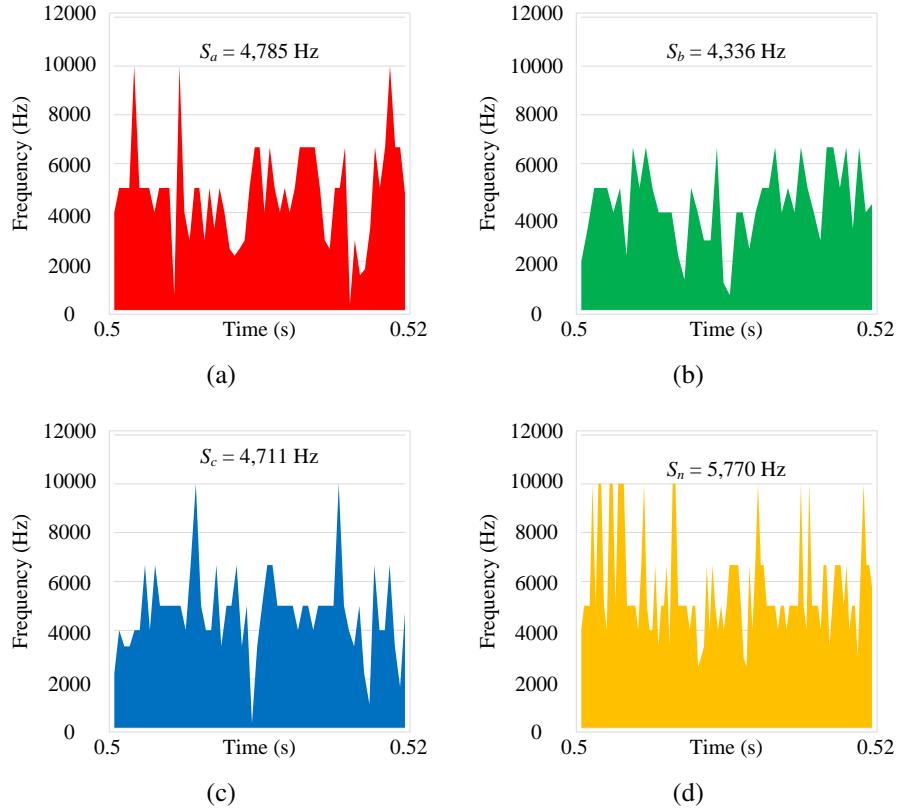

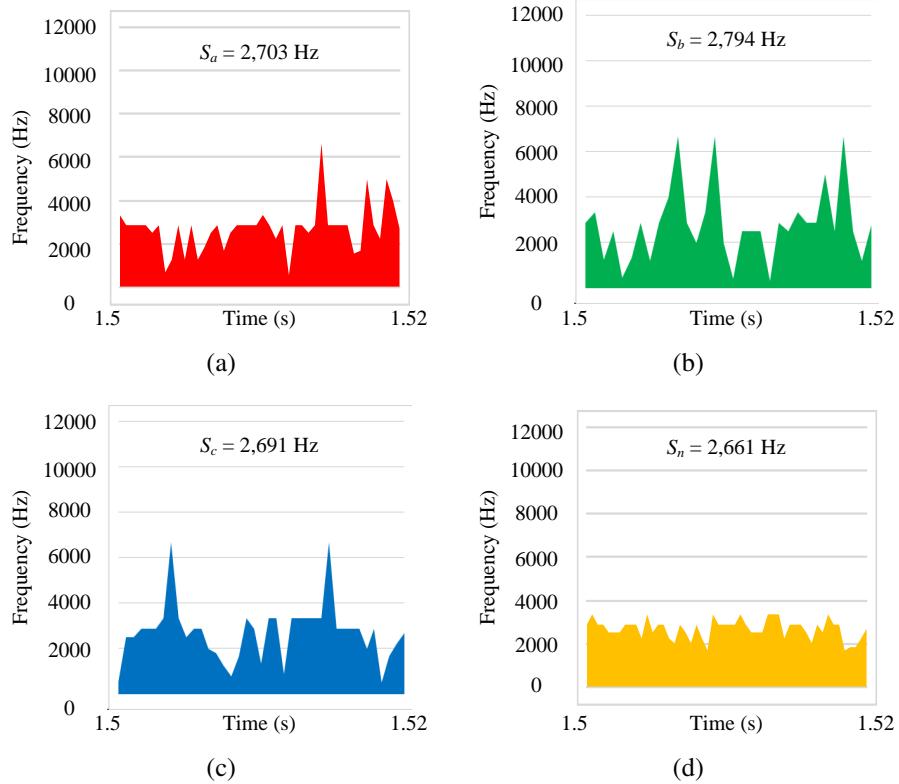

| 4.11 | Switching frequencies with current control (a) Phase- <i>a</i> (b) Phase- <i>b</i> (c) Phase- <i>c</i> , and (d) Neutral leg. . . . .                                                                            | 90  |

| 4.12 | Source currents THD with only current control (a) Phase- <i>a</i> (b) Phase- <i>b</i> , and (c) Phase- <i>c</i> . . . . .                                                                                        | 90  |

| 4.13 | Switching frequencies after including switching frequency reduction constraint (a) Phase- <i>a</i> (b) Phase- <i>b</i> (c) Phase- <i>c</i> , and (d) Neutral leg. . . . .                                        | 91  |

| 4.14 | THD of source currents during current control along with switching frequency reduction (a) Phase- <i>a</i> (b) Phase- <i>b</i> , and (c) Phase- <i>c</i> . . . . .                                               | 91  |

| 5.1  | Schematic diagram of FL-DSTATCOM connected distribution system. . . . .                                                                                                                                          | 94  |

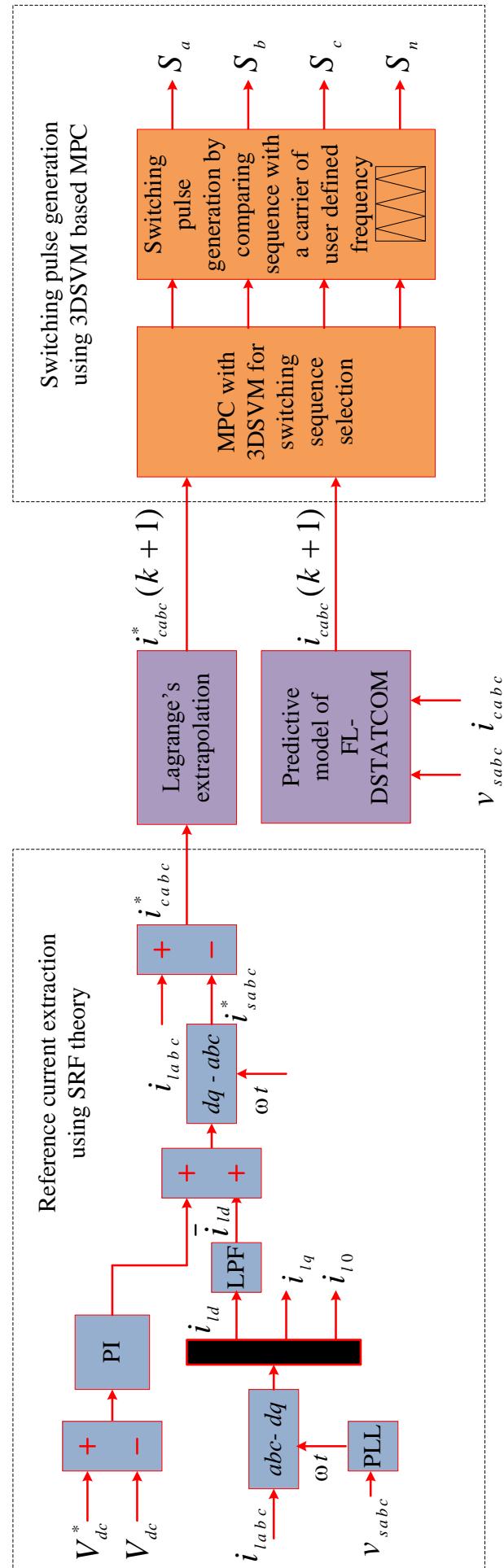

| 5.2  | Reference current extraction using SRF and switching pulse generation using MPC. . . . .                                                                                                                         | 96  |

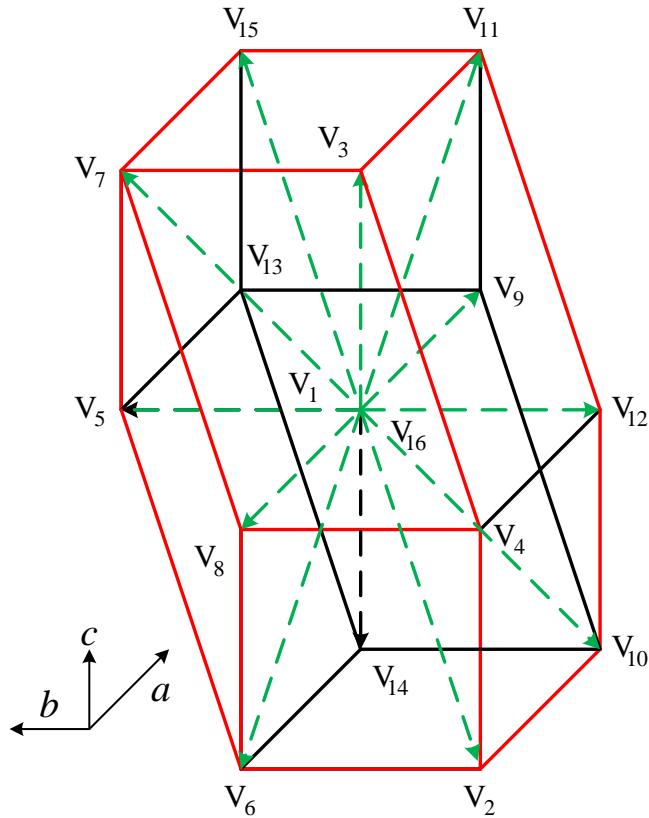

| 5.3  | Dodecahedron of all the voltage vectors. . . . .                                                                                                                                                                 | 98  |

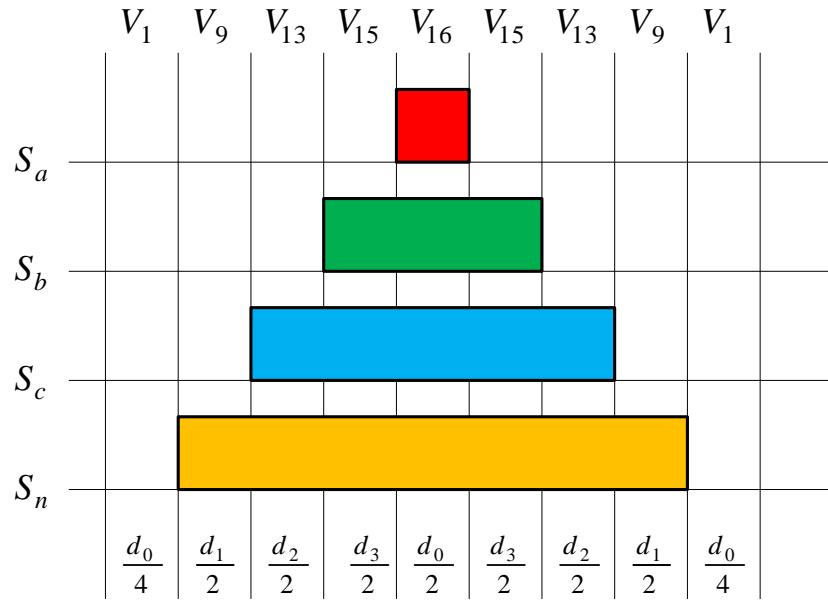

| 5.4  | Switching sequence for tetrahedron 1. . . . .                                                                                                                                                                    | 101 |

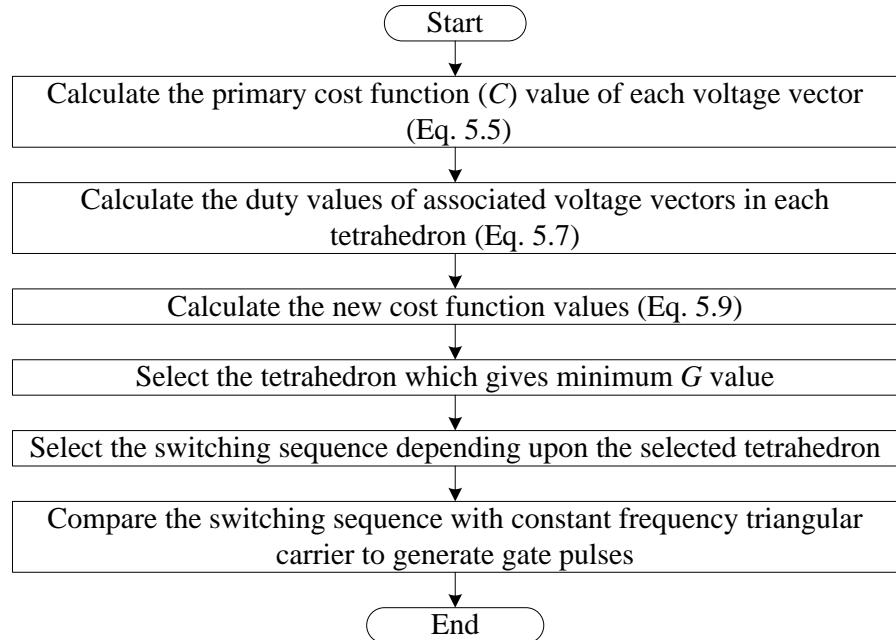

| 5.5  | Flowchart of switching pulse generation using 3DSVM. . . . .                                                                                                                                                     | 102 |

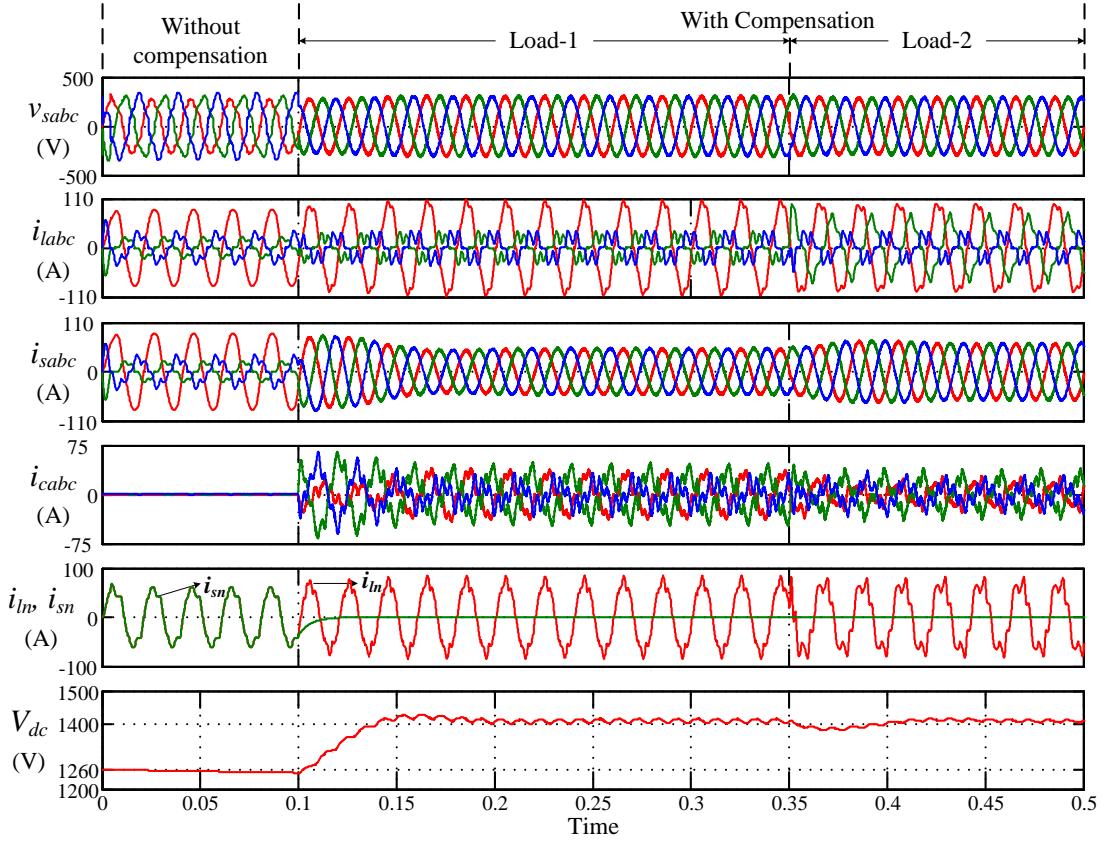

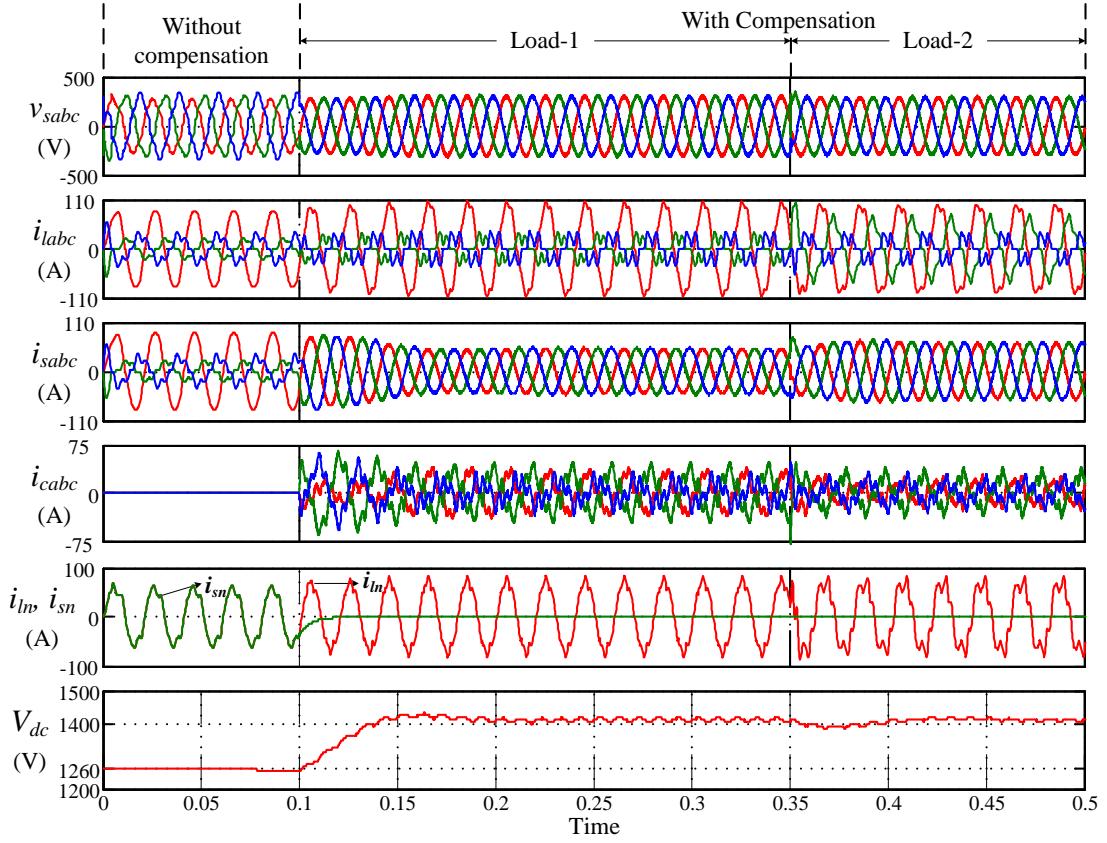

| 5.6  | Voltages and currents before and after connecting the FL-DSTATCOM to the distribution system. . . . .                                                                                                            | 103 |

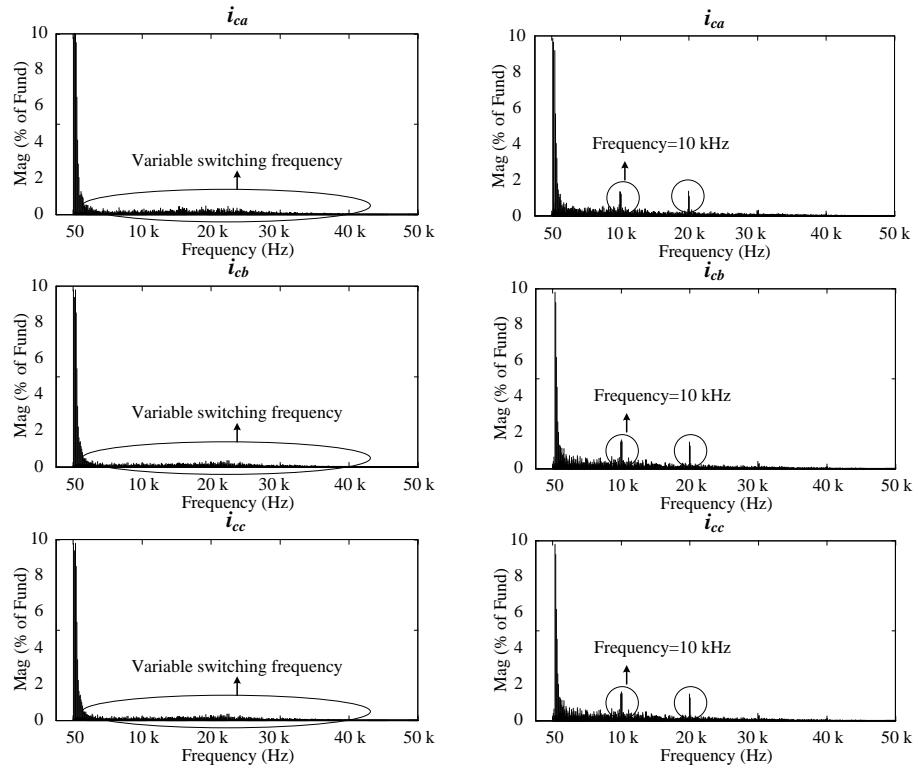

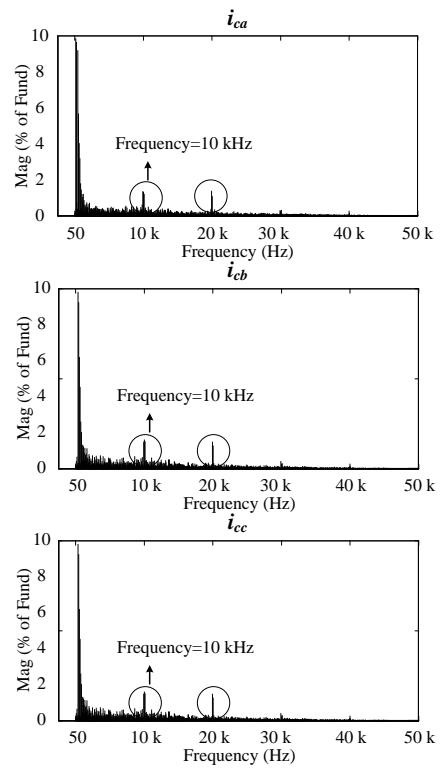

| 5.7  | Harmonic spectrum of FL-DSTATCOM and source currents for load-1 (a) DSTATCOM currents with conventional method (b) DSTATCOM currents with proposed method, and (c) Source currents with proposed method. . . . . | 104 |

| 5.8  | Voltages and currents of the system during higher THD loads. . . . .                                                                                                                                             | 105 |

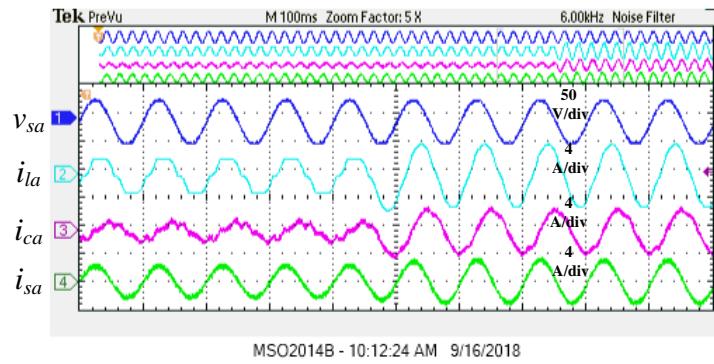

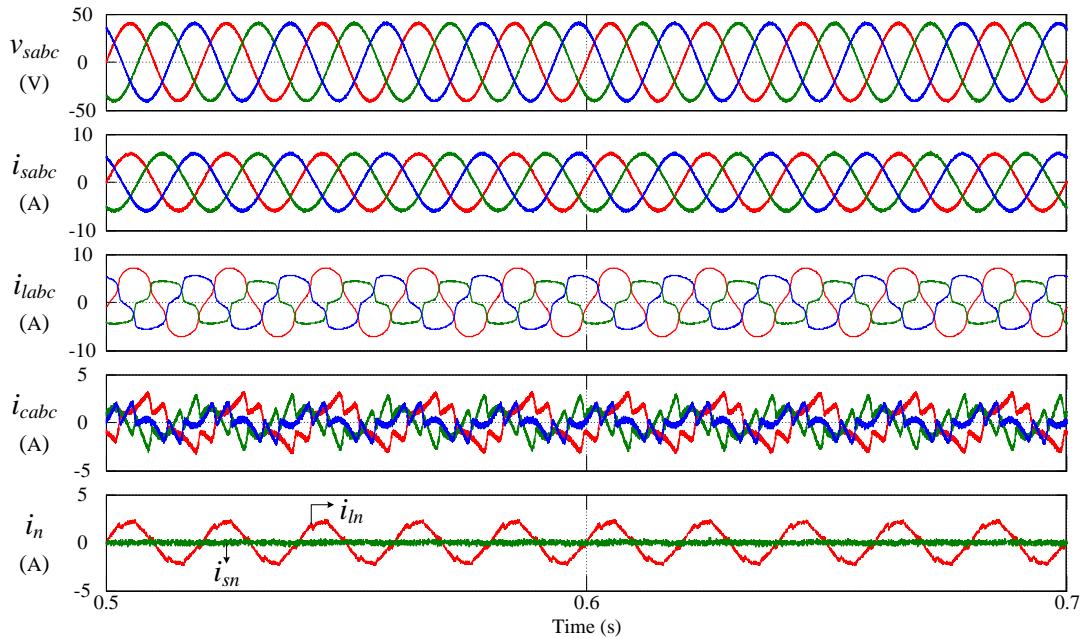

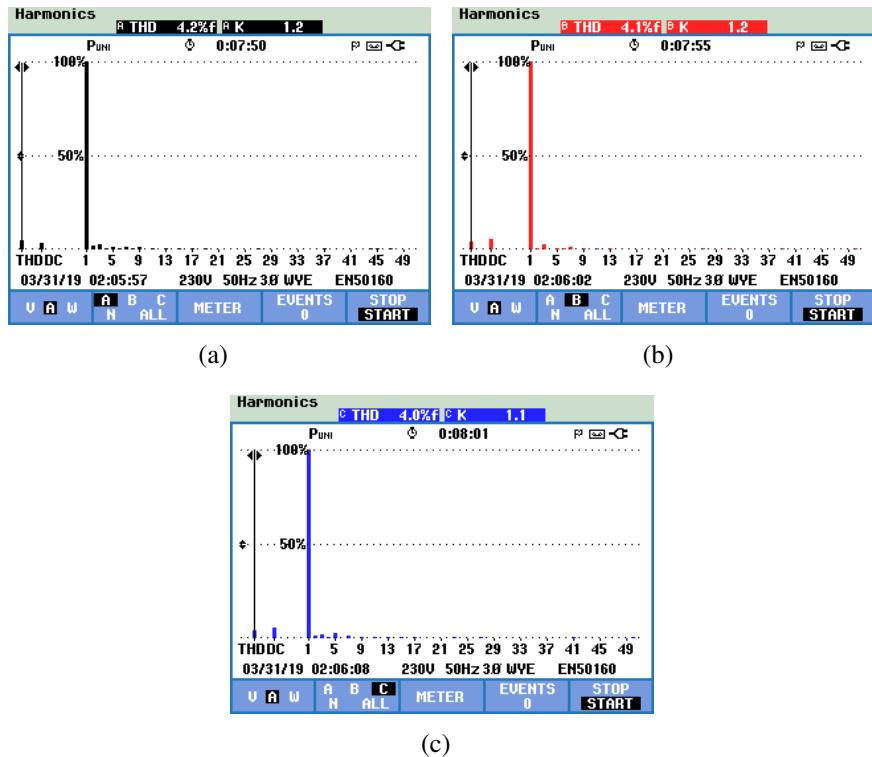

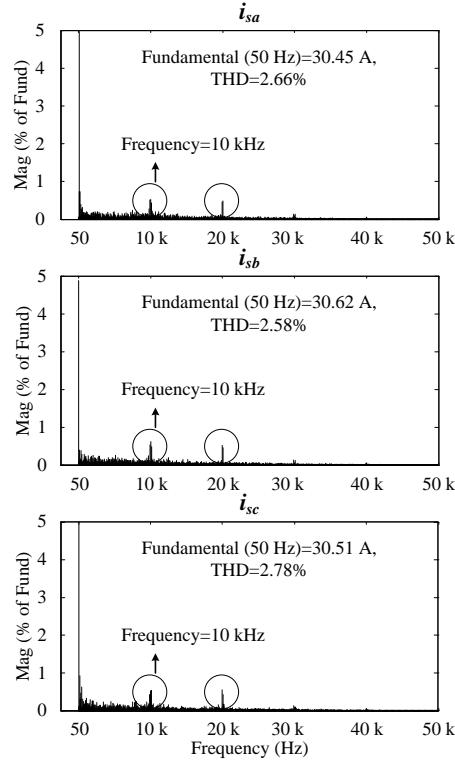

| 5.9  | Various parameters of the distribution system (a) PCC voltages ( $v_{sabc}$ ) (b) Load currents ( $i_{labc}$ ) (c) Source currents ( $i_{sabc}$ ), and (d) DSTATCOM currents ( $i_{cabc}$ ). . . . .             | 108 |

| 5.10 | $v_{sa}$ and $i_{sa}$ after compensation with FL-DSTATCOM. . . . .                                                                                                                                               | 109 |

| 5.11 | Harmonic spectrum of FL-DSTATCOM currents (a) $i_{ca}$ (b) $i_{cb}$ , and (c) $i_{cc}$ . . . . .                                                                                                                 | 109 |

| 5.12 | Harmonic spectrum of source currents (a) $i_{sa}$ (b) $i_{sb}$ , and (c) $i_{sc}$ . . . . .                                                                                                                      | 110 |

| 6.1  | (a) Schematic diagram of TPFS DSATCOM connected distribution system (b) FSSC topology, and (c) FSOC topology. . . . .                                                                                            | 114 |

| 6.2  | Connection diagram and phasor diagram of (a) Zigzag transformer, and (b) T-connected transformer. . . . .                                                                                                        | 116 |

|      |                                                                                                                                                  |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3  | Generation of gate pulses using instantaneous symmetrical component theory (ISCT) . . . . .                                                      | 117 |

| 6.4  | Zero sequence equivalent circuit of special transformer connected distribution system. . . . .                                                   | 119 |

| 6.5  | FSOC topology with zigzag transformer. . . . .                                                                                                   | 121 |

| 6.6  | FSOC topology with T-connected transformer. . . . .                                                                                              | 122 |

| 6.7  | FSSC topology with zigzag transformer. . . . .                                                                                                   | 123 |

| 6.8  | FSSC topology with T-connected transformer. . . . .                                                                                              | 124 |

| 6.9  | Photograph of complete experimental setup. . . . .                                                                                               | 129 |

| 6.10 | Experimental results of FSOC with (a) Zigzag transformer, and (b) T-connected transformer. . . . .                                               | 130 |

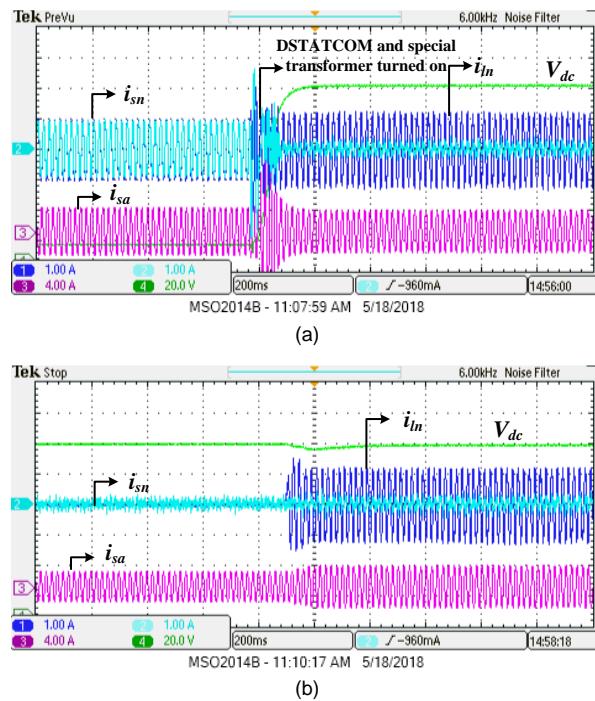

| 6.11 | Variation of neutral currents and dc link voltage (a) Before and after connecting DSTATCOM, and (b) During balanced and unbalanced load. . . . . | 130 |

| 6.12 | Experimental results of FSSC with (a) Zigzag transformer, and (b) T-connected transformer. . . . .                                               | 131 |

| A.1  | Phasor form of representing in-phase and quadrature unit vectors. . . . .                                                                        | 137 |

## ABBREVIATIONS

|                    |                                                   |

|--------------------|---------------------------------------------------|

| <b>3DSVM</b>       | Three dimensional SVM                             |

| <b>3HB</b>         | Three H-Bridge                                    |

| <b>3P3W</b>        | Three-Phase Three-Wire                            |

| <b>3P4W</b>        | Three-Phase Four-Wire                             |

| <b>AC</b>          | Alternating Current                               |

| <b>APF</b>         | Active Power Filter                               |

| <b>CCM</b>         | Current Control Mode                              |

| <b>CPD</b>         | Custom Power Device                               |

| <b>CSI</b>         | Current Source Inverter                           |

| <b>DC</b>          | Direct Current                                    |

| <b>DSTATCOM</b>    | Distribution Static Compensator                   |

| <b>FACTS</b>       | Flexible AC Transmission Devices                  |

| <b>FL-DSTATCOM</b> | Four Leg DSTATCOM                                 |

| <b>FSOC</b>        | Four-Switch One-Capacitor                         |

| <b>FSSC</b>        | Four-Switch Split-Capacitor                       |

| <b>HC</b>          | Hysteresis Controller                             |

| <b>HVDC</b>        | High Voltage Direct Current                       |

| <b>IEC</b>         | International Electrotechnical Commission         |

| <b>IEEE</b>        | Institute of Electrical and Electronics Engineers |

| <b>IGBT</b>        | Insulated Gate Bipolar Transistor                 |

| <b>IRPT</b>        | Instantaneous Reactive Power Theory               |

| <b>ISCT</b>        | Instantaneous Symmetrical Component Theory        |

| <b>MCDM</b>        | Multi-Criteria Decision Making                    |

| <b>MPC</b>         | Model Predictive Control                          |

| <b>PCC</b>         | Point of Common Coupling                          |

| <b>PI</b>          | Proportional Integral                             |

| <b>PLL</b>         | Phase Locked Loop                                 |

| <b>PQ</b>          | Power Quality                                     |

|             |                             |

|-------------|-----------------------------|

| <b>PWM</b>  | Pulse Width Modulation      |

| <b>RMS</b>  | Root Mean Square            |

| <b>SRF</b>  | Synchronous Reference Frame |

| <b>SSB</b>  | Solid State Breaker         |

| <b>SSCL</b> | Solid State Current Limiter |

| <b>SSTS</b> | Solid State Transfer Switch |

| <b>SVM</b>  | Space Vector Modulation     |

| <b>THD</b>  | Total Harmonic Distortion   |

| <b>TPFL</b> | Three-Phase Four Leg        |

| <b>TPFS</b> | Three-Phase Four-Switch     |

| <b>TPSC</b> | Three-Phase Split-Capacitor |

| <b>UCC</b>  | Unit Capacitor Constant     |

| <b>UTT</b>  | Unit Template Technique     |

| <b>VA</b>   | Volt-Ampere                 |

| <b>VAR</b>  | Volt Ampere Reactive        |

| <b>VCM</b>  | Voltage Control Mode        |

| <b>VSI</b>  | Voltage Source Inverter     |

## NOTATIONS

|              |                                                      |

|--------------|------------------------------------------------------|

| $\lambda$    | Weighting factor                                     |

| $\Delta I$   | Acceptable current limit                             |

| $\omega$     | Fundamental frequency of the supply voltage in rad/s |

| $\theta$     | Angle between voltage and current                    |

| $C$          | Cost function                                        |

| $C_{dc}$     | DC-link capacitance                                  |

| $f$          | Fundamental supply frequency                         |

| $f_{sw,max}$ | Maximum switching frequency                          |

| $f_{sw}$     | Switching frequency                                  |

| $G$          | Conductance factor                                   |

| $h$          | Hysteresis band                                      |

| $i_c^*$      | Reference rms filter current                         |

| $i_c$        | Instantaneous filter or DSTATCOM current             |

| $I_c$        | rms filter current                                   |

| $i_{cn}$     | Instantaneous compensator side neutral current       |

| $I_{dc}$     | DC-link current for CSI                              |

| $i_l$        | Instantaneous load current                           |

| $i_{ln}$     | Instantaneous load neutral current                   |

| $i_p$        | Active current component of load                     |

| $i_q$        | Reactive current component of load                   |

| $i_s$        | Instantaneous source current                         |

| $I_s$        | rms source current                                   |

| $i_{sn}$     | Instantaneous source side neutral current            |

| $I_{spm}^*$  | Peak value of reference source current               |

| $I_l$        | rms load current                                     |

| $L_{dc}$     | DC-link inductance for CSI                           |

| $L_s$        | Equivalent inductance of feeder                      |

| $L_f$        | Interfacing inductance                               |

|                        |                                                      |

|------------------------|------------------------------------------------------|

| $m$                    | Amplitude modulation index                           |

| $n$                    | Number of cycles with transient operation            |

| $P_{lavg}$             | Average real or active power of load                 |

| $Q_{f,max}$            | Maximum DSTATCOM reactive power                      |

| $R$                    | Regret measure                                       |

| $R_s$                  | Equivalent resistance of feeder                      |

| $R_f$                  | Internal resistance of Interfacing inductance        |

| $S$                    | Utility measure                                      |

| $S_1$                  | Upper switch of inverter leg connected to phase- $a$ |

| $S_2$                  | Lower switch of inverter leg connected to phase- $a$ |

| $S_3$                  | Upper switch of inverter leg connected to phase- $b$ |

| $S_4$                  | Lower switch of inverter leg connected to phase- $b$ |

| $S_5$                  | Upper switch of inverter leg connected to phase- $c$ |

| $S_6$                  | Lower switch of inverter leg connected to phase- $c$ |

| $S_7$                  | Upper switch of inverter leg connected to neutral    |

| $S_8$                  | Lower switch of inverter leg connected to neutral    |

| $T$                    | Fundamental time period                              |

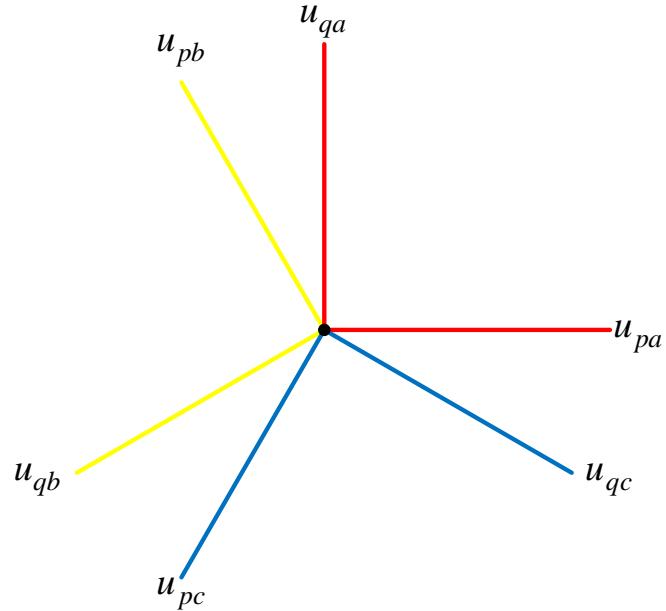

| $u_p$                  | In-phase unit vector                                 |

| $u_q$                  | Quadrature unit vector                               |

| $V_{dc}^*, V_{dc,ref}$ | Reference dc-link voltage                            |

| $v_c$                  | Inverter output voltage                              |

| $V_{dc}$               | DC-link voltage                                      |

| $v_{inv}$              | Instantaneous inverter or converter ac side voltage  |

| $v_s$                  | Instantaneous source voltage                         |

| $X$                    | kVA rating of inverter                               |

# CHAPTER 1

## Introduction

The role of the alternating current (ac) distribution system is to deliver the generated electric power to industrial, commercial and residential load centers. Distribution system has always been susceptible to problems regarding reactive power and unbalance from the very beginning. Continuous research in the area of power semiconductor devices has motivated researchers, to use them in applications such as adjustable speed drives, battery chargers, home appliances and electric vehicles [1], [2]. However, these power electronic equipment draw, non-linear currents which affect the distribution system as well as other loads connected to the system. In olden days, power outage is the only power quality issue known to most of the consumers. However, increased awareness among customers, has led them demanding manufacturers to develop electric equipment, which are susceptible to override power quality disturbances. **Similarly, utilities must supply good quality of power to consumers for satisfactory operation of equipment.** In general, power quality is the set of boundaries that allows a system to work in its intended manner without any significant loss in its performance [3]. It is necessary to maintain quality of power at various stages in power sector such as generation, transmission and distribution. **Especially, it is very important at the utilization level, because the end user gets effected, if there are any issues in the quality of power.**

### 1.1 Classification of power quality problems and their causes

The primary reasons for power quality issues are equipment failure, lightning, faults, notches, voltage distortions, operation of non-linear and unbalanced loads [4]. In general, power quality is quantified as current, voltage and frequency variations in the supply, which results in either mal-operation or failure of customer equipment. Voltage sags, swells, surge, notches, flicker, fluctuations, unbalance and harmonics are voltage related power quality issues that occur in the distribution system. Similarly, current

related issues are poor power factor, harmonic currents, unbalanced currents and large neutral current because of the presence of non-linear and unbalanced loads. The important reasons for power quality issues are mentioned below:

- The presence of arc furnaces, adjustable speed drives, uninterrupted power supplies and switch mode power supplies in the vicinity of consumers.

- Natural reasons such as lightning phenomena, flash-over and failure of electrical equipment.

- Operation of large capacitor banks and transformers.

- Distribution of single-phase loads with unequal rating.

- Frequent turn on and off of large motors and fluctuating loads.

- Operation of non-linear, unbalanced and reactive loads.

A brief explanation of major power quality issues are explained here.

## **Transients**

Transient is defined as the part of change in a variable that disappears during transition from one operating condition to other operating condition. Transients can be further classified as impulsive and oscillatory. Impulsive transient is a sudden non-power frequency change in the steady-state condition of voltage, current or both in either positive or negative direction. However, oscillatory transient is change in both positive and negative directions.

## **Long-duration voltage variations**

It is defined as the root mean square (rms) deviations at power frequencies for more than 1 minute. Long-duration voltage variations are further classified as over voltages, under voltages, and sustained interruptions. An increase in ac rms voltage to greater than 110 percent at power frequency for longer than 1 minute is defined as an over voltage. Energization of capacitor banks or switching off a large loads will create over voltages. At the same time, under voltage is defined as decrease in rms voltage to

90 percent at power frequency for more than 1 minute. The reason behind the under voltage is exactly opposite to over voltage. When the supply voltage is zero for a period of more than 1 minute it is named as sustained interruption.

### **Short-duration voltage variations**

Fault conditions, higher starting currents due to turning and on of heavier loads and loose connections in power wiring are leading to short-duration voltage variations. They are further classified as sags, swells and interruptions. A sag is defined as the decrease in rms voltage or current to 0.1 to 0.9 per unit (pu) for a duration of 0.5 cycles to 1 minute. Similarly, swell is defined as an increase in rms voltage or current to 1.1 pu to 1.8 pu for a duration of 0.5 cycle to 1 minute. Finally, an interruption occurs when the load current or supply voltage decreases to less than 0.1 pu for a period of less than 1 minute.

### **Voltage imbalance**

It is also named as voltage unbalance and it is defined as the ratio of maximum deviation from the average of three-phase voltages or currents to the average of three-phase voltages or currents. Voltage imbalance is always expressed in percent. It is also defined as, the ratio of either negative or positive sequence component to the positive sequence component. Presence of single-phase loads in three-phase system are the primary reason for voltage imbalance.

### **Waveform distortion**

At power frequency, a steady state deviation from an ideal sine wave is defined as waveform distortion. There are five different types of waveform distortions and they are dc offset, harmonics, inter harmonics, notching and noise.

## 1.2 Effects of power quality problems on end users

The problems in power quality affect consumers, manufacturers and utilities, which can lead to production damage, wastage of raw material, missing data and equipment failure. Out of all the causes of power quality problems, operation of non-linear, unbalanced and reactive loads are considered to be one of the most significant reasons for power quality problems in modern distribution systems [4], [5]. [Therefore, the scope of this thesis is limited to compensation of current related power quality issues only.](#) These power quality issues lead to several problems in the distribution system such as:

- Increased losses in the system due to the requirement of large amount of reactive power.

- Excessive neutral current which require large size of conductor.

- Harmonic currents leading to harmonic torques in electric machines.

- Occurrence of resonance in inductor and capacitor banks due to the presence of harmonics.

- Negative and zero sequence currents in the distribution system.

- Vibrations, noise, over heating, derating of electric cables and causes dielectric breakdown.

- Mal-function of circuit breakers and relays.

A brief description of current related power quality issues are discussed below.

### 1.2.1 Reactive power burden

Reactive power burden on distribution systems is due to the operation of loads that draw high reactive power. Reactive power is a concept used by engineers to describe the background energy movement in an ac system arising from the production of electric and magnetic fields. These fields store energy which is exchanged in each ac cycle. Devices which store energy by virtue of a magnetic field produced by flow of current

are said to absorb reactive power; while those which store energy by virtue of electric fields are said to generate reactive power [6]. Volt-ampere reactive (VAR) is a unit used to measure reactive power in an ac electric power system. Reactive power is required to maintain the voltage to deliver active power through transmission lines and distribution feeders. Electric machines require reactive power for successful operation. When enough reactive power is not available, it is not possible to push the real power demanded by the loads through the lines. The satisfactory operation of customer appliances and industries require reactive power and it has to be supplied by the source. Motors, tap changing transformers, choke coils, inductive loads, phase controlled rectifiers are some of the examples of reactive loads in the distribution system [6]. This reactive power requirement will further reduce the power factor of the system. The increasing demand for reactive power or poor power factor causes,

- Increase in current rating of the system to supply the same amount of active power.

- Large copper losses which further reduce the efficiency of the system.

- Poor Voltage regulation.

- Necessity to increase conductor size which increases the cost.

- Requirement of large kilo-volt-ampere (kVA) rating equipment such as alternators and transformers.

### **1.2.2 Influence of harmonic currents**

Harmonic currents are the unwanted frequency components superimposed on the fundamental current waveform. The main sources of harmonic currents, before the deployment of power electronic devices in the equipment are fluorescent lamps and electric arc furnaces. Similarly transformers and electric machines produce harmonic currents in low proportion [7]. In recent times, the rapid growth in the area of power electronic devices increased the amount of harmonic currents. The important sources of harmonic currents are adjustable speed drives using converters, ac voltage controllers, cyclo-converters, switched mode power supplies, high voltage direct current (HVDC) transmission, static VAR compensators and phase controlled rectifiers. The effects of harmonic currents are:

- Voltage waveform distortion.

- Series and parallel resonance problem.

- Requirement of capacitor banks for power factor correction.

- Over heating of electrical machines because of harmonic losses.

- Development of harmonic torques in electrical motors.

- The increment in the root mean square (rms) currents, causes additional power loss in the distribution network.

### 1.2.3 Influence of excess neutral current

In electrical power system, electricity is generated, transmitted and distributed mostly as a three-phase three-wire system (3P3W) or sometimes as three-phase four-wire (3P4W) system. In the distribution system, most of the consumer loads are single-phase with unequal rating [8]. The unequal distribution of single-phase loads on three phase distribution system will lead to unbalanced source currents, which further increase the amount of neutral current. Sometimes, the amount of neutral current flowing through the neutral conductor will be more than the line current [9]. In a balanced system, the use of non-linear loads will allow the flow of zero sequence currents which further increase the amount of neutral current [9]. Some of the sources of neutral currents are personal computers, printers and single-phase power supplies. The effects of higher neutral current are excessive power loss in neutral conductor, common mode noise, over loading of transformers and distribution feeders, wiring failure and flat topping of voltage waveform.

## 1.3 Power quality standards

There are several organizations on the national and international stages working closely with equipment manufacturers, research organizations and engineers to come up with standards governing guidelines, recommended practices, and harmonic limits [7]. The primary objective of the standards is to decide whether the amount of distortion will

affect the performance or not and they will provide a common ground for all involved parties to work together to ensure compatibility between the end-user equipment and the system. Therefore, to quantify these problems some standards have been developed by various institutes and organizations, so that, consumers, manufacturers and industries are required to follow standards to maintain acceptable level of power quality. Along with these standards, some measuring devices and measurement methodologies have been developed to quantify the level of power quality and its causes. The available standards are, IEEE Standard 519-1992, IEEE standard 1159-1995, IEC 61000-2-2, IEC 61000-2-4, and IEC 61000-3-2 and so on [10], [11]. IEEE 5191992 standard, limits the amount of current harmonics injected by a user at the point of common coupling (PCC). For example, the IEEE 5191992 standard recommends a limit of 5% total harmonic distortion (THD) in the current at the PCC in a weak system.

## 1.4 Solutions to power quality issues

Low quality power affects the customers in many ways. The lack of quality power will cause loss of production, damage of equipment or appliances or can even be detrimental to human health. Therefore, it is very important to maintain a high standard of power quality. There are sets of conventional solutions to the power quality problems, which have existed for a long time. [However these conventional solutions use passive elements and do not always respond correctly with ever changing power systems.](#) The increased power capabilities, ease of control, and reduced costs of modern semiconductor devices have made power electronic converters affordable in a large number of applications. New flexible solutions to many power quality problems have become possible with the aid of these power electronic converters. Therefore, from past few decades, several mitigation techniques have been evolved to improve power quality, which includes,

- Passive power filters.

- Active power filters such as custom power devices.

- Hybrid power filters.

### 1.4.1 Passive power filters

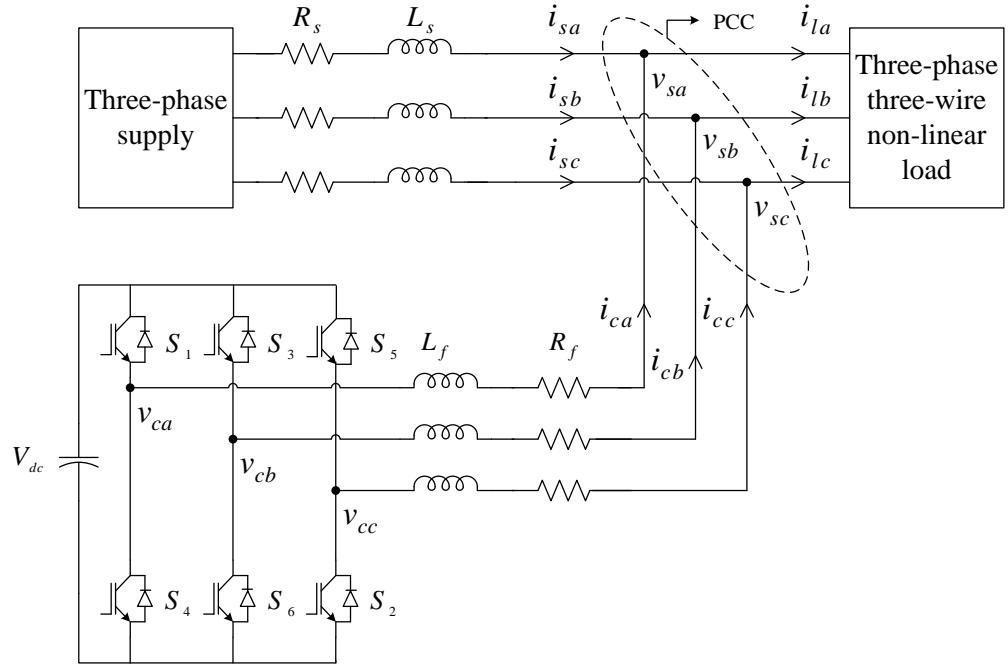

As non-linear loads draw harmonic and reactive currents from the ac source for their satisfactory operation, these current components will reduce power factor of the system thereby reducing efficiency. These are also disturbing the other customers, protecting devices connected to the same system. Normally, harmonic currents are reduced by passive power filters and especially, when capacitors are connected to supply the required reactive power, which further improves the power factor [7]. These passive power filters are a combination of passive elements such as inductors, capacitors and resistors. Passive power filters are classified as series, shunt and hybrid power filters [12], [13]. **Series filters are connected in series with non-linear loads which provides high impedance for harmonic currents, which does not allow them to enter into the supply system.** Shunt filters are connected in shunt with harmonic loads, and provide low impedance path for the harmonic currents so that it will not enter into supply. Finally, hybrid filters are a combination of series and shunt filters.

These passive power filters can be sub classified as tuned and damped filters. Tuned filter act like a high pass filter in shunt connection and high block filter in series connection. Similarly, damped filters behave like a low pass filter in shunt connection and low block filter in series connection [7]. Some of the examples of tuned and damped filters are shown in Fig. 1.1 and Fig. 1.2. In these two figures, resistance, inductance and capacitance of the filter are represented as  $R$ ,  $L$ , and  $C$ .

Fig. 1.1 Series passive power filters (a) Tuned filter, and (b) Damped filter.

The advantages of passive power filters are

- Implementation is simple.

- There are no switching and conduction losses which actually improve the efficiency.

Fig. 1.2 Shunt passive power filters (a) Tuned filter, and (b) Damped filter.

- Improving voltage profile by supplying reactive power.

However, these passive filters have several limitations such as

- These filters are fixed once installed.

- Large size which further increases the cost.

- **The changes in operating and weather conditions will lead to detuning of filter and also increases the level of distortion.**

- Loss of missing or damaged elements leads to change in resonant frequency.

- The presence of dc components will saturate filter reactors.

The rapid growth in the power electronic devices encouraging the researchers to develop power electronic based compensating devices to overcome the limitations of passive power filters and they are named as active power filters.

### 1.4.2 Active power filters

The continuous increase in problems due to harmonic, reactive currents and the disadvantages of passive power filters, have attracted the attention of researchers to develop adjustable and dynamic solutions to mitigate power quality problems using power electronic devices and they are named as active power filters [14]–[16]. These active power

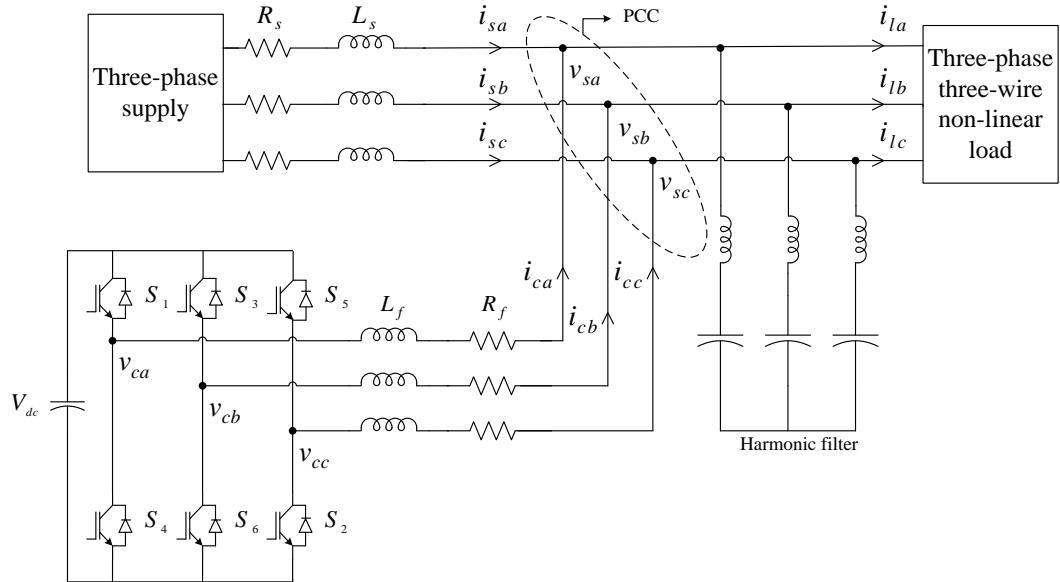

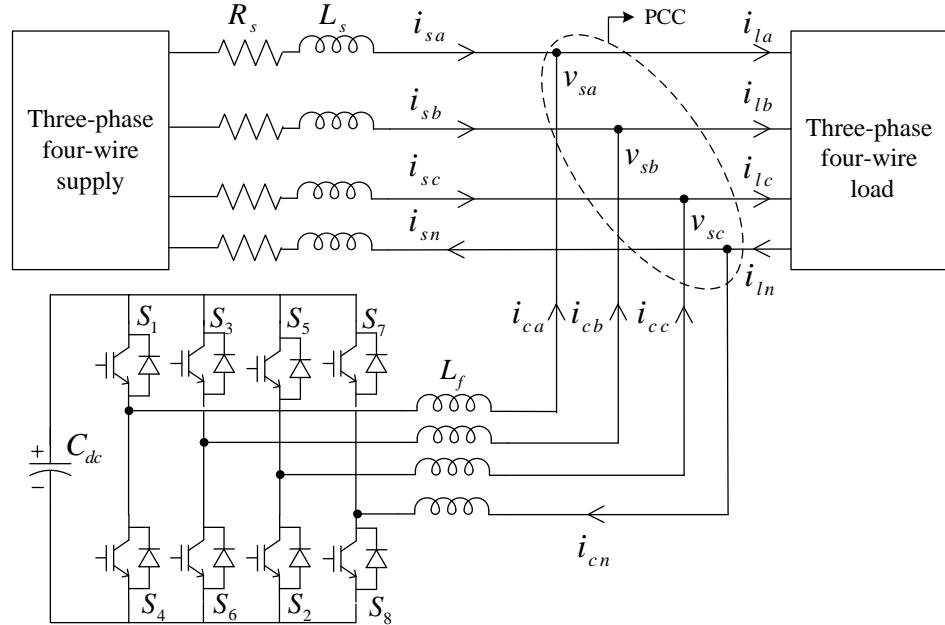

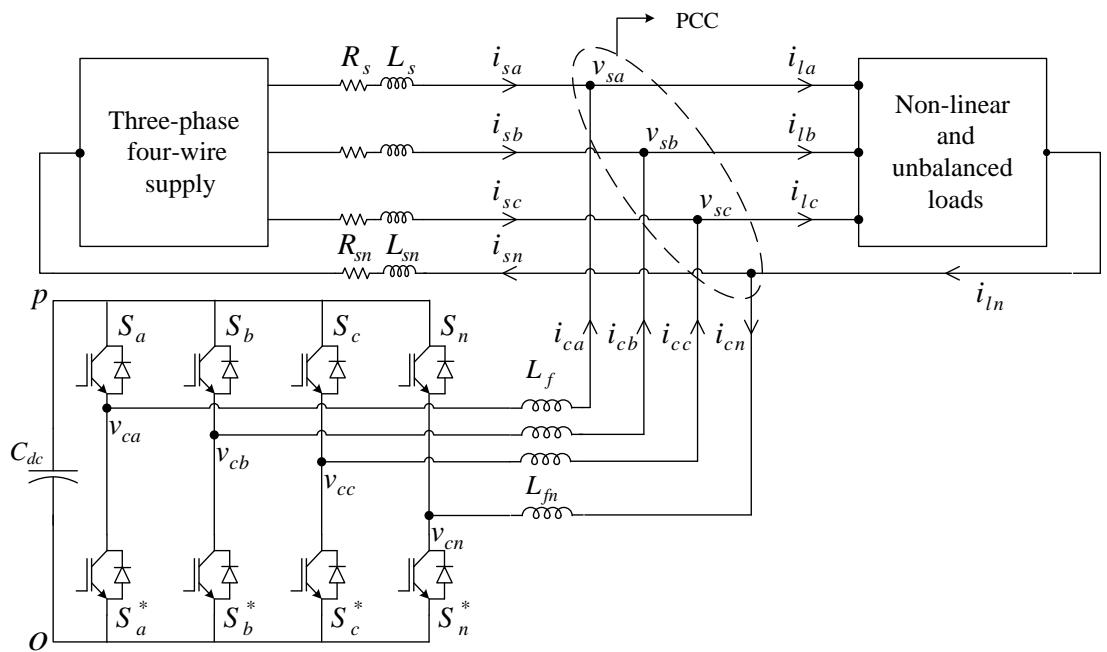

filters are classified as series, shunt and combination of series-shunt active power filters, depending on the type of connection. Series active power filters are designed to compensate the voltage related power quality issues. Shunt active power filters are used to compensate the current related power quality issues such as reactive power burden, harmonic elimination, load balancing, and elimination of excessive neutral current. After the evolution of insulated gate bipolar transistors (IGBT), these active power filters gain much more attention because of their easy implementation and control. With the continuous evolution of active power filters, the researchers are widened their compensation capabilities and formed a new group of compensating devices. These devices are named as custom power devices (CPD). The available CPDs are, distribution static compensator (DSTATCOM), dynamic voltage restorer (DVR) and unified power quality conditioner (UPQC). Among them, DSTATCOM is used to compensate current and voltage related power quality issues. The schematic diagram of a DSTATCOM connected distribution system is shown in Fig. 1.3. In this figure,  $i_{sa}$ ,  $i_{sb}$ , and  $i_{sc}$  represents the source currents.  $i_{la}$ ,  $i_{lb}$ , and  $i_{lc}$  represents the load currents.  $i_{ca}$ ,  $i_{cb}$ , and  $i_{cc}$  represents the filter or compensator or DSTATCOM currents.  $v_{sa}$ ,  $v_{sb}$ , and  $v_{sc}$  represents the voltages at PCC.  $L_f$  is interfacing inductance,  $R_f$  is internal resistance of  $L_f$ , source inductance and resistance are represented with  $L_s$  and  $R_s$ .  $S_1$ – $S_6$  are the inverter switches. The operation of DSTATCOM and active power filter are identical to each other.

Fig. 1.3 Schematic diagram of DSTATCOM connected distribution system.

### 1.4.3 Hybrid power filters

Hybrid power filter is a combination of passive and active power filters. The ratings of the active filters are reduced by adding passive components to them and converting them as hybrid power filters [17]–[19]. These filters are cost effective solutions for some of the non-linear loads. The schematic diagram of the hybrid filter is shown in Fig. 1.4. The control and design complexity of hybrid power filters have limited its applications.

Fig. 1.4 Schematic diagram of hybrid filter connected distribution system.

## 1.5 Objectives

DSTATCOM is a shunt connected custom power device (CPD) which is used to compensate current and voltage related power quality issues in the distribution system. The performance of any DSTATCOM depends on its topology, reference current generation technique and control algorithm to generate switching pulses for the inverter. Based on literature of active power filters and their control algorithms [21]–[59], the following limitations are observed and motivated to consider them as objectives of this research work.

1. Conventional three-phase split-capacitor (TPSC) DSTATCOM has the limitation of voltage divergence of dc link capacitors during the compensation of unbalance.

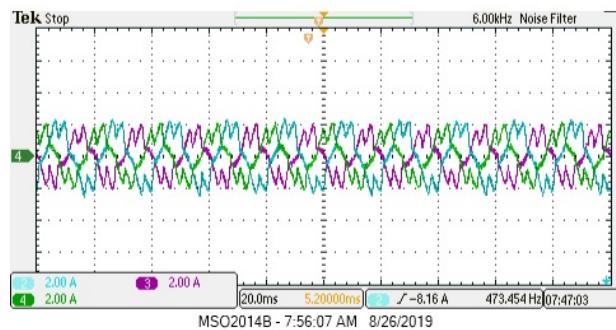

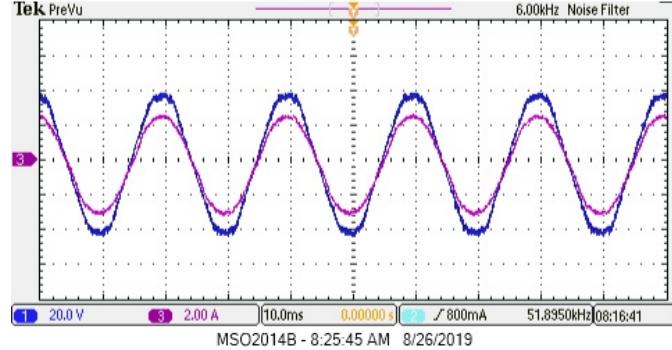

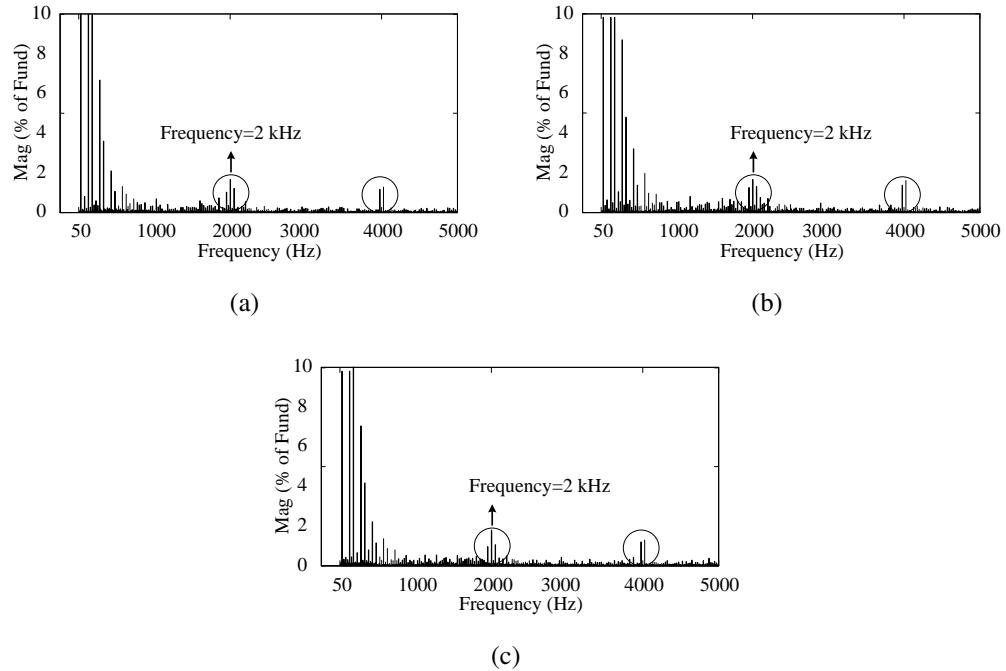

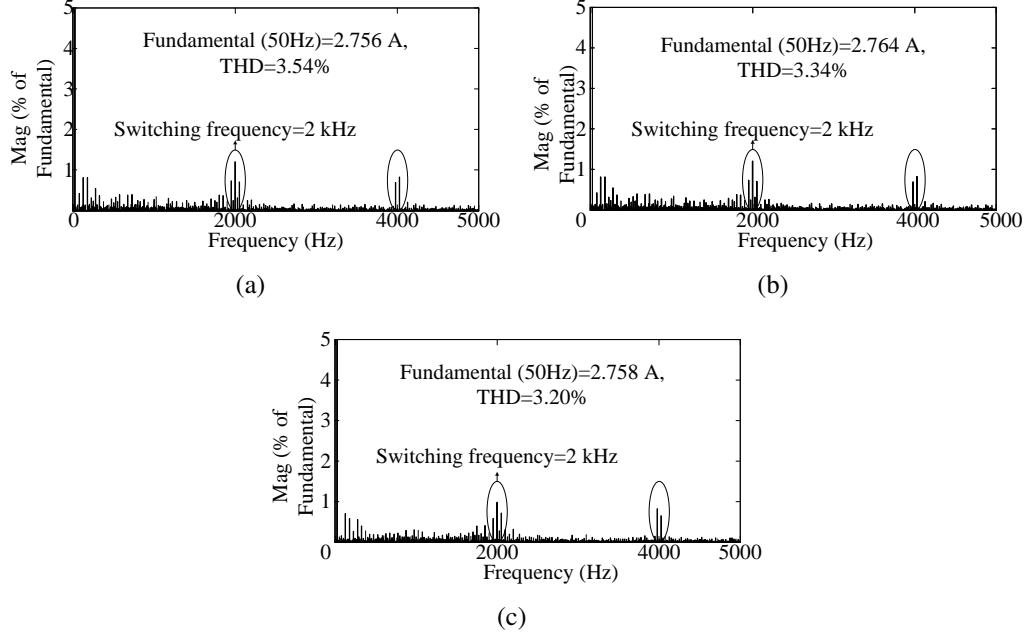

anced load currents [34], [35]. In literature, switching of inverter is adjusted to overcome this limitation; however, it further increases the control complexity. In recent years, model predictive control (MPC) methods have been used in many research areas because of its easy implementation, providing good dynamic and steady-state response, and constraints can be easily added to the cost function [54]–[57]. However, it has the limitation of higher switching frequency. To alleviate these problems, one constraint is to suppress voltage divergence and the other is to reduce the switching frequency is included in the cost function using weighting factors. Optimal selection of switching state for minimization of a multi-constraint cost function depends on the weighting factor; however, its tuning is a challenging task. Therefore, in this objective, the simplification of weighting factor tuning is achieved using VlseKriterijumska Optimizacija I Kompromisno Resenje (VIKOR) method and it further selects the optimal switching to improve power quality, reduce voltage divergence, reduce switching frequency and simplification of weighting factor tuning.