# Reduced carrier PWM scheme with unified logical expressions for reduced switch count multilevel inverters

Hari Priya Vemuganti<sup>1</sup>, Dharmavarapu Sreenivasarao<sup>1</sup>✉, Ganjikunta Siva Kumar<sup>1</sup>, Appikonda Sai Spandana<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, National Institute of Technology, Warangal, India

<sup>2</sup>ALSTOM Transport India Limited, India

✉ E-mail: luckysrinu@gmail.com

**Abstract:** The significant reduction in switch count of symmetrical/asymmetrical reduced switch count multilevel inverters (RSC-MLI) topologies has modified the operation of inverter such that the conventional carrier-based pulse width modulation (PWM) schemes such as level-shifted PWM and phase-shifted PWM can no more realise them. To control these RSC-MLI topologies, reduced carrier PWM schemes with modified switching logic gained more prominence. These schemes involve suitable logical expressions to realise the switching states of the inverter. However, these logical expressions vary with topological arrangement and number of levels. Moreover, these schemes produce high total harmonic distortion (THD) in line-voltages. Therefore, to improve the line-voltage THD and generalise the switching logic, a modified reduced carrier PWM scheme with unified logical expressions is presented here. The proposed PWM scheme is directly valid for any topology and can be easily scalable to any number of levels in the inverters. To validate the implementation of the proposed PWM to control any RSC-MLI, experimental studies of various asymmetrical RSC-MLI topologies with the proposed PWM scheme are carried out. Further, to verify the superiority of the proposed scheme in terms of THD, complexity, scalability, and computation burden, its performance is compared with carrier-based PWM schemes reported in the literature.

## 1 Introduction

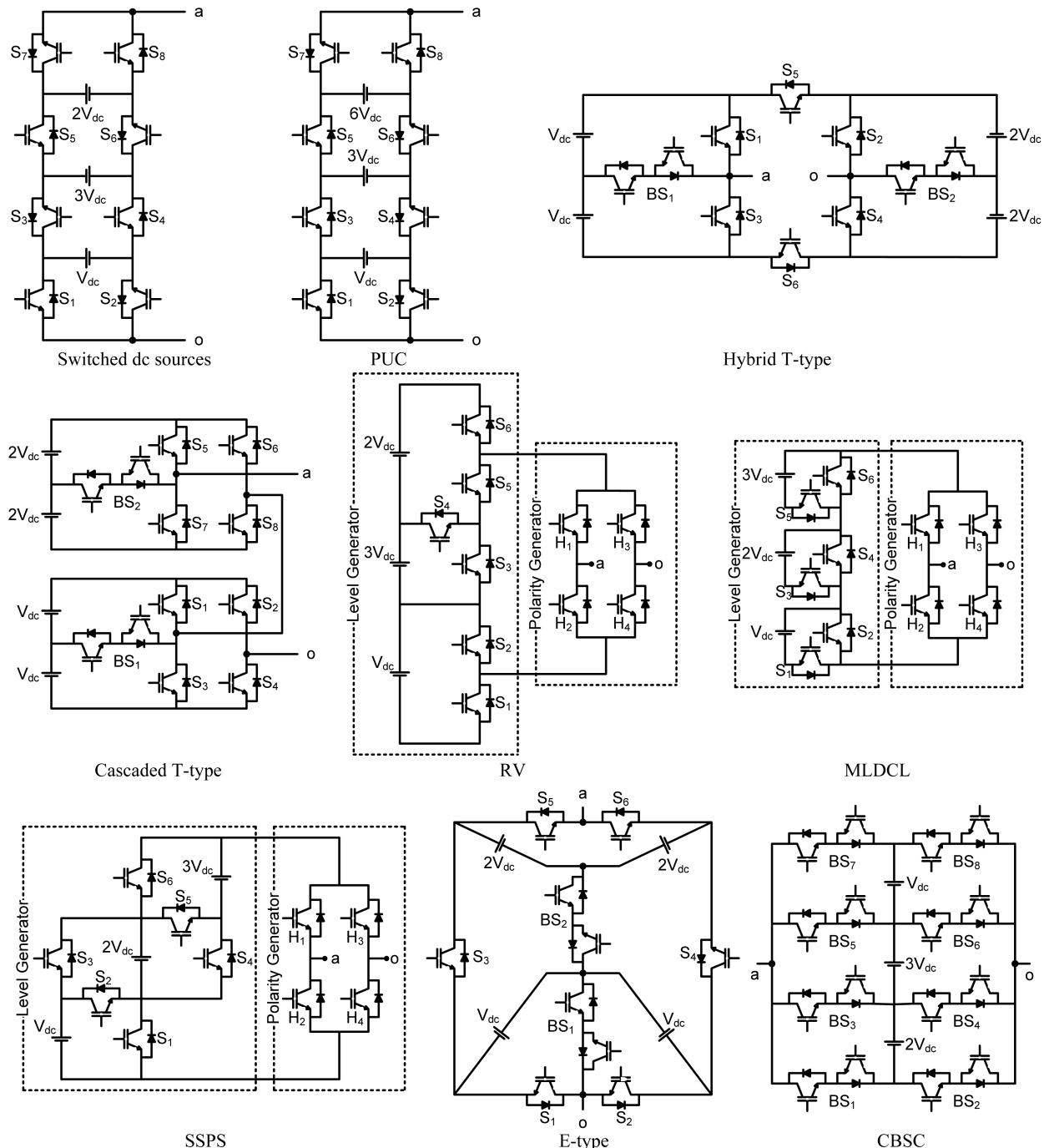

The demand for reducing the size of multilevel inverters (MLI) has led to a new domain of MLIs, named as reduced switch count (RSC) MLIs [1]. Depending on dc source voltage ratios, these RSC-MLIs are classified as symmetrical and asymmetrical. With asymmetrical dc source voltages, further reduction in switch count can be achieved. Several RSC-MLI topologies such as multilevel dc link (MLDCL) [2], packed U-cell (PUC) [3], cascaded bi-polar switched cells (CBSC) [4], reverse voltage (RV) [5], switched dc sources [6], basic unit MLI [7], envelope-type (E-type) [8], T-type [9–13], hybrid T-type [14, 15], series-connected switched sources (SCSS) [16], switched series parallel sources (SSPS) [17, 18], nested MLI [19], switched capacitor unit [20, 21], reduced cascaded [22–25], and various other topologies [26–28] are reported in the literature. Fig. 1 shows the circuit configuration of various single-phase 13-level asymmetrical RSC topologies such as switched dc sources, PUC, cascaded T-type, hybrid T-type, CBSC, SSPS, RV, MLDCL, and E-type.

Among the pulse width modulation (PWM) schemes reported for MLIs, carrier-based schemes such as level-shifted PWM (LSPWM) and phase-shifted PWM (PSPWM) are the simplest due to their easiness in implementation [29–31]. These PWM schemes can realise inverter switching states in which devices conducting for achieving lower levels remain in conduction at higher levels as well. This acted as a limitation of the conventional carrier-based schemes to realise RSC-MLIs, since these topologies has limited redundancies and possess the switching action where the lower level conduction devices may not remain in conduction at higher level.

In the literature, various modulation schemes are reported for controlling symmetrical and asymmetrical RSC-MLI configurations. Among them, hybrid PWM is one of the popular schemes for implementing asymmetrical cascaded topologies such as Cascade H-bridge [20, 22, 32]. This scheme can also be implemented to non-cascaded topologies such as SSPS by adding an additional H-bridge in each phase [17]. In this scheme, measurement or estimation of output voltage of the higher voltage

bridge/units is necessary, to derive the reference signal for the lower voltage bridge/units. Hence, any lag or errors in the estimation or measurement will impact the output voltage. PWM schemes such as selective harmonic elimination [8] and space vector [3, 19, 26, 28] are reported for E-type, PUC, nested cell, and various three-phase RSC topologies. These switching schemes can be generalised to higher levels, but requires elusive calculations to obtain switching instants.

Switching schemes using low-frequency carrier (50 or 100 Hz) with and without logical operators are reported for various RSC MLIs such as MLDCL, CBSC, basic unit MLI, T-type, and hybrid T-type [2, 4, 7, 12, 14, 15, 20, 28]. These low-frequency PWM schemes results in lower order harmonics and poor THD. To obtain better THD and reduce the complexity in implementation, various novel PWM schemes are reported. Multi-reference modulation scheme is one of such scheme reported for T-type, cascaded T-type, and few other cascaded topologies [11, 13, 23, 25]. This scheme can be applicable to any MLI with any number of levels, but this scheme results high THD in line-voltages [33]. Switching function PWM is the other popular scheme reported for PUC, switched dc sources, and hybrid T-type topologies [6, 16]. To obtain the switching pulses, this scheme develops a hybrid function using minimum and maximum limits of each carrier. Therefore, to realise these carrier constraints, controller requires numerous comparators, which increases the complexity at higher levels.

Reduced carrier PWM [5, 9, 10, 27] is the other popular PWM, which involves a unipolar modulating and level-shifted carrier signals. In this scheme, pulses are generated by directly comparing reference with its carriers and further operated with user-defined logical expressions to obtain desired switching pulses to control the inverter. However, these logical expressions vary with topological arrangement and number of phase-voltage levels. Further, this conventional reduced carrier arrangement results high THD in line-voltage [33]. Hence, an alternate modulating signal and reduced carrier arrangement is reported [33]. The switching logic of this scheme involves minimum and maximum constraints of each carrier to obtain desired operation. However, it is to be noted that

**Fig. 1** Thirteen-level RSC-MLI topologies for asymmetrical single-phase configurations

reduced carrier PWM schemes with generalised logical expressions are the simplest and much easier to implement compared to switching scheme involving carrier minimum and maximum constraints.

By reviewing the various modulations of RSC-MLI topologies, the following conclusions can be drawn

- Among the modulation schemes reported for RSC-MLIs, reduced carrier PWM scheme with logical expressions are the simplest. However, these logical expressions are not generalised and vary with inverter topology and number of levels.

- Conventional reduced carrier PWM scheme results degraded line THD performance, as its carrier arrangement is similar to LSPWM–opposite phase disposition (OPD) [33].

Hence, in this paper, a modified reduced carrier PWM scheme with generalised logical expressions is proposed, such that the proposed switching logic can control any RSC-MLI irrespective to

the voltage ratios and topological arrangement. To derive these unified logical expressions, limitations of conventional reduced carrier modulation scheme in controlling RSC-MLI topologies are analysed. To verify the efficiency of the proposed PWM scheme, its performance in controlling various 13-level asymmetrical RSC-MLI topologies is investigated. Further, to ensure the superior performance of the proposed scheme, a comprehensive experimental comparison with state of the art schemes reported in the literature is presented.

This paper is laid out as follows: Section 2 investigates the limitations of conventional reduced carrier modulation schemes and presents the necessity of unified logical expressions to realise RSC-MLI topologies. Section 3 presents the methodology of the proposed scheme and derivation of unified logical expressions. Experimental performance of the proposed scheme to various RSC topologies are discussed in Section 4.

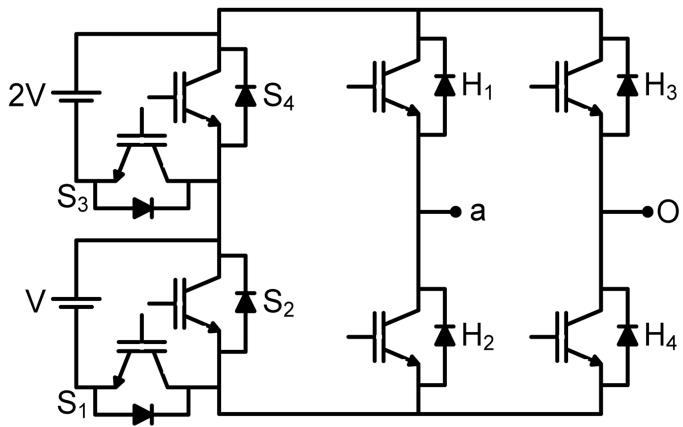

**Fig. 2** Seven-level single-phase configuration of RSC-MLI-based MLDCL

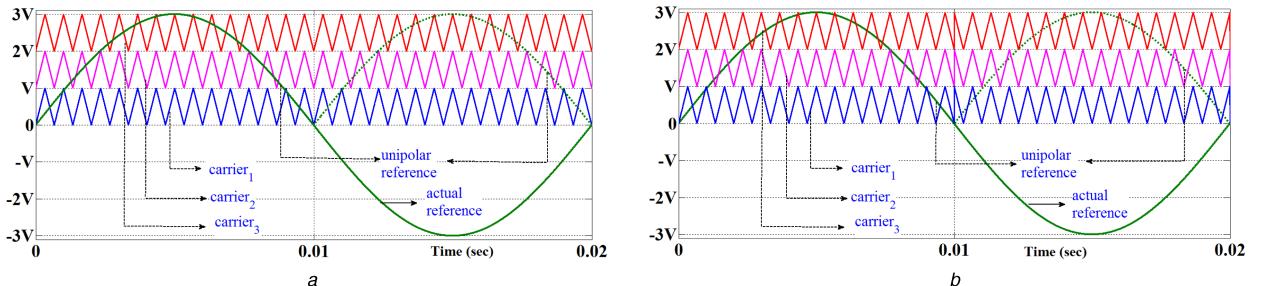

**Fig. 3** Reduced carrier PWM for seven-levels in phase-voltage

(a) Conventional reduced carrier arrangement, (b) alternative carrier arrangement

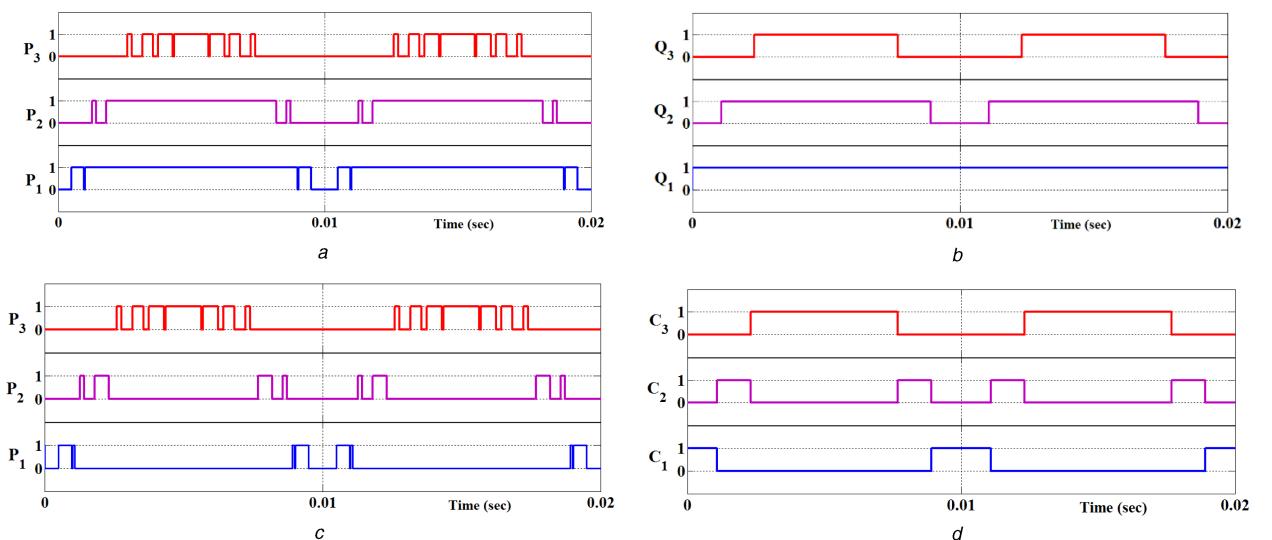

**Fig. 4** Switching pulses ( $P$ ) and conduction intervals ( $Q$  and  $C$ ) of seven-level reduced carrier PWM scheme:

(a) Overlapped switching pulses, (b) Overlapped conduction intervals ( $Q$ ), (c) Non-overlapped switching pulses, (d) Non-overlapped conduction interval ( $C$ )

## 2 Reduced carrier-based modulation schemes: limitations

Reduced carrier modulation schemes uses unipolar reference and  $(n-1)/2$  level-shifted carriers to obtain ‘ $n$ ’ levels in phase-voltage [5, 9, 10, 27]. Fig. 2 shows one of the RSC-MLI topologies for seven level. To control this inverter with reduced carrier modulation scheme, Fig. 3 shows two possible approaches for arranging the unipolar level-shifted carriers for obtaining seven-levels in phase-voltage.

Fig. 3a depicts the conventional reduced carrier arrangement. This type of reduced carrier PWM scheme results high THD in line-voltages as its carrier alignment is similar to LSPWM with OPD [29]. Hence to improve THD, an alternate carrier arrangement shown in Fig. 3b is presented in [33].

Fig. 4a depicts the switching pulses ( $P$ ) obtained from Fig. 3a, by comparing unipolar reference with carrier signals (conventional

switching logic). From Figs. 3a and 4a, it is observed that  $P_3$  is active when reference is greater than carrier<sub>3-min</sub> and is responsible for obtaining voltage band of 2 V to 3 V, if the reference is in between carrier<sub>3</sub> limits. Similarly,  $P_2$  and  $P_1$  are responsible for obtaining voltage bands V to 2 V and 0 to V, respectively. It is observed that when  $P_3$  is active, the remaining lower pulses  $P_2$  and  $P_1$  are high. This nature of switching pulses can be analysed by observing their conduction intervals ( $Q$ ) shown in Fig. 4b. This conduction interval show the duration over which each switching pulse is active and is defined in the below equation

$$Q_i = 1; \text{ reference} > \text{Carrier}_{i_{\min}} \quad (1)$$

$$Q_i = 0; \text{ else}$$

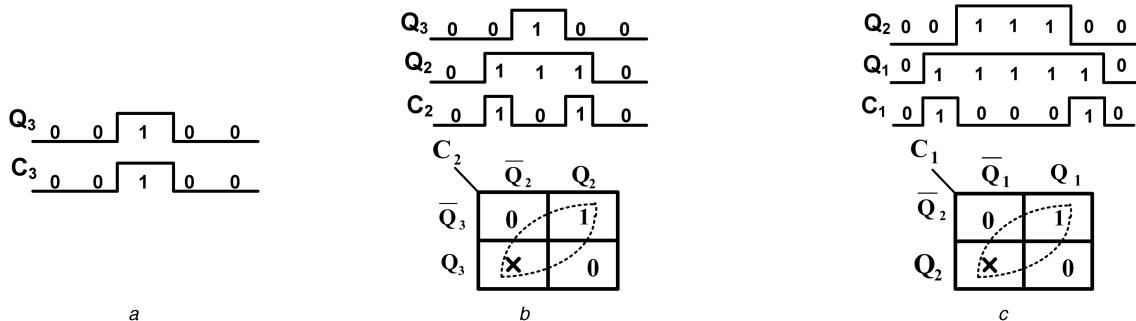

**Fig. 5** Mapping of overlapped conduction intervals ( $Q$ ) with non-overlapped conduction intervals ( $C$ ) and their associated K-maps

From Fig. 4b, the overlapped nature of these conduction intervals ( $Q$ ) can be clearly observed. Hence, applying these pulses directly to an inverter reflects that devices responsible for obtaining lower levels are remain in conduction at higher levels as well. However, this nature of switching cannot realise RSC-MLIs, as they possess the switching states where lower level conduction devices may not remain in conduction at higher levels [1]. Further with asymmetrical RSC-MLI topologies, these switching states turn more difficult to realise with conventional reduced carrier PWM scheme. This observation plays a vital role in proposing a modified switching logic to control RSC-MLIs.

Therefore, to control these asymmetrical RSC-MLI topologies with carrier-based PWM schemes, modifications in the conventional switching scheme are required. One simplest possible approach is to control these RSC-MLIs topologies by performing logical operations between the pulses obtained from conventional switching logic. These logical expressions modify the nature of the switching pulses such that they can be directly applied to control the considered inverter. As these expressions depend on switching pattern of the devices in the considered inverter, any change in the topological arrangement or number of levels needs a change in the logical expressions.

In case, if the nature of the switching pulses is non-overlapped, then they can realise any RSC-MLI, irrespective to its topological arrangement. Fig. 4c shows the non-overlapped switching pulses, obtained from the carrier arrangement shown in Fig. 4b, where each pulse is active when the reference is in between minimum and maximum value of its respective carrier. The non-overlapping nature of these pulses can be verified by observing their conduction intervals ( $C$ ) shown in Fig. 4d. From Figs. 4c and d, it is observed that at any instant, only one among these pulse is active and is responsible for attaining a specific phase-voltage level. Hence, the methodology to obtain non-overlapped switching pulses by controlling their conduction intervals using unified logical expression is discussed in the below section.

### 3 Methodology and implementation of the proposed modulation scheme

To derive a unified logic expression for obtaining non-overlapped interval ( $C$ ) from the overlapped interval ( $Q$ ), the nature of both these conduction intervals should be analysed. Fig. 5 (obtained from Figs. 4b and d) shows the conduction intervals  $Q$  and  $C$  together. This figure infers that the desired conduction interval  $C$  can be obtained by performing a logical operation on  $Q$  with its adjacent bands. From Fig. 5a, by observing  $Q_3$  and  $C_3$  reveals their identical nature of switching and hence

$$C_3 = Q_3 \quad (2)$$

However,  $Q_2$  and  $C_2$  are different from each other and from Fig. 5b, the following relationships are obtained.

- If  $Q_3 = 0$  and  $Q_2 = 0$ , then  $C_2 = 0$ ;

- if  $Q_3 = 1$  and  $Q_2 = 1$ , then  $C_2 = 0$ ;

- if  $Q_3 = 0$  and  $Q_2 = 1$ , then  $C_2 = 1$ .

It should be noted that  $Q_3 = 1$  and  $Q_2 = 0$  case does not appear as lower conduction interval  $Q_2$  always remains high when upper

conduction interval  $Q_3$  is high. To obtain a logical relation for  $C_2$  in terms of  $Q_3$  and  $Q_2$ , a two-variable Karnaugh-map (K-map) is implemented in Fig. 5b. From Fig. 5b, logical relation for  $C_2$  is obtained as  $C_2 = \bar{Q}_3 Q_2$ . To realise this logic in hardware, two logic gates NOT and AND are required. To reduce these logic gates, a *do not care* variable is included in K-map and the logical relation (3) is obtained, which requires an Ex-OR gate only

$$C_2 = \bar{Q}_3 Q_2 + Q_3 \bar{Q}_2 = Q_2 \oplus Q_3 \quad (3)$$

To obtain conduction interval  $C_1$ , Fig. 5c is considered and following relationships are obtained.

- If  $Q_2 = 0$  and  $Q_1 = 0$ , then  $C_1 = 0$ ;

- if  $Q_2 = 1$  and  $Q_1 = 1$ , then  $C_1 = 0$ ;

- if  $Q_2 = 0$  and  $Q_1 = 1$ , then  $C_1 = 1$ .

With the help of K-map shown in Fig. 5c, logical relation (4) is obtained for conduction interval  $C_1$

$$C_1 = Q_1 \oplus Q_2 \quad (4)$$

Generalising (2)–(4), (5) can be obtained, where  $i$  is the carrier number

$$\begin{aligned} \text{for } i &= (n-1)/2 \\ C_i &= Q_i \\ \text{for } 1 \leq i < (n-1)/2 \\ C_i &= Q_i \oplus Q_{i+1} \end{aligned} \quad (5)$$

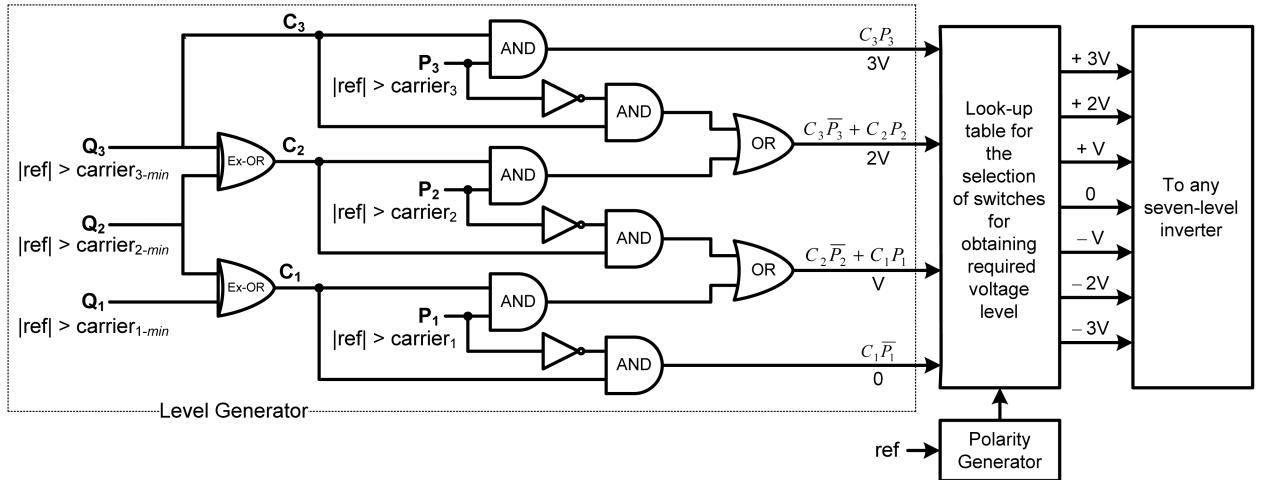

Applying the pulse  $P_i$  ( $\text{ref} > \text{carrier}_i$ ) over the interval  $C_i$  results in desired non-overlapped switching pulses. This switching action of the proposed modulation scheme to control seven-level inverter is shown in Fig. 6.

In Fig. 6,  $C_3$  should be active to obtaining voltage band of 3 V to 2 V. Similarly,  $C_2$  and  $C_1$  should be active for obtaining voltage band of 2 V to V and V to 0, respectively.  $C_3$  high with  $P_3$  high, i.e. pulse  $C_3 P_3$  is responsible for obtaining 3 V voltage state.  $C_3$  high with  $P_3$  low or  $C_2$  high with  $P_2$  high, i.e. pulse  $C_3 \bar{P}_3 + C_2 P_2$  obtains 2 V voltage state. Similarly,  $C_2$  high with  $P_2$  low or  $C_1$  high with  $P_1$  high, i.e.  $C_2 \bar{P}_2 + C_1 P_1$  results in V voltage state.  $C_1$  high with  $P_1$  low, i.e. pulse  $C_1 \bar{P}_1$  results in zero voltage. The polarity of these voltage states is decided by the polarity of the modulating signal, where positive voltage levels are obtained for the positive half of the reference and negative voltage levels are obtained for negative half of the modulating signal. Table 1 shows the implementation of the proposed switching logic to realise a seven-level inverter topology shown in Fig. 1. For example, to obtain +3 V voltage-level, switches  $H_4$ ,  $S_1$ ,  $S_3$ , and  $H_1$  should be in conduction. Therefore, these switches are applied with pulse  $C_3 P_3$  for the positive half of the reference. Similarly, to obtain -3 V voltage-level, pulse  $C_3 P_3$  applied to switches  $H_2$ ,  $S_1$ ,  $S_3$ , and  $H_3$  for the negative half of the reference. A similar explanation holds good for remaining voltage level as presented in Table 1.

In this proposed scheme, the obtained number of desired pulses will be equal to the number of phase-voltage levels, where each

Fig. 6 Implementation of the proposed PWM scheme for seven-level phase-voltage

Table 1 Selection of switching devices to control seven-level inverter with the proposed scheme

| Polarity generation | Voltage level | Switching pulse           | Devices to be in on to obtain the respective voltage level in Fig. 2 |

|---------------------|---------------|---------------------------|----------------------------------------------------------------------|

| ref $\geq 0$        | +3 V          | $C_3 P_3$                 | $H_4-S_1-S_3-H_1$                                                    |

|                     | +2 V          | $C_3 \bar{P}_3 + C_2 P_2$ | $H_4-S_2-S_3-H_1$                                                    |

|                     | +V            | $C_2 \bar{P}_2 + C_1 P_1$ | $H_4-S_1-S_4-H_1$                                                    |

|                     | 0             | $C_1 \bar{P}_1$           | $H_4-S_2-S_4-H_1$ or $H_2-S_2-S_4-H_3$                               |

| for zero-level      | —             | —                         | —                                                                    |

|                     | -V            | $C_2 \bar{P}_2 + C_1 P_1$ | $H_2-S_1-S_4-H_3$                                                    |

|                     | -2 V          | $C_3 \bar{P}_3 + C_2 P_2$ | $H_2-S_2-S_3-H_3$                                                    |

| ref < 0             | -3 V          | $C_3 P_3$                 | $H_2-S_1-S_3-H_3$                                                    |

Table 2 Experimental parameters

| Circuit/parameter                               | Component/value                                                        |

|-------------------------------------------------|------------------------------------------------------------------------|

| 30 V isolated dc power supplies (12 no.)        | 30 V, 3 A dual channel regulated power supply                          |

| 13-level asymmetrical RSC-MLI                   | developed using 2 modules of generalised converter with 24 IGBTs each  |

| IGBT model and rating                           | IKW40T120, 40 A and 1200 V                                             |

| carrier frequency ( $f_{cr}$ )                  | 2 kHz                                                                  |

| amplitude modulation index ( $m_a$ )            | 0.98                                                                   |

| load                                            | three-phase star-connected 1 kW 0.85 power factor lagging.             |

| controller (to obtain firing signals for IGBTs) | dSPACE micro-lab box RTI1202 R&D controller sampling time (20 $\mu$ s) |

pulse is responsible for obtaining a particular voltage level. Further, each of these desired pulse will be given to the devices (of the considered inverter) to be in conduction to achieve the respective voltage state. Further, generalising these obtained switching pulses for higher voltage levels (6) is obtained

$$\begin{aligned}

\text{for } \frac{n-1}{2}V & \Rightarrow \text{switching pulse} = C_{\frac{n-1}{2}} P_{\frac{n-1}{2}} \\

\text{for } V \leq iV \leq \left(\frac{n-1}{2} - 1\right)V & \Rightarrow \text{switching pulse} = C_{i+1} \bar{P}_{i+1} + C_i P_i \\

\text{for } 0V & \Rightarrow \text{switching pulse} = C_1 \bar{P}_1

\end{aligned} \quad (6)$$

#### 4 Implementation of the proposed scheme to 13-level asymmetrical RSC-MLI topologies

The performance of the proposed PWM scheme is validated by developing experimental set-ups of different three-phase IGBT-based 13-level asymmetrical RSC-MLI topologies. The developed topologies are MLDCL, SSPS, switched dc sources, hybrid T-type, and E-type (as shown in Fig. 1). Further, to validate the superiority

of the proposed PWM scheme, the above selected topologies are also controlled using conventional reduced carrier PWM scheme. Different inverter topologies are developed by using two inverter modules with 24 individual IGBTs in each. The modulation schemes are implemented in dSPACE Micro-lab box RTI1202 R&D controller. The carrier signal frequency ( $f_{cr}$ ) and amplitude modulation index ( $m_a$ ) are selected as 2 kHz and 0.98, respectively. The dc input source voltage ( $V_{dc}$ ) is selected as 30 V and with this, the maximum amplitude of phase-voltage is 180 V. The complete list of parameters used in experimental study is given in Table 2 and the photograph of the experimental set-up is shown in Fig. 7. Table 3 shows the implementation of the proposed switching logic to realise these selected RSC-MLI topologies.

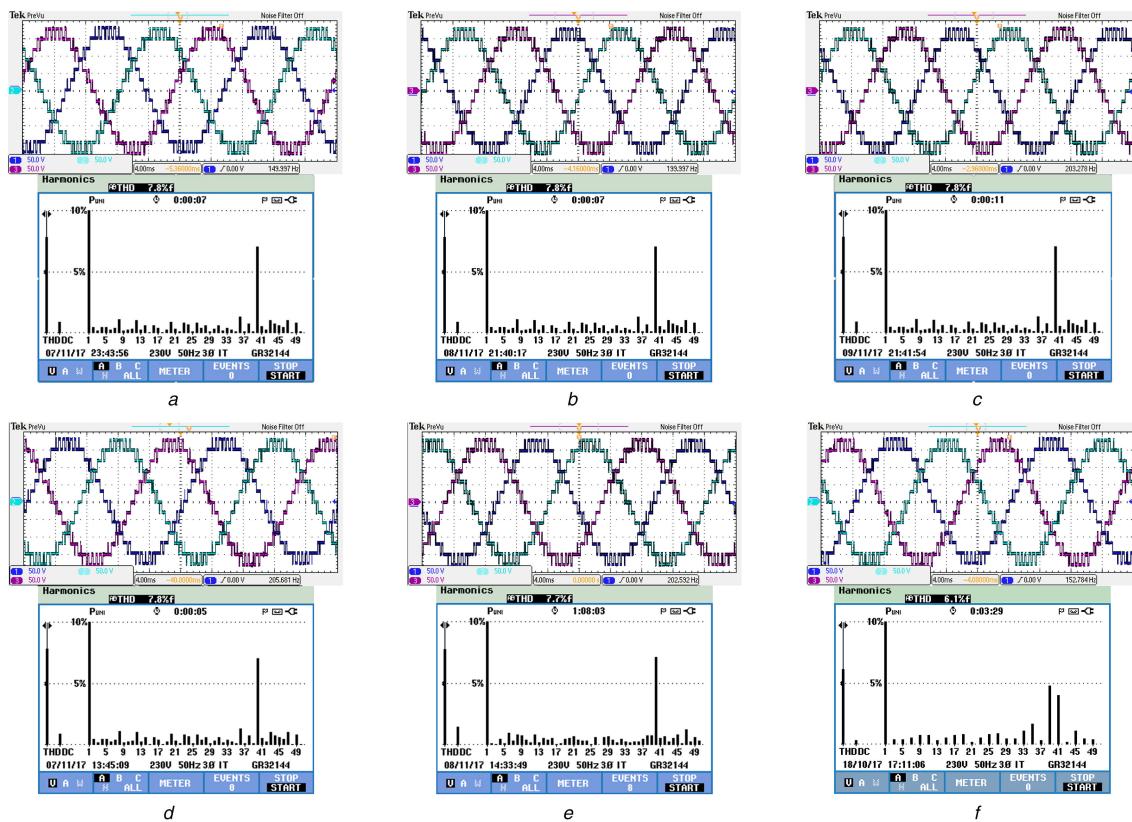

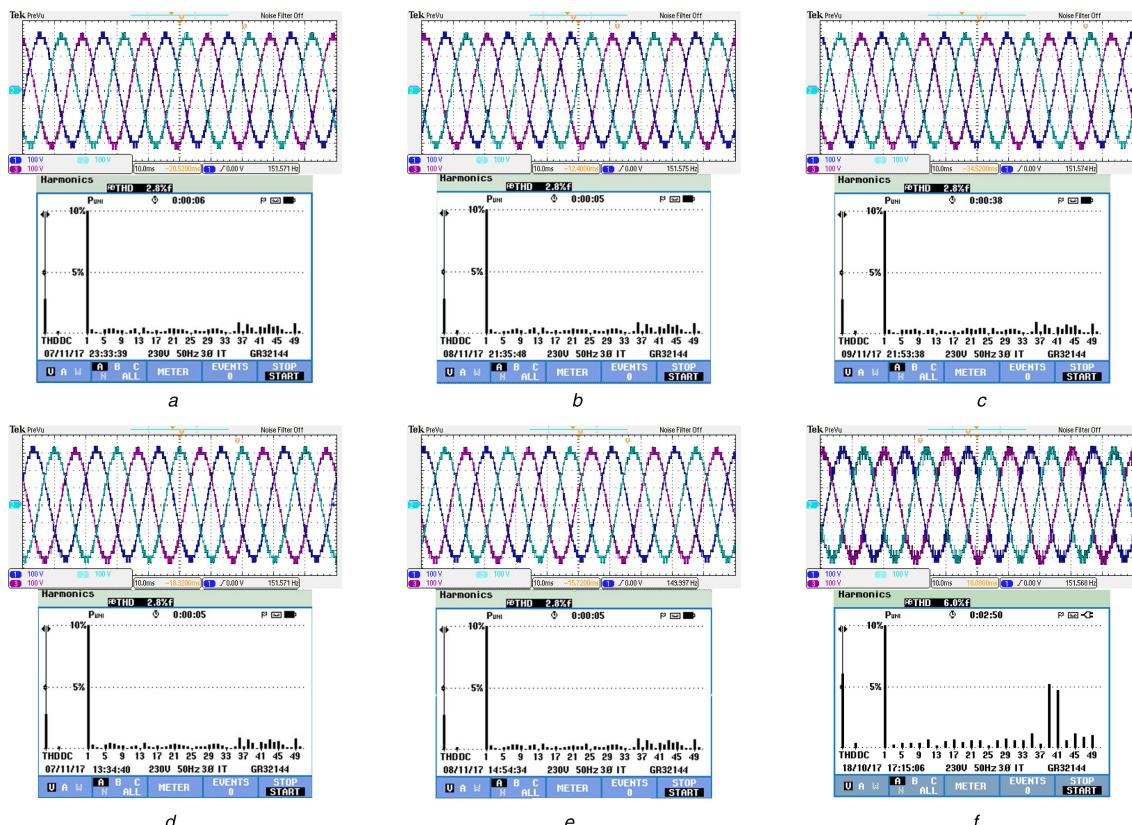

Fig. 8 shows the experimental performance of phase-voltages and their corresponding harmonic spectra. Figs. 8a–e show the phase-voltage performance of 13-level MLDCL, SSPS, switched dc sources, hybrid T-type, and E-type asymmetrical topologies with the proposed PWM scheme. Fig. 8f depicts the phase-voltage performance of 13-level MLDCL with conventional reduced carrier PWM scheme. Similarly, Fig. 9 depicts the experimental line-voltage performance of these RSC topologies with the proposed PWM scheme and conventional reduced carrier PWM scheme. Line-voltages and their corresponding harmonic spectra of the proposed scheme for considered 13-level asymmetrical topologies are shown in Figs. 9a–e. Fig. 9f depicts the line-voltage

**Fig. 7** Photograph of the experimental set-up for realising 13-level asymmetrical switched dc source inverter

**Table 3** Selection of switching devices to control 13-level inverter with the proposed scheme

| Polarity generation | Level | Switching pulse         | Devices to be in conduction to obtain the respective voltage level |                        |                     |                 |                 |

|---------------------|-------|-------------------------|--------------------------------------------------------------------|------------------------|---------------------|-----------------|-----------------|

|                     |       |                         | MLDCL                                                              | SSPS                   | Switched dc sources | Hybrid T-type   | E-type          |

| ref $\geq 0$        | +6 V  | $C_6P_6$                | $H_4-S_1-S_3-S_5-H_1$                                              | $H_4-S_2-S_5-H_1$      | $S_2-S_3-S_6-S_7$   | $S_2-S_6-S_1$   | $S_1-S_4-S_5$   |

|                     | +5 V  | $C_6\bar{P}_6 + C_5P_5$ | $H_4-S_2-S_3-S_5-H_1$                                              | $H_4-S_1-S_5-H_1$      | $S_1-S_3-S_6-S_7$   | $S_2-S_6-BS_1$  | $BS_1-S_4-S_5$  |

|                     | +4 V  | $C_5\bar{P}_5 + C_4P_4$ | $H_4-S_1-S_4-S_5-H_1$                                              | $H_4-S_2-S_4-H_1$      | $S_2-S_3-S_6-S_8$   | $BS_2-S_6-S_1$  | $S_2-S_4-S_5$   |

|                     | +3 V  | $C_4\bar{P}_4 + C_3P_3$ | $H_4-S_1-S_3-S_6-H_1$                                              | $H_4-S_1-S_4-H_1$      | $S_1-S_3-S_6-S_8$   | $BS_2-S_6-BS_1$ | $S_1-BS_2-S_5$  |

|                     | 2 V   | $C_3\bar{P}_3 + C_2P_2$ | $H_4-S_2-S_3-S_6-H_1$                                              | $H_4-S_1-S_6-H_1$      | $S_2-S_4-S_6-S_7$   | $S_4-S_6-S_1$   | $S_1-S_4-S_6$   |

|                     | V     | $C_2\bar{P}_2 + C_1P_1$ | $H_4-S_1-S_4-S_6-H_1$                                              | $H_4-S_3-S_6-H_1$      | $S_2-S_3-S_5-S_7$   | $S_4-S_6-BS_1$  | $BS_1-S_4-S_6$  |

| for zero-level      | 0     | $C_1\bar{P}_1$          | $H_4-S_2-S_4-S_6-H_1$ or<br>$H_2-S_2-S_4-S_6-H_3$                  | $H_1-H_3$ or $H_2-H_4$ | $S_1-S_3-S_5-S_7$   | $S_4-S_6-S_3$   | $S_1-S_3-S_5$   |

|                     |       |                         |                                                                    |                        |                     |                 |                 |

| ref < 0             | -V    | $C_2\bar{P}_2 + C_1P_1$ | $H_2-S_1-S_4-S_6-H_3$                                              | $H_2-S_3-S_6-H_3$      | $S_1-S_4-S_6-S_8$   | $S_2-S_5-BS_1$  | $BS_1-S_3-S_5$  |

|                     | -2 V  | $C_3\bar{P}_3 + C_2P_2$ | $H_2-S_2-S_3-S_6-H_3$                                              | $H_2-S_1-S_6-H_3$      | $S_1-S_3-S_5-S_8$   | $S_2-S_5-S_3$   | $BS_1-BS_2-S_6$ |

|                     | -3 V  | $C_4\bar{P}_4 + C_3P_3$ | $H_2-S_1-S_3-S_6-H_3$                                              | $H_2-S_1-S_4-H_3$      | $S_2-S_4-S_5-S_7$   | $BS_2-S_5-BS_1$ | $S_2-BS_2-S_6$  |

|                     | -4 V  | $C_5\bar{P}_5 + C_4P_4$ | $H_2-S_1-S_4-S_5-H_3$                                              | $H_2-S_2-S_4-H_3$      | $S_1-S_4-S_5-S_7$   | $BS_2-S_5-S_3$  | $S_1-S_3-S_6$   |

|                     | -5 V  | $C_6\bar{P}_6 + C_5P_5$ | $H_2-S_2-S_3-S_5-H_3$                                              | $H_2-S_1-S_5-H_3$      | $S_2-S_4-S_5-S_8$   | $S_4-S_5-BS_1$  | $BS_1-S_3-S_6$  |

|                     | -6 V  | $C_6P_6$                | $H_2-S_1-S_3-S_5-H_3$                                              | $H_2-S_2-S_5-H_3$      | $S_1-S_4-S_5-S_8$   | $S_4-S_5-S_3$   | $S_2-S_3-S_6$   |

performance of 13-level MLDCL with conventional reduced carrier PWM scheme.

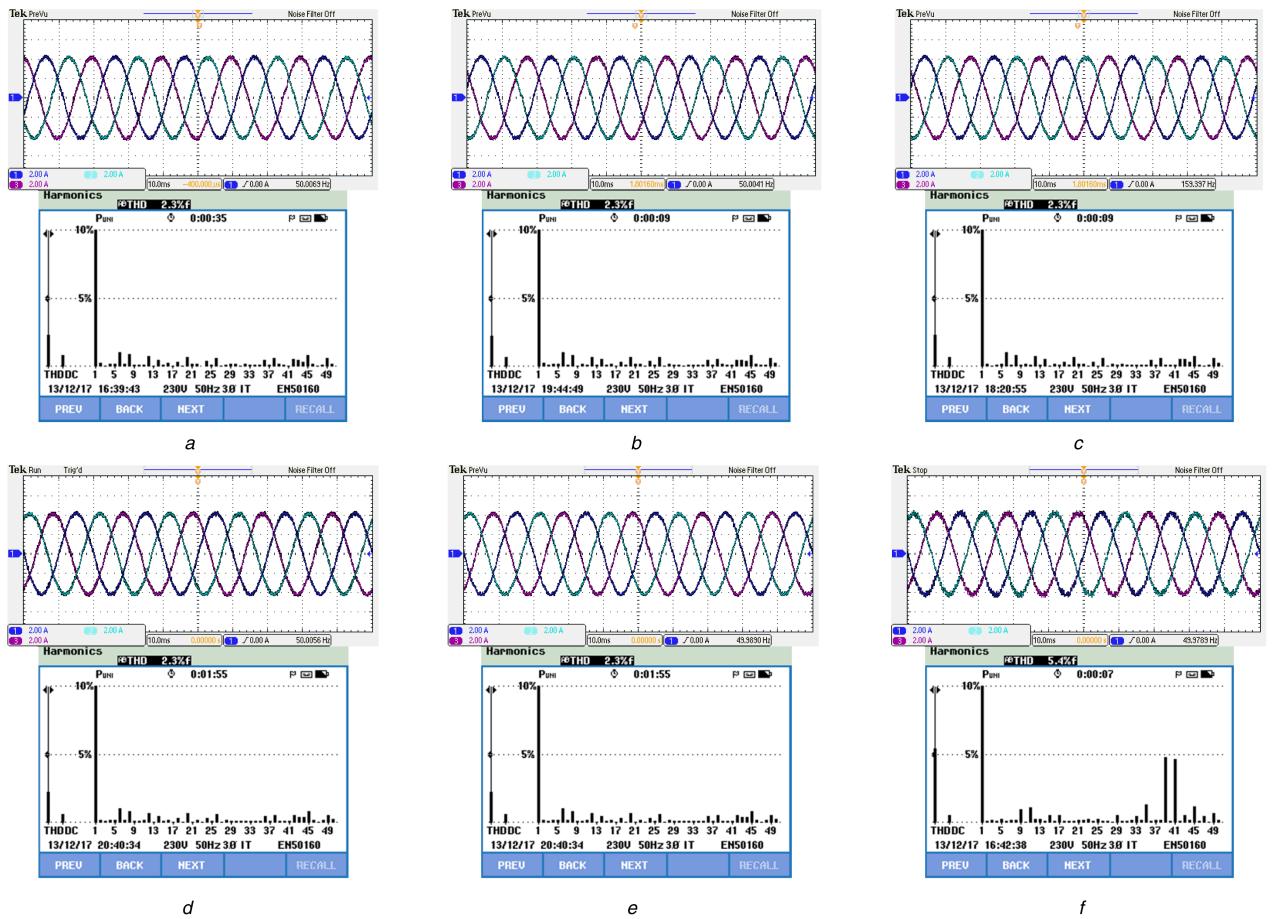

In order to evaluate the whole inverter system, it is necessary to show the performance of the inverter currents. Fig. 10 depicts the experimental line-current performance of RSC topologies with proposed and conventional reduced carrier PWM schemes for three-phase star-connected load. Line-current and their corresponding harmonic spectra of the proposed scheme for considered 13-level asymmetrical topologies are shown in Figs. 10a–e. Fig. 10f depicts the line-current performance of 13-level MLDCL with conventional reduced carrier PWM scheme.

In a view to estimate the effectiveness of the proposed PWM scheme, a comprehensive comparison is carried out with carrier-based PWM schemes reported in the literature. For this, the PWM scheme along with the inverter reported in the literature is implemented experimentally and compared with the proposed PWM scheme in terms of harmonic performance, complexity in implementation, and computation burden. The summary of merits and demerits are presented in Table 4. Comparing Figs. 8–10 along with Table 4, the following conclusions are derived.

- From Figs. 8a–e, it is observed that all the phase-voltage waveforms and their harmonic spectra are identical with dominant harmonic appeared at frequency modulation index ( $m_f = 40$ ).

- Comparing Fig. 8f with Figs. 8a–e, it can be observed that THD values of conventional reduced carrier scheme (6.1%) are less when compared with the proposed scheme (7.8%). Nevertheless, the conventional reduced carrier PWM scheme

has less THD value but its side-band harmonics are different and centred at  $m_f$ . The magnitude of the harmonics are also different in both methods, which leads to significant difference in line-voltage THD.

- The line-voltage waveforms and their corresponding harmonic spectra with the proposed PWM scheme shown in Figs. 9a–e are identical in terms of waveform shape and harmonic performance. The obtained THD are identical with side-band harmonics centred at  $m_f = 40$ .

- Comparing Figs. 9a–e with Fig. 9f, it can be observed that the proposed scheme produces improved harmonic performance (2.8%) when compared with conventional reduced carrier PWM scheme (6.0%). The reason for this is the proposed PWM scheme will help for better cancellation of harmonics presented in phase-voltages.

- From line-current performance shown in Fig. 10, it is observed that line-current waveforms and their corresponding harmonic spectra with the proposed PWM scheme are identical in terms of waveform shape and harmonic performance. It can also be observed that the proposed scheme produces improved harmonic performance (2.3%) when compared with conventional reduced carrier PWM scheme line-currents (5.4%) shown in Fig. 10f.

- The proposed scheme can be directly applicable to any MLI topology and easily scalable to higher number of levels irrespective of topological arrangement and dc voltage ratios.

- The proposed PWM scheme produces improved line THD performance compared with conventional reduced carrier and

**Fig. 8** Phase-voltage waveforms and their corresponding harmonic spectra (scale: X-axis: 4 ms/div and Y-axis: 50 V/div)

(a) MLDCL, (b) SSPS, (c) Switched dc sources, (e) E-type, (f) MLDCL with conventional reduced carrier PWM

**Fig. 9** Line-voltage waveforms and their corresponding harmonic spectra (scale: X-axis: 10 ms/div and Y-axis: 100 V/div)

(a) MLDCL, (b) SSPS, (c) Switched dc sources, (d) Hybrid T-type, (e) E-type, (f) MLDCL with conventional reduced carrier PWM

multicarrier PWM schemes and similar THD performance when compared with switching function PWM scheme.

vii The turnaround time for implementation of the proposed PWM scheme is significantly reduced and remains almost same for a given number of level in any inverter topology. The less

computation burden of the proposed scheme will allow the controller to accurately implement higher switching frequencies.

**Fig. 10** Line-current waveforms and their corresponding harmonic spectra (scale: X-axis: 10 ms/div and Y-axis: 2 A/div)

(a) MLDCL, (b) SSPS, (c) Switched dc sources, (d) Hybrid T-type, (e) E-type, (f) MLDCL with conventional reduced carrier PWM

## 5 Conclusion

To overcome the limitations of conventional reduced carrier PWM scheme, this paper presented a modified reduced carrier PWM scheme with unified logical expressions. The efficacy of the proposed switching logic is validated with experimental studies on various 13-level asymmetrical RSC-MLI topologies. Further, superior performance of the proposed scheme is verified by comparing its performance with conventional carrier PWM schemes. Topology-independent operation, simplified switching logic generalisation to higher levels, less computation burden, and improved line-voltage THD performance of the proposed reduced carrier PWM scheme serves as a viable solution to overcome the demerits of conventional multicarrier, reduced carrier, and multi-reference PWM schemes.

**Table 4** Performance comparison of carrier-based PWM schemes reported in the literature with the proposed PWM scheme

| Carrier-based PWM scheme and topology reported in the literature |                                                   |                      |                     |                          | With the proposed PWM scheme |                     |                          | Merits and demerits of PWM scheme reported in the literature                                                                         |  |

|------------------------------------------------------------------|---------------------------------------------------|----------------------|---------------------|--------------------------|------------------------------|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| PWM scheme                                                       | Topology                                          | Phase-voltage THD, % | Line-voltage THD, % | Turnaround time, $\mu$ s | Phase-voltage THD, %         | Line-voltage THD, % | Turnaround time, $\mu$ s |                                                                                                                                      |  |

| multi-reference [11, 13, 23, 25]                                 | T-type seven-level [11]                           | 15.7                 | 14.8                | 6.5                      | 15.7                         | 4.9                 | 6.2                      | ✓ require less computational time                                                                                                    |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✓ scalable to higher levels                                                                                                          |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✓ directly applicable to all topologies                                                                                              |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ high line-voltage THD                                                                                                              |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ difficulty in implement for closed-loop applications due to the presence of multiple references                                    |  |

| reduced carrier with logic gates [9, 10, 27]                     | modified T-type seven-level [10]                  | 15.8                 | 15.0                | 19                       | 15.6                         | 4.8                 | 5.9                      | ✗ high line-voltage THD                                                                                                              |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ switching logic is complex and requires more computational time                                                                    |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ neither scalable nor directly applicable to all topologies                                                                         |  |

| switching function PWM [6, 16]                                   | symmetrical seven-level switched dc-sources [6]   | 15.6                 | 4.8                 | 7.5                      | 15.5                         | 4.7                 | 6.0                      | ✓ good line-voltage THD performance                                                                                                  |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✓ scalable and applicable to all topologies                                                                                          |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ involves large number of comparators which occupies more memory and requires more computation time to realise the switching pulses |  |

| reduced carrier [5]                                              | RV seven-level [5]                                | 15.7                 | 14.9                | 5.3                      | 15.6                         | 4.8                 | 6.1                      | ✓ scalable with simplified switched logic and takes very less computational time                                                     |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ not applicable to all topologies                                                                                                   |  |

| hybrid PWM [17, 20, 22, 32]                                      | asymmetrical SSPS with H-bridge eleven-level [17] | 9.9                  | 3.1                 | 6.6                      | 9.6                          | 3.0                 | 7.2                      | ✗ high line-voltage THD                                                                                                              |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✓ good line-voltage THD performance                                                                                                  |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✓ scalable and possess simplified switched logic and takes very less computational time                                              |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ applicable only to asymmetrical cascaded topologies                                                                                |  |

|                                                                  |                                                   |                      |                     |                          |                              |                     |                          | ✗ may involve mixed switching frequencies, hence may produce unwanted voltage spikes in phase and line-voltages                      |  |

## 6 References

- [1] Gupta, K.K., Ranjan, A., Bhatnagar, P., *et al.*: 'Multilevel inverter topologies with reduced device count: a review', *IEEE Trans. Power Electron.*, 2016, **31**, (1), pp. 135–151

- [2] Su, G.-J.: 'Multilevel DC-link inverter', *IEEE Trans. Ind. Appl.*, 2005, **41**, (3), pp. 848–854

- [3] Sanjeevan, A.R., Kaarthik, R.S., Gopakumar, K., *et al.*: 'Reduced common-mode voltage operation of a new seven-level hybrid multilevel inverter topology with a single DC voltage source', *IET Power Electron.*, 2016, **9**, (3), pp. 519–528

- [4] Babaei, E.: 'A cascade multilevel converter topology with reduced number of switches', *IEEE Trans. Power Electron.*, 2008, **23**, (6), pp. 2657–2664

- [5] Najafi, E., Yatim, A.H.M.: 'Design and implementation of a new multilevel inverter topology', *IEEE Trans. Ind. Electron.*, 2012, **59**, (11), pp. 4148–4154

- [6] Gupta, K.K., Jain, S.: 'A novel multilevel inverter based on switched DC sources', *IEEE Trans. Ind. Electron.*, 2014, **61**, (7), pp. 3269–3278

- [7] Babaei, E., Laali, S., Bayat, Z.: 'A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches', *IEEE Trans. Ind. Electron.*, 2015, **62**, (2), pp. 922–929

- [8] Samadai, E., Gholamian, S.A., Sheikholeslami, A., *et al.*: 'An envelope type (E-type) module: asymmetric multilevel inverters with reduced components', *IEEE Trans. Ind. Electron.*, 2016, **63**, (11), pp. 7148–7156

- [9] Park, S.-J., Kang, F.-S., Lee, M.H., *et al.*: 'A new single-phase five-level PWM inverter employing a deadbeat control scheme', *IEEE Trans. Power Electron.*, 2003, **18**, (3), pp. 831–843

- [10] Choi, J.-S., Kang, F.-S.: 'Seven-level PWM inverter employing series-connected capacitors paralleled to a single DC voltage source', *IEEE Trans. Ind. Electron.*, 2015, **62**, (6), pp. 3448–3459

- [11] Rahim, N.A., Chaniago, K., Selvaraj, J.: 'Single-phase seven-level grid-connected inverter for photovoltaic system', *IEEE Trans. Ind. Electron.*, 2011, **58**, (6), pp. 2435–2443

- [12] Alishah, R.S., Nazarpour, D., Hosseini, S.H., *et al.*: 'Reduction of power electronic elements in multilevel converters using a new cascade structure', *IEEE Trans. Ind. Electron.*, 2015, **62**, (1), pp. 256–269

- [13] Rahim, N.A., Elias, M.F.M., Hew, W.P.: 'Transistor-clamped H-bridge based cascaded multilevel inverter with new method of capacitor voltage balancing', *IEEE Trans. Ind. Electron.*, 2013, **60**, (8), pp. 2943–2956

- [14] Gautam, S.P., Kumar, L., Gupta, S.: 'Hybrid topology of symmetrical multilevel inverter using less number of devices', *IET Power Electron.*, 2015, **8**, (11), pp. 2125–2135

- [15] Gautam, S.P., Sahu, L.K., Gupta, S.: 'Reduction in number of devices for symmetrical and asymmetrical multilevel inverters', *IET Power Electron.*, 2016, **9**, (4), pp. 698–709

- [16] Choi, W.K., Kang, F.S.: 'H-bridge based multilevel inverter using PWM switching function'. 31st Int. Conf. on Telecommunications Energy, INTELEC 2009, October 2009, pp. 1–5

- [17] Hinago, Y., Koizumi, H.: 'A single-phase multilevel inverter using switched series/parallel dc voltage sources', *IEEE Trans. Ind. Electron.*, 2010, **57**, (8), pp. 2643–2650

- [18] Hinago, Y., Koizumi, H.: 'A switched-capacitor inverter using series/parallel conversion with inductive load', *IEEE Trans. Ind. Electron.*, 2012, **59**, (2), pp. 878–887

- [19] dos Santos, E.C., Muniz, J.H.G., da Silva, E.R.C., *et al.*: 'Nested multilevel topologies', *IEEE Trans. Power Electron.*, 2015, **30**, (8), pp. 4058–4068

- [20] Barzegarkhoo, R., Zamiri, E., Vosoughi, N., *et al.*: 'Cascaded multilevel inverter using series connection of novel capacitor-based units with minimum switch count', *IET Power Electron.*, 2016, **9**, (10), pp. 2060–2075

- [21] Babaei, E., Gowgani, S.S.: 'Hybrid multilevel inverter using switched capacitor units', *IEEE Trans. Ind. Electron.*, 2014, **61**, (9), pp. 4614–4621

- [22] Babaei, E., Kangarlu, M.F., Hosseinzadeh, M.A.: 'Asymmetrical multilevel converter topology with reduced number of components', *IET Power Electron.*, 2013, **6**, (6), pp. 1188–1196

- [23] Odeh, C.I.: 'A cascaded multi-level inverter topology with improved modulation scheme', *Electr. Power Compon. Syst.*, 2014, **42**, (7), pp. 768–777

- [24] Babaei, E., Laali, S., Alilu, S.: 'Cascaded multilevel inverter with series connection of novel H-bridge basic units', *IEEE Trans. Ind. Electron.*, 2014, **61**, (12), pp. 6664–6671

- [25] Odeh, C.I., Obe, E.S., Ojo, O.: 'Topology for cascaded multilevel inverter', *IET Power Electron.*, 2016, **9**, (5), pp. 921–929

- [26] Masaoud, A., Ping, H.W., Mekhilef, S., *et al.*: 'New three-phase multilevel inverter with reduced number of power electronic components', *IEEE Trans. Power Electron.*, 2014, **29**, (11), pp. 6018–6029

- [27] Salem, A., Ahmed, E.M., Orabi, M., *et al.*: 'New three-phase symmetrical multilevel voltage source inverter', *IEEE J. Emerg. Sel. Top. Circuits Syst.*, 2015, **5**, (3), pp. 430–442

- [28] Masaoud, A., Ping, H.W., Mekhilef, S., *et al.*: 'Novel configuration for multilevel DC-link three-phase five-level inverter', *IET Power Electron.*, 2014, **7**, (12), pp. 3052–3061

- [29] Carrara, G., Gardella, S., Marchesoni, M., *et al.*: 'A new multilevel PWM method: a theoretical analysis', *IEEE Trans. Power Electron.*, 1992, **7**, (3), pp. 497–505

- [30] McGrath, B.P., Holmes, D.G.: 'Multicarrier PWM strategies for multilevel inverters', *IEEE Trans. Ind. Electron.*, 2002, **49**, (4), pp. 858–867

- [31] Sreenivasarao, D., Agarwal, P., Das, B.: 'Performance evaluation of carrier rotation strategy in level-shifted pulse-width modulation technique', *IET Power Electron.*, 2014, **7**, (3), pp. 667–680

- [32] Rech, C., Pinheiro, J.R.: 'Hybrid multilevel converters: unified analysis and design considerations', *IEEE Trans. Ind. Electron.*, 2007, **54**, (2), pp. 1092–1104

- [33] Hari Priya, V., Sreenivasarao, D., Siva Kumar, G.: 'Improved pulse-width modulation scheme for T-type multilevel inverter', *IET Power Electron.*, 2017, **10**, (8), pp. 968–976