# Efficient Interleaved Buck Converter Driver for LED Applications

**Sangani Prasanth**

Student of M.Tech. (PED)

Electrical Engineering Department

NIT-Warangal, Telangana.

prashanthdhoni183@gmail.com

**Udaya Bhasker Manthati**

Assistant Professor,

Electrical Engineering

Department

NIT-Warangal, Telangana

ub@nitw.ac.in

**Vishnu Sidharthan P**

Junior Research Fellow,

Electrical Engineering Department

NIT-Warangal, Telangana.

psvishnuchentrappinni@gmail.com

**Srinivas Punna**

Ph.D Scholar,

Electrical Engineering Department

NIT-Warangal, Telangana

srinu240@gmail.com

**Abstract:**—This paper proposes the Interleaved Buck Converter (IBC) for improving the performance of LED. The converter itself will be acting as a driver for the LED. Interleaved buck converter (IBC) operates with continuous input current, extremely low output current ripple with small inductance and high frequency of operation (40 kHz), avoiding audible noises. IBC is introduced to diminish the disadvantages of conventional Buck converter as LED driver. Also, the proposed converter can provide current sharing between two interleaved modules without using additional current-sharing control method. All of these benefits are obtained without any additional stress on the circuit components. A prototype converter with 20 V input and 6.5V–5A output is implemented to verify the theoretical analysis. Operational principles are based on analytical approach, MATLAB-Simulink and LT spice results are presented in this paper.

**Keywords**— *Interleaved Buck Converter (IBC), Proportional Integral Controller (PI), and Light Emitting Diode (LED).*

## I. INTRODUCTION

In olden days light emitting diodes (LED) were used as an indicator in different circuit (temperature limit, current limit, battery level, initiation indicator in Television, alarming, etc.). Nowadays LED plays a significant role in the lighting arena. Most of the modern lighting designs are utilizing LED and the traditional lighting are also being replaced by LED. Hence the technologies slowly developed for implementing LED drivers with higher efficiencies. Power electronics can condition the quality of the power to LED so that it can get an extended lifetime. Main advantages that focused LED over the traditional lighting (incandescent lamps, fluorescent lamps, halogen lamps) are improved lifetime, high reliability and the reduced energy consumption for developing more lumen [1]. Another tremendous advantage of LED is that it can reach the maximum brightness in millionth of a second and the lifetime is approximately eight times more than the traditional lighting. For 1 Watt LED can provide 740 Lumens as compared to 100 Watts incandescent lamp. LED series and parallel arrays can be developed and utilized for various applications. Moreover for these important advantages to be further developed with the incorporation of efficient drivers for the LED [2].

Power electronics interfacing for supplying rated voltage and current with low current ripple is a major concept for designing the components and circuitry. Even the load or source are disturbed the rated parameters should be retained in a minute time delay. The controller should be designed accordingly. Conventional Buck converter as the driver circuit is explained and the disadvantages arises due to high current ripple is briefly is specified, hence a higher level converter is proposed to rectify those disadvantages [3]. Interleaved buck converter is introduced for driving the high brightness LED is briefly described in [4][5][6]. The response of the system can be further improved with an efficient controller.

This work describes the importance of interleaved buck converter as output stage as a LEDs driver, with a double loop control strategy (voltage and current). Interleaved converters are widely used for some particular applications, due to the low current ripples obtained and the reduced size of the components. In this proposed work we mainly points out the four main concepts of the circuits. 1) The output current ripple is much smaller at the interleaved converter, and can be theoretically zero under certain conditions, which provides a perfect constant current waveform through the LEDs. 2) Much smaller inductor values can be used in the converter, which leads to a faster turning ON and OFF of the whole converter. Thus, a much faster dimming frequency can be selected, avoiding possible acoustic noise problems.

In Section II the characteristics of LED and equivalent circuit is also developed. Implementation of series and parallel arrays of LED is also described. Later, Section III analyzes the interleaved buck converter, methodology and focusses on the modes of operation with complete designing of the circuit components considering the current ripple and size of the components. Section IV provides a design procedure of the controller for interleaved buck converter with clear explanation by deriving the state space equations for each modes of operation. The LT spice analysis of the circuit is briefly derived to design the  $K_P$  and  $K_I$  values for developing the compensator. In Section V, simulation is done in MATLAB Simulink for the IBC with current and voltage control loop. The load and source disturbance are injected in different steps at various time intervals and the controller will rectify the variation in the output and the analysis is done with the analytical approach. Finally, Section VI summarizes the main advantages and drawbacks of the proposed converter, and states the conclusions of this paper.

## II. CHARACTERISTICS AND EQUIVALENT CIRCUIT OF LED

LED can be an interesting alternative to traditional lighting due to its efficiency, performance and reliability. The equivalent model of an LED can be developed for the analysis with the (1).

$$V_L(t) = V_{th}(t) + I(t) \cdot R_{LED} \quad (1)$$

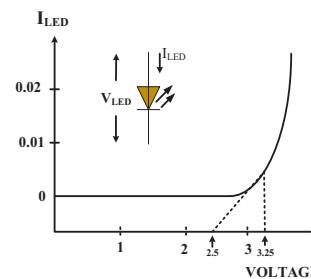

Fig.1. V-I characteristics of LED

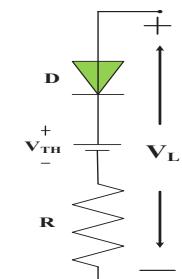

Fig.2. LED model

V-I characteristics of an LED can determine the operating point where the LED has to operate. As we know the threshold voltage ( $V_{th}$ ) of LED is 2.3 V. From the V-I characteristics plotted in figure 1, the operating point is selected as  $V_L = 3.25$  V and Current  $I_L = 0.5$  A. The plot shows the operating point is also shown in figure 1 [2].

Basically LED can be modeled with a DC source and series resistance. The model is shown in the figure.2. The voltage source is the threshold voltage ( $V_{th}$ ) of LED and resistance represents the dynamic resistance. Hence the equivalent dynamic resistance can be designed from (2).

$$R_{LED} = \frac{V_L(t) - V_{th}(t)}{I(t)} \quad (2)$$

$$R_{LED} = \frac{3.25 - 2.3}{0.5} = 1.9 \Omega$$

Here in this work series and parallel array of LED are taken in consideration. Two LED with 3 Watts rating are connected in series and ten parallel combination of the same is done to develop an array structure of LED. The rating of the total LED structure is of 32.5 Watts (6.5V, 5A). Table I briefs the parameters of LED.

TABLE I : PARAMETERS OF LED

| Sl no | LED PARAMETERS                 |       |      |

|-------|--------------------------------|-------|------|

|       | Parameters                     | Value | Unit |

| 1     | Threshold Voltage ( $V_{th}$ ) | 2.3   | V    |

| 2     | Supply Voltage ( $V_L$ )       | 3.25  | V    |

| 3     | Forward Current ( $I_f$ )      | 0.5   | A    |

| 4     | Power of single LED ( $P_d$ )  | 1.625 | W    |

| 5     | Total power of array of LED    | 32.5  | W    |

### III. METHODOLOGY AND ANALYSIS OF INTERLEAVED BUCK CONVERTER

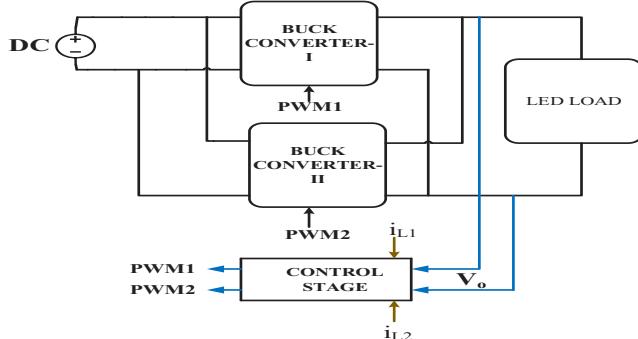

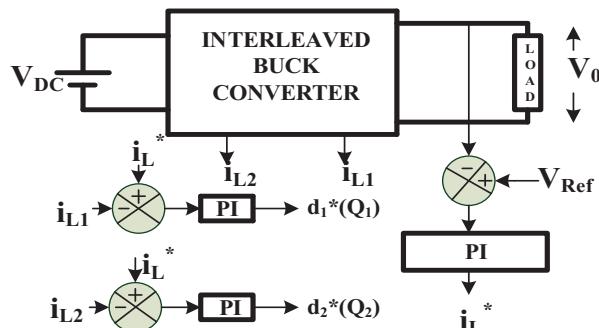

This work focusses on the developing the converter with highly efficient control for driving the LED. The interleaved converter is used as the driver for conditioning the power whenever any disturbance in load or source arises. The controller will take the action immediately to neglect the change in output voltage and will keeps the inductor current constant. Here two control loops are introduced 1) inner current control loop and 2) outer voltage control loop. Figure. 3 shows the complete block diagram with control loops. DC voltage is applied as the source for the LED. An Interleaved buck converter (IBC) (with two buck converters connected in parallel) is designed and developed for controlling the LED voltage and current under source and load disturbances.

Fig.3. Block diagram of Interleaved Buck converter.

The control stage explains the control strategy for switching the pulses of both buck converters under various disturbances and is explained briefly in later section.

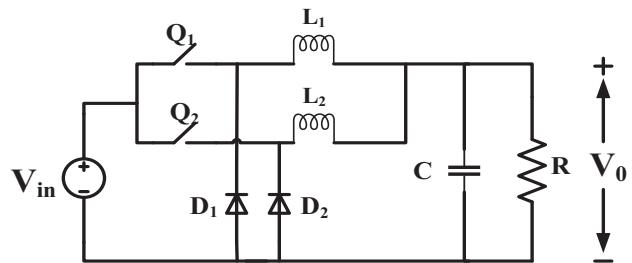

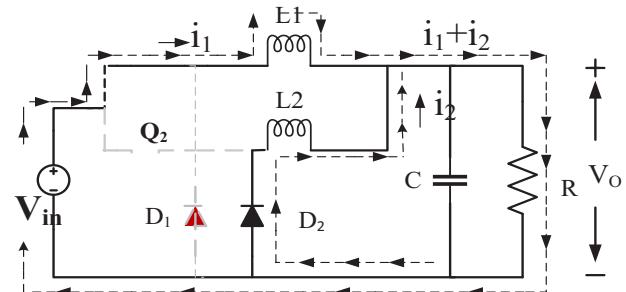

#### A. Circuit Diagram of IBC

The circuit diagram of IBC is shown in figure 4 in which two buck converters are connected in parallel with switches  $Q_1$ ,  $Q_2$  diodes  $D_1$ ,  $D_2$  and inductors  $L_1$ ,  $L_2$ . The two buck converters are connected in parallel. In this work input capacitor is also considered for removing the discontinuity in source current. It is designed on the basis of the amount of ripple in the input voltage. The working of the IBC can be explained with four different modes of operation in which switches will decide the power flow and is controlled by the controller is shown in Table II.

Fig.4. Circuit diagram of IBC

#### B. Modes of Operation

TABLE II : MODES OF OPERATION

| Modes of operation | Switch ( $Q_1$ ) | Switch ( $Q_2$ ) | Diode ( $D_1$ ) | Diode ( $D_2$ ) |

|--------------------|------------------|------------------|-----------------|-----------------|

| Mode-I             | ON               | OFF              | OFF             | ON              |

| Mode-II            | OFF              | OFF              | ON              | ON              |

| Mode-III           | OFF              | ON               | ON              | OFF             |

| Mode-IV            | OFF              | OFF              | ON              | ON              |

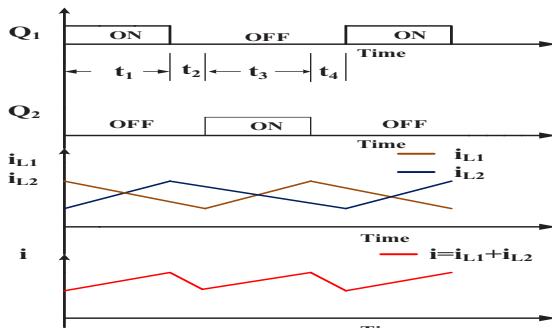

**Mode-I ( $0 < t < t_1$ ):** Fig.4 (a) depicts equivalent circuit of the mode-I. During this interval switch  $Q_1$  turned ON and switch  $Q_2$  turned OFF. Inductor current ( $i_{L1}$ ) starts increases with a slope of  $(V_{in} - V_o)/R$  and another inductor releases energy through resistor so inductor current ( $i_{L2}$ ) starts decreases with a slope of  $-V_o/R$  and inductor current directions are marked with arrows. In this mode output current is the sum of two inductor currents shown in equivalent circuit of Mode-1.

Fig.4 (a) Equivalent circuit of Mode-I

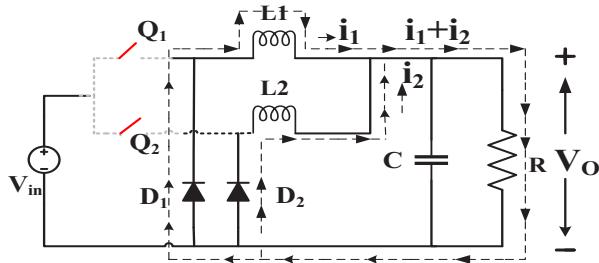

**Mode-II ( $t_1 < t < t_2$ ):** Fig.4 (b) depicts equivalent circuit of the mode-II. During this interval both the switches  $Q_1$  and  $Q_2$  are OFF. Both the inductors releases energy through resistor so inductor current starts decreasing with a slope of  $-V_o/R$ . resultant current also starts decreasing.

Fig.4 (b) Equivalent circuit of Mode-2

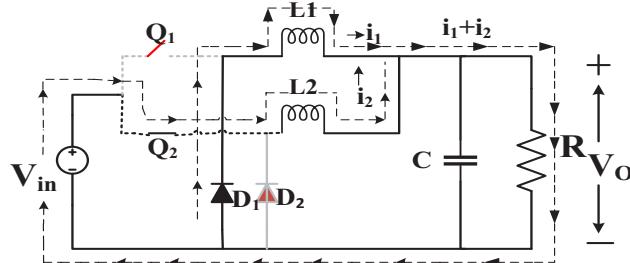

**Mode-III ( $t_2 < t < t_3$ ):** Fig.4 (c) depicts equivalent circuit of the mode-III. During this interval switch  $Q_1$  turned OFF and switch  $Q_2$  turned ON. Inductor current ( $i_{L2}$ ) starts increases with a slope of  $(V_{in}-V_0)/R$  and another inductor releases energy through resistor so inductor current ( $i_{L1}$ ) starts decreases with a slope of  $-V_0/R$  and inductor current directions are marked with arrows. In this mode output current is the sum of two inductor currents shown in equivalent circuit of Mode-III.

Fig.4 (c) Equivalent circuit of Mode-3

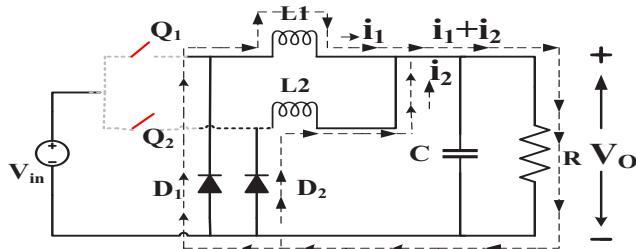

**Mode-IV ( $t_3 < t < t_4$ ):** Fig.4 (d) depicts equivalent circuit of the mode-IV. During this interval both the switches  $Q_1$  and  $Q_2$  are OFF. Both the inductors releases energy through resistor so inductor current starts decreasing with a slope of  $-V_0/R$ . resultant current also starts decreasing. Sample waveforms for each modes of operation explained below is described in figure 5.

Fig.4 (d) Equivalent circuit of Mode-4

Fig. 5. Sample waveform of modes of operation

### C. Design of Circuit Components of IBC

#### Inductor design

Inductor value can be designed by considering the ripple in the inductor current to be a maximum value of 2% [7]. As a worst case when the duty cycle  $D = 0.25$ ,  $N = 2$  (no. of parallel converters),  $f_s=40$  kHz (switching frequency), input supply voltage is 20 V, the inductor value designed with (3) is  $L=2.5mH$ .

$$L(D) = \frac{V_{DC}}{\Delta I_0 \cdot f_s} \cdot D \cdot N \cdot \frac{\prod_{i=1}^N \left| \frac{i}{N} - D \right|}{\prod_{i=1}^{N-1} \left( \left| \frac{i}{N} - D \right| + \frac{1}{N} \right)} \quad (3)$$

#### Output capacitor design

Output Capacitor is designed by considering output voltage ripple as 1% under low duty cycle operation. Here a duty cycle  $D = 0.25$ ,  $f_s = 40$  kHz where the inductor current ripple is considered as maximum during inductor design. From (4) it is identified that the capacitor value will be very less for  $D < 0.5$ . Also the output voltage frequency of interleaved buck converter is  $2f_s$ . Hence the capacitor can be designed to a very low value with the output voltage ripple as 1%.

$$C_0 = \frac{1-2D}{16f_s^2 \cdot L_1 \left( \frac{\Delta V_0}{V_0} \right)} = 2 \mu F \quad (4)$$

#### Input capacitor design

Input capacitor is designed by considering input voltage ripple as 12 %. From (5) the value of input capacitor can be designed [8].

$$\text{Input capacitor } C_{IN} = \frac{I_{in}(1-2D)}{2\Delta V_{in} \cdot f_s} \quad (5)$$

$$C_{IN} = 3 \mu F$$

$$\text{Input average current } I_{in} = \frac{P_{out}}{V_{in}}$$

$$\text{where } D \text{ is minimum duty cycle is } 0.325 = \frac{V_{out}}{V_{in}}$$

$$\Delta V_{in}, \text{input voltage ripple} = 2.25V$$

$$\% \text{Voltage ripple} = 12 \%$$

$$\text{Switching frequency } (f_s) = 40 \text{ kHz}$$

Current rating of input capacitor can be derived from (6)

$$I_{rms} = \sqrt{\frac{2}{3} D(\Delta I)^2 + I_{in}(1-2D)} \quad (6)$$

$$I_{rms} = 0.79A$$

## IV. CONTROLLER DESIGN

The plant transfer functions of IBC can be determined by state space averaging technique [9] [10].

#### A. Calculation of plant transfer function

For each modes of operation, separate state space equations derived and those equations are averaged over a time period,  $T$ . [3] Perturbing these averaged state space equations around the operating point and equating steady state terms and first order terms will give:

$$\frac{dx(t)}{dt} = Ax + B(d)V_{in} + B(D)v_{in} \quad (7)$$

$$y(t) = Cx(t) \quad (8)$$

Appling superposition principle on (7) and (8) by keeping input voltage ( $v_{in}$ ) perturbations as zero and to find transfer functions of ( $i_{L1}$  &  $i_{L2}$ ) with respective to duty ratio perturbation ( $d_1$  &  $d_2$ ).

By taking Laplace transform of above equations (7) & (8), making source perturbations to zero

$$G(s) = C(SI - A)^{-1}BV_{in} \quad (9)$$

$$\frac{I_{L1}(s)}{d_1(s)} = \frac{V_{in}}{L_1} \cdot \frac{s + \frac{1}{rC}}{s^2 + \frac{1}{rC} + \frac{1}{C \cdot L_{eq}}} \quad (10)$$

$$\frac{I_{L2}(s)}{d_2(s)} = \frac{V_{in}}{L_2} \cdot \frac{s + \frac{1}{rC}}{s^2 + \frac{1}{rC} + \frac{1}{C \cdot L_{eq}}} \quad (11)$$

where  $r = R_{LED}$ ,  $L_{eq} = L_1 \parallel L_2$

### B. Design Procedure of Compensator

The compensator is designed for the IBC as shown in figure 6. As the inductor current dynamics should be faster than the capacitor voltage dynamics the controller is divided in to two loops i.e., two inner current loops and one outer voltage loop. Hence it is assumed that bandwidth of inner loop must be greater than that of outer loop. For different values of bandwidth and phase margin,  $K_p$  and  $K_i$  values for both current and voltage controllers can be designed [10].

Fig.6. Control strategy block diagram with voltage and current loops of IBC

Voltage loop band width is varied and inner current loop band width keeping constant as 4.2 kHz and phase margin as 60° different values of  $K_p$  and  $K_i$  are tabulated in table III. As the voltage loop bandwidth decreases settling time and rise time increases and as the phase margin decreases the transient response will be very fast.

TABLE III :  $K_p$   $K_i$  VALUES OF VARYING BANDWIDTH

| S. no | P M (Φ) | B W (Hz) | CC $K_p$ | CC $K_i$    | VC $K_p$ | VC $K_i$ |

|-------|---------|----------|----------|-------------|----------|----------|

| 1     | 90      | 944      | 28.128   | 478630.0923 | 0.01255  | 724.4    |

| 2     | 90      | 182      | 28.128   | 478630.0923 | 0.017    | 158.78   |

| 3     | 55      | 2720     | 28.128   | 478630.0923 | 0.0718   | 1778.27  |

PM: PHASE MARGIN, BW: BAND WIDTH, CC:CURRENT CONTROLLER VC: VOLTAGE CONTROLLER

### C. LT Spice circuit design and LT Spice Simulation Results

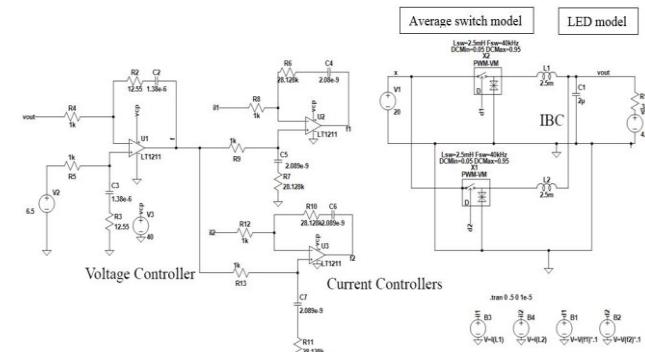

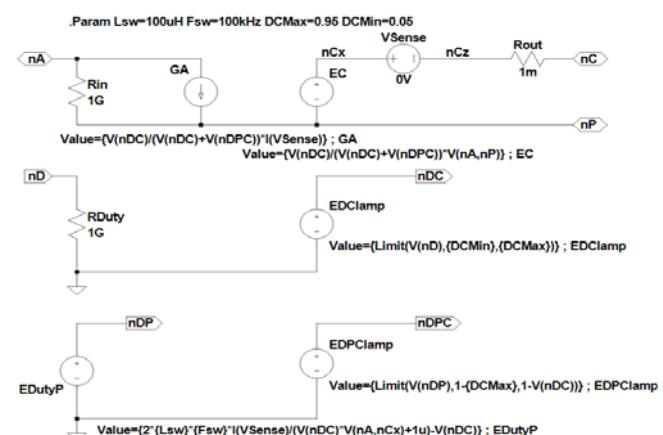

The closed loop IBC is designed in Linear Technology simulation software as shown in figure 7. In this simulation the switch and diode were replaced by average switch model.

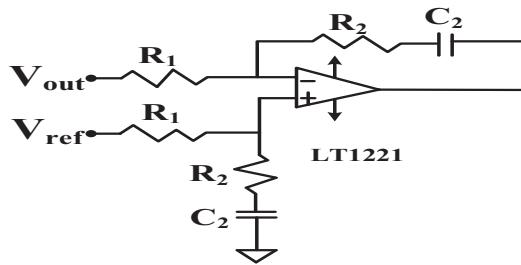

The switch model is shown in figure 8. In this simulation PI controller is implemented by a differential amplifier using Op- Amp LT 1211. Figure 9 shows the implementation of differential amplifier For respective  $K_p$  and  $K_i$  values shown in Table III the controller parameters  $R_1$ ,  $R_2$  and  $C_2$  are designed with (12) and (13).

$$K_p = \frac{R_2}{R_1} \quad (12)$$

$$K_i = \frac{1}{R_1 \cdot C_2} \quad (13)$$

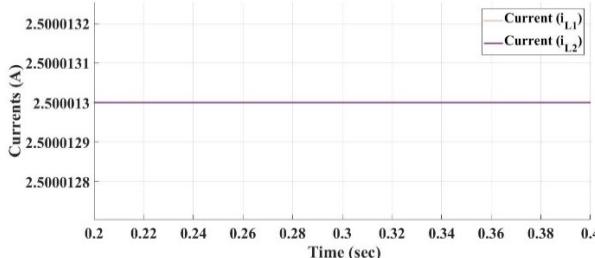

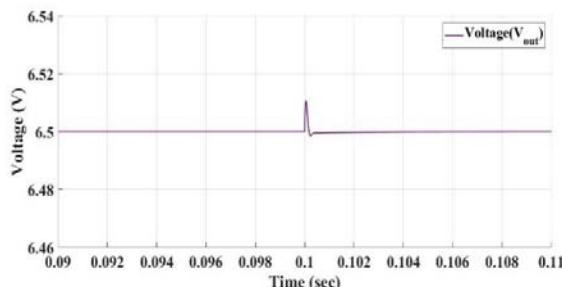

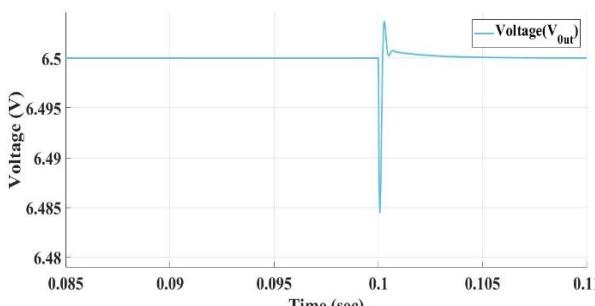

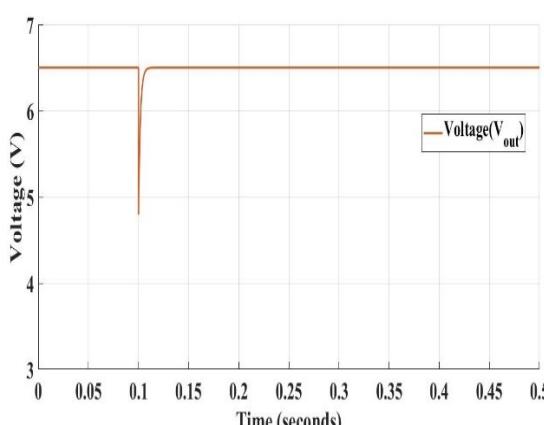

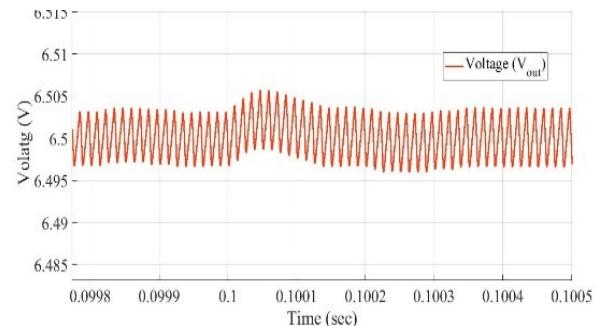

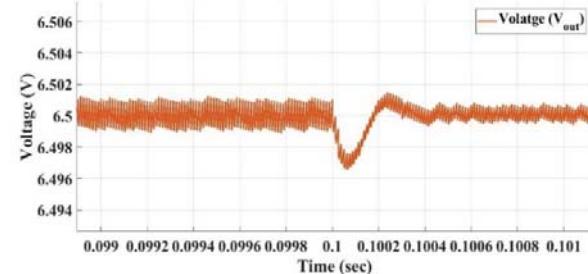

Average techniques are developed to represent buck, boost and buck boost types of switched DC-DC converters by approximate continuous models. Simple analytical expressions of the circuit components are derived for the characteristics transient and frequency response. Switch and diode can be replaced by three terminals and termed as Verperian model. Figure 10 shows the waveform of inductor currents, no switching ripples are present as an average switch model is used in simulation. Figure 11 and 12 shows the output voltage variation with a source disturbance at 0.1 sec and figure 13 shows the load disturbance effect on output voltage. The controller will rectify the effect of disturbances as shown in the above mentioned figures.

Fig.7. Closed loop circuit diagram in LTspice with average switch model

Fig.8. Average switch model of combination of switch and diode

Fig.9. Implementation of PI in differential mode

Fig.10. Inductor current waveforms in LTspice

Fig.11. Output Voltage when input is varied from 20 V to 25 V at t=0.1 sec

Fig.12. Output Voltage when input is varied from 20 V to 15 V at t=0.1 sec

Fig.13. Output Voltage when step load of 4.5A (0.5A to 5A) at t=0.1 sec

## V. SIMULATION OF IBC IN MATLAB

### A. Simulation Parameters

Simulation of IBC is done in MATLAB-Simulink with two closed loop control, inner current loop and outer voltage loop.  $L$  and  $C$  values are designed for specified voltage and current ratings. In simulation load and source disturbances are induced and the efficiency of controlled is clearly identified. Table IV briefs the parameters of MATLAB simulation. All the components are designed for efficient operation of converter.

TABLE IV : SIMULATION PARAMETERS

| Sl no | Table Column Head         |       |         |

|-------|---------------------------|-------|---------|

|       | Parameters                | Value | Unit    |

| 1     | Input voltage $V_{in}$    | 20    | V       |

| 2     | Switching frequency $f_s$ | 40    | kHz     |

| 3     | Inductor $L_1, L_2$       | 2.5   | mH      |

| 4     | Input capacitor $C_{IN}$  | 3     | $\mu$ F |

| 5     | Output capacitor $C_O$    | 2     | $\mu$ F |

### B. Simulation results and analysis

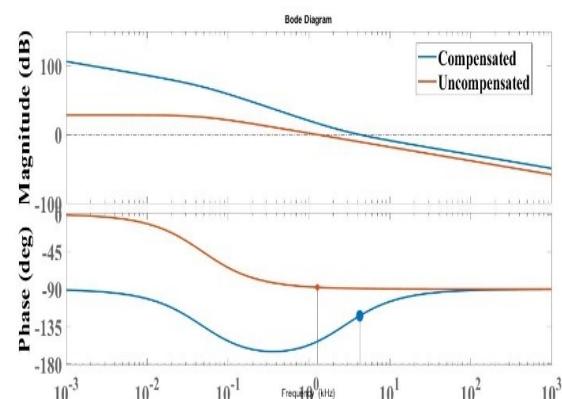

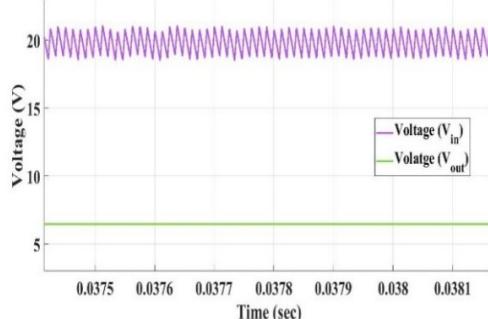

The performance of interleaved Buck converter can be evaluated by using MATLAB/Simulation platform. Figure 16 shows the input voltage of 20V with  $\pm 12\%$  allowed ripple being the ripple content in input voltage the controller take appropriate control action to make output voltage should be constant with a magnitude of 6.5V. Parameters PI controller for inner current loop and outer voltage loop is designed by using bode plots as a tool for inner current loop bandwidth of 4.2 kHz and Phase margin of 60° Bode plot of compensated and uncompensated transfer function is shown in figure 14. The proportional and integral constants obtained are 28.128 and 478630.09 respectively.

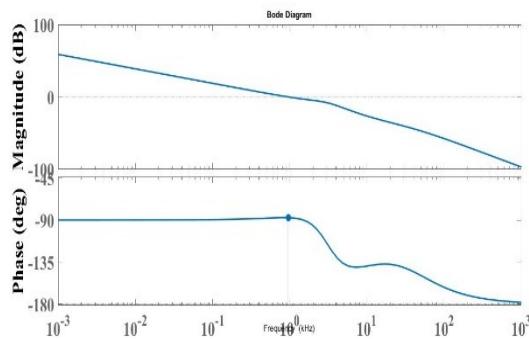

PI controller for outer voltage loop is also designed based on time based method (outer loop control action should be slower then inner loop control action). So the designed voltage controller has a bandwidth of 945Hz and phase margin of 90°. The Bode plot for the same as shown in figure 15. The proportional and integral constants obtained are 0.01255 and 724.4 respectively.

Fig. 14. Bode plot of inner current control loop with and without controller

Fig15. Bode plot of outer voltage control loop with controller

Fig.16. Input voltage (top) and Output voltage (bottom)

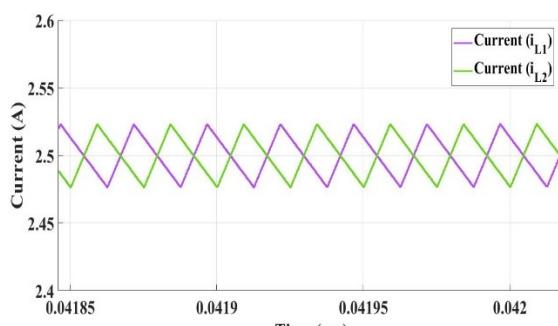

In figure 16 the input voltage  $V_{in}$  and output voltage  $V_{out}$  is shown. The waveforms briefs that the input voltage is 20V with 12% ripple as we discussed in earlier sections. The output voltage is constant 6.5V which powers the LED. Figure 17 shows the current flowing through the inductors  $L_1$  and  $L_2$  with 2% ripple which is considered during the analytical designing of inductor.

Fig.17.Inductor currents ( $i_{L1}, i_{L2}$ )

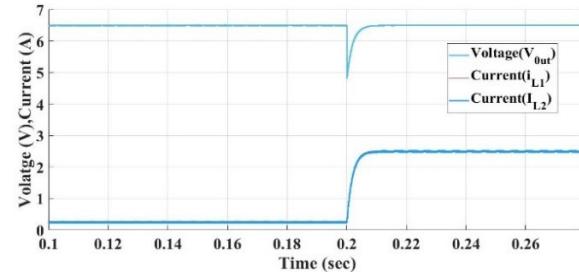

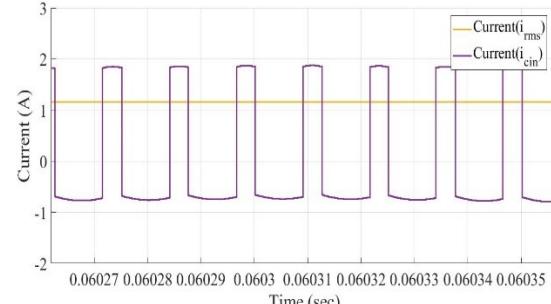

The input voltage is changing from 20V to 25V (source overshoot disturbance) and 20V to 15V (source undershoot disturbance at 0.1sec). The controller is handling the output voltage to retain its value as 6.5V after 0.1msec delay as shown in figure 18 and figure 19. Effect of load disturbance is shown in figure 20 as the load current is changed from 0.5A to 5A at 0.2 sec. The output voltage is dipped and the controller will take care the effect and stabilize the output voltage back to 6.5 V. Figure 21 shows the input capacitor current and its RMS waveform which explains that the value of  $I_{rms} = 1.14$  A is near to the designed value as per (6). Thus the analytical and simulation results seems to be matching.

Fig.18. Output voltage when Input is varied from 20V to 25V, at  $t = 0.1$  secFig.19. Output voltage when Input is varied from 20V to 15V, at  $t = 0.1$  secFig.20.  $V_{out}$  and  $i_{L1}$  and  $i_{L2}$  when a step load of 4.5 A were injected

Fig.21. Input capacitor current and RMS value

## VI. CONCLUSION

In this paper an interleaved buck converter is designed and the simulation is done in MATLAB 2017 and LT spice XVII environment. The converter is designed for driving the LED array to ensure the output voltage to be constant and ripple current to be very small. The double loop controller is designed for stabilizing the outputs for load and source disturbances with a much faster response.

Moreover, the main advantages of the proposed interleaved buck converter as LEDs driver are the ability to reduce the ripple current to a minimum level as the ripple current frequency is twice the switching frequency, thus the output capacitor required to maintain output voltage constant

is very small. Source current waveform of IBC is uniform when compared to that of buck converter. Input capacitor is designed to keep the input current as without any discontinuity. The RMS current rating of input capacitor is small compared to buck converter and is discussed in previous chapter. So the input capacitor value designed to be very small. Effect of load disturbance in the output voltage is diminished by the controller and the value is stabilized at 6.5V. The source disturbances injected develops a variation in output voltage which is taken care by controller as explained in the results of simulation. The load and source disturbance effects which is implemented in MATLAB and LTspice XVII are rectified by controller with higher efficiency which improves the life time of LED. The application of this converter can be easily implemented from dc sources, such as batteries or ultra-capacitors.

Future development of this paper includes the hardware analysis of this work and can be designed and developed for high power applications. Hard ware can be implemented using D-Space 1104.

## REFERENCES

- [1] M. A. Juárez, J.A. Martínez, G. Vázquez, J. M Sosa P. R, Martínez, I. Villanueva R, Osorio, “**A model for electrical characteristics of high power UV LED**” 2016 13<sup>th</sup> International conference on Power Electronics (CIEP). 20-23 June 2016.

- [2] Ray-Lee Lin, Yi-Fan Chen, “**Equivalent circuit model of Light Emitting Diode fro system analisis of Lighting**” 2009 IEEE Industry ApplicationsSociety Annual Meeting.

- [3] Andressa C. Schittler, Douglas Pappis, Cassiano Rech, Alexandre Campos, Marco A. Dalla Costa, “**Generalized State-space Model For The Interleaved Buck Converter**” XI Brazilian Power Electronics Conference, 21 November 2011.

- [4] S. Iturriaga-Medina, P.R. Martinez-Rodriguez, M. Juarez-Balderas, J.M. Sosa and C.A. Limones, “**A buck converter controller design in an electronic drive for LED lighting applications**” 2015 IEEE International Autumn Meeting on Power Electronic and Computing (ROPEC) ,01 February 2016.

- [5] Jorge Garcia, Antonio J. Calleja, Emilio L'opez Corominas, David Gacio Vaquero, Lidia Campa, “**Interleaved Buck Converter for Fast PWM Dimming of High-Brightness LEDs**” IEEE Transactions on Power Electronics, vol. 26, no. 9, september 2011

- [6] Beczkowski, Szymon; Munk-Nielsen, Stig, “**Two phase interleaved buck converter for driving high power LEDs**” Published in: Proceedings of the 14th European Conference on Power Electronics and Applications (EPE 2011), United Kingdom.

- [7] Mohamed. A. Shrud, Ahmad Kharaz, Ahmed. S. Ashur, Mustafa Shater and Ismail Benyoussef, “**A study of Modeling and Simulation for Interleaved Buck Converter**” 2010 1st Power Electronic & Drive Systems & Technologies Conference (PEDSTC) , 24 May 2010

- [8] High Efficiency, High Density, PolyPhase Converters for High Current Applications, “**Linear Technology**” Sept 1999.

- [9] “**Analysis And Design Of Input Filter For DC-DC Circuit SNV4801**”–November 2017 Copyright © 2017, Texas Instruments Incorporated

- [10] R.W. Erickson and D. Maksimovic, “**Fundamentals of power electronics**”, 2nd ed. New York: Kluwer, 2001.

**Sangani Prashanth** received B.Tech degree in Electrical and Electronics Engineering from JNTU University in year 2016, Hyderabad, India and pursuing M.Tech degree in Power Electronics and Drives from National Institute of Technology, Warangal, India. His research interests include design and modeling of DC-DC Converters.

**Udaya Bhasker Manthati** received B.Tech degree in electrical and electronics engineering and M.E. in power electronics & drives in 2003 and 2006. And Ph.D. in electrical engineering in 2011. Since 2012, he has been working as assistant professor in department of electrical engineering at National Institute of Technology-Warangal, India. In 2011, he worked as assistant professor at Manipal University Jaipur-India. He was a research assistant at CITCEA-UPC, Spain during 2007-2011. His research interest include bi-directional DC-DC converters, power electronics application to micro grid and smart grid technologies, energy storage systems, digital control and synchrotrons power supplies. He is a recipient of SLL-UPC fellowship during 2007-2010.

**Vishnu Sidharthan P** received B.Tech degree in Electrical and Electronics Engineering from Mahatma Gandhi University, Kottayam, India and M.Tech degree in Power Electronics from Amrita University, Coimbatore, India in the years 2012 and 2015 respectively. He is presently working as Junior Research Fellow at National Institute of Technology, Warangal, India. His research interests include design and modeling of DC-DC Converters interface for Piezoelectric energy Harvesting applications, Efficient Power Electronics controlling of Electric vehicle.

**Punna Srinivas** received B.Tech degree in electrical and electronics engineering from JNTU, Hyderabad, India and M.Tech degree from National Institute of Technology, Warangal, India in the years 2006 and 2009 respectively. He is presently working towards Ph.D. degree from National Institute of Technology, Warangal, India. His research interests include design and modeling of DC-DC converters for Energy storage systems, DC-micro grid integrated Hybrid energy storage systems.