# PV Distributed-MPP Tracking: Total-Cross-Tied Configuration of String-Integrated-Converters to Extract the Maximum Power Under Various PSCs

Suneel Raju Pendem, *Student Member, IEEE*, Suresh Mikkili , *Member, IEEE*, and Praveen Kumar Bonthagorla, *Student Member, IEEE*

**Abstract**—The building integrated photovoltaic (PV) central inverter architecture comprises various PV module configurations. The PV module configurations are vulnerable to shading effects and cause mismatching power losses. To reduce the detrimental impact of shading and mismatching on energy production, the PV distributed-maximum power point tracking (D-MPPT) architecture has been proposed. In this architecture, an individual dc–dc converter with an MPPT controller is integrated to each PV module for extracting the maximum power. This topology is referred to as module-integrated-converter (M-I-C). In the conventional PV D-MPPT architecture, the output terminals of M-I-Cs are connected either in series or parallel configuration only. The conventional configurations of M-I-Cs have the drawbacks of cross-coupling effects, lower conversion efficiency, two-stage voltage conversion, etc. This paper proposes the total-cross-tied (T-C-T) configuration of string-integrated-converters (S-I-Cs) to overcome the drawbacks of M-I-C configurations. The detailed mathematical analysis of the proposed T-C-T configuration of S-I-Cs is also presented in this paper. The perturb and observe MPPT technique is used for extracting the maximum power. The performance of the proposed T-C-T configuration of S-I-Cs is analyzed under various partial shading conditions and also compared with the PV central inverter architecture as well as with conventional M-I-C configurations.

**Index Terms**—Cross-coupling effects, distributed-maximum power point tracking (D-MPPT), maximum power point (MPP), module-integrated-converters (M-I-Cs), partial shading, perturb and observe (P&O) MPPT, string-integrated-converters (S-I-Cs), total-cross-tied (T-C-T) configuration.

## I. INTRODUCTION

THE utilization of renewable energy sources has enticed more and more courtesy due to its sustainability and environment friendly nature. Among the various renewable energy sources, the power generated by solar photovoltaic (PV) systems has been raised 20%–25% per annum over the last 20 years due to reduction in the cost of PV modules, government incentives,

Manuscript received October 12, 2018; revised April 8, 2019 and May 16, 2019; accepted May 25, 2019. Date of publication June 12, 2019; date of current version February 27, 2020. This work was supported by the Science and Engineering Research Board (SERB), Department of Science and Technology, Government of India, under Grant ECR/2017/000316. (Corresponding author: Suresh Mikkili.)

The authors are with the Electrical and Electronics Engineering Department, National Institute of Technology Goa, Ponda 403401, India (e-mail: psuneelraju.eee@nitgoa.ac.in; mikkili.suresh@nitgoa.ac.in; praveen.nitgoa2017@gmail.com).

Digital Object Identifier 10.1109/JSYST.2019.2919768

and also inventive business models in the grid integrated and stand-alone PV system applications [1], [2]. The power rating of PV installation systems ranges from few kilowatts to several megawatts. Generally, the performance of PV system depends on the PV system architectures [3]–[5], PV module configurations [6], [7], maximum power point tracking (MPPT) techniques [8]–[10], dc–dc converter topologies [11]–[13], and inverter topologies [14], [15].

The PV module is an important device of a PV system, typically composed of 30–50 PV cells connected in a series connection. The PV system architecture depends on the arrangement of PV modules, number of converter stages, and the type of MPPT techniques used for extracting the maximum power [3]. Generally, the building integrated PV systems have the central inverter architecture [16], [17]. The PV central inverter architecture comprises various PV module configurations, such as series, parallel, series-parallel, total-cross-tied (T-C-T), series-parallel-T-C-T, bridge-linked-T-C-T, honey-comb-T-C-T, [6], [7]. The output power from the PV module configurations decreases considerably due to mismatching and partial shading conditions (PSCs) [18]. The PV module configurations have several connections among the PV modules, hence it brings more complicity in addition to the mismatching power losses. This architecture has an additional problem in maintenance and control operations since a failure in one PV module placed at a big facade or rooftops is difficult to detect. The problems due to mismatching power losses have been addressed by connecting a bypass diode in anti-parallel to each PV module [19]. However, the bypass diode connection results in multiple maximum power points (MPPs) in the nonconvex output power versus output voltage characteristics [20]. There are numerous optimization techniques available in the literature for tracking the global maximum power, but they are complex and may fail in tracking the maximum available power under some instances [9], [10].

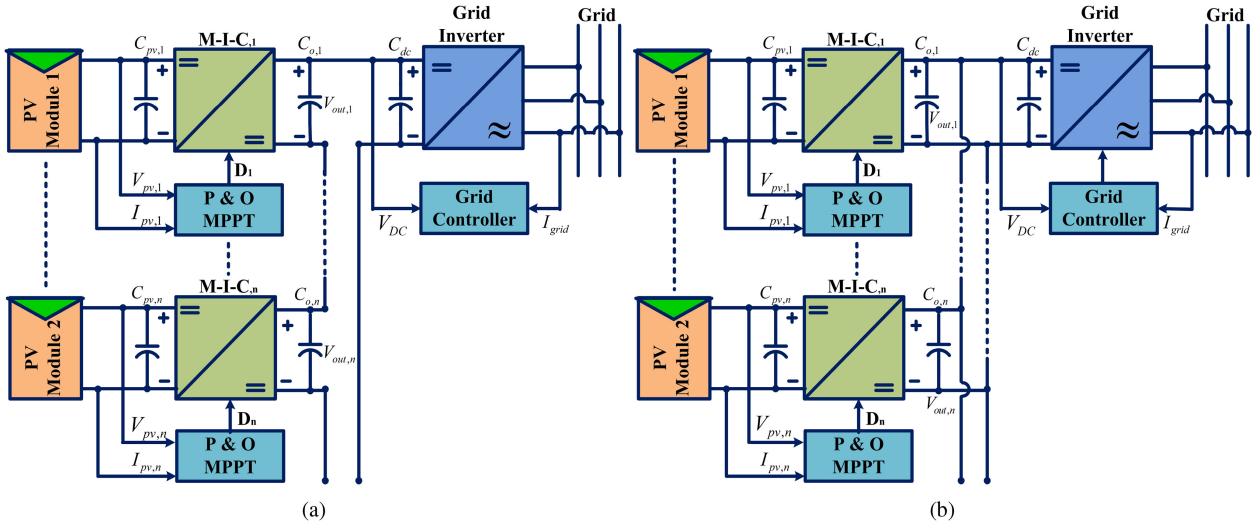

The PV distributed-MPPT (D-MPPT) architecture is an effective solution for building integrated PV systems to overcome the problems of mismatching and PSCs [21]. The PV D-MPPT architecture has an advantage of quick detection of failures in PV module operation and would avoid power losses due to malfunctioning of PV systems. In this architecture, the output terminals of the M-I-Cs are connected either in series or parallel configuration as shown in Fig. 1 [22]. In a series configuration, the output terminals of the M-I-Cs are connected in series. Thus, the dc-link

Fig. 1. Conventional configurations of M-I-Cs. (a) Series configuration. (b) Parallel configuration.

voltage is distributed between the output terminals. In a parallel configuration, the output terminals of the M-I-Cs are connected directly to the dc-link. Therefore, each M-I-C has to endure a full dc-link voltage. The series and parallel configurations of M-I-Cs are having certain drawbacks [23]. In a series configuration, the operating points of M-I-Cs deviate from the MPP due to cross-coupling effects and hence the output power of the PV system reduces [24]. The cross-coupling effect is an undesired phenomenon of cascaded converters, causing disturbances in the M-I-Cs operation and power generation. The parallel configuration of M-I-Cs is free from cross-coupling effects, but the drawbacks of parallel configuration are two-stage voltage conversion, use of isolated converters, higher duty ratios, higher voltage stress on the switches, and lower conversion efficiency. To overcome the drawbacks of series and parallel configuration of M-I-Cs, this paper proposes T-C-T configuration for string-integrated-converters (S-I-Cs).

The proposed T-C-T configuration of S-I-Cs is a subset of the hybrid configuration and also considered as one of the full-power processing structures [25]. Here, a dc–dc boost converter along with the MPPT controller is integrated to few number of PV modules which are connected in series connection (referred to as PV short-string) and is designated as S-I-C. The proposed configuration extracts the maximum power from PV short-strings by minimizing the cross-coupling effects. The performance of the proposed configuration is compared with the PV central inverter architecture and conventional series configuration of S-I-Cs under various partial shading patterns, such as uneven row, uneven column, diagonal, and long and narrow. The advantages of the proposed configuration are single-stage voltage conversion, use of nonisolated S-I-Cs, lower duty ratios, the lower voltage stress on the switches, higher conversion efficiency, etc. In view of an economic aspect, the proposed PV system requires 16 number of S-I-Cs, voltage sensors, and current sensors. Whereas, in case of conventional M-I-C configurations, the cost of the components will increase by five times.

The remaining of this paper is organized as follows. Section II describes the PV short-string  $I - V$  and  $P - V$  characteristics, the design of S-I-Cs, the implementation of perturb and observe (P&O) MPPT technique in MATLAB/Simulink environment, and the proposed PV D-MPPT architecture with the T-C-T configuration of S-I-Cs. The modeling and description of various shading patterns under PSCs are given in Section III. Section IV describes the performance of proposed T-C-T configuration of S-I-Cs and its comparison with the PV central inverter architecture as well as with the series configuration of S-I-Cs. Finally, Section V highlights the relevant conclusions of this paper.

## II. MODELING OF PROPOSED PV D-MPPT ARCHITECTURE

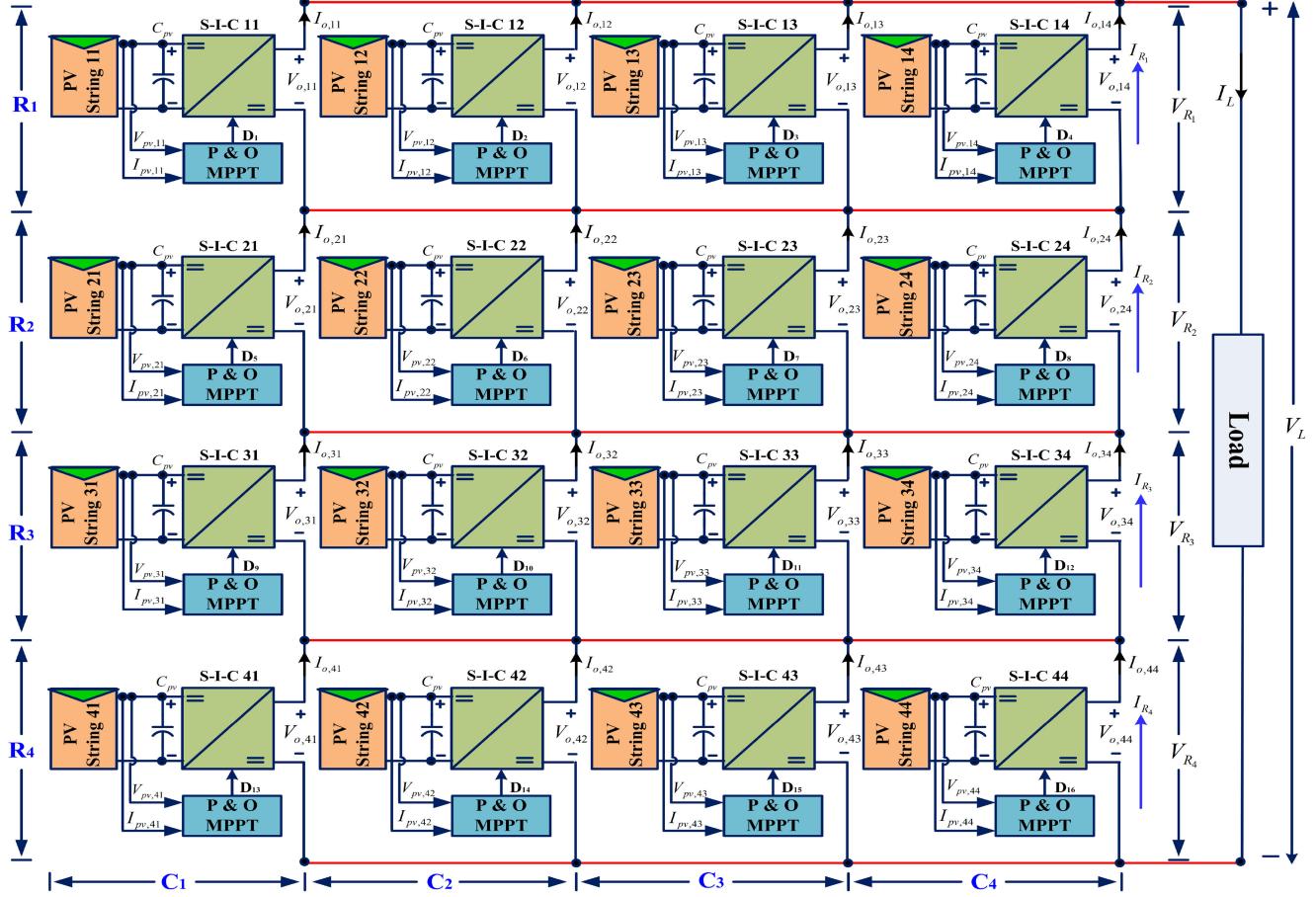

The proposed PV D-MPPT architecture with the T-C-T configuration of S-I-Cs is modeled for a power rating of 4.96 kW at standard test condition (STC) and is driving a resistive load as depicted in Fig. 2. It comprises of PV short-strings, S-I-Cs, and P&O MPPT controllers.

### A. PV Short-String Characteristics

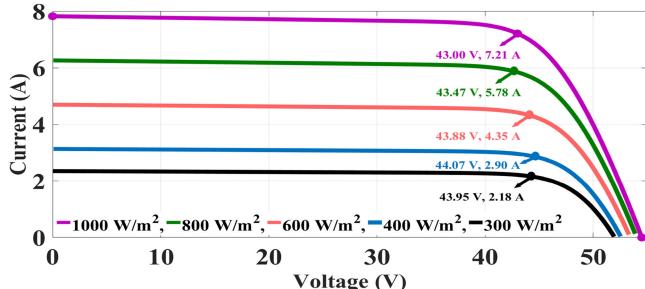

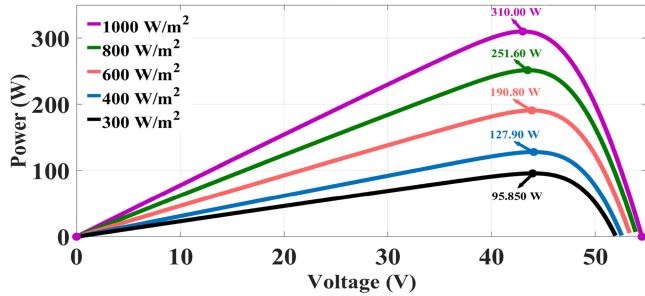

The PV short-string has a series connection of five number of PV modules (model no: SHARP-ND-62RU2). For implementing the proposed PV D-MPPT architecture, 16 PV short-strings are considered. At STC, a single PV short-string generate the power of 310.03 W at the MPP voltage and current (43 V, 7.21 A). Fig. 3 shows the  $I - V$  and  $P - V$  characteristics of a single PV short-string under various solar insolation levels [26]. At an insolation of 800, 600, 400, and 300 W/m<sup>2</sup>, the PV short-string generate the power of 251.60, 190.80, 127.90, and 95.850 W, respectively. The corresponding operating voltage and current are (43.47 V, 5.78 A), (43.88 V, 4.35 A), (44.07 V, 2.90 A), and (43.95 V, 2.18 A), respectively.

### B. Design of S-I-C

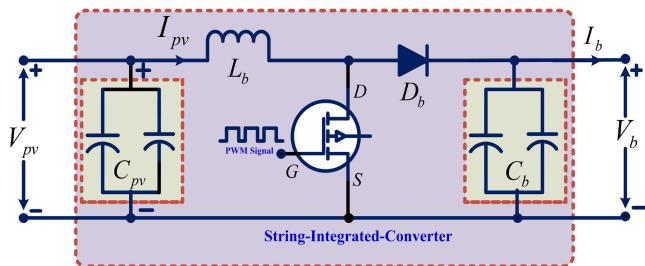

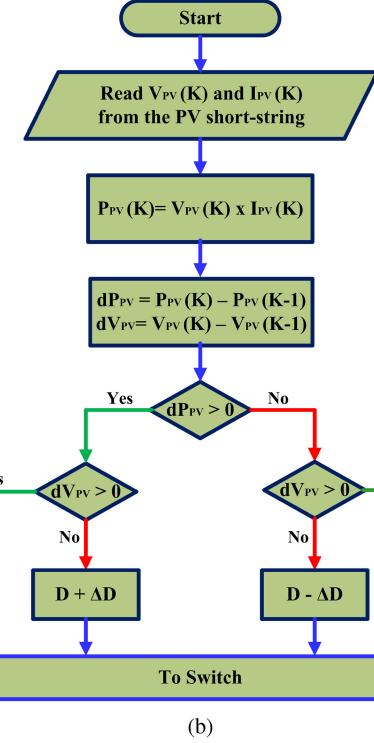

Fig. 4 shows the circuit connection of a single S-I-C (non-isolated dc–dc boost converter) which ensures an efficient MPPT

Fig. 2. Proposed T-C-T configuration of S-I-Cs.

and it is also used to boost the output voltage of the PV short-string. The PV short-string output voltage ( $V_{pv}$ ) and current ( $I_{pv}$ ) at MPP are considered as the input parameters to the S-I-C. The components of the S-I-C are, main MOSFET switch ( $SW_b$ ), output diode ( $D_b$ ), inductor ( $L_b$ ), input capacitor ( $C_{pv}$ ), and output capacitor ( $C_b$ ). The design parameters of the S-I-C are given as follows [27].

1) *Selection of Input Capacitor:* The input capacitor ( $C_{pv}$ ) is directly interfaced between the output terminals of the PV short-string and the input terminals of the S-I-C to smoothen the output voltage. The capacitance  $C_{pv}$  of the input capacitor can be calculated by

$$C_{pv} = \frac{\Delta I_L}{8 \times \Delta V_{pv} \times F_{sw}} \quad (1)$$

where  $\Delta I_L$  is the inductor current ripple,  $\Delta V_{pv}$  is the PV short-string output voltage ripple and  $F_{sw}$  is the switching frequency of the main switch ( $SW_b$ ), respectively.

2) *Selection of Inductor:* The inductor has continuous current from the output terminals of PV short-string and is used to smoothen the current. Its current rating is always higher than the short-circuit current of the PV short-string. The inductance ( $L_b$ )

of the inductor can be calculated by

$$L_b = \frac{V_{pv} \times D}{2 \times \Delta I_L \times F_{sw}} \quad (2)$$

where  $V_{pv}$  is the output voltage of the PV short-string and  $D$  is the duty ratio of the main switch ( $SW_b$ ), respectively. The relation between the input voltage ( $V_{pv}$ ) and output voltage ( $V_b$ ) of S-I-C is expressed by (3). Similarly, the relation between the input current ( $I_{pv}$ ) and output current ( $I_b$ ) of the S-I-C is expressed by (4)

$$V_b = \frac{V_{pv}}{1 - D} \quad (3)$$

$$I_b = I_{pv} (1 - D). \quad (4)$$

3) *Selection of Output Capacitor:* The output capacitor is used to smoothen the output voltage of the S-I-C. The capacitance ( $C_b$ ) of the output capacitor can be calculated by

$$C_b = \frac{V_o \times D}{2 \times \Delta V_o \times R_b \times F_{sw}} \quad (5)$$

where  $V_o$  is the output voltage,  $\Delta V_o$  is the output voltage ripple, and  $R_b$  is the load resistance of each S-I-C.

4) *Selection of Power Devices:* The MOSFET power electronic switch ( $SW_b$ ) has been chosen based on the PV short-string

(a)

(b)

Fig. 3. PV short-string characteristics under various insolation levels. (a)  $I$  –  $V$  characteristics. (b)  $P$  –  $V$  characteristics.

Fig. 4. Circuit connection of an S-I-C (nonisolated boost converter).

output voltage and current rating. The specifications of  $SW_b$  should be higher than the PV short-string output voltage and current ratings.

The reverse voltage rating is the main characteristic for selecting the power diode ( $D_b$ ) and it is decided by the output voltage of S-I-C. The current rating of  $D_b$  is lower than the PV short-string output current.

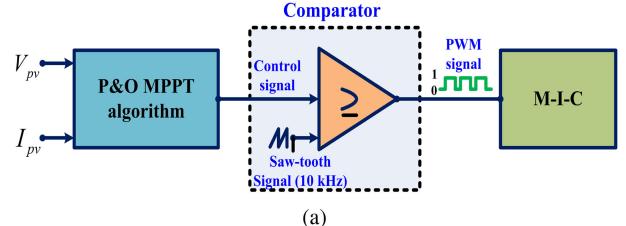

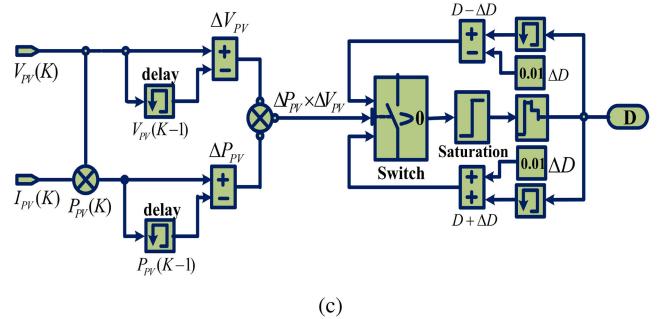

### C. Implementation of P&O MPPT Technique

The P&O MPPT technique is the simplest and classical method to extract the maximum power from PV short-strings. Fig. 5(a) shows the functional block diagram of the PV fed S-I-C. As shown in Fig. 5(a),  $V_{pv}$  and  $I_{pv}$  are given as input parameters to the MPPT controller, and it generate the control signal at the output. The control signal is compared with the saw-tooth waveform of frequency 10 kHz for generating the PWM signal. The generated PWM signal is fed to the S-I-C for extracting the maximum power. The flowchart of the P&O MPPT algorithm and its implementation in MATLAB/Simulink environment are

(a)

(b)

(c)

Fig. 5. P&O MPPT controller implementation. (a) Block diagram of PV fed S-I-C. (b) P&O MPPT algorithm and (c) MATLAB/Simulink model of the P&O MPPT algorithm.

shown in Fig. 5(b) and (c), respectively [28]. In the P&O MPPT technique, a voltage perturbation ( $\Delta V_{pv}$ ) is provided with respect to the change in the power of the PV short-string ( $\Delta P_{pv}$ ), and the corresponding perturbation in the duty ratio ( $\Delta D$ ) of the S-I-C is expressed by

$$D_{\text{new}} = \begin{cases} \frac{dP}{dV} = 0, & D_{\text{old}} \\ \frac{dP}{dV} < 0, & D_{\text{old}} - \Delta D \\ \frac{dP}{dV} > 0, & D_{\text{old}} + \Delta D. \end{cases} \quad (6)$$

The two important parameters for implementing the P&O MPPT technique are selection of perturbation step-size ( $\Delta D$ ) and perturbation step-time ( $T_a$ ). The perturbation step-size ( $\Delta D$ ) determines the efficiency and convergence speed of the MPPT algorithm. The convergence speed of MPPT algorithm can be improved by selecting larger perturbation step-size, which depreciates the efficiency of MPPT controller, and vice-versa. The perturbation step-time ( $T_a$ ) should be greater than the settling time of a system for a step change in the duty cycle. In this paper, for implementing the P&O MPPT technique,  $\Delta D$  and  $T_a$  are selected as 0.01 and 25 ms.

#### D. Proposed T-C-T Configuration of S-I-Cs

The proposed PV D-MPPT architecture comprises 16 number of PV short-strings and S-I-Cs. Each S-I-C along with a MPPT controller is integrated to a PV short-string. Initially, the output terminals of the S-I-Cs are connected in a series configuration and divided into four rows and four columns. The rows of the S-I-Cs are represented by  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively; and columns are represented by  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ , respectively. There by, the cross-tied connections (represented by red colour lines) between the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  forms the T-C-T configuration of the S-I-Cs. The cross-tied connections also establishes the series connection between the rows. Each row comprises the parallel connection of four S-I-Cs. The rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  comprises the parallel connection between the S-I-Cs (11, 12, 13, 14), (21, 22, 23, 24), (31, 32, 33, 34), and (41, 42, 43, 44), respectively.

Therefore, the T-C-T configuration of S-I-Cs output voltage ( $V_L$ ) is equal to sum of the output voltages of S-I-Cs across the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively, (i.e.,  $V_{R_1} + V_{R_2} + V_{R_3} + V_{R_4}$ ). Similarly, the output current ( $I_L$ ) is equal to sum of the output currents of S-I-Cs in any one of the row ( $\because I_{R_1} = I_{R_2} = I_{R_3} = I_{R_4}$ ). Hence, the output power ( $P_L$ ) of the T-C-T configuration of S-I-Cs is expressed by

$$P_L = V_L \times I_L. \quad (7)$$

The T-C-T configuration of S-I-Cs output voltage ( $V_L$ ) in terms of row voltages is expressed by (8). The row voltages in terms of output and input voltages of the S-I-Cs are expressed by (9)

$$V_L = \sum_{i=1}^4 V_{R_i} \text{ where } i \text{ represents the no. of rows} \quad (8)$$

where

$$\begin{cases} V_{R_1} = V_{o,j} = \frac{V_{pv,j}}{1-D_j} & \text{where } j = 11, 12, 13 \text{ and } 14 \\ V_{R_2} = V_{o,k} = \frac{V_{pv,k}}{1-D_k} & \text{where } k = 21, 22, 23, \text{ and } 24 \\ V_{R_3} = V_{o,l} = \frac{V_{pv,l}}{1-D_l} & \text{where } l = 31, 32, 33, \text{ and } 34 \\ V_{R_4} = V_{o,m} = \frac{V_{pv,m}}{1-D_m} & \text{where } m = 41, 42, 43, \text{ and } 44. \end{cases} \quad (9)$$

Similarly, the T-C-T configuration of S-I-Cs output current ( $I_L$ ) in terms of row currents is expressed by (10). The row currents in terms of output and input currents of the S-I-Cs are

expressed by (11)

$$I_L = I_{R_i} \text{ where } i = 1 \text{ to } 4 \quad (10)$$

where

$$\begin{cases} I_{R_1} = \sum_{j=11}^{14} I_{o,j} = \sum_{j=11}^{14} I_{pv,j} \times (1 - D_j) \\ I_{R_2} = \sum_{k=21}^{24} I_{o,k} = \sum_{k=21}^{24} I_{pv,k} \times (1 - D_k) \\ I_{R_3} = \sum_{l=31}^{34} I_{o,l} = \sum_{l=31}^{34} I_{pv,l} \times (1 - D_l) \\ I_{R_4} = \sum_{m=41}^{44} I_{o,m} = \sum_{m=41}^{44} I_{pv,m} \times (1 - D_m). \end{cases} \quad (11)$$

The variables represented in (8)–(11) are defined as follows.

- 1)  $V_{R_1}$ ,  $V_{R_2}$ ,  $V_{R_3}$ , and  $V_{R_4}$  are the voltages across the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 2)  $V_{o,j}$ ,  $V_{o,k}$ ,  $V_{o,l}$ , and  $V_{o,m}$  are the output voltages of the S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 3)  $V_{pv,j}$ ,  $V_{pv,k}$ ,  $V_{pv,l}$ , and  $V_{pv,m}$  are the operating voltages of the PV short-strings in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 4)  $I_{R_1}$ ,  $I_{R_2}$ ,  $I_{R_3}$ , and  $I_{R_4}$  are the currents through the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 5)  $I_{o,j}$ ,  $I_{o,k}$ ,  $I_{o,l}$ , and  $I_{o,m}$  are the output currents of the S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 6)  $I_{pv,j}$ ,  $I_{pv,k}$ ,  $I_{pv,l}$ , and  $I_{pv,m}$  are the operating currents of the PV short-strings in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

- 7)  $D_j$ ,  $D_k$ ,  $D_l$ , and  $D_m$  are the duty ratios of S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , respectively.

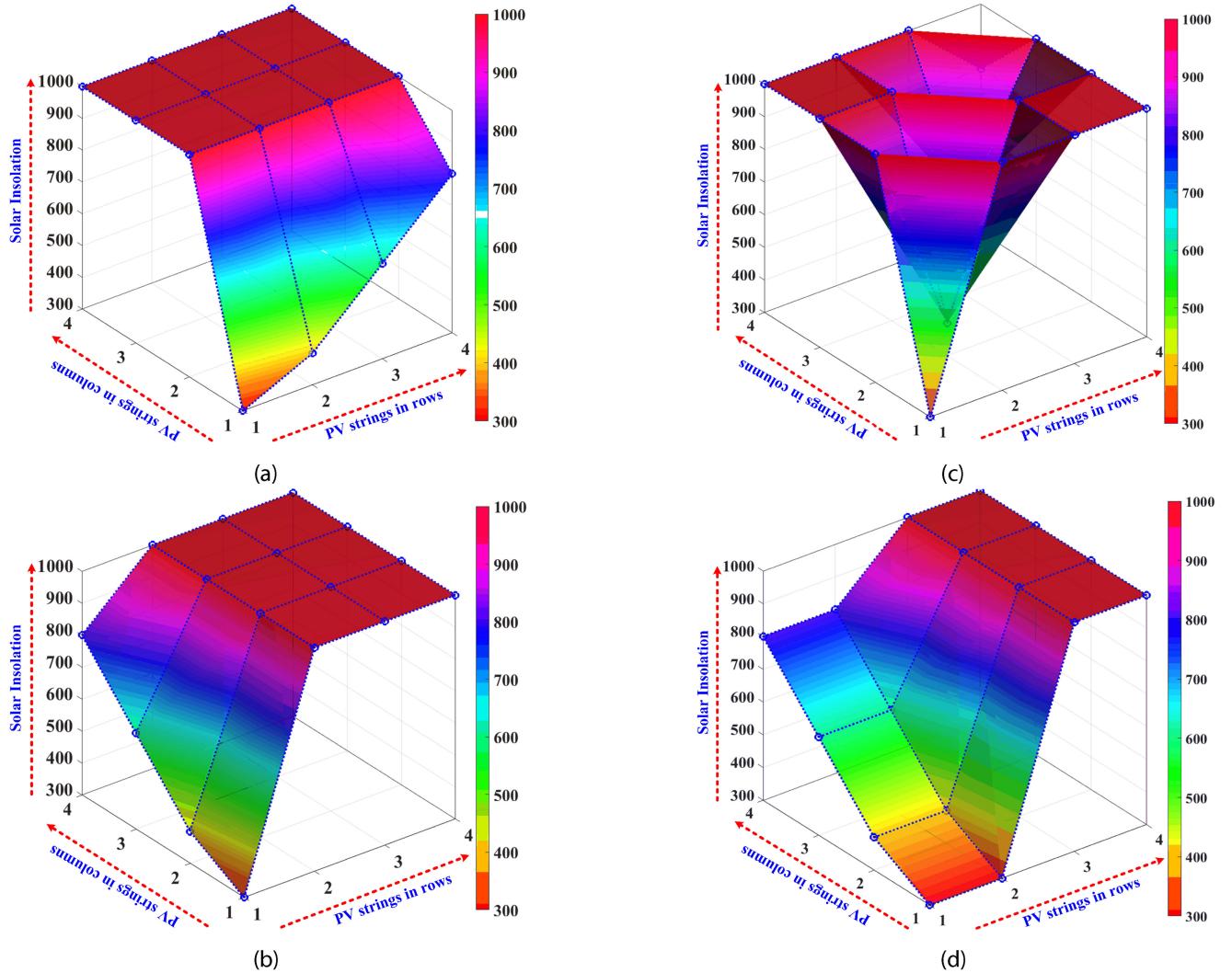

### III. MODELING OF PARTIAL SHADING PATTERNS

One of the important aspects of this paper is to analyze and investigate the performance of PV central inverter architecture, series configuration, and T-C-T configuration of S-I-Cs under various partial shading patterns, such as an uneven row, uneven column, diagonal, and long and narrow. The shading patterns and the corresponding insolation levels on the PV short-strings are represented in Fig. 6. The  $x$ -axis,  $y$ -axis, and  $z$ -axis of Fig. 6 represent the number of rows of PV short-strings (or S-I-Cs), the number of columns of PV short-strings (or S-I-Cs) and solar insolation levels, respectively.

Each shading pattern comprises five various solar insolation levels, i.e., 300, 400, 600, 800, and 1000 W/m<sup>2</sup> which represent the most dark cloud, dark cloud, cloud center, clear cloud, and full insolation, respectively. The description of each shading patterns is given as follows.

- 1) *Uneven row shading*: The cloud is spread unevenly over first row of PV short-strings and is moving from left to right as shown in Fig. 6(a). The PV short-strings 11, 12, 13, and 14 are covered by most dark, dark, cloud center, and clear cloud, respectively. The full insolation covers remaining PV short-strings.

- 2) *Uneven column shading*: The cloud is spread unevenly over first column of PV short-strings and is moving from top to bottom as shown in Fig. 6(b). The PV short-strings 11, 21, 31, and 41 are covered by the most dark, dark, cloud center, and clear cloud, respectively. The full insolation covers remaining PV short-strings.

Fig. 6. Representation of moving cloud over the PV short-strings with different insolation levels. (a) Uneven row. (b) Uneven column. (c) Diagonal. (d) Long and narrow shading pattern.

- 3) *Diagonal shading*: The cloud is spread unevenly over diagonally placed PV short-strings and is moving from top to bottom as shown in Fig. 6(c). The PV short-strings 11, 22, 33, and 44 are covered by most dark, dark, cloud center, and clear cloud, respectively. The full insolation covers remaining PV short-strings.

- 4) *Long and narrow shading*: The cloud is spread unevenly over first and second column of PV short-strings, and it is moving from top to bottom as shown in Fig. 6(d). The PV short-strings (11, 12) are covered by most dark cloud, (21, 22) are covered by dark cloud, (31, 32) are covered by cloud center (41, 42) are covered by clear cloud. The full insolation covers remaining PV short-strings.

#### IV. RESULTS AND DISCUSSIONS

This section describes the simulation results of PV central inverter architecture, series configuration, and T-C-T configuration of S-I-Cs under various shading patterns, as mentioned in

Section III. The specifications of components required for the implementing proposed PV D-MPPT architecture are listed in Table I. Initially, from  $t = 0$  to  $0.3$  s, all PV short-strings in the three PV system architectures operate at STC. At this condition, each PV short-string generate the power of 310.03 W at an operating voltage and current of 43 V and 7.21 A, respectively. The corresponding steady-state duty ratio of the S-I-Cs is 0.57. Afterward, various partial shading patterns have been applied to the PV short-strings.

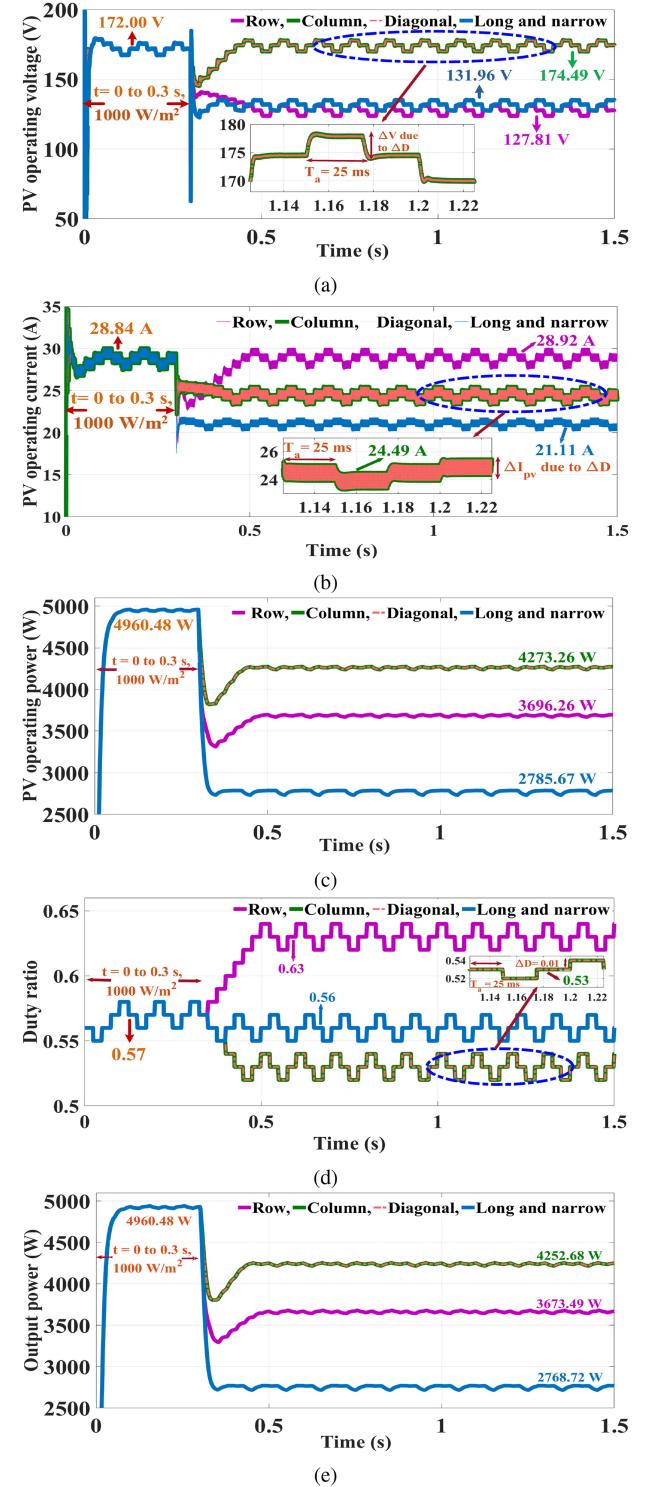

##### A. PV Central Inverter Architecture

The PV central inverter architecture [29] comprises the T-C-T configuration of PV strings, boost converter with an MPPT controller, and a resistive load ( $R_L$ ). A bypass diode is connected in anti-parallel to each PV string, to protect from hot-spot effects. The simulation results of the PV central inverter architecture under various shading patterns are shown in Fig. 7.

TABLE I

SPECIFICATIONS OF PV D-MPPT ARCHITECTURE

| Specifications                            | Values                     |

|-------------------------------------------|----------------------------|

| <i>PV Module Specifications</i>           |                            |

| Maximum power, $P_{mp}$                   | 62.006 W                   |

| Open-circuit voltage, $V_{oc}$            | 10.9 V                     |

| Short-circuit current, $I_{sc}$           | 7.82 A                     |

| Voltage at maximum power point, $V_{MPP}$ | 8.6 V                      |

| Current at maximum power point, $I_{MPP}$ | 7.21 A                     |

| Photogenerated current, $I_{Ph}$          | 7.8503 A                   |

| Diode saturation current, $I_o$           | $3.0763 \times 10^{-11}$ A |

| Diode ideality factor, $a$                | 0.89864                    |

| Series resistance, $R_s$                  | 0.14761 $\Omega$           |

| Shunt resistance, $R_{sh}$                | 38.1127 $\Omega$           |

| No. of cells per module, $n_s$            | 18                         |

| Temperature coefficient of voltage, $K_V$ | -0.30349 V/K               |

| Temperature coefficient of current, $K_I$ | 0.052801 A/K               |

| <i>S-I-C Specifications</i>               |                            |

| Inductor current ripple, $\Delta I_L$     | 10%                        |

| Input voltage ripple, $\Delta V_{PV}$     | 3%                         |

| Output voltage ripple, $\Delta V_O$       | 3%                         |

| Switching frequency, $F_{SW}$             | 10 kHz                     |

| Input voltage range, $V_{pv}$             | 40-60 V                    |

| Output voltage range, $V_b$               | 50-125 V                   |

| Input current range, $I_{pv}$             | 10 A                       |

| Output current range, $I_b$               | 4.8 A                      |

| Inductance                                | 2 mH                       |

| Input capacitance                         | 100//100 $\mu F$           |

| Output capacitance                        | 200//200 $\mu F$           |

| Resistive load to converter               | 32.255 $\Omega$            |

| <i>MPPT Parameters</i>                    |                            |

| Initial Dutyratio, $D_{initial}$          | 0.57                       |

| Maximum Dutyratio, $D_{max}$              | 0.8                        |

| Minimum Dutyratio, $D_{min}$              | 0.2                        |

| perturbation step-size, $\Delta D$        | 0.01                       |

| perturbation time, $T_a$                  | 25ms                       |

Under uneven row shading pattern, from  $t = 0$  to  $0.3$  s, each PV short-string in the rows  $R_2$ ,  $R_3$ , and  $R_4$  is generating the power of 309.95 W at an operating voltage and current (42.87 V, 7.23 A), respectively. Therefore, sum of voltages across the rows  $R_2$ ,  $R_3$ , and  $R_4$  is equal to 128.61 V (i.e.,  $V_{R_2} + V_{R_3} + V_{R_4} = 3 \times 42.87 V$ ) and each row is operating at a current of 28.92 A (i.e.,  $I_{R_2} = I_{R_3} = I_{R_4} = 4 \times 7.23 A$ ), respectively. From  $t = 0.3$  to  $1.5$  s, the row  $R_1$  is unevenly shaded. At this condition, the PV short-strings 11, 12, 13, and 14 are operating at a current of 2.18, 2.90, 4.34, and 5.78 A, respectively. Therefore, the shaded row current,  $I_{R_1}$  is equal to 15.20 A (i.e.,  $I_{pv,11} + I_{pv,12} + I_{pv,13} + I_{pv,14} = 2.18 A + 2.90 A + 4.34 A + 5.78 A$ ). Due to the series connection between all the rows, each row should be operated at the same current. Therefore, the bypass diodes across the PV short-strings 11, 12, 13, and 14 are short-circuited, and the currents flowing through them are equal to 5.05, 4.33,

Fig. 7. Results of PV central inverter architecture under various partial shading patterns. (a) PV voltages. (b) PV currents. (c) PV powers. (d) Duty ratios. (e) Output powers.

2.89, and 1.45 A, respectively. Hence, voltage across the row  $R_1$  is equal to  $-0.8$  V. Therefore, the operating power of this architecture is equal to 3696.26 W at a voltage and current of 127.81 V (i.e.,  $V_{R_1} + V_{R_2} + V_{R_3} + V_{R_4} = 128.60 V - 0.8 V$ ) and 28.92 A ( $I_{R_1} = I_{R_2} = I_{R_3} = I_{R_4}$ ), respectively.

The corresponding steady-state duty ratio of the boost converter is 0.63 and produces the output power of 3673.49 W. The power loss of the boost converter is 22.77 W.

Under uneven column and diagonal shading pattern, from  $t = 0.3$  to  $1.5$  s, the PV short-strings in the row  $R_1$  decides the operating current. The PV short-strings 12, 13, and 14 are operating at a current of 7.46 A, and PV short-string 11 is operating at a current of 2.11 A. Therefore, the operating current  $I_{R_1}$  is equal to 24.49 A [i.e.,  $I_{pv,11} + I_{pv,12} + I_{pv,13} + I_{pv,14} = 2.11 A + (3 \times 7.46) A$ ]. The corresponding operating voltages of the PV short-strings are 40.85, 42.94, 44.83, and 45.87 V, respectively. Therefore, the operating power is equal to 4273.26 W at a voltage and current of 174.49 V and 24.49 A, respectively. The corresponding steady-state duty ratio of the boost converter is 0.53 and generate the output power of 4252.68 W. The power loss of the boost converter is 20.58 W.

Similarly, under long and narrow shading pattern, from  $t = 0.3$  to  $1.5$  s, the PV short-strings in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are operating at a voltage of  $-0.8$ , 39.76, 45.74, and 47.26 V, respectively. The operating current of each row is equal to 21.11 A. The operating power is equal to 2785.67 W at a voltage and current (131.96 V, 21.11 A), respectively. The corresponding steady-state duty ratio of the boost converter is 0.56 and generate the output power of 2768.72 W. The power loss of the boost converter is 16.95 W.

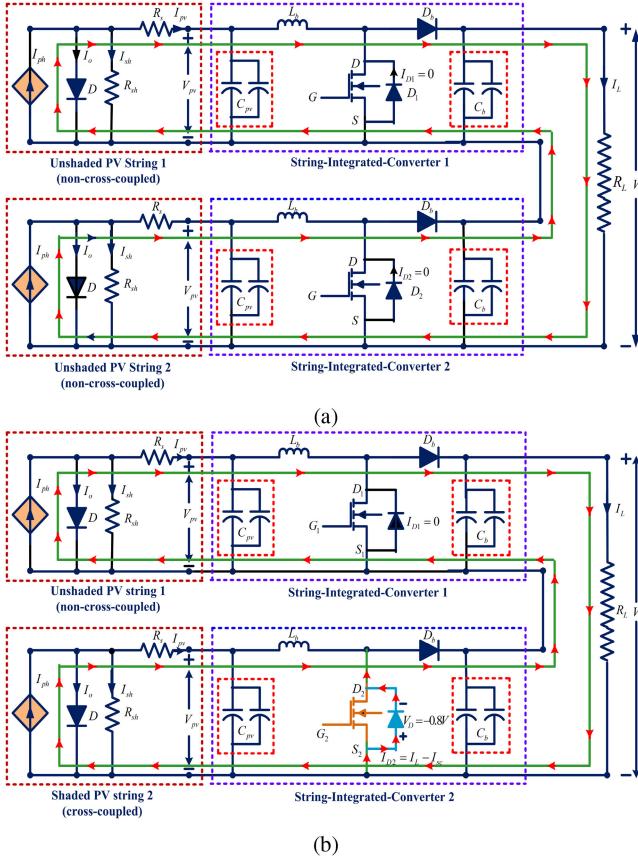

### B. Series Configuration of S-I-Cs

In this configuration, the output terminals of the S-I-Cs shown in Fig. 2 are connected in series connection (no cross-ties are presented). Therefore, the output current ( $I_L$ ) of the series configuration of S-I-Cs is same as the output current of any single S-I-C (i.e.,  $I_L = I_{o,11} = I_{o,12} = \dots = I_{o,14} = I_{o,21} = I_{o,22} = \dots = I_{o,24} = I_{o,31} = I_{o,32} = \dots = I_{o,34} = I_{o,41} = I_{o,42} = \dots = I_{o,44}$ ). The output voltage ( $V_L$ ) is equal to sum of the output voltages across all the S-I-Cs (i.e.,  $V_{o,11} + V_{o,12} + \dots + V_{o,14} + V_{o,21} + V_{o,22} + \dots + V_{o,24} + V_{o,31} + V_{o,32} + \dots + V_{o,34} + V_{o,41} + V_{o,42} + \dots + V_{o,44}$ ). The simulation results of the series configuration of S-I-Cs under various shading patterns are shown in Fig. 8.

Under uneven row, uneven column, and diagonal shading pattern from  $t = 0.3$  to  $1.5$  s, the output current is equal to 2.75 A. Therefore, to maintain each S-I-C output current of 2.75 A, the PV short-strings receiving an insolation of 1000, 800, and 600 W/m<sup>2</sup> are operating at a voltage and current (42.80 V, 7.21 A), (43.79 V, 5.74 A), and (44.09 V, 4.32 A), respectively. The corresponding operating powers of PV short-strings are 308.59, 251.41, and 190.51 W, respectively. The duty ratios of S-I-Cs integrated to above-referred PV short-strings at their operating powers are 0.62, 0.51, and 0.35, respectively.

The S-I-Cs integrated to PV short-strings which are receiving an insolation of 400 and 300 W/m<sup>2</sup>, generate the power of 3.44 and  $-1.88$  W, respectively. The corresponding operating voltage and current are (1.1 V, 3.13 A (nearest to short-circuit current)) and [ $-0.8$  V, 2.35 A (short-circuit current)]. Here, it is observed that the operating voltage and current of S-I-Cs are deviated from

Fig. 8. Results for series configuration of S-I-Cs under various partial shading patterns. (a) PV voltages. (b) PV currents. (c) PV powers. (d) Duty ratios. (e) Output powers.

MPP due to cross-coupling effects, but to equal the output current ( $I_L$ ) to 2.75 A of series configuration of S-I-Cs, the internal body diode of the MOSFET switch starts conducting and supports the flow of 0.4 A current. (i.e.,  $2.75 - 2.35$  A). Due to the conduction of internal body diode of MOSFET switch, the switching

Fig. 9. Representation of current paths for the series configuration of S-I-Cs. (a) Current path for the noncross-coupled S-I-Cs. (b) Current path for cross-coupled S-I-Cs.

action of cross-coupled S-I-Cs does not happen. Therefore, the duty ratio of cross-coupled S-I-Cs reaches its lower limit. Hence the operating power of series configuration of S-I-Cs is equal to 4146.56 W [i.e.,  $(12 \times 308.59 W) + (1 \times 251.41 W) + (1 \times 190.51 W) + (1 \times 3.44 W) + (1 \times -1.88 W)$ ] and produces the output power of 4072.92 W. The power loss of the S-I-Cs is equal to 73.64 W. The current path (green colour lines) for the two unshaded S-I-Cs (noncross-coupled S-I-Cs) is shown in Fig. 9(a). Here, the switching action of two unshaded S-I-Cs is happening at their corresponding operating voltage and current. Fig. 9(b) shows the current path for a single unshaded (noncross-coupled) and shaded (cross-coupled) S-I-Cs. The flow of current through internal body diode (ball blue colour line) of the cross-coupled S-I-C MOSFET switch is equal to  $I_{D,2} = (I_L - I_{sc})$ , where  $I_{sc}$  is the short-circuit current of the cross-coupled S-I-C.

Under long and narrow shading pattern, from  $t = 0.3$  to  $1.5$  s, the output current of series configuration of S-I-Cs is equal to 2.53 A. Therefore, to maintain each S-I-C output current to 2.53 A, the operating powers of S-I-Cs receiving an insolation of 1000, 800, and 600 W/m<sup>2</sup> are similar to under uneven column and diagonal shading patterns. The corresponding operating voltage and current are also the same, but the corresponding duty ratios of S-I-Cs are equal to 0.64, 0.56, and 0.41, respectively. Here also, the S-I-Cs receiving an insolation of 400 and

300 W/m<sup>2</sup> are cross-coupled and generate the power of 3.70 W and  $-1.88$  W, at an operating voltage and current (1.18 V, 3.13 A) and ( $-0.8$  V, 2.35 A), respectively. In this shading pattern, the current through the internal body diode of MOSFET switch ( $I_{D,2}$ ) is equal 0.18 A (i.e., 2.53 – 2.35 A). Due to cross-coupling effects, the operating power of this configuration is equal to 3356.20 W [i.e.,  $(8 \times 308.59 W) + (2 \times 251.41 W) + (2 \times 190.51 W) + (2 \times 3.70 W) + (2 \times -1.88 W)$ ] and produces the output power of 3290.46 W. Here, the power loss of S-I-Cs is equal to 65.74 W.

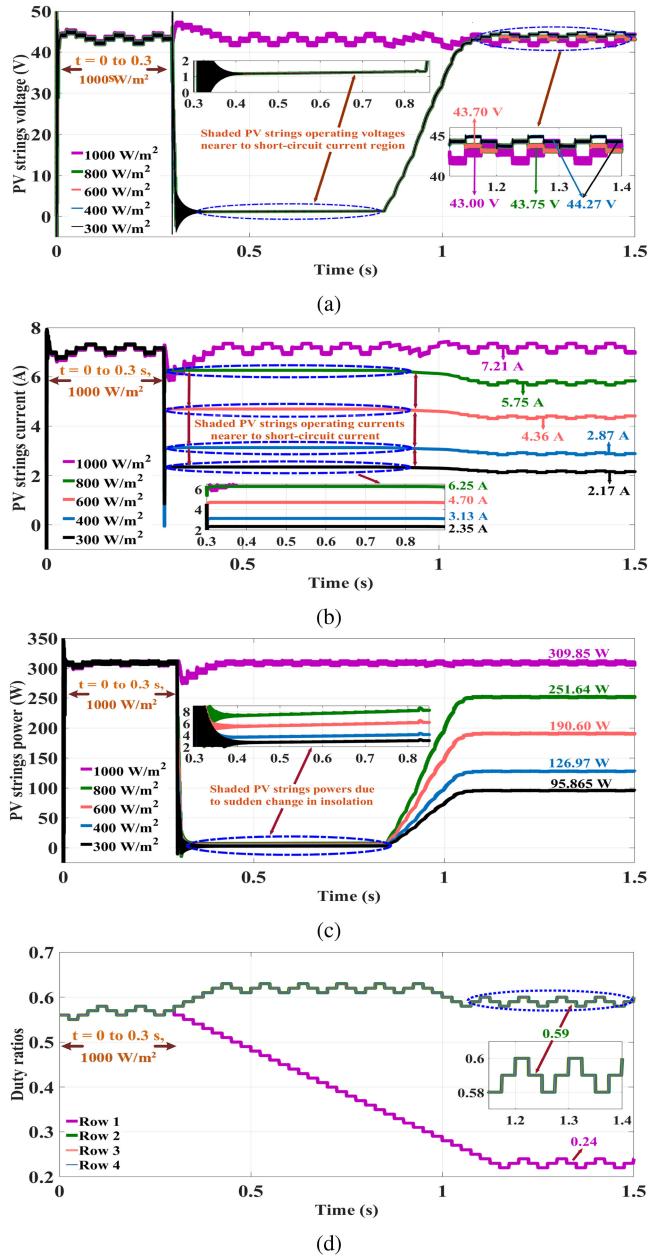

### C. T-C-T Configuration of S-I-Cs

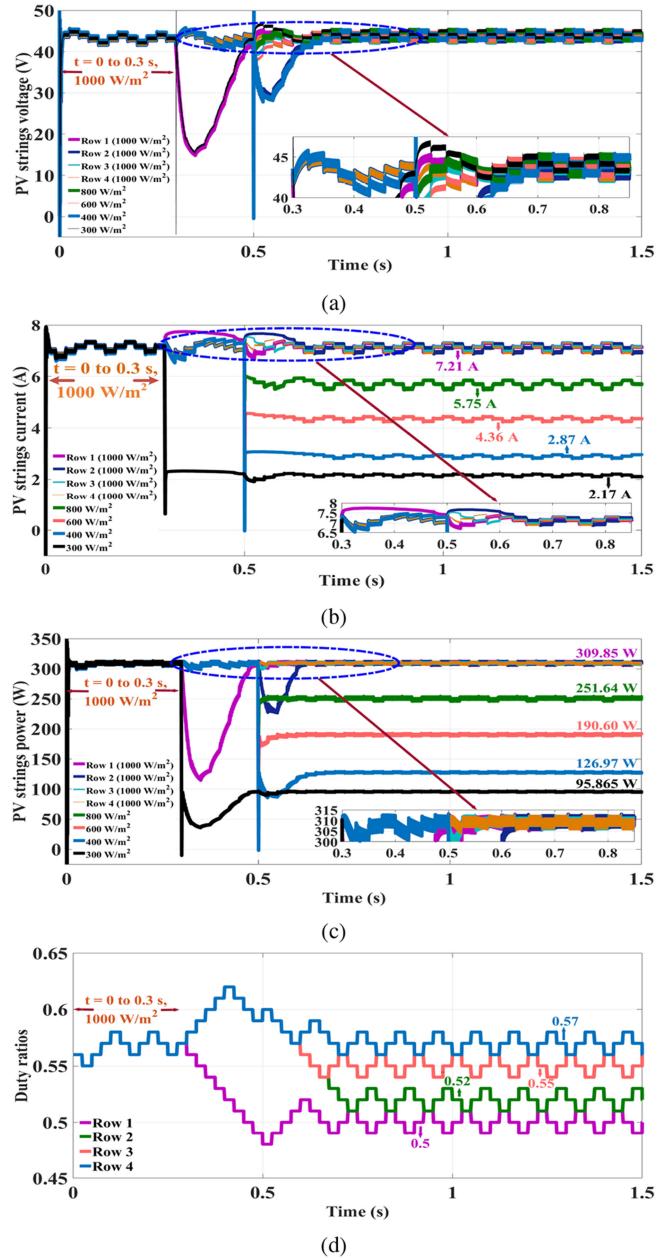

Under uneven row shading pattern, from  $t = 0.3$  to  $1.5$  s, the S-I-Cs receiving an insolation of 1000, 800, 600, 400, and 300 W/m<sup>2</sup> are operating at a voltage and current (43 V, 7.20 A), (43.75 V, 5.75 A), (43.70 V, 4.36 A), (44.27 V, 2.87 A), and (44.27 V, 2.17 A), respectively, and are shown in Fig. 10(a) and (b). The corresponding operating powers of S-I-Cs 309.85, 251.64, 190.60, 126.97, and 95.865 W, respectively, and are shown in Fig. 10(c). At this condition, the T-C-T configuration of S-I-Cs generate the power of 4383.28 W ( $= (12 \times 309.85 W) + (1 \times 251.64 W) + (1 \times 190.60 W) + (1 \times 126.97 W) + (1 \times 95.865 W)$ ). The corresponding steady-state duty ratios of S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are equal to 0.24, 0.59, 0.59, and 0.59, respectively, and are shown in Fig. 10(d). Therefore, according to (9) and (11), the S-I-Cs output voltage and current in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  is determined as  $V_{R_1} = 57.57$  V,  $V_{R_2} = V_{R_3} = V_{R_4} = 104.88$  V and  $I_{R_1} = I_{R_2} = I_{R_3} = I_{R_4} = 11.60$  A. The T-C-T configuration of S-I-Cs output voltage ( $V_L$ ) and current ( $I_L$ ) according to the (8) and (10) are determined as 372.21 V (i.e.,  $V_{R_1} + V_{R_2} + V_{R_3} + V_{R_4}$ ) and 11.60 A. From (7), the output power ( $P_L$ ) of this configuration is determined as 4318 W, and the power loss is determined as 65.28 W.

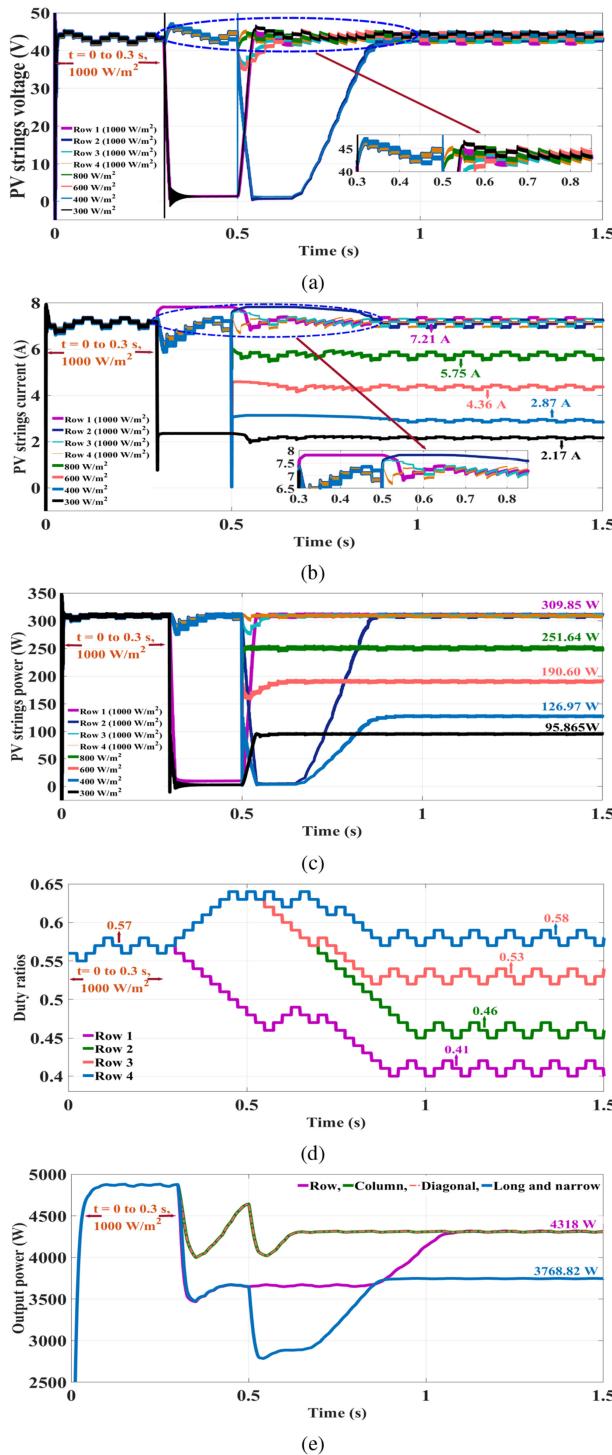

Under uneven column and diagonal shading pattern, from  $t = 0.3$  to  $1.5$  s, the PV short-strings in rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  receiving an insolation of 1000 W/m<sup>2</sup> generate the power of 309.85 W, but the operating voltage and current are different. The operating voltage and current of PV short-strings in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are (42.97 V, 7.21 A), (43.15 V, 7.18 A), (43.51 V, 7.12 A), and (43.27 V, 7.16 A), respectively. The operating voltages, currents and powers of PV short-strings receiving insolation of 800, 600, 400, and 300 W/m<sup>2</sup> are same as under uneven row shading pattern. Therefore, the operating power of the T-C-T configuration is also the same as under the uneven row shading pattern. The operating voltages, currents, and powers of PV short-strings under the uneven column and diagonal shading patterns are shown in Fig. 11(a)–(c), respectively. The corresponding steady-state duty ratios of the S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are equal to 0.5, 0.52, 0.55, and 0.57, respectively, and are shown in Fig. 11(d). The S-I-Cs output voltage in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  is determined as  $V_{R_1} = 85.94$  V,  $V_{R_2} = 89.89$  V,  $V_{R_3} = 96.28$  V, and  $V_{R_4} = 100.62$  V. Therefore, T-C-T configuration of S-I-Cs output voltage ( $V_L$ ) and current ( $I_L$ ) is determined as 372.60 V and

Fig. 10. Results for the T-C-T configuration of S-I-Cs under uneven row shading pattern. (a) PV strings voltage. (b) PV strings current. (c) PV strings power. (d) Duty ratios.

11.59 A. The T-C-T configuration of S-I-Cs under uneven column and diagonal shading patterns produces the output power, and power loss as same as that of under uneven row shading pattern.

Under long and narrow shading pattern, from  $t = 0.3$  to  $1.5$  s, the operating voltages, currents, and powers of all PV short-strings in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are same as under uneven column and diagonal shading patterns, and are shown in Fig. 12(a)–(c), respectively. Therefore, the operating power of the T-C-T configuration of S-I-Cs is equal to  $3808.95 \text{ W}$  ( $= (8 \times 309.85 \text{ W}) + (2 \times 251.64 \text{ W}) + (2 \times$

Fig. 11. Results for T-C-T configuration of S-I-Cs under uneven column and diagonal shading pattern. (a) PV strings voltage. (b) PV strings current. (c) PV strings power. (d) Duty ratios.

$190.60 \text{ W}) + (2 \times 126.97 \text{ W}) + (2 \times 95.865 \text{ W})$ ). The corresponding steady-state duty ratios of S-I-Cs in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are equal to 0.41, 0.46, 0.52, and 0.58 V, respectively, and are shown in Fig. 12(d). The S-I-Cs output voltage in the rows  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  is determined as  $V_{R_1} = 72.83 \text{ V}$ ,  $V_{R_2} = 79.90 \text{ V}$ ,  $V_{R_3} = 92.57 \text{ V}$ , and  $V_{R_4} = 103.02 \text{ V}$ . Therefore, the output voltage and current of T-C-T configuration of S-I-Cs is determined as  $348.32 \text{ V}$  and  $10.82 \text{ A}$ , respectively. The T-C-T configuration of S-I-Cs produces the output power of  $3768.82 \text{ W}$  and the power loss of S-I-Cs is equal to  $40.13 \text{ W}$ . The output power of T-C-T configuration of S-I-Cs under considered shading patterns are shown in Fig. 12(e).

Fig. 12. Results for T-C-T configuration of S-I-Cs under long & narrow pattern. (a) PV strings voltage. (b) PV strings current. (c) PV strings power. (d) Duty ratios. (e) Output powers.

The output powers of considered PV system architectures under various partial shading patterns are given in Table II. From these results, it can be inferred that under PSCs, the proposed T-C-T configuration of S-I-Cs is more efficient compared to PV central inverter architecture and series configuration of S-I-Cs.

TABLE II

COMPARISON OF THE PV SYSTEM ARCHITECTURES OUTPUT POWER (IN KW)

UNDER VARIOUS SHADING PATTERNS

| Shading patterns | PV central inverter | Series configuration | Proposed T-C-T configuration |

|------------------|---------------------|----------------------|------------------------------|

| Uneven row       | 3673.49             | 4072.92              | 4318                         |

| Uneven column    | 4252.68             | 4072.92              | 4318                         |

| Diagonal         | 4252.68             | 4072.92              | 4318                         |

| Long and narrow  | 2768.72             | 3356.20              | 3768.82                      |

## V. CONCLUSION

This paper focuses on various PV system architectures used for the building integrated PV systems. First, it illustrates the PV short-string characteristics, design of S-I-C, and the implementation of P&O MPPT controller. To overcome the drawbacks of PV central inverter and conventional M-I-C configuration, this paper proposes the T-C-T configuration for S-I-Cs to extract the maximum power. The P&O MPPT controller is used to track the maximum power. Because of the parallel connections between the S-I-Cs in a row, the T-C-T configuration of S-I-Cs mitigates the cross-coupling effects. The performance of the proposed T-C-T configuration of S-I-Cs has been compared with the above-reported PV system architectures by considering the variations in output power. The advantages of the proposed configuration are: improved energy harvest, improved system efficiency, plug- and play-operation, and enhanced flexibility. For implementing the proposed PV system configuration, the cost of components is five times less over the M-I-C configurations.

## REFERENCES

- [1] B. I. Rani, G. S. Ilango, and C. Nagamani, "Enhanced power generation from PV array under partial shading conditions by shade dispersion using Su Do Ku configuration," *IEEE Trans. Sustain. Energy*, vol. 4, no. 3, pp. 594–601, Jul. 2013.

- [2] J. M. Carrasco *et al.*, "Power-electronic systems for the grid integration of renewable energy sources: A survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, Jun. 2006.

- [3] J. D. Bastidas-Rodriguez, E. Franco, G. Petrone, C. A. Ramos-Paja, and G. Spagnuolo, "Maximum power point tracking architectures for photovoltaic systems in mismatching conditions: A review," *IET Power Electron.*, vol. 7, no. 6, pp. 1396–1413, Jan. 2014.

- [4] Y.-C. Kuo, T.-J. Liang, and J.-F. Chen, "Novel maximum-power-pointtracking controller for photovoltaic energy conversion system," *IEEE Trans. Ind. Electron.*, vol. 48, no. 3, pp. 594–601, Jun. 2001.

- [5] C. Lin, A. Amirahmadi, Q. Zhang, N. Kutkut, and I. Batarseh, "Design and implementation of three-phase two-stage grid-connected module integrated converter," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 3881–3892, Aug. 2014.

- [6] S. R. Pendem and S. Mikkili, "Modelling and performance assessment of PV array topologies under partial shading conditions to mitigate the mismatching power losses," *Solar Energy*, vol. 160, pp. 303–321, Jan. 2018.

- [7] A. S. Yadav, R. K. Pachauri, Y. K. Chauhan, S. Choudhury, and A. R. Singh, "Performance enhancement of partially shaded PV array using novel shade dispersion effect on magic-square puzzle configuration," *Solar Energy*, vol. 144, pp. 780–797, Feb. 2017.

- [8] B. Subudhi and R. Pradhan, "A comparative study on maximum power point tracking techniques for photovoltaic power systems," *IEEE Trans. Sustain. Energy*, vol. 4, no. 1, pp. 89–98, Jan. 2013.

- [9] C. Manickam, G. P. Raman, G. R. Raman, G. Saravana Ilango, and C. Nagamani, "Fireworks enriched P&O algorithm for GMPPT and detection of partial shading in PV systems," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4432–4443, Jun. 2017.

- [10] J. Prasanth Ram and N. Rajasekar, "A novel flower pollination based global maximum power point method for solar maximum power point tracking," *IEEE Trans. Power Electron.*, vol. 32, no. 11, pp. 8486–8499, Nov. 2017.

- [11] E. Romero-Cadaval, G. Spagnuolo, L. G. Franquelo, C.-A. Ramos-Paja, T. Suntio, and W.-M. Xiao, "Grid-connected photovoltaic generation plants: Components and operation," *IEEE Ind. Electron. Mag.*, vol. 7, no. 3, pp. 6–20, Sep. 2013.

- [12] Q. Zhao and F. C. Lee, "High-efficiency, high step-up dc-dc converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 65–73, Jan. 2003.

- [13] A. Ajami, H. Ardi, and A. Farakhor, "A novel high step-up dc/dc converter based on integrating coupled inductor and switched-capacitor techniques for renewable energy applications," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4255–4263, Aug. 2015.

- [14] S. Kouro, J. I. Leon, D. Vinnikov, and L. G. Franquelo, "Grid-connected photovoltaic systems: An overview of recent research and emerging PV converter technology," *IEEE Ind. Electron. Mag.*, vol. 9, no. 1, pp. 47–61, Mar. 2015.

- [15] V. Lal and S. Singh, "Control and performance analysis of a single-stage utility-scale grid-connected PV system," *IEEE Syst. J.*, vol. 11, no. 3, pp. 1601–1611, Sep. 2017.

- [16] E. Roman, R. Alonso, P. Ibanez, S. Elorduizapatarietxe, and D. Goitia, "Intelligent PV module for grid-connected PV systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1066–1073, Jun. 2006.

- [17] B. Liu, S. Duan, and T. Cai, "Photovoltaic dc-building-module-based BIPV system-concept and design considerations," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1418–1429, May 2011.

- [18] H. Patel and V. Agarwal, "MATLAB-based modeling to study the effects of partial shading on PV array characteristics," *IEEE Trans. Energy Convers.*, vol. 23, no. 1, pp. 302–310, Mar. 2008.

- [19] E. Diaz-Dorado, A. Suarez-Garcia, C. Carrillo, and J. Cidras, "Influence of the shadows in photovoltaic systems with different configurations of bypass diodes," in *Proc. Int. Symp. Power Electron. Elect. Drives Autom. Motion*, Pisa, Italy, Jun. 2010, pp. 134–139.

- [20] H. Patel and V. Agarwal, "Maximum power point tracking scheme for PV systems operating under partially shaded conditions," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1689–1698, Apr. 2008.

- [21] D. Shmilovitz and Y. Levron, "Distributed maximum power point tracking in photovoltaic systems, emerging architectures, and control methods," *Automatika*, vol. 53, no. 2, pp. 142–155, Jun. 2012.

- [22] J. Huusari and T. Suntio, "Distributed-MPP tracking: Cross-coupling effects in series and parallel connected dc/dc converters," in *Proc. 27th Eur. Photovolt. Solar Energy Conf. Exhib.*, Frankfurt, Germany, Sep. 2012, pp. 3103–3109.

- [23] J. Huusari and T. Suntio, "Interfacing constraints of distributed maximum power point tracking converters in photovoltaic applications," in *Proc. 15th IEEE Int. Conf. Power Electron. Motion Control Conf.*, Novi Sad, Serbia, Sep. 2012, pp. 1–7.

- [24] J. Huusari and T. Suntio, "Origin of cross-coupling effects in distributed dc-dc converters in photovoltaic applications," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4625–4635, Oct. 2013.

- [25] M. Kasper, D. Bortis, and J. W. Kolar, "Classification and comparative evaluation of PV panel-integrated dc-dc converter concepts," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2511–2526, May 2014.

- [26] N. Priyadarshi, S. Padmanaban, P. K. Maroti, and A. Sharma, "An extensive practical investigation of FPSO-based MPPT for grid integrated PV System under variable operating conditions with anti-islanding protection," *IEEE Syst. J.*, vol. 13, no. 2, pp. 1861–1871, Jun. 2019.

- [27] W. Xiao, N. Ozog, and W. G. Dunford, "Topology study of photovoltaic interface for maximum power point tracking," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1696–1704, Jun. 2007.

- [28] K. Muralidhar and S. Samanta, "Modified perturb and observe MPPT algorithm for drift avoidance in photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 62, no. 9, pp. 5549–5559, Sep. 2015.

- [29] N. Rakesh and T. V. MadhavaRam, "Performance enhancement of partially shaded solar PV array using novel shade dispersion technique," *Frontiers Energy*, vol. 10, no. 2, pp. 227–239, Oct. 2015.

**Suneel Raju Pendem** (S'19) was born in Chilakaluripet, India, in 1988. He received the B.Tech. degree in electrical and electronics engineering from RVR & JC College of Engineering, Guntur, India, in 2009 and the M.Tech. degree in electrical engineering from the National Institute of Technology Rourkela, Rourkela, India, in 2012. He is currently working toward the Ph.D. degree in electrical and electronics engineering at the National Institute of Technology Goa, Ponda, India.

His research interests include dc-dc converters, applications of renewable energy sources, and soft computing techniques.

**Suresh Mikkili** (M'16) was born in Bapatla, India, in 1985. He received the B.Tech. degree in electrical and electronics engineering (EEE) from Sasi Institute of Technology & Engineering, Tadepalligudem (S.I.T.E, T.P.), India, in 2006. He received the M.Tech. and Ph.D. degrees in electrical engineering from the National Institute of Technology Rourkela, Rourkela, India, in 2008 and 2013, respectively.

He is currently working as an Assistant Professor with the Department of EEE, National Institute of Technology Goa (NIT Goa), Ponda, India. He had been the Head of the EEE Department, NIT Goa from June 2014 to November 2015. Since September 2015, he has been the Dean, Student Welfare with NIT Goa. He has authored a book entitled, *Power Quality Issues: Current Harmonics*, (CRC Press, Taylor & Francis Group, August 2015). He has reported results of his research (50+ articles) in reputed international journals and conferences. His research interests include power quality improvement issues, active filters, power electronics applications to power systems, applications of soft computing techniques, and renewable energy sources.

**Praveen Kumar Bonthagora** (S'19) was born in Bapatla, India, in 1991. He received the B.Tech. degree in electrical and electronics engineering from Bapatla Engineering College, Guntur, India, in 2012 and the M.Tech. degree in electrical and electronics engineering from the Annamacharya Institute of Technology and Sciences, Hyderabad, India, in 2015. He is currently working toward the Ph.D. degree in electrical and electronics engineering at the National Institute of Technology Goa, Ponda, India.

His research interests include multilevel inverters, soft computing techniques, and applications of renewable energy sources.