# Fault-tolerant multi-level inverter topologies for open-end winding induction motor drive

Narender Reddy Kedika  | Srinivasan Pradabane

Department of Electrical Engineering,

National Institute of Technology

Warangal, Warangal, India

## Correspondence

Srinivasan Pradabane, Department of

Electrical Engineering, National Institute

of Technology Warangal, Warangal, India.

Email: spradabane@nitw.ac.in

## Summary

This paper presents two nine-level inverter topologies for open-end winding induction motor drive with fault-tolerance for all possible switch faults. The proposed topologies are designed with three voltage-source inverters each with eight switches, an isolated DC source and a capacitor. The number of components and the scheme of connection employed for phase windings in both the topologies are identical. The voltage across the capacitors is controlled using the phase currents and hence does not require any additional pre-charging circuit. The direction of phase currents flowing through the capacitors determines their charging and discharging states. Hence the proposed topologies are categorized as flying-capacitor leg based topology (FCLBT) and switched-capacitor based topology (SCBT) considering the technique employed for generating intermittent voltages. Although these topologies require three sources, the output voltage peak across each phase winding would be twice the source voltage, hence lower rating renewable energy sources can be employed as input sources. Conventional level-shifted carrier sinusoidal pulse width modulation technique (SPWM) is employed for generating switching pulses. The proposed topologies employ reduced number of devices compared to existing similar nine-level topologies and also exhibit fault-tolerance for switch faults. The post-fault operation of the proposed topologies does not require any additional hardware but necessitates the modifications of switching pulses. Simulations are performed in the MATLAB/Simulink environment and results are presented. A prototype is constructed to validate the performance of the proposed topologies and experimental results are presented.

## KEY WORDS

fault tolerant, flying-capacitor, multi-level inverter, open-end winding, pulse width modulation

**List of Symbols and Abbreviations:** ACHB, Asymmetrical CHB; CHB, Cascaded H-bridge; DSP, Digital signal processors; DSP/ACE, Digital signal processing and control engineering; FCLBT, Flying-Capacitor leg based topology; FC, Flying-Capacitor; FFT, Fast Fourier Transform; IM, Induction motor; NPC, Neutral point clamped; OEWIM, Open-end winding induction motor; OC, Open-circuit;  $I_p$ , Maximum value of load phase current; Ma, Modulation Index; MLI, Multilevel inverter; MSL, Modified switching logic; Q, Charge; T, Time-period; THD, Total harmonic distortion; SC, Short-circuit; SCBT, Switched-Capacitor based topology; SPWM, sinusoidal pulse width modulation technique; VSI, voltage-source inverter; V/F, Volts per Hertz; VB, Blocking Voltage; Z, Load Impedance;  $\delta T$ , Inverter switching time period;  $\delta V$ , Maximum permissible voltage ripple.

## 1 | INTRODUCTION

In recent days, multi-level voltage-source inverters (VSIs) have been receiving greater acceptance from the industry in the range of medium- and high-power induction motor (IM) drive applications. Owing to the certain advantages of multi-level inverters (MLIs) such as operation with higher DC-link voltages using lower rating semiconductor switching devices and producing output voltage with superior harmonic profile mark their importance in industrial applications.<sup>1,2</sup> Conventional topologies such as (a) neutral point clamped (NPC) inverter, (b) flying-capacitor (FC) inverter and (c) cascaded H-bridge (CHB) inverter belong to early era of MLIs and are employed in applications with lower levels of output voltage. These topologies have their own advantages and disadvantages based on their control and operation. NPC and FC topologies will have capacitor voltage balancing issues and require complex control techniques when designed for higher levels in the output. CHB topology can be designed for any level of output voltage but requires increased number of isolated sources. Although these topologies can be configured for the increased number of levels in the output, the power and control circuit complexity increases as the number of switching devices required are high. Hence this provides the scope of research for developing MLI topologies with reduced complexity in power and control circuits. A comprehensive MLI topology combining NPC and FC inverter topologies is presented,<sup>3</sup> in which the self-balancing of the capacitor voltages is achieved without complex algorithms but this topology requires additional capacitors and several active switches to produce the multi-level output voltage. A modified topology designed for a single-phase system employing CHB with single DC source and an FC is proposed.<sup>4</sup> This topology can deliver multi-level output voltage but the floating-capacitor voltage gets unbalanced with change in modulation range and requires a complex control scheme. Recent years have witnessed vast research in areas of MLI topologies and many of such topologies that are present in the literature are the blend of conventional topologies.<sup>5-7</sup> Several topologies were proposed to satisfy the desires of the industry such as reduced device count and fault-tolerance.<sup>8-13</sup>

Certain MLI topologies are designed based on the application, such as the topologies for open-end winding induction motor (OEWIM) drive. The three-phase stator winding terminals of IM are brought out and are fed from both ends to achieve multi-level output voltage across the phase windings.<sup>14</sup> Several effective and efficient modulation techniques were proposed for three-level and four-level operation of the dual inverter fed OEWIM drive configuration.<sup>15-17</sup> Apart from dual inverter configuration with conventional two-level inverters, several topologies were proposed for OEWIM drive with increased number of levels in the output voltage. MLI topologies employing conventional three-phase VSIs and FC connected H-bridges are proposed to generate nine- and seven-level output voltage. These topologies employ an increased number of components, complex modulation technique and deliver a peak output voltage equal to the magnitude of a single source voltage.<sup>18,19</sup> A modular fault-tolerant seven-level inverter topology configured with conventional two-level and NPC inverters for OEWIM drive is also proposed. This topology exhibits better fault-tolerance with reduced modulation range during switch faults but employs a large number of components and complex control scheme.<sup>20</sup> A 17-level inverter topology with low-switch count for OEWIM drive is presented. This topology employs DC sources of unequal magnitude and a complex modulation scheme for operation.<sup>21</sup> A nine-level inverter topology for OEWIM drive is proposed with minimum component count and employs a simple control scheme. This topology provides fault tolerance to switch faults but cannot produce average sinusoidal output voltage in post-fault operation.<sup>22</sup>

MLIs with a high number of levels in the output voltage are desired in drive applications as the increase in the number of levels decreases harmonic distortions and hinders the need for expensive and bulky filters. However, the increase in the levels of the output voltage is obtained at a cost of an increased number of components, hence the industry is reluctant for a higher number of levels as it makes the system bulky, less reliable and complex. Therefore, there is a necessity to attain an increased number of levels in the inverter output voltage without an enormous rise in the number of components, and reliability of the system is also important. The power circuit complexity can be reduced with lower switching devices and hence control complexity can be reduced proportionally. As the component count of MLIs increases, the reliability of the system decreases. Failure of any one switch may lead to a complete shutdown of the system. Thus, fault tolerant reduced device topologies find importance in the MLI family.<sup>23,24</sup> A fault-tolerant MLI topology with reduced switching devices for OEWIMs that can be controlled by conventional sinusoidal pulse width modulation (SPWM) techniques is also presented.<sup>25</sup>

Hence, this paper presents two nine-level inverter topologies for OEWIM drive with fault-tolerance capability to switch fault conditions. The proposed topologies are designed with a minimum number of switching devices. The two nine-level inverter topologies proposed are envisioned for an IM with open-end stator winding construction. In these topologies, the six terminals of the three-phase windings of the IM are fed from three three-phase VSIs along with the FCs. The modulation techniques employed can effectively charge and discharge the capacitors to realize middle voltage

levels throughout its modulation range. The proposed topologies employ a reduced number of switches and lower voltage rating isolated DC sources than conventional topologies.

The content of this paper is organised as follows: the working principle of the proposed topologies is detailed in Section 2, modulation scheme employed is presented in Section 3; comparative analysis and determination of capacitance value are presented in Sections 4 and 5, respectively. Operation of the proposed topologies during normal condition, with switch faults and with fault-tolerant strategy along with simulation results, is illustrated in Section 6. Experimental results and conclusions are presented in Sections 7 and 8 respectively.

## 2 | DESCRIPTION OF PROPOSED TOPOLOGIES

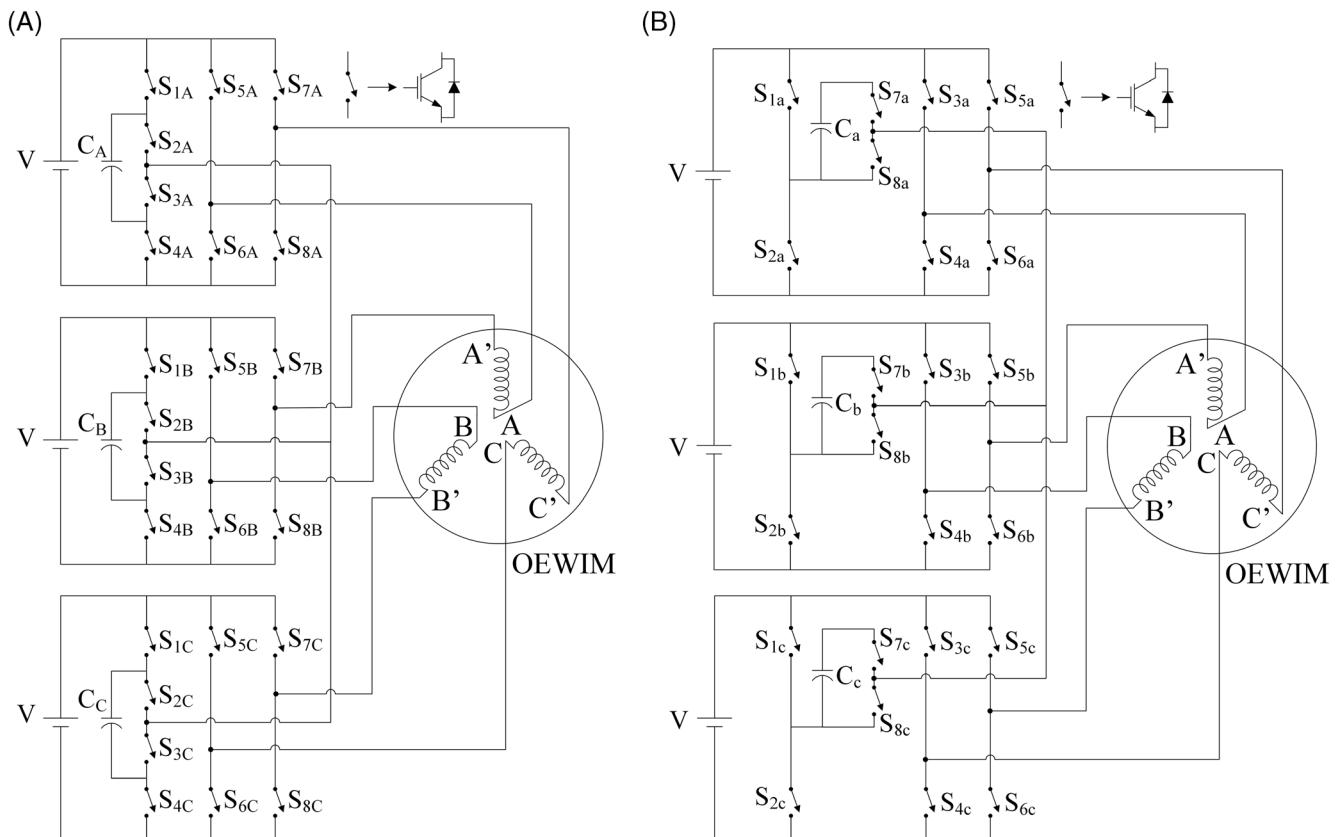

The proposed topologies are designed to feed an OEWIM with lower-rated voltage sources. These inverters are configured to feed the three-phase IM stator windings from both the ends to yield nine-level voltage across each phase winding. This configuration produces increased voltage levels with reduced devices and the output voltage peak will be twice the magnitude of input source voltage. This allows us to employ lower-voltage renewable energy sources as input elements. The scheme of connection employed exhibits inherent fault tolerance for switch faults as well. The scheme of connection employed for the proposed topologies is illustrated in Figure 1.

Figure 1A presents an FC-leg based topology (FCLBT) and Figure 1B presents a switched-capacitor based topology (SCBT). The FCLBT is designed with three inverters, in which each inverter consists of an FC leg and a conventional H-bridge and are connected across an isolated DC source. SCBT is designed with three three-phase inverters and each of these inverters are fed from an isolated DC source and also are provided with a capacitor with two series-connected switches across it. In the proposed topologies, switches  $S_{1A}$  through  $S_{8A}$  constitute inverter-A. Similarly, switches  $S_{1B}$  through  $S_{8B}$  constitute inverter-B and switches  $S_{1C}$  through  $S_{8C}$  constitute inverter-C.

In FCLBT, the circuit configuration for inverter-A is done in the following manner: the series connection of switches  $S_{1A}$ ,  $S_{2A}$ ,  $S_{3A}$  and  $S_{4A}$  constitute a leg of the inverter and a capacitor is connected across the switches  $S_{2A}$  and

**FIGURE 1** Proposed topologies: A, flying-capacitor leg based topology (FCLBT); B, switched-capacitor based topology (SCBT)

| Voltage level | Inverter-A      |                 |                 | Inverter-B      |                 |                 | Capacitor state             |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------|

|               | S <sub>1A</sub> | S <sub>2A</sub> | S <sub>5A</sub> | S <sub>1B</sub> | S <sub>2B</sub> | S <sub>7B</sub> |                             |

| 2 V           | 0               | 0               | 1               | 1               | 1               | 0               | No change                   |

| 3 V/2         | 0               | 0               | 1               | 1               | 0               | 0               | C <sub>B</sub> -charging    |

|               | 0               | 1               | 1               | 1               | 1               | 0               | C <sub>A</sub> -charging    |

| V             | 0               | 0               | 1               | 0/1             | 0/1             | 0/1             | No change                   |

|               | 0/1             | 0/1             | 0/1             | 1               | 1               | 0               |                             |

| V/2           | 0               | 0               | 1               | 1               | 0               | 1               | C <sub>B</sub> -charging    |

|               | 0               | 1               | 0               | 1               | 1               | 0               | C <sub>A</sub> -charging    |

| 0             | 1               | 1               | 1               | 0/1             | 0/1             | 0/1             | No change                   |

|               | 0               | 0               | 0               | 1/0             | 1/0             | 1/0             |                             |

| -V/2          | 0               | 1               | 0               | 0/1             | 0/1             | 0/1             | C <sub>A</sub> -discharging |

|               | 0/1             | 0/1             | 0/1             | 1               | 0               | 1               | C <sub>B</sub> -discharging |

| -V            | 1               | 1               | 0               | 0/1             | 0/1             | 0/1             | No change                   |

|               | 0/1             | 0/1             | 0/1             | 0               | 0               | 1               |                             |

| -3 V/2        | 1               | 1               | 0               | 1               | 0               | 1               | C <sub>B</sub> -discharging |

|               | 0               | 1               | 0               | 0               | 0               | 1               | C <sub>A</sub> -discharging |

| -2 V          | 1               | 1               | 0               | 0               | 0               | 1               | No change                   |

**TABLE 1** Possible switching states to generate different voltage levels for FCLBT.

S<sub>3A</sub>. The mid-point of switches S<sub>2A</sub> and S<sub>3A</sub> is taken as output terminal-1 of inverter-A. Similarly, the mid-point of switches S<sub>5A</sub> and S<sub>6A</sub> is considered as output terminal-2 and mid-point of switches S<sub>7A</sub> and S<sub>8A</sub> is considered as output terminal-3. In SCBT, the switches S<sub>1a</sub> and S<sub>2a</sub> constitute a leg of the inverter and to the point between these two switches the negative terminal of the capacitor is connected. The switches S<sub>7a</sub> and S<sub>8a</sub> constitute a leg and are connected across the capacitor. The mid-point of switches S<sub>7a</sub> and S<sub>8a</sub> is taken as output terminal-1 of inverter-a. Similarly, the mid-point of switches S<sub>3a</sub> and S<sub>4a</sub> is considered as output terminal-2 and mid-point of switches S<sub>5a</sub> and S<sub>6a</sub> is considered as output terminal-3. Hence, in both the proposed topologies, each inverter has three output terminals and output terminal-1 of all the three inverters is shorted to form a neutral connection. The phase-A winding of OEWIM is connected between output terminal-2 of inverter-a and output terminal-3 of the inverter-b. Similarly, the phase-B and phase-C windings are connected in the same configuration. The scheme of connection and the components required for both the topologies are the same.

The proposed topologies are proficient of generating output voltage across any phase winding with nine levels, namely  $\pm 2$  V,  $\pm 3$  V/2,  $\pm V$ ,  $\pm V/2$ , 0. The possible switching states to generate nine-level output voltage across the terminals of phase winding A-A' of OEWIM are presented in Table 1 for FCLBT and in Table 2 for SCBT. However, the reduction in the number of switching devices has a divergent influence on the number of overall redundant switching states as evident from Tables 1 and 2. However, an observation of switching tables depicts the information that the charging and discharging times of FC in both the proposed topologies are equivalent over one complete cycle of output voltage.

Considering the output voltage and also current have half-wave symmetry, the average current (Average[i<sub>c</sub>]) that flow through the capacitor during output voltage levels  $\pm 3$  V/2 and  $\pm V/2$  with the load impedance of Z can be given as follows:

$$\text{Average}[i_c^+]_{V_2} = \frac{V - v_c}{Z}; \quad (1)$$

$$\text{Average}[i_c^-]_{3V_2} = \frac{V + v_c}{Z}; \quad (2)$$

$$\text{Average}[i_c^+]_{3V_2} = \frac{2V - v_c}{Z}; \quad (3)$$

**TABLE 2** Possible switching states to generate different voltage levels for SCBT

| Voltage level | Inverter-a      |                 |                 | Inverter-b      |                 |                 | Capacitor state             |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------|

|               | S <sub>1a</sub> | S <sub>3a</sub> | S <sub>7a</sub> | S <sub>1b</sub> | S <sub>5b</sub> | S <sub>7b</sub> |                             |

| 2 V           | 0               | 1               | 0               | 1               | 0               | 0               | No change                   |

| 3 V/2         | 0               | 1               | 1               | 1               | 0               | 0               | C <sub>a</sub> -charging    |

|               | 0               | 1               | 0               | 0               | 0               | 1               | C <sub>b</sub> -discharging |

| V             | 0               | 1               | 0               | 0/1             | 0/1             | 0               | No change                   |

|               | 0/1             | 0/1             | 0               | 1               | 0               | 0               |                             |

| V/2           | 0               | 1               | 1               | 1               | 1               | 0               | C <sub>a</sub> -charging    |

|               | 0               | 0               | 0               | 0               | 0               | 1               | C <sub>b</sub> -discharging |

| 0             | 0               | 0               | 0               | 0/1             | 0/1             | 0               | No change                   |

|               | 1               | 1               | 0               | 0/1             | 0/1             | 0               |                             |

| -V/2          | 0               | 1               | 1               | 0               | 0               | 1               | C <sub>a</sub> -discharging |

|               | 0               | 0               | 1               | 0               | 0               | 0               | C <sub>b</sub> -charging    |

| -V            | 1               | 0               | 0               | 1/0             | 1/0             | 0               | No change                   |

|               | 0/1             | 0/1             | 0               | 0               | 1               | 0               |                             |

| -3 V/2        | 0               | 0               | 1               | 0               | 1               | 0               | C <sub>a</sub> -discharging |

|               | 1               | 0               | 0               | 0               | 1               | 1               | C <sub>b</sub> -charging    |

| -2 V          | 1               | 0               | 0               | 0               | 1               | 0               | No change                   |

$$\text{Average}[i_c^-]_{V_2} = \frac{v_c}{Z}. \quad (4)$$

Therefore, the net charge (Q) absorbed/supplied for a time period (T) can be expressed as follows:

$$Q = \left\{ \text{Average}[i_c^+]_{V_2} + \text{Average}[i_c^+]_{3V_2} - \text{Average}[i_c^-]_{V_2} - \text{Average}[i_c^-]_{3V_2} \right\} * T = \left\{ \frac{2V - 4v_c}{Z} \right\}. \quad (5)$$

Owing to the symmetric property of the output current in steady-state, the average charge Q over a complete cycle is zero, substituting charge (Q) as zero in Equation (5) will result in a relation of  $v_c = 0.5$  V. The voltage across the FC is maintained as 0.5 V where V is the voltage rating of each source in the proposed topologies. This self-balancing property of maintaining voltage 0.5 V across the FC is achieved without any additional circuitry or closed-loop control that expedites lowered overall inverter design cost.

The voltage at the output terminals is reliant on the switching states of the power switches. Considering the switches as ideal, let the binary variables 0 and 1 represent their blocking and conduction states, respectively. In other words,

that is, if  $S_{vu} = 0$  then  $S_{wu} = 1$ ; switch  $S_{vu}$  is OFF and switch  $S_{wu}$  is ON

if  $S_{wu} = 0$ , then  $S_{vu} = 1$ ; switch  $S_{wu}$  is OFF and switch  $S_{vu}$  is ON.

- Where  $u \in A, B, C$  and  $v \in 1, 2, 5, 7$  and  $w \in 4, 3, 6, 8$  for FCLBT.

- Where  $u \in a, b, c$  and  $v \in 1, 3, 5, 7$  and  $w \in 2, 4, 6, 8$  for SCBT.

With this depiction and considering  $\hat{S}_{1A} = S_{4A}$ ,  $\hat{S}_{2A} = S_{3A}$ ,  $\hat{S}_{5A} = S_{6A}$ ,  $S_{5A} = S_{7A}$  and  $\hat{S}_{7A} = S_{8A}$ , for FCLBT and similarly  $\hat{S}_{1a} = S_{a2}$ ,  $\hat{S}_{3a} = S_{4a}$ ,  $\hat{S}_{5a} = S_{6a}$ ,  $S_{3a} = S_{5a}$ ,  $S_{4a} = S_{6a}$  and  $\hat{S}_{7a} = S_{8a}$  for SCBT, the output voltage across the terminals of OEWIM for the proposed topologies can be written as follows:

For FCLBT

$$V_{AA'} = V \left[ \begin{array}{l} S_{5A}(\hat{S}_{1A}\hat{S}_{2A} + 0.5\hat{S}_{1A}S_{2A}) + \hat{S}_{7B}(S_{1B}S_{2B} + 0.5\hat{S}_{1B}S_{2B}) \\ - \hat{S}_{5A}(S_{1A}S_{2A} + 0.5\hat{S}_{1A}S_{2A}) - S_{7B}(\hat{S}_{1B}\hat{S}_{2B} + 0.5\hat{S}_{1B}S_{2B}) \end{array} \right]. \quad (6)$$

For SCBT

$$V_{AA'} = V \left[ \begin{array}{l} S_{3a}(\hat{S}_{1a}\hat{S}_{7a} + 0.5\hat{S}_{1a}S_{7a}) + \hat{S}_{5b}(S_{1b}\hat{S}_{7b} + 0.5\hat{S}_{1b}S_{7b}) \\ - \hat{S}_{3a}(S_{1a}\hat{S}_{7a} + 0.5\hat{S}_{1a}S_{7a}) - S_{5b}(\hat{S}_{1b}\hat{S}_{7b} + 0.5\hat{S}_{1b}S_{7b}) \end{array} \right]. \quad (7)$$

The proposed topologies are capable of providing balanced three-phase output voltage even under switch fault conditions. This makes the proposed topologies reliable when used for low-voltage medium-power applications such as feeding motors in an electrical vehicle. For operation of the proposed topologies during switch fault conditions does not require any additional hardware, but requires modification of switching pulses. To obtain balanced output voltage across all the phases, the switching of the inverters should also be identical. Hence when switch fault occurs in any of the switches, some of the healthy switches are also turned-off in post-fault operation to ensure symmetrical switching of the inverters. Under normal operation of the proposed topologies, nine-level voltage is fed to the windings of the OEWIM drive, whereas with switch fault, the levels in the output voltage reduce to five and the power delivered will also be reduced to half for most of the switch faults. The output power supplied might be reduced during switch fault conditions but it ensures continuity in operation of the OEWIM drive.

### 3 | MODULATION SCHEME

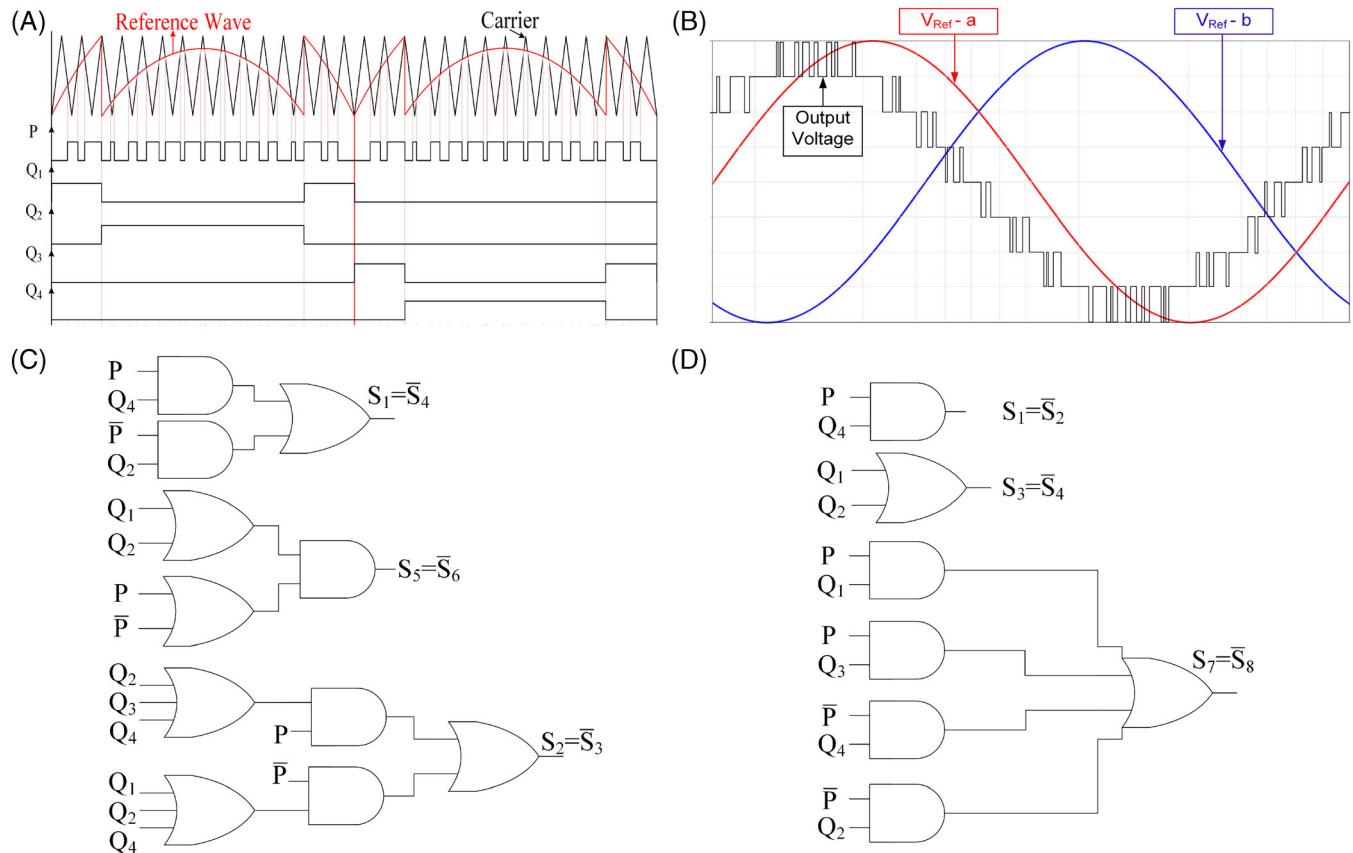

The gate pulses for the switches in the proposed topologies are produced by the conventional SPWM technique. A fundamental frequency sinusoidal reference signal,  $V_{\text{Ref}}$  is compared with the high-frequency level shifted triangular carrier signals to generate the gate pulses. In general, the magnitude of the sinusoidal reference signal is taken as unity that represents the modulation index,  $Ma = 1$ , where the magnitude of the level-shifted carriers is half the reference

**FIGURE 2** Modulation scheme employed to generate gate pulses for the proposed topologies: A, modified reference wave with a single carrier wave to generate gate pulses; B, representation of nine-level generation with two reference signals,  $V_{\text{Ref-a}}$  and  $V_{\text{Ref-b}}$ ; C, switching logics for switches in FCLBT; D, switching logics for switches in SCBT

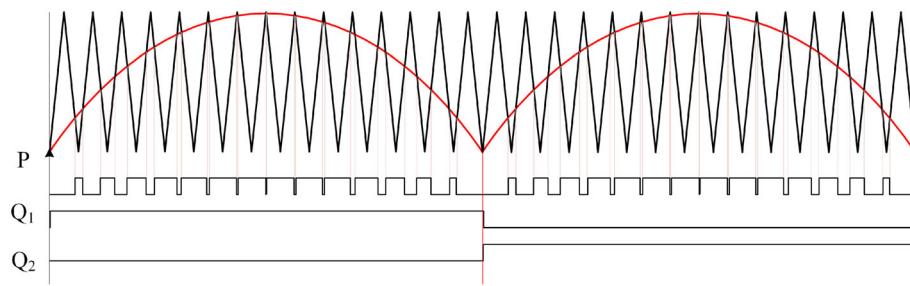

voltage magnitude. For such a modulation scheme, the number of level-shifted carriers required for an  $N$ -level inverter will be  $(N - 1)$ . To reduce the number of carrier signals required, the reference wave can be modified in such a way that the negative cycle is flipped as positive cycle, which reduces the number of carrier waves required.<sup>26</sup> The reference wave can be further modified as shown in Figure 2A, in such a way that the number of carriers required is only one.<sup>27</sup> This reduces the computational burden on the controllers while implementing on digital platforms like dSPACE and digital signal processors (DSP). The gate pulses for the proposed topologies are generated using dSPACE 1104.

The connection of phase windings is done such that two ends of each winding are fed from two different inverters. For example, considering SCBT, the phase winding terminal-A is connected to inverter-a and winding terminal-A' is connected to inverter-b. Similarly, phase winding terminals B-B' are also connected between two different inverters. Three inverters are operated by gate pulses generated by SPWM technique. The reference waves used for three inverters are displaced by  $120^\circ$ . Therefore, each terminal of every phase winding is operating with a phase difference of  $120^\circ$  with respect to its other terminal. This scheme of connection permits the phase winding to experience the output voltage with nine levels with maximum output voltage as twice the source voltage. The modified reference PWM used to produce gate pulses for the proposed topologies is illustrated in Figure 2A. Figure 2B illustrates the logic of generating nine levels in the output voltage with two reference waveforms displaced by  $120^\circ$ . The switching logics employed for FCLBT and SCBT are presented in Figure 2C,D, respectively.

**TABLE 3** Comparison of proposed topologies with other similar topologies feeding OEWIM drives

| Type of inverter        | Active switches |                                                                                                                                       | DC capacitors |                                                                                                                           | Clamping diodes |                                                                                                                                                                                                                                                                                                       | Sources |                             |

|-------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|

|                         | $N$             | $V_B$                                                                                                                                 | $N$           | $V_B$                                                                                                                     | $N$             | $V_B$                                                                                                                                                                                                                                                                                                 | $N$     | Rating                      |

| NPC                     | 48              | $0.25 \text{ V}_{\text{DC}}$                                                                                                          | 8             | $0.125 \text{ V}_{\text{DC}}$                                                                                             | 42              | 6 diodes— $0.125 \text{ V}_{\text{DC}}$<br>6 diodes— $0.25 \text{ V}_{\text{DC}}$<br>6 diodes— $0.375 \text{ V}_{\text{DC}}$<br>6 diodes— $0.5 \text{ V}_{\text{DC}}$<br>6 diodes— $0.625 \text{ V}_{\text{DC}}$<br>6 diodes— $0.75 \text{ V}_{\text{DC}}$<br>6 diodes— $0.875 \text{ V}_{\text{DC}}$ | 1       | $\text{V}_{\text{DC}}$      |

| FC                      | 48              | $0.25 \text{ V}_{\text{DC}}$                                                                                                          | 108           | $0.125 \text{ V}_{\text{DC}}$                                                                                             | 0               | —                                                                                                                                                                                                                                                                                                     | 1       | $\text{V}_{\text{DC}}$      |

| Conventional CHB (CCHB) | 48              | $\text{V}_{\text{DC}}$                                                                                                                | 0             | —                                                                                                                         | 0               | —                                                                                                                                                                                                                                                                                                     | 12      | $\text{V}_{\text{DC}}/8$    |

| Asymmetrical CHB (ACHB) | 24              | 12 switches— $0.75 \text{ V}_{\text{DC}}$<br>12 switches— $0.25 \text{ V}_{\text{DC}}$                                                | 0             | —                                                                                                                         | 0               | —                                                                                                                                                                                                                                                                                                     | 3       | $3 \text{ V}_{\text{DC}}/8$ |

| [18]                    | 36              | 12 switches— $\text{V}_{\text{DC}}$<br>12 switches— $0.5 \text{ V}_{\text{DC}}$<br>12 switches— $0.25 \text{ V}_{\text{DC}}$          | 6             | —                                                                                                                         | 0               | —                                                                                                                                                                                                                                                                                                     | 2       | $\text{V}_{\text{DC}}$      |

| [19]                    | 36              | 12 switches— $\text{V}_{\text{DC}}$<br>24 switches— $0.33 \text{ V}_{\text{DC}}$                                                      | 6             | $0.33 \text{ V}_{\text{DC}}$                                                                                              | 0               | —                                                                                                                                                                                                                                                                                                     | 2       | $\text{V}_{\text{DC}}$      |

| [20]                    | 48              | $0.166 \text{ V}_{\text{DC}}$                                                                                                         | 6             | $0.0833 \text{ V}_{\text{DC}}$                                                                                            | 12              | $0.083 \text{ V}_{\text{DC}}$                                                                                                                                                                                                                                                                         | 6       | $\text{V}_{\text{DC}}/12$   |

| [21]                    | 36              | 12 switches— $0.125 \text{ V}_{\text{DC}}$<br>12 switches— $0.375 \text{ V}_{\text{DC}}$<br>12 switches— $0.75 \text{ V}_{\text{DC}}$ | 9             | 3 Cap's— $0.125 \text{ V}_{\text{DC}}$<br>3 Cap's— $0.375 \text{ V}_{\text{DC}}$<br>3 Cap's— $0.75 \text{ V}_{\text{DC}}$ | 0               | —                                                                                                                                                                                                                                                                                                     | 3       | $3 \text{ V}_{\text{DC}}/4$ |

| [22]                    | 24              | 18 switches— $\text{V}_{\text{DC}}$<br>6 switches— $0.5 \text{ V}_{\text{DC}}$                                                        | 6             | $0.5 \text{ V}_{\text{DC}}$                                                                                               | 0               | —                                                                                                                                                                                                                                                                                                     | 3       | $\text{V}_{\text{DC}}/2$    |

| FCLBT                   | 24              | 12 switches— $\text{V}_{\text{DC}}$<br>12 switches— $0.5 \text{ V}_{\text{DC}}$                                                       | 3             | $0.5 \text{ V}_{\text{DC}}$                                                                                               | 0               | —                                                                                                                                                                                                                                                                                                     | 3       | $\text{V}_{\text{DC}}/2$    |

| SCBT                    | 24              | 18 switches— $\text{V}_{\text{DC}}$<br>6 switches— $0.5 \text{ V}_{\text{DC}}$                                                        | 3             | $0.5 \text{ V}_{\text{DC}}$                                                                                               | 0               | —                                                                                                                                                                                                                                                                                                     | 3       | $\text{V}_{\text{DC}}/2$    |

Abbreviations: Cap's, capacitors;  $N$ , number;  $V_B$ , blocking voltage.

## 4 | COMPARISON OF THE PROPOSED TOPOLOGIES

The proposed topologies are compared with other similar topologies in terms of blocking voltage capability ( $V_B$ ) of switches, DC capacitors, clamping diodes and number of sources required along with their rating, and are presented in Table 3. The comparison is done based on the assumption that the voltage blocking capability of the components is calculated when all these topologies are excited with a source voltage of  $V_{DC}$  and the actual source voltages required with their rating are mentioned under the sources column. From Table 3, it is evident that the proposed topologies employ least number of switches as that used in ACHB and topology in Reference 22, out of the total switches used in FCLBT half of the switches have a blocking voltage equal to 0.5  $V_{DC}$  and the other half have a blocking voltage of 0.25  $V_{DC}$ . Whereas in SCBT three-fourth of the switches have a blocking voltage equal to 0.5  $V_{DC}$  and rest have a blocking voltage of 0.25  $V_{DC}$  (since the source voltage used for the proposed topologies is only 0.5  $V_{DC}$ ). It implies that the total switch count is low and that the rating required is also low for the proposed topologies.

## 5 | DETERMINATION OF CAPACITANCE

The proposed topologies are designed based on FC. So, it is important to determine the value of capacitance of such a capacitor that depends upon the peak value of load current, ripple voltage and discharging period. Capacitors designed for lower ripple will yield lower power loss and work with higher efficiency.

The value of capacitance of the FC can be determined as<sup>28</sup>

$$I_p = C \frac{dv}{dt} = C \frac{\Delta V}{\Delta T},$$

$$C = I_p \frac{\Delta T}{\Delta V} = \frac{I_p}{\Delta V * f_{sw}}, \quad (8)$$

where  $C$  is the minimum capacitance of FC required,  $I_p$  is the maximum value of load phase current,  $\Delta T$  is the inverter switching time period ( $T_s$ ) and  $\Delta V$  is the maximum permissible peak-to-peak voltage ripple in the FC. For a switching frequency of 1.5 kHz, if the capacitor peak-to-peak ripple voltage has to be limited to 4 V, capacitance required is 666  $\mu$ F. To be on the safe side, the capacitance for the experimental prototype is taken as 1000  $\mu$ F.

## 6 | OPERATION OF THE PROPOSED TOPOLOGIES

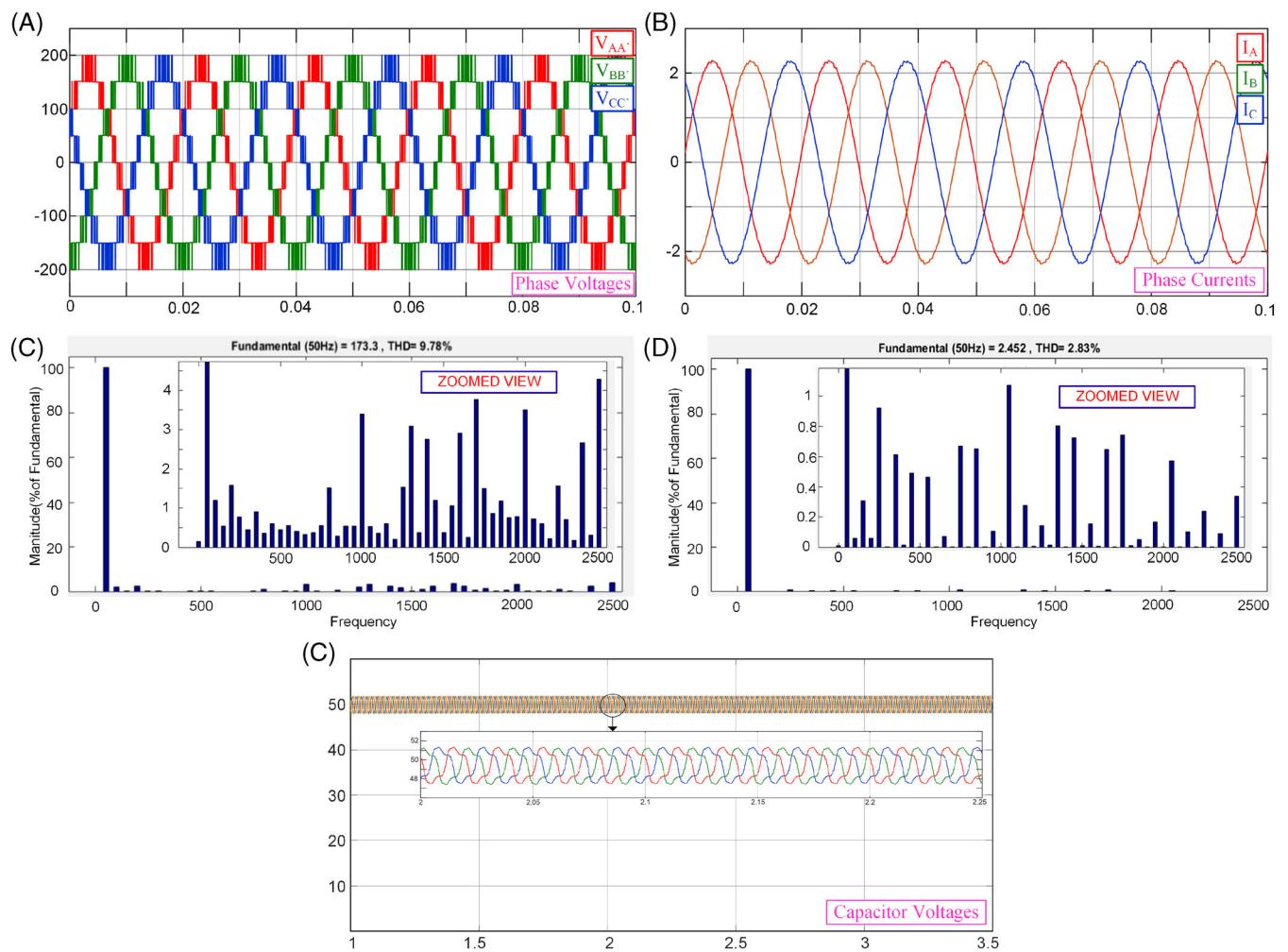

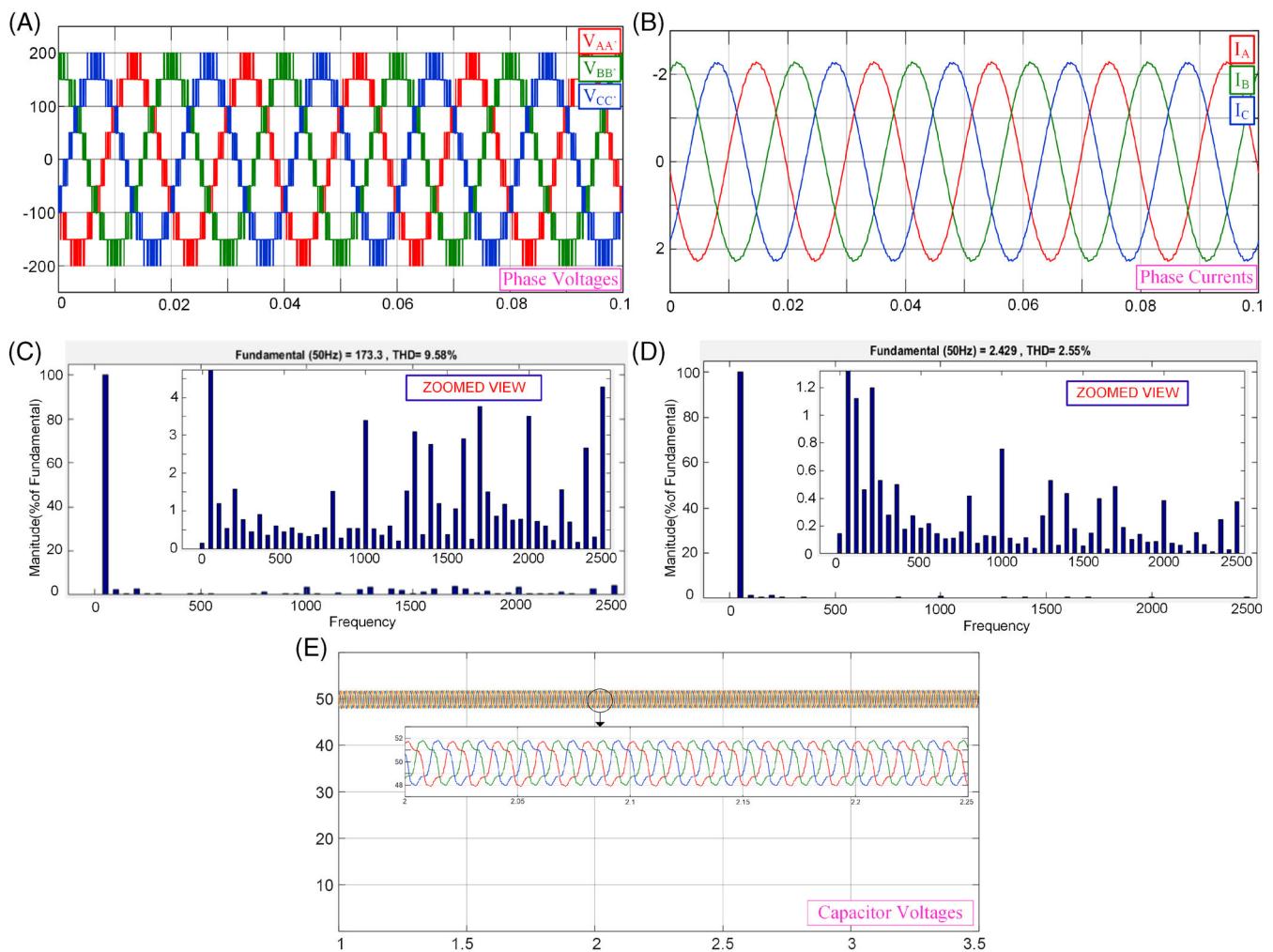

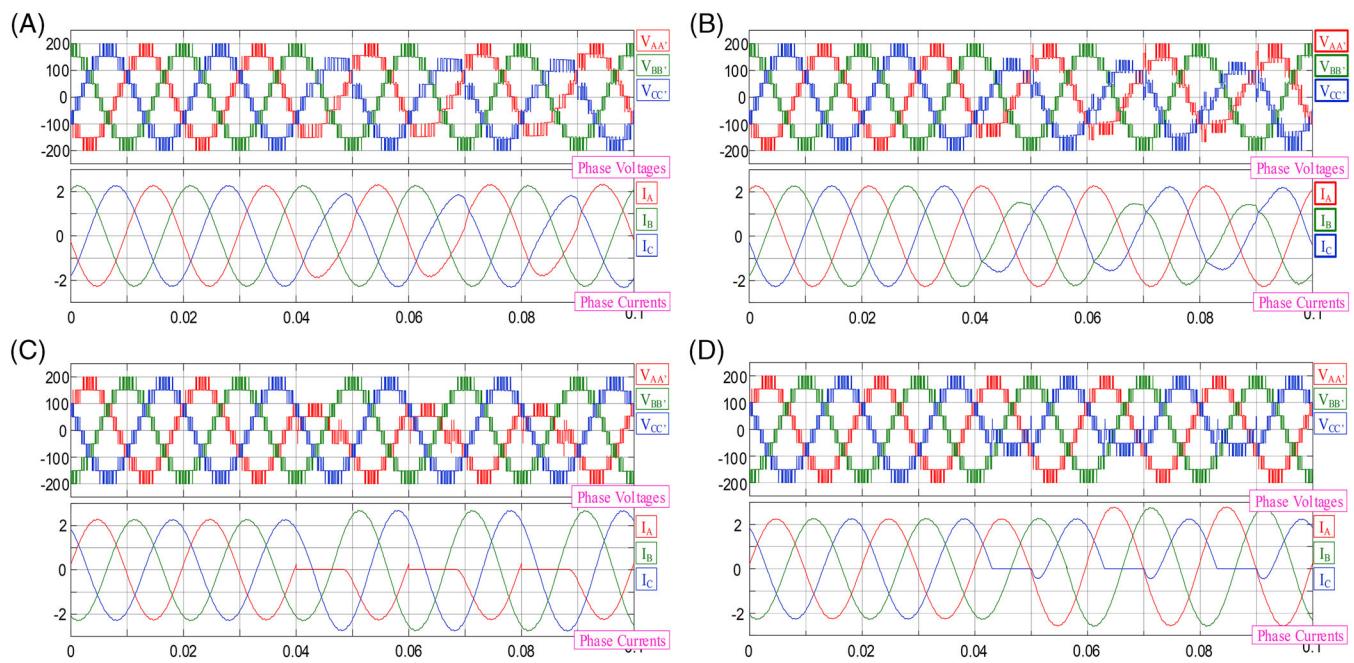

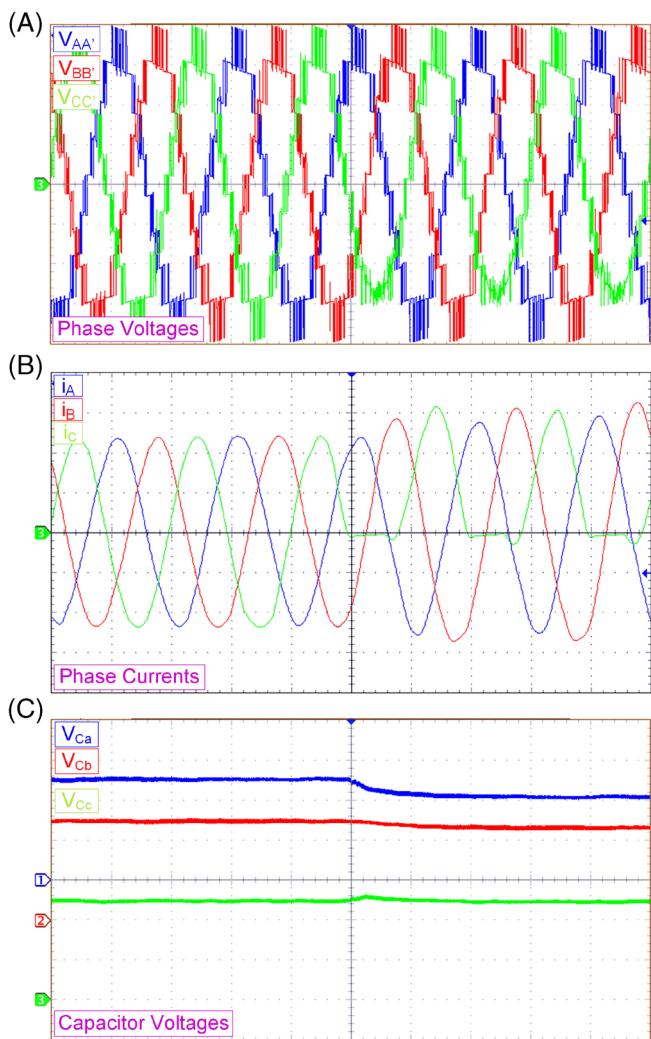

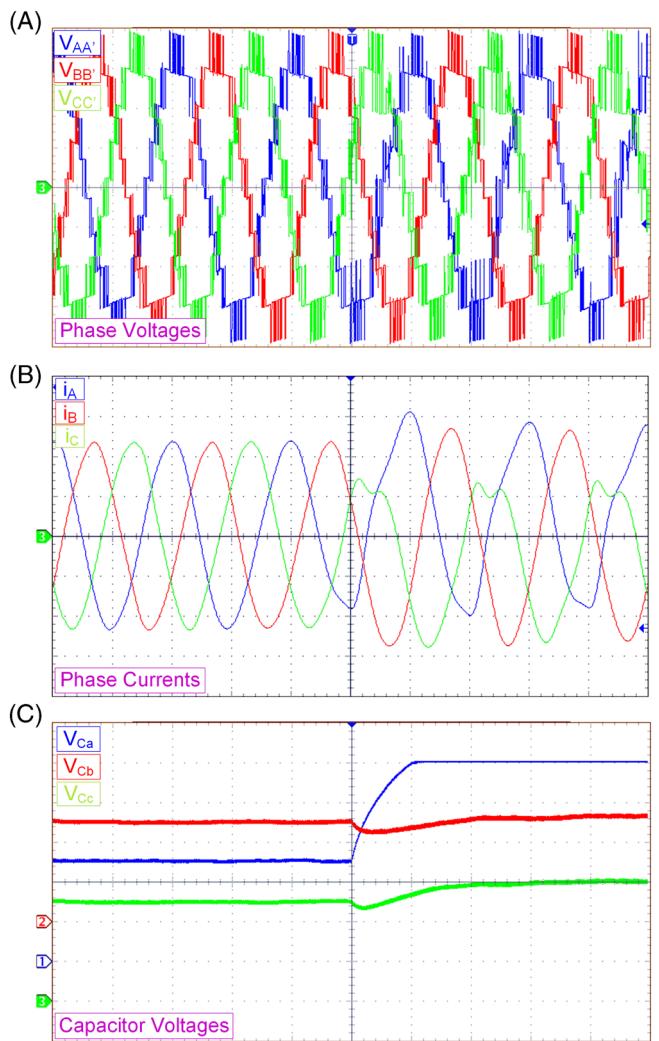

To demonstrate the viability of the proposed topologies and the control scheme, the models are developed and simulated in the MATLAB/Simulink environment. The simulation results of three-phase output voltage and currents, total harmonic distortion (THD) of the phase voltage and current, FC voltages during normal operating conditions of FCLBT and SCBT are presented in Figures 3 and 4, respectively. The parameters considered for the simulation and experimentation are presented in Table 4.

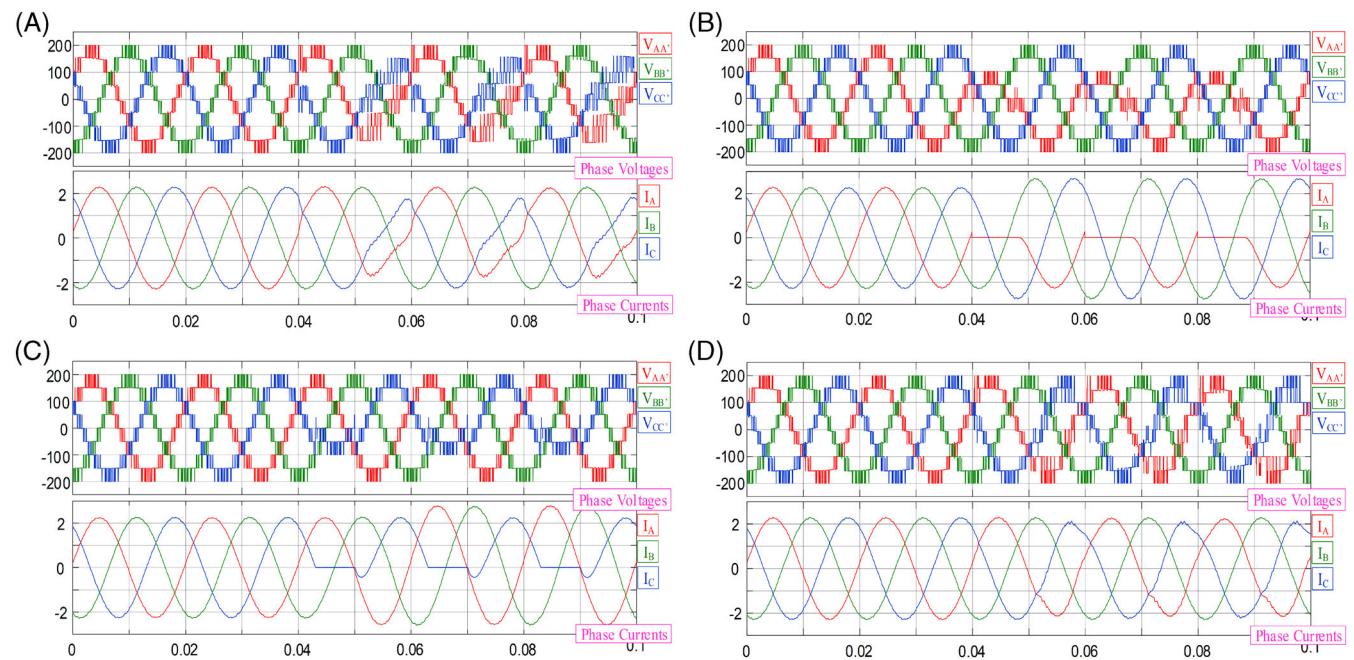

### 6.1 | Inverter operation during switch faults

The proposed topologies employ three-phase inverters, and the total number of switches employed is 24 for each topology. Each winding is associated with six switches, at least, to deliver the output power. The switches in the inverters can be faulted either with an open-circuit (OC) or with a short circuit (SC). The proposed topologies can still be operated under such switch fault conditions with rated or reduced output power depending upon the switch under fault and the type of fault (SC or OC). Simulation results for various switch OC faults in the proposed topologies are presented in Figures 5 and 6. From the results presented in Figures 5 and 6, it is evident that both the topologies behave identical during switch faults (introduced at time 0.04 seconds) as well depending upon the switch position in their respective topologies. The switches  $S_{2A}$  and  $S_{3A}$  in FCLBT are identical to switches  $S_{7a}$  and  $S_{8a}$  in SCBT and are meant for charging and discharging of the FC. And switches  $S_{1A}$  and  $S_{4A}$  in FCLBT are

**FIGURE 3** Simulation results of FCLBT. A, Three-phase output voltages  $V_{AA'}$ ,  $V_{BB'}$  and  $V_{CC'}$ ; B, three-phase currents  $I_A$ ,  $I_B$  and  $I_C$ ; C, THD for phase voltage; D, THD of phase current; and E, voltages across the capacitor in each inverter

identical to switches  $S_{1a}$  and  $S_{2a}$  in SCBT and are meant for neutral connection. Hence OC fault in such switches will yield similar output voltages and currents and hence experimental validation can be done with any of the topologies.

In FCLBT, switch  $S_{1A}$  operates in complimentary with  $S_{4A}$  and switch  $S_{2A}$  operates in complimentary with  $S_{3A}$ . Hence the results are presented only for  $S_{1A}$  and  $S_{2A}$  OC faults. Similarly, switches  $S_{5A}$  and  $S_{7A}$  operate in complementary with  $S_{6A}$  and  $S_{8A}$ , respectively. Therefore, waveforms of output voltage and current for switches  $S_{5A}$  and  $S_{7A}$  OC fault are presented. The output waveforms for OC faults in switch  $S_{6A}$  (or  $S_{8A}$ ) would be the same as the vertical flip of the results presented for OC fault of switch  $S_{5A}$  (or  $S_{7A}$ ). Similarly, in SCBT, switches  $S_{1a}$ ,  $S_{3a}$ ,  $S_{5a}$  and  $S_{7a}$  are operated in complementary with switches  $S_{2a}$ ,  $S_{4a}$ ,  $S_{6a}$  and  $S_{8a}$ , respectively. Hence waveforms for OC faults in switches  $S_{1a}$ ,  $S_{3a}$ ,  $S_{5a}$  and  $S_{7a}$  are presented in Figure 6.

## 6.2 | Fault-tolerant operation

The proposed topologies are capable of operating even under switch fault conditions. The switching logic has to be modified when a fault occurs in a switch in any of the inverters. If the fault occurred in the switch is an OC fault, then the switching strategy is that the gate pulses of the faulty switch are to be withdrawn and the switching logic has to be designed for the available healthy switches only. For the proposed topologies, out of the 24 switches, if any of the switches is either open-circuited or short-circuited, then the modulation index has to be reduced to half (ie,  $M_a = 0.5$ ) and the

**FIGURE 4** Simulation results of SCBT. A, Three-phase output voltages  $V_{AA'}$ ,  $V_{BB'}$  and  $V_{CC'}$ ; B, Three-phase currents  $I_A$ ,  $I_B$  and  $I_C$ ; C, THD for phase voltage; D, THD of phase current; and E, Voltages across the capacitor in each inverter

**TABLE 4** Circuit parameters used for simulation and experimentation

| Particulars           | Value                               |

|-----------------------|-------------------------------------|

| Source voltage        | 100 V                               |

| Flying capacitors     | 1000 $\mu$ F                        |

| Fundamental frequency | 50 Hz                               |

| Switching frequency   | 1500 Hz                             |

| Load                  | Open-end winding induction motor    |

|                       | Specifications                      |

|                       | Rated torque                        |

|                       | Stator and rotor resistance         |

|                       | Stator and rotor leakage inductance |

|                       | Mutual inductance                   |

|                       | Moment of inertia                   |

inverter continues to operate as five-level inverter with modified switching logic (MSL). For example, if the switches  $S_{xa}$  or  $S_{ya}$  (where  $x \in 2$  or  $3$ ,  $y \in 7$  or  $8$ ), are faulty, still the rated output power can be delivered with five levels in the output

**FIGURE 5** Simulation results of three-phase voltages and currents of FCLBT with open-circuit fault in switch: A,  $S_{1A}$ ; B,  $S_{2A}$ ; C,  $S_{5A}$ ; D,  $S_{7A}$

**FIGURE 6** Simulation results of three-phase voltages and currents of SCBT with open-circuit fault in switch: A,  $S_{1a}$ ; B,  $S_{3a}$ ; C,  $S_{5a}$ ; D,  $S_{7a}$

voltage, and for faults in any other switches than these, the power delivered will decrease. The maximum output voltage ( $V$ ) is restricted to source voltage ( $V$ ) under these conditions. The SPWM with reduced  $M_a$  for MSL is shown in Figure 7.

Whenever an OC fault occurs in any of the switches, instead of complete shutdown of the supply system, the proposed topologies are made to operate with MSL provided in Tables 5 and 6. If the OC fault occurs in switch  $S_{1A}$ , then the switching logic is designed for the healthy switches in the inverter-A and such logic is given in column-I in Table 5 for FCLBT and in Table 6 for SCBT. The switching logic for other switches when switch  $S_{1A}$  is open-circuited in

**FIGURE 7** Modulation scheme with  $Ma = 0.5$  and corresponding gate pulses

**TABLE 5** Modified switching logic for FCLBT during switch OC fault conditions

| Inverter-A            | Open-circuited switch                   |                                         |                                         |                                         |                                         |                                         |

|-----------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| Switch                | I. $S_{1A}$                             | II. $S_{4A}$                            | III. $S_{2A}$                           | IV. $S_{3A}$                            | V. $S_{5A}$ or $S_{7A}$                 | VI. $S_{6A}$ or $S_{8A}$                |

| $S_{1A}$              | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | $P\bar{C}^*(Q_1 + Q_2)$                 |                                         | $P*Q_1$                                 |                                         |

| $S_{2A}$              | $P*(Q_1 + Q_2)$                         |                                         | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | $P*Q_2$                                 |                                         |

| $S_{3A}$              | $P\bar{C}^*(Q_1 + Q_2)$                 |                                         | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       | $P*Q_1 + P\bar{C}^*(Q_1 + Q_2)$         |                                         |

| $S_{4A}$              | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       | $P*(Q_1 + Q_2)$                         |                                         | $P*Q_2 + P\bar{C}^*(Q_1 + Q_2)$         |                                         |

| $S_{5A}$ and $S_{7A}$ | $P*Q_1$                                 |                                         | $P*Q_1 + P*(Q_1 + Q_2)$                 |                                         | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ |

| $S_{6A}$ and $S_{8A}$ | $P*Q_2 + P\bar{C}^*(Q_1 + Q_2)$         |                                         | $P*Q_2$                                 |                                         | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       |

**TABLE 6** Modified switching logic for SCBT during switch OC fault conditions

| Inverter-a            | Open-circuited switch                   |                                         |                                         |                                         |                                         |                                         |

|-----------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| Switch                | I. $S_{1a}$                             | II. $S_{2a}$                            | III. $S_{3a}$ or $S_{5a}$               | IV. $S_{4a}$ or $S_{6a}$                | V. $S_{7a}$                             | VI. $S_{8a}$                            |

| $S_{1a}$              | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | $P*Q_2 + P\bar{C}^*(Q_1 + Q_2)$         |                                         | $P*Q_2$                                 |                                         |

| $S_{2a}$              | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       | $P*Q_1$                                 |                                         | $P*Q_1 + P\bar{C}^*(Q_1 + Q_2)$         |                                         |

| $S_{3a}$ and $S_{5a}$ | $P*Q_1$                                 |                                         | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | $P*Q_1$                                 |                                         |

| $S_{4a}$ and $S_{6a}$ | $P*Q_2 + P\bar{C}^*(Q_1 + Q_2)$         |                                         | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       | $P*Q_2 + P\bar{C}^*(Q_1 + Q_2)$         |                                         |

| $S_{7a}$              | $P*(Q_1 + Q_2)$                         |                                         | $P*(Q_1 + Q_2)$                         |                                         | 0                                       | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ |

| $S_{8a}$              | $P\bar{C}^*(Q_1 + Q_2)$                 |                                         | $P\bar{C}^*(Q_1 + Q_2)$                 |                                         | $P*(Q_1 + Q_2) + P\bar{C}^*(Q_1 + Q_2)$ | 0                                       |

Note:  $P\bar{C}$  is the complementary of gate pulse  $P$ .

inverter-A as presented in column-I in Table 5, the same switching logic has to be applied for all the corresponding switches in the inverter-B and inverter-C, as well to make the switching identical in all the inverters. Identical switching of inverters results in identical output voltages in all the phases.

Similarly, if the SC fault occurs in any switch, the healthy switch in such leg is completely turned-off and the gate pulses for the other switches are dispensed as given in Table 5. For example, if an SC fault occurs in switch  $S_{1A}$  then the switching logic provided in column-II for switch  $S_{4A}$  open-circuit condition is employed. This clearly shows that the switching logic for SC fault in any switch is the switching logic of the OC fault condition of its complementary switch in

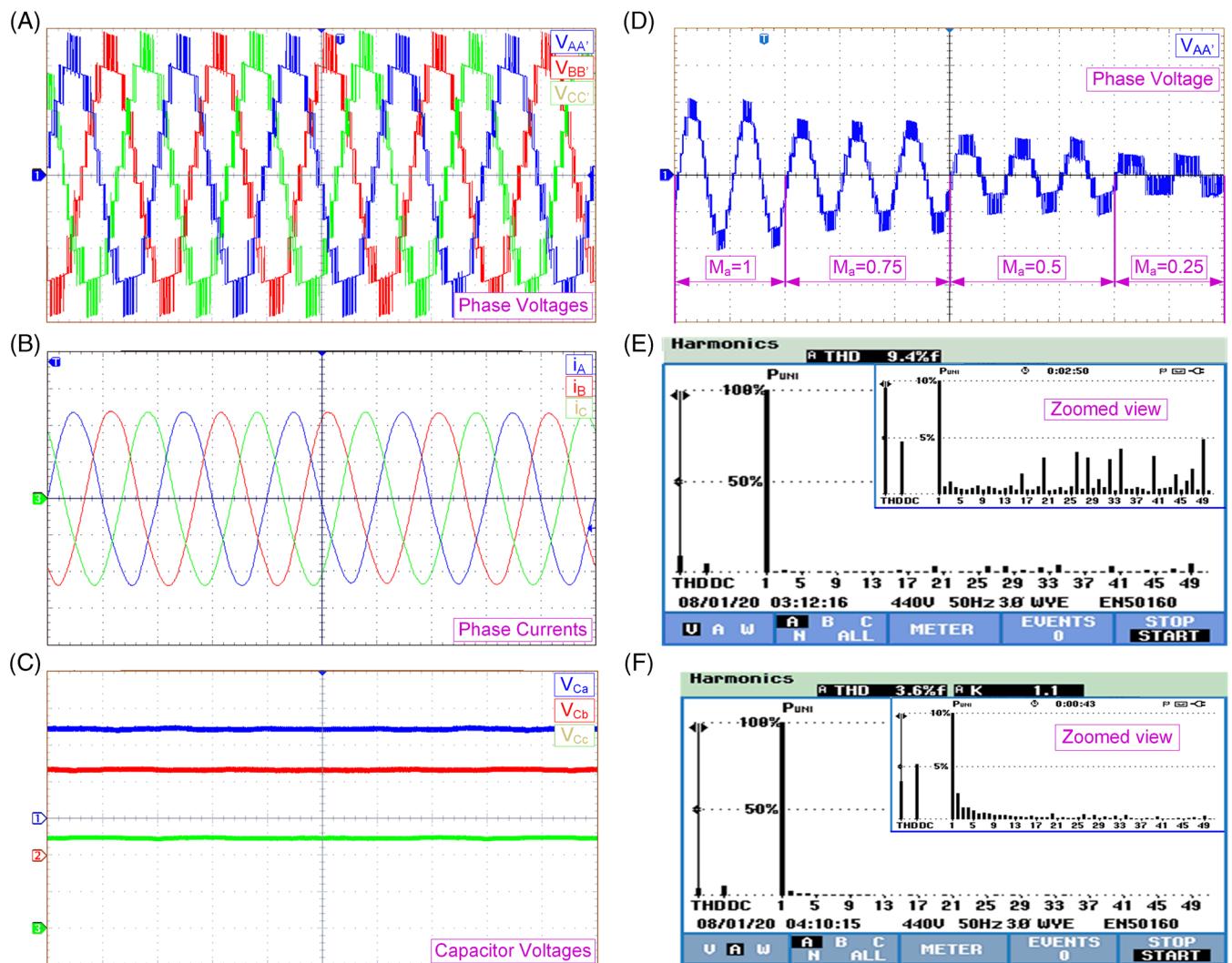

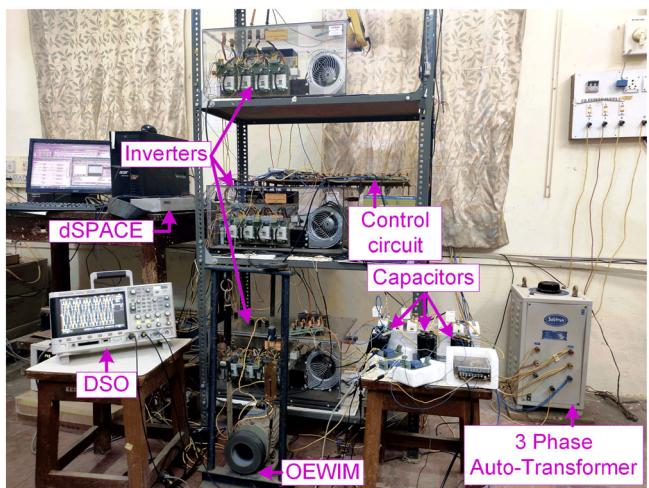

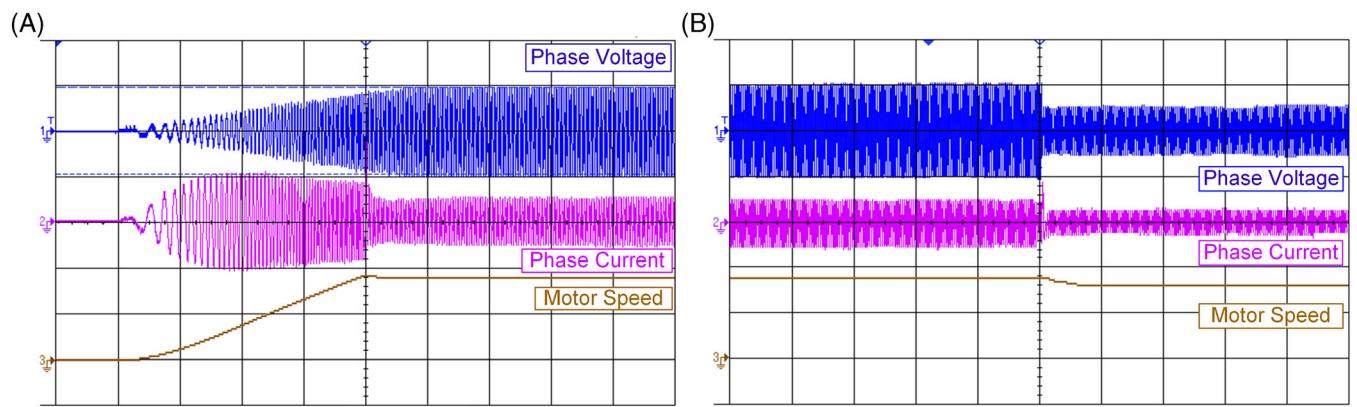

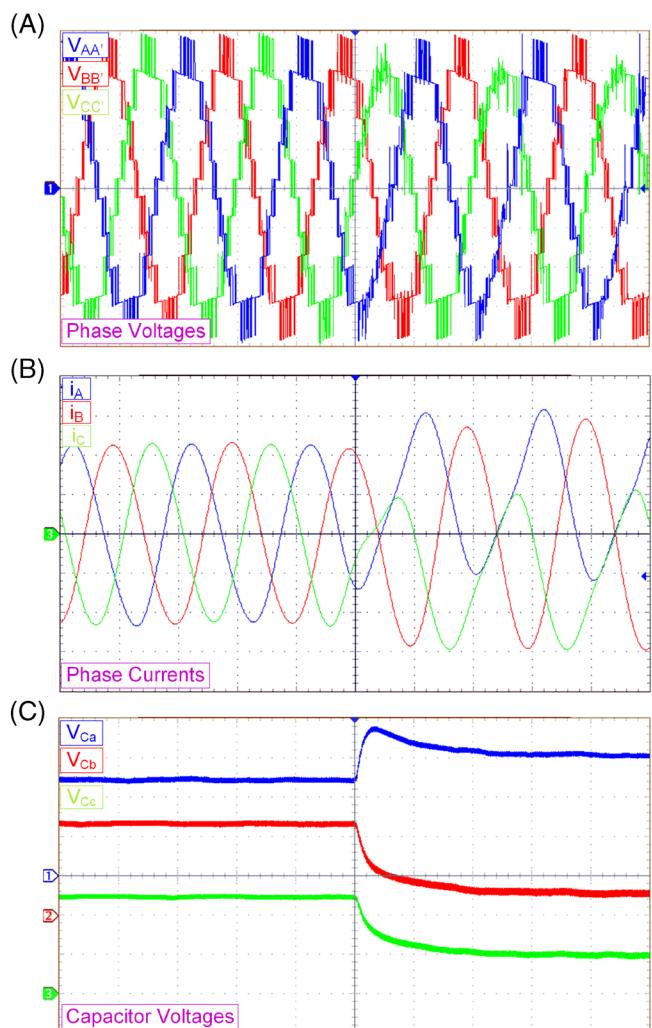

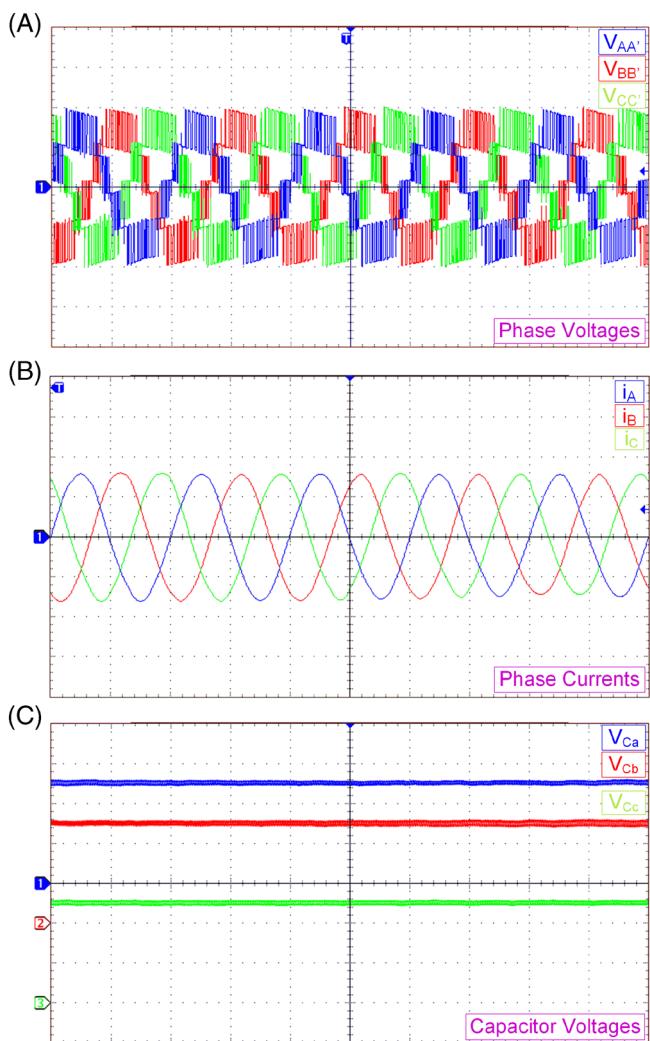

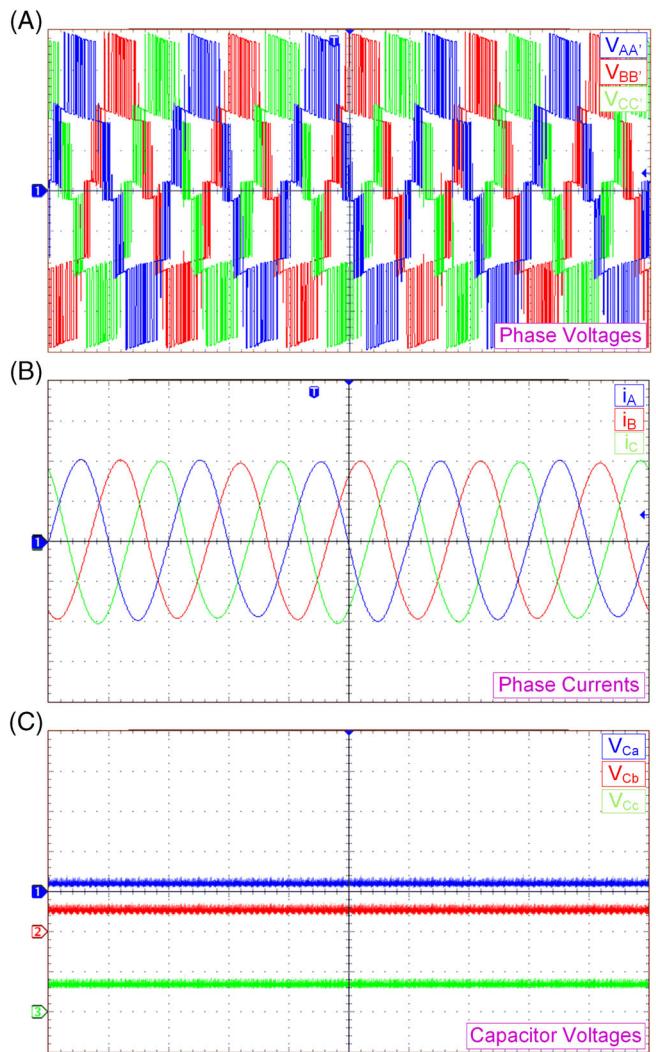

**FIGURE 8** Experimental set-up**FIGURE 9** Experimental results of SCBT; A, three-phase output voltages  $V_{AA'}$ ,  $V_{BB'}$  and  $V_{CC'}$  (X-axis: 10 ms/div, Y-axis: 50 V/div); B, three-phase currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, voltages across capacitor in each phase (X-axis: 1 s/div, Y-axis: 20 V/div); D, output voltage  $V_{AA'}$  with variation in modulation index; E, THD for phase voltage; F, THD of phase current

**FIGURE 10** Experimental results for SCBT; A, output voltage across phase-A winding (X-axis: 1 s/div, Y-axis: 50 V/div), current through phase-A winding (Y-axis: 5A/div) and speed of the motor during starting (Y-axis: 800 rpm/div); B, output voltage across phase-A winding (X-axis: 2 s/div, Y-axis: 50 V/div), current through phase-A winding (Y-axis: 5A/div) and speed of the motor (Y-axis: 800 rpm/div) with change in modulation index from 1 to 0.5 after 5 seconds

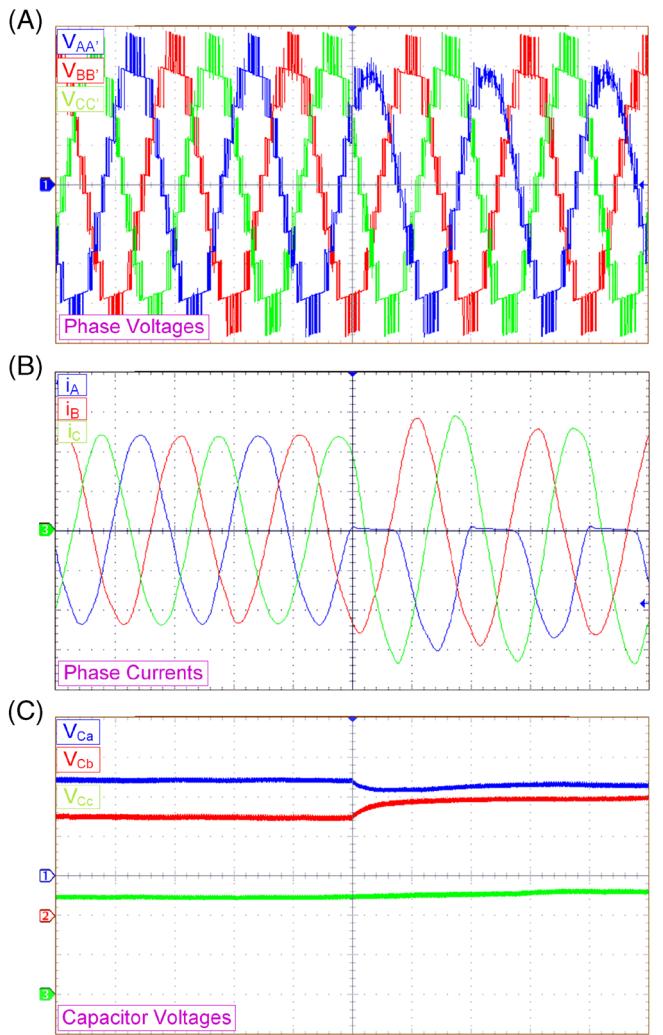

**FIGURE 11** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) for OC fault in switch  $Sa_1$

the same leg. The strategy applied to the OC and SC faults in any switch is the same for both the topologies. The proposed topologies are capable of operating under switch faults, hence are more reliable compared to conventional topologies.

**FIGURE 12** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) for OC fault in switch Sa3

## 7 | RESULTS AND DISCUSSIONS

The proposed topologies are designed such that the switches in neutral path act as level generators, whereas the switches connected to the windings act as polarity generators. As a result, the output voltages obtained across every phase have nine levels ( $\pm 2$  V,  $\pm 3$  V/2,  $\pm V$ ,  $\pm V/2$ , 0) in it and the maximum output voltage is twice the source voltage (V), that is, 2 V. The proposed topologies are fed from three isolated DC sources each of 100 V to feed 1-HP OEWIM. The modified-reference PWM technique is employed to produce switching pulses for the proposed topologies and are dispensed using dSPACE 1104. A modified sinusoidal reference of the fundamental frequency is compared with the triangular carrier of frequency 1.5 kHz to generate switching pulses. The experimental set-up of the proposed topology (SCBT) feeding 1-hp OEWIM is presented in Figure 8.

### 7.1 | Experimental results

The three-phase output voltages, currents at no-load through three-phase windings and the voltage across the FCs in the inverters feeding the OEWIM from SCBT are illustrated in Figure 9. Figure 9A presents the phase voltages  $V_{AA'}$  (blue trace),  $V_{BB'}$  (red trace) and  $V_{CC'}$  (green trace) across the load terminals A-A', B-B' and C-C', respectively. The terminals A-A', B-B' and C-C' represent phase-A, phase-B and phase-C windings of the OEWIM, respectively. Figure 9B represents three-phase currents  $i_A$  (blue trace),  $i_B$  (red trace) and  $i_C$  (green trace) drawn by the OEWIM at no-load condition. Figure 9C presents the voltages  $V_{ca}$  (blue trace),  $V_{cb}$  (red trace) and  $V_{cc}$  (green trace) that represent the voltage across the FC in inverter-a, inverter-b and inverter-c, respectively. The output voltage  $V_{AA'}$

**FIGURE 13** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) for OC fault in switch Sa5

for various values of modulation index ( $Ma = 1, 0.75, 0.5, 0.25$ ) is presented in Figure 9D. The fast Fourier transform (FFT) of THD in the output phase voltage ( $V_{AA'}$ ) and current ( $i_A$ ) in phase-A are presented in Figure 9E,F, respectively.

The behaviour of the system during starting with an increase in modulation index from 0.2 to 1 is illustrated in Figure 10A. The reference wave magnitude is determined by constant  $V/F$  ratio and speed requirement of the motor. The transition of output voltage from three levels to nine levels can be observed clearly. During starting, the current drawn by the IM is high and as the motor speed approaches the rated value, the current approaches the rated value. Figure 10B illustrates the behaviour of the system for a change in modulation index from 1 to 0.5. Decrease in modulation index will decrease the number of levels from nine to five in the output voltage, hence the output voltage magnitude reduces to half. The speed of the motor also reduces from 1440 rpm to 1270 rpm.

## 7.2 | Performance of SCBT during switch faults

The SCBT delivers nine-level output voltage across all the three phases under normal operating conditions. The balanced and identical output voltage across all the three phases is obtained from the inverters owing to symmetrical switching of the switching devices. However, if any of the switch fails (either OC or SC), then it leads to loss of symmetry in switching and results in unbalance in the voltage fed to the OEWIM drive. Therefore, the unbalance in the supply fed to the motor will result in unbalanced currents that lead to excessive heating of the winding.

**FIGURE 14** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) for OC fault in switch  $S_{a1}$

The effect of OC fault in switches on three-phase output voltages, no-load currents and the voltage across the FCs are to be analysed. The OC fault is created by disengaging switching pulses to the switch. Since each inverter is provided with an FC, the variation of capacitor voltages due to switch faults will be substantial depending upon the fault location. To clearly understand the variation in the FC voltages during switch faults, the scale for X-axis of capacitor voltages is taken as 1 s/div. The waveforms of the output voltages and currents for OC of switch  $S_{a1}$  in inverter-a are presented in Figure 11A,B. The effect of switch  $S_{a1}$  OC on FC voltages is presented in Figure 11C. Switch  $S_{a1}$  is in the neutral path of the inverter topology and is linked with phase-A and phase-C. Hence the OC of the switch  $S_{a1}$  will affect the output of two phases. The negative peak of voltage  $V_{AA'}$  and the positive peak of the voltage  $V_{CC'}$  are affected. The voltages across FCs also get affected with this switch fault. The voltage across FC in inverter-a increases to 60 V and the voltage across FC in inverter-b and inverter-c decreases to 10 V and 20 V, respectively.

Similarly, if OC fault occurs in switch  $S_{2a}$ , since the switch  $S_{2a}$  is operating in complementary to the switch  $S_{a1}$ , the positive peak of the voltage  $V_{AA'}$  and the negative peak of the voltage  $V_{CC'}$  will be affected. Consequently, the OC fault in switch  $S_{2a}$  would produce outputs as a vertical flip version of the results presented for OC of switch  $S_{a1}$ . Hence the faults in lower switches in the inverter legs that operate in complementary with upper switches are not produced. Figure 12 presents the output voltages, no-load currents and FC voltages when switch  $S_{3a}$  is open-circuited. Since the switch  $S_{3a}$  in inverter-a is connected to phase-A winding, fault in such switch will affect the phase voltage  $V_{AA'}$  and limits the flow of current during positive half cycle as illustrated in Figure 12A,B. The current  $i_A$  will be a positive clamped wave with this switch fault. The FC voltage  $V_{Cc}$  is least affected with this fault, whereas the voltage  $V_{Ca}$  decreases slightly from 50 V to 46 V and the voltage  $V_{Cb}$  rises to 60 V as illustrated in Figure 12C.

**FIGURE 15** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) with MSL for  $S_{a1}$  OC in SCBT

Similarly, if OC fault occurs in switch  $S_{5a}$  in inverter-a, the output voltages, no-load currents and the voltage across FCs will be as illustrated in Figure 13. As the switch  $S_{5a}$  is connected to phase-C, then the OC fault in  $S_{5a}$  will affect the negative peak of voltage  $V_{CC'}$  and does not allow any current in the negative cycle as illustrated in Figure 13A,B. The voltage across all the three FCs will be affected as illustrated in Figure 13C.

The output voltages, no-load currents and voltage across FCs when switch  $S_{7a}$  gets OC are presented in Figure 14. The OC fault in  $S_{7a}$  will avoid FC  $C_a$  from charging and discharging, hence the number of levels in the output voltage will gradually decrease to five levels, keeping the maximum voltage the same as that with nine levels in the output voltage as illustrated in Figure 14A,B. The voltages  $V_{AA'}$  and  $V_{CC'}$  will get affected with this fault and the voltage  $V_{Ca}$  will rise to source voltage  $V_{DC}/2$  as the switch  $S_{7a}$  is open-circuited. The FC voltage  $V_{Cb}$  rise marginally and  $V_{Cc}$  increase from 50 V to 60 V as illustrated in Figure 14C. Hence the withstanding voltage of the FCs used for this topology should be the same as that of the source voltage ( $V_{DC}/2$ ) such that the capacitors can withstand the voltage under such fault conditions without any damage.

### 7.3 | Performance of the proposed topologies with MSL

The proposed topologies are capable of operating even under switch fault conditions. Whenever OC fault occurs in any of the switches, instead of complete shutdown of the supply system, the proposed topologies are made to operate with MSL provided in Tables 5 and 6 designed considering the available switches exempting the faulty switch.

**FIGURE 16** Experimental results of: A, three-phase output voltage (X-axis: 10 ms/div, Y-axis: 50 V/div); B, no-load currents (X-axis: 10 ms/div, Y-axis: 500 mA/div); C, floating capacitor voltages (X-axis: 1 s/div, Y-axis: 20 V/div) with MSL for Sa7 OC in SCBT

Lowering the value of  $M_a$  not only reduces the number of levels in the output voltage, its magnitude also reduces to half and hence the output power reduces. The FCs are charged to the same voltage level of  $V/2$  with MSL as illustrated in Figure 15C. However, for the faults in switches  $S_{x7}$  and  $S_{x8}$  (where  $x \in a, b, c$ ), the application of MSL will result in five-level output voltage with maximum output voltage twice the source voltage as depicted in Figure 16A. Since the FCs have no role to play in the post-fault operation, the voltages across the FCs drop near to zero as illustrated in Figure 16C. Therefore, the presented results prove that the proposed topologies work satisfactorily as five-level inverters with rated power even if the fault occurs in FC or the switches across the FC.

The proposed topologies ensure operation through normal conditions with nine-level output voltage with each step level as  $V/2$  across each phase winding. During fault conditions, such as switch OC or SC, the proposed topologies still ensure uninterrupted operation with the decrease in levels in the output voltage as well as power. This uninterrupted operation of the proposed topologies is ensured by amending the switching pulses fed to the switches for post-fault operation. Through this study of proposed topologies over normal and abnormal conditions with pre- and post-fault analyses, it can be justified that the proposed topologies exhibit fault-tolerance property for switch faults.

Every single MLI topology possesses both advantages and shortcomings based on the area of application, and the proposed topologies are not an exemption. Compared with the conventional topologies (NPC, FC and CHB topologies), the proposed topologies have certain shortcomings such as non-modular structure and require three isolated DC sources. However, with the advantages of low source voltage requirement, simple construction and its fault-tolerance property, the proposed topologies find applications in low-voltage applications such as solar PV or fuel cell fed battery-driven electric vehicles or in industries such as steel rolling mills, paper rolling mills, etc.

## 8 | CONCLUSION

This paper presents FC-based fault-tolerant MLI topologies that can deliver nine-level output voltage. The proposed topologies employ a configuration that requires three three-phase inverters with an isolated DC source, FCs and additional active switches for each inverter. The FCs are charged and discharged to generate intermediate levels of the output voltage. Conventional SPWM techniques can be employed to generate switching pulses for these topologies. The proposed topologies are designed with fewer components compared to other nine-level topologies feeding OEWIM drive that are present in the literature. The magnitude of voltage sources required is also less compared to conventional topologies, hence the proposed topologies find good scope in renewable energy source applications and industry as well. The voltage rating of the FCs required is only half the source voltage rating, but to withstand the voltage during certain switch faults, the rating of the FCs should be made equal to source voltage. Both the topologies are capable of delivering power to the load during switch fault conditions. In the post-fault operation, the inverters are run with MSL and can deliver balanced three-phase output voltage with reduced number of levels, thereby ensuring continuity of supply to load even under switch fault conditions. The proposed topologies suit better for medium- and high-power traction and industrial drive applications.

## PEER REVIEW

The peer review history for this article is available at <https://publons.com/publon/10.1002/2050-7038.12718>.

## DATA AVAILABILITY STATEMENT

The data that support the findings of this study are available within the article and also in appropriate references.

## ORCID

Narender Reddy Kedika  <https://orcid.org/0000-0001-7193-655X>

## REFERENCES

1. Rodríguez J, Bernet S, Wu B, Pontt JO, Kouro S. Multilevel voltage-source-converter topologies for industrial medium-voltage drives. *IEEE Trans Ind Electron*. 2007;54(6):2930-2945.

2. Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MAM. The age of multilevel converters arrives. *IEEE Ind Electron Mag*. 2008;2(2):28-39.

3. Peng FZ. A generalized multilevel inverter topology with self voltage balancing. *IEEE Trans Ind Appl*. 2001;37(2):611-618.

4. Vazquez S, Leon JI, Franquelo LG, Padilla JJ, Carrasco JM. DC-voltage-ratio control strategy for multilevel cascaded converters fed with a single DC source. *IEEE Trans Ind Electron*. 2009;56(7):2513-2521.

5. Kuncham SK, Annamalai K, Nallamothu S. A new structure of single-phase two-stage hybrid transformerless multilevel PV inverter. *International Journal of Circuit Theory and Applications*. 2019;47(1):152-174. <http://dx.doi.org/10.1002/cta.2580>.

6. Jammy RR, Annamalai K. A new configuration of seven-level quasi Z-source-based isolated inverter for renewable applications. *Int Trans Electr Energy Syst*. 2019;29(5):1-19.

7. Can E. Novel high multilevel inverters investigated on simulation. *Electr Eng*. 2016;99(2):633-638.

8. Mahato B, Majumdar S, Jana KC. Single-phase modified T-type-based multilevel inverter with reduced number of power electronic devices. *Int Trans Electr Energy Syst*. 2019;29(11):1-16.

9. Sedaghati F, Majareh SHL. A multilevel inverter based on cascade connection of submultilevel units with reduced switch count. *Int J Circuit Theory Appl*. 2019;47(7):1152-1172.

10. Siddique MD, Mekhilef S, Shah NM, Sarwar A, Memon MA. A new single-phase cascaded multilevel inverter topology with reduced number of switches and voltage stress. *Int Trans Electr Energy Syst*. 2020;30(2):1-21.

11. Ajaykumar T, Patne NR. Fault-tolerant switched capacitor-based boost multilevel inverter. *Int J Circuit Theory Appl*. 2019;47(10):1615-1629.

12. Dewangan NK, Gupta KK, Bhatnagar P. Modified reduced device multilevel inverter structures with open circuit fault-tolerance capabilities. *Int Trans Electr Energy Syst*. 2020;30(1):1-15.

13. Can E. Fault determination and analysis of complex switching structure at multilevel inverter. *Tehnicki Vjesnik*. 2019;26(2):398-404.

14. Stemmler H, Gegenbach P. Configurations of high power voltage source inverter drives. *Proc EPE Conf*. 1993;5:7-12.

15. Srinivasan P, Narasimharaju BL, Srikanth NV. Space-vector pulse width modulation scheme for open-end winding induction motor drive configuration. *IET Power Electron*. 2015;8(7):1083-1094.

16. Lakhimsetty S, Somasekhar VT. An efficient predictive current control strategy for a four-level open-end winding induction motor drive. *IEEE Trans Power Electron*. 2020;35(6):6198-6207.

17. Srinivasan P, Venugopal Reddy B, Somasekhar VT. PWM switching strategy for the elimination of common mode voltage of a two-level inverter drive with an open-end winding induction motor configuration; 2010 Joint International Conference of Power Electronics, Drives and Energy Systems PEDES 2010 and 2010 Power India.

18. Rajeevan PP, Sivakumar K, Gopakumar K, Patel C, Abu-Rub H. A nine-level inverter topology for medium-voltage induction motor drive with open-end stator winding. *IEEE Trans Ind Electron*. 2013;60(9):3627-3636.

19. Rajeevan PP, Sivakumar K, Patel C, Ramchand R, Gopakumar K. A seven-level inverter topology for induction motor drive using two-level inverters and floating capacitor fed H-bridges. *IEEE Trans Power Electron*. 2011;26(6):1733-1740.

20. Mondal G, Sivakumar K, Ramchand R, Gopakumar K, Levi E. A dual seven-level inverter supply for an open-end winding induction motor drive. *IEEE Trans Ind Electron*. 2009;56(5):1665-1673.

21. Kshirsagar A, Kaarthik RS, Rahul A, et al. 17-Level inverter with low component count for open-end induction motor drives. *IET Power Electron*. 2018;11(5):922-929.

22. Reddy KN, Pradabane S. Modified H-bridge inverter based fault-tolerant multilevel topology for open-end winding induction motor drive. *IET Power Electron*. 2019;12(11):2810-2820.

23. Omer P, Kumar J, Surjan BS. A review on reduced switch count multilevel inverter topologies. *IEEE Access*. 2020;8:22281-22302.

24. Karthik A, Loganathan U. A reduced component count five-level inverter topology for high reliability electric drives. *IEEE Trans Power Electron*. 2020;35(1):725-732.

25. Pires VF, Foito D, Silva JF. Fault-tolerant multilevel topology based on three-phase H-bridge inverters for open-end winding induction motor drives. *IEEE Trans Energy Convers*. 2017;32(3):895-902.

26. Vemuganti HP, Sreenivasarao D, Kumar GS. Improved pulse-width modulation scheme for T-type multilevel inverter. *IET Power Electron*. 2017;10(8):968-976.

27. Wu F, Duan J, Feng F. Modified single-carrier multilevel sinusoidal pulse width modulation for asymmetrical insulated gate bipolar transistor-clamped grid-connected inverter. *IET Power Electron*. 2015;8(8):1531-1541.

28. Abhilash T, Annamalai K, Tirumala SV. A seven-level VSI with a front-end cascaded three-level inverter and flying-capacitor-fed H-bridge. *IEEE Trans Ind Appl*. 2019;55(6):6073-6088.

**How to cite this article:** Kedika NR, Pradabane S. Fault-tolerant multi-level inverter topologies for open-end winding induction motor drive. *Int Trans Electr Energ Syst*. 2021;31:e12718. <https://doi.org/10.1002/2050-7038.12718>