# An Asymmetrical Dual Quasi-Z-Source Based 7-Level Inverter for PV Applications

P. Manoj , A. Kirubakaran , *Senior Member, IEEE*, and V. T. Somasekhar , *Member, IEEE*

**Abstract**—This paper presents a new single-stage quasi-z-source (qZS) based power converter for Photovoltaic (PV) applications. This seamless topology is obtained by the fusion of two quasi-z-source networks with a 7-level cascaded multilevel inverter (MLI). The proposed converter requires fewer passive components and power switching devices compared to the seven-level topologies with impedance and quasi-impedance sources, reported in the literature. The proposed modulation technique achieves the required level of voltage boosting using the qZS networks while synthesizing seven levels in the output voltage waveform. While the proposed power converter can regulate the output voltage in the standalone mode, it can inject active power into the grid at Unity power factor (UPF) in the grid-connected mode of operation. This paper also aims to mitigate the leakage current, which is one of the major issues in transformerless PV inverters, by reducing the magnitude of voltage transitions in the parasitic capacitor and the suppression of higher-order harmonics in the ground leakage current. The steady-state and the dynamic performances of the proposed power converter during grid-connected mode of operation is assessed with simulation studies and are validated with experimental results.

**Index Terms**—Quasi-Z-source (qZS) network, leakage current, voltage boosting, 7-level cascaded MLI.

## I. INTRODUCTION

**P**HOTOVOLTAIC generation of electrical energy has steadily grown in the last couple of decades owing to its cleanliness and reliability. Lower maintenance, durability, and falling costs are likely to cause an increased generation of solar energy in the foreseeable future. However, the solar PV systems output DC voltage which requires a power converter to convert it to AC form, either to be utilized in standalone systems or inject power into the grid [1]. In solar PV systems, the low output voltage of PV panels is boosted to a higher voltage using a separate DC-DC boost converter. The boosted DC-link voltage is then fed to an inverter to generate the AC voltage of the required magnitude and frequency. This two-stage conversion achieves its objectives at the expense of efficiency at an increased cost [2], [3]. To overcome these disadvantages, a single-stage Z-source inverter (ZSI) topology is proposed. This monolithic structure, while boosting the PV voltage, can produce an AC output

Manuscript received 11 May 2022; revised 7 September 2022; accepted 12 November 2022. Date of publication 17 November 2022; date of current version 23 May 2023. Paper no. TEC-00493-2022. (Corresponding author: P. Manoj.)

The authors are with the Department of Electrical Engineering, National Institute of Technology at Warangal, Warangal 506004, India (e-mail: manoj100592@gmail.com; kiruba81@nitw.ac.in; sekhar@nitw.ac.in).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TEC.2022.3222498>.

Digital Object Identifier 10.1109/TEC.2022.3222498

voltage of the required voltage and magnitude. Additionally, this system offers an inherent shoot-through (ST) protection of power semiconductor switching devices [4], [5]. The Z-source is a symmetrically configured LC network consisting of a DC source and a series diode, which displays an inherent ability to boost the input voltage. However, switching of the series power diode in Z-source results in a discontinuous input current, which is not favorable for PV applications. This disadvantage is overcome with a variant of the Z-source, which is known as the quasi-z-source (qZS) [6]. While resulting in a continuous input current, the qZS reduces the voltage rating of one of the capacitors significantly.

In recent years, multilevel inverters (MLI) [7], [8] are extensively used in high power applications over the conventional 2-level inverters due to the following advantages: (i) reduced harmonic contamination in the output (ii) reduced voltage stress on semiconductor devices (iii) smaller filter sizes and (iv) lower EMI. Despite these advantages, conventional multilevel inverters (being buck type DC-AC power converters) produce an output voltage with a peak value that is less than the input DC voltage. This limitation is successfully overcome by integrating a ZS / qZS with an MLI, making it a buck-boost inverter [9], [10].

Initially, Z-sources are integrated with MLIs of Neutral point clamped (NPC) and Cascaded-H-bridge (CHB) types. A three-level NPC is integrated with two isolated ZS networks to boost the input voltage to produce a 5-level phase voltage waveform [11], [12]. In the work reported in [13], a three-level NPC topology is integrated with a single Z-source and two DC sources. Despite this attempt to optimize the topology, the cost of the system could not be brought down as a consequence of the increased rating of passive elements. Furthermore, both of these topologies demand additional clamping diodes, which increases the cost and lowers the reliability. Further, a seven-level inverter topology is reported in [14], wherein a cascaded Z-source network with two switches is connected to an H-bridge inverter. This power converter requires fewer semiconductor switches compared to the other ZS-NPC topologies. However, this topology needs three isolated Z-source networks, which increase the number of passive components. The drawback of discontinuous input current associated with the Z-source-MLIs is overcome by fusing the NPC and CHB topologies with a quasi-z-source.

The research work presented in [15] describes an integrated system, wherein two symmetrical qZS networks are integrated with a 3-level NPC converter. Apart from the requirement of clamping diodes, this topology suffers from the drawback of neutral point deviations, which are typically found in all NPC-

based power circuits. In qZS-based CHB topologies [16], [17], [18], each H-bridge inverter requires an exclusive qZS. This increases the number of passive elements as well as switching devices. In addition, all the isolated PV sources require independent Maximum power point tracking (MPPT) and DC-link voltage control, thereby increasing the complexity of control [19]. In [20], a five-level quasi switched boost MLI (qSB-MLI) is proposed, which avoids two inductors and two capacitors compared to qZS-CHB. However, the qSB-MLI requires two additional switches and diodes to boost the input DC voltage. In all of these topologies [15], [16], [17], [18], [19], [20], the number of passive components and switching devices increases with an increase in the number of voltage levels. A modified qZS-based hybrid 3-level inverter is proposed in [21], which needs fewer inductors and semiconductor devices with a single DC source. However, in [21], the device current and voltage stress are increased when compared to qZS-CHB and qSB-MLI topologies. In addition to this the power converter results in a discontinuous input current which is not favorable for PV applications. Further in [22], an NPC-based qZS inverter is proposed which employs 8 switching devices to synthesize a 5-level output voltage waveform. However, in addition to the switching devices, additional clamping diodes are also required for freewheeling operation.

Leakage current is another major issue in PV-fed grid-connected transformerless inverter [23], [24]. High-frequency transitions in the Common mode voltage (CMV) of the MLI charge the parasitic capacitance of the PV panel, facilitating the flow of leakage current. If this leakage current is not restricted to be within the prescribed limits, the safety of the PV system could be compromised. Apart from the regular switching transitions, the shoot-through states (which are deliberately introduced in ZS / qZS-based MLIs to achieve the required voltage boosting) also contribute to the high-frequency transitions in CMV.

The research work reported in [25] minimizes high-frequency transitions in CMV with the employment of a modified PWM scheme, which selects appropriate zero-states in a switching cycle. The qZS inverter described in [26] employs two additional switches to connect the grid neutral to the negative DC bus of the input source. When switched at grid frequency, these devices show a path to the leakage current while limiting high-frequency transitions in common-mode voltage. In contrast to [26], the power converter proposed in [27] connects two switches and two diodes across the grid, which conduct during the freewheeling conditions, effectively decoupling the PV source from the grid. As far as the issue of leakage current is concerned, the aforementioned literature [25], [26], [27] is confined to two-level, single-phase qZS-based inverters.

The aforementioned literature on single-phase, qZS-MLI reveals the following limitations in the present state-of-the-art: (i) requirement of a higher number of power semiconductor switching devices, (ii) leakage current, and (iii) discontinuous input current. These shortcomings are the impetus for the development of the single-stage dual quasi-z-source 7-level inverter (DqZS-7LI) topology proposed in this manuscript. This power converter configuration, which utilizes a lower number of devices, is obtained by combining two antiparallel qZS networks with a cascaded 7-level H-bridge circuit. This paper also pro-

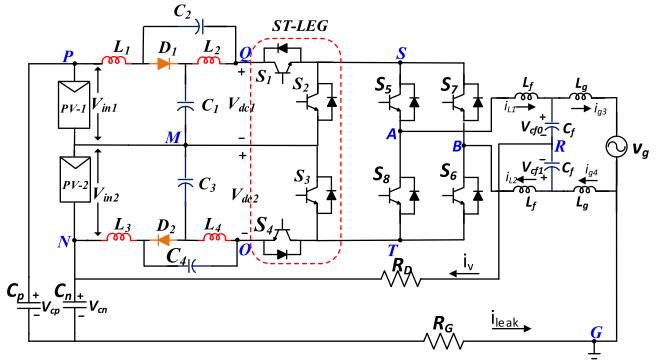

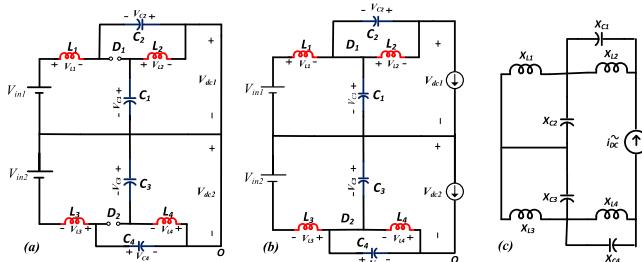

Fig. 1. Proposed DqZS-7LI.

poses a modified level-shifted PWM scheme, which achieves the twin objectives of input voltage boosting and generation of 7-levels in the output voltage. Along with the proposed PWM technique, an LCL filter is used to reduce the high-frequency voltage transitions across the parasitic capacitance. This restricts the leakage current within the safety standards stipulated by the VDE0126-1-1 [28]. Steady-state and dynamic performances of the power converter are evaluated both in standalone and the grid-connected modes with the aid of simulation studies and are experimentally verified with a hardware prototype.

## II. THE PROPOSED DQZS-7LI

### A. Proposed Power Converter

The proposed PV fed dual- quasi-z-source 7-level inverter (DqZS-7LI) topology is shown in Fig. 1. This configuration employs two PV sources, PV-1 and PV-2, with an unequal voltage ratio of 1:2 respectively. Also, this topology consists of two quasi-z-source networks and a cascaded 7-level H-bridge inverter. The outputs of the PV sources are input to the quasi-z-source networks as shown in Fig. 1. The qZS networks boost the input PV voltage to suit the requirements of the 7-level inverter. The top qZS network (qZS-1) employs switches S<sub>1</sub> and S<sub>2</sub> to obtain the required shoot-through. Similarly, the switches S<sub>3</sub> and S<sub>4</sub> are used to obtain the shoot-through for the bottom qZS network (qZS-2). As shown in Fig. 1, the midpoints of the switches S<sub>1</sub>, S<sub>2</sub>, and S<sub>3</sub>, S<sub>4</sub> respectively serve as the positive and negative DC rails for the output H-bridge inverter, which is constituted by the switches S<sub>5</sub>-S<sub>8</sub>. The midpoints A and B of the H-bridge are interfaced to the grid with a symmetrical LCL filter. The detailed description of the parameters C<sub>p</sub>, C<sub>n</sub>, R<sub>D</sub>, and R<sub>G</sub> are explained in section V.

### B. Output Voltage Levels and Corresponding Switching States of the Power Converter

The proposed configuration is capable of generating seven levels in the output phase voltage waveform  $V_{AB}$  (see Column-2, Table I). In Table I, the 'on' and the 'off' states of the semiconductor devices are indicated as logic '1' and '0' respectively. These switching states are classified into two types namely, the non-shoot-through states (NST), and the shoot-through states (ST). The NST states are further sub-divided into six active states and two zero states. These active -states generate six

TABLE I

SWITCHING COMBINATIONS TO ACHIEVE 7-LEVEL OPERATION

| State type | Voltage ( $V_{AB}$ ) for<br>$V_{in1} = V$ &<br>$V_{in2} = 2V$ | Switching states (1-ON, 0-OFF) |       |       |       |       |       |       |       |

|------------|---------------------------------------------------------------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|

|            |                                                               | $S_1$                          | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$ |

| <i>NST</i> | 3V                                                            | 1                              | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

| <i>NST</i> | 2V                                                            | 0                              | 1     | 0     | 1     | 1     | 1     | 0     | 0     |

| <i>NST</i> | V                                                             | 1                              | 0     | 1     | 0     | 1     | 1     | 0     | 0     |

| <i>NST</i> | 0                                                             | 0                              | 0     | 0     | 0     | 1     | 0     | 1     | 0     |

| <i>NST</i> | 0                                                             | 0                              | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

| <i>NST</i> | $-V$                                                          | 1                              | 0     | 1     | 0     | 0     | 0     | 1     | 1     |

| <i>NST</i> | $-2V$                                                         | 0                              | 1     | 0     | 1     | 0     | 0     | 1     | 1     |

| <i>NST</i> | $-3V$                                                         | 1                              | 0     | 0     | 1     | 0     | 0     | 1     | 1     |

| <i>ST</i>  | 0                                                             | 1                              | 1     | 0     | 0     | 1     | 0     | 1     | 0     |

| <i>ST</i>  | 0                                                             | 0                              | 0     | 1     | 1     | 1     | 0     | 1     | 0     |

| <i>ST</i>  | 0                                                             | 1                              | 1     | 1     | 1     | 1     | 0     | 1     | 0     |

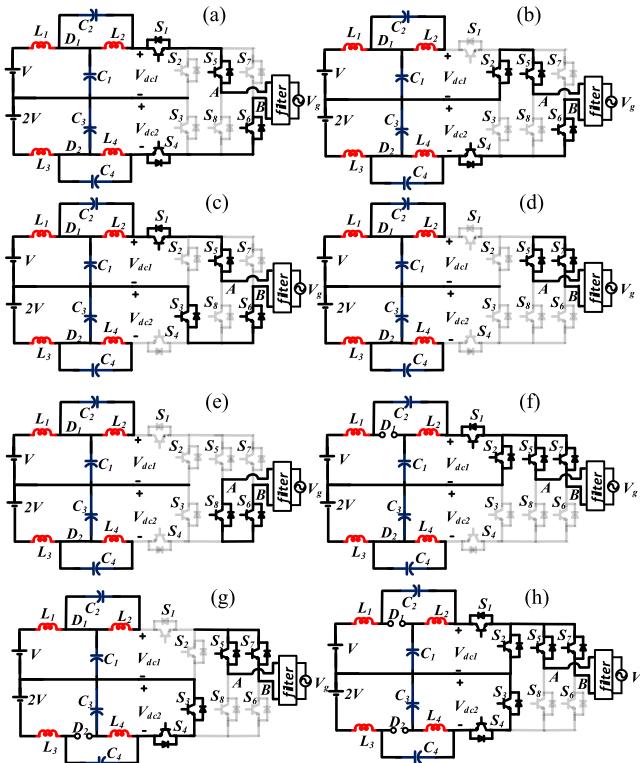

Fig. 2. Circuit diagrams for NST and ST states of the power converter.

distinct voltage levels  $\pm V$ ,  $\pm 2V$ , and  $\pm 3V$  in the output voltage waveform (considering  $V_{in} = V$ ).

Fig. 2 presents the operating modes of the proposed converter during the NST and the ST states. While Fig. 2(a)–(e) represent the NST modes of the power converter, Fig. 2(f)–(h) represents the ST mode. From Fig. 2(a), it may be noticed that by turning on  $S_1$  and  $S_4$ , the combined DC-link voltage ( $V_{dc1} + V_{dc2}$ , Fig. 1) is equal to  $+3V$ , which is applied to the H-bridge inverter terminals. Fig. 2(b) shows the operating mode to synthesize the voltage level of  $+2V$ , wherein the switches  $S_2$  and  $S_4$  are turned on. The operating mode to generate the level of  $+V$  is demonstrated in Fig. 2(c), wherein the switches  $S_1$  and  $S_3$  are turned on (Table I and Fig. 2(c)). It may be noted that the switches

$S_5$  and  $S_8$  are turned on in all these three modes to connect the rails of the H-bridge to the outputs of the qZS networks. The method of synthesizing the three negative levels ( $-V$ ,  $-2V$ , and  $-3V$ ) can readily be deduced with the aid of Table I. In the zero states, the H-bridge is completely isolated from the qZS networks by turning off all the four switches  $S_1$  -  $S_4$  as shown in Fig. 2(d) and (e). During these two states, there is no power transfer between the PV source and the load. Thus, it is evident that the shoot-through (ST) mode of operation can be inserted in the zero-state.

In the proposed power converter, the shoot-through mode of operation can be implemented in three different ways. These are: (i) qZS-1 shoot-through (Fig. 2(f)) (ii) qZS-2 shoot-through (Fig. 2(g)) (iii) both qZS-1 and qZS-2 shoot-through (Fig. 2(h)). In (i) and (ii) shoot-through modes of operation the respective DC-link voltages ( $V_{dc1}$ ,  $V_{dc2}$ ) of the qZS networks drop to zero, and in (iii) the total DC-link voltage ( $V_{dc1} + V_{dc2}$ ) of the power converter drop to zero. In this configuration, the zero-state (which includes the ST state) is inserted in all the 7 levels of operation to obtain the required boosting of the DC-link voltage. Consequently, the output voltage displays pulsation (from zero to the synthesized voltage level) in any given time period.

### III. CONTROL SCHEME FOR THE PROPOSED DUAL QZS 7-LEVEL INVERTER

#### A. Implementation of the MLS-PWM Scheme

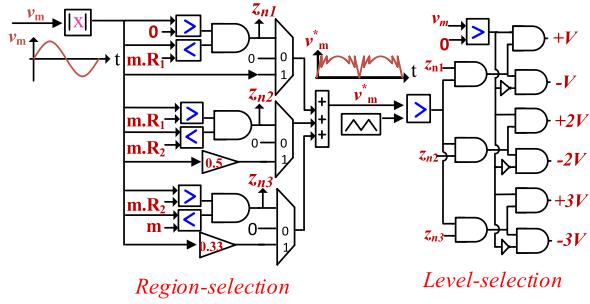

Generally, two control techniques are commonly employed to obtain a multilevel output waveform: (i) level-shifted PWM (LSPWM) and, (ii) phase-shifted PWM. In this work, a modified level-shifted PWM (MLSPWM) is implemented to synthesize the desired 7-level phase voltage waveform with input voltage boosting. To synthesize the required 7-level output voltage waveform despite the asymmetry in the input voltages, the sinusoidal modulating signal ( $v_m = m \sin(\omega t)$ ) should be modified to  $v_m^*$  as shown in Fig. 3. The PWM scheme is implemented by comparing a modified reference signal ( $v_m^*$ ) with a single carrier signal. Initially, the modulated sine wave ( $v_m$ ) is divided into three regions of operation  $Z_{n1}$ ,  $Z_{n2}$ , and  $Z_{n3}$  (shown in Fig. 3) based on the value of modulation index ( $m$ ) and ' $R_1$ ', ' $R_2$ ', where ' $R_1$ ' and ' $R_2$ ' are defined as the multiplication factors which are taken into consideration for asymmetry of the input voltages. The multiplication factors ' $R_1$ ' and ' $R_2$ ' are expressed as:

$$R_1 = V_{in1}/V_{in1} + V_{in2}, R_2 = V_{in2}/V_{in1} + V_{in2} \quad (1)$$

In region-1, wherein  $0 < v_m < (R_1 \cdot m)$ , the modulated sine wave ( $v_m$ ) is not modified. In region-2 ( $R_1 \cdot m < v_m < R_2 \cdot m$ ), the sine wave ( $v_m$ ) is scaled down to  $v_m/2$  and in region-3 ( $R_2 \cdot m < v_m < m$ ), it is scaled down to  $v_m/3$ . The summation of the references in regions 1, 2 & 3 synthesizes the modified reference wave ( $v_m^*$ ) as shown in Fig 3. The modified reference wave ( $v_m^*$ ), shown in Fig. 3, is plotted considering the voltage ratio of the input PV sources (1:2). Hence  $R_1$  and  $R_2$  are selected as 1/3 and 2/3.

The modified reference wave ( $v_m^*$ ) is compared with the carrier wave (C) in the three regions mentioned above, for both positive and negative half-cycles. The voltage level in the

Fig. 3. Implementation of modified reference wave ( $v_m^*$ ) for DqZS-7LI.Fig. 4. Implementation of modified reference wave ( $v_m^*$ ) for DqZS-7LI.

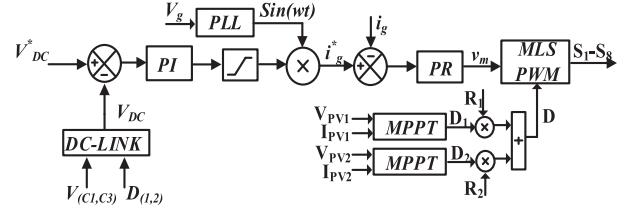

Fig. 5. Equivalent circuit of DqZS-7LI during (a) Shoot-through state (ST) (b) Non-shoot-through (NST) state. (c) Simplified equivalent circuit.

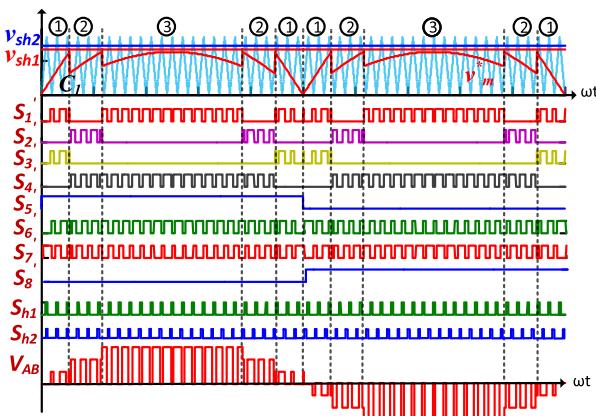

output is determined by the output of the comparator and the region of operation ( $Z_{n1}$ ,  $Z_{n2}$ , and  $Z_{n3}$ ) as shown in Fig. 3. Table I shows the generation of gating signals for the power devices to synthesize various voltage levels. Fig. 4 presents the PWM pulses ( $S_1$  -  $S_8$ ) required to synthesize the 7-level output voltage waveform. Further, to implement voltage boosting in qZS networks, two shoot-through pulses  $S_{h1}$  and  $S_{h2}$  are generated by comparing the DC references  $v_{sh1}$ ,  $v_{sh2}$  with the carrier signal (C). To facilitate the boosting operation with qZS-1 and qZS-2, logical 'OR' operations are respectively performed between the shoot-through pulse train ( $S_{h1}$ ) and the signals ( $S_1$  -  $S_2$ ), and the shoot-through pulse train ( $S_{h2}$ ) and the signals ( $S_3$  -  $S_4$ ). The signals obtained after these logical 'OR' operations are employed to gate the switches  $S_1$ - $S_4$ . It may be noted that the gating signals ( $S_5$  -  $S_8$ ) are directly used

to gate the switches  $S_5$ - $S_8$  to generate polarity in the output voltage.

### B. Boost-Factor of the Proposed DqZS-7LI

Fig. 5 shows the equivalent circuit for the proposed DqZS-7LI during shoot-through (ST) and non-shoot-through (NST) states of operation.

During the ST, the inductor voltages ( $V_{L1}$ ,  $V_{L2}$ ) and DC-link voltages are presented in (2), (3) & (4):

$$V_{L1} = V_{in1} + V_{c2}, \quad V_{L2} = V_{c1} \quad (2)$$

$$V_{L3} = V_{in2} + V_{c4}, \quad V_{L4} = V_{c3} \quad (3)$$

$$V_{dc1} = 0, \quad V_{dc2} = 0 \quad (4)$$

Similarly, in the NST state these are given by:

$$V_{L1} = V_{in1} - V_{c1}, \quad V_{dc2} = 0 \quad (5)$$

$$V_{L3} = V_{in2} - V_{c3}, \quad V_{L4} = -V_{c4} \quad (6)$$

$$V_{dc1} = V_{c1} + V_{c2}, \quad V_{dc2} = V_{c3} + V_{c4} \quad (7)$$

Applying the volt-sec balance to the inductors (2), (5), (3) & (6) over one switching time-period ( $T_s$ ) the following equations are derived:

$$V_{C1} = \frac{1 - D_1}{1 - 2D_1} V_{in1}, \quad V_{C2} = \frac{D_2}{1 - 2D_2} V_{in1} \quad (8)$$

$$V_{C3} = \frac{1 - D_1}{1 - 2D_1} V_{in2}, \quad V_{C4} = \frac{D_2}{1 - 2D_2} V_{in1} \quad (9)$$

where 'D<sub>1</sub> & D<sub>2</sub>' are the shoot-through (ST) duty ratios, which are expressed as  $T_{sh}/T_s$ , where  $T_{sh}$  is the ST time.

From (7), (8) & (9), the boosted DC-link voltages are expressed as:

$$V_{dc1} = \frac{1}{1 - 2D_1} V_{in1}, \quad V_{dc2} = \frac{1}{1 - 2D_2} V_{in2} \quad (10)$$

### C. Design of qZS Network of Proposed DqZS-7LI

In the proposed power converter the design of the quasi-z-source inductors and capacitors are derived based on the allowable low frequency current ripple of the inductor and DC-link voltage ripple of the inverter. This low-frequency ripple is caused by the second harmonic component of the output power. Further, to simplify the design equations only the low-frequency ripple component is considered neglecting the switching frequency ripple of the inductor current. The simplified equivalent circuit of the power converter is shown in Fig. 5(c). The current source  $i_{DC}^*$  shown in Fig. 5(c), represents the fundamental component of the DC-link current and  $X_{l(1-4)}$  to  $X_{c(1-4)}$  represent the reactive components of the quasi-z-source network.

From the equivalent circuit, the low-frequency component of  $i_{L1}$  is derived as:

$$i_{L1}^* = \frac{4\sqrt{2}}{3\pi} \cdot \frac{k(P_{OUT})}{V_{OUT}} \cdot \sin\left(\frac{4\pi t}{T} - \frac{\pi}{2}\right) \cdot \frac{x_{C2}}{x_{L1} + x_{C2}} \quad (11)$$

Where the variable 'k' represents the percentage of the power delivered by the PV-1. From (11) and the power balance of the power converter the low-frequency inductor ripple 'x' is

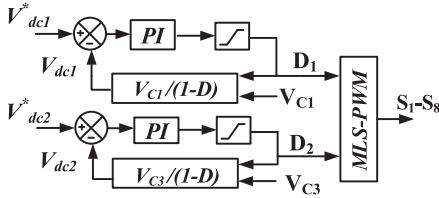

Fig. 6. Closed-loop DC-link voltage control for the proposed DqZS-7LI.

expressed as

$$x = \frac{4\sqrt{2}}{3\pi} \frac{V_{in1}}{V_{OUT}} \frac{T^2}{(16\pi^2 L_1 C_2 - T^2)} \quad (12)$$

Similarly, the low frequency voltage across the capacitor 'C<sub>1</sub>' is given by

$$v_{C1} \sim = \frac{4\sqrt{2}}{3\pi} \frac{k(P_{OUT})}{V_{OUT}} \sin\left(\frac{4\pi t}{T} - \frac{\pi}{2}\right) \cdot \frac{x_{L2} \cdot x_{C1}}{x_{L2} + x_{C1}} \quad (13)$$

From (13) the low frequency voltage ripple 'y' across the capacitor 'C<sub>1</sub>' is expressed as:

$$y = \frac{4\sqrt{2}}{3\pi} \frac{k(P_{OUT}) \cdot (D)}{V_{OUT} \cdot (1 - 2D) V_{in1}} \frac{4\pi T L_2}{(16\pi^2 L_2 C_1 - T^2)} \quad (14)$$

Solving the (12) and (14) and considering L<sub>1</sub> = L<sub>2</sub> and C<sub>1</sub> = C<sub>2</sub> the inductor and capacitor values of qZS-1 are obtained. A similar analysis is applied to the inductor and capacitor of qZS-2 to derive L<sub>3</sub>, L<sub>4</sub> and C<sub>3</sub>, C<sub>4</sub> parameters.

#### IV. STANDALONE AND GRID CONNECTED CONTROL STRATEGY OF DQZS-7LI

##### A. Stand-Alone Mode

It is well known that the output voltage of the quasi-z-source MLI is determined by the gain, which is the product of the boost factor 'B' and modulation index 'm' and obtained by the qZS network. In the standalone mode of operation, the modulation index (m) is held constant while controlling the output voltage. In such a situation, the gain of the power converter is solely determined by the boosting factor (B), which needs to be controlled to regulate the output voltage against the load and source disturbances.

In the proposed topology, a pulsating DC-link is produced across the qZS-1 and qZS-2 networks, when shoot-through (ST) is inserted in the shoot-through leg constituted by S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub> (Fig. 1). An indirect measurement of the DC-link voltage is required as the pulsating DC voltage cannot be measured directly or it can be used as a feedback signal.

In the present work, the DC-link voltage V<sub>dc1</sub> and V<sub>dc2</sub> of the 7-level inverter are estimated using shoot-through duty ratios (D<sub>1</sub>, D<sub>2</sub>) and the capacitor voltages (V<sub>c1</sub>, V<sub>c3</sub>) (8) & (9). Fig. 6 presents the closed-loop control scheme to control the DC-link voltages (V<sub>dc1</sub> and V<sub>dc2</sub>) of the proposed converter. The estimated DC-link voltages V<sub>dc1</sub>, V<sub>dc2</sub> are then compared with the reference voltages V<sub>dc1</sub><sup>\*</sup>, V<sub>dc2</sub><sup>\*</sup> respectively and the error generated is compensated by the PI controllers. The outputs of the PI controllers determine the required shoot-through duty ratios (D<sub>1</sub>, D<sub>2</sub>). These duty ratios are translated into the reference signals 'V<sub>sh1</sub> and V<sub>sh2</sub>' (Fig. 4), which are compared with the

Fig. 7. The grid control scheme for DqZS-7LI.

carrier signal to implement the shoot-through mode as discussed in Section III. Thus, the output voltage of the DqZS-7LI is regulated solely with the closed-loop feedback control of DC-link voltages (V<sub>dc1</sub>, V<sub>dc2</sub>).

##### B. Grid-Connected Mode

The grid-connected mode of operation requires the fulfillment of three objectives: (i) DC-link voltage regulation (ii) Injection of power into the grid at unity power factor (iii) Independent MPPT control of the two quasi-z-source networks. The two degrees of freedom offered by the qZS converter namely, the shoot-through duty ratio 'D' and the modulation index 'm' and are utilized to control these three objectives. Fig. 7 shows the control scheme for the closed-loop control of the proposed DqZS-7LI in the grid connection mode.

Perturb & Observe MPPT algorithm is employed to extract the maximum power from the PV panels. The currents (I<sub>PV1</sub>, I<sub>PV2</sub>) and voltages (V<sub>PV1</sub>, V<sub>PV2</sub>) of the PV panels are sensed and fed to the respective MPPT controllers. These controllers generate the required duty ratios (D<sub>1</sub> and D<sub>2</sub>), which are multiplied by R<sub>1</sub> and R<sub>2</sub> (1) to generate the shoot-through duty ratio (D) [33]. Further, the duty ratio is fed to the MLS-PWM to implement the ST mode with the help of the shoot-through leg.

As stated in the previous section, the total DC-link voltage is assessed by sensing the voltages across capacitors and the duty ratios of the qZS-1 and qZS-2 networks. The error between the reference DC-link voltage (V<sub>DC</sub><sup>\*</sup>) and the estimated value (V<sub>dc1</sub> + V<sub>dc2</sub>) is compensated by the PI controller that is present in the outer voltage loop. The control signal generated by the PI controller is multiplied with a unit-sine signal (sin ωt) to generate the reference value for the inner current loop (i<sub>g</sub><sup>\*</sup>) which is synchronized to the grid using a PLL. The reference grid current (i<sub>g</sub><sup>\*</sup>) is then compared to the actual grid current (i<sub>g</sub>) and the resultant error is compensated by a PR controller. The output of the PR controller then generates the required modulation signal v<sub>m</sub>, which is employed by the MLS-PWM control scheme to control the magnitude of the active power injected into the grid. [30].

#### V. REDUCTION OF LEAKAGE CURRENT

In transformerless PV systems, due to the absence of galvanic isolation, the leakage current flows through the path that is formed by the frame of the PV panel, the parasitic capacitance, and the common ground. The VDE0126-1-1 standard [23] specifies that the maximum leakage current is limited to 300mA. As mentioned earlier, quasi-z-source multilevel inverters boost the input voltage with the insertion of the shoot-through mode in the zero states of the switching period. Although PV sources

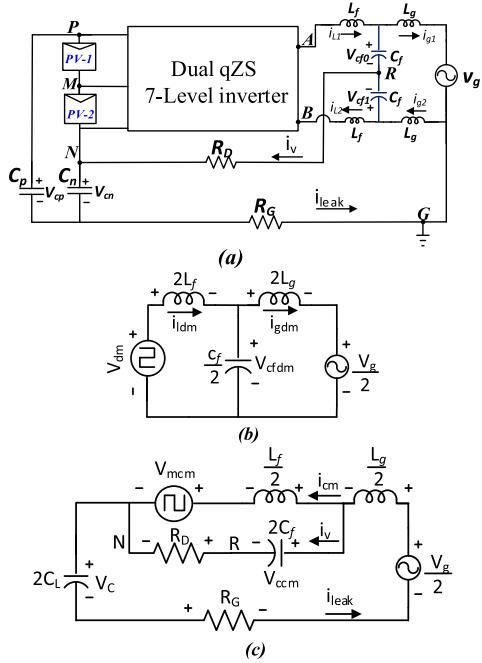

Fig. 8. (a) DqZS-7LI with leakage ground current path (b) Equivalent circuit of the differential-mode model (c) Equivalent circuit of the common-mode model.

are isolated from the grid during the zero-states (Fig. 2(d) and (e)), the addition of the shoot-through state introduces high-frequency transitions in the voltage impressed across the parasitic capacitor. These high-frequency transitions generate the leakage current, which flows from the PV source to the ground. Thus, it stands to reason that maintenance of a constant voltage across the parasitic capacitance eliminates the leakage current. Though it is generally desirable to eliminate the leakage current, it is not possible in qZS-based multilevel inverters owing to the insertion of the shoot-through in the zero-states. In such a scenario, the leakage current is reduced by reducing the magnitude of high-frequency transitions in the voltage, which is impressed across the parasitic capacitor. It is well known that the magnitude of these high-frequency transitions is determined by the common-mode voltage (CMV), which is defined as follows:

$$V_{cm} = \frac{V_{AO} + V_{BO}}{2} \quad (15)$$

As shown in Fig. 1 the qZS-2 network is connected with a reversed orientation compared to the qZS-1 network (Fig. 1). This facilitates the inclusion of inductor \$L\_3\$ and the capacitor \$C\_4\$ between inverter negative terminal 'O' and negative terminal of PV panels 'N' throughout the shoot-through (ST) as well as the non-shoot-through (NST) states. Hence, the effective CMV (\$V\_{mcm}\$) is represented as:

$$V_{mcm} = V_{cm} + V_{L3} - V_{C4} \quad (16)$$

Furthermore, an LCL filter is connected across the inverter output terminals (AB), as shown in Fig. 8(a), to achieve the dual objectives of (i) reducing higher-order current harmonic components in the leakage current induced by the effective CMV (\$V\_{mcm}\$) and (ii) filtering the output voltage of the inverter. To damp out the oscillations in the leakage current, a damping resistor (\$R\_D\$) is connected between the midpoint of the filter

capacitor and the negative terminal of the PV source (N) as shown in Fig. 8(a). In Fig. 8(a), \$C\_p\$ and \$C\_n\$ respectively represent the parasitic capacitance formed between the PV cells and their metallic frame, while \$R\_G\$ represents the ground resistance [29].

The mathematical model of the system shown in Fig. 8(a) may be resolved into the differential-mode and the common-mode models.

The equations corresponding to the differential-mode model are given by:

$$2L_f \hat{i}_{ldm} = V_{dm} - V_{cf dm} \quad (17)$$

$$2L_g \hat{i}_{gdm} = V_{cf dm} - V_g \quad (18)$$

$$\frac{C_f}{2} \hat{V}_{cf dm} = i_{ldm} - i_{gdm} \quad (19)$$

where the symbols \$i\_{ldm}\$, \$i\_{gdm}\$, \$V\_{dm}\$ and \$V\_{cf dm}\$ respectively denote the differential-mode inverter current (\$i\_{l1} + i\_{l2}/2\$), differential-mode grid current (\$i\_{g1} + i\_{g2}/2\$), differential-mode inverter voltage (\$V\_{AN} - V\_{BN}\$) and the differential-mode filter voltage (\$V\_{cf0} + V\_{cf1}\$). A pictorial representation of (17)–(19) results in the differential-mode equivalent circuit presented in Fig. 8(b).

On the other hand, the equations corresponding to the common-mode model are given by:

$$\frac{L_f}{2} \hat{i}_{lcm} = \frac{V_g}{2} - i_{leak} R_G - V_c - V_{mcm} - \frac{L_g}{2} \hat{i}_{leak} \quad (20)$$

$$\frac{L_f}{2} \hat{i}_{lcm} = V_{mcm} - V_{cf cm} + i_v R_D \quad (21)$$

$$2C_L \hat{V}_c = i_{leak} \quad (22)$$

$$2C_f \hat{V}_{cf cm} = i_{leak} - i_{lcm} \quad (23)$$

where the symbols \$i\_{lcm}\$ and \$V\_{cf cm}\$ respectively denote the common-mode inverter current (\$i\_{l2} - i\_{l1}\$) and the common-mode voltage of the filter (\$V\_{cf0} - V\_{cf1}/2\$).

A pictorial representation of (20)–(23) results in the common-mode equivalent circuit presented in Fig. 8(c). In this analysis, it is assumed that both PV parasitic capacitors have the same value of capacitance (i.e., \$C\_p = C\_n = C\_L\$).

From Fig. 8(c), it may be noted that the leakage current (\$i\_{leak}\$) is split into two components \$i\_{lcm}\$ and \$i\_v\$ (the high-frequency current flowing through the midpoint of capacitors 'R' and the 'N' terminal, Fig. 8(a)). This mid-point connection creates an alternate path to the current produced by the high-frequency voltage transitions in \$V\_{mcm}\$. This branch bypasses higher-order components of leakage current (on account of the presence of the capacitor \$2C\_f\$) and allows only lower-order components of currents to flow through the ground path. From this analysis, it is evident that the LCL filter reduces the leakage current significantly.

## VI. SIMULATION RESULTS

MATLAB-Simulink is utilized to validate the proposed single-phase DqZS-7LI. Fig. 9 presents the grid-connected operation of the proposed power converter with time-varying insolation for the PV sources. The following three cases are

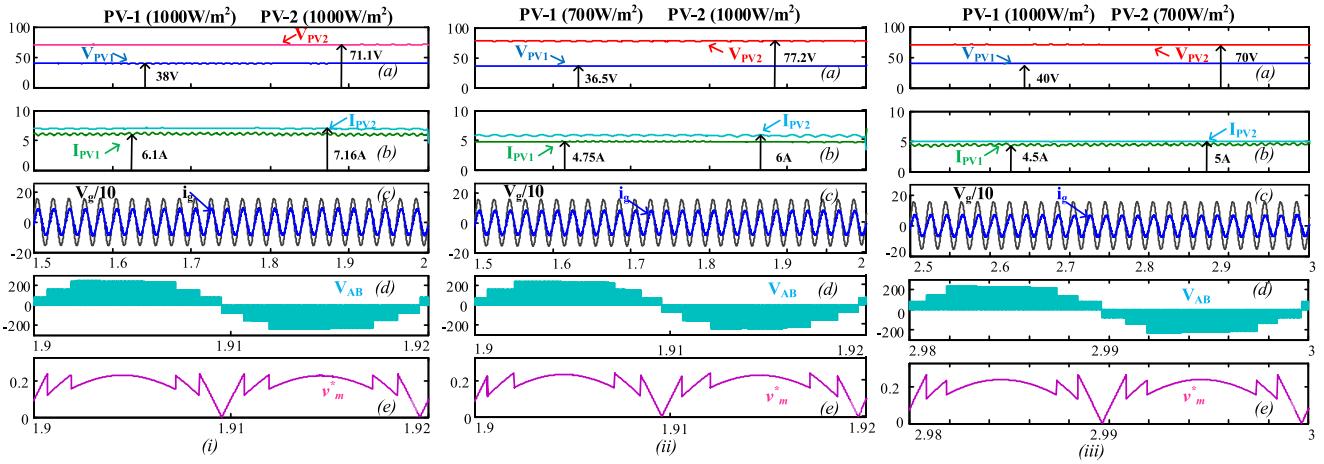

Fig. 9. Simulation results of grid control of the power converter for (i) PV-1 = PV-2 = 1000W/m<sup>2</sup> (ii) PV-1 = 700 W/m<sup>2</sup>, PV-2 = 1000W/m<sup>2</sup> (iii) PV-1 = 1000 W/m<sup>2</sup>, PV-2 = 700W/m<sup>2</sup>. The subplots give the waveforms of : (a) PV voltages ( $V_{PV1}$ ,  $V_{PV2}$ ) (b) PV currents ( $I_{PV1}$ ,  $I_{PV2}$ ) (c) Grid voltage ( $V_g$ ) and currents (d) Output voltage ( $V_{AB}$ ) (e) Modified modulation index ( $v_m^*$ ) voltage.

simulated to study the behavior of MPPT and the grid current control for the changes in insolation levels: (i) both PV-1 and PV-2 operate at 1000W/m<sup>2</sup> (ii) PV-1 operates at 700 W/m<sup>2</sup> and PV-2 operates at 1000 W/m<sup>2</sup> (iii) PV-1 operate at 1000 W/m<sup>2</sup> and PV-2 operate at 700 W/m<sup>2</sup>. A solar panel of open-circuit voltage 21.05V and a short circuit current of 3.74A is considered for simulation. Series and parallel combinations of the solar panels are used to form PV-1 ( $V_{oc1} = 42.1$ ,  $I_{sc1} = 7.48$ ) and PV-2 ( $V_{oc2} = 84.2$ ,  $I_{sc2} = 7.48$ ) sources. In Fig. 9. subplots (a) and (b) presents the PV voltages ( $V_{PV1}$ ,  $V_{PV2}$ ) and PV currents ( $I_{PV1}$ ,  $I_{PV2}$ ) during changes in the insolation of PV sources with a constant temperature. The maximum power point control tracks the power by adjusting the shoot-through duty ratios ( $D_1$  and  $D_2$ , Fig. 7) to obtain the maximum power from the PV sources. Further, these shoot-through duty ratios are multiplied with the multiplication factors  $R_1$  and  $R_2$  to account for the asymmetry of the PV voltages. The resultant shoot-through duty ratio 'D' is fed to MLSPWM to generate shoot-through in the qZS network. It may be noted that in case I, the maximum voltage and the maximum current generated by the sources PV-1 and PV-2 (Fig. 1) at 1000W/m<sup>2</sup> are (38V, 6.1A) and (71.1, 7.16A) respectively.

In case II, as the source PV-1 operates at an insolation level of 700 W/m<sup>2</sup>, the maximum currents of PV-1 and PV-2 are reduced to 4.75A and 6A respectively by the MPPT algorithm by re-adjusting the shoot-through duty ratio 'D'. In case III, while the source PV-2 operates at a maximum voltage of 70V and a reduced peak current of 5A (due to the lower insolation level of 700 W/m<sup>2</sup>), the source PV-1 operates at a non-MPPT point at (40V, 4.5A) to facilitate the 7-level operation. These results clearly show that the MPPT control (in Fig. 7) tracks the changes in insolation with effective control of the shoot-through duty ratio. The subplot (c) in Fig. 9 presents the grid voltage and grid current in all three cases of operation. It may be observed that a sinusoidal current of varying magnitude, which depends on the level of insolation, is injected into the grid at UPF. This shows the effective control of modulation index 'm' by the current controller shown in Fig. (7). The subplots (d) and (e) present the output voltage ( $V_{AB}$ ) and the modified modulation wave ( $v_m^*$ )

Fig. 10. Hardware prototype of the power converter.

of the proposed power converter (Fig. 9). Both the modulation wave ( $v_m^*$ ) and phase voltage are modified based on the voltage asymmetry of the PV sources. The change in the modulation signal ( $v_m^*$ ) can be observed by comparing the subplots (e) of case-I, II, and III.

## VII. EXPERIMENTAL RESULTS

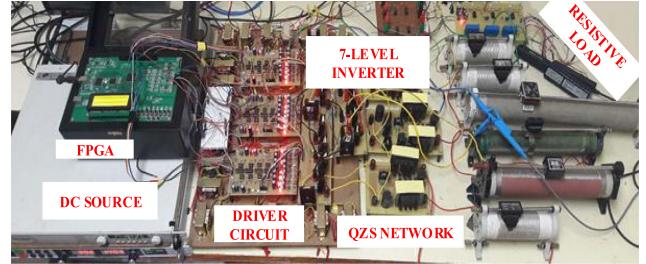

A low-scale hardware prototype of the proposed DqZS-7LI is fabricated to verify the MATLAB-Simulink results. Fig. 10 shows the fabricated hardware prototype.

To emulate the PV source two programmable DC power supplies with CC-CV characteristics are employed. The PWM scheme is implemented with a Spartan-6 FPGA board, which outputs gating pulses which are employed to drive the switches  $S_1$ - $S_8$  (power MOSFETs). A Yokogawa DL850 power oscilloscope is utilized to capture the experimental waveforms. Table II presents the details of the component and the specifications of the hardware prototype.

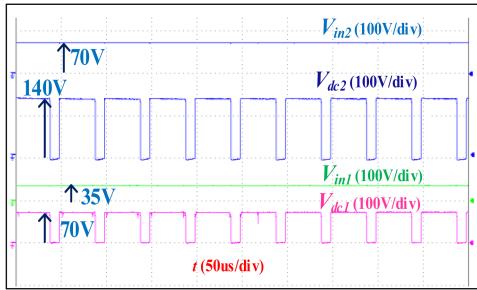

Fig. 11 demonstrates the applied input voltages ( $V_{in1}$ ,  $V_{in2}$ ) and boosted DC-link voltages ( $V_{dc1}$ ,  $V_{dc2}$ ) of the 7-level inverter. As shown in the figure the input voltages of 35 V ( $V_{in1}$ ) and 70V ( $V_{in2}$ ) are input to the top and bottom qZS networks respectively. As stated in the earlier sections, the proposed converter utilizes the dual-quasi-Z source networks to achieve the required voltage boosting. In the present experimental studies, a shoot-through duty ratio (D) of 0.25 to achieve a boosting factor of 2 (10). A modulation index (m) of 0.75 is chosen to obtain the

TABLE II

HARDWARE PROTOTYPE SPECIFICATIONS

| Parameters                   | Values               |

|------------------------------|----------------------|

| Input DC voltage( $V_{DC}$ ) | 105V                 |

| Total boosted voltage        | 210V                 |

| output voltage               | 110V (RMS)-50Hz      |

| Switching-frequency(fs)      | 20kHz                |

| Modulation-Index (m)         | 0.75                 |

| Inductors                    | EE65CORE, 3-mH       |

| Capacitors (Electrolytic)    | 1400 $\mu$ F,300V    |

| Ultra-Fast rectifier diode   | MUR1560CT            |

| Parasitic capacitor $C_p$    | 100nF                |

| $R_d, L_f, C_f, L_g$         | 1ohm,1mH, 6uf, 2.5mH |

| Power                        | 300W                 |

Fig. 11. Experimental results of DC-input voltages ( $V_{in1}$ ,  $V_{in2}$ ) and DC-link voltages ( $V_{dc1}$ ,  $V_{dc2}$ ) of DqZS-7LI.

Fig. 12. Experimental results of the DC input voltage ( $V_{in2}$ ), DC-link voltage ( $V_{dc2}$ ) and inductor current ( $i_{L4}$ ) and capacitor voltages ( $V_{c3}$ ,  $V_{c4}$ ) of the qZS-1 network.

required output voltage (110 V). From Fig. 11 it may be observed that the input voltages are boosted to 70 and 140V as indicated by the traces of  $V_{dc1}$  and  $V_{dc2}$ . It may also be noted that the waveforms of the DC-link voltages are typically pulsating, as they drop to a value of zero whenever a shoot-through mode is inserted.

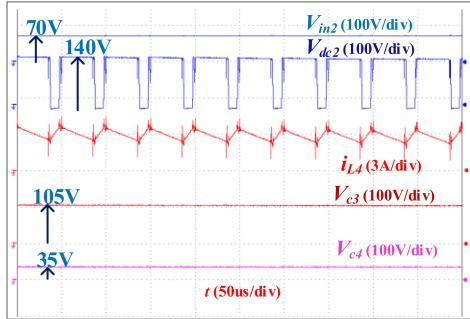

The experimental waveforms of inductor current ( $i_{L4}$ ) and the capacitor voltages ( $V_{c3}$ ) and ( $V_{c4}$ ) of the qZS-2 are shown in Fig. 12. For a shoot-through (ST) duty ratio (D) of 0.25, the input voltage (top trace) of 70V is boosted to 140V DC-link (second trace). From the figure it is evident that the boosted DC-link voltage of 140V is distributed across the capacitors  $C_3$  and  $C_4$  in the ratio of (1-D): (D). Fig. 12 also shows that the voltages across the capacitors ( $C_3$ ,  $C_4$ ) attain steady-state values of 105 and 35V respectively. It may be observed that whenever the DC-link voltage drops to a value of zero (during the ST time period), the inductor current ( $i_{L4}$ ) (third trace) increases linearly.

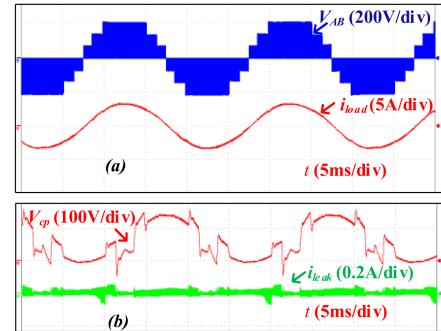

Fig. 13. Experimental results of (a) Output voltage waveform ( $V_{AB}$ ), Load voltage ( $i_{Load}$ ) (b) Parasitic capacitor voltage ( $V_{cp}$ ) and Leakage current ( $i_{leak}$ ) of DqZS-7LI.

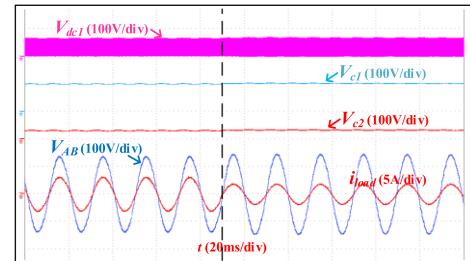

Fig. 14. Experimental results of DC-link voltage ( $V_{dc1}$ ), capacitor voltages ( $V_{c1}$ ,  $V_{c2}$ ), output voltage ( $V_{AB}$ ), and the load current ( $i_{load}$ ).

During the non-shoot-through time period, the inductor current decreases linearly.

Fig. 13(a) presents the output voltage and the load current of the proposed DqZS-7LI in the stand-alone mode of operation. The output voltage displays seven distinct levels between its negative and positive peak values (-210V to +210V). It may be noted that the phase voltage is a pulsating waveform that drops to a value of zero during the shoot-through period. The terminal voltage of the PV parasitic capacitor ( $V_{cp}$ ) and leakage current ( $i_{leak}$ ) are shown in Fig. 13(b). It may be observed that all high-frequency voltage transitions in the terminal voltage of the parasitic capacitor ( $V_{cp}$ ) are filtered out, resulting in a low leakage current ( $i_{leak}$ ) of 11.97mA (RMS). This leakage current, which flows between the PV source and the ground, is well within the limits of 300mA stipulated by VDE0126-1-1.

The dynamic performance of the power converter with closed-loop control in the standalone mode of operation is shown in Fig. 14. The control scheme shown in Fig. 6, which regulates the DC-link voltage, is employed for experimentation. The top three traces of this figure show the DC-link voltage of the top qZS ( $V_{dc1}$ ) and the capacitor voltages ( $V_{c1}$ ,  $V_{c2}$ ) of the corresponding qZS network. The bottom two traces show the output voltage ( $V_{AB}$ ) and the load current ( $i_{load}$ ) of the power converter. The load on the proposed converter is suddenly reduced (2.2 A to 1.4A) to evaluate its dynamic response against load disturbances. Fig. 14 reveals that neither the DC-link voltage ( $V_{dc1}$ ) nor the capacitor voltages (which add up to the DC-link voltage) show any noticeable change despite a sudden change in the load. It may also be noted that the output voltage ( $V_{AB}$ ) remains unperturbed as its magnitude is solely determined by the DC-link voltage in the standalone mode of operation.

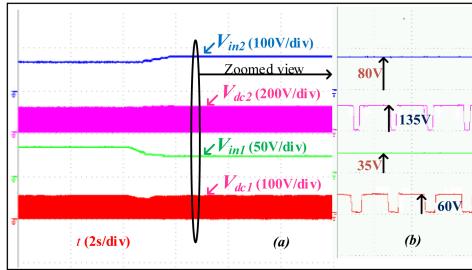

Fig. 15. Experimental results of (a) DC input voltages ( $V_{in1}$ ,  $V_{in2}$ ) and DC-link voltages waveforms of DqZS-7LI in the course of source disturbance (b) Zoomed view of the DC-link and DC input voltages of the DqZS-7LI.

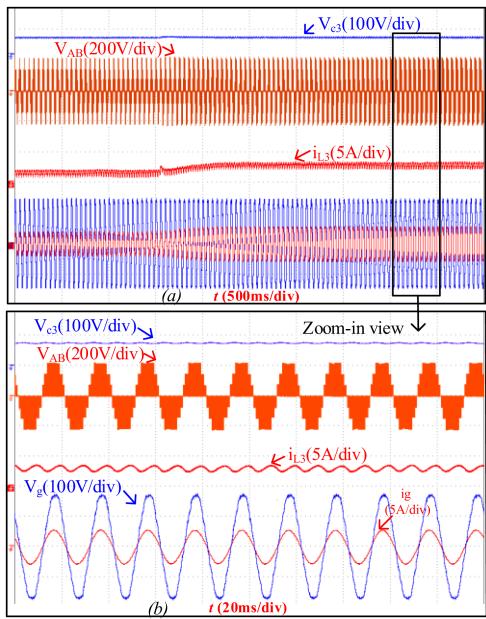

Fig. 16. Experimental results (a) Capacitor voltage ( $V_{c3}$ ), Phase voltage ( $V_{AB}$ ), Inductor current ( $i_{L3}$ ), Grid voltage ( $V_g$ ), and Grid current ( $i_g$ ) (b) Zoom-in view at 300W.

Further, the dynamic response of the power converter against the source disturbance is assessed. In this experiment (Fig. 15),  $V_{in1}$  and  $V_{in2}$ , which are initially maintained at 70V and 45V respectively, are suddenly changed to 80V and 35V. It may be noted that the second and the last traces of Fig. 15, which respectively show the two DC-link voltages, do not show any appreciable transients following the source disturbance.

Fig. 16 demonstrates the dynamic behavior of the proposed power converter while it feeds the grid. In this experiment, the active power of 135 W is fed into the grid initially. The shoot-through duty factor ( $D$ ), which is automatically adjusted by the controller (Fig. 7) based on the insolation, is then increased to inject higher power into the grid. This action momentarily disturbs the DC-link voltage, which is quickly regulated by the action of the outer loop PI controller. This increases the reference grid current, which determines the magnitude of the current which should be fed into the grid to maintain the DC-link voltage and the output voltage. The PR regulator injects the required current into the grid by adjusting the modulation index. Fig. 16 clearly shows the action of the controller, which automatically adjusts the modulation index. The adjustment of the modulation

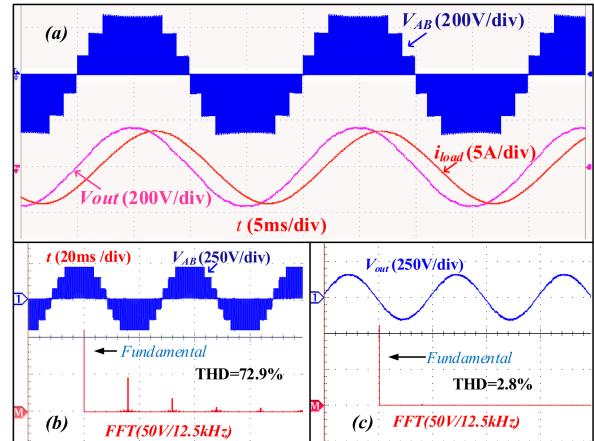

Fig. 17 (a) Output voltage ( $V_{AB}$ ), load voltage ( $V_{out}$ ), and load current ( $i_{load}$ ) for 0.8 lagging power factor (b) FFT of inverter output voltage ' $V_{AB}$ ' (c) FFT of output voltage ' $V_{out}$ '.

index results in (a) restoration of the DC-link voltage, which is evident from the first and second traces (b) increase in the source current  $i_{L3}$  (from 1.3 A to 3 A, third trace), and (c) increase in the power injected into the grid (fourth trace, wherein the grid current increases from 1.23 to 2.2 A, RMS). The zoomed picture of the aforementioned quantities and waveforms clearly shows the power injection into the grid at UPF.

Fig. 17(a) demonstrates the reactive power capability of the power converter. The power converter is tested for a 0.8 lagging ( $R = 40\Omega$ ,  $L = 95\text{mH}$ ) power factor. From Fig. 17(a) it may be noted that, load current ' $i_{load}$ ' is lagging w.r.t to load voltage ' $V_{out}$ ' which displays the reactive power capability of the proposed power converter.

### VIII. COMPARISON WITH THE PROPOSED DQZS-7LI

This section summarizes the merits of the proposed topology over the other impedance-source-based topologies, which have been reported so far in the literature. As qZS-based 7-level inverters available in the literature are scanty, a comparison with recent 5-level inverters is also considered. Table III presents the comparison of the number of components required, boost, and voltage stress across the devices in these topologies.

The proposed power converter (DqZS-7LI) requires a lesser number of capacitors, inductors, and switches when compared to the seven-level topologies presented in [14] and [18]. It may be noted that the proposed power converter requires an equal number of passive components and switches when compared to the 5-level topologies described in [15], [22]. Further, it is seen that the proposed power converter requires a lesser number of power diodes compared to all of these topologies. It may be noted that the voltage stress in [18] is lower when compared to all other topologies.

However, this advantage is overshadowed by the increased number of switches, diodes, and passive components needed in this topology. As seen from the Table, it may be noted that all these power converters have the same boost factors for a given shoot-through duty ratio ' $D$ ' except [21]. The voltage stresses on the capacitors, diodes, and switches in all these topologies are calculated on a per-unit basis, taking the output voltage (RMS)

TABLE III

COMPARISON OF THE PROPOSED POWER CONVERTER WITH QZS TOPOLOGIES

| Parameters                          | ZS- 7L[14]                        | qZS-NPC[15]                | qZS-CHB[18]                                               | MqZS[21]                        | qZS-5L [22]                     | Proposed                                                                                             |

|-------------------------------------|-----------------------------------|----------------------------|-----------------------------------------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------|

| Levels( $N_L$ )                     | 7                                 | 5                          | 7                                                         | 5                               | 5                               | 7                                                                                                    |

| Sources                             | 3                                 | 1                          | 3                                                         | 1                               | 1                               | 2                                                                                                    |

| Capacitors                          | 6                                 | 4                          | 6                                                         | 4                               | 4                               | 4                                                                                                    |

| Inductors                           | 6                                 | 4                          | 6                                                         | 2                               | 4                               | 4                                                                                                    |

| $N_{SW}$                            | 10                                | 8                          | 12                                                        | 8                               | 8                               | 8                                                                                                    |

| Diodes                              | 3                                 | 6                          | 3                                                         | 3                               | 4                               | 2                                                                                                    |

| Input current                       | discontinuous                     | continuous                 | continuous                                                | discontinuous                   | continuous                      | continuous                                                                                           |

| Boost                               | $1/(1-2D)$                        | $1/(1-2D)$                 | $1/(1-2D)$                                                | $2/(1-2D)$                      | $1/(1-2D)$                      | $1/(1-2D)$                                                                                           |

| Switch voltage stress               | $(x\sqrt{2})/3$<br>$(x/\sqrt{2})$ | $(x/\sqrt{2})$             | $(x\sqrt{2})/3$                                           | $(x/\sqrt{2})$                  | $(x/\sqrt{2})$                  | $x\sqrt{2}$ for $S_1, S_2$<br>$(x\sqrt{2})/3$ for $S_3, S_4$<br>$(x.2\sqrt{2})/3$ for $S_5$ to $S_8$ |

| Capacitor voltage stress            | $\sqrt{2}/3$                      | $1/\sqrt{2}$ for $C_1$     | $\sqrt{2}/3$ for $C_1$                                    | $1/\sqrt{2}$ for $C_1$          | $1/\sqrt{2}$ for $C_1, C_3$     | $\sqrt{2}/3$ for $C_1$<br>$(x.D.\sqrt{2})/3$ for $C_2$                                               |

|                                     |                                   | $(x.D)/\sqrt{2}$ for $C_2$ | $(x.D.\sqrt{2})/3$ for $C_2$                              | $(x.D)/\sqrt{2}$ for $C_2, C_4$ | $(x.D)/\sqrt{2}$ for $C_2, C_4$ | $(2\sqrt{2})/3$ for $C_3$<br>$(x.D.2\sqrt{2})/3$ for $C_4$                                           |

| Diode voltage stress                | $(x\sqrt{2})/3$                   | $(x/\sqrt{2})$             | $(x\sqrt{2})/3$                                           | $(x/\sqrt{2})$                  | $(x/\sqrt{2})$                  | $(x\sqrt{2})/3$ for $D_1$<br>$(x.2\sqrt{2})/3$ for $D_2$                                             |

| TSV/ $N_L$                          | 1                                 | 1.4                        | 0.71                                                      | 1.5                             | 1.2                             | 1                                                                                                    |

| Voltage THD                         | 24.3%                             | 76.4%                      | 29.3%                                                     | 38.2%                           | 74.2%                           | 72.9%                                                                                                |

| $N_{SW}^*$ cost of high side driver | $10*263=$<br>Rs.2630/-            | $8*263=$ Rs.2104/-         | $6*263=$ Rs.1578/-<br>$6*117=$ Rs.702/-<br>Total = 2280/- | $8*263=$ Rs.2104/-              | $8*263=$ Rs.2104/-              | $8*263=$ Rs.2104/-                                                                                   |

\* $x=1(1-D)$  where D is shoot-through duty ratio; cost of high side driver(1EDF5673K)=Rs.263 ; /cost of low side driver(1EDF5673K)=Rs.117.

value as the base value. As the numbers of diodes, switches, and the voltage levels of the compared topologies are unequal, the Total Standing Voltage (TSV) (the sum of blocking voltages of all the switches and diodes w.r.t the peak voltage value) per number of voltage levels ( $N_L$ ) is calculated [27]. It may be noted that the proposed power converter registers a lower (TSV/  $N_L$ ) ratio when compared to the topologies [14], [15], [21], and [22].

The proposed power converter has higher voltage THD when compared to [14], [18], and [21] as the zero-level is inserted in each level of operation to boost the input voltage, achieve 7-level operation, and minimize the leakage current. However, the inverter output voltage is filtered by the LCL filter to provide a sinusoidal output voltage with a THD of 2.8% (as shown in Fig. 17(c)) to load/grid.

All the topologies compared in Table III except [18], requires high side drivers for multilevel operation. All the topologies, are evaluated for  $M = 0.75$ ,  $P_o = 1\text{kW}$ ,  $V_o$  (RMS) = 230V. The minimum available high side gate driver is rated for 600V, hence cost of the 600V high side gate driver is considered for all the topologies. As the number of switches is equal in the topologies presented in [15], [21], [22], and the proposed power converter, the cost (w.r.t high side driver) is also equal. Further, the proposed power converter incurs a lower cost (w.r.t to high side gate driver) when compared to topologies [14], as the number of switches is less. The power converter [18] has 6 low-side drivers, however, this advantage is offset by an equal number of high-side switches.

## IX. LOSS ANALYSIS FOR THE DQZS-7LI

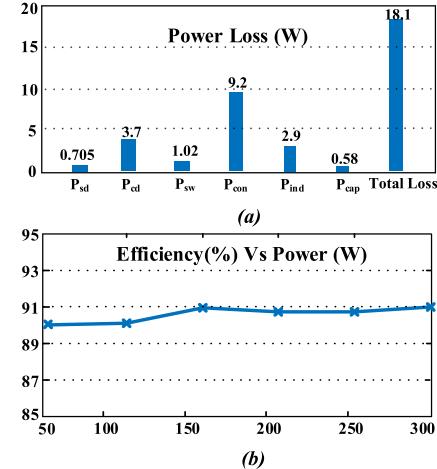

The efficiency of the proposed power converter is assessed by evaluating the following losses (i) switching loss ( $P_{sw}$ ) and conduction power losses ( $P_{con}$ ) occurring in the semiconductor switches  $S_1 - S_8$  (ii) switching loss ( $P_{sd}$ ) and conduction losses ( $P_{cd}$ ) in anti-parallel and quasi-z-source diodes (Fig. 1). To

Fig. 18. (a)Power Loss distribution in DqZS-7LI at 300W. (b)Experimental efficiency of the proposed DqZS-7LI.

this end, the Powersim (PSIM) software is employed, which possesses thermal models of several popular switching devices. These simulation studies are carried out by employing MOSFET IRFP460 and the power diode 150EBU04 to construct the power converter. Further, the ESR losses ( $P_{cap}$ ) in the capacitors and the conduction losses ( $P_{ind}$ ) in the inductors are calculated using the method described in [31]. The loss distribution for the proposed converter for 300W power output is shown in Fig. 18(a). From Fig. 18(a) it may be noted that simulated efficiency of the converter is around 94% at 300W output power. These losses have been evaluated assuming  $V_{in1} = 35V$ ,  $V_{in2} = 70V$ ,  $f_s = 20$  kHz,  $M = 0.75$ ,  $D = 0.25$ ,  $V_o$  (ph-RMS) = 110V,  $PF = 1$ .

Fig. 18(b) shows the experimental efficiency of the power converter for a step change of power ranging from 50W to 300W. To validate the efficiency of the power converter, a power analyser (UNI-T UT283A) is employed to measure the output

power. The input power is measured by a digital power meter (Yokogawa WT332E). From Fig. 18(b), it may be observed that the efficiency of the prototype reaches 91% at 300W output. It may be noticed that the efficiency achieved in experimental prototype is less in comparison with simulation studies as the ripple due to high frequency and  $2\omega$  component in the DC-link voltage and inductor current are neglected.

## X. CONCLUSION

This manuscript proposes a single-phase, single-stage dual-quasi-z-source 7-level inverter (DqZS-7LI), which is suitable for standalone as well as grid-connected PV applications. In this single-stage power converter, a modified LSPWM achieves the twin objectives of boosting the input PV voltages (using dual-qZS networks) and synthesizing the 7-level output voltage waveform (using the 7-level output inverter). Being a seamless structure, this power converter requires fewer semiconductor switching devices, compared to the other qZS and ZS-based seven-level topologies reported in earlier literature. Experimental studies are carried out to assess the steady-state and dynamic performances of the proposed power converter in the standalone mode as well as the grid-connected modes of operation. It is also shown that the leakage current is minimized by the combined effort of the modulation technique and the symmetrical LCL filter. Experimentation results demonstrate that the leakage current is well within the limits of the standards set by the VDE 0126-1-1. Based on the simulation and experimental results, it can be concluded that the proposed power converter could be effective for solar PV applications.

## REFERENCES

- 1] L. Wang, Q. H. Wu, and W. Tang, "Novel cascaded switched-diode multilevel inverter for renewable energy integration," *IEEE Trans. Energy Convers.*, vol. 32, no. 4, pp. 1574–1582, Dec. 2017.

- 2] M. Shen, A. Joseph, J. Wang, F. Z. Peng, and D. J. Adams, "Comparison of traditional inverters and Z-source inverter for fuel cell vehicles," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1453–1463, Jul. 2007.

- 3] N. Rana, M. Kumar, A. Ghosh, and S. Banerjee, "A novel interleaved tri-state boost converter with lower ripple and improved dynamic response," *IEEE Trans. Ind. Electron.*, vol. 65, no. 7, pp. 5456–5465, Jul. 2018.

- 4] F. Z. Peng, "Z-source inverter," *IEEE Trans. Ind. Appl.*, vol. 39, no. 2, pp. 504–510, Mar./Apr. 2003.

- 5] F. Z. Peng et al., "Z-source inverter for motor drives," *IEEE Trans. Power Electron.*, vol. 20, no. 4, pp. 857–863, Jul. 2005.

- 6] J. Anderson and F. Z. Peng, "A class of quasi-Z-source inverters," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting*, 2008, pp. 1–7.

- 7] A. Ahmed, M. S. Manoharan, and J.-H. Park, "An efficient single-sourced asymmetrical cascaded multilevel inverter with reduced leakage current suitable for single-stage PV systems," *IEEE Trans. Energy Convers.*, vol. 34, no. 1, pp. 211–220, Mar. 2019.

- 8] P. K. Chamarthi, V. Agarwal, M. S. E. Moursi, and V. Khadkikar, "A novel 1- $\varphi$  dual input nine-level inverter topology with generalized modulation technique," *IEEE Trans. Energy Convers.*, vol. 37, no. 3, pp. 1789–1802, Sep. 2022. doi: [10.1109/TEC.2022.3140232](https://doi.org/10.1109/TEC.2022.3140232).

- 9] S. Busquets-Monge, J. Rocabert, P. Rodriguez, S. Alepuz, and J. Bordonau, "Multilevel diode-clamped converter for photovoltaic generators with independent voltage control of each solar array," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2713–2723, Jul. 2008.

- 10] P. K. Kar, A. Priyadarshi, S. B. Karanki, and A. Ruderman, "Voltage and current THD minimization of a single-phase multilevel inverter with an arbitrary RL-load using a time-domain approach," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 6, pp. 6817–6827, Dec. 2021.

- 11] P. C. Loh, F. Blaabjerg, and C. P. Wong, "Comparative evaluation of pulselwidth modulation strategies for Z-source neutral-point-clamped inverter," *IEEE Trans. Power Electron.*, vol. 22, no. 3, pp. 1005–1013, May 2007.

- 12] P. C. Loh, F. Gao, F. Blaabjerg, S. Y. C. Feng, and K. N. J. Soon, "Pulselwidth-modulated Z-source neutral-point-clamped inverter," *IEEE Trans. Ind. Appl.*, vol. 43, no. 5, pp. 1295–1308, Sep./Oct. 2007.

- 13] P. C. Loh, S. W. Lim, F. Gao, and F. Blaabjerg, "Three-level Z-source inverters using a single LC impedance network," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 706–711, Mar. 2007.

- 14] M. R. Banaei, A. R. Dehghanzadeh, E. Salary, H. Khounjahan, and R. Alizadeh, "Z-source-based multilevel inverter with reduction of switches," *IET Power Electron.*, vol. 5, no. 3, pp. 385–392, May 2012.

- 15] O. Husev, C. Roncero-Clemente, E. Romero-Cadaval, D. Vinnikov, and S. Stepenko, "Single phase three-level neutral-point-clamped quasi-Z-source inverter," *IET Power Electron.*, vol. 8, no. 1, pp. 1–10, 2015.

- 16] D. Sun, B. Ge, F. Z. Peng, A. R. Haitham, D. Bi, and Y. Liu, "A new grid-connected PV system based on cascaded H-bridge quasi-Z-source inverter," in *Proc. IEEE Int. Symp. Ind. Electron.*, 2012, pp. 951–956.

- 17] Y. Zhou, L. Liu, and H. Li, "A high-performance photovoltaic module-integrated converter (MIC) based on cascaded quasi-Z-source inverters (qZSI) using eGaN FETs," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2727–2738, Jun. 2013.

- 18] B. Ge, Y. Liu, H. Abu-Rub, and F. Z. Peng, "State-of-charge balancing control for a battery-energy-stored quasi-Z-source cascaded-multilevel-inverter-based photovoltaic power system," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 2268–2279, Mar. 2018.

- 19] Y. Liu, H. Abu-Rub, B. Ge, and F. Z. Peng, "An effective control method for quasi-Z-source cascade multilevel three-phase grid-tie photovoltaic power system," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2014, pp. 1733–1737.

- 20] T.-T. Tran and M.-K. Nguyen, "Cascaded five-level quasi-switched-boost inverter for single-phase grid-connected system," *IET Power Electron.*, vol. 10, no. 14, pp. 1896–1903, Nov. 2017.

- 21] A.-V. Ho and T.-W. Chun, "Single-phase modified quasi-Z-source cascaded hybrid five-level inverter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 5125–5134, Jun. 2018.

- 22] C. K. Das, K. Annamalai, and S. V. Tirumala, "A quasi-Z-source-based five-level PV inverter with leakage current reduction," *IEEE Trans. Ind. Appl.*, vol. 58, no. 1, pp. 400–412, Jan./Feb. 2022.

- 23] F. Faraji, A. A. M. Birjandi, S. M. M. G, J. Zhang, B. Wangand, and X. Guo, "An improved multilevel inverter for single-phase transformerless PV system," *IEEE Trans. Energy Convers.*, vol. 36, no. 1, pp. 281–290, Mar. 2021.

- 24] N. Vosoughi, S. H. Hosseini, and M. Sabahi, "A new transformer-less five-level grid-tied inverter for photovoltaic applications," *IEEE Trans. Energy Convers.*, vol. 35, no. 1, pp. 106–118, Mar. 2020.

- 25] Y. Liu, B. Ge, X. Li, and Y. Xue, "Common mode voltage reduction of single-phase quasi-Z-source inverter-based photovoltaic system," *IEEE Access*, vol. 7, pp. 154572–154580, 2019.

- 26] W. Y. Choi and M. K. Yang, "Transformerless quasi-z-source inverter to reduce leakage current for single-phase grid-tied applications," *Electronics*, vol. 8, no. 3, Mar. 2019, Art. no. 312.

- 27] M. Meraj, S. Rahman, A. Iqbal, and L. Ben-Brahim, "Common mode voltage reduction in a single-phase quasi-Z-source inverter for transformerless grid-connected solar PV applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 2, pp. 1352–1363, Jun. 2019.

- 28] W. Li, Y. Gu, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Trans. Ind. Electron.*, vol. 62, no. 7, pp. 4537–4551, Jul. 2015.

- 29] G. Escobar, P. R. Martinez-Rodriguez, S. Iturriaga-Medina, J. C. Mayo-Maldonado, J. Lopez-Sarabia, and O. M. Micheloud-Vernackt, "Mitigation of leakage-ground currents in transformerless grid-tied inverters via virtual-ground connection," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 3, pp. 3111–3123, Sep. 2020.

- 30] Y. Yang, G. Liu, H. Liu, and W. Wang, "A single-phase grid synchronization method based on frequency locked loop for PV grid-connected inverter under weak grid," in *Proc. IEEE 11th World Congr. Intell. Control Automat.*, 2014, pp. 5453–5456.

- 31] D. Sun et al., "Modeling, impedance design, and efficiency analysis of quasi-Z source module in cascaded multilevel photovoltaic power system," *IEEE Trans. Ind. Electron.*, vol. 61, no. 11, pp. 6108–6117, Nov. 2014.

- 32] S. Majumdar, B. Mahato, and K. C. Jana, "Implementation of an optimum reduced components multicell multilevel inverter (MC-MLI) for lower standing voltage," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 2765–2775, Apr. 2020.

- 33] V. Sonti, S. Jain, and S. Bhattacharya, "Analysis of the modulation strategy for the minimization of the leakage current in the PV grid-connected cascaded multilevel inverter," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 1156–1169, Feb. 2017.