# Exploring Design of Physical Unclonable Functions (PUFs) for Robust Hardware-Assisted Security

*Submitted in partial fulfilment of the requirements*

*for the award of the degree of*

**Doctor of Philosophy**

by

**Podeti Raveendra**

(Roll No: 719068)

Under the supervision of

**Prof. Patri Sreehari Rao**

(Supervisor)

**Dr. P. Muralidhar**

(Co-Supervisor)

Department of Electronics & Communication Engineering

National Institute of Technology Warangal

Telangana, India - 506004

**2024**

---

Dedicated

To

Amma & Nanna,

Uma & Karthi

## Approval Sheet

This thesis entitled **Exploring Design of Physical Unclonable Functions (PUFs) for Robust Hardware-Assisted Security** by **Podeti Raveendra** is approved for the degree of **Doctor of Philosophy**.

### **Examiners**

---

#### **Research Supervisor**

**Prof. Patri Sreehari Rao**

Department of ECE,

NIT Warangal, India-506004

---

#### **Research Co-Supervisor**

**Dr. P. Muralidhar**

Department of ECE,

NIT Warangal, India-506004

---

#### **DSC Chairman**

**Prof. N. Bheema Rao**

Department of ECE,

NIT Warangal, India-506004

---

#### **Head of the Department**

**Prof. D. Vakula**

Department of ECE,

NIT Warangal, India-506004

Place:

Date:

## Declaration

This is to certify that the work presented in this thesis entitled **Exploring Design of Physical Unclonable Functions (PUFs) for Robust Hardware-Assisted Security** is a bonafied work done by me under the supervision of **Prof. Patri Sreehari Rao and Dr. P. Muralidhar** and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my own ideas and even considered others ideas which are adequately cited and further referenced the original sources. I understand that any violation of the above will cause disciplinary action by the institute and can also evoke panel action from the sources or from whom proper permission has not been taken when needed. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea or data or fact or source in my submission.

Place:

Date:

Podeti Raveendra

Research Scholar

Roll No.: 719068

# NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL, INDIA-506004

Department of Electronics and Communication Engineering

## CERTIFICATE

This is to certify that the thesis work entitled **Exploring Design of Physical Unclonable Functions (PUFs) for Robust Hardware-Assisted Security** is a bonafide record of work carried out by **Podeti Raveendra** submitted to the faculty of **Electronics and Communication Engineering** department, in partial fulfilment of the requirements for the award of the degree of **Doctor of Philosophy** in **Electronics and Communication Engineering, National Institute of Technology Warangal, India-506004**. The contributions embodied in this thesis have not been submitted to any other university or institute for the award of any degree.

Prof. Patri Sreehari Rao

Research Supervisor,

Department of ECE,

NIT Warangal, India-506004.

Dr. P. Muralidhar

Research Co-Supervisor

Department of ECE,

NIT Warangal, India-506004.

Place:

Date:

## Acknowledgements

First, I would like to express my deepest gratitude to the exceptional individuals Prof. Patri Sreehari Rao and Dr. Pullakandam Muralidhar, who supported and guided me throughout this transformative journey with promptness and care. I am profoundly grateful for the immeasurable contributions they made to my development.

I take this privilege to thank all my Doctoral Scrutiny Committee members Prof. D. Vakula (HoD), Prof. N. Bheema Rao (Chairman), Prof. C. B. Rama Rao (Retd.), Prof. J.V. Ramana Murthy (Dept. of Mathematics), and Dr. Ekta Goel for their detailed review, constructive suggestions, and excellent advice during the progress of this research work. I would also like to thank all the faculty of the Department of ECE who helped me during the course.

I would like to convey my sincere gratitude to Prof. Sree Rama Krishna (Former HoD of Velagapudi Ramakrishna Siddhartha Engineering College, Vijayawada), Dr. Sirigiri Chittibabu (Late), Prof. M. Padmaja, Prof. Jhansi Rani, Dr. Sk. Fayaz Ahamed, RV Hanumanth Prasad, Dr. K. Vara Prasad, A Ravi Raja, K.V Ratna Prabha, Dr. P.V. Satya Narayana, Dr. Ch. Naga Raghuram, Dr. A. Vijaya Shankar, Dr. P. Phani kumar, Dr. B.L. Sirisha, Dr. G. Hema Kumar, Dr. P.S. Suhasini, Dr. A. Anitha, and Dr.N.S. Murthy, who provided exceptional guidance and unwavering support throughout my teaching endeavours.

I want to express my heartfelt appreciation to My Gurus (Intermediate) Mr. Seshu, Mr. P. Srinivasa Rao, Mr.Devanandam, Mr.Dinesh, Mr.Khan, Mr.Varaprasad, My Gurus (High school) Mr. A. Arun Kumar, Mr.Sharma, Mr.Kornel, Mr.Acharya, Mr.Vincent, Mr.Lurthiah, Mr.Baala swamy, Mr.Jnananandam, Mr.Balireddy, Mrs. Karuna, Mrs. Sandhya rani, Tuition: Mr.Ravikumar (Late), Mr. Haranath, and Mrs. Usha, who

engraved my knowledge and directed me in a positive way.

I am deeply indebted to Dr. S. Subbarao, Dr. D. Vijaya Kumar, Dr. G. Chakravarthy, Dr. BJ Rani Deepika, and Dr. Ch. Vijayadurga by making conversations vital in inspiring me to think outside the box and also treated me as one of their family members. I'm extremely grateful to thank my co-scholars M. Praveen, Ravi shankar, Kiran, Malalaiah, Yesudasu, Laxmikanth, Hari, Mahesh, Srinivas, My friends: Dr. Praveen naidu, Srikanth, Babu, and well-wishers for sharing their knowledge and spending valuable time with me.

I would like to express my deepest appreciation to Mixed Signal Design Lab warriors: Dr. K Krishna Reddy, Dr. Mudassir Mir Bashir, Dr. A. Suresh, Dr. Pavan Kumar sharma, Dr. Mushahhid Majeed, Dr. KVBV Rayudu, Dr. LAV Sanhith Rao, Nandini, D. Baba Fayaz, Ch. Jayaram, M. Fathima, MV Krishna Reddy, Suresh Nagula, E Koti Hanuman Reddy, Nagarani, K Kamalakar for their suggestions and support regarding technical discussions about circuits and tools. I would like to thank Dr. Karthik, Dr. Asish, Dr. Srikar, Dr. Sri Ram Tej, Dr. Siva Rama Krishna, Dr. Ahadith, Ganesh, and Dr. Rambabu for their valuable suggestions during my coursework, review presentations and thesis writing with their support.

I would like to convey my heartfelt gratitude to my childhood friends Hemaraju, and S.L. Suresh, who stood by my side and helped me morally, ethically, and financially. I would like to thank my friends Naga Mallikarjun, Dr. M. Vijaya kumar and Veerababu, who supported me financially in critical times. And also convey my heartfelt appreciation to my Intermediate friends Murali krishna (late), D. Venkateswara rao, and Dhanvi.

I want to express my deepest gratitude to my family who believe in my abilities and support. Your encouragement played an integral role in my accomplishments. I would also like to extend my heartfelt appreciation to my family: Pinni, Akka, Narendra, and Tinku.

Finally, I thank my nation India, for giving me the opportunity to carry out my research work at the National Institute of Technology Warangal. A special thanks to MHRD for its financial support.

# Abstract

Physical unclonable function (PUF) is a promising hardware that augments the security feature for Integrated Circuit (IC) identification and authentication. It is one of the reliable solutions to many security threats as it facilitates die-unique identifier features by increasing uncertainty and prediction. PUF technology, especially for compact IoT-enabled devices, makes use of inherent Process Variations (PVs) of ICs attained by chip manufacturers and transforms them into distinctive digital keys to offer a possible solution to security-related issues. Fascinatingly, Machine Learning (ML) is a relatively prominent and inexpensive method that is frequently employed to tackle PUFs. As a result of the PUF's instability due to environmental changes, additional circuits are now being explored to fix the threats that ensue.

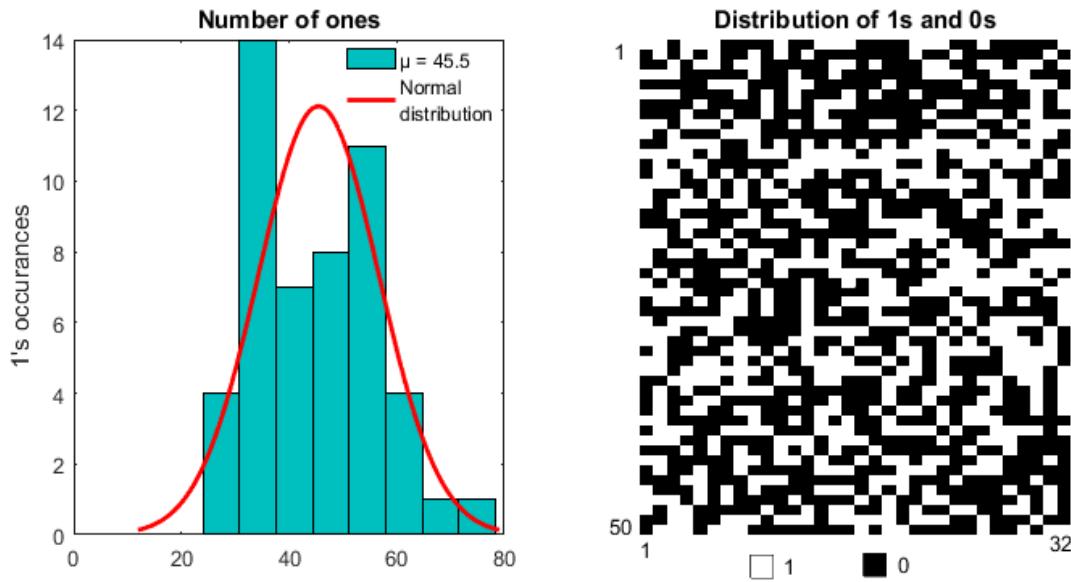

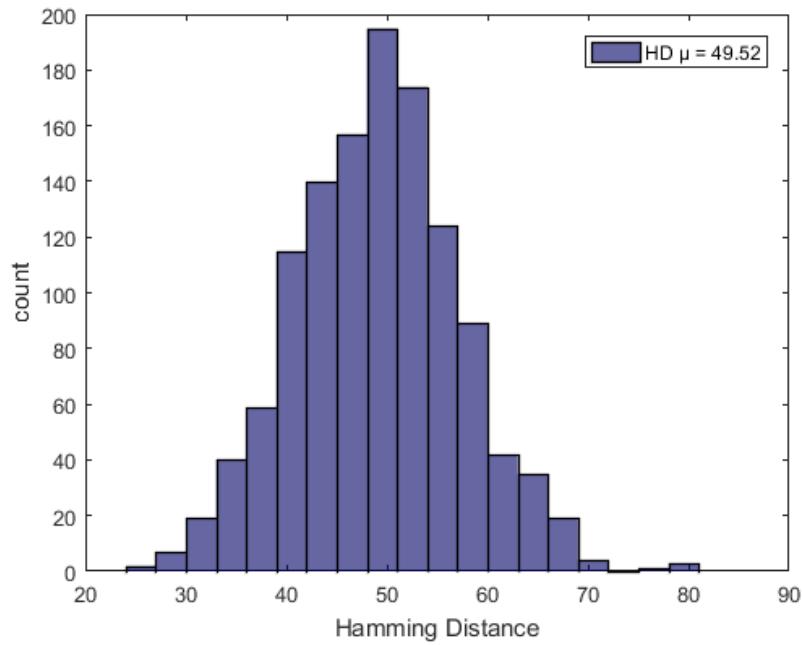

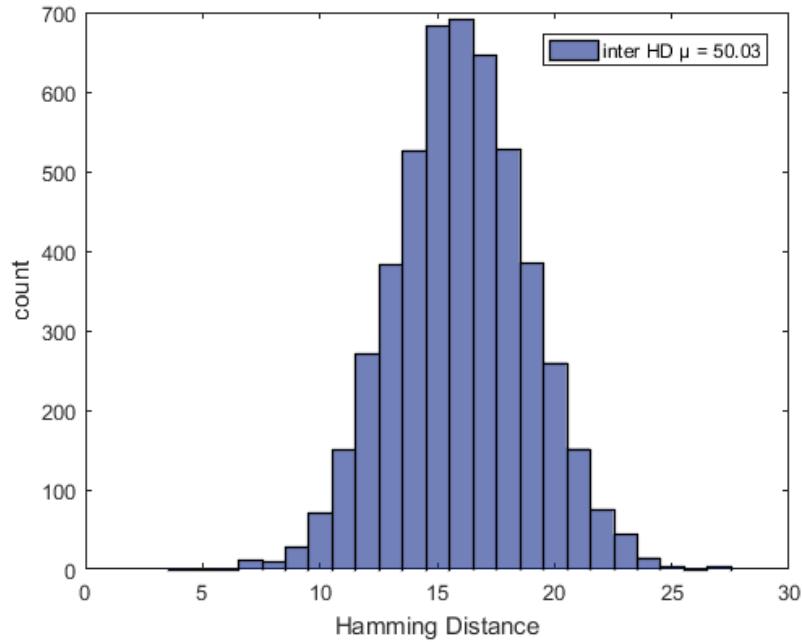

In this thesis, we discuss different facets of PUF design with a strong emphasis on the circuit details. From basic PUF designs presented by the researchers, the ultimate design challenges are identified, and prominent solutions are offered that should satisfy the PUF evaluation metrics before contrasting different PUF core implementations. Concerning the detailed literature, we proposed an XoR Feed Arbiter PUF (XFAPUF) that minimizes vulnerabilities by introducing more complexity in the arbitration process using a relatively smaller number of challenges against conventional Arbiter PUF (APUF). It offers better uniqueness and reliability than prior works as it achieves promising results, such as uniqueness of 50.03%, diffuseness of 49.52%, and worst-case reliability of 99.81% that ranges from 10°C to 80°C, with 10% fluctuations in supply voltage ( $V_{DD}$ ). In addition, an enhancement in reliability is achieved by a chaotic-based challenge generation mechanism introduced for feeding APUFs to increase the non-linearity in the arbitration process.

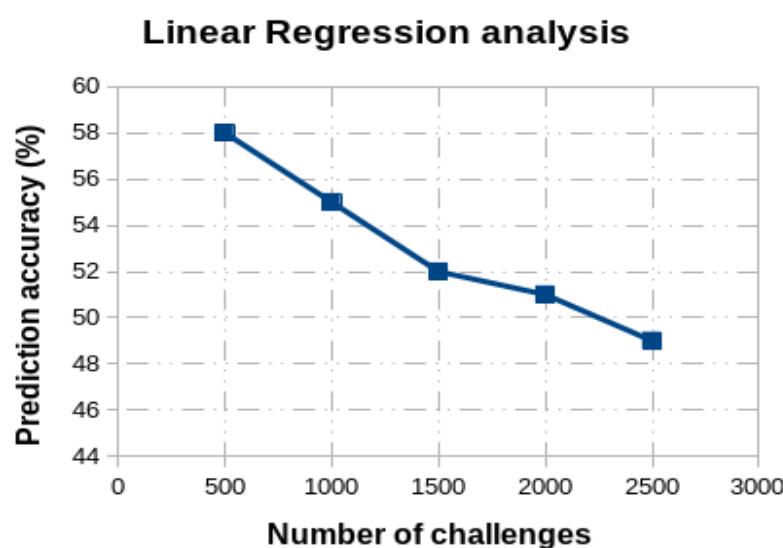

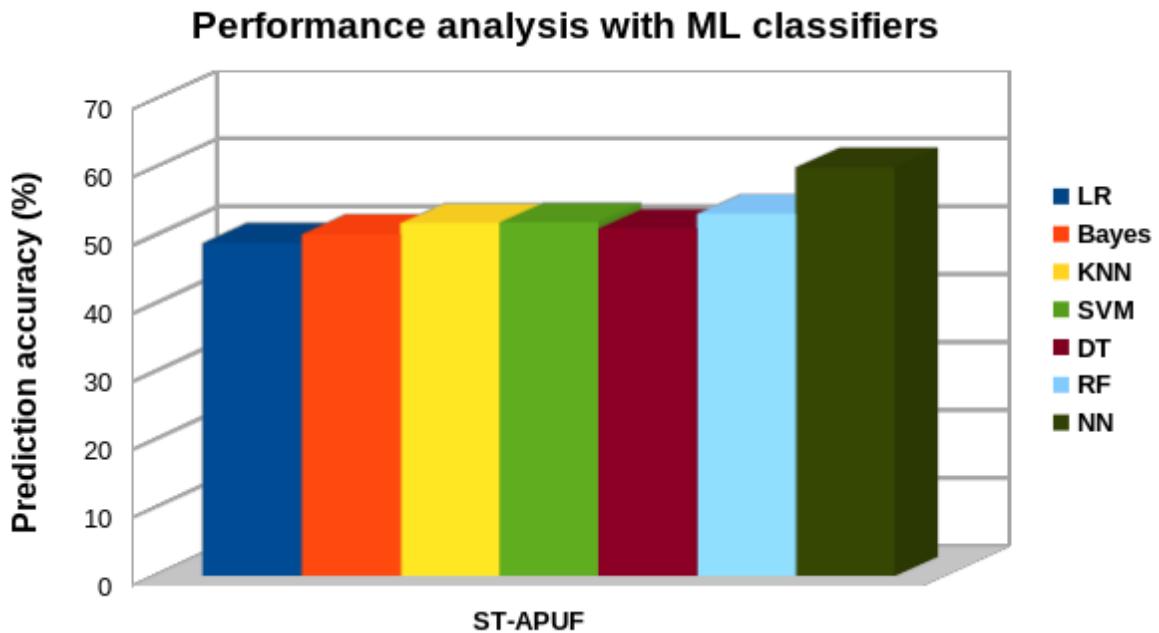

Subsequently, an automated challenge-feeding mechanism by Recursive Challenge

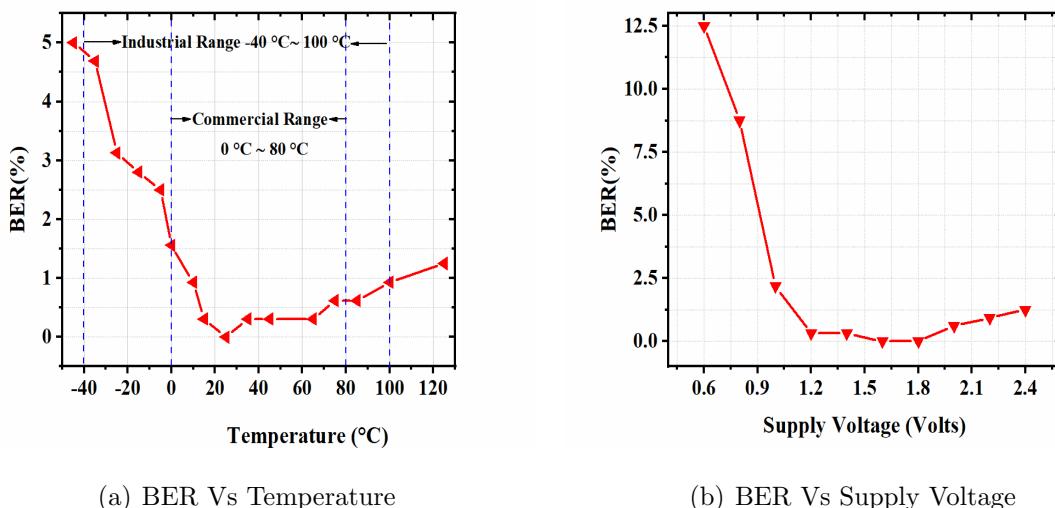

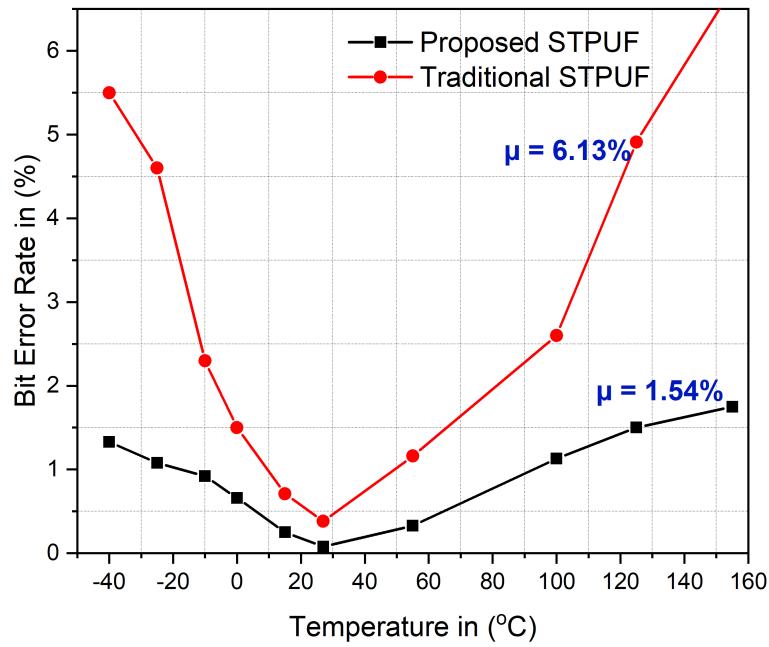

---

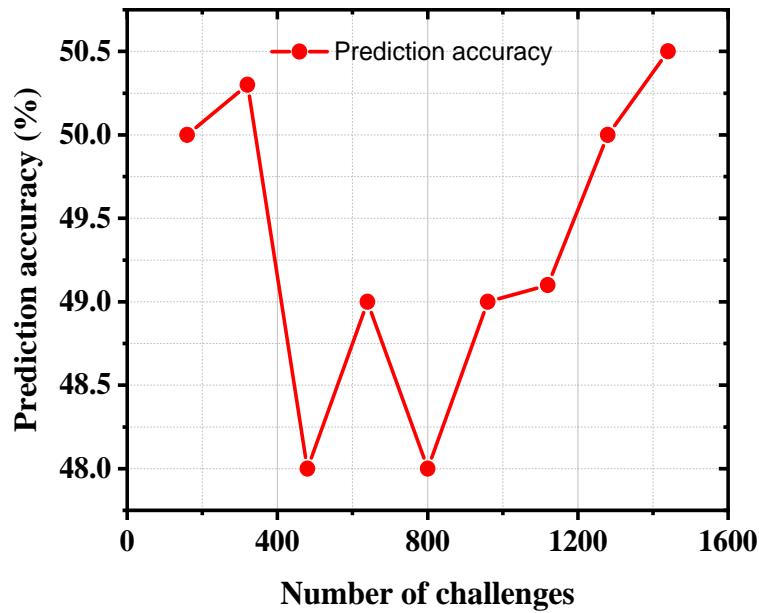

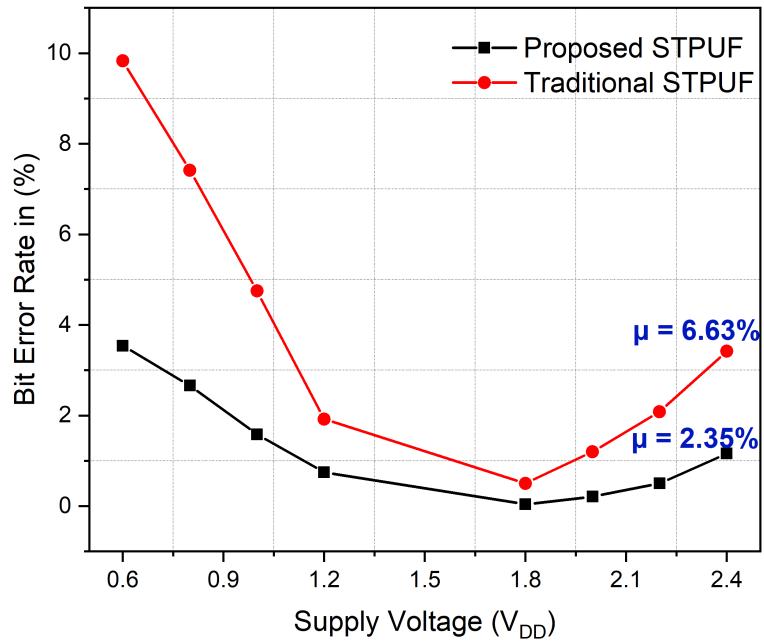

Feed Arbiter Physical Unclonable Function (RC-FAPUF) is proposed to generate unique, unpredictable, and reliable keys that are independent of the challenges that are generally fed by the user. The robustness of the keys is measured by an average reliability of 99.91% and also validated through a lower prediction accuracy of 48% and 52.7% with Linear Regression (LR), and ML classifiers respectively. Furthermore, to power up suitable IoT sub-systems or sensors, a Relaxation Oscillator PUF (ReOPUF) is designed to generate a 4.4MHz frequency along with key generation. The reliability of ReOPUF responses has been improved from 95.33% for the conventional Ring Oscillator (RO) PUF to 99.19%. Besides, a Schmitt-Trigger (ST) based APUF instance is introduced that uses PVs in Hysteresis Width (HW) to attain the non-linearity in the Challenge Response Pair (CRP) mechanism. Thereby, impersonation of the responses (keys) is complex perhaps various trials are performed to predict the keys. It offers reliability while achieving 0.15%, and 0.31% Bit Error Rate (BER) concerning the variations in temperature and  $V_{DD}$  respectively. Finally, the proposed PUF designs are implemented in UMC180nm CMOS technology that is suitable for prominent security assistance to IoT-enabled devices and is more resilient against ML attacks.

# Contents

|                                                 |             |

|-------------------------------------------------|-------------|

| <b>Declaration</b>                              | <b>iii</b>  |

| <b>Acknowledgements</b>                         | <b>v</b>    |

| <b>Abstract</b>                                 | <b>vii</b>  |

| <b>List of Figures</b>                          | <b>xvi</b>  |

| <b>List of Tables</b>                           | <b>xx</b>   |

| <b>List of Abbreviations</b>                    | <b>xxii</b> |

| <b>1 Introduction</b>                           | <b>1</b>    |

| 1.1 Internet of Things (IoT) . . . . .          | 2           |

| 1.2 IoT Cryptographic Primitives . . . . .      | 3           |

| 1.2.1 Symmetric Key cryptography . . . . .      | 3           |

| 1.2.2 Asymmetric Key cryptography . . . . .     | 4           |

| 1.2.3 Hash functions . . . . .                  | 4           |

| 1.2.4 Random Number Generators (RNGs) . . . . . | 5           |

| 1.2.5 Lightweight cryptography . . . . .        | 6           |

| 1.2.6 Cryptographic Algorithms . . . . .        | 6           |

| 1.3 Process Variations (PVs) . . . . .          | 7           |

---

|          |                                                 |           |

|----------|-------------------------------------------------|-----------|

| 1.3.1    | Sources of variances in ICs . . . . .           | 9         |

| 1.3.1.1  | Layout and design variations . . . . .          | 10        |

| 1.3.1.2  | Thermal Variations . . . . .                    | 10        |

| 1.3.1.3  | Voltage and Bias Variations . . . . .           | 10        |

| 1.3.1.4  | Random Variations . . . . .                     | 10        |

| 1.3.1.5  | Aging and Wear . . . . .                        | 10        |

| 1.4      | Physical cryptographic primitives . . . . .     | 11        |

| 1.4.1    | Physical Unclonable Functions (PUFs) . . . . .  | 11        |

| 1.4.2    | Hardware Security Module (HSM) . . . . .        | 13        |

| 1.4.3    | True Random Number Generators (TRNGs) . . . . . | 13        |

| 1.4.4    | Side-channel analysis (SCA) . . . . .           | 14        |

| 1.5      | Motivation . . . . .                            | 16        |

| 1.6      | Problem Statement . . . . .                     | 17        |

| 1.7      | Research Objectives . . . . .                   | 18        |

| 1.8      | Thesis Contributions . . . . .                  | 18        |

| 1.9      | Thesis Organization . . . . .                   | 19        |

| <b>2</b> | <b>Physical Unclonable Functions (PUFs)</b>     | <b>21</b> |

| 2.1      | Concept of PUF in IoT device . . . . .          | 21        |

| 2.2      | Characteristics of PUFs . . . . .               | 23        |

| 2.2.1    | PUF quality metrics . . . . .                   | 24        |

| 2.2.1.1  | Uniformity (u) . . . . .                        | 24        |

| 2.2.1.2  | Diffuseness (D) . . . . .                       | 25        |

| 2.2.1.3  | Uniqueness (U) . . . . .                        | 25        |

| 2.2.1.4  | Reliability (R) . . . . .                       | 25        |

---

---

|         |                                         |    |

|---------|-----------------------------------------|----|

| 2.3     | Types of PUFs                           | 26 |

| 2.3.1   | Delay-based PUFs                        | 26 |

| 2.3.1.1 | Arbiter PUFs (APUFs)                    | 26 |

| 2.3.1.2 | Ring Oscillator PUFs (ROPUFs)           | 28 |

| 2.3.1.3 | Other delay-based PUFs                  | 29 |

| 2.3.2   | Memory-based PUFs                       | 30 |

| 2.3.2.1 | Static Random-Access Memory (SRAM) PUF  | 31 |

| 2.3.2.2 | Dynamic Random Access Memory (DRAM) PUF | 31 |

| 2.3.2.3 | Other Memory-based PUFs                 | 32 |

| 2.3.3   | Mixed-signal PUFs                       | 32 |

| 2.3.3.1 | Temperature stable PUF                  | 33 |

| 2.3.3.2 | Current Mirror Array (CMA) PUF          | 34 |

| 2.3.3.3 | Schmitt Trigger (ST) PUF                | 34 |

| 2.3.3.4 | Power management circuit based PUFs     | 35 |

| 2.3.3.5 | Other Mixed-signal PUFs                 | 37 |

| 2.3.4   | Strong and Weak PUFs                    | 38 |

| 2.3.4.1 | Strong PUFs                             | 39 |

| 2.3.4.2 | Weak PUFs                               | 40 |

| 2.4     | Attacks on PUFs                         | 41 |

| 2.4.1   | Invasive attacks                        | 41 |

| 2.4.1.1 | Semi-invasive attacks                   | 41 |

| 2.4.2   | Non-invasive attacks                    | 42 |

| 2.4.2.1 | Modeling attacks                        | 42 |

| 2.4.2.2 | Side-channel attacks                    | 43 |

---

|          |                                                              |           |

|----------|--------------------------------------------------------------|-----------|

| 2.5      | Summary                                                      | 44        |

| <b>3</b> | <b>XoR Feed Arbiter PUF (XFAPUF)</b>                         | <b>45</b> |

| 3.1      | Arbiter PUF                                                  | 46        |

| 3.2      | Implementation of XFAPUF                                     | 48        |

| 3.2.1    | Design considerations for XFAPUF                             | 48        |

| 3.2.2    | Feed Forward Stage (FFS)                                     | 48        |

| 3.2.3    | n-bit key generation                                         | 50        |

| 3.2.4    | Earlier Response Detection (ERD) circuit                     | 52        |

| 3.3      | Evaluation of XFAPUF                                         | 52        |

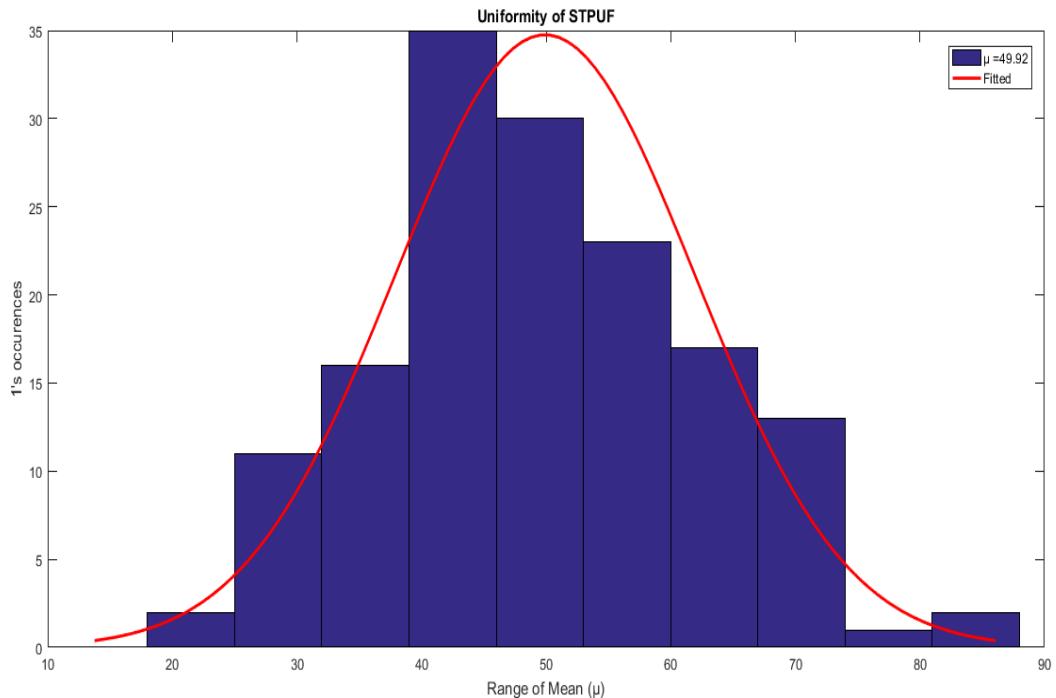

| 3.3.1    | Uniformity (u)                                               | 53        |

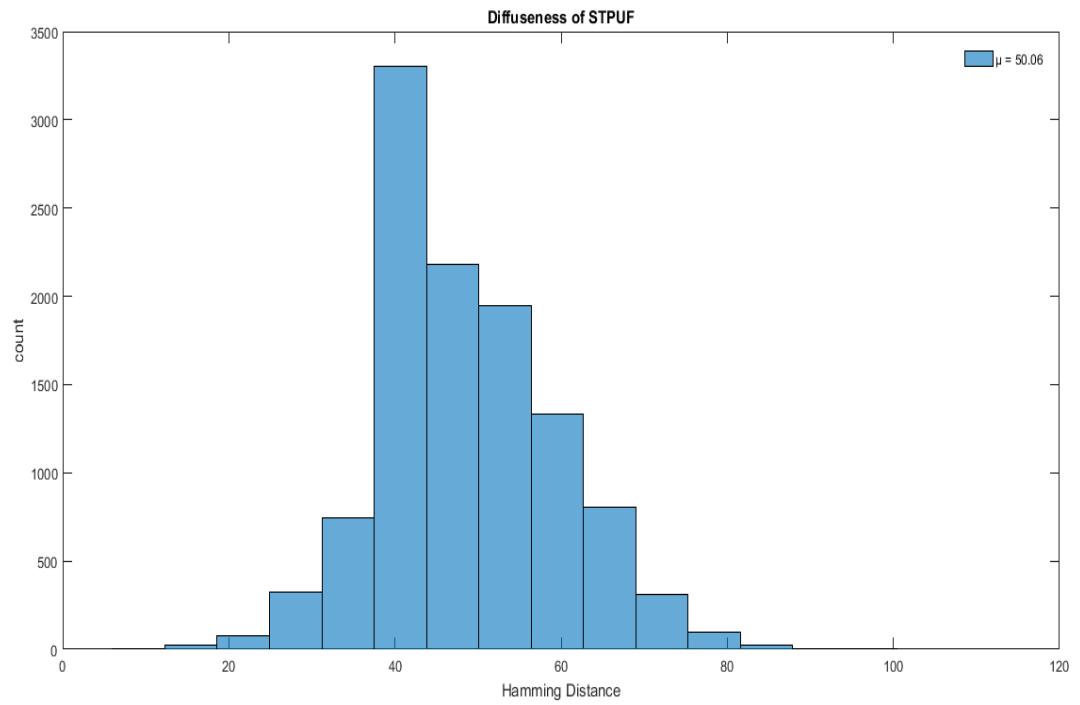

| 3.3.2    | Diffuseness (D)                                              | 53        |

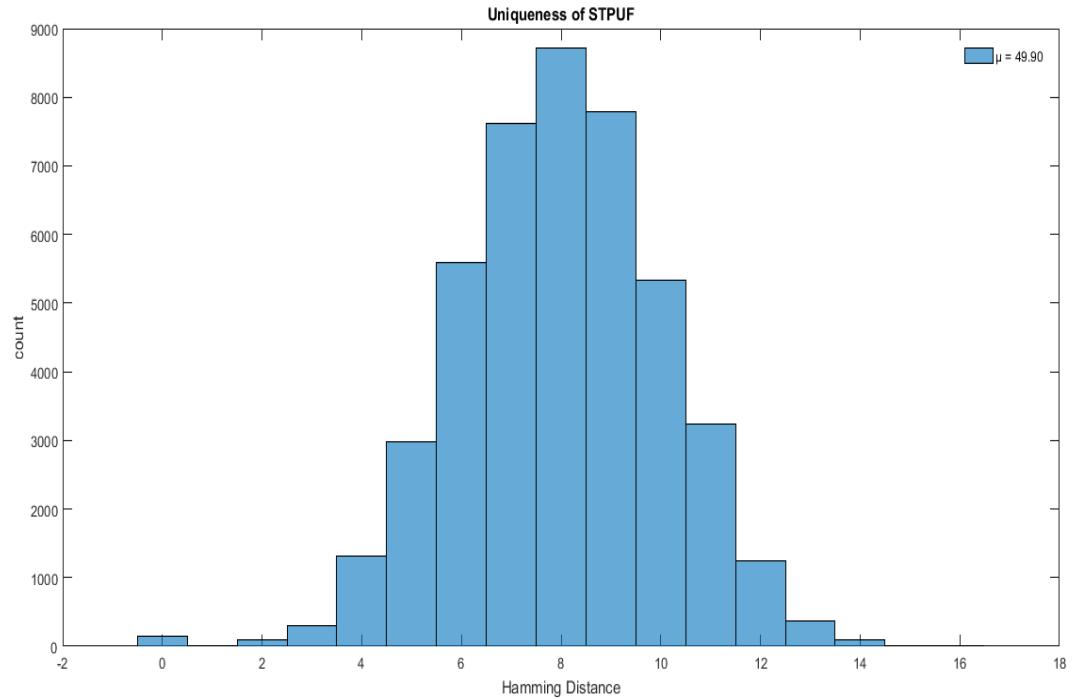

| 3.3.3    | Uniqueness (U)                                               | 53        |

| 3.3.4    | Reliability (R)                                              | 55        |

| 3.3.5    | Security evaluation                                          | 55        |

| 3.3.6    | Analysis and Comparison of XFAPUF                            | 56        |

| 3.3.7    | Performance evaluation                                       | 57        |

| 3.4      | Random Number Generators (RNGs)/Random Bit Generators (RBGs) | 58        |

| 3.4.1    | Chaotic RNGs                                                 | 59        |

| 3.5      | Chaotic-APUF                                                 | 59        |

| 3.5.1    | Design considerations for Chaotic-APUF                       | 60        |

| 3.5.2    | Implementation of Chaotic-APUF                               | 60        |

| 3.5.3    | Evaluation of Chaotic-APUF                                   | 62        |

| 3.5.3.1  | Uniformity (u)                                               | 63        |

| 3.5.3.2  | Diffuseness (D)                                              | 64        |

---

|          |                                                        |           |

|----------|--------------------------------------------------------|-----------|

| 3.5.3.3  | Reliability (R) . . . . .                              | 64        |

| 3.5.3.4  | Analysis and Comparison . . . . .                      | 65        |

| 3.5.3.5  | Performance evaluation . . . . .                       | 67        |

| 3.6      | Summary . . . . .                                      | 67        |

| <b>4</b> | <b>Recursive Challenge Feed Arbiter PUF (RC-FAPUF)</b> | <b>69</b> |

| 4.1      | Design considerations for RC-FAPUF . . . . .           | 69        |

| 4.2      | Implementation of RC-FAPUF . . . . .                   | 70        |

| 4.3      | Evaluation of RC-FAPUF . . . . .                       | 74        |

| 4.3.1    | Uniformity (u) . . . . .                               | 75        |

| 4.3.2    | Diffuseness (D) . . . . .                              | 76        |

| 4.3.3    | Reliability (R) . . . . .                              | 76        |

| 4.3.4    | Security evaluation of RC-FAPUF . . . . .              | 78        |

| 4.3.5    | Analysis and Comparison . . . . .                      | 80        |

| 4.3.6    | Performance analysis . . . . .                         | 81        |

| 4.4      | Summary . . . . .                                      | 83        |

| <b>5</b> | <b>Relaxation Oscillator PUF (ReOPUF)</b>              | <b>85</b> |

| 5.1      | Ring Oscillator (RO) PUF . . . . .                     | 86        |

| 5.2      | Relaxation Oscillator PUF (ReOPUF) . . . . .           | 87        |

| 5.2.1    | Design considerations . . . . .                        | 87        |

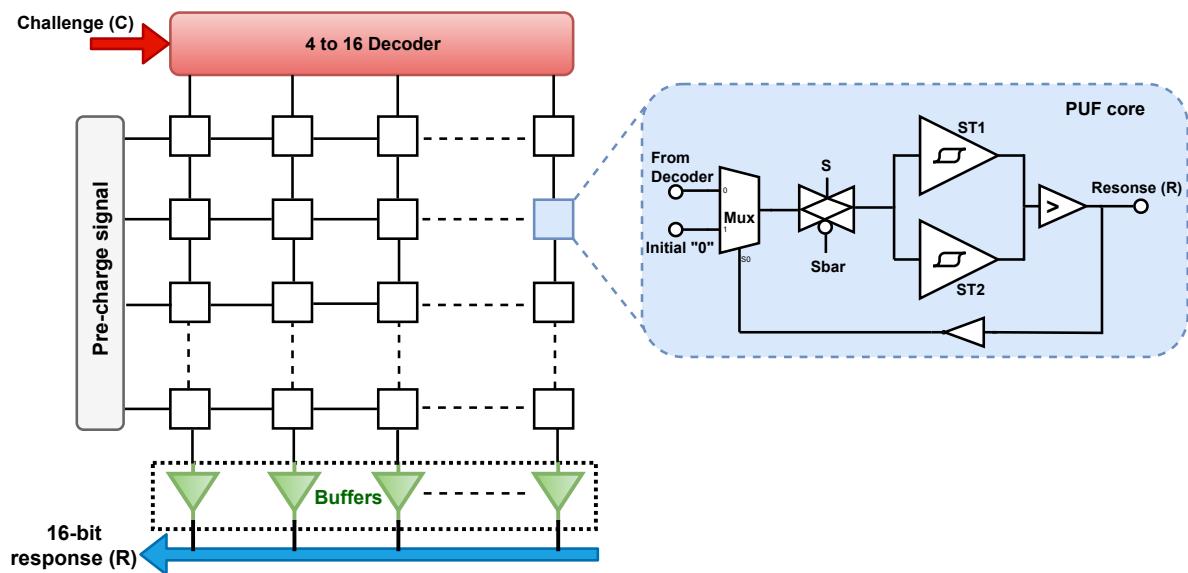

| 5.2.2    | Implementation of ReOPUF . . . . .                     | 89        |

| 5.2.3    | n-stage ReOPUF . . . . .                               | 90        |

| 5.2.4    | Evaluation of ReOPUF . . . . .                         | 90        |

| 5.2.4.1  | Uniformity (u) . . . . .                               | 91        |

---

---

|          |                                                                           |            |

|----------|---------------------------------------------------------------------------|------------|

| 5.2.4.2  | Diffuseness (D) . . . . .                                                 | 91         |

| 5.2.4.3  | Uniqueness (U) . . . . .                                                  | 92         |

| 5.2.4.4  | Reliability (R) . . . . .                                                 | 93         |

| 5.2.5    | Security evaluation . . . . .                                             | 94         |

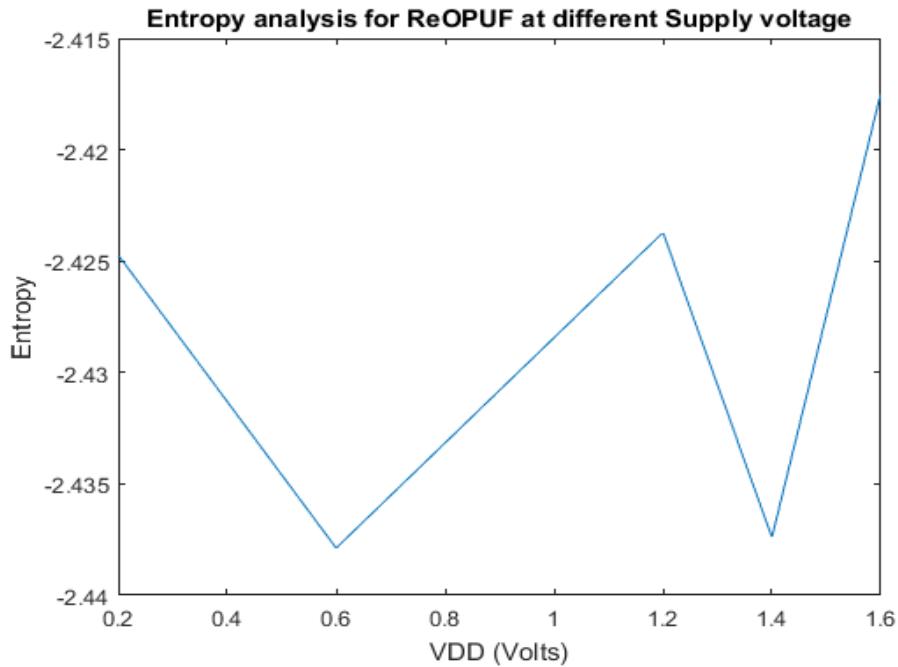

| 5.2.5.1  | Entropy Analysis . . . . .                                                | 95         |

| 5.2.5.2  | Correlation Coefficient Analysis . . . . .                                | 95         |

| 5.2.5.3  | Analysis and Comparison . . . . .                                         | 97         |

| 5.2.5.4  | Power Analysis . . . . .                                                  | 98         |

| 5.3      | Summary . . . . .                                                         | 98         |

| <b>6</b> | <b>ST-APUF: Schmitt Trigger (ST) Arbiter Physical Unclonable Function</b> | <b>100</b> |

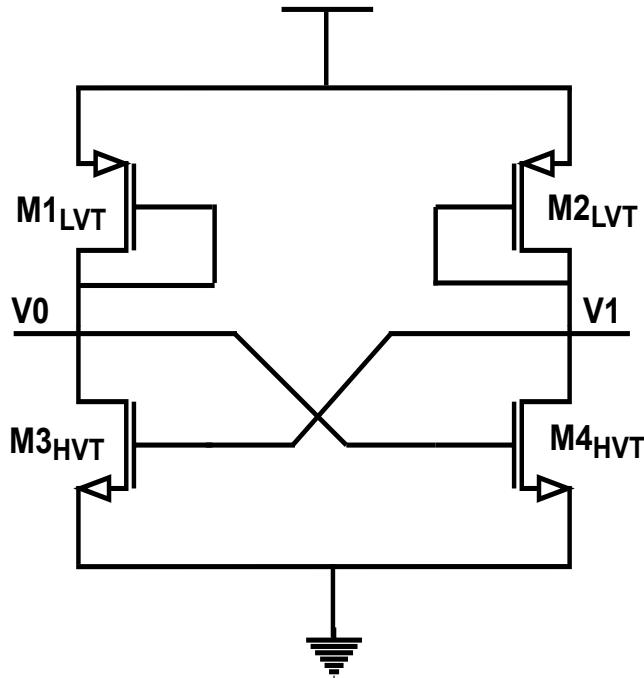

| 6.1      | Design considerations . . . . .                                           | 101        |

| 6.2      | Implementation of ST-APUF . . . . .                                       | 101        |

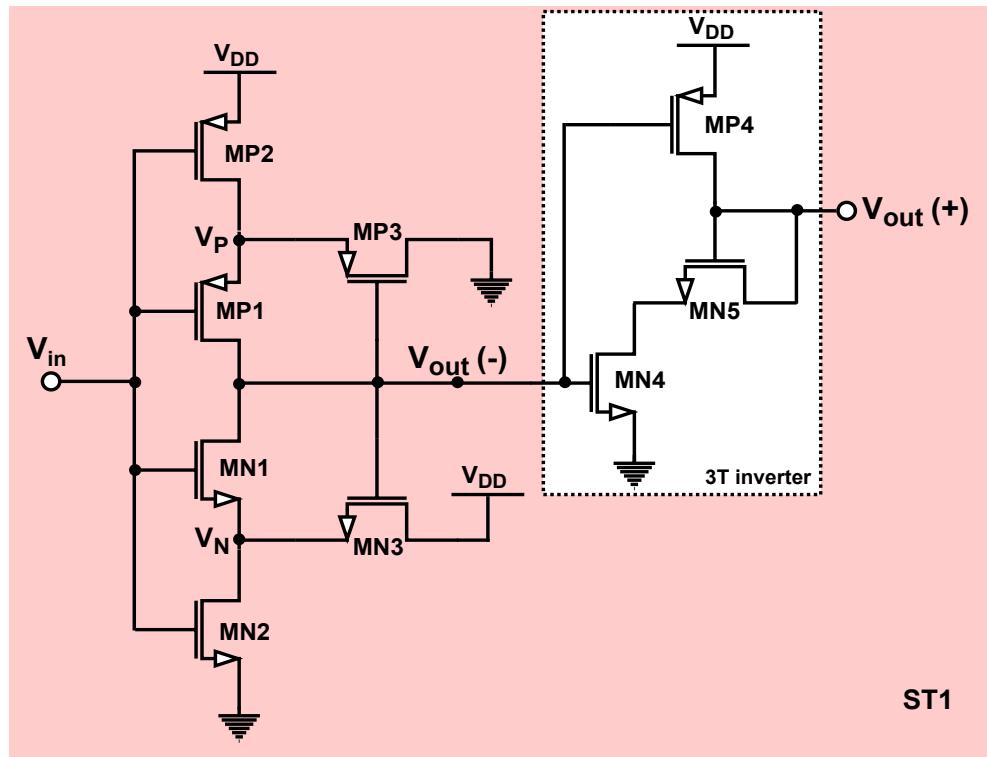

| 6.2.1    | Circuit analysis of ST1 . . . . .                                         | 106        |

| 6.2.1.1  | Current-Voltage Subcircuit Characteristics for ST1 . . . . .              | 106        |

| 6.2.1.2  | 3T inverter analysis for ST1 . . . . .                                    | 107        |

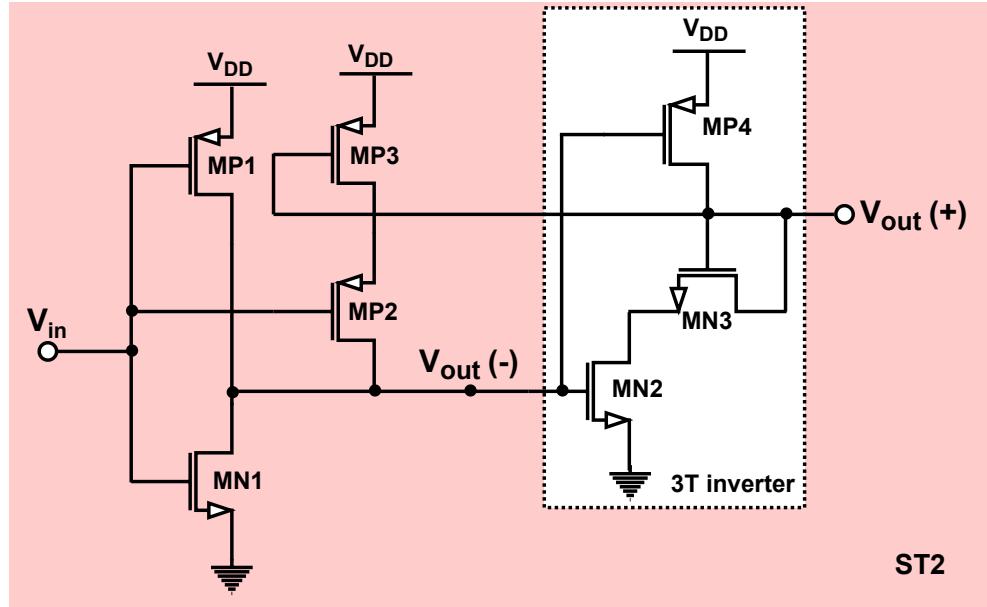

| 6.2.2    | Circuit analysis of ST2 . . . . .                                         | 108        |

| 6.2.2.1  | Current-Voltage Subcircuit Characteristics for ST2 . . . . .              | 108        |

| 6.2.2.2  | 3T inverter analysis for ST2 . . . . .                                    | 109        |

| 6.2.3    | Threshold, Transition of Proposed Schmitt-Trigger . . . . .               | 110        |

| 6.3      | Evaluation of ST-APUF . . . . .                                           | 111        |

| 6.3.1    | Uniformity (u) . . . . .                                                  | 111        |

| 6.3.2    | Diffuseness (D) . . . . .                                                 | 112        |

| 6.3.3    | Uniqueness (U) . . . . .                                                  | 112        |

| 6.3.4    | Reliability (R) . . . . .                                                 | 114        |

---

---

|                     |                                                                                   |            |

|---------------------|-----------------------------------------------------------------------------------|------------|

| 6.3.5               | Security evaluation . . . . .                                                     | 116        |

| 6.3.6               | Analysis and Comparison . . . . .                                                 | 117        |

| 6.3.6.1             | Performance analysis . . . . .                                                    | 117        |

| 6.4                 | Summary . . . . .                                                                 | 120        |

| <b>7</b>            | <b>Low Dropout (LDO) Regulator integrated PUF for improving attack resilience</b> | <b>121</b> |

| 7.1                 | Low Dropout (LDO) Regulator . . . . .                                             | 121        |

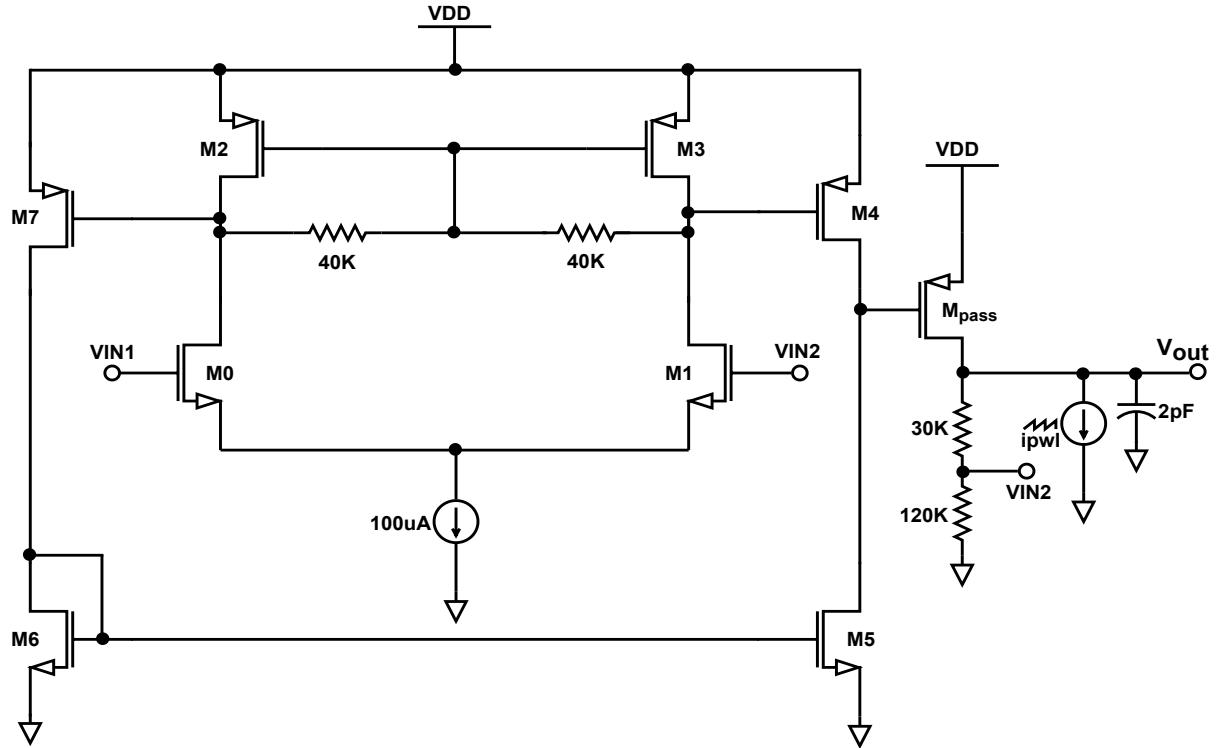

| 7.1.1               | Characterization of LDO . . . . .                                                 | 122        |

| 7.1.2               | Implementation of LDO . . . . .                                                   | 125        |

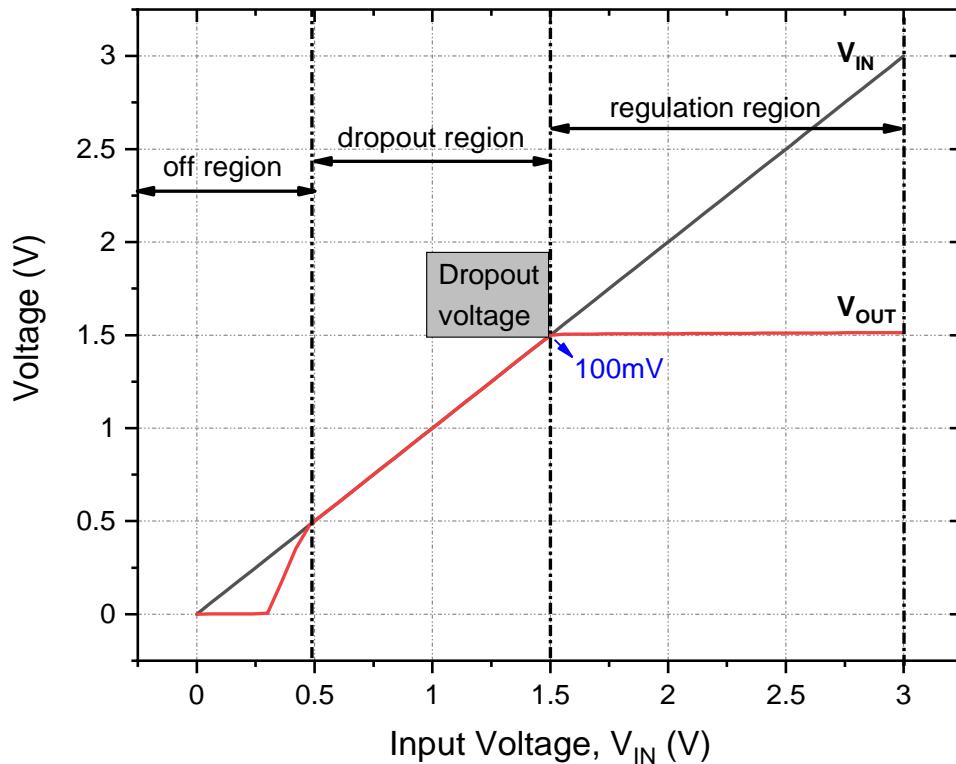

| 7.2                 | Operating regions of LDO . . . . .                                                | 126        |

| 7.2.1               | Measurement of power traces from LDO . . . . .                                    | 127        |

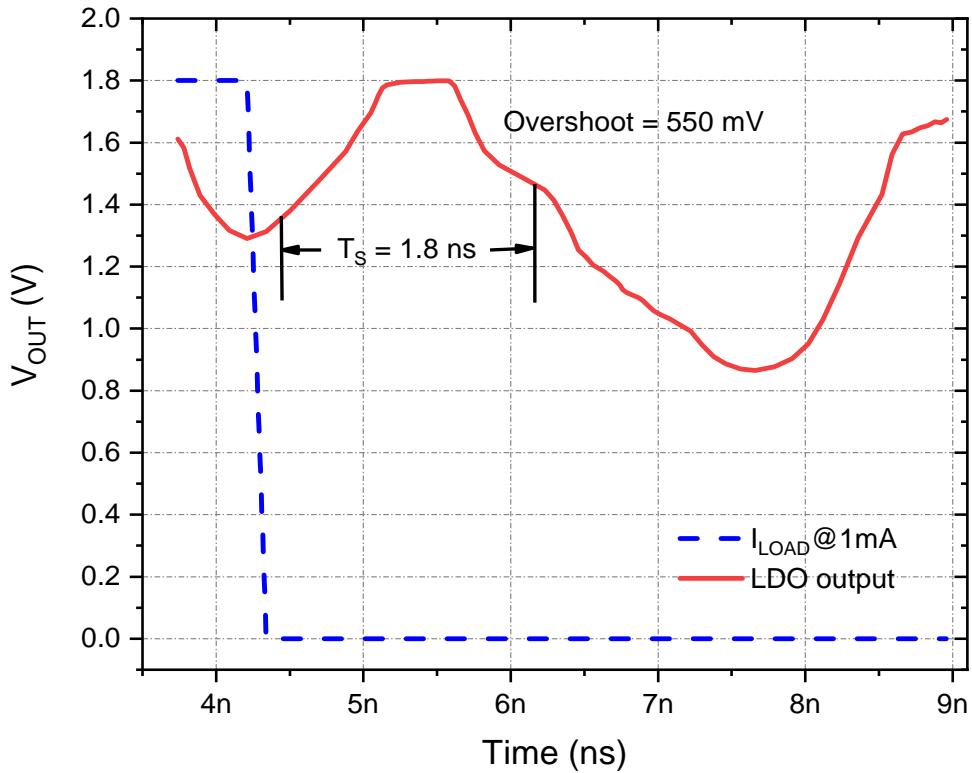

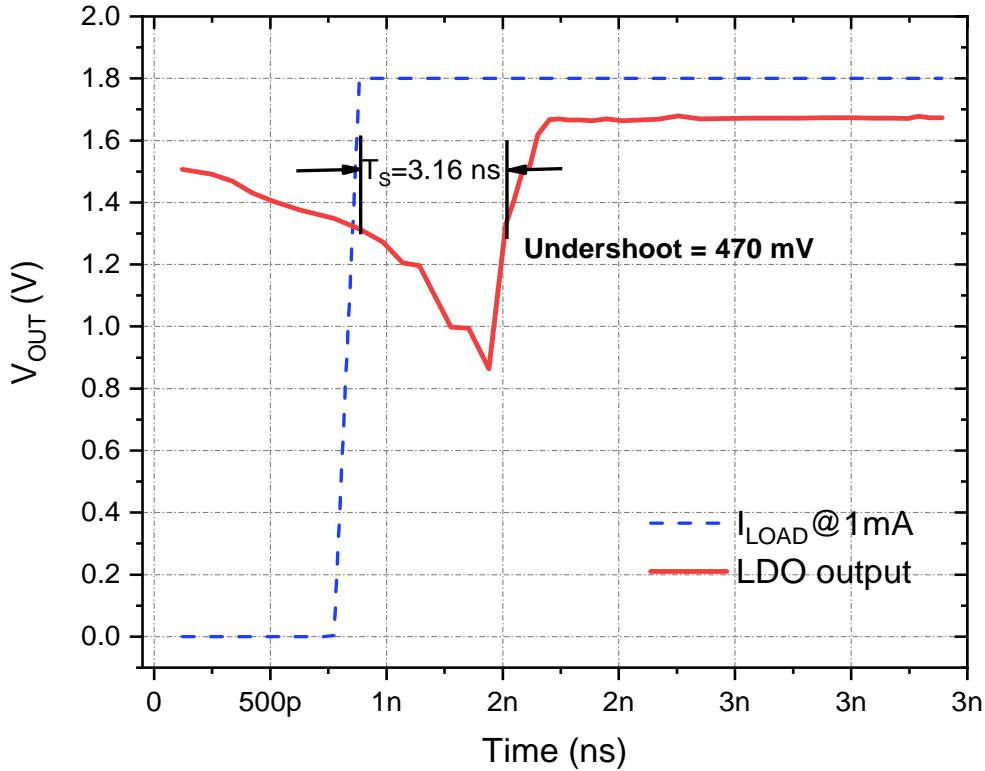

| 7.2.1.1             | Analysis of load transients . . . . .                                             | 127        |

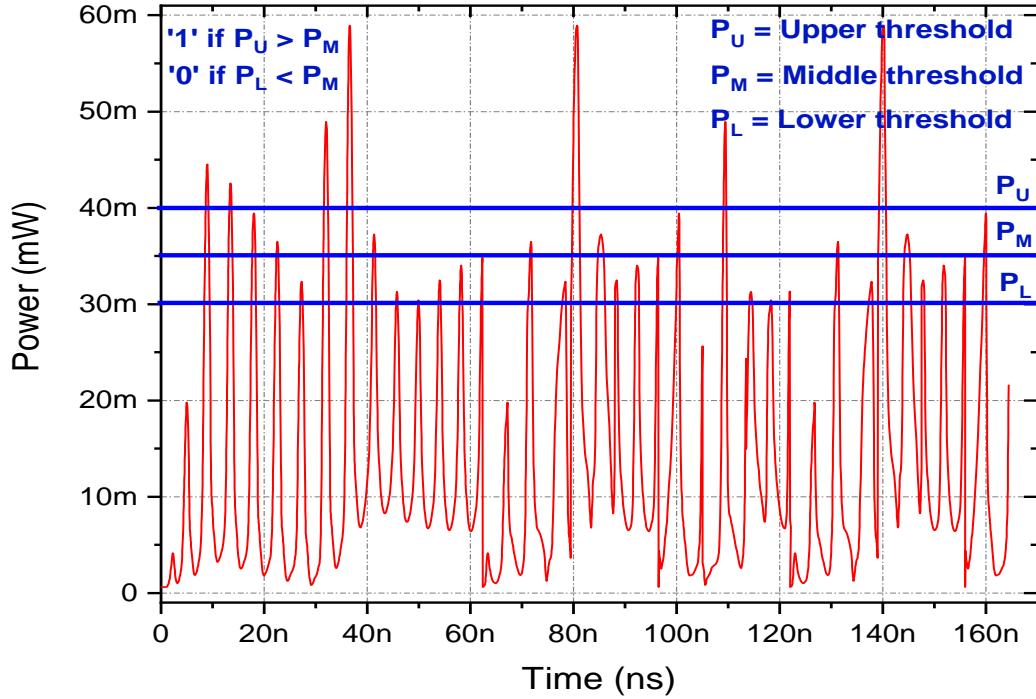

| 7.2.1.2             | Analysis of power traces towards security . . . . .                               | 129        |

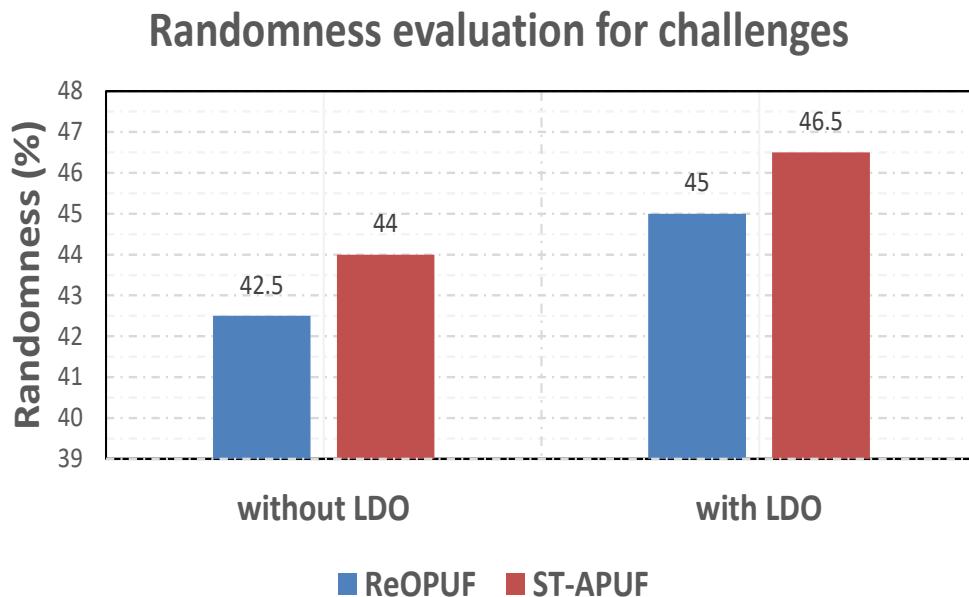

| 7.2.2               | Evaluation of randomness of challenges of ReOPUF and ST-APUF                      | 131        |

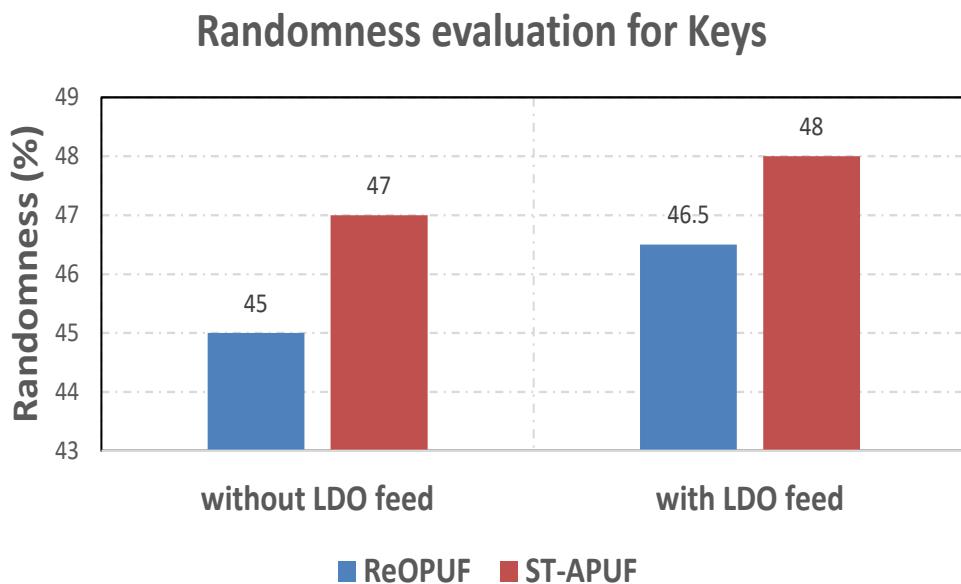

| 7.2.3               | Evaluation of randomness for responses or keys from ReOPUF or ST-APUF . . . . .   | 132        |

| 7.3                 | Summary . . . . .                                                                 | 134        |

| <b>8</b>            | <b>Conclusions and Future Scope</b>                                               | <b>135</b> |

| 8.1                 | Conclusions . . . . .                                                             | 135        |

| 8.2                 | Future Scope . . . . .                                                            | 137        |

| <b>Publications</b> |                                                                                   | <b>139</b> |

| <b>Bibliography</b> |                                                                                   | <b>141</b> |

# List of Figures

|      |                                    |    |

|------|------------------------------------|----|

| 1.1  | IoT in the security domain [3]     | 2  |

| 1.2  | Symmetric key cryptography [5,6]   | 4  |

| 1.3  | Asymmetric key cryptography [5,6]  | 4  |

| 1.4  | Hash functions [5,6]               | 5  |

| 1.5  | Random Number Generator            | 6  |

| 1.6  | Lightweight cryptography [9]       | 7  |

| 1.7  | Sources of variances in ICs [10]   | 9  |

| 1.8  | Physical Unclonable Function [12]  | 12 |

| 1.9  | Hardware Security Module [14]      | 13 |

| 1.10 | True Random Number Generator [16]  | 14 |

| 1.11 | Side channel attack materials [18] | 15 |

| 2.1  | PUF in IoT device                  | 22 |

| 2.2  | Basic APUF                         | 27 |

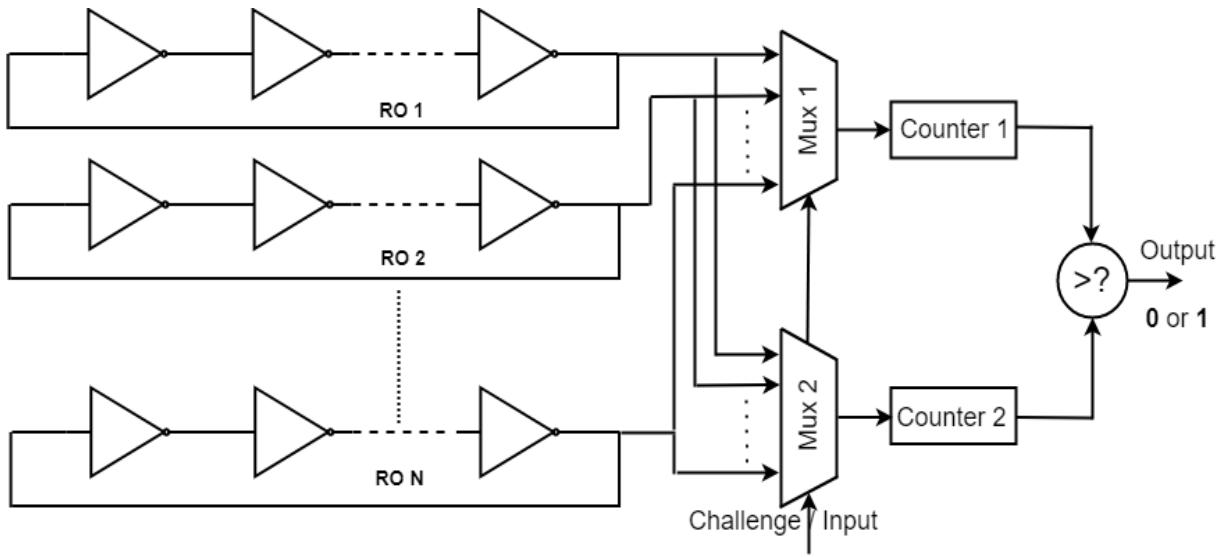

| 2.3  | Ring Oscillator PUF [32]           | 28 |

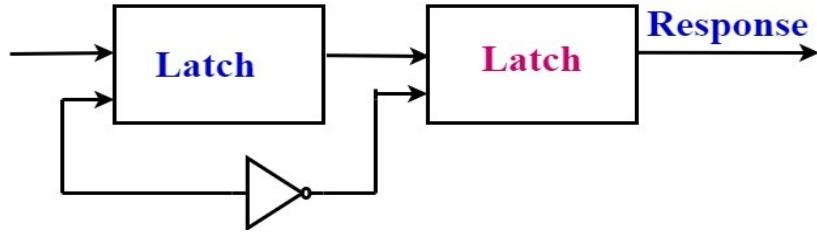

| 2.4  | Butterfly or clock PUF [45]        | 29 |

| 2.5  | Rotating Ring PUF [46]             | 30 |

| 2.6  | SRAM PUF [47]                      | 31 |

| 2.7  | DRAM PUF [49]                      | 32 |

|      |                                                                   |    |

|------|-------------------------------------------------------------------|----|

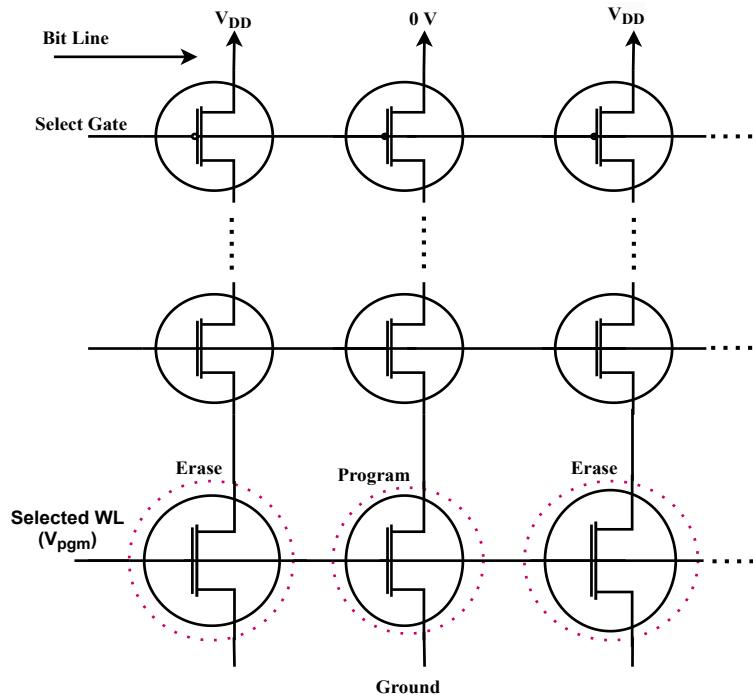

| 2.8  | Flash PUF [50] . . . . .                                          | 33 |

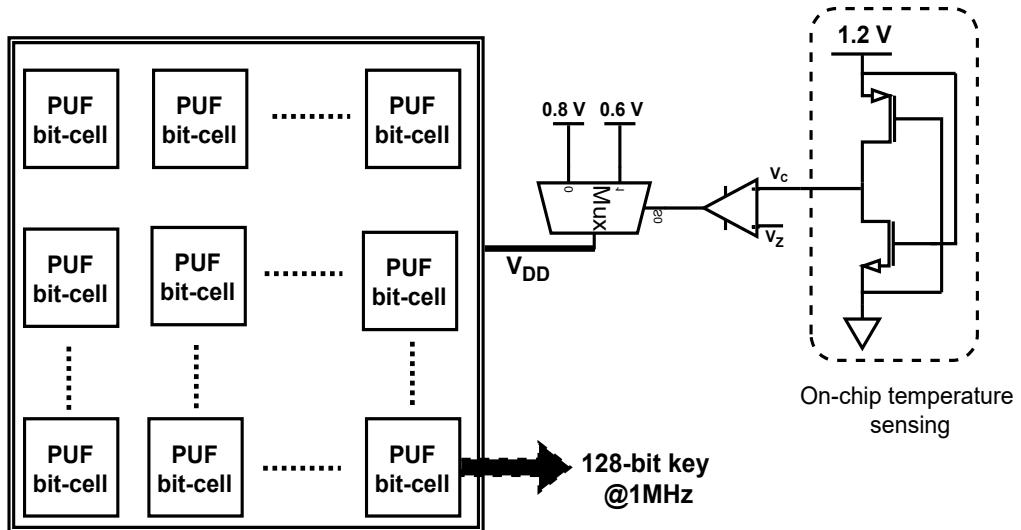

| 2.9  | Temperature stable PUF [55] . . . . .                             | 34 |

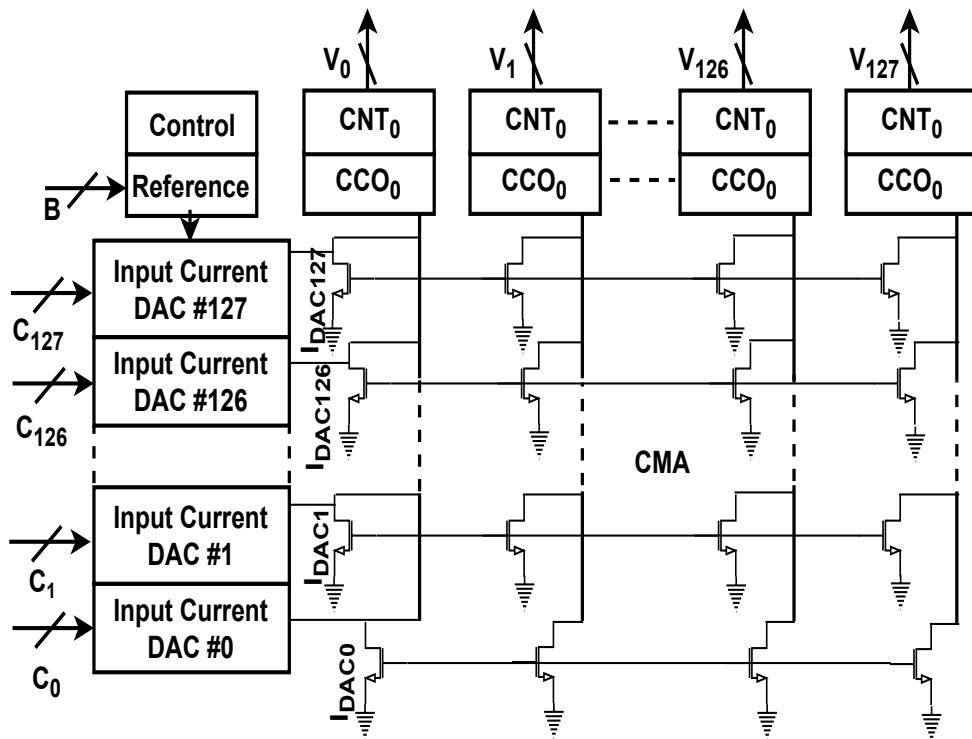

| 2.10 | Current Mirror Array PUF [59] . . . . .                           | 35 |

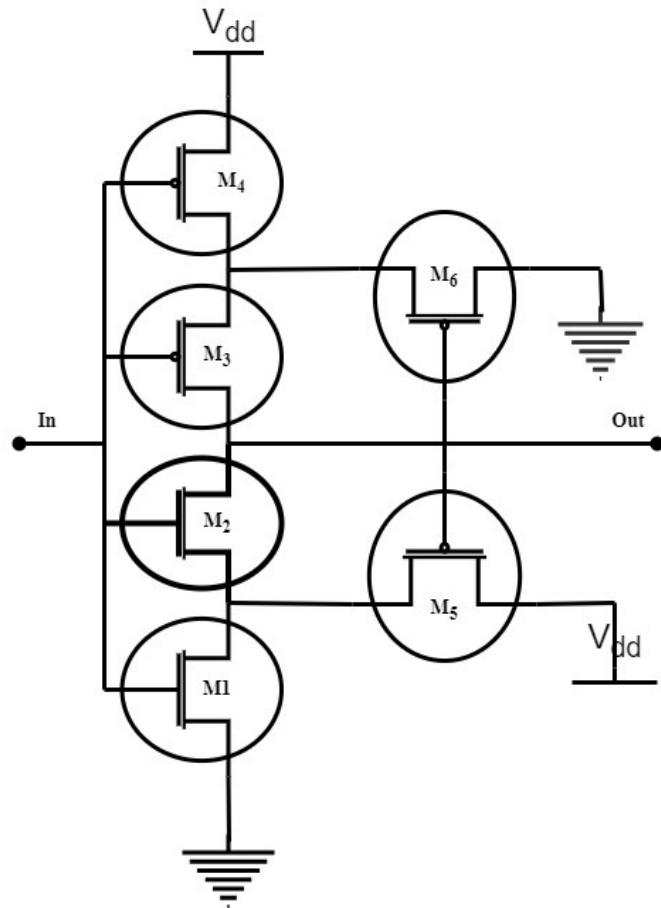

| 2.11 | Schmitt Trigger PUF [60] . . . . .                                | 36 |

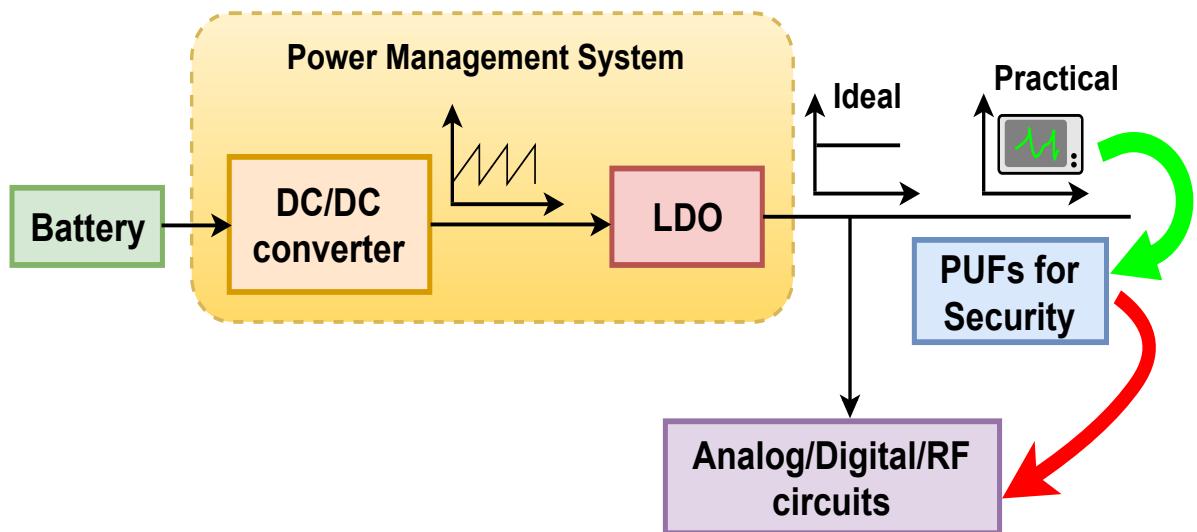

| 2.12 | Power management system for PUFs . . . . .                        | 36 |

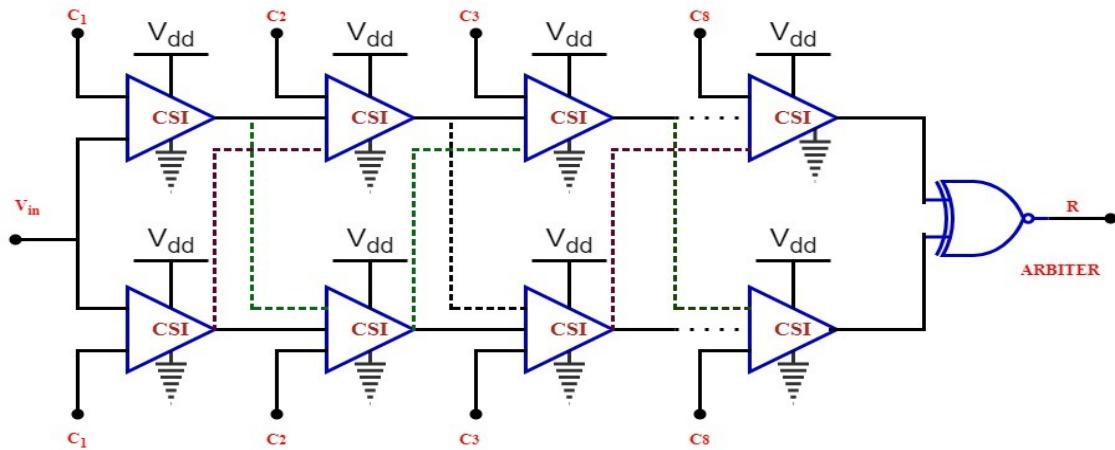

| 2.13 | Current Starved Inverter PUF [65] . . . . .                       | 37 |

| 2.14 | Comparator PUF [57] . . . . .                                     | 38 |

| 2.15 | Strong PUF design . . . . .                                       | 40 |

| 2.16 | Weak PUF design . . . . .                                         | 41 |

| 2.17 | Modeling attacks [78] . . . . .                                   | 42 |

| 2.18 | Side channel attack protection [82] . . . . .                     | 44 |

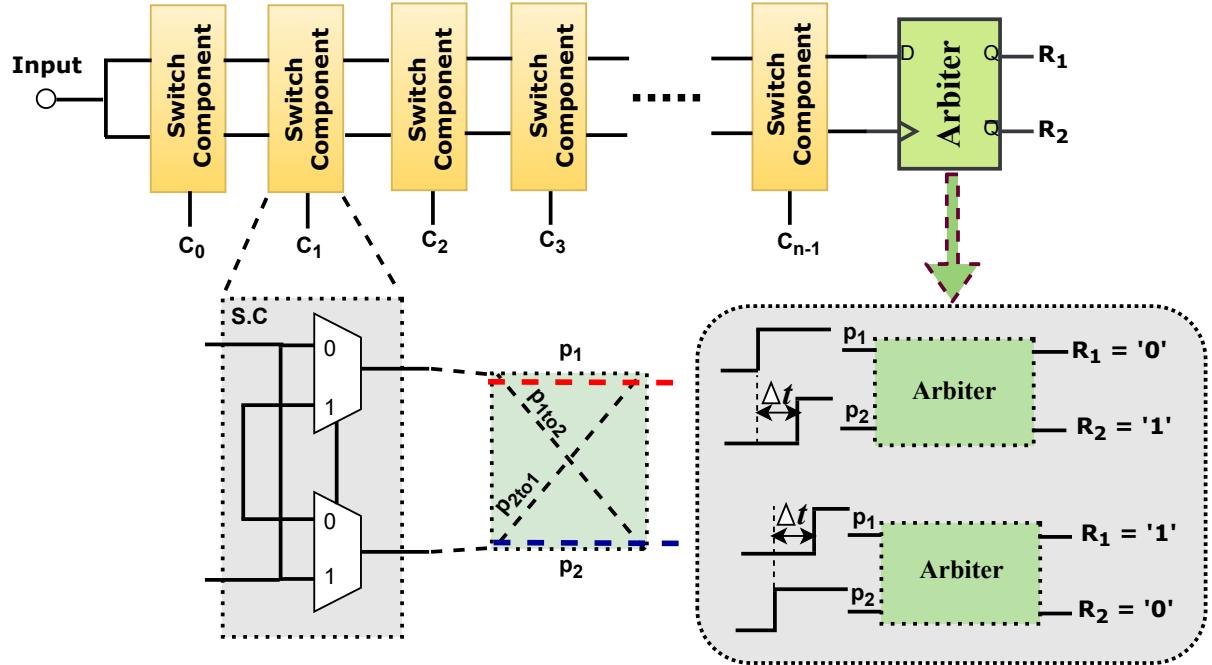

| 3.1  | Basic Arbiter PUF . . . . .                                       | 46 |

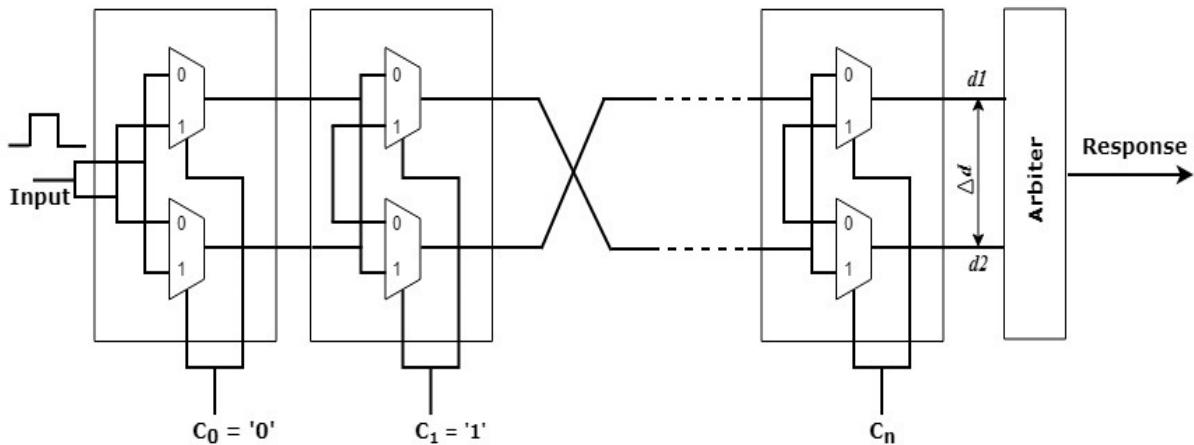

| 3.2  | Arbiter PUF mechanism . . . . .                                   | 47 |

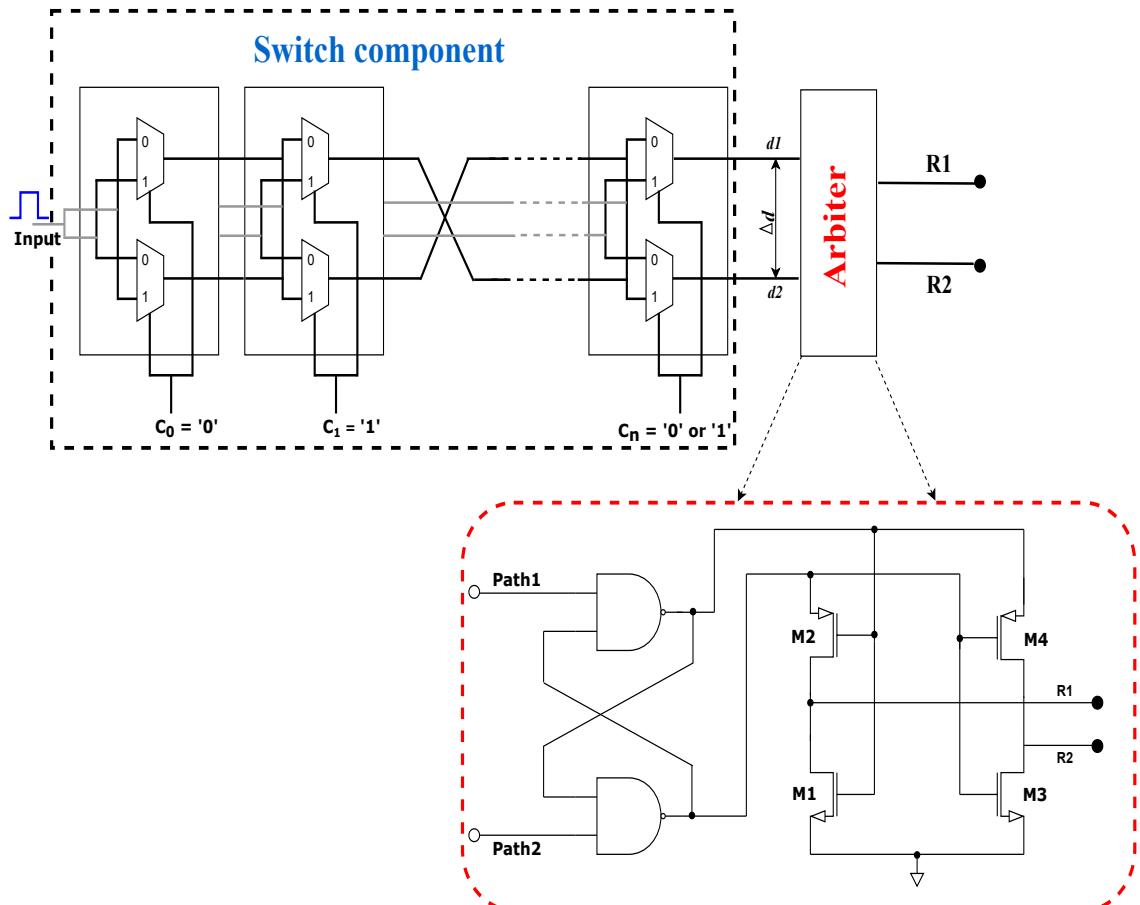

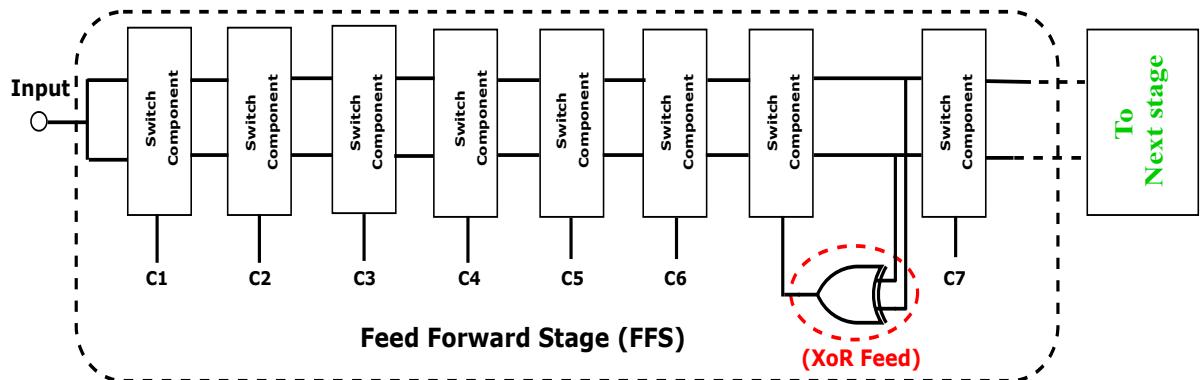

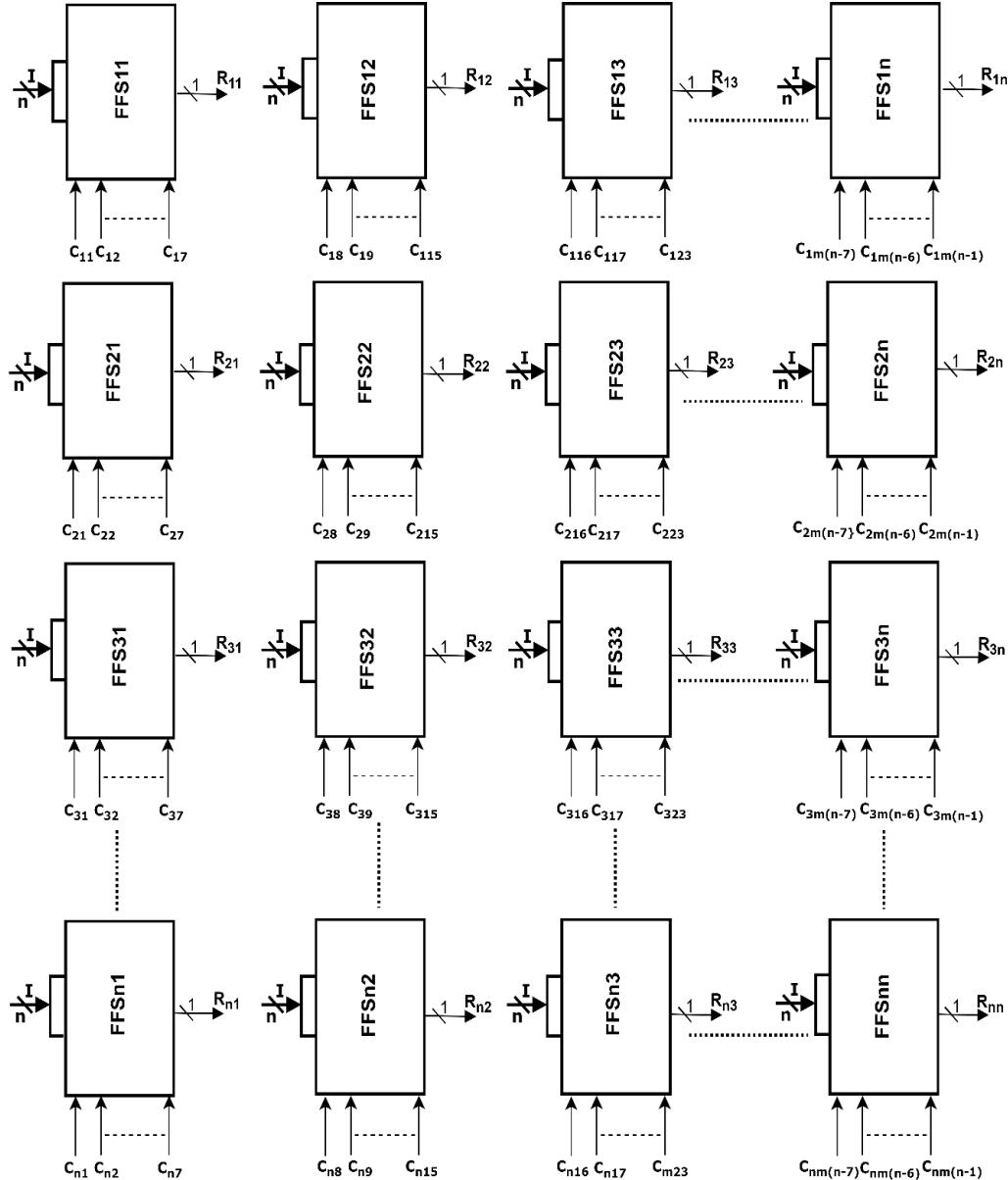

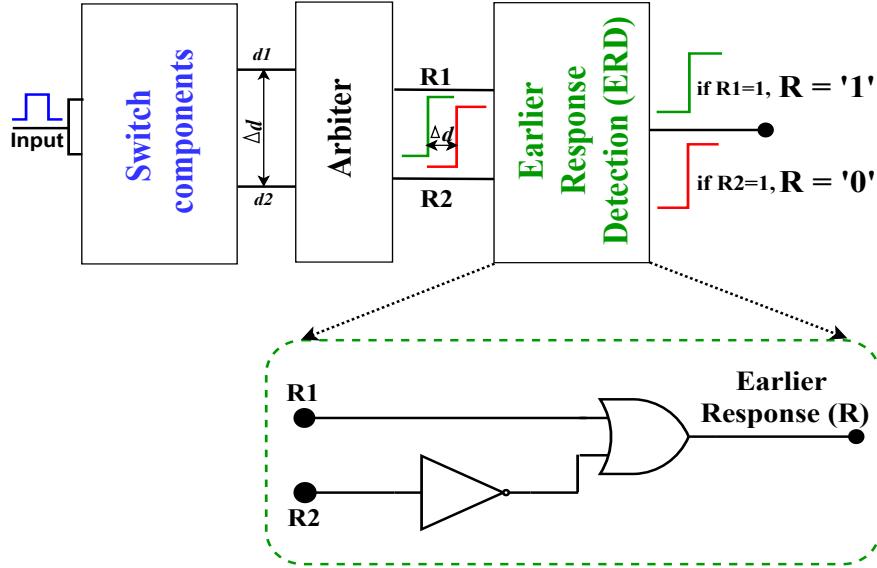

| 3.3  | Single FFS arbitration . . . . .                                  | 49 |

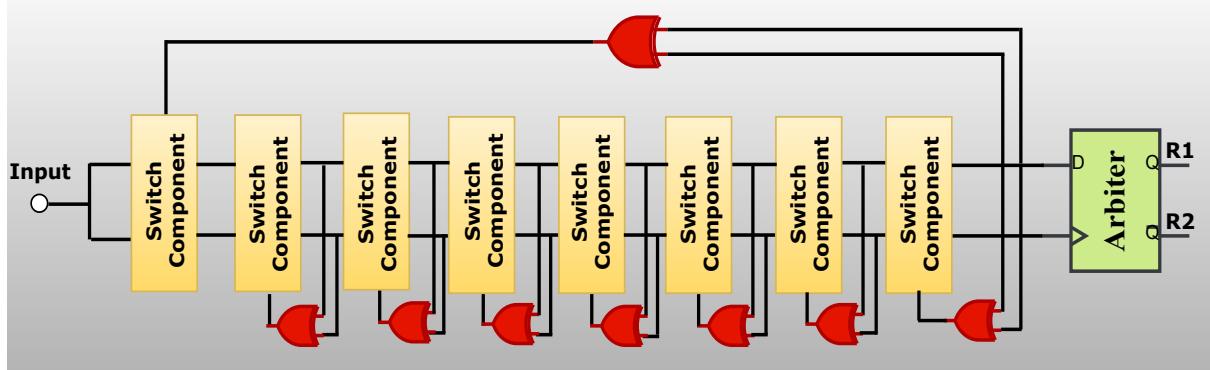

| 3.4  | n-stage XFAPUF with 8-challenge FFS . . . . .                     | 51 |

| 3.5  | ERD circuit . . . . .                                             | 52 |

| 3.6  | Uniformity of XFAPUF with a distribution of 1's and 0's . . . . . | 53 |

| 3.7  | Diffuseness of XFAPUF . . . . .                                   | 54 |

| 3.8  | Uniqueness of XFAPUF (inter-HD) . . . . .                         | 54 |

| 3.9  | Reliability assessment through BER . . . . .                      | 55 |

| 3.10 | Prediction accuracy of LR to XFAPUF . . . . .                     | 56 |

| 3.11 | Random number generation . . . . .                                | 59 |

| 3.12 | Chaotic APUF for key generation . . . . .                         | 61 |

| 3.13 | Chaotic sequence generation . . . . .                             | 62 |

---

|      |                                                                 |    |

|------|-----------------------------------------------------------------|----|

| 3.14 | Uniformity of chaotic PUF . . . . .                             | 63 |

| 3.15 | Diffuseness of Chaotic APUF . . . . .                           | 64 |

| 3.16 | Reliability analysis through supply voltage variation . . . . . | 65 |

| 3.17 | Reliability analysis through temperature variation . . . . .    | 66 |

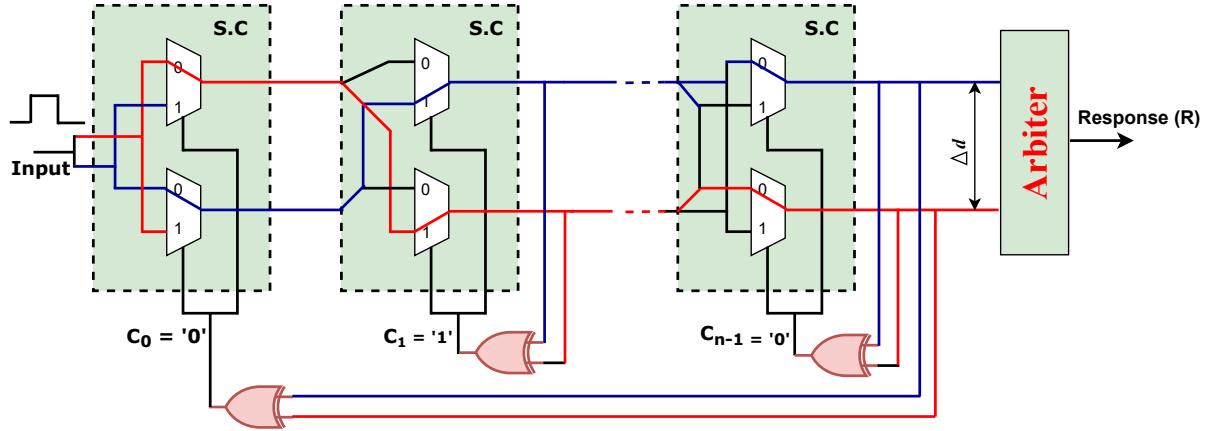

| 4.1  | APUF design and operation of Arbiter . . . . .                  | 71 |

| 4.2  | Proposed design of RC-FAPUF . . . . .                           | 72 |

| 4.3  | Operation of RC-FAPUF . . . . .                                 | 73 |

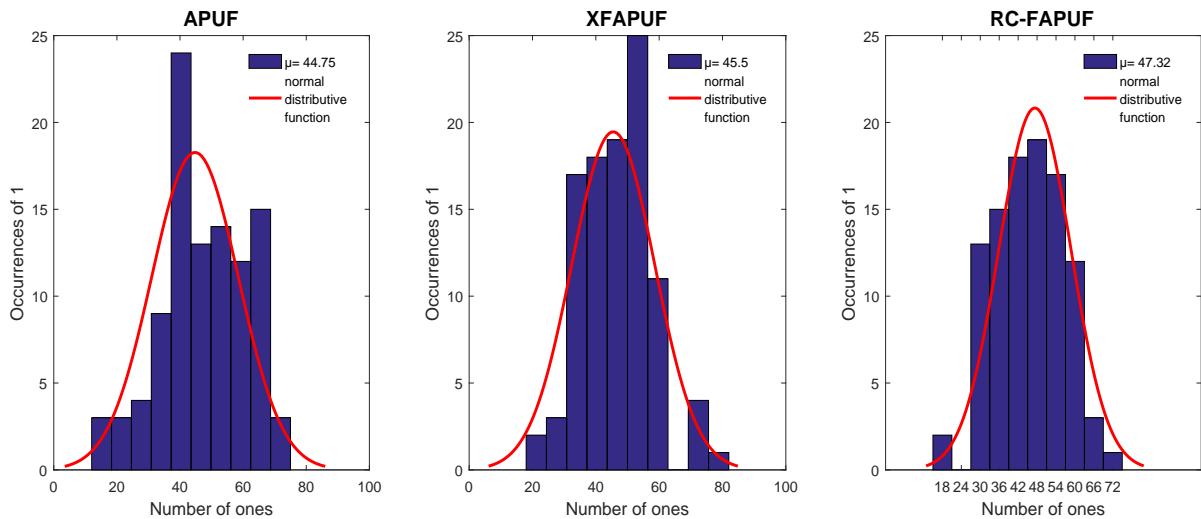

| 4.4  | Uniformity of RC-FAPUF . . . . .                                | 75 |

| 4.5  | Diffuseness of RC-FAPUF . . . . .                               | 76 |

| 4.6  | BER Vs Temperature in °C . . . . .                              | 77 |

| 4.7  | BER Vs Supply voltage $V_{DD}$ . . . . .                        | 78 |

| 4.8  | Prediction analysis of RC-FAPUF with LR . . . . .               | 79 |

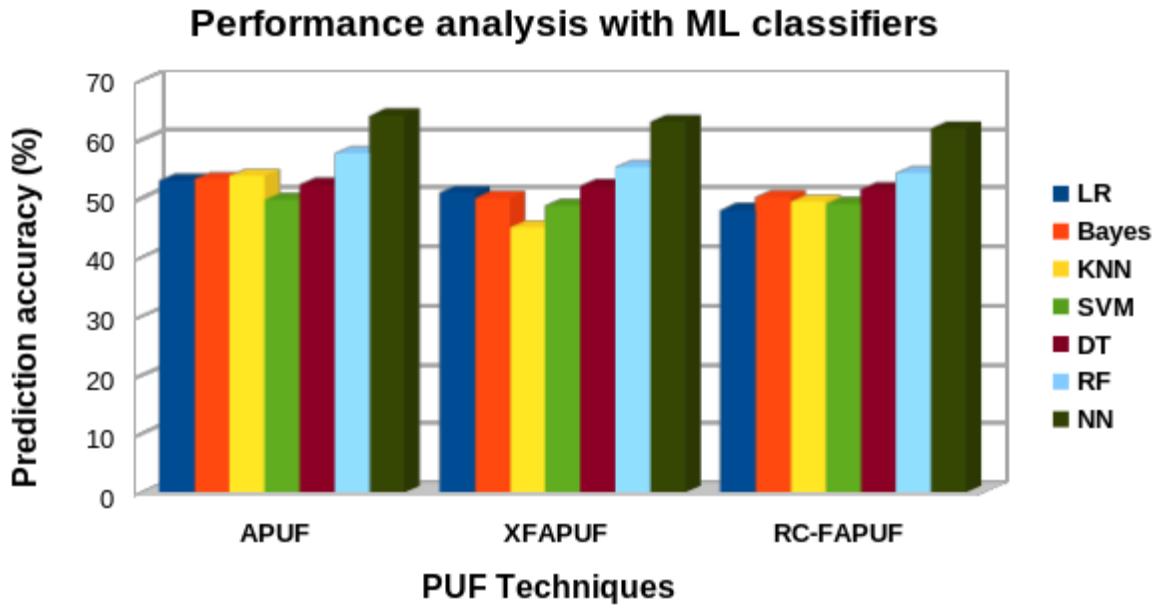

| 4.9  | Performance analysis of PUFs with various classifiers . . . . . | 80 |

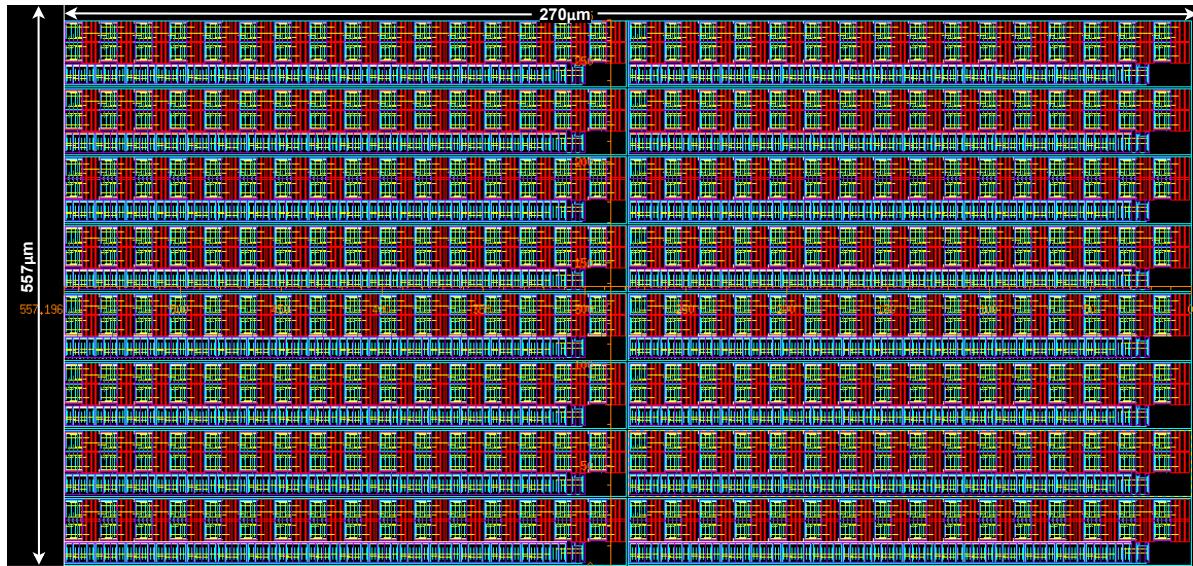

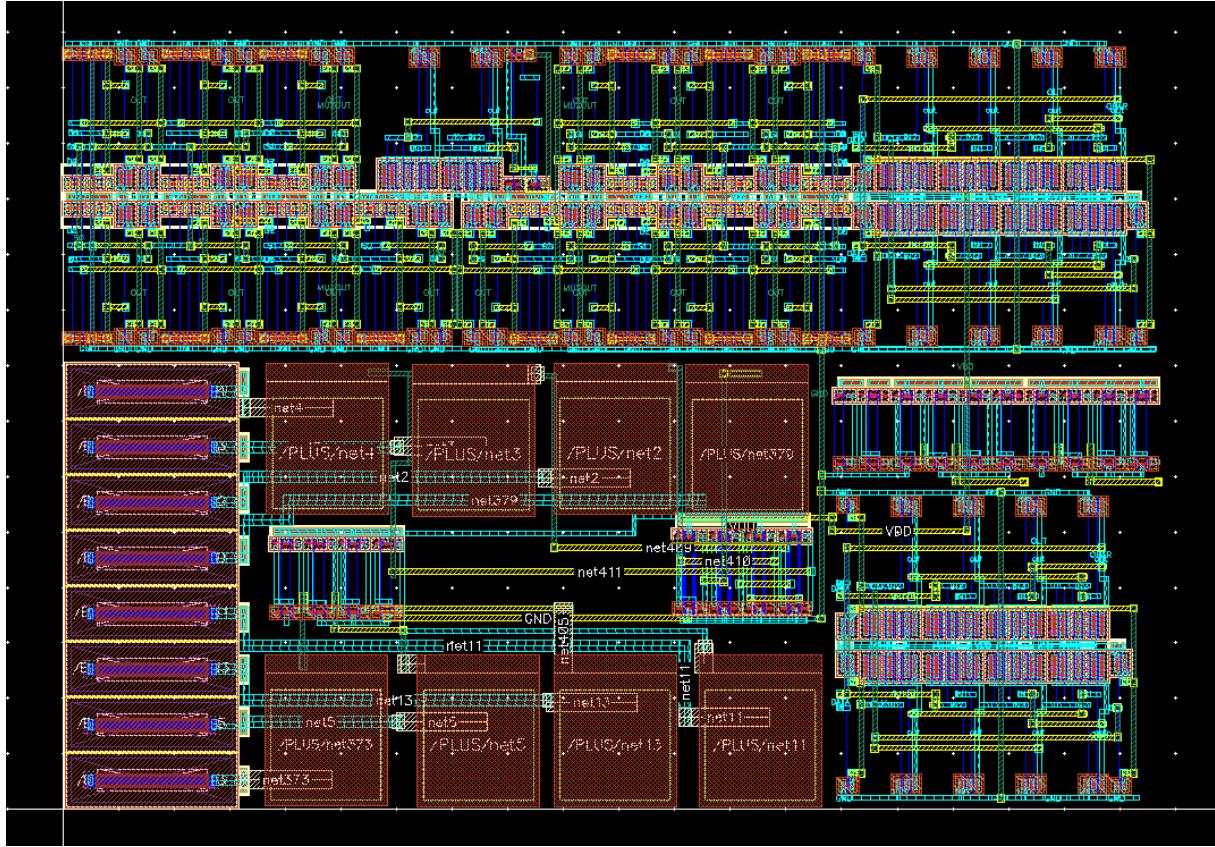

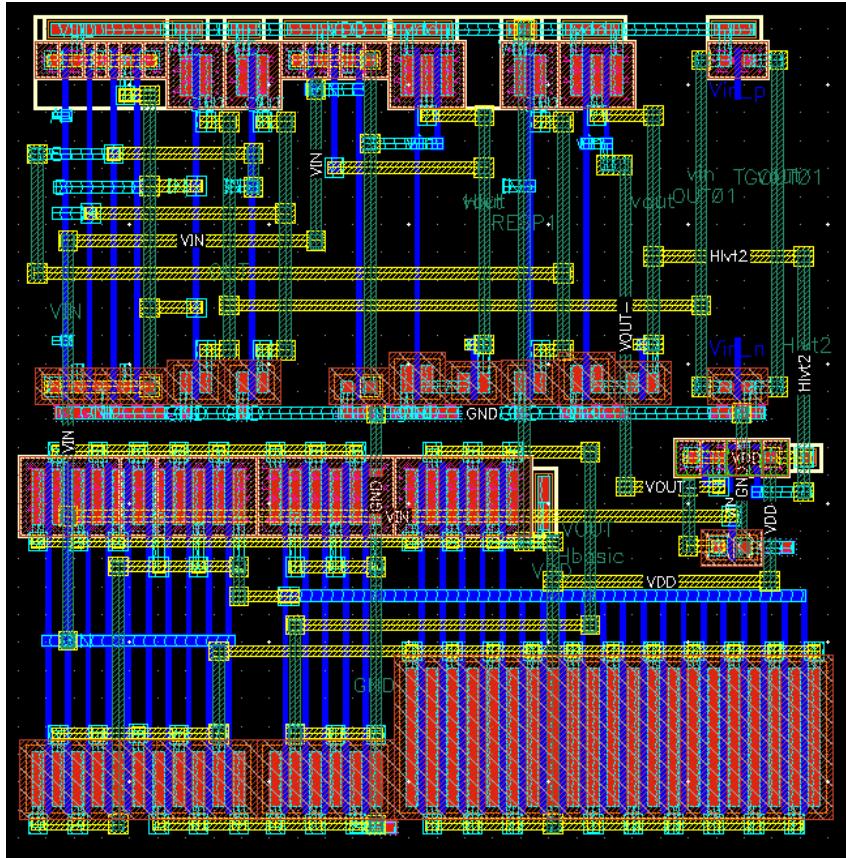

| 4.10 | Layout of RC-FAPUF . . . . .                                    | 84 |

| 5.1  | Ring Oscillator PUF . . . . .                                   | 86 |

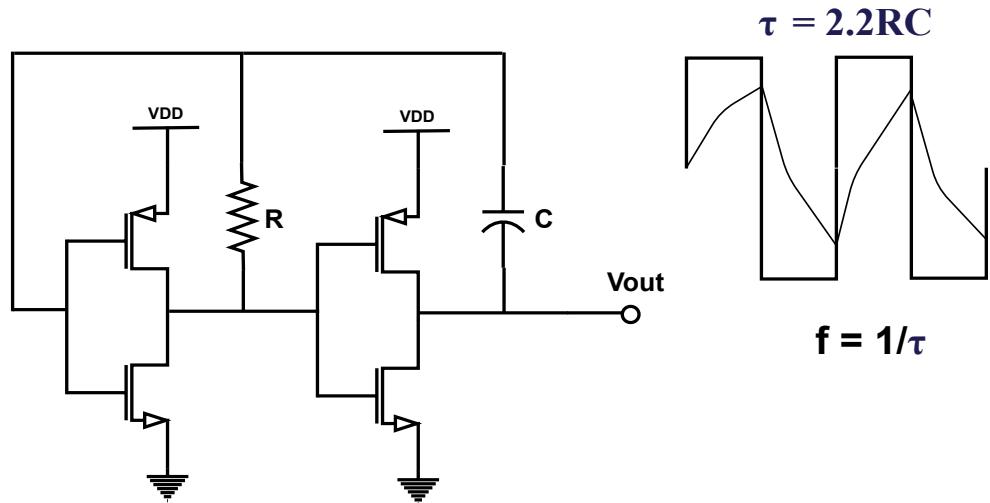

| 5.2  | Basic Relaxation Oscillator . . . . .                           | 88 |

| 5.3  | Proposed design of ReOPUF . . . . .                             | 89 |

| 5.4  | n-stage ReOPUF . . . . .                                        | 90 |

| 5.5  | Uniformity of ReOPUF . . . . .                                  | 91 |

| 5.6  | Diffuseness of ReOPUF . . . . .                                 | 92 |

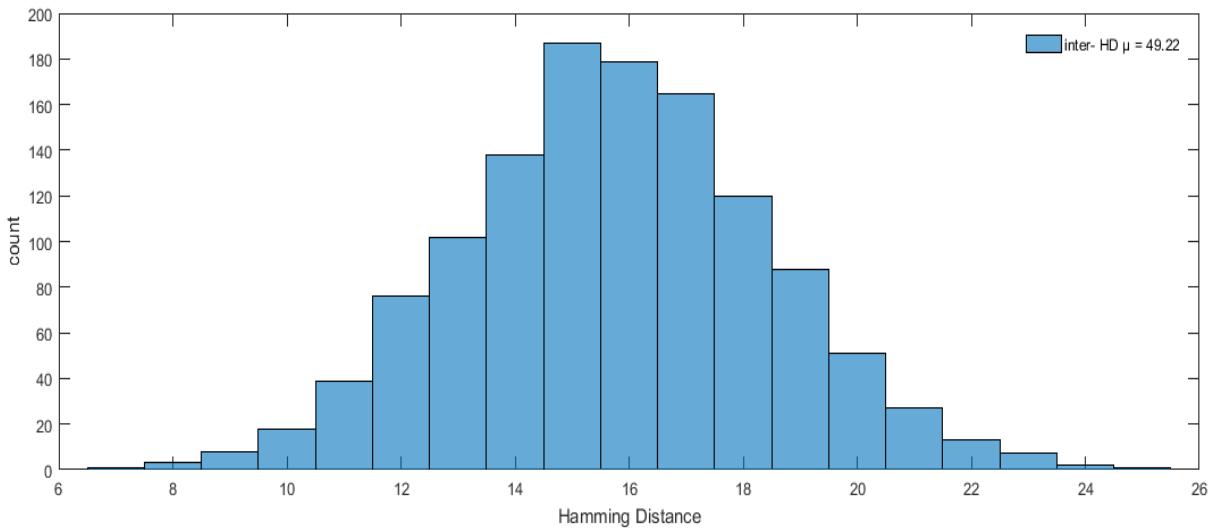

| 5.7  | Uniqueness of ReOPUF . . . . .                                  | 93 |

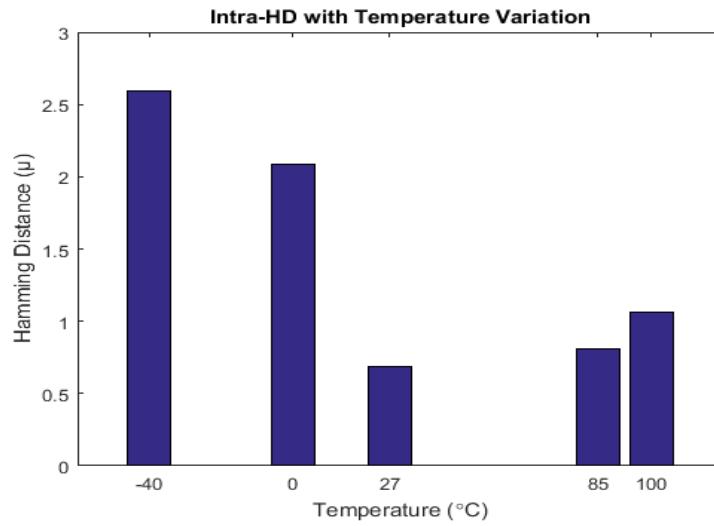

| 5.8  | Reliability of ReOPUF temperature variation . . . . .           | 94 |

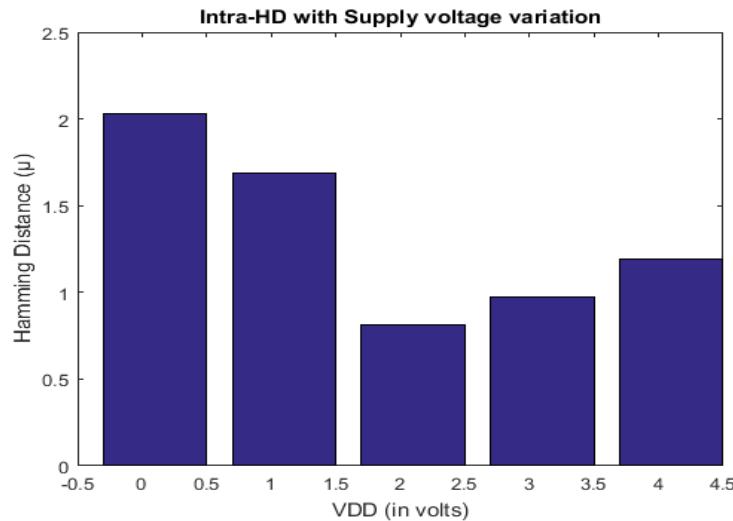

| 5.9  | Reliability of ReOPUF with $V_{DD}$ variation . . . . .         | 94 |

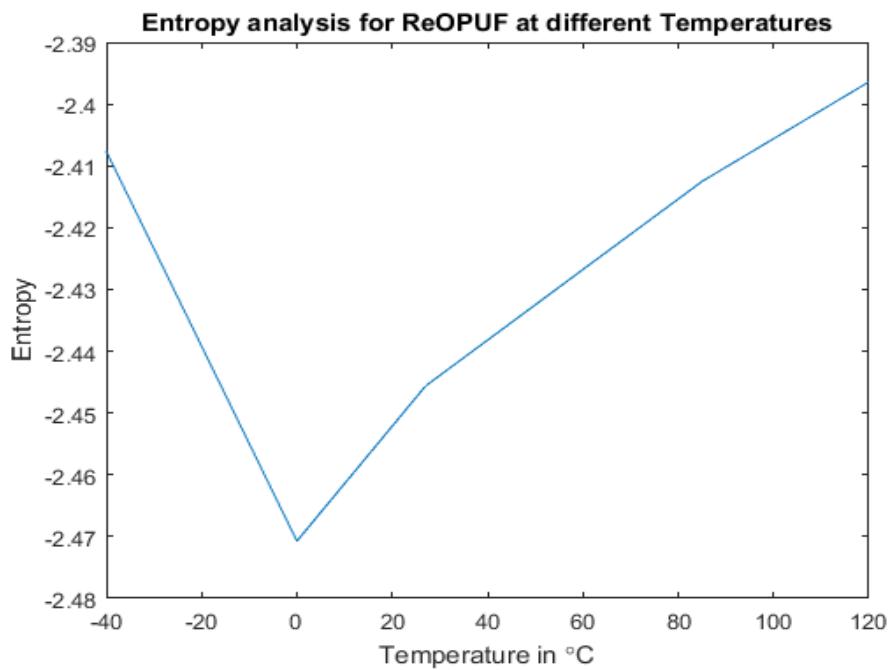

| 5.10 | Entropy of ReOPUF with temperature variation . . . . .          | 95 |

---

---

|      |                                                                          |     |

|------|--------------------------------------------------------------------------|-----|

| 5.11 | Entropy of ReOPUF with supply voltage variation . . . . .                | 96  |

| 5.12 | Layout of ReOPUF . . . . .                                               | 98  |

| 6.1  | Architecture of the proposed ST-APUF . . . . .                           | 102 |

| 6.2  | Transistor level schematic of ST1 inverter . . . . .                     | 103 |

| 6.3  | Transistor level schematic of ST2 inverter . . . . .                     | 104 |

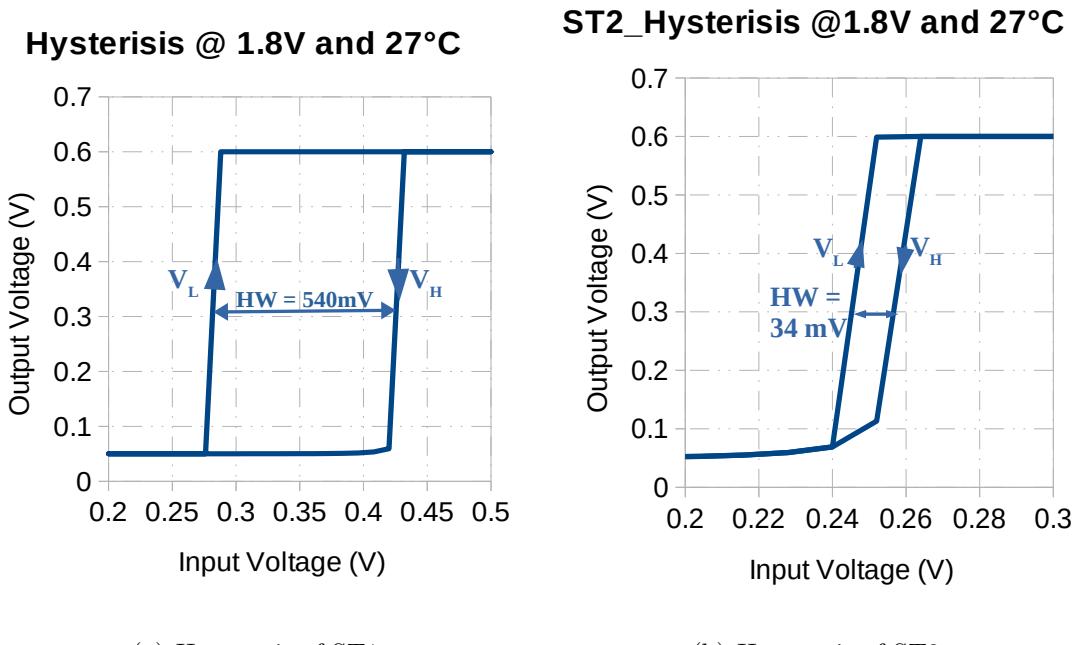

| 6.4  | Hysteresis analysis of ST . . . . .                                      | 104 |

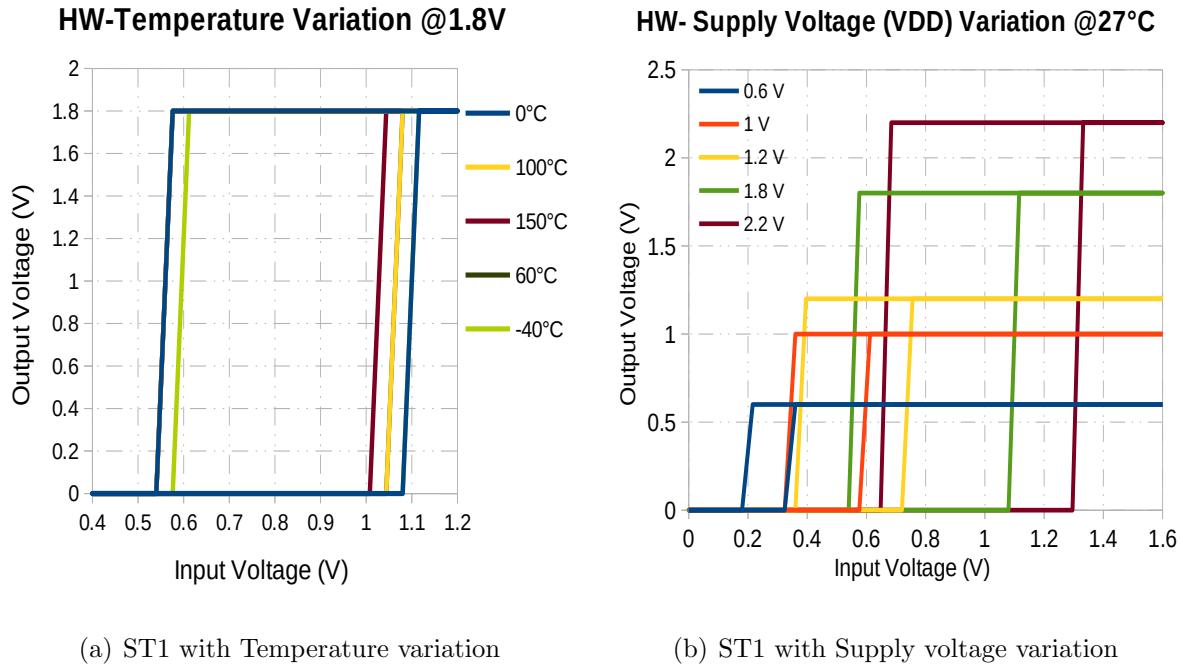

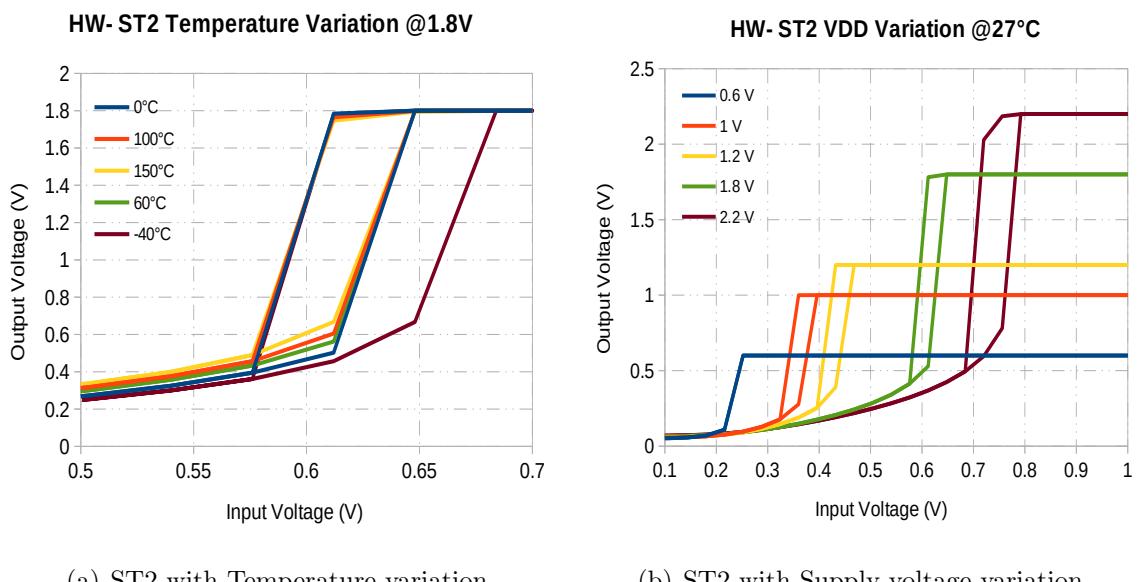

| 6.5  | Hysteresis Width variation in ST1 . . . . .                              | 105 |

| 6.6  | Hysteresis Width variation in ST2 . . . . .                              | 105 |

| 6.7  | Uniformity of ST-APUF with distribution of 1's and 0's . . . . .         | 112 |

| 6.8  | Diffuseness of ST-APUF . . . . .                                         | 113 |

| 6.9  | Uniqueness of STAPUF (inter-HD) . . . . .                                | 113 |

| 6.10 | Reliability assessment through BER . . . . .                             | 115 |

| 6.11 | Prediction analysis of ST-APUF . . . . .                                 | 116 |

| 6.12 | Performance with ML classifiers . . . . .                                | 117 |

| 6.13 | Layout of ST-APUF . . . . .                                              | 120 |

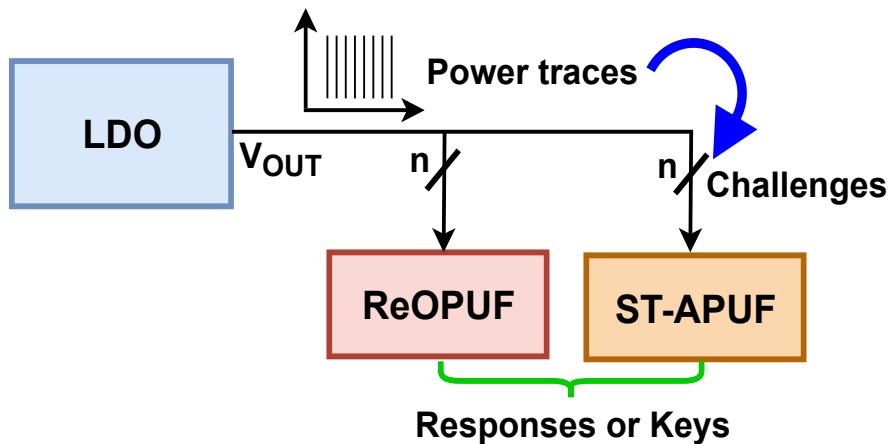

| 7.1  | Block diagram of LDO challenge generation through power traces . . . . . | 122 |

| 7.2  | Design of LDO [96] . . . . .                                             | 126 |

| 7.3  | Operating regions of LDO . . . . .                                       | 127 |

| 7.4  | Overshoot transient of LDO . . . . .                                     | 128 |

| 7.5  | Undershoot transient of LDO . . . . .                                    | 129 |

| 7.6  | Power traces of LDO measured at various $I_{LOAD}$ . . . . .             | 130 |

| 7.7  | Randomness estimation of challenges for ReOPUF and ST-APUF . . . . .     | 131 |

| 7.8  | Randomness estimation of keys for ReOPUF and ST-APUF . . . . .           | 132 |

## List of Tables

|     |                                                              |     |

|-----|--------------------------------------------------------------|-----|

| 3.1 | Specifications for XFAPUF . . . . .                          | 49  |

| 3.2 | Comparison of metrics of different PUF designs . . . . .     | 57  |

| 3.3 | XFAPUF quality metrics at different temperatures . . . . .   | 58  |

| 3.4 | Specifications for Chaotic-APUF . . . . .                    | 60  |

| 3.5 | Comparison of metrics of different PUF designs . . . . .     | 66  |

| 4.1 | Specifications for RC-FAPUF . . . . .                        | 70  |

| 4.2 | RC-FAPUF evaluation with ML classifiers . . . . .            | 80  |

| 4.3 | RC-FAPUF quality metrics at different temperatures . . . . . | 81  |

| 4.4 | RC-FAPUF quality metrics at various $V_{DD}$ . . . . .       | 81  |

| 4.5 | Comparison of metrics of different PUF designs . . . . .     | 82  |

| 5.1 | Specifications for ReOPUF . . . . .                          | 88  |

| 5.2 | Comparison of metrics of different PUF designs . . . . .     | 97  |

| 5.3 | ReOPUF quality metrics at different temperatures . . . . .   | 97  |

| 5.4 | Power comparison with RO PUF . . . . .                       | 98  |

| 6.1 | Specifications for ST-APUF . . . . .                         | 101 |

| 6.2 | Comparison of metrics of different PUF designs . . . . .     | 118 |

| 6.3 | ST-APUF quality metrics at different temperatures . . . . .  | 119 |

|     |                                                     |     |

|-----|-----------------------------------------------------|-----|

| 6.4 | ST-APUF quality metrics at different supply voltage | 119 |

| 7.1 | Specifications for LDO                              | 125 |

| 7.2 | Performance of randomness for ReOPUF and ST-APUF    | 133 |

| 7.3 | Comparison of randomness with different PUF designs | 133 |

## List of Abbreviations

|               |                                                     |

|---------------|-----------------------------------------------------|

| <b>AES</b>    | Advanced Encryption Standard                        |

| <b>AI</b>     | Artificial Intelligence                             |

| <b>AMS</b>    | Analog and Mixed Signal                             |

| <b>APUF</b>   | Arbiter Physical Unclonable Function                |

| <b>ASIC</b>   | Application Specific Integrated Circuit             |

| <b>ATM</b>    | Automated Teller Machine                            |

| <b>CMA</b>    | Current Mirror Array                                |

| <b>CMOS</b>   | Complementary Metal Oxide Semiconductor             |

| <b>CRP</b>    | Challenge Response Pair                             |

| <b>DAPUF</b>  | Double Arbiter Physical Unclonable Function         |

| <b>DES</b>    | Data Encryption Standard                            |

| <b>DLFET</b>  | Doping Less Field Effect Transistor                 |

| <b>DRAM</b>   | Dynamic Random Access Memory                        |

| <b>EEPROM</b> | Electrically Erasable Programmable Read Only Memory |

| <b>FFA</b>    | Feed Forward Arbiter                                |

| <b>FIB</b>    | Focused Injection Beam                              |

| <b>FinFET</b> | Fin Field Effect Transistor                         |

| <b>FPGA</b>   | Field Programmable Gate Array                       |

| <b>HCI</b>    | Hot Carrier Injection                               |

| <b>HRNG</b>   | Hardware Random Number Generator                    |

| <b>HSM</b>    | Hardware Security Module                            |

| <b>IP</b>     | Intellectual Property                               |

| <b>IoMT</b>   | Internet of Medical Things                          |

| <b>LDO</b>    | Low Dropout regulator                               |

| <b>LFSR</b>   | Linear Feedback Shift register                      |

| <b>ML</b>     | Machine Learning                                    |

| <b>MVL</b>    | Multiple Value Logic                                |

| <b>NBTI</b>   | Negative Bias Thermal Instability                   |

|                       |                                                |

|-----------------------|------------------------------------------------|

| <b>NIST</b>           | National Institute of Standards and Technology |

| <b>NMOS</b>           | N-channel Metal Oxide Semiconductor            |

| <b>NN</b>             | Neural Networks                                |

| <b>OP-AMP</b>         | Operational Amplifier                          |

| <b>OTP</b>            | One Time Programmable                          |

| <b>PBTI</b>           | Positive Bias Thermal Instability              |

| <b>PKI</b>            | Public Key Infrastructure                      |

| <b>PMOS</b>           | P-channel Metal Oxide Semiconductor            |

| <b>PMU</b>            | Power Management Unit                          |

| <b>PRNG</b>           | Pseudo Random Number Generator                 |

| <b>PTAT</b>           | Positive To Absolute Temperature               |

| <b>PUF</b>            | Physical Unclonable Function                   |

| <b>PV</b>             | Process Variation                              |

| <b>RFID</b>           | Radio Frequency IDentification                 |

| <b>RNG</b>            | Random Number Generator                        |

| <b>RO</b>             | Ring Oscillator                                |

| <b>RRAM</b>           | Rotating Random Access Memory                  |

| <b>SbD</b>            | Security by Design                             |

| <b>SCA</b>            | Side Channel Attacks                           |

| <b>SRAM</b>           | Static Random Access Memory                    |

| <b>ST</b>             | Schmitt Trigger                                |

| <b>SVM</b>            | Support Vector Machine                         |

| <b>TCRO</b>           | Temperature Control Ring Oscillator            |

| <b>TPM</b>            | Trust Platform Module                          |

| <b>TRNG</b>           | True Random Number Generator                   |

| <b>UMC</b>            | United Microelectronics Corporation            |

| <b>VLSI</b>           | Very Large Scale Integration                   |

| <b>mm<sup>2</sup></b> | square millimeter                              |

| <b>nm</b>             | nanometer                                      |

| <b>ns</b>             | nanosecond                                     |

| <b>μm</b>             | micrometer                                     |

| <b>μs</b>             | microsecond                                    |

# Chapter 1

## Introduction

Security is the major concern for Internet of Things (IoT) enabled devices and is a challenging area as it is mandatory to protect our privacy concerns from various security attacks. IoT [1] is one of the fast-growing technologies that has simplified our personal lives and brought easy exposure to the outside world. It is not only limited to our personal lives but also can be advantageous for our future industrial systems to control and access devices without human intervention. It has brought revolution across all computing application domains, such as home automation, wearable electronics, Artificial Intelligence (AI) enabled services, etc [1, 2]. On the other hand, IoT devices face many issues as they are susceptible to cyber-attacks and need many computational resources while consuming low power. For example, IoT devices frequently access the confidential information of the user with security attacks, which are performed by intruders from unauthorized resources. Nowadays, most of the IoT-enabled devices are equipped with Integrated circuits (ICs) to withstand malicious attacks.

ICs are witnessing great demand as they are being used to execute security-critical jobs and handle sensitive information in electronic gadgets [1]. So, secret keys are essential to identify and authenticate users in the development of the system's security. Many applications, such as intellectual property protection and software licensing, key cards to regulate access to restricted areas, smart card usage to perform financial transactions, and smartphones to store sensitive data of confidential papers, personal emails, etc., are emerging rapidly [3]. The protection of the secret keys is the main function of these applications enabling active logical controls to identify and authenticate users. However, malicious users can impersonate authorized users against various kinds of logical and

physical tampering attacks when the secret key is exposed. Therefore, a common element is required to enable the aforementioned security operations, which an attacker cannot access or replicate.

To authenticate a device and secure confidential information, the existing practice is to store a secret key in memory-based techniques like fuses, Electrically Erasable Programmable Read-Only Memory (EEPROM), and cryptographic mechanisms like digital signature and encryption. Eventually, responses (secret keys) are always retained in digital form in memory-based systems. As a result, robustness decreases and cost increases as non-volatile memory systems are frequently subjected to invasive attacks. Also, it is due to the usage of battery-backed Random Access Memory (RAM), where keys can be read afterwards and stored for a long period. A high level of security is achieved when the IC must be safeguarded with costly tamper-sensing circuitry that must be continuously powered by batteries.

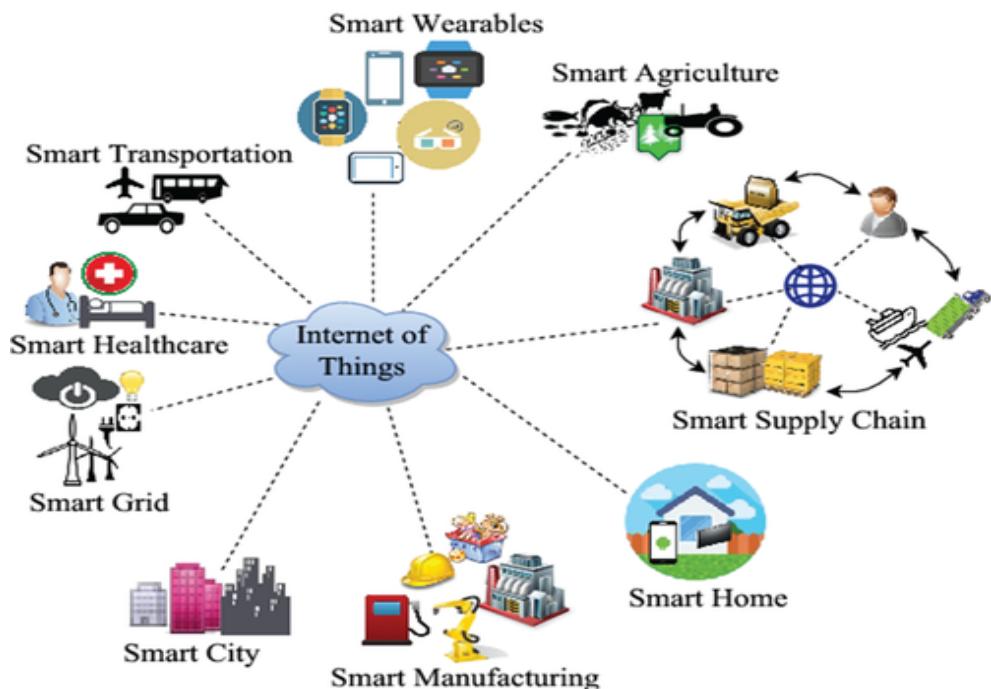

**Figure 1.1** IoT in the security domain [3]

## 1.1 Internet of Things (IoT)

IoT is a network of interconnected physical objects or "things" that are embedded with sensors, software, and other technologies to collect or exchange data with other devices/systems over the Internet [1]. As shown in Fig.1.1, IoT things might be any-

thing from commonplace like domestic appliances, automobiles, and wearable devices to industrial machinery and building materials. IoT has the potential to transform firms by facilitating more connectivity, automation, and data-driven decision-making [4]. The enormous amount of data generated by connected devices must be managed, and there are issues with data security, interoperability, and management. IoT is probably going to become a bigger part of how we connect with the physical world and the digital world advances in technology.

A PUF-based device authentication scheme PMSec [112] provides a mechanism that is appropriate for the Internet of Medical Things (IoMT). This authentication scheme's primary benefit is that no information about IoMT devices is kept in server memory. It took between 1.2 and 1.5 seconds to fully authenticate the devices. An Oscillator Arbiter Hybrid Physical Unclonable Function was employed to verify the suggested authentication method. Moreover, the device information is not kept in the server's memory, which is one benefit of this technique. Although each device has a PUF module that can be used for authentication, the server RAM does not save the challenge and response from the client PUF modules. This can assist in situations where the device information is not compromised and the attacker gains access to the hacked server.

## 1.2 IoT Cryptographic Primitives

IoT includes a wide range of internet-connected devices, including industrial sensors and smart thermostats. Since many IoT devices collect sensitive data or control crucial activities, their immense scale and diversity present several security challenges. Cryptography is one of the key principles of IoT security that deals with security issues associated with IoT-enabled devices. The building blocks for building secure protocols and security services are known as cryptographic IoT primitives [5] that are discussed in the following sections for the provision of IC security.

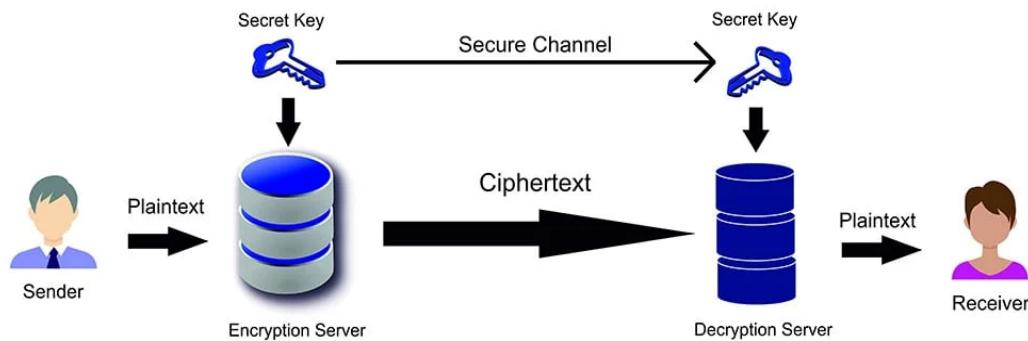

### 1.2.1 Symmetric Key cryptography

Symmetric key cryptography [5, 6] is a sort of encryption technique where the same key is used to both encrypt and decrypt messages as illustrated in Fig.1.2. In the past, secret communications between governments and militaries have been made possible in great part by using this method of data encoding. The symmetric key is also referred to

---

**Figure 1.2** Symmetric key cryptography [5,6]

as shared-key, secret-key, one-key, and eventually private-key cryptography. It is obvious that the shared key must be known by the sender and the recipient when using this type of cryptography. The distribution of the key presents a challenge with this method.

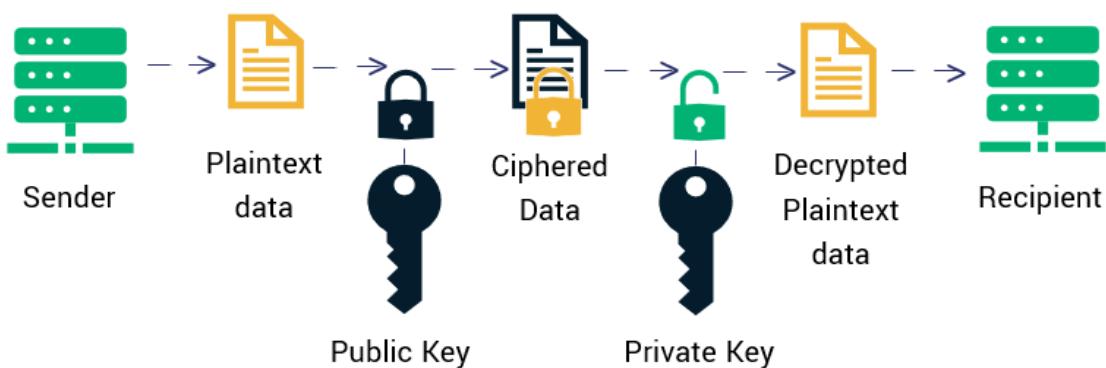

### 1.2.2 Asymmetric Key cryptography

A Public Key Infrastructure (PKI) [5, 6] is a cryptographic technique requiring two separate keys, one to lock or encrypt the plain text and another to unlock or decrypt the cipher text built on asymmetric keys. As represented in Fig.1.3 no key can perform both tasks. A private key is kept private, while a public key is made public. The technology enables private communication from the general public to the owner. The system functions as a signature verification for documents locked by the owner of the private key.

**Figure 1.3** Asymmetric key cryptography [5,6]

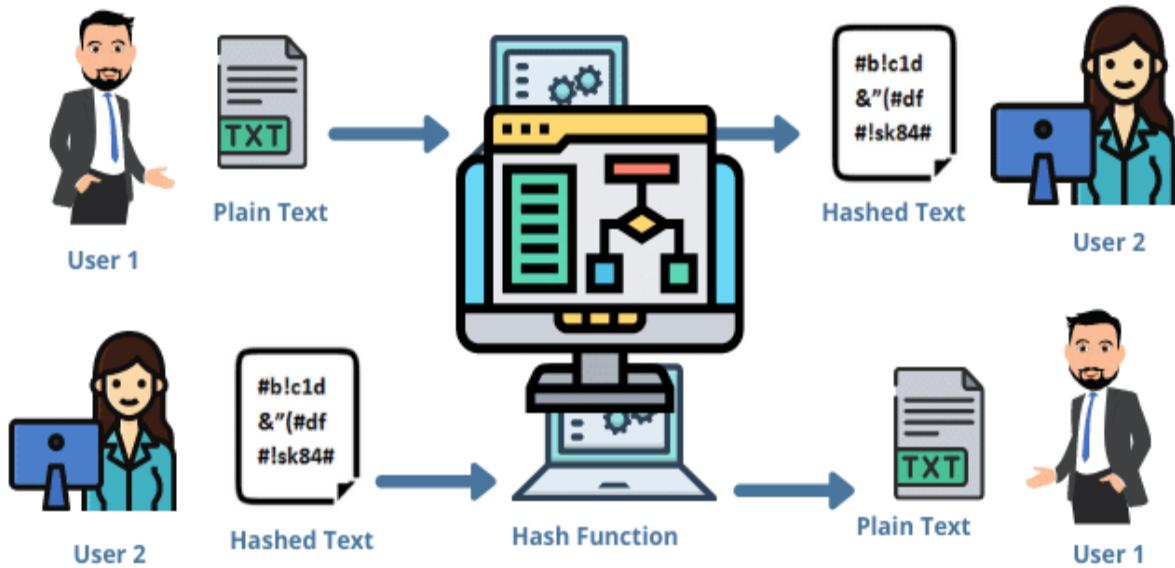

### 1.2.3 Hash functions

A mathematical operation employed in cryptography is known as a hash function [5, 6] is shown in Fig.1.4. Most hash functions accept inputs with varying lengths and outputs with fixed lengths. The message-passing abilities of hash functions are combined

with security features in a cryptographic hash function. Hash functions that "map" or transform a given data set into a fixed-length bit string known as the "hash value." The complexity and difficulty of hash functions, which are employed in cryptography, can vary. However, for the provision of security to the messages, passwords, and cryptocurrency, hash functions are the best choice to employ.

**Figure 1.4** Hash functions [5,6]

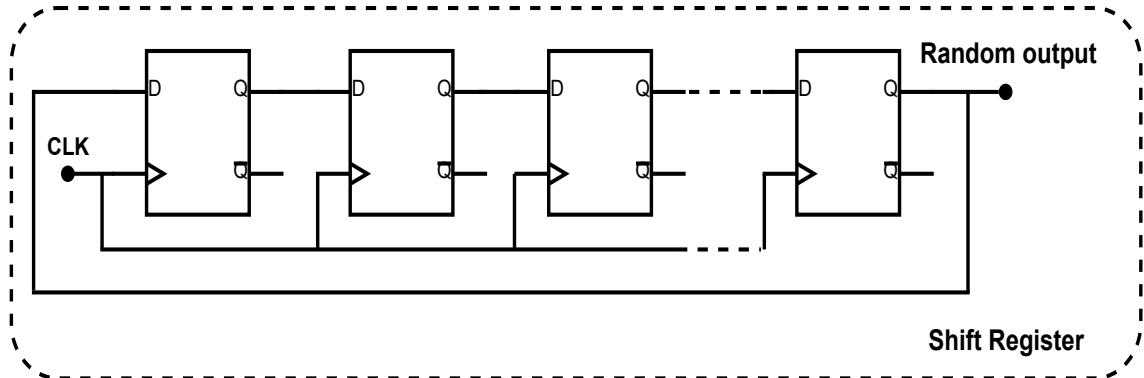

#### 1.2.4 Random Number Generators (RNGs)

Random numbers play a crucial role in cryptography applications due to their non-deterministic nature. Basically, RNGs or Random Bit Generators (RBGs) [7] shown in Fig.1.5 are preferred to generate random numbers or random bits to manipulate the system by foreseeing processes. Random numbers are essentially required in the following applications such as cashless payments, Automated Teller Machines (ATMs), online payments, e-banking, point of sale, prepaid cards, etc. In cryptography, the key protocols use random numbers to generate a secret key between the sender and receiver. Whereas, the presumption of the secret key will diminish the key rate when random numbers are generated by RBGs. A Pseudo-Random Number Generator (PRNG) [8] produces periodic or deterministic random numbers based on a mathematical formula, which is determined by the initial state called a seed. PRNGs form a strong correlation between 0's and 1's thereby increasing the cryptographic strength. In contrast to PRNGs, Hardware Random Number Generator (HRNG) [8] is proposed to generate random numbers through ran-

domness extracted from physical processes that make them a better candidate for secret key generation.

**Figure 1.5** Random Number Generator

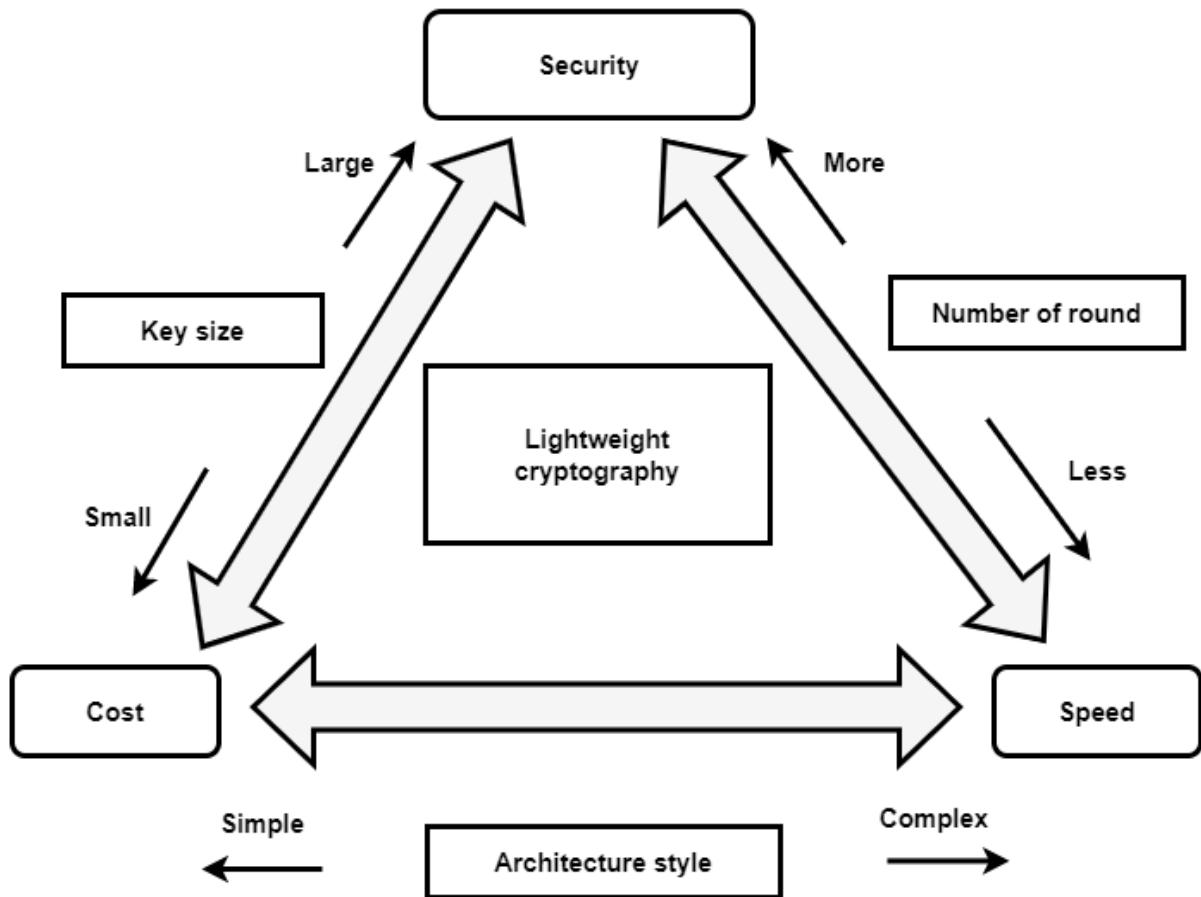

#### 1.2.5 Lightweight cryptography

Lightweight cryptography is an encryption method that features a small footprint and/or low computational complexity. It can be measured by the execution time and the number of calculations used to estimate processing speed. Moreover, it is aimed at expanding the applications of cryptography to constrained devices [9] based on international standardization and guidelines. For the implementation of lightweight cryptography, factors like circuit size (or memory size), power consumption, and processing delay (delay, throughput) should be considered. The respective cycle of lightweight cryptography is represented in Fig.1.6.

Generally, the size is the major factor that determines whether a design can be implemented in a certain device or not. Whereas power consumption is crucial for battery-powered devices, power is particularly important for devices like Radio Frequency Identification (RFID) and energy harvesting systems. A low delay is crucial for the real-time control processing of control-based systems but a high throughput is required for devices with significant data transmissions, such as a camera or a vibration sensor.

#### 1.2.6 Cryptographic Algorithms

The mathematical processes incorporated in cryptographic algorithms [6,9] protect the sensible data of the user. These methods convert plain text (readable data) into cipher text (unreadable data), and vice versa. They are essential in maintaining the privacy, accuracy, and integrity of data. It is critical to take into account the unique

**Figure 1.6** Lightweight cryptography [9]

security concerns, performance constraints, and eventual shortcomings while selecting a cryptographic algorithm. The accurate implementation of the algorithms can be ensured by well-tested and well-known cryptographic libraries that are equipped in crypto ICs to execute challenges or keys. Even though they are accurate but are not reliable due to the Process Variations (PVs) existing in the ICs that are discussed in the following section.

### 1.3 Process Variations (PVs)

Individual chips can differ in performance and behaviour due to variations in ICs, which can come from a variety of sources. PVs [10] are the variabilities in circuits, such as Random Dopant Fluctuations (RDFs) and process control limitations, that are challenging for any technology nodes. Additionally, there is a mismatch between the sizes set up during design and the sizes achieved during manufacture due to process variances. For instance, with a 65 nm CMOS process technology node, it is anticipated that the differences in a MOSFET's threshold voltage and channel length can reach up

to 30% [107]. PVs affect the performance of circuit operation at the gate level even though the circuits are designed with identically sized gates. The design's functionality is impacted by process variances. The ability to convey current and delay can be impacted by changes in the channel length. Leakage and delay below the threshold can be impacted by changes in the threshold voltage. Variations in the process can alter the circuit and system parameters from the design specification, which could impact the yield [107].

As the technology scales down the performance and speed of the ICs may increase but result in PVs. Due to PVs, delay variations occurred and affected the frequency performance of the design and yield. This can be stated as how many chips can perform within the target frequency after fabrication. To create reliable circuits and systems with the highest possible yield and lowest possible cost, variability-tolerant design is required. To create a chip that can withstand process variations, it is crucial to include variability awareness in the early design cycles. The common PVs are,

- **Intrinsic material variability:** The characteristics of transistors and the behaviour of the entire circuit can be impacted by variations in material qualities at the atomic level.

- **Dopant fluctuations:** Transistor performance can be affected by the precise location and concentration of dopant particles during manufacture.

- **Oxide thickness:** Oxide thickness variations can affect the threshold voltage and other properties of transistors.

- **Lithography and etching:** Critical dimensions and forms of circuit elements may deviate due to variations in photolithography and etching procedures.

Possibly, either static or dynamic fluctuations in the parameter may occur [107]. Variations in the manufacturing process are the source of the static parameter variations. On the other hand, changes in workload and environmental circumstances cause dynamic parameter variations to occur over time as the circuit and system operate. There are numerous potential sources from which the process deviations can arise. Process changes can therefore be at the wafer, reticle, or local levels, and they have fairly distinct characteristics.

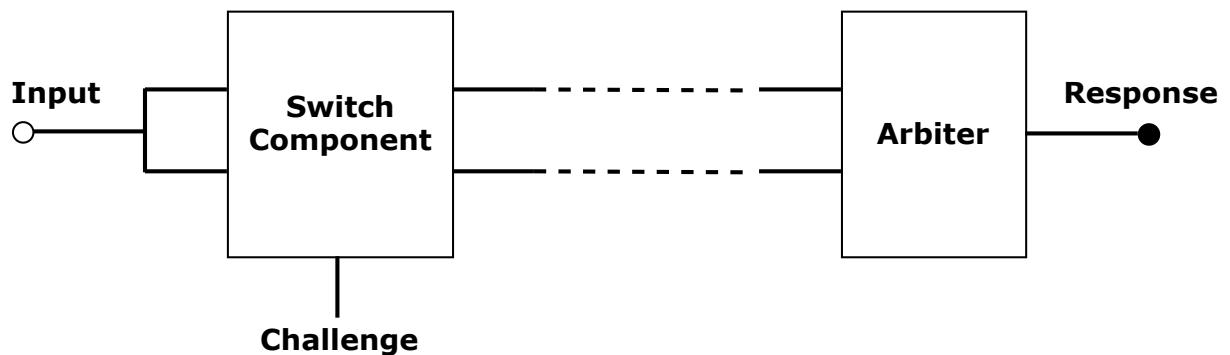

A novel hardware-intrinsic security mechanism, Physical Unclonable Function (PUF) [11] came into existence to utilize PVs in a proper way that is inexpensive, unique, and

---

secured. Also, it provides reliable solutions for security issues faced by IoT devices. The PVs observed in PUF could generate unique signatures as identifications when random challenges are fed during runtime. These PVs can be a bit higher than the physical variations. Also, they are considered major side effects that occur during the manufacturing process, so circuits can be defective. Fortunately, APUF can withstand PVs since its responses depend on the difference in delays between two adjacent paths, which are fed as input to the Switch Component (SC). Due to PVs, some challenges may affect the arbiter latch with setup time violation, which leads to an unpredicted response, thus resulting in the poor reliability of the PUF. Therefore, to make the conventional logic systems unique and unclonable, their design has to be variability-aware in the implementation of PUF.

### 1.3.1 Sources of variances in ICs

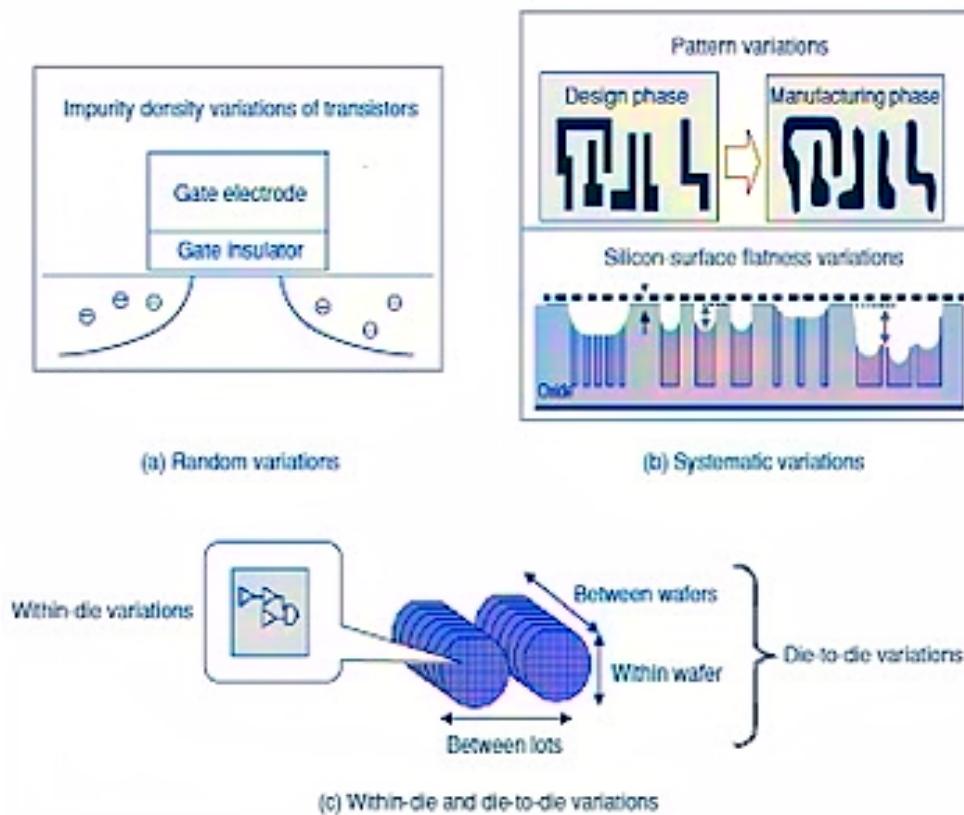

The PVs [10] can be classified into two categories: systematic variations and random variations. Random variations are intrinsically unpredictable, whereas systematic variations are deterministic and can be predicted or controlled. The common sources of variations shown in Fig.1.7 are discussed below.

**Figure 1.7** Sources of variances in ICs [10]

### 1.3.1.1 Layout and design variations

- Layout-Dependent Effects: Due to proximity effects, optical diffraction, and other considerations, the physical architecture of transistors and interconnects can affect performance.

- Parasitic Capacitance and Resistance: Circuit timing and signal integrity can be affected by parasitic components such as capacitance and resistance that can vary depending on the arrangement.

### 1.3.1.2 Thermal Variations

- Thermal Gradients: The performance of a circuit can change as a result of variances in transistor properties caused by temperature differences across the semiconductor.

### 1.3.1.3 Voltage and Bias Variations

- Supply voltage variation: Circuit speed, power consumption, and noise margin may be impacted by changes in the power supply voltage.

- Threshold voltage variation: The switching behaviour of digital circuits is impacted by changes in transistor threshold voltage brought on by manufacturing and bias variations.

### 1.3.1.4 Random Variations

- Statistical variability: Statistics-based fluctuations in parameters like carrier concentration and channel length are caused by quantum mechanical phenomena.

- Thermal Noise: It results from random electron migration owing to temperature, and reduces the precision of analog circuits.

- Random Telegraph Noise: Over time, random changes in transistor properties may be the result of discrete trapping and untrapping of charge carriers.

### 1.3.1.5 Aging and Wear

- Electromigration and Stress Migration: Circuit reliability and performance may be impacted over time by changes in the characteristics of metal conductors brought on by electromigration and stress-induced effects.

- Negative Bias Thermal Instability (NBTI) and Positive Bias Thermal Instability (PBTI): Due to continuous exposure to bias conditions, these effects gradually produce threshold voltage alterations in transistors.

- Hot Carrier Injection (HCI): It describes the process by which high-energy electrons (also known as "hot carriers") acquire sufficient energy to go past potential obstacles in a transistor's gate oxide or junction, eventually causing device degradation or failure. MOS transistors, which are frequently employed in ICs, are particularly pertinent to this variation.

It is essential that the variances must be minimized to maximize the performance of the ICs. Process control, redundant circuit design, statistical analysis, and error-correcting mechanisms are only a few of the methods used to lessen the effects of variances. However, innovative manufacturing techniques like adaptive lithography and process compensation are used to overcome variances that may improve chip yield and quality.

## 1.4 Physical cryptographic primitives

Cryptographic operations that rely on the physical characteristics of objects or systems are known as physical cryptographic primitives. They take advantage of PUFs [11] or other hardware-based properties, as opposed to conventional cryptographic primitives, which are based on mathematical techniques. These are especially important for hardware security in situations when software-based techniques can be ineffective or inappropriate.

### 1.4.1 Physical Unclonable Functions (PUFs)

PUFs can extract a response from hidden timing or delay that occurred due to inherent manufacturing variations and could replace digital memories for storing keys. Moreover, these circuit delays produce a volatile response (key) that is perhaps difficult to expect or extract. Even though a PUF key is implemented on an IC, it is being cloned to access physically using different attacks. Modern cryptographic algorithms provide security to IoT devices but are unable to counterfeit since the security blocks are designed with cryptographic hash functions (implemented by mathematical and algorithmic mechanisms). So, when cyber-attacks happen, they fail to provide secure communication among IoT devices. In fact, it is a tedious task to build security functions for inexpensive

---

sive IoT devices. Generally, PUF is not only to protect hardware components i.e. ICs sourced from manufacturers but also handles serious reliability implications. An on-chip PUF is a Challenge-Response (CR) based hardware function and exploits the inherent random physical variations in the manufacturing process. The physical variations of

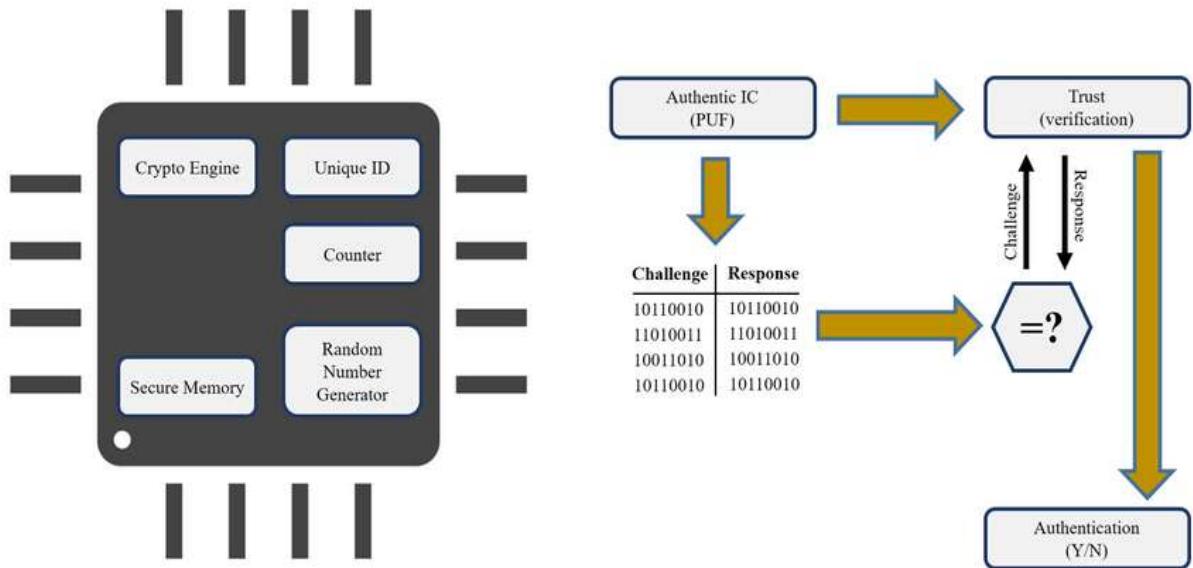

**Figure 1.8** Physical Unclonable Function [12]

PUF are determined by deep sub-micrometre level variations, which are produced due to uncontrollable deviations in the manufacturing process [12]. These variations are complex and random in nature making PUF very hard to be cloned. Hence, they are tamper-resistant against attacks. The extracted instance-specific keys from hardware components, which are hard to predict, are unique and unclonable to identify or authenticate each device [12, 13]. A PUF shown in Fig.1.8 can efficiently improve the device's resistance to various attacks when an on-demand generation of random keys from a CR-based scheme exists. Moreover, it ensures that there is no storing of keys in non-volatile memory during deployment.

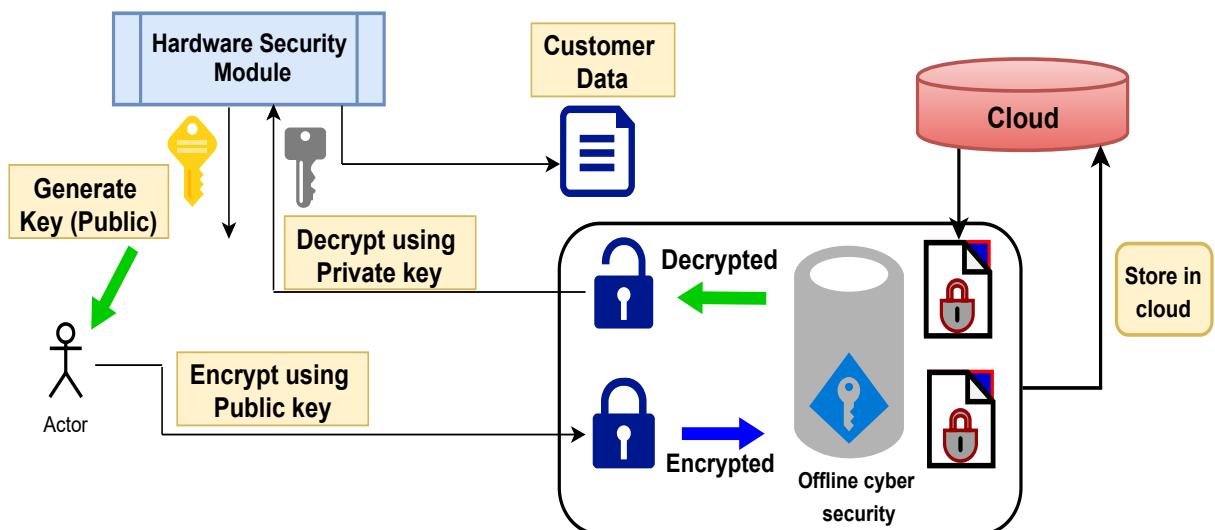

### 1.4.2 Hardware Security Module (HSM)

A Hardware Security Module (HSM) is a specialized crypto processor created with the goal of safeguarding the crypto key lifecycle. It adds additional security for sensitive data by safely managing, processing, and storing cryptographic keys inside a hardened, tamper-resistant device. HSMs illustrated in Fig.1.9 are employed to provide cryptographic keys [14] for crucial operations like encryption, decryption, and authentication for the use of applications, identities, databases etc. However, HSMs serve as trust anchors that safeguard the cryptographic infrastructure of some of the most security-conscious operations in the world.

Figure 1.9 Hardware Security Module [14]

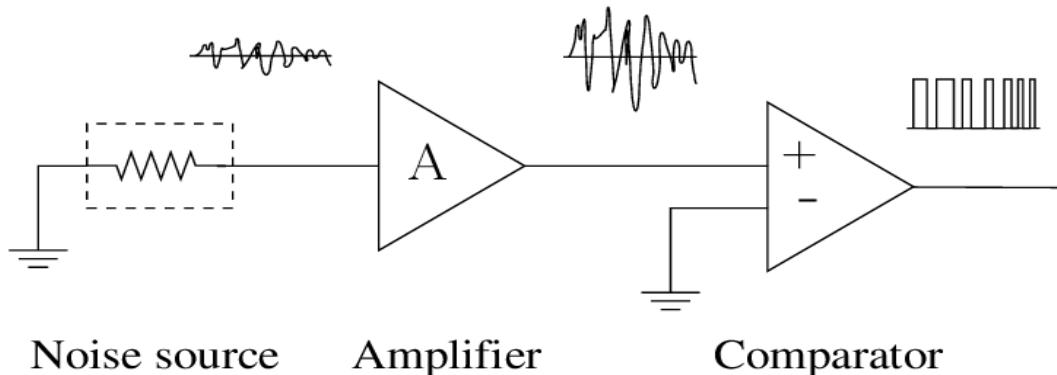

### 1.4.3 True Random Number Generators (TRNGs)

The generation of random numbers is crucial for high-speed processing at the core part of data encryption systems. These systems rely on fast RNGs for stochastic modeling, Monte Carlo simulations, etc [15]. The source of randomness is uncertain in a TRNG [16] that is typically accomplished by hardware. TRNG shown in Fig.1.10 is based on a physical source which makes it difficult to anticipate a random value, so the random number it generates is difficult to predict. In view of the complexity involved in creating an equal value, the random number generated by the TRNG is a secure method. The output of a TRNG may be biased in some way, such as having more ones than zeros or vice versa. There are several ways to alter a bit stream in order to lessen or eliminate bias. However, the bit stream can be generated through “de-skewing algorithms” which

**Figure 1.10** True Random Number Generator [16]

run through a hash function. The hash function converts an input of any length into an  $n$ -bit result. The hash function can acknowledge blocks of  $m$  input bits with  $m \times n$  for de-skewing. TRNG is too repetitive, and there are several complex PRNGs [17] available. TRNGs can take advantage of both physical and intangible noise sources represented in Fig.1.10. Generally, the following physical phenomena are used to generate random numbers in logic devices.

- Clock Jitter: The clock edge is changed from its optimal position.

- Metastability: A circuit has the power to remain in an infinite state for an arbitrary amount of time.

- Chaos: It is the unpredictability of a system that is deterministic and highly responsive to its initial conditions.

- Analog signals: The noise present in thermal noise, and other types of noise are present in analog signals.

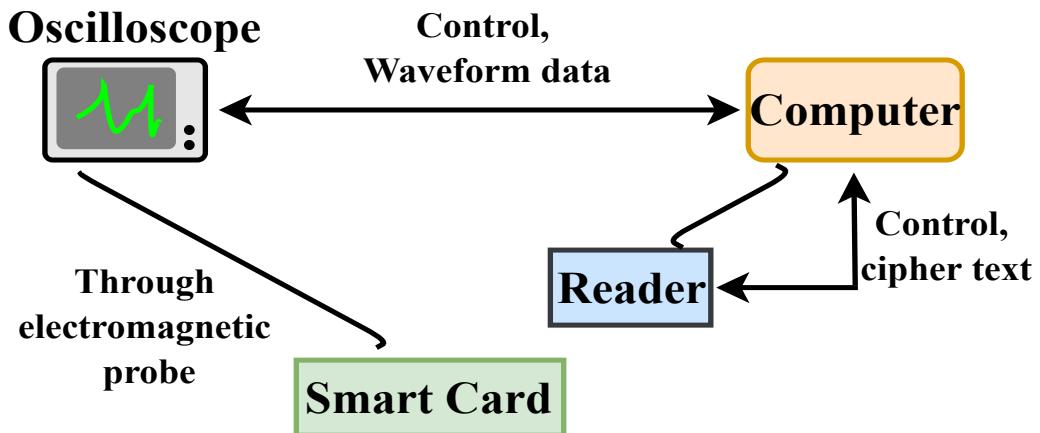

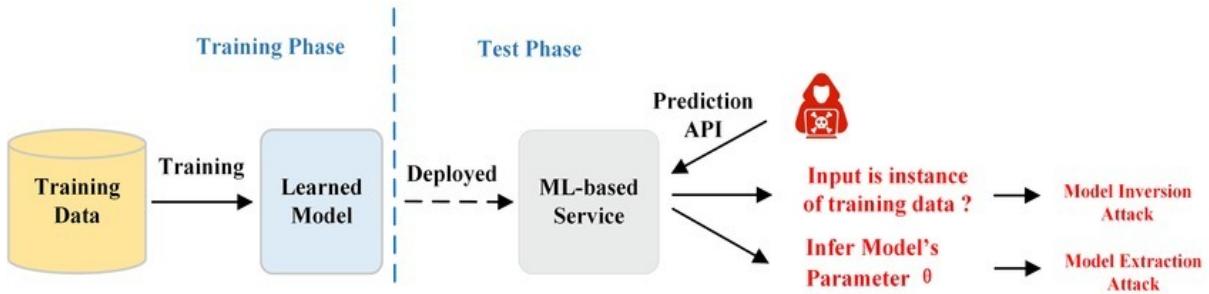

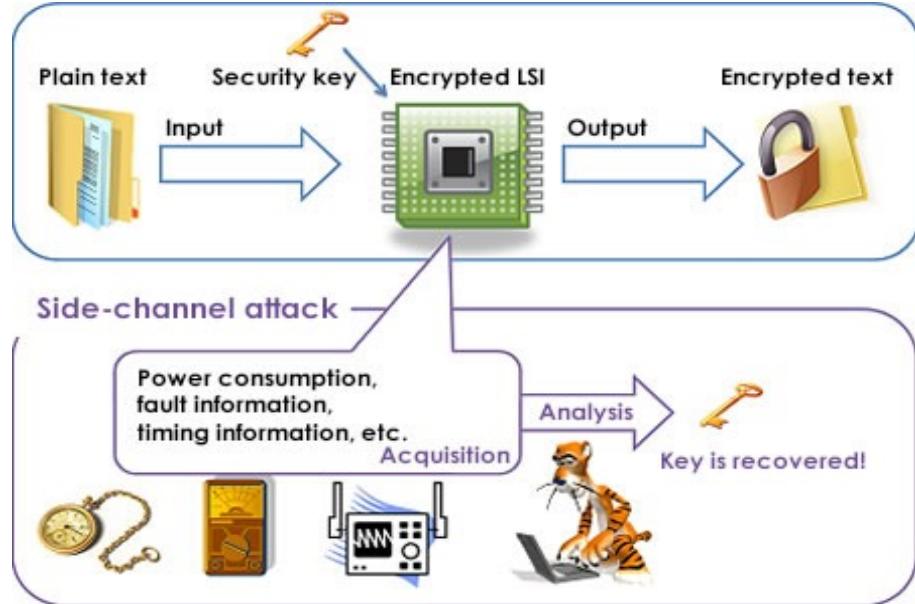

#### 1.4.4 Side-channel analysis (SCA)

Side-channel analysis (SCA) [18] refers to a variety of techniques for taking advantage of inadvertent information leakage from a device's process (such as a computer program or application). Every device leaks some sort of side-channel information for each instruction, piece of processed data, or input to the device, whether it is a restricted IoT device, a smartphone, a laptop, or a supercomputer with hundreds of CPU cores. The side channels shown in Fig.1.11 have happened in distinct forms of physical characteristics like power usage or electromagnetic emissions and logical characteristics like processing speed or memory access patterns. An attacker may be able to observe the

variation in side-channel emissions that relate to internal activities by deducing both the operations carried out and the data processed by the device. Moreover, it is possible to extract secret data, such as a cryptographic key, by observing and categorizing data-dependent side-channel emissions, or side-channel leaks when the hidden data's content directly influences it. Instead of taking advantage of software flaws or algorithmic weak-

**Figure 1.11** Side channel attack materials [18]

nesses, side-channel attacks concentrate on gathering information from a system's physical implementation. It is possible to determine the actions taking place inside a device and, in some situations, recover encryption keys or other sensitive data by examining power consumption patterns. The general approach to extracting binary information from power traces is,

- Utilize statistical techniques to associate particular patterns of power usage with binary operations when there are enough traces and an understanding of the patterns.

- Extract specific pieces of information, such as encryption keys, advanced approaches can be used, such as Differential Power Analysis (DPA) or Correlation Power Analysis (CPA).

The first-ever hardware-assisted blockchain for simultaneously handling device and data security in smart healthcare. This article [113] presents the hardware security primitive PUF and blockchain technology together as PUFchain 2.0 with a two-level authentication mechanism. The proposed PUFchain 2.0 [113] security primitive presents a scalable approach by allowing Internet of Medical Things (IoMT) devices to connect and obtain

PUF keys from the edge server with an embedded PUF module instead of connecting a PUF module to each device. Blockchain is a decentralized, unchangeable transaction record that is kept on file at every network node. A system of consensus is a standard protocol that is used to validate and add transactions between any two nodes in the network to the chain. The implementation and outcomes have demonstrated that the combination of PUF and blockchain technology [113] can provide safe, intelligent healthcare. Every security protocol now in use for smart healthcare is centred around either blockchain-based data security or hardware-assisted security. To provide security for IoMT device authentication and data integrity guarantees through a two-level authentication protocol, this article [113] suggested and implemented the PUFchain 2.0 primitive, which combines Blockchain with PUF.

## 1.5 Motivation

The generation and protection of the secret keys, which are the main function of security applications, enable active logical controls to identify and authenticate users. However, malicious users can impersonate authorized users against various kinds of logical and physical tampering attacks when the secret key is exposed. Therefore, a common element is required to enable the aforementioned security operations, which an attacker cannot access or replicate. To authenticate a device and secure confidential information, the existing practice is to store a secret key using memory-based means fuses and Electrically Erasable Programmable Read- Only Memory (EEPROM) and using cryptographic mechanisms like digital signature and encryption.

The digital algorithms [6] manage the security attacks with cryptographic algorithms e.g. Advanced Encryption Standard (AES), Data Encryption Standard (DES), and Message Digest (MD). However, digital platforms produce a key generation with hash functions (implemented by mathematical algorithms and cryptographic algorithms) that are able to make secure and counterfeit to some extent. So, PUFs are considered the more secure designs in IoT security because of their unpredictable nature. PUFs don't need any memory function to store the keys because they produce on-demand key generation for identification and authentication. The major issues observed in hardware security are,

---

- Persistent security threat in the digital domain

- Privacy inefficiency in IoT-constrained devices

- Lack of implementing AI development in the analog environment

- On-chip encryption has high memory overhead which is not practical for constrained IoT nodes

- Need to analyze a device for security purposes i.e. ensuring it's resistant to side-channel attacks

- Necessity of improvement in the resilience of PUF systems

## 1.6 Problem Statement

Generally, responses (secret keys) are always retained in digital form in memory-based systems. As a result, robustness decreases and cost increases as non-volatile memory systems are frequently subjected to invasive attacks. Also, it is due to the usage of battery-backed RAMs, where keys can be read afterwards and stored for a long period. A high level of security is achieved when the IC must be safeguarded with costly tamper-sensing circuitry that must be continuously powered by batteries. In the replacement of digital memories for storing keys, PUFs are used to extract a response from hidden timing or delay that may result due to inherent manufacturing variations [10]. Moreover, these circuit delays produce a volatile response (key) that is perhaps difficult to expect or extract [12, 13]. The provision of security to constrained IoT-enabled devices helps the user to protect themselves from exposing valuable information. The issues summed up regarding the provision of security to the ICs are,

- Avoid exploiting the secret information from authorized devices.

- Provision of security to the ICs against unauthorized attacks

- Provision of on-demand key generation with enhanced reliability

- Memory-less maintenance at endpoint devices.

## 1.7 Research Objectives

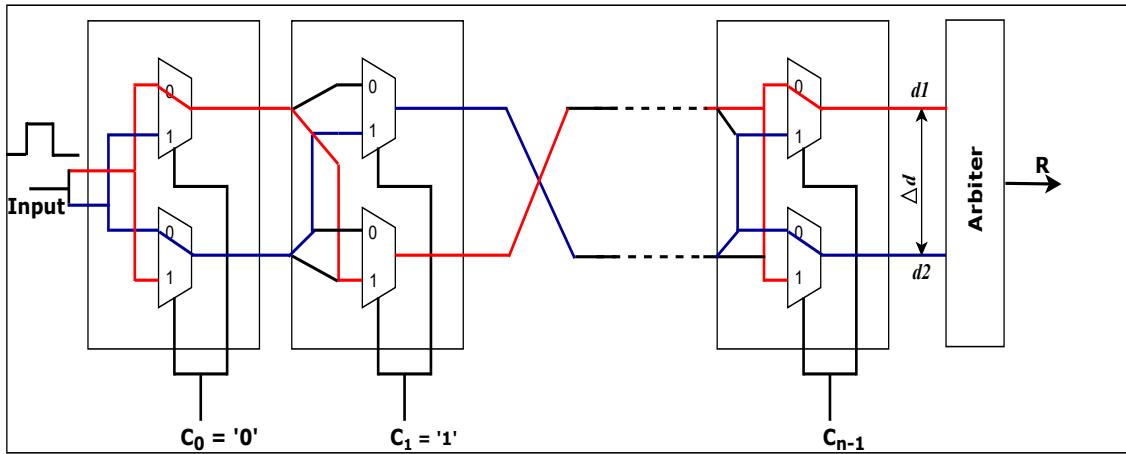

An arbiter-based scheme generates digital information from the PUF responses through the absolute delay values of two identical delay paths and evaluates the identification capability, authenticity, and security. The proposed architectures improve the reliability of arbiter-based PUFs against various malicious attacks by adding impulsive non-linearity. The issues related to the provision of security using PUFs are addressed by following the objectives mentioned below.

- Designing efficient PUF topologies to enhance the identification or authentication of ICs.

- Implementing arbitrary delays to produce uncertainty in the switching operations

- Design low-frequency PUFs suitable to IoT sensors

- Evaluate the reliability of PUFs from security analysis

- Introduce power management circuits to feed PUFs for the challenge generation

- Adding random noise or purposefully changing the power consumption to conceal sensitive activities

- Apply machine learning algorithms to evaluate the PUFs against sophisticated attacks.

## 1.8 Thesis Contributions

- 1. XoR Feed Arbiter Physical Unclonable Function (XFAPUF) for reliable key generation in IoT security:** Introduced feed-forward mechanism to attain non-linearity in the arbitration process to reduce manual feeding of the challenges. Thereby, prominent randomness is achieved that can be measured in terms of unpredictability.

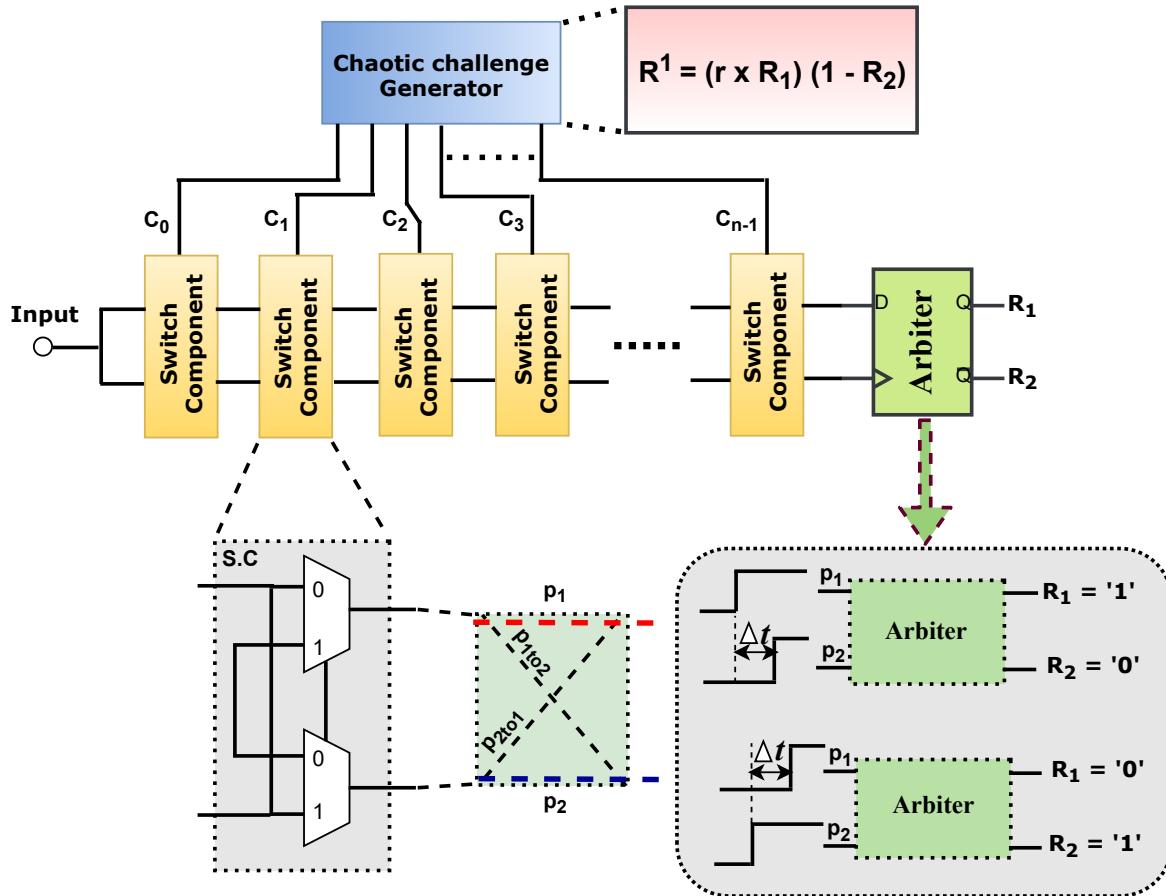

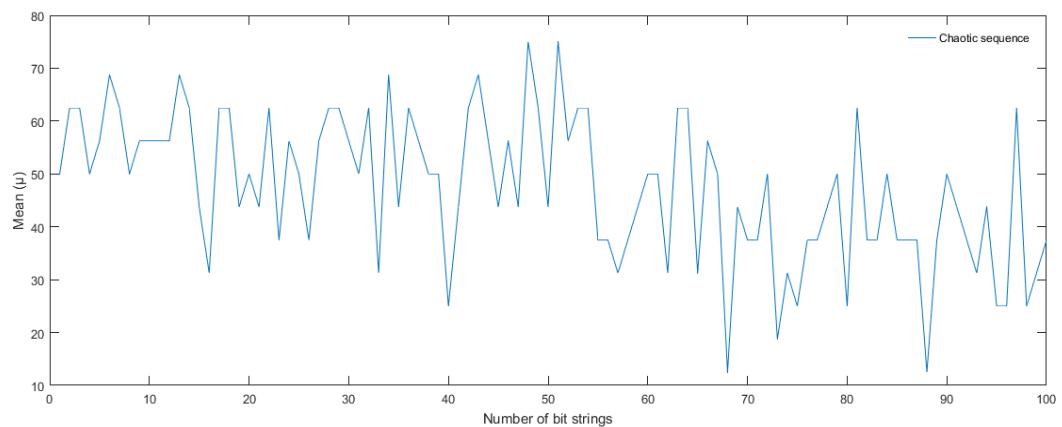

- 2. The Chaotic-based Challenge Feed Mechanism for Arbiter PUFs with enhanced reliability:** Introduced chaotic function in the challenge generation to attain non-linearity in the arbitration process. Whereas the challenge generation is from the Chaotic Code Generator (CCG).

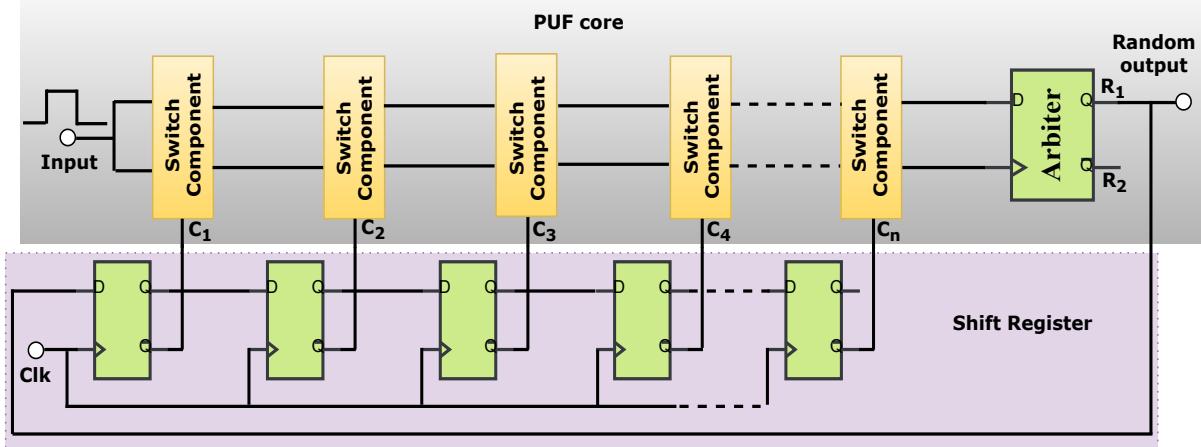

**3. Recursive Challenge Feed Arbiter PUF (RC-FAPUF) for Key Generation:**

Introduced automated challenge generation mechanism through XoR gates between switch components, which are used for the arbitration process. Thereby, a high randomness is achieved to enhance the reliability.

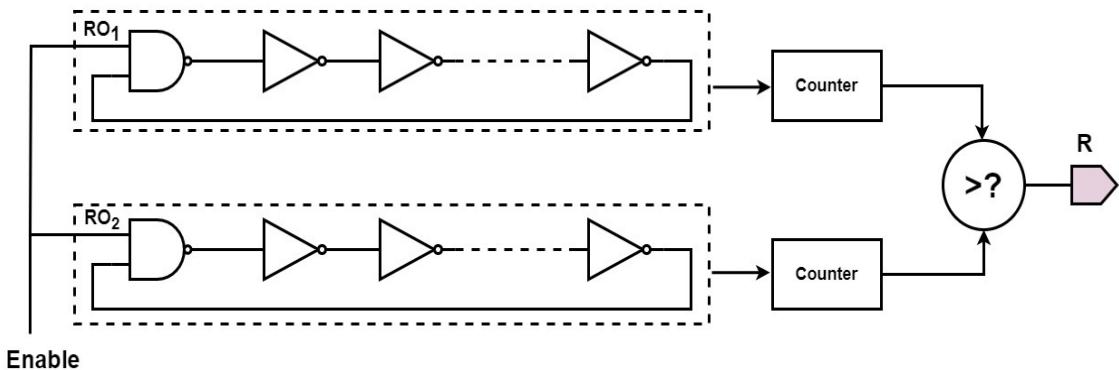

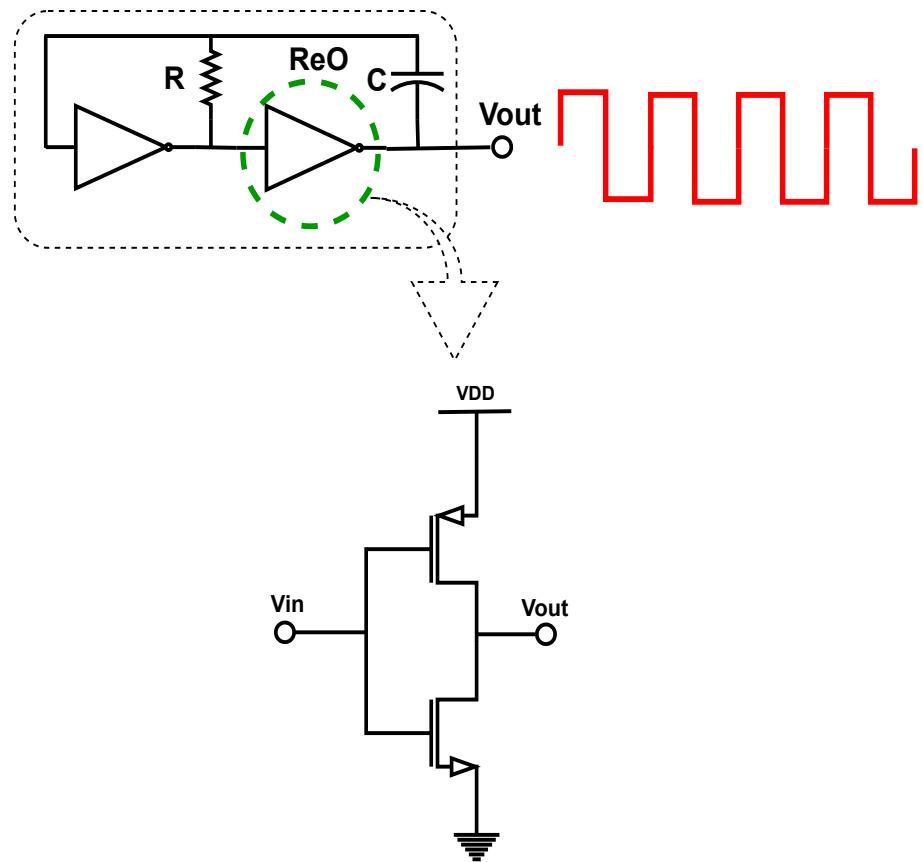

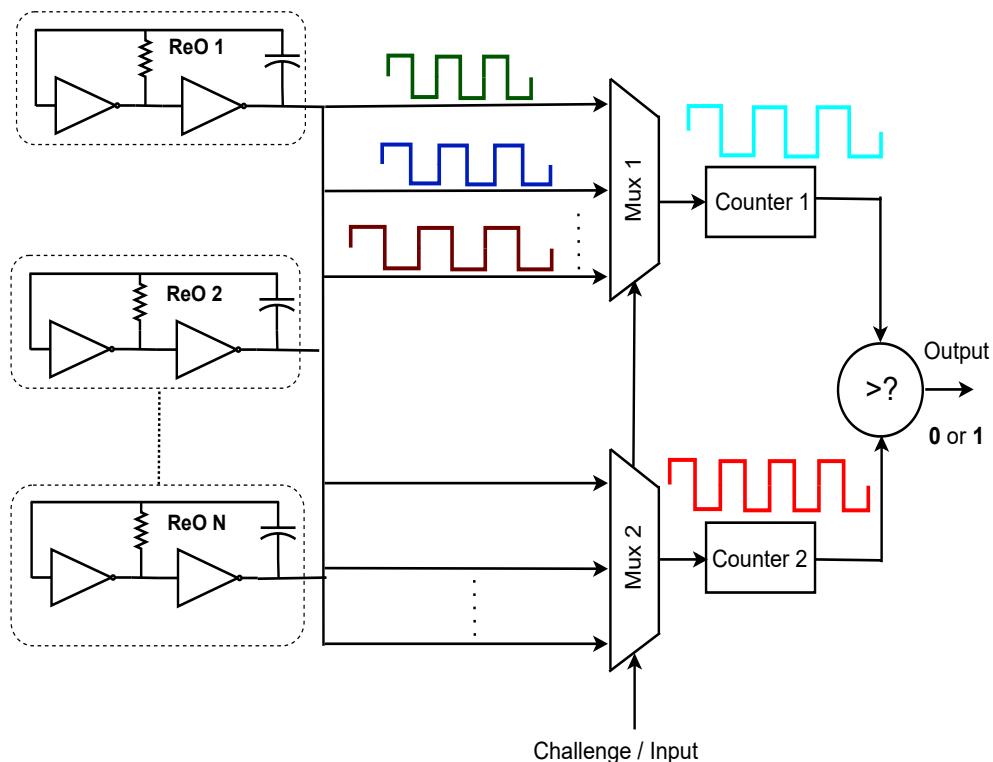

**4. ReOPUF: Design of Relaxation Oscillator Physical Unclonable Function for Identification Applications:**

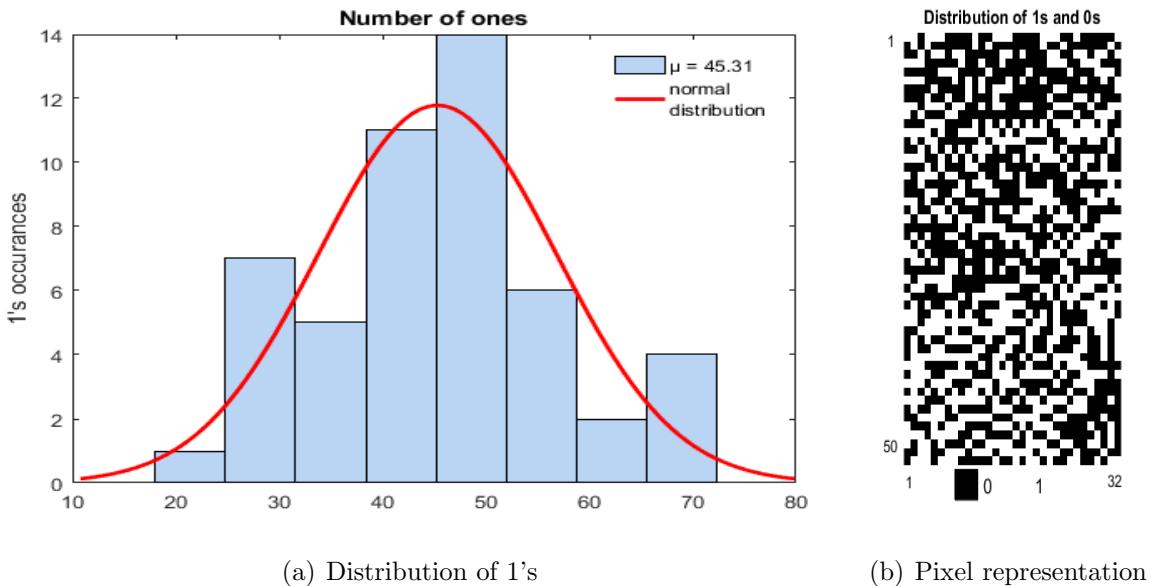

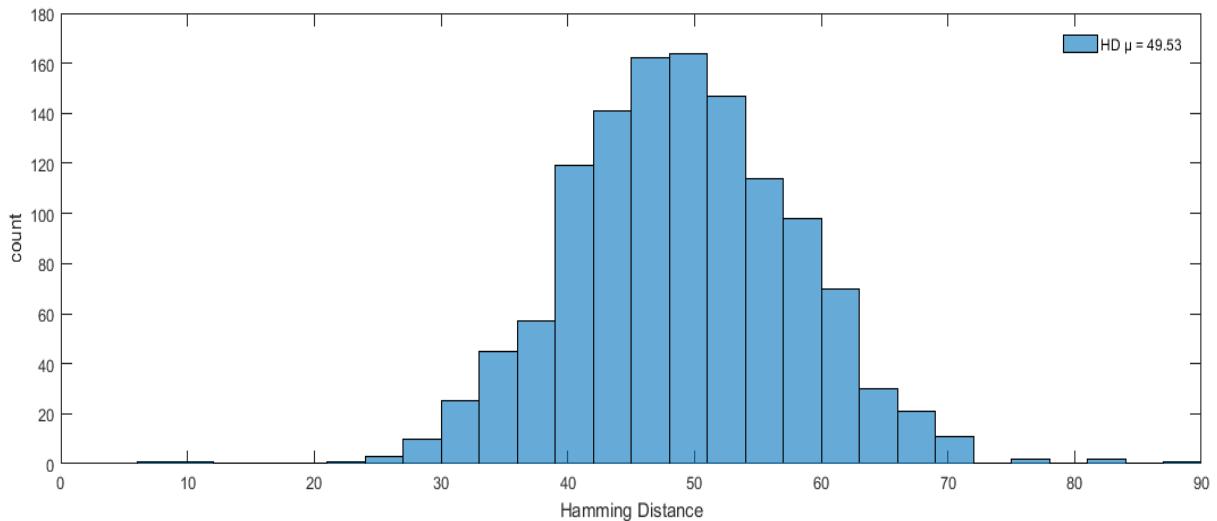

Generated required frequency for IoT nodes with Relaxation Oscillator and attained more reliability. It is the replacement for RO PUF and is claimed that more reliable and power-efficient.

**5. Schmitt Trigger Arbiter PUF (ST-APUF) with enhanced Uniqueness and Reliability in IoT security:**

Introduced arbitration between STs to attain the non-linearity using Hysteresis Width (HW) variation. Based on the HW differences it is claimed that the high uniqueness and randomness.

**6. Low Dropout Regulator (LDO) based challenge generation mechanism:**

Designed to feed ReOPUFs and STPUFs to augment the randomness in challenges. Thereby, the reliability is achieved by the challenges generated through the power traces that occurred from LDO in terms of undershoot and overshoot.

## 1.9 Thesis Organization

**Chapter 1:** Contributes an introduction to the PUFs, Motivation, Objectives, and Thesis organization.

**Chapter 2:** Imparts literature survey corresponding to the related works and basic implementations of arbiter PUFs.

**Chapter 3:** Provides design and implementation of XFAPUF for key generation along with automated challenge generation through Chaos-PUF.

**Chapter 4:** Presents design and implementation of RC-FAPUF for a reliable key generation. without any external feed from the user

**Chapter 5:** Provides design and implementation of ReOPUF to power up IoT sensors.

**Chapter 6:** Ensues design and implementation of ST-APUF for enhancement in reliability.

---

**Chapter 7:** Augments the randomness by incorporating LDO as a key generation mechanism.

**Chapter 8:** Gives the conclusion for the proposed PUF designs and the Future scope will give the enhancements and possibilities to strengthen PUF designs.

The contributions of the aforementioned chapters will convey information about the design of various security mechanisms for key generation, supportive challenge feed mechanisms, and performance evaluation through PUF metrics. The following chapter will introduce the basic background of PUFs and their mechanism in the application of IoT. Subsequently, various PUFs will be discussed along with the inclusion of different types of attacks.

# Chapter 2

## Physical Unclonable Functions (PUFs)

PUFs are a family of security components that use the distinctive physical properties of semiconductor devices to provide random and unrepeatable digital identifiers or keys. PUFs are used in a variety of applications, such as device anti-counterfeiting, secure key generation, and authentication, to improve security. In recent years, different architectures in the Complementary Metal Oxide Semiconductor (CMOS) level for PUFs have been proposed by researchers for IC-level security. Among them, Arbiter PUF [11–15] is the conventional delay-based approach realized between two symmetrical engaged paths that provide efficient Challenge–Response Pair (CRP) space for device identification and authentication. PUFs have drawn interest because of their capacity to offer reliable, hardware-based cryptography solutions. They provide a mechanism to produce secrets that are firmly connected to the unique physical characteristics of particular chips, making it challenging for attackers to reverse-engineer or clone equipment.

### 2.1 Concept of PUF in IoT device

With the increasing demands of security, key generation and device authentication become the most challenging design concerns, particularly in developing security for IoT-enabled devices. Traditional security mechanisms suffer from power limits, and store keys in erasable programmable memories. To implement encryption and authentication, the tamper-resistant devices are equipped with countermeasures that are developed to defeat different kinds of physical attacks. However, resources like memory, Central Processing Unit (CPU) and limited battery power are not affordable to implement security using classic cryptographic solutions. Therefore, PUF has become a relatively simple and

fast solution for security. PUFs are promising secure hardware primitives that produce device-dependent CRPs [19–21] based on unclonable properties and provide reliable key generation. The keys generated by PUFs are more resilient to malicious attacks from physical tampering attempted by the intruders. Fig.2.1 shows the security concept of IoT-enabled devices.

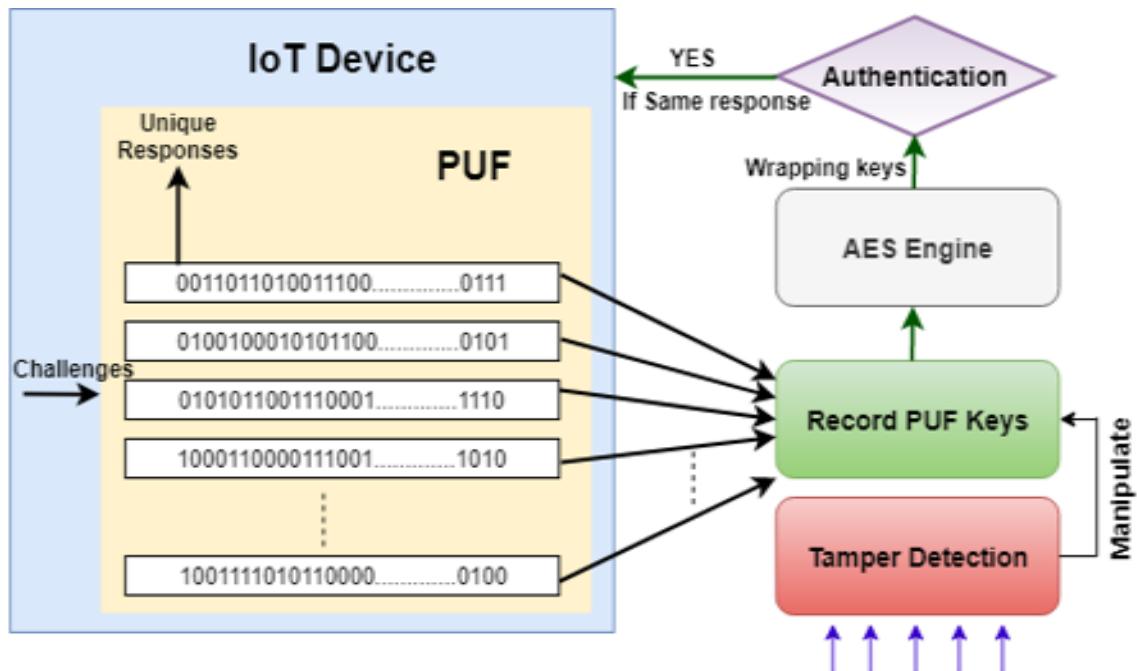

**Figure 2.1** PUF in IoT device

An IoT device equipped with PUF generates unique IDs as PUF keys and is shared through a gateway with the cloud. PUF keys are acquired by the Advanced Encryption Standard (AES) engine which is situated in the cloud and can convert plain text to cipher text. Thus, the IoT device is to be identified and authorized with encryption. For example, an IoT-enabled sensor node is arranged in the field to sense the temperature or moisture data continuously from the atmosphere and upload the data to the cloud at every predefined interval of time. This stipulated data could be protected in the cloud by adding PUF keys generated from the designed PUF and correlated with the AES engine can produce encrypted data. While tampering is detected in the node or cloud, there is the chance that data manipulation is possible by intruders. So, an efficient security mechanism i.e. PUF with high uniqueness and reliability is to be deployed to identify or authenticate the sensor node.

Based on the fabrication, the PUFs fall into the categories of silicon and non-silicon

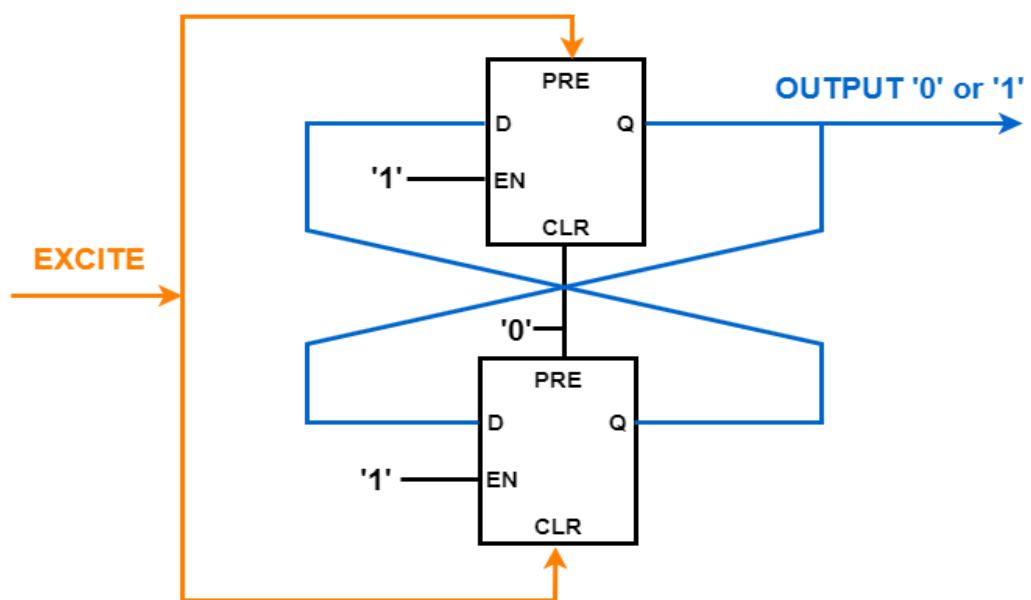

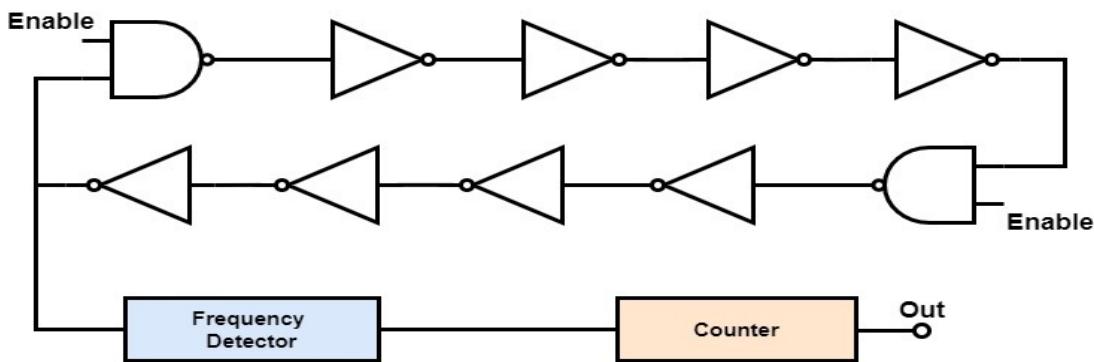

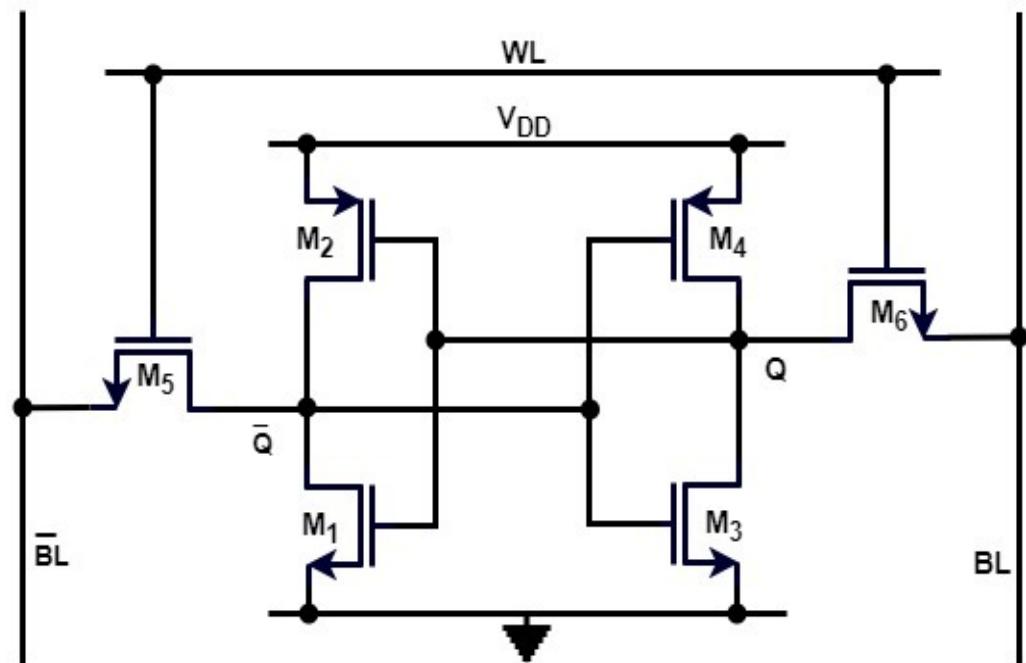

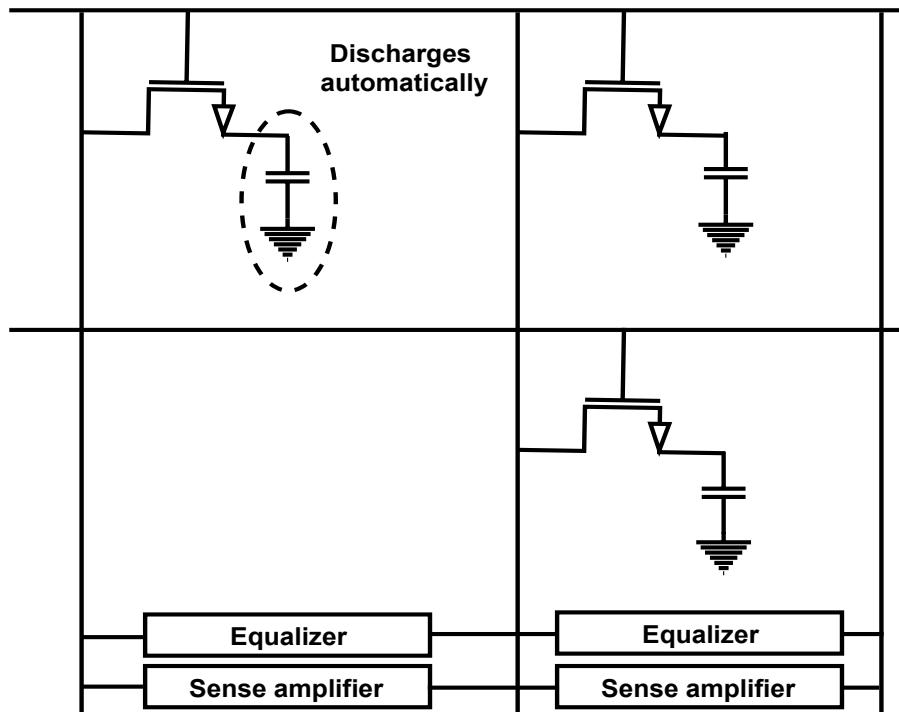

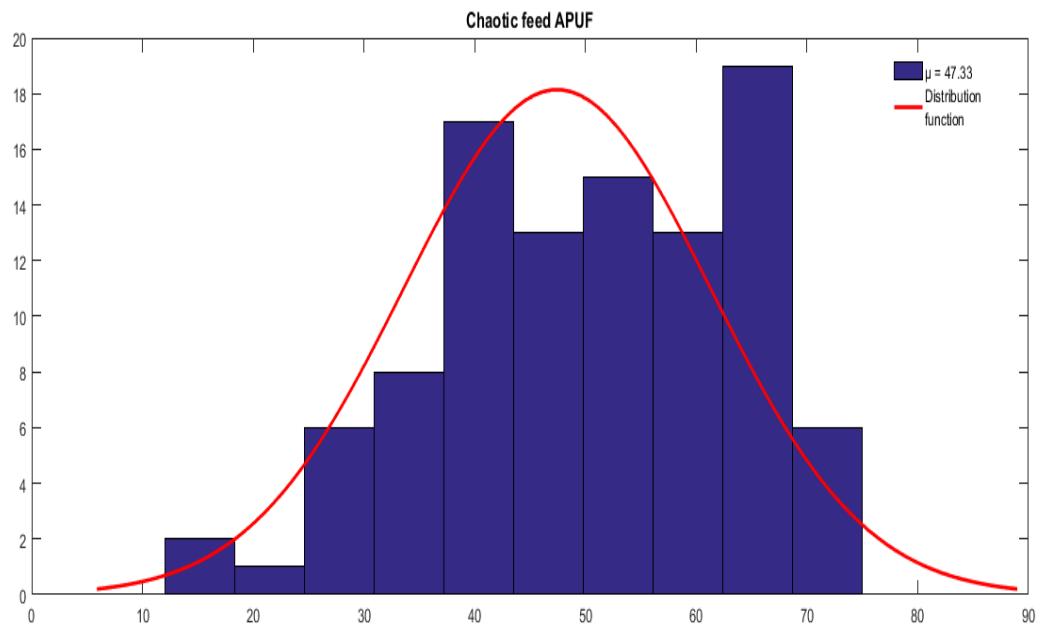

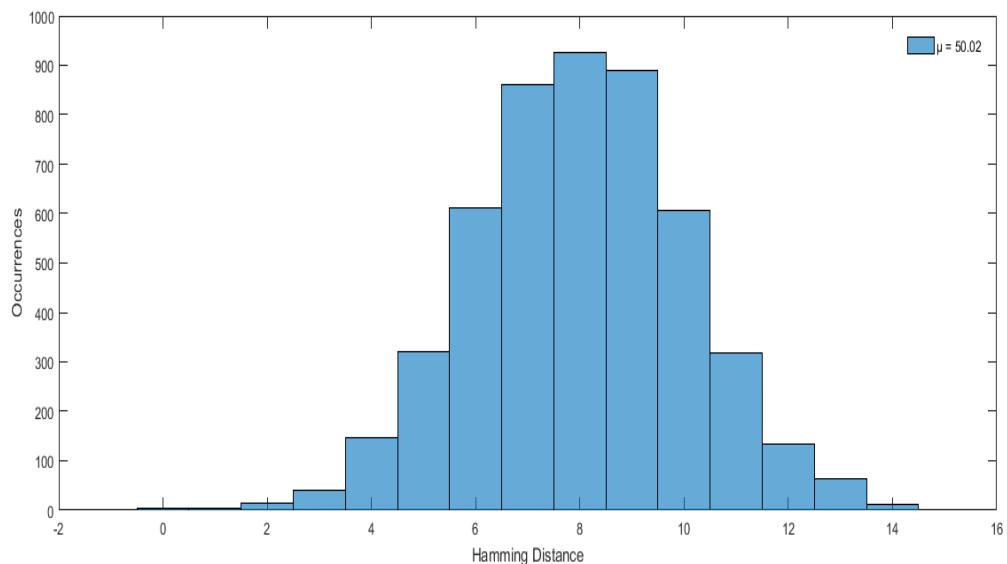

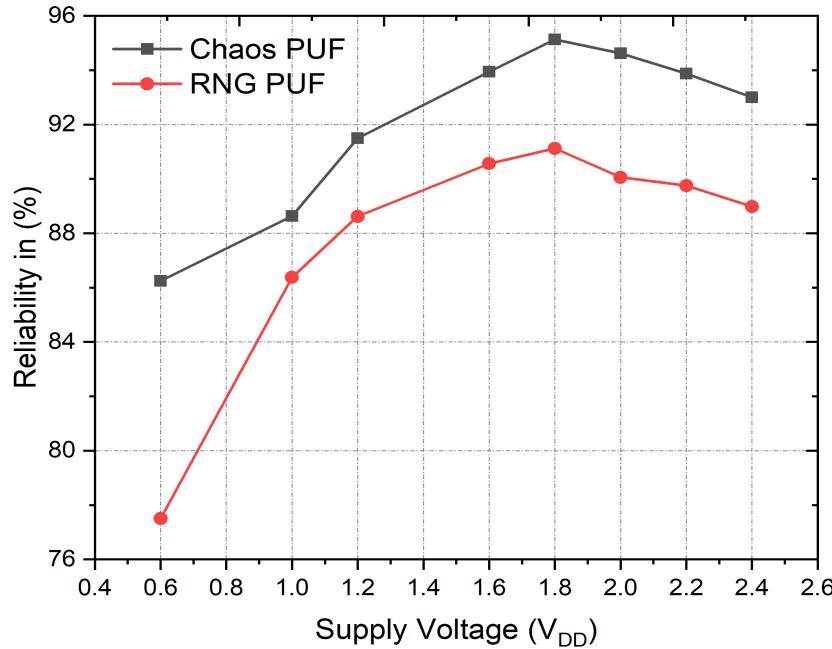

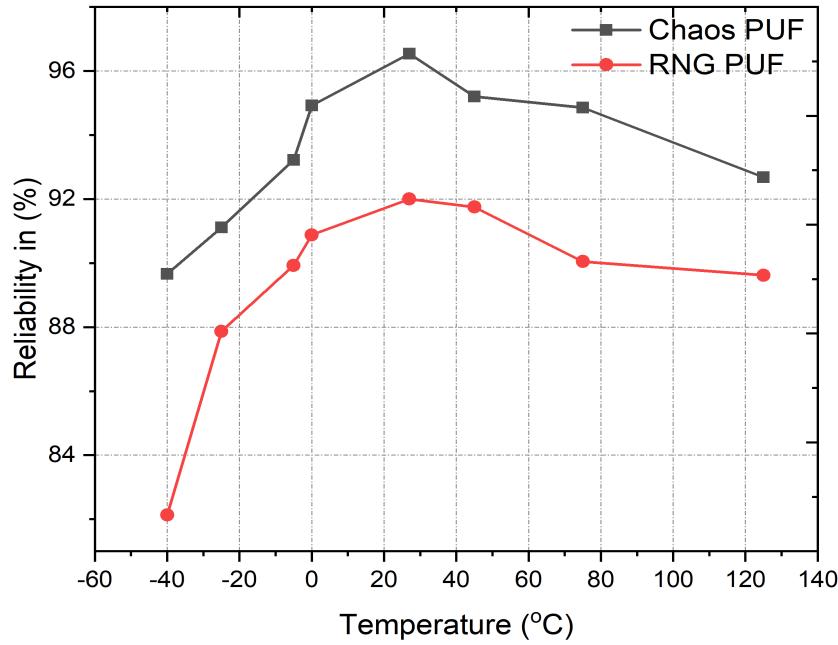

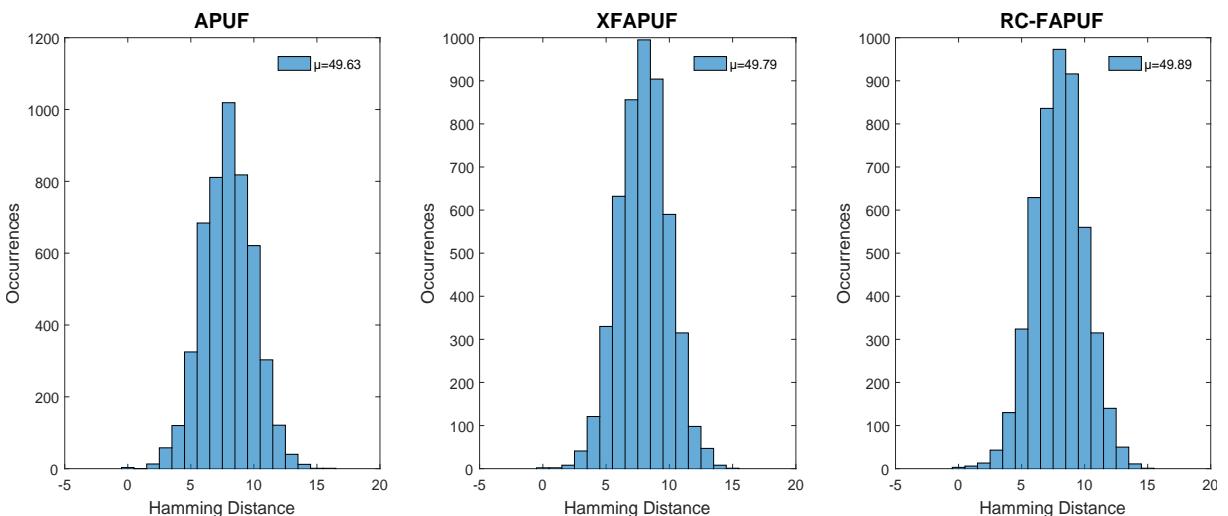

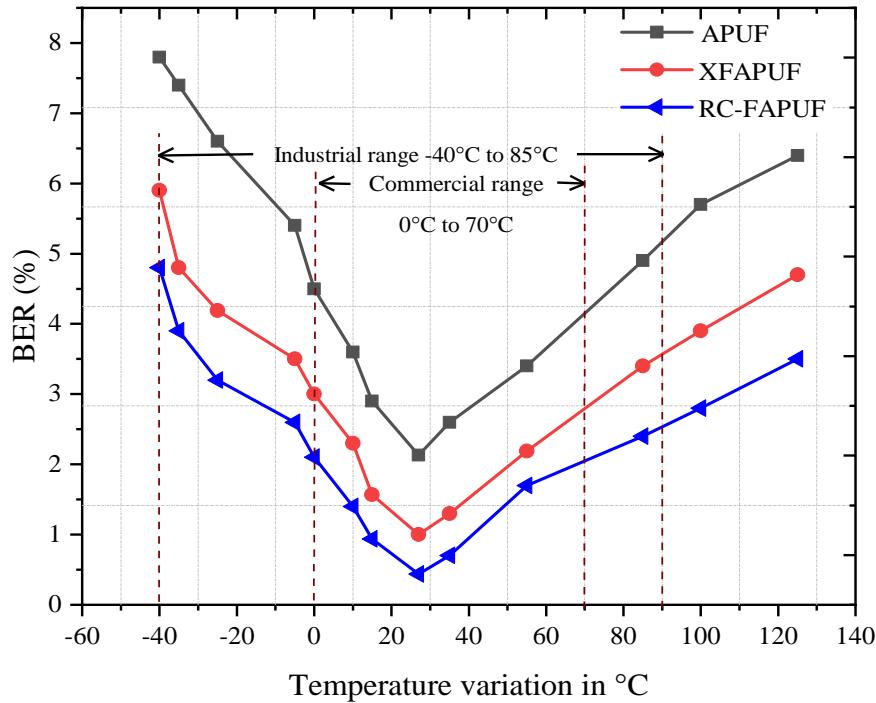

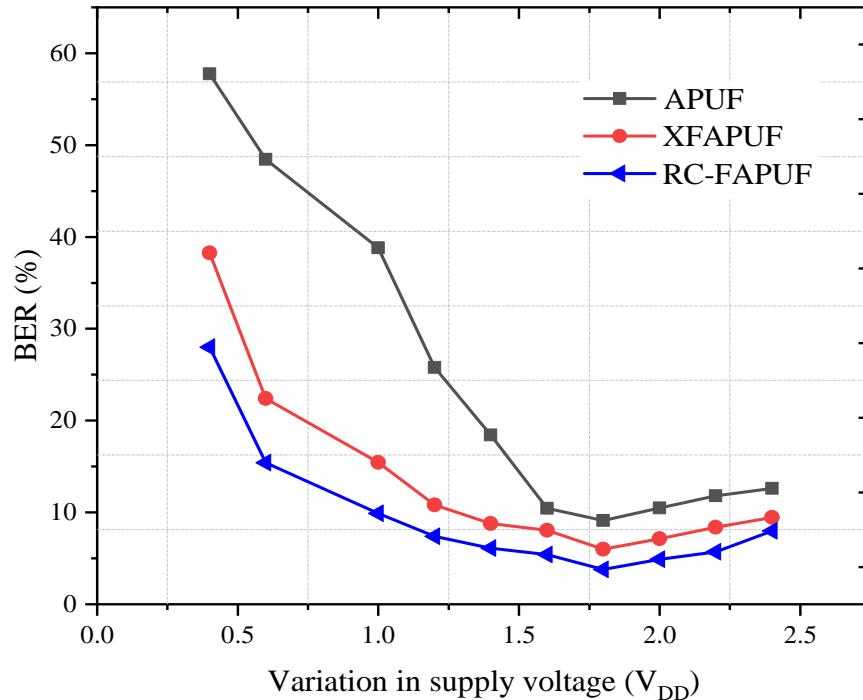

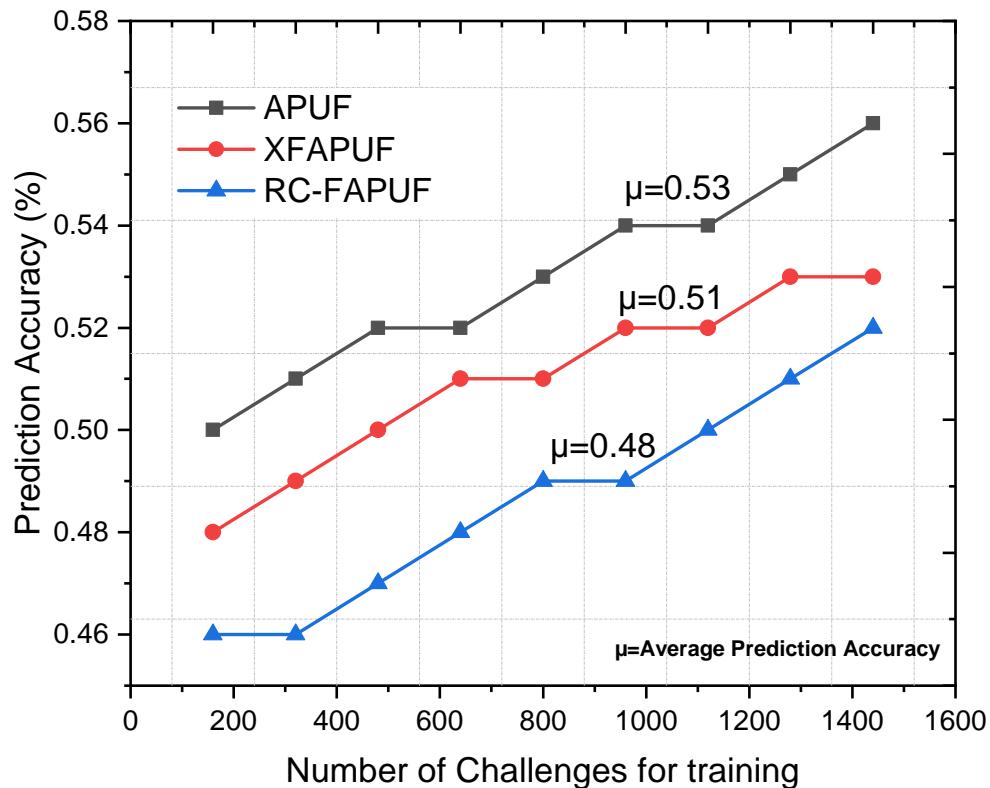

[108]. Silicon PUFs are made on the same die as the circuit and interface with other ICs. Different circuit features (timing and delay information) are produced as a unique response for a specific challenge, and PV during fabrication is captured as a challenge. Non-silicon PUFs are unique fabrication methods that are outside the scope of conventional CMOS fabrication technologies. Rather than using ICs, the response is derived from the challenge set acquired from the random physical variation in the physical system.