# Design and evaluation of scalable 2D, 3D and hybrid interconnects for Network-on-Chip

*Submitted in partial fulfilment of the requirements*

*for the award of the degree of*

**Doctor of Philosophy**

by

**V. Lakshmi Kiranmai**

(Roll No: 718140)

Under the supervision

of

**Dr. B.K.N. Srinivasarao**

Department of Electronics & Communication Engineering

National Institute of Technology Warangal

Telangana, India - 506004

**2024**

## Approval Sheet

This thesis entitled **Design and evaluation of scalable 2D, 3D and hybrid interconnects for Network-on-Chip** by **V. Lakshmi Kiranmai** is approved for the degree of **Doctor of Philosophy**.

### **Examiners**

---

---

### **Research Supervisor**

---

**Dr. B.K.N Srinivasarao**

Department of ECE,

NIT Warangal, India-506004

### **Chairman**

---

**Prof. D. Vakula**

Head, Department of ECE,

NIT Warangal, India-506004

Place:

Date:

## Declaration

This is to certify that the work presented in this thesis entitled **Design and evaluation of scalable 2D, 3D and hybrid interconnects for Network-on-Chip** is a bonafied work done by me under the supervision of **Dr. B.K.N Srinivasarao** and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my own ideas and even considered others ideas which are adequately cited and further referenced the original sources. I understand that any violation of the above will cause disciplinary action by the institute and can also evoke panel action from the sources or from whom proper permission has not been taken when needed. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea or data or fact or source in my submission.

Place:

Date:

V.Lakshmi Kiranmai

Research Scholar

Roll No.: 718140

# NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL, INDIA-506004

Department of Electronics and Communication Engineering

## CERTIFICATE

This is to certify that the thesis work entitled **Design and evaluation of scalable 2D, 3D and hybrid interconnects for Network-on-Chip** is a bonafide record of work carried out by **V. Lakshmi Kiranmai** submitted to the faculty of **Electronics and Communication Engineering** department, in partial fulfilment of the requirements for the award of the degree of **Doctor of Philosophy in Electronics and Communication Engineering, National Institute of Technology Warangal, India-506004**. The contributions embodied in this thesis have not been submitted to any other university or institute for the award of any degree.

Dr.B.K.N Srinivasarao

Place:

Research Supervisor

Date:

Department of ECE,

NIT Warangal, India-506004.

## Acknowledgements

I would like to express my profound gratitude to my supervisor, Dr.B.K.N Srinivasarao for his valuable guidance, constructive suggestions, unwavering support and constant encouragement throughout this research. I am thankful to him for his critical suggestions during the preparation of manuscripts. The accomplishment of this work would have been challenging without his consistent supervision and continuous feedback.

I would like to express my sincere thanks to my DSC members, to Prof.Vishwanathan N, Dr.P.Muralidhar and Dr.Mohammad Farukh Hashmi, for their insightful suggestions and encouragement during the progress of this research work. I am grateful to Head of the ECE department, Prof. D. Vakula and the former Heads of the ECE department, Prof. N. Bheema Rao, Prof. L. Anjaneyulu and Prof. P. Sreehari Rao for their continuous support and encouragement. I thank all the faculty and staff of Department of Electronics and communication Engineering for their encouragement and constant moral support.

I take this opportunity to extend my gratitude and convey my regards to all co-scholars, friends and my well wishers for consistently being by my side. Thanks to Dr.Ch.Balaram, Dr.Sagar, Dr.Bharat, P.Hari, Mahesh, J.Nandini, Ragini, P.Raveendra, Ravi shankar, Venkat for their motivation and support throughout my work.

I express my gratitude to all my teachers, colleagues, and relatives across various locations for their support, which played a crucial role in the successful completion of this work. Special thanks to my close friends Smt.Sudha, Smt.Swapna and Smt.Bhargavi for their motivation and moral support. I would also extend my gratitude and thank my close friend Smt.Madhavi for introducing me the intricacies of programming. I am grateful and I appreciate Mr.Teja for helping me comprehend the programming concepts.

Special thanks to Prof.B.R.Phanikumar, for the motivation and encouragement,

which helped me a lot for the successful completion of my research work. Along the way, I have met many bright and enthusiastic people who have influenced me and regardless of whether or not they know they did, I sincerely appreciate their efforts.

I extend my sincere and immense sense of gratitude to my beloved family members, my parents Sri.V.V.Suryanarayana Murty and Smt.Prabhavati for their motivation, support and blessings without which it would not have been possible for me to reach so far. I would like to convey my deepest thanks to my husband Dr.K.V.R Ravi shankar and my beloved son K.Srikrishna for their unwavering support, constant encouragement, patience, understanding and remarkable co-operation. I would like to express my sincere gratitude to my brother and sister-in-law -Sri.V.V.J.S.Subrahmanyam and Smt.Sirisha and their children Pranavi and Abhiram for their support and encouragement during my research. I express my profound gratitude to my elder brother-in-law and sister - Sri K.Ch.V.S. Kameswara Rao and Smt. Durga Satyavathi and their children, Praneeth and Lakshmi, Pratyush and Monica, second elder brother-in-law and sister - Sri K.V.S. Ramakrishna Rao and Smt. Prasanna, and their children, Shriya, Sneha for their support and encouragement throughout this endeavour. Last, but by no means least, I express my gratitude to my in-laws, Sri K.V.M. Sharma and Smt. K. Ratnam for their blessings.

Above all, I am grateful to GOD almighty for showering the grace and endowing me with the wisdom, health, and strength necessary to undertake and successfully complete this research endeavor.

**V. Lakshmi Kiranmai**

---

## Abstract

Network-on-Chip (NoC) is an emerging and efficient on-chip interconnect technology. NoC is a viable option to design modular, scalable, robust communication interconnect architectures. Topology is one among many crucial design aspects of NoC, as it affects the performance of the interconnection network. Mesh is the most extensively used and favoured architecture for implementing less sophisticated SoCs due to its simple, scalable, regular structure, low-radix routers and short-range links. However, as the network scales, Mesh suffers from degraded performance because of large diameter. The present work aims at developing efficient and scalable novel topologies – 2D, 3D topology, hybrid wired topology and hybrid wired-wireless topology for on-chip interconnect architectures that outperform Mesh topology.

The objectives of the research are threefold – First, to design a hybrid wired topology i.e., combining two topologies. Second, to design a diagonal Mesh based topology by inserting diagonal links into the conventional Mesh topology retaining the simple, scalable, regular structure of Mesh simultaneously improving the performance. Third, to design a three-level hierarchical hybrid wired-wireless interconnection architecture for large networks.

To begin, the present work proposes a novel, scalable, hybrid Hexagonal Star (HS) topology for on-chip connectivity networks. The proposed topology's properties have been investigated and compared to those of the Mesh, Torus, and Honeycomb Mesh topologies. The performance of the Hexagonal Star topology has been studied and compared to that of the Mesh topology in different scenarios. The comparative studies of topological properties have indicated that the proposed topology can be a potential choice for on-chip interconnection networks. For different traffic patterns and traffic loads, HS topology has registered a reduction of packet latency ranging from 15% to 50% and from 9% to 23% for

---

18 nodes and 32 nodes, respectively, compared to Mesh topology. Further, the synthesis results indicate a significant reduction of area consumed by HS topology compared to the area consumed by an identically configured Mesh topology.

Second, the present work proposes DiamondMesh, an area and energy efficient diagonal mesh based topology. By incorporating diagonal links into the basic mesh topology, the proposed DiamondMesh increases network performance while keeping the Mesh topology's regular, simple, and scalable features. Topological properties of DiamondMesh have been explored and compared with that of other competitive diagonal mesh topologies. The proposed topology and other state-of-the-art diagonal Mesh topologies have been simulated and synthesised. The evaluation results indicate that there has been a significant reduction of latency compared to Mesh and other diagonal mesh topologies except DMesh and a considerable reduction of area and power compared to the DMesh topology.

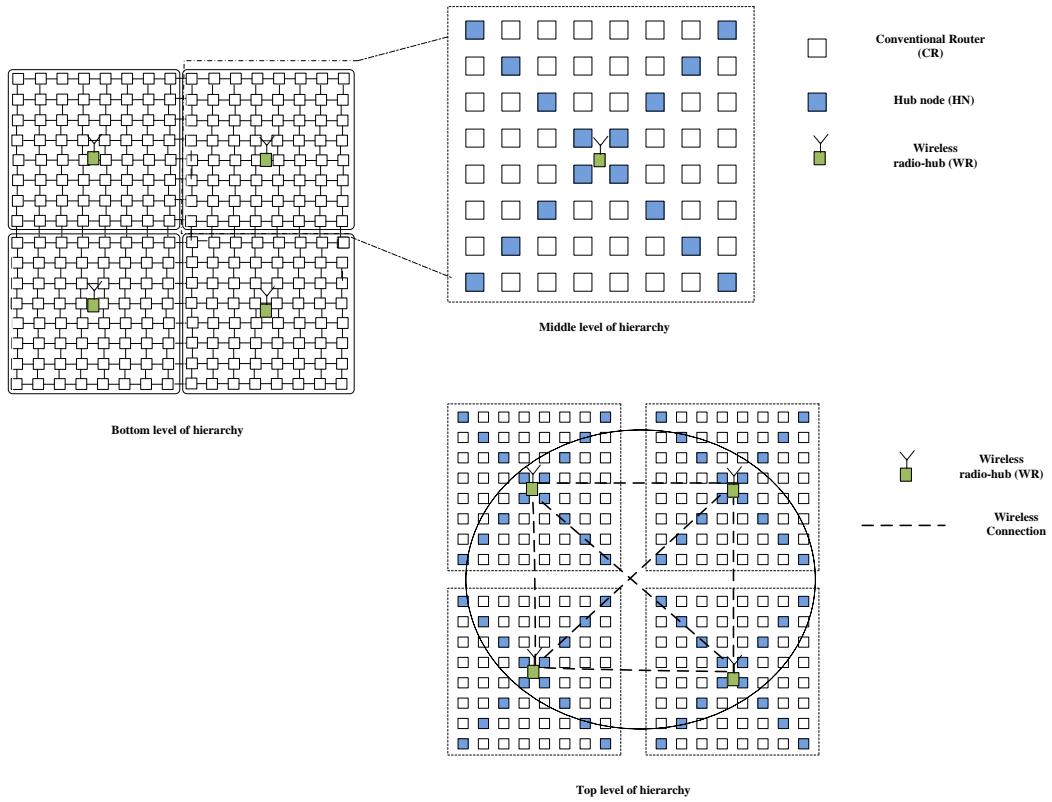

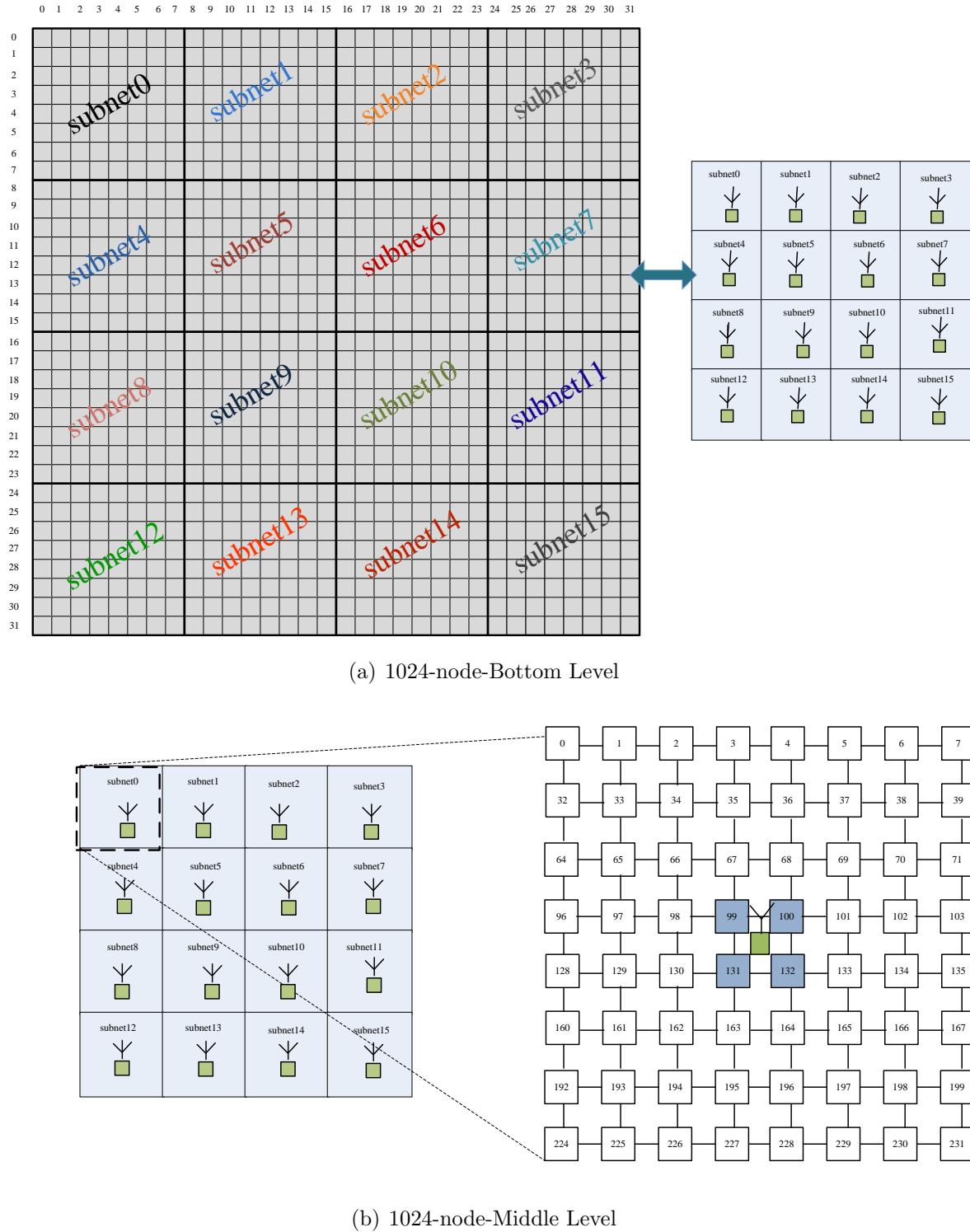

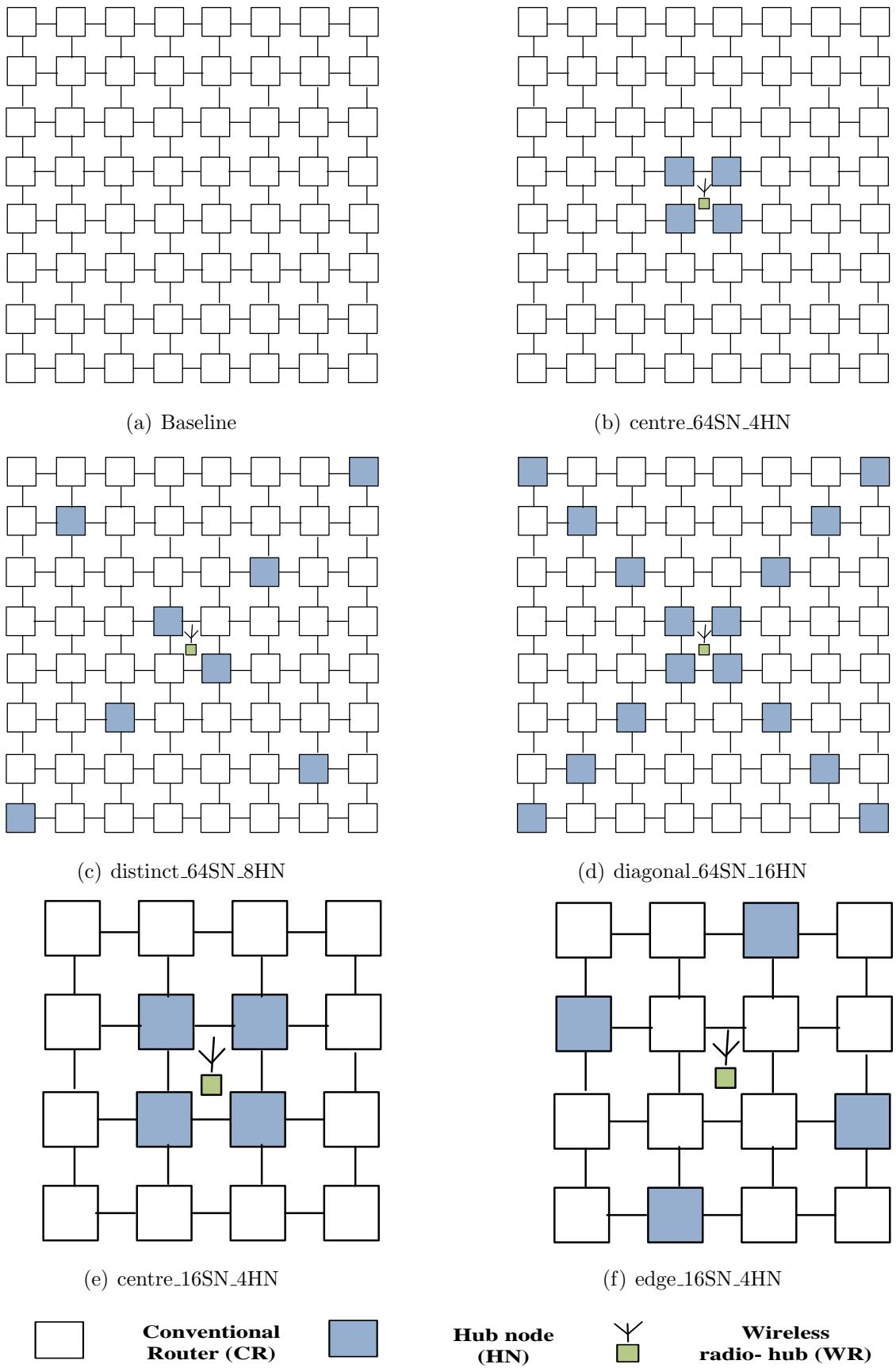

Finally, in order to address the limitations of electrical interconnects, the current work investigated hybrid wired-wireless topologies. Three-level hierarchical hybrid wired-wireless Network-on-Chip (NoC) designs have been proposed and evaluated under different traffic patterns at low, medium, and high traffic loads. In the proposed three-level hierarchy, the bottom and top levels are concerned with subnet topology and wireless hub topology, respectively. The present research introduces a middle level that investigates the number of nodes that will be connected to a subnet's wireless hub. Mesh and fully connected wireless topologies have been chosen for the bottom and top levels of the hierarchy, respectively. Different hybrid wired-wireless configurations have been developed and studied by varying the number of subnets and the number of nodes to be attached to the subnet at the middle level. The objective of investigating the middle level is to reduce the number of subnets and, consequently, the number of wireless nodes in large network architectures without compromising performance. The proposed hybrid architectures outperform baseline wired Mesh architecture in terms of latency and throughput characteristics.

Index Terms : Network on Chip (NoC), Mesh, wireless NoC, hybrid NoC, Hexagonal star, DiamondMesh, Diagonal Mesh, hierarchical WiNoC, hybrid NoC topology.

---

# Contents

|                                                     |     |

|-----------------------------------------------------|-----|

| <b>Declaration</b>                                  | ii  |

| <b>Acknowledgements</b>                             | iv  |

| <b>Abstract</b>                                     | vi  |

| <b>List of Figures</b>                              | xii |

| <b>List of Tables</b>                               | xvi |

| <b>List of Abbreviations</b>                        | xix |

| <b>1 Introduction</b>                               | 1   |

| 1.1 Fundamentals of Network-on-Chip (NoC) . . . . . | 2   |

| 1.1.1 Evolution of NoC . . . . .                    | 2   |

| 1.1.2 NoC: A layered architecture . . . . .         | 3   |

| 1.1.2.1 Application layer . . . . .                 | 3   |

| 1.1.2.2 Transport layer . . . . .                   | 4   |

| 1.1.2.3 Network layer . . . . .                     | 4   |

| 1.1.2.4 Data Link layer . . . . .                   | 4   |

| 1.1.2.5 Physical layer . . . . .                    | 5   |

| 1.1.3 Basic building blocks of NoC . . . . .        | 5   |

---

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| 1.1.4    | Topology . . . . .                                               | 7         |

| 1.1.4.1  | Significant topological parameters considered . . . . .          | 9         |

| 1.1.5    | Routing . . . . .                                                | 10        |

| 1.1.6    | Flow control . . . . .                                           | 12        |

| 1.1.7    | Interconnect technologies . . . . .                              | 13        |

| 1.2      | Motivation . . . . .                                             | 13        |

| 1.3      | Research Objectives . . . . .                                    | 14        |

| 1.4      | Organization of the Thesis . . . . .                             | 15        |

| <b>2</b> | <b>Literature</b>                                                | <b>17</b> |

| 2.1      | On-chip interconnect topologies . . . . .                        | 17        |

| 2.1.1    | Numerous approaches to enhance the performance of NoCs . . . . . | 17        |

| 2.1.2    | Hexagonal based topologies . . . . .                             | 19        |

| 2.1.3    | Diagonal Mesh topologies . . . . .                               | 20        |

| 2.2      | On-chip interconnect technologies . . . . .                      | 21        |

| 2.2.1    | Electrical interconnect technology . . . . .                     | 21        |

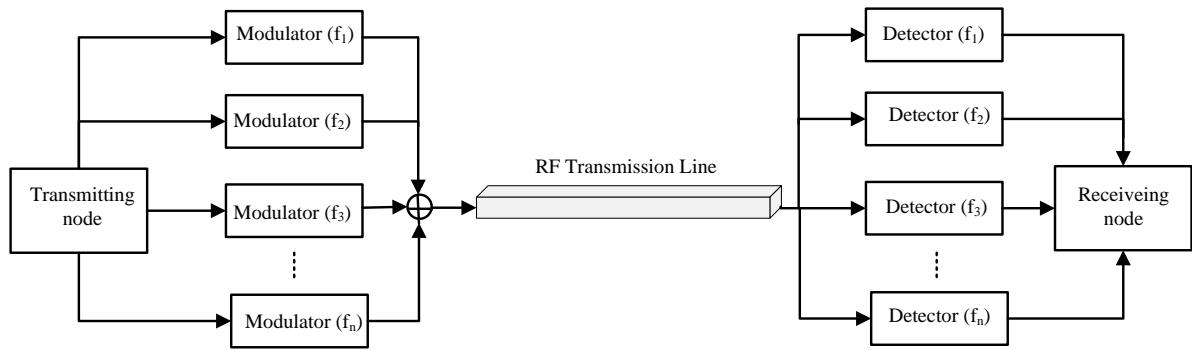

| 2.2.2    | RF interconnect (RF-I) technology . . . . .                      | 24        |

| 2.2.3    | Graphene-based interconnect technology . . . . .                 | 26        |

| 2.2.3.1  | Limitations and advancements . . . . .                           | 30        |

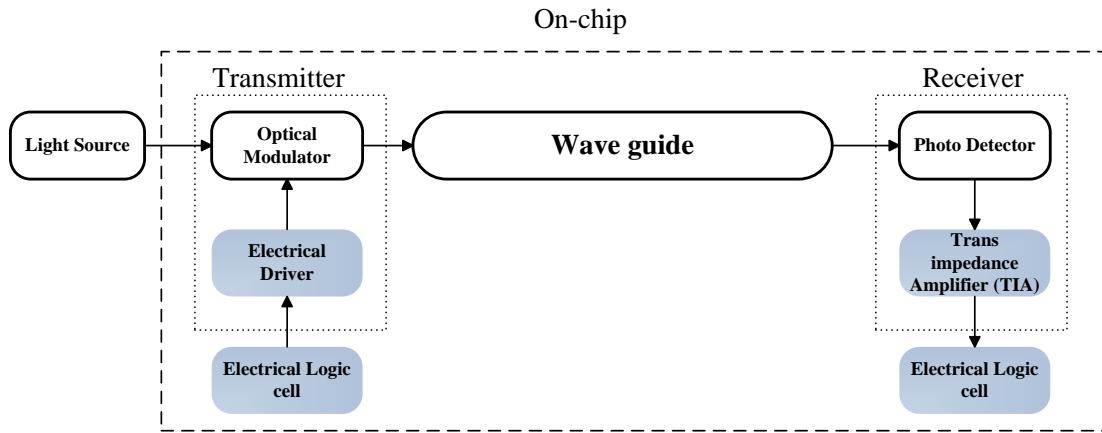

| 2.2.4    | Photonic (Optical) Interconnect Technology . . . . .             | 30        |

| 2.2.4.1  | Basic concepts . . . . .                                         | 31        |

| 2.2.4.2  | Limitations and advancements . . . . .                           | 34        |

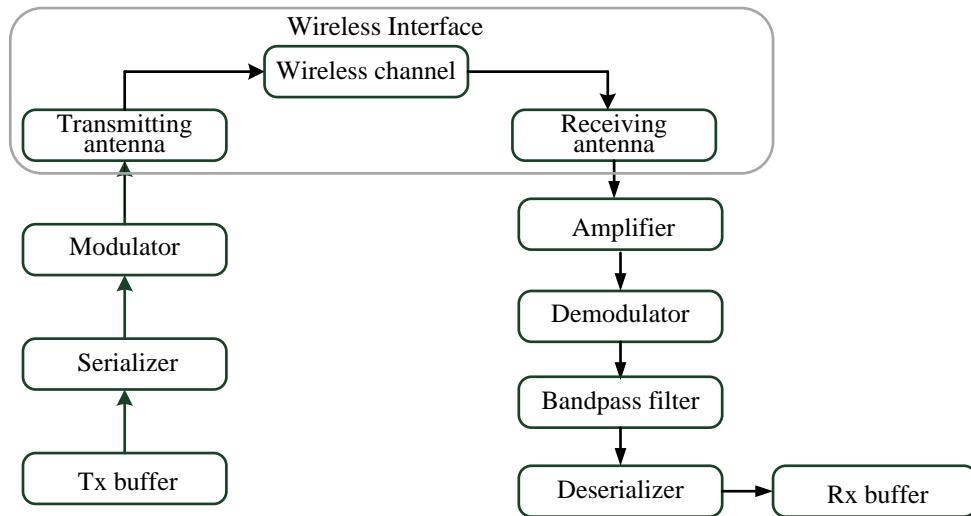

| 2.2.5    | Wireless Interconnect Technology . . . . .                       | 35        |

| 2.2.5.1  | Limitations and advancements . . . . .                           | 36        |

| 2.2.6    | Surface wave Interconnect (SWI) Technology . . . . .             | 37        |

---

---

|          |                                                           |           |

|----------|-----------------------------------------------------------|-----------|

| 2.2.7    | Comparison of on-chip interconnect technologies . . . . . | 38        |

| <b>3</b> | <b>Hexagonal Star: Hybrid topology for NoC</b>            | <b>40</b> |

| 3.1      | Introduction . . . . .                                    | 40        |

| 3.2      | Hybrid Hexagonal Star (HS) . . . . .                      | 41        |

| 3.2.1    | Proposed HS Topology . . . . .                            | 41        |

| 3.2.2    | Router and organization of links . . . . .                | 48        |

| 3.2.3    | Buffer Resources . . . . .                                | 48        |

| 3.2.4    | Topological parameters . . . . .                          | 51        |

| 3.2.5    | Possible scalable architectures . . . . .                 | 54        |

| 3.3      | Evaluation . . . . .                                      | 54        |

| 3.3.1    | Routing algorithm . . . . .                               | 55        |

| 3.3.2    | Performance analysis . . . . .                            | 56        |

| 3.3.3    | Synthesis results . . . . .                               | 63        |

| 3.4      | Summary . . . . .                                         | 64        |

| <b>4</b> | <b>DiamondMesh : A diagonal Mesh topology for NoC</b>     | <b>66</b> |

| 4.1      | Introduction . . . . .                                    | 66        |

| 4.2      | 2D-DiamondMesh . . . . .                                  | 67        |

| 4.2.1    | Proposed DiamondMesh topology . . . . .                   | 67        |

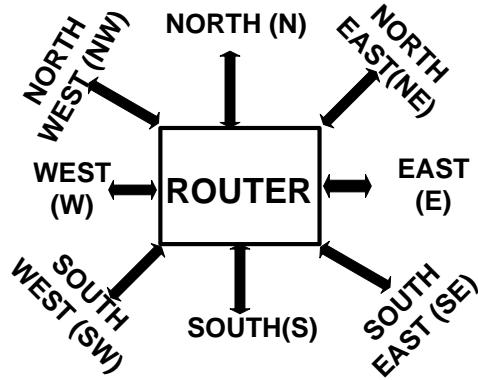

| 4.2.2    | Router and Port Directions . . . . .                      | 69        |

| 4.2.3    | Topological Parameters . . . . .                          | 69        |

| 4.3      | Evaluation . . . . .                                      | 71        |

| 4.3.1    | Experimental Setup . . . . .                              | 71        |

| 4.3.2    | Routing Algorithm . . . . .                               | 72        |

---

---

|                     |                                                                        |            |

|---------------------|------------------------------------------------------------------------|------------|

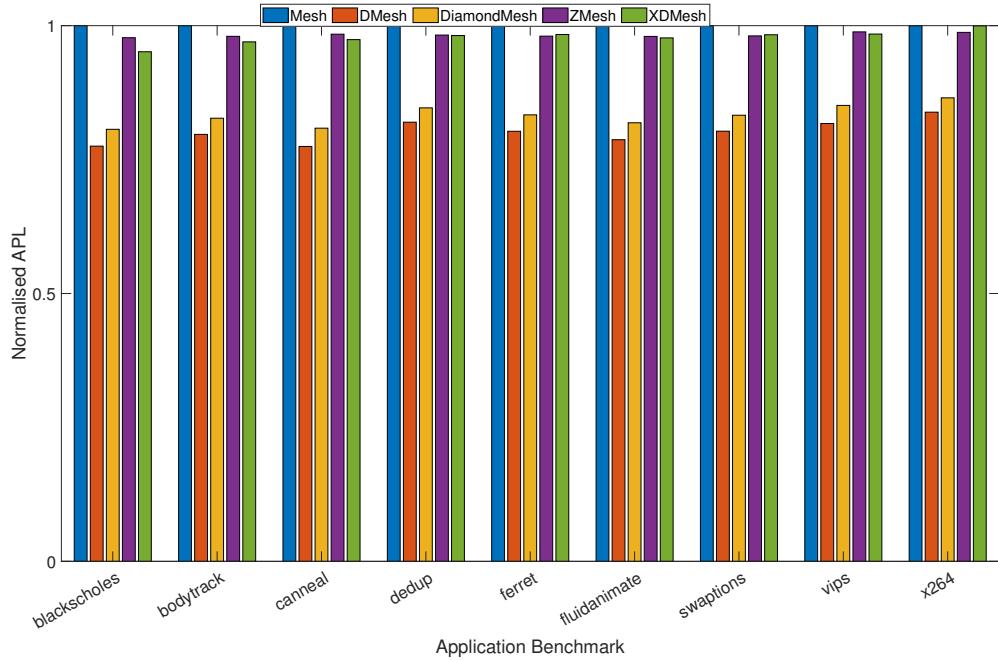

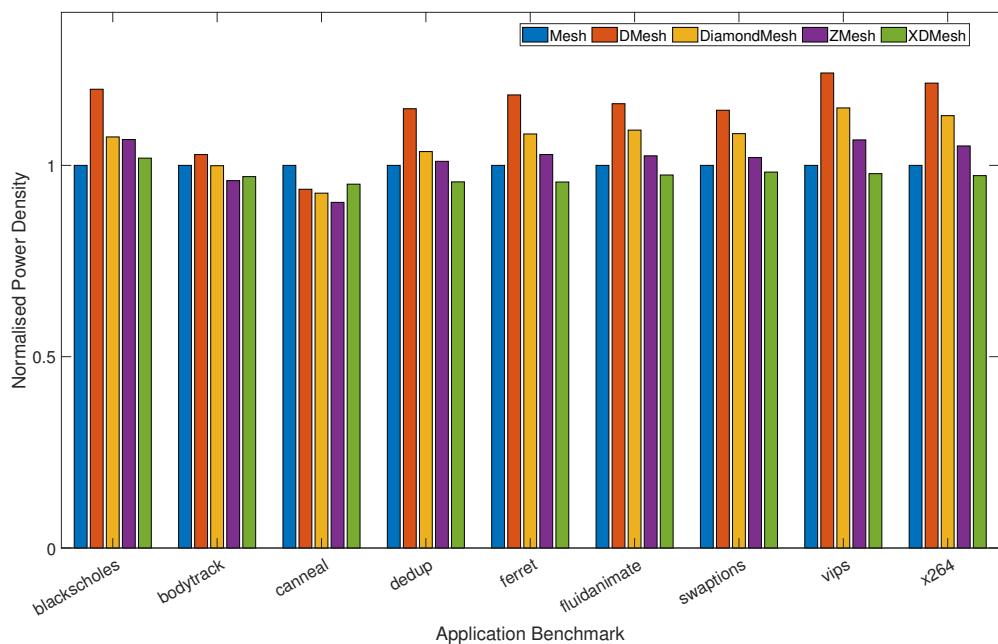

| 4.3.3               | Performance Analysis for synthetic traffic . . . . .                   | 74         |

| 4.3.4               | Performance Analysis for real application workloads . . . . .          | 82         |

| 4.3.5               | Synthesis results . . . . .                                            | 84         |

| 4.4                 | 3D-DiamondMesh . . . . .                                               | 85         |

| 4.4.1               | Evaluation . . . . .                                                   | 87         |

| 4.4.1.1             | Methodology . . . . .                                                  | 87         |

| 4.4.1.2             | Performance analysis . . . . .                                         | 88         |

| 4.5                 | Summary . . . . .                                                      | 92         |

| <b>5</b>            | <b>Three level hierarchical hybrid wired-wireless NoC architecture</b> | <b>94</b>  |

| 5.1                 | Introduction . . . . .                                                 | 94         |

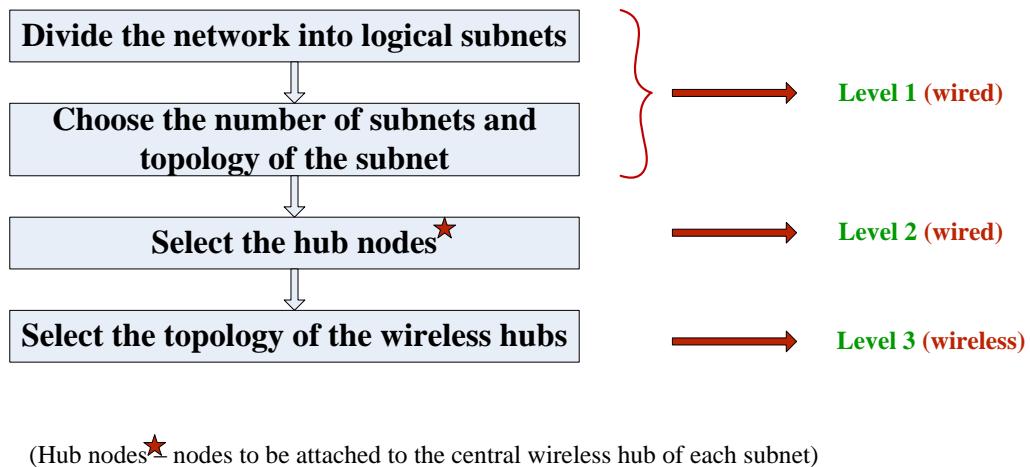

| 5.2                 | Design methodology . . . . .                                           | 95         |

| 5.3                 | Proposed architectures . . . . .                                       | 96         |

| 5.4                 | Evaluation . . . . .                                                   | 101        |

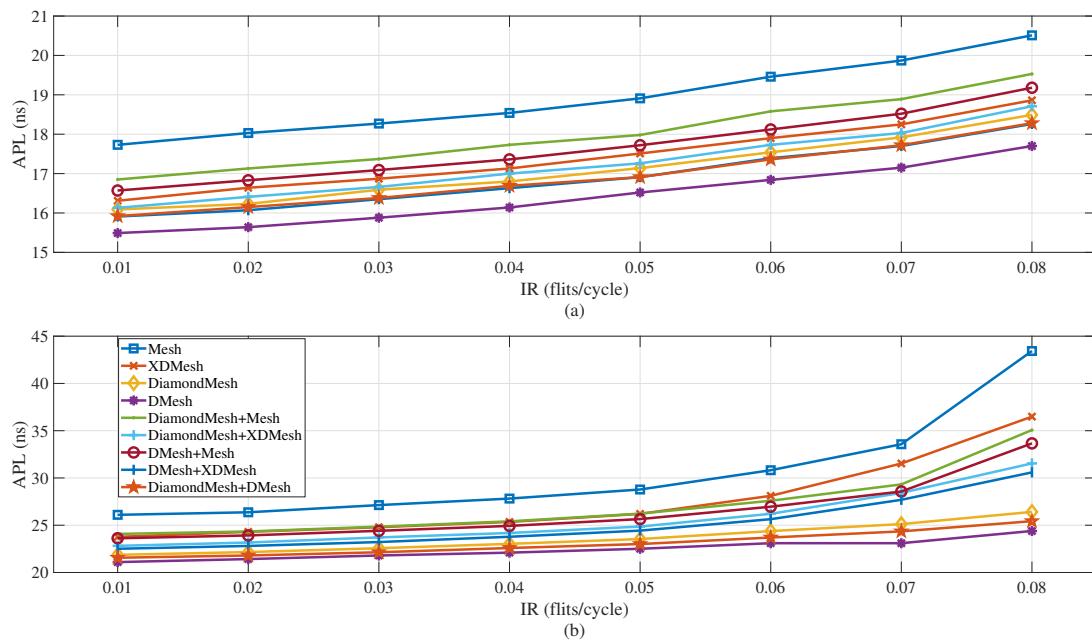

| 5.4.1               | Performance analysis . . . . .                                         | 104        |

| 5.4.2               | Wiring and Buffer resources requirements . . . . .                     | 115        |

| 5.5                 | Summary . . . . .                                                      | 117        |

| <b>6</b>            | <b>Conclusions and Scope for future research</b>                       | <b>119</b> |

| 6.1                 | Conclusions . . . . .                                                  | 119        |

| 6.2                 | Scope for future research . . . . .                                    | 122        |

| <b>Publications</b> |                                                                        | <b>124</b> |

| <b>Bibliography</b> |                                                                        | <b>125</b> |

# List of Figures

|     |                                                                                               |    |

|-----|-----------------------------------------------------------------------------------------------|----|

| 1.1 | Evolution of NoC [1]                                                                          | 2  |

| 1.2 | Layered architecture of NoCs [2]                                                              | 3  |

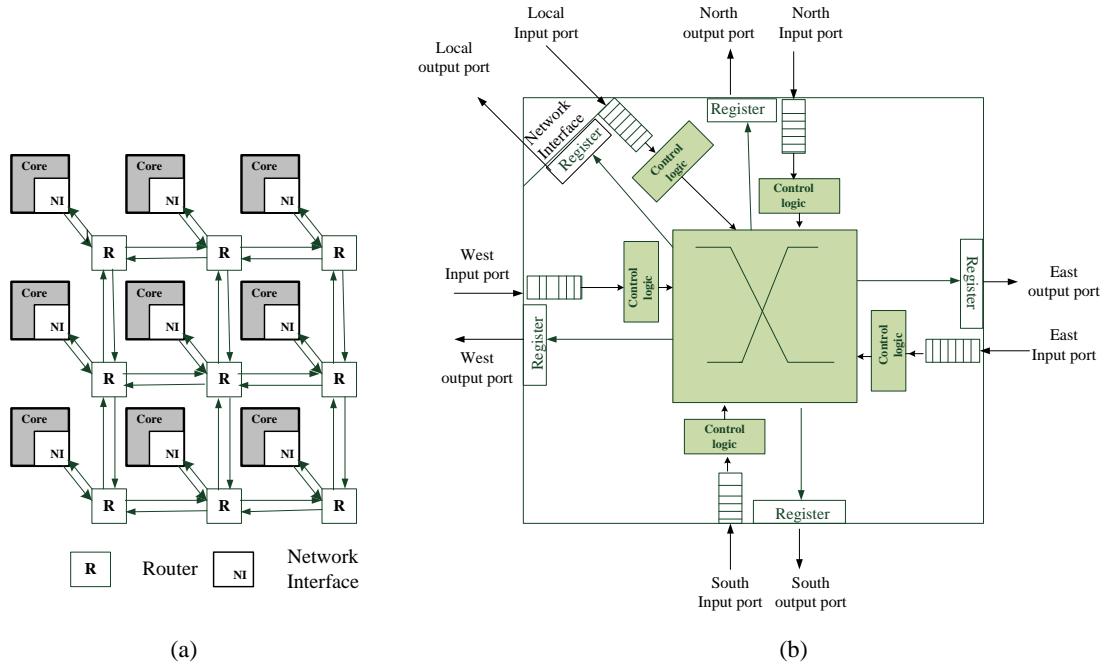

| 1.3 | (a) A typical NoC architecture; (b) A generic NoC router [3]                                  | 6  |

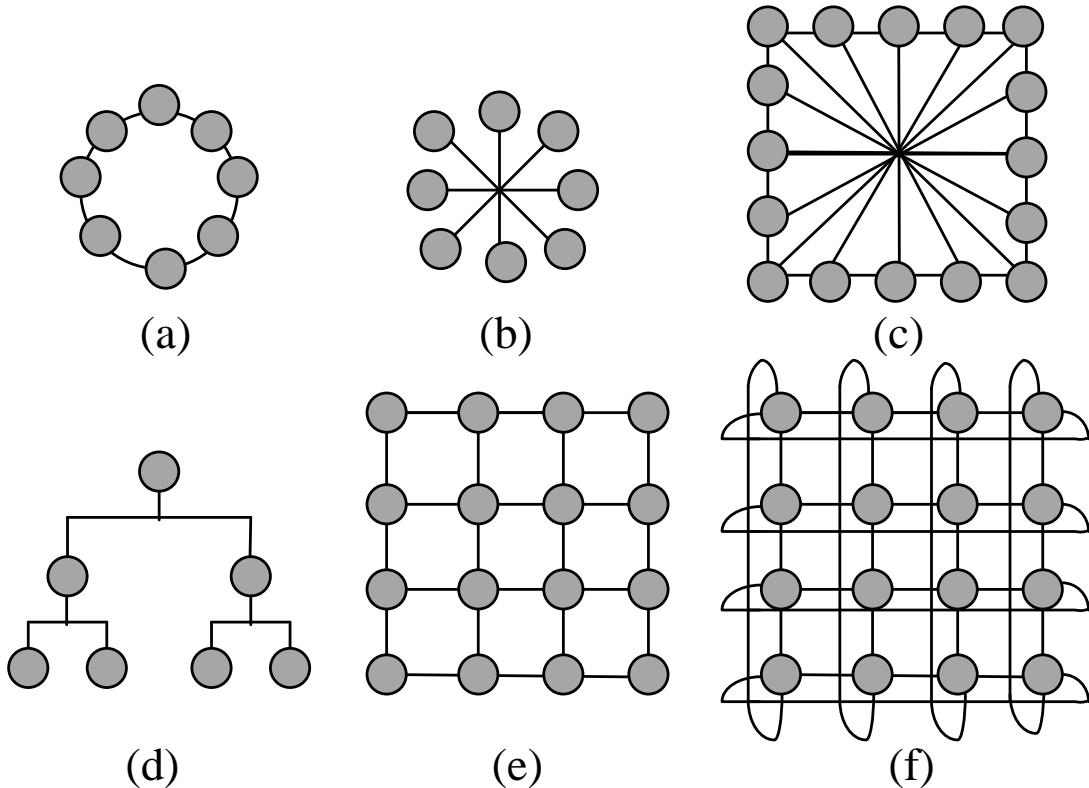

| 1.4 | NoC Topologies [1]                                                                            | 8  |

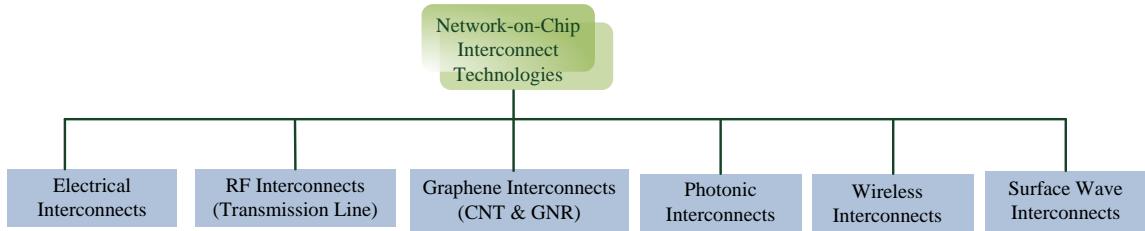

| 1.5 | On-Chip interconnect technologies                                                             | 13 |

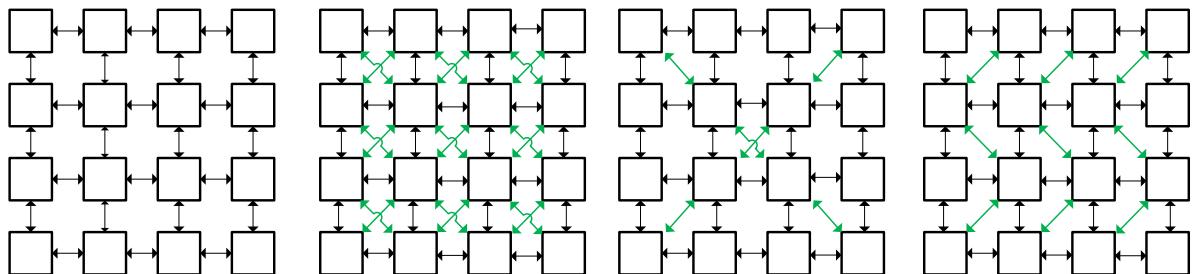

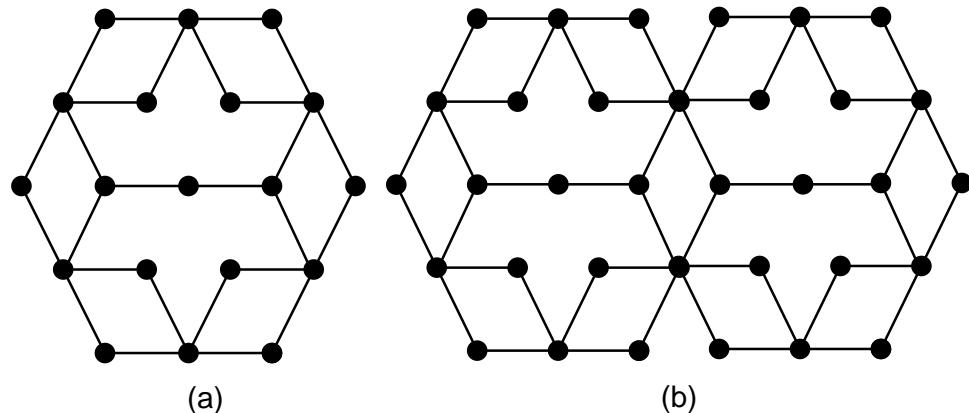

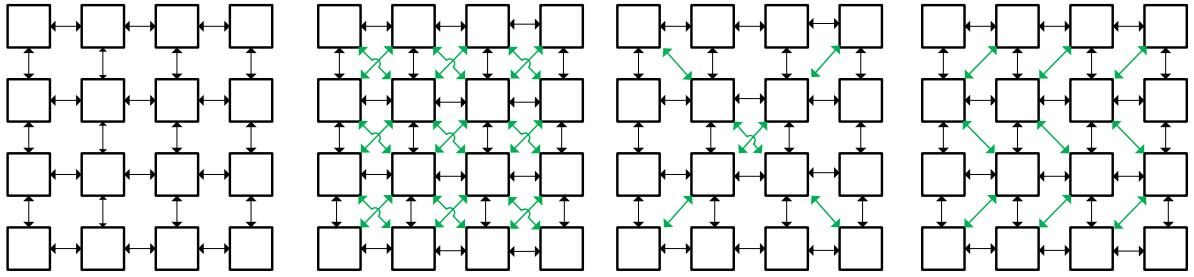

| 2.1 | (a) Mesh; (b) DMesh; (c) XDMesh; (d) ZMesh                                                    | 20 |

| 2.2 | Electrical communication system                                                               | 22 |

| 2.3 | Schematic of TL based RF-I [4]                                                                | 25 |

| 2.4 | Schematic of Photonic/Optical interconnect technology [5]                                     | 31 |

| 2.5 | On-Chip wireless communication system                                                         | 36 |

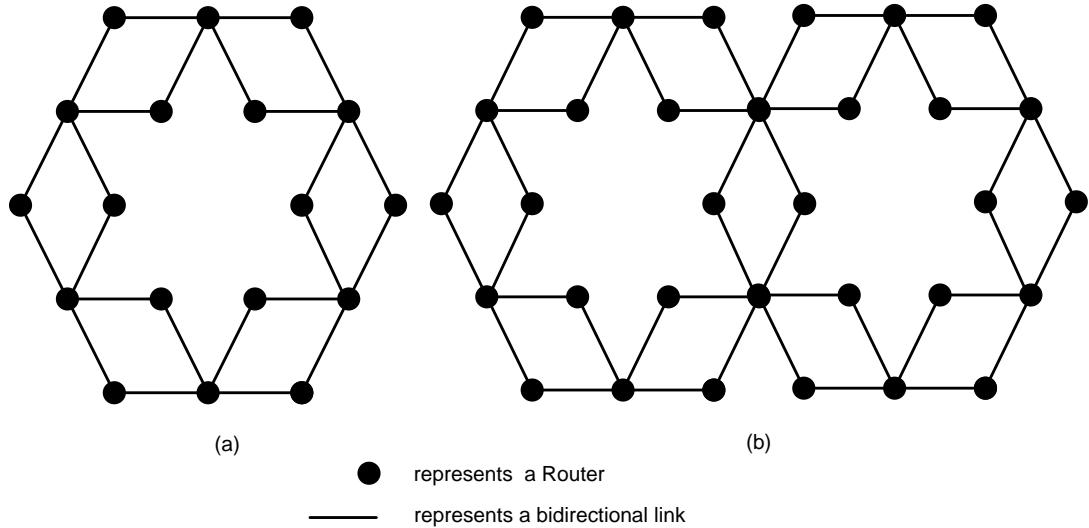

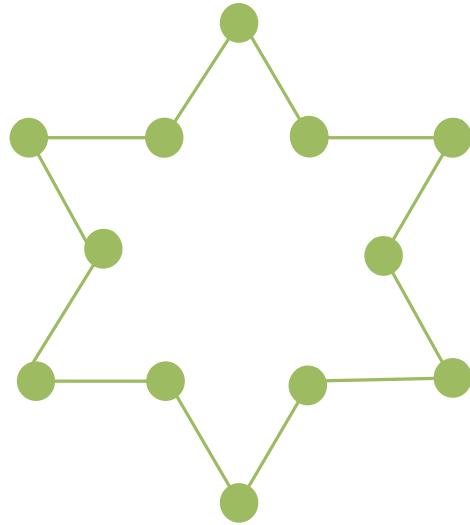

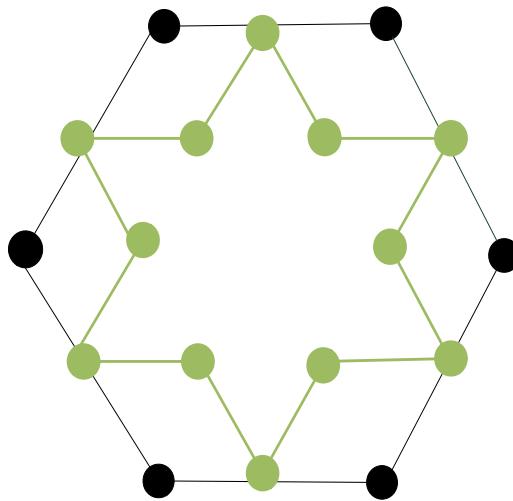

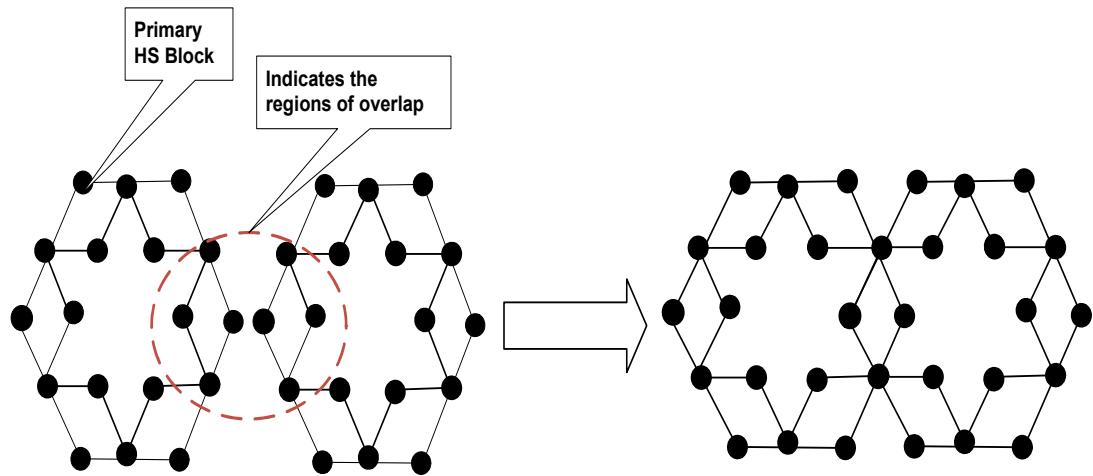

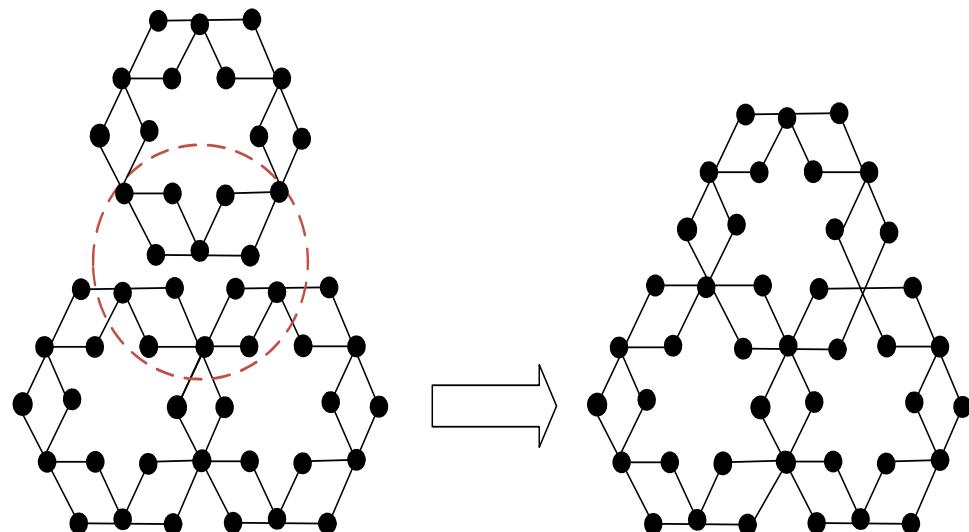

| 3.1 | (a) Basic block of Hexagonal star(18 nodes); (b) Two hexagonal stars(32 nodes)                | 42 |

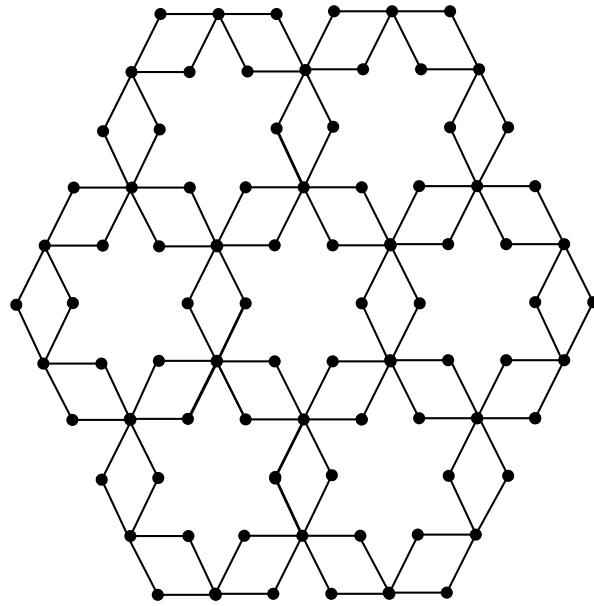

| 3.2 | Two-dimensional Hexagonal star topology for 84 nodes                                          | 43 |

| 3.3 | (a) Block of Hexagonal star V1 (HS-V1) (19 nodes); (b) Two Hexagonal Stars (HS-V1) (34 nodes) | 44 |

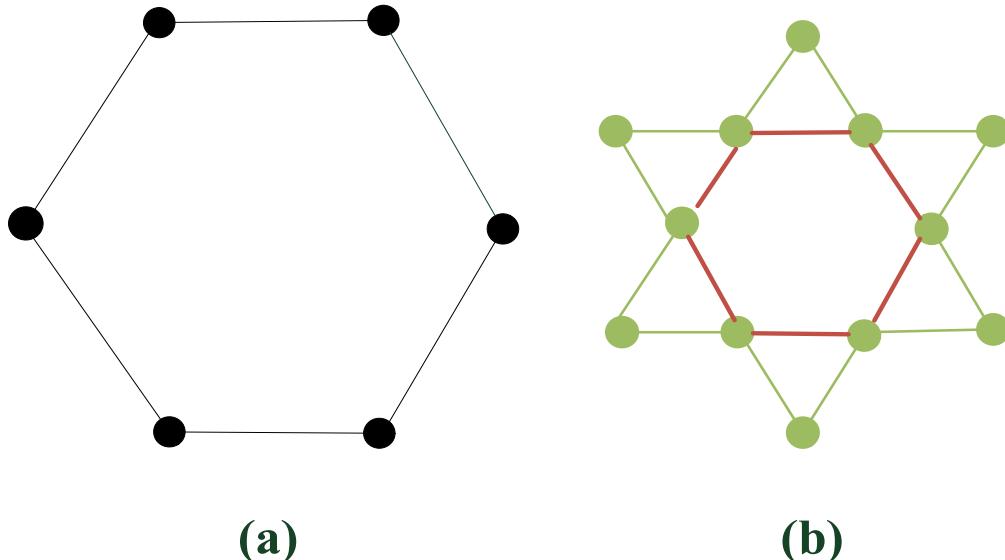

| 3.4 | (a) Regular Hexagon; (b) Hexagram or star of David                                            | 45 |

| 3.5 | star                                                                                          | 46 |

| 3.6 | Primary block of Hexagonal Star                                                               | 46 |

---

|      |                                                                                                                                                                                                |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | Adding 1st HS block                                                                                                                                                                            | 47 |

| 3.8  | Adding 2nd HS block                                                                                                                                                                            | 47 |

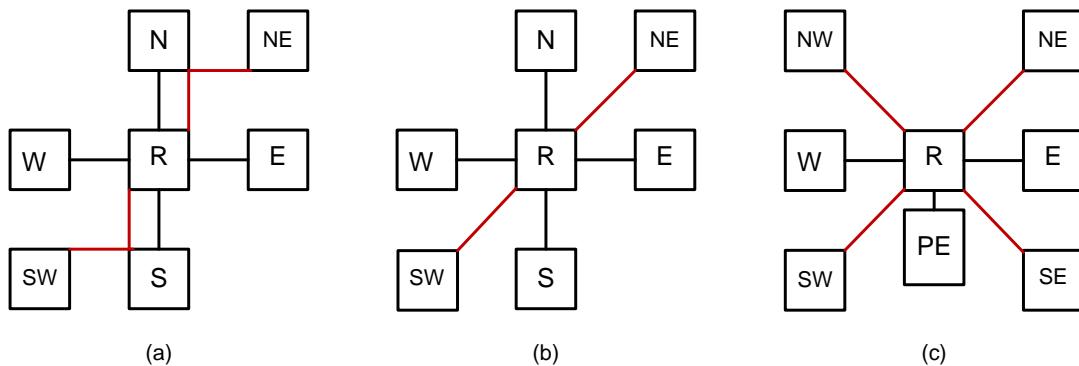

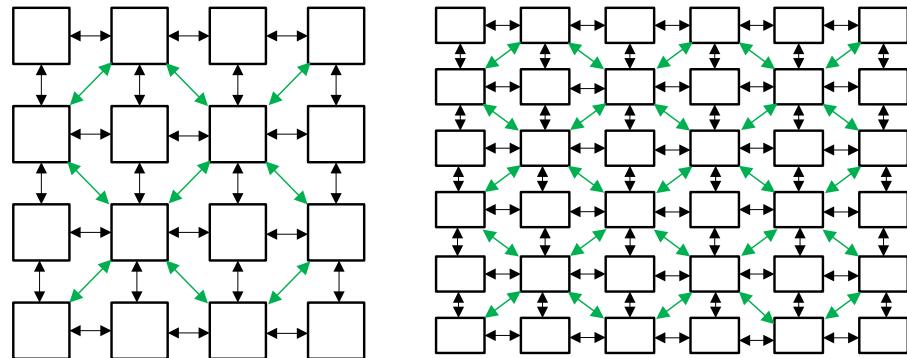

| 3.9  | (a) Manhattan layout style; (b) X-architecture layout style; (c)Router with all port directions including the local port that connects PE in the HS topology using X-architecture layout style | 48 |

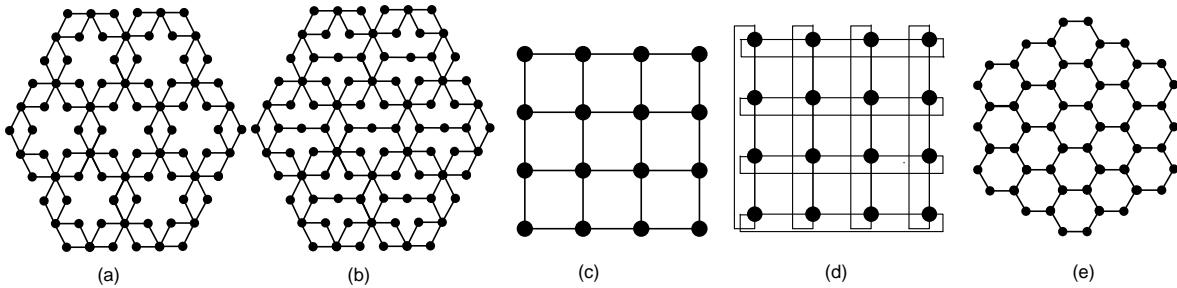

| 3.10 | (a) 2D-Hexagonal Star; (b) 2D-Hexagonal Star-V1; (c) Mesh; (d) Torus; (e) Honeycomb Mesh                                                                                                       | 51 |

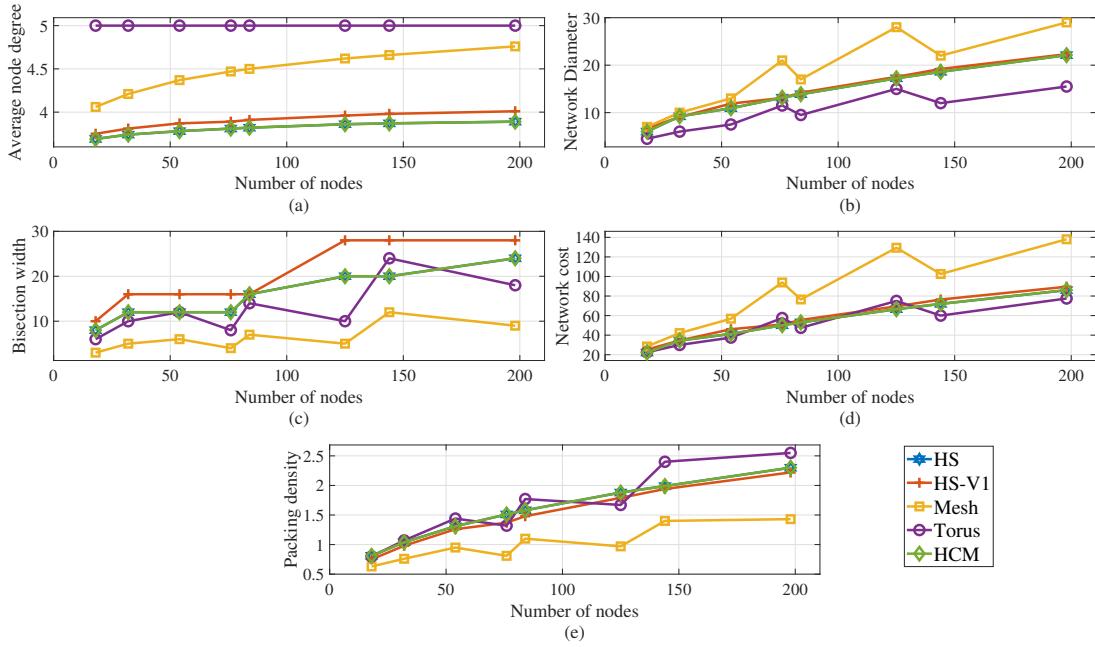

| 3.11 | Graphical representation of the comparison of topological parameters                                                                                                                           | 53 |

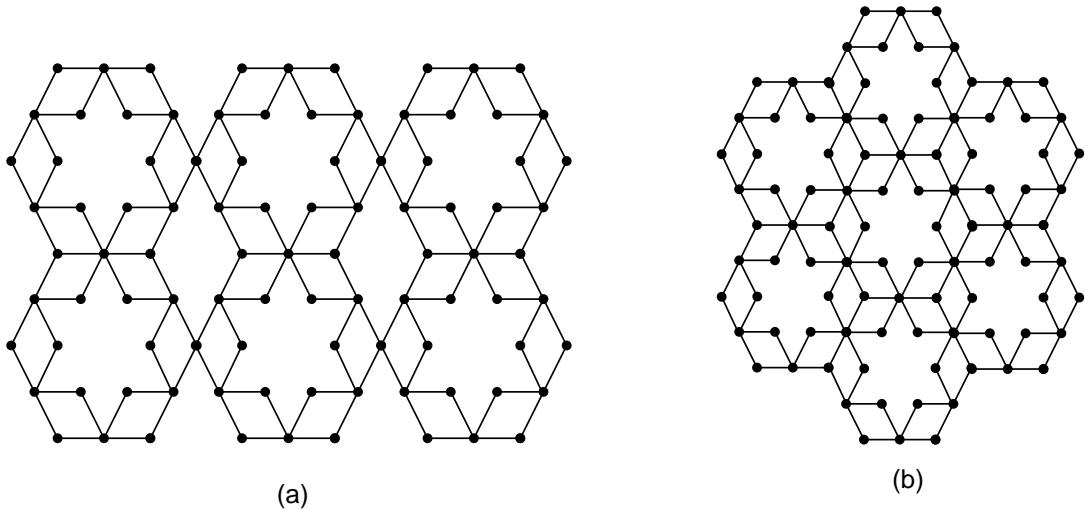

| 3.12 | Scalable architectures of HS topology (a) Mesh of Hexagonal stars ; (b) Honeycomb Hexagonal star                                                                                               | 54 |

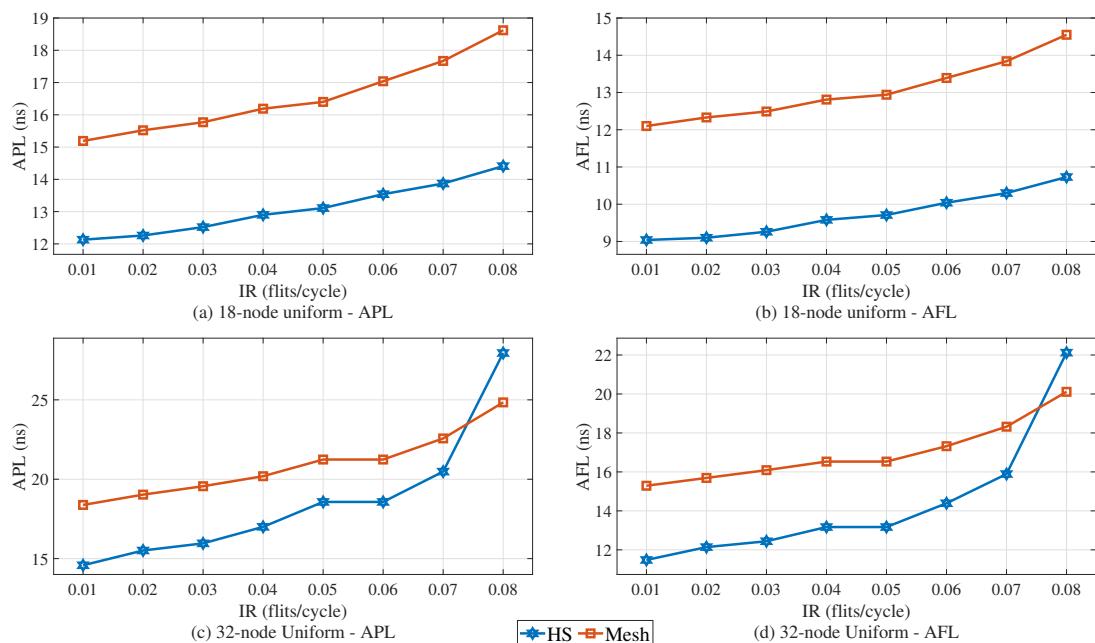

| 3.13 | Simulation results of HS and Mesh topologies for uniform traffic pattern                                                                                                                       | 57 |

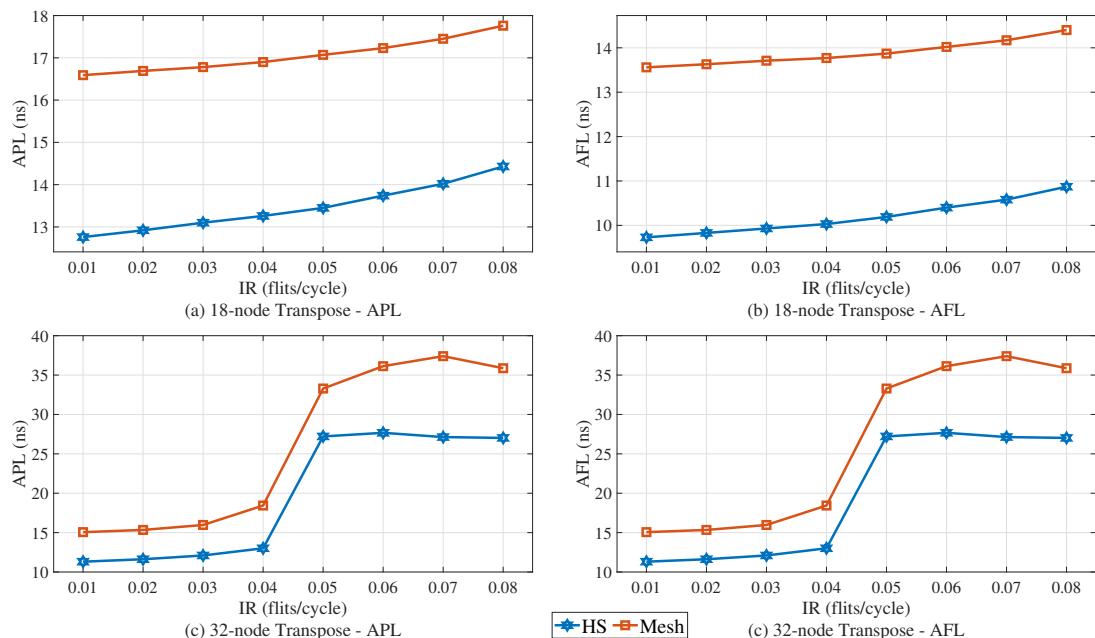

| 3.14 | Simulation results of HS and Mesh topologies for transpose traffic pattern                                                                                                                     | 58 |

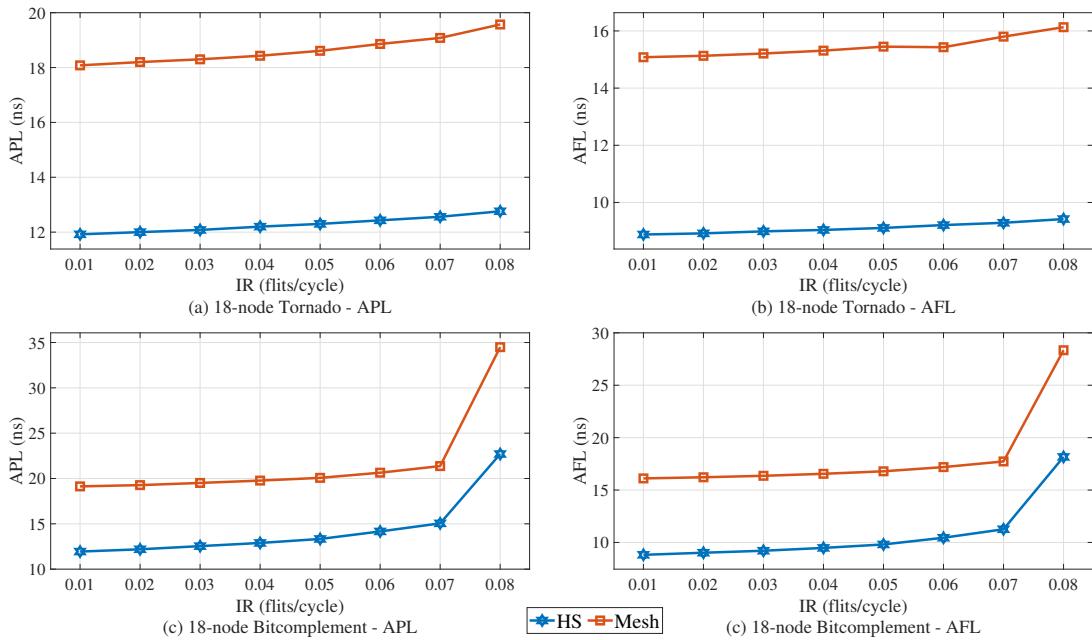

| 3.15 | Simulation results of HS and Mesh topologies for tornado and bit complement traffic pattern                                                                                                    | 59 |

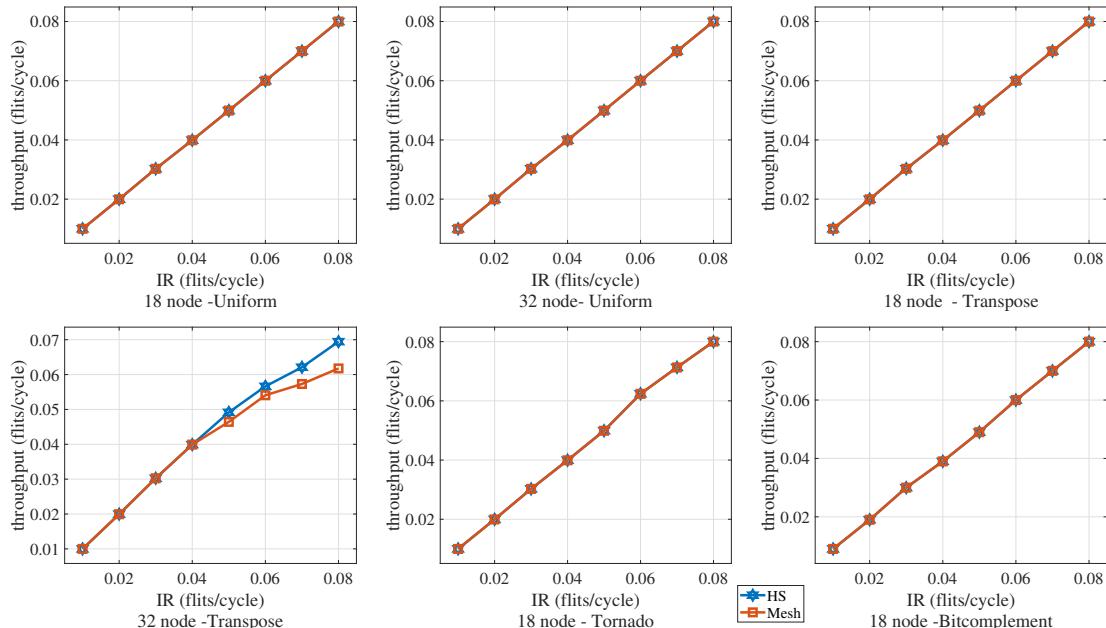

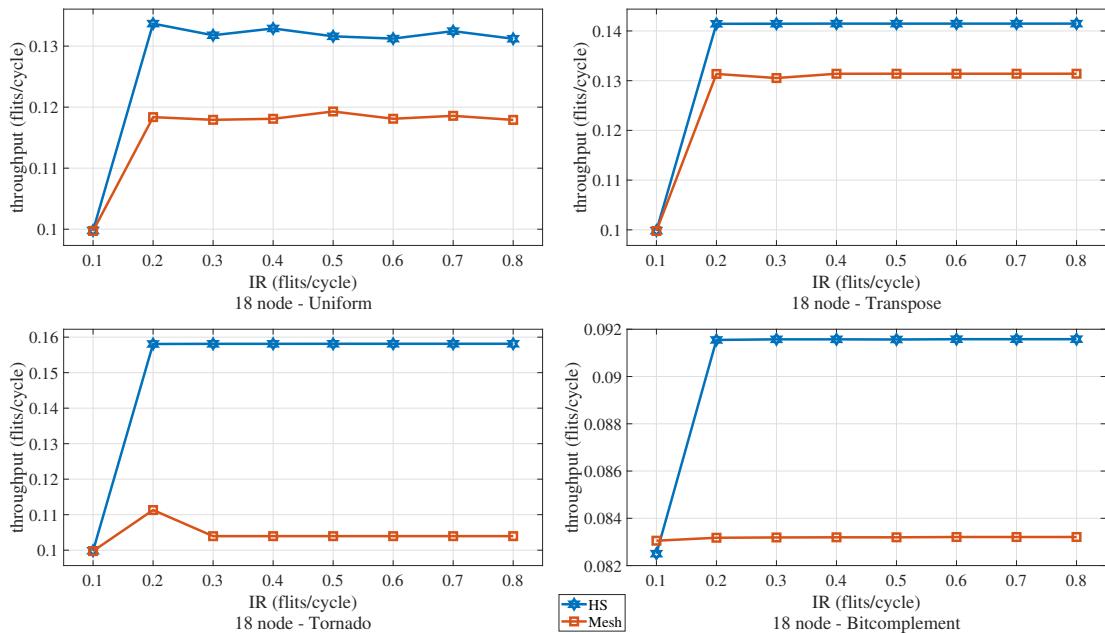

| 3.16 | Throughput characteristics of HS and Mesh topologies for varying injection rates from 0.01 to 0.08                                                                                             | 59 |

| 3.17 | Throughput characteristics of HS and Mesh topologies for varying injection rates from 0.1 to 0.8                                                                                               | 60 |

| 4.1  | (a)16 Node DiamondMesh; (b)36 Node DiamondMesh                                                                                                                                                 | 67 |

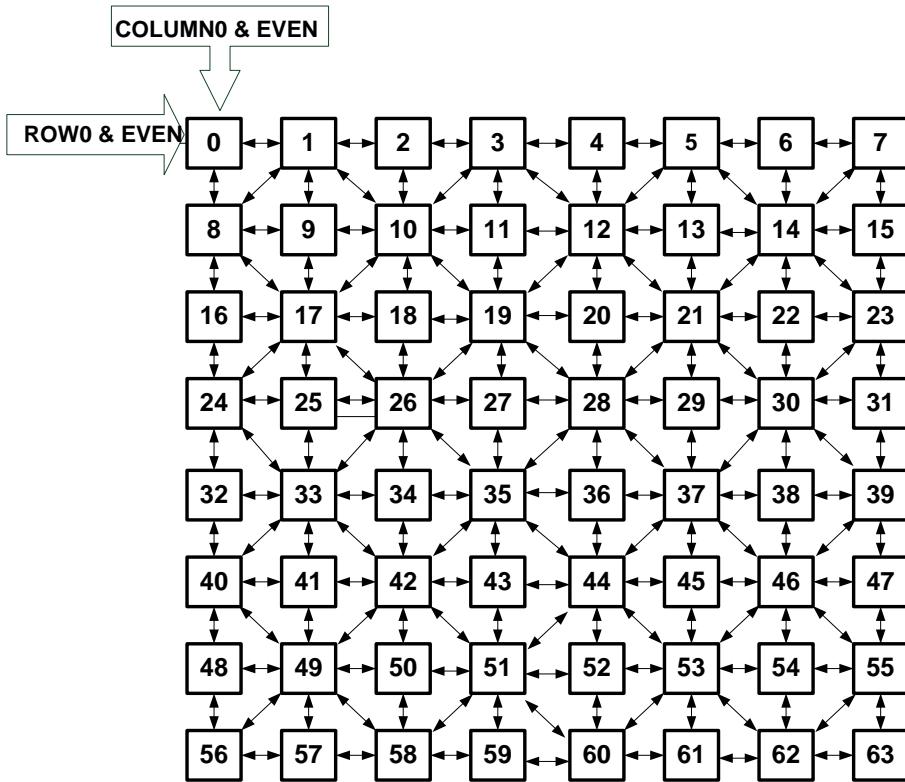

| 4.2  | 8×8 DiamondMesh                                                                                                                                                                                | 68 |

| 4.3  | Router with Port Directions                                                                                                                                                                    | 69 |

| 4.4  | (a) Mesh; (b) DMesh; (c) XDMesh; (d) ZMesh                                                                                                                                                     | 71 |

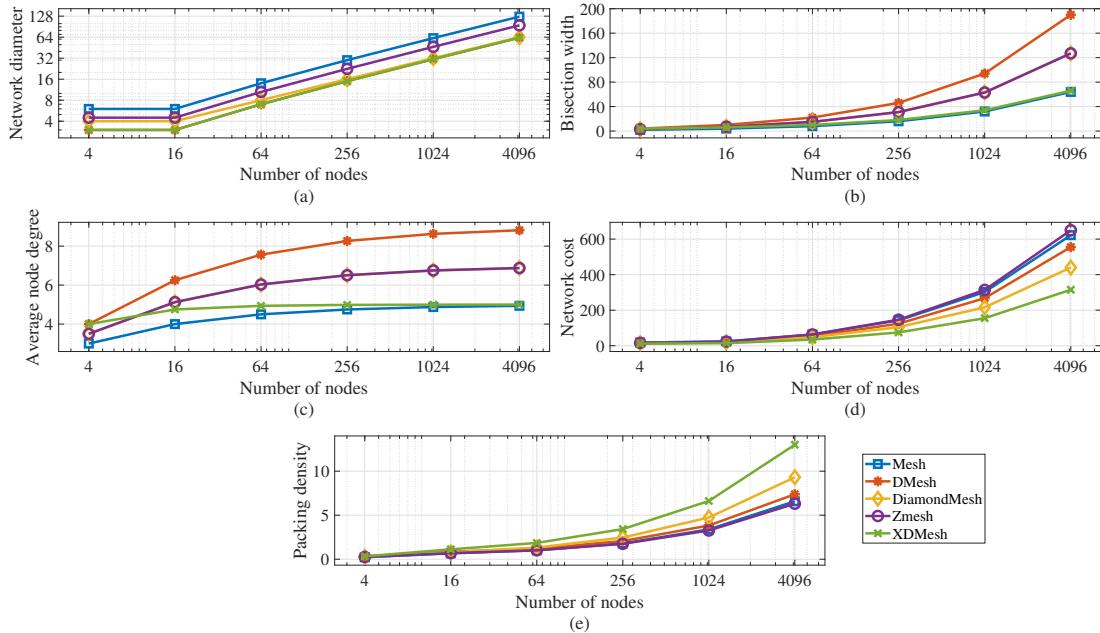

| 4.5  | Graphical comparison of topological parameters of the considered topologies; (a)Network Diameter; (b)Bisection Width; (c)Average Node Degree; (d)Network Cost; (e) Packing Density             | 74 |

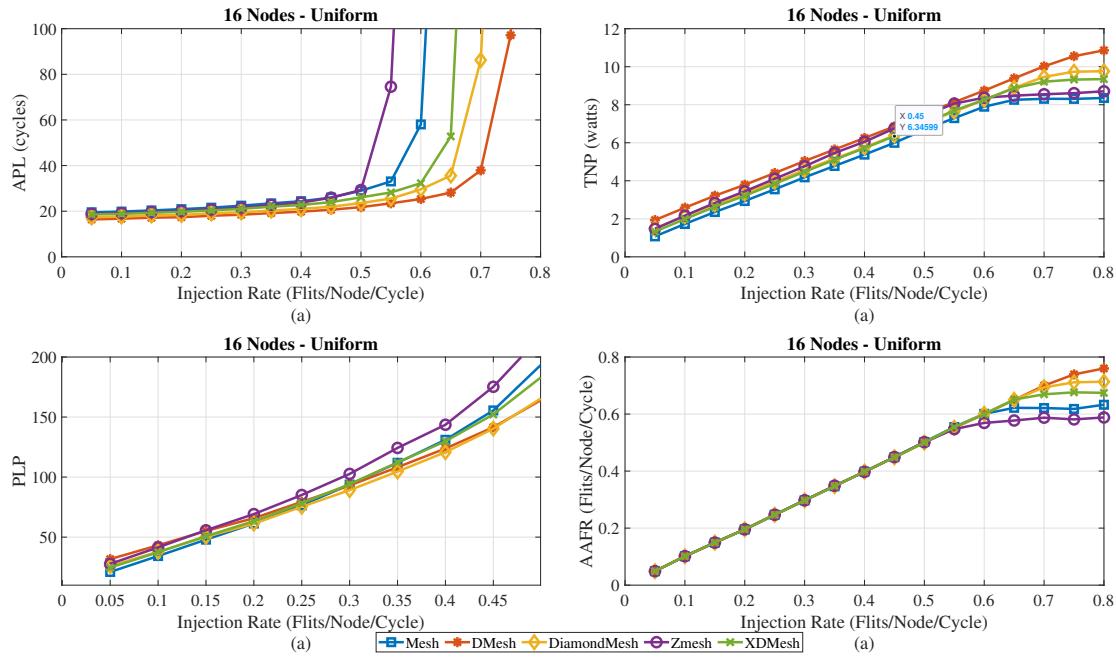

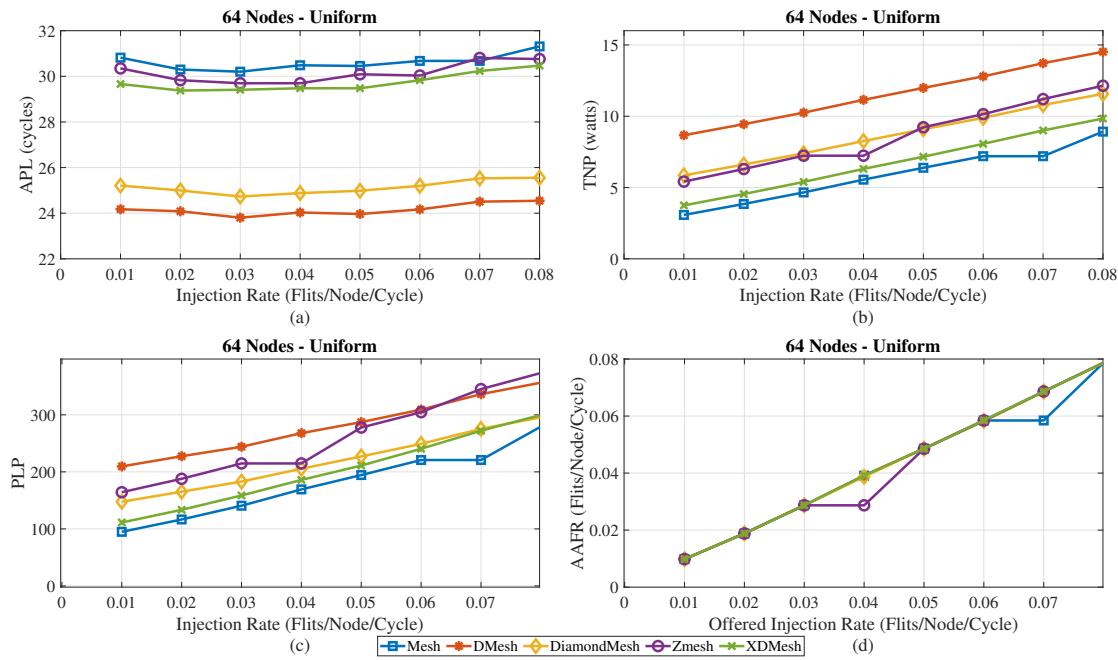

| 4.6  | Comparison of 16 node network simulated under uniform traffic pattern.                                                                                                                         | 76 |

---

|      |                                                                                                                                                                                                                                                                                    |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

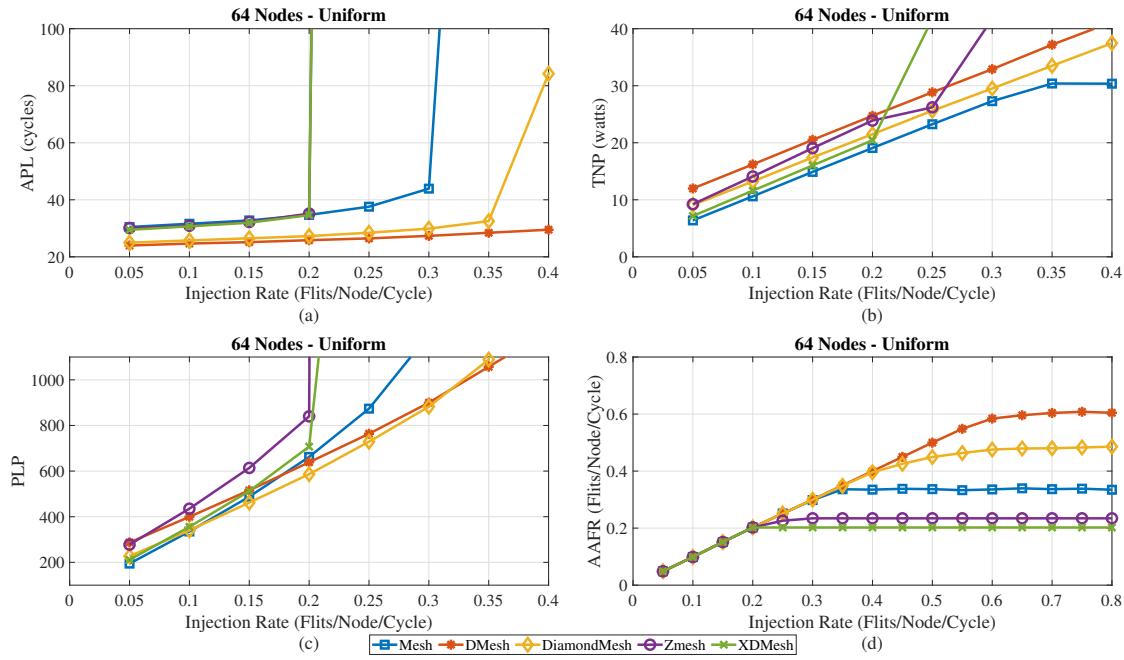

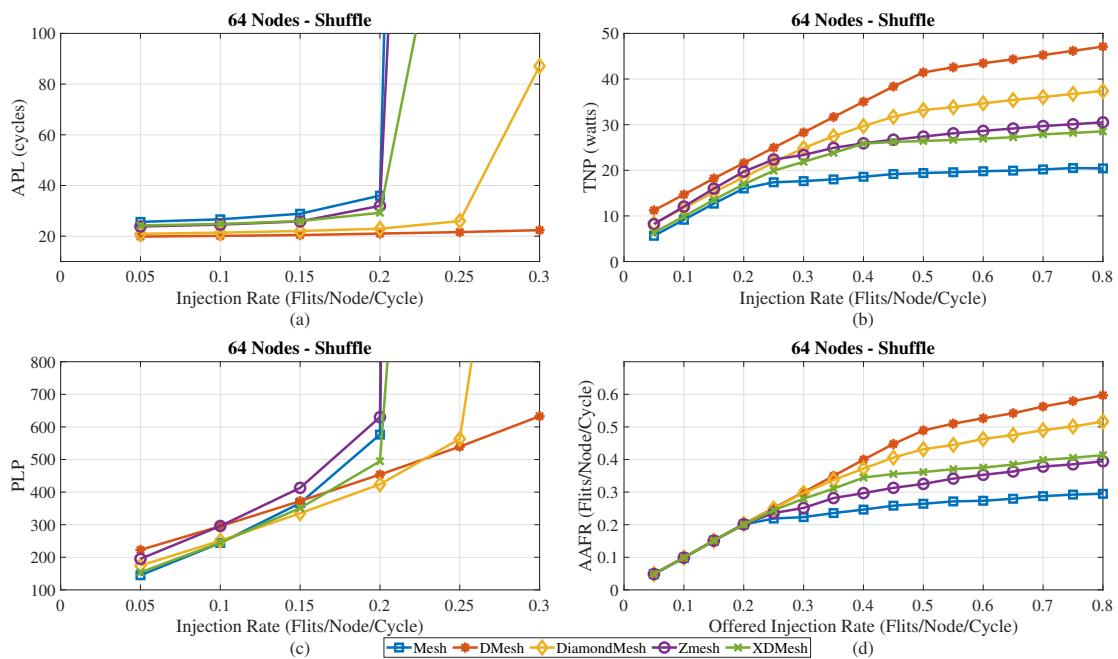

| 4.7  | Comparison of 64 node network simulated under uniform traffic pattern . . . . .                                                                                                                                                                                                    | 77 |

| 4.8  | Comparison of 64 node network simulated under uniform traffic pattern for low injection rates . . . . .                                                                                                                                                                            | 78 |

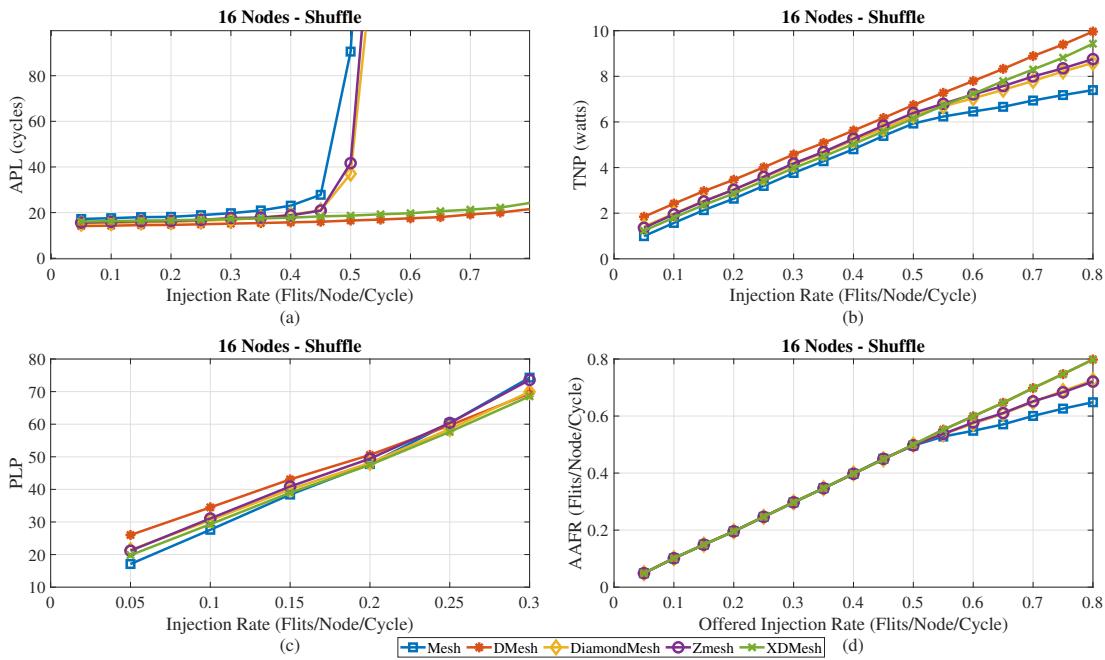

| 4.9  | Comparison of 16 node network simulated under shuffle traffic pattern . . . . .                                                                                                                                                                                                    | 79 |

| 4.10 | Comparison of 16 node network simulated under bit reversal traffic pattern . . . . .                                                                                                                                                                                               | 80 |

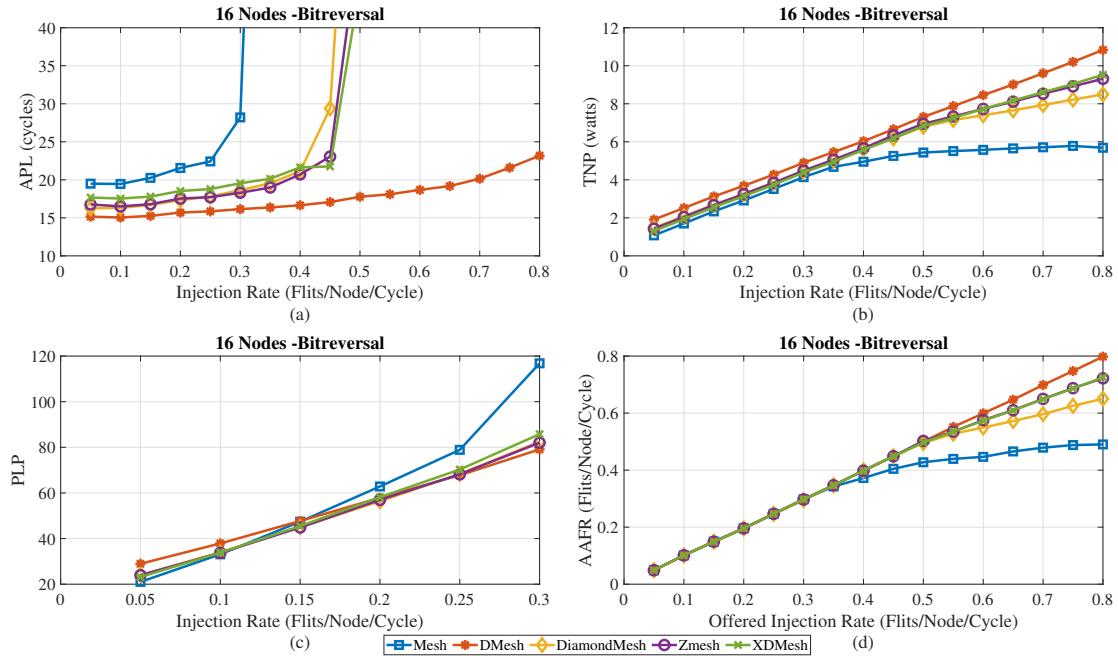

| 4.11 | Comparison of 64 node network simulated under shuffle traffic pattern . . . . .                                                                                                                                                                                                    | 80 |

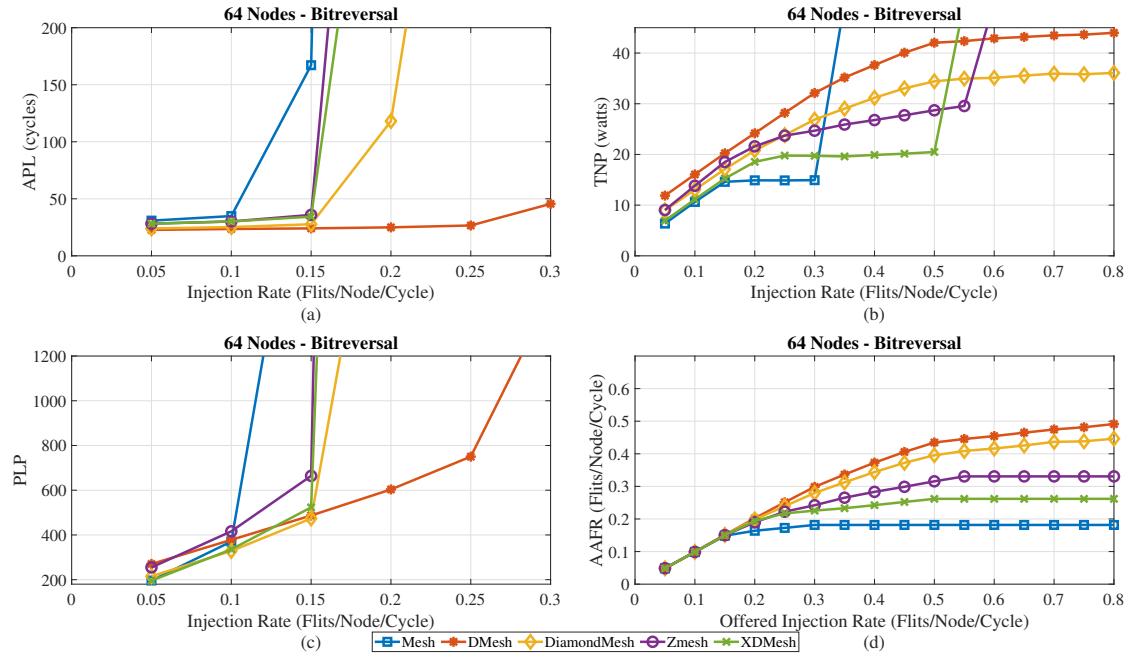

| 4.12 | Comparison of 64 node network simulated under bit reversal traffic pattern . . . . .                                                                                                                                                                                               | 81 |

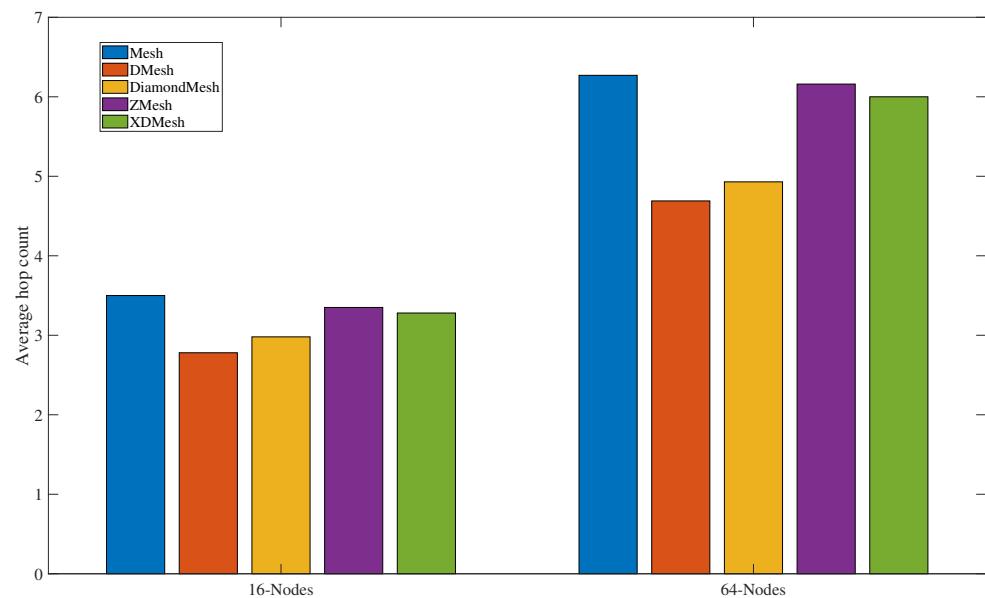

| 4.13 | Comparison of Average Hop Count of 16 and 64 node networks simulated under uniform traffic . . . . .                                                                                                                                                                               | 81 |

| 4.14 | Comparison of normalised average packetLatency (APL) 64 node network simulated under real application workloads . . . . .                                                                                                                                                          | 83 |

| 4.15 | Comparison of normalised power density 64 node network simulated under real application workloads . . . . .                                                                                                                                                                        | 83 |

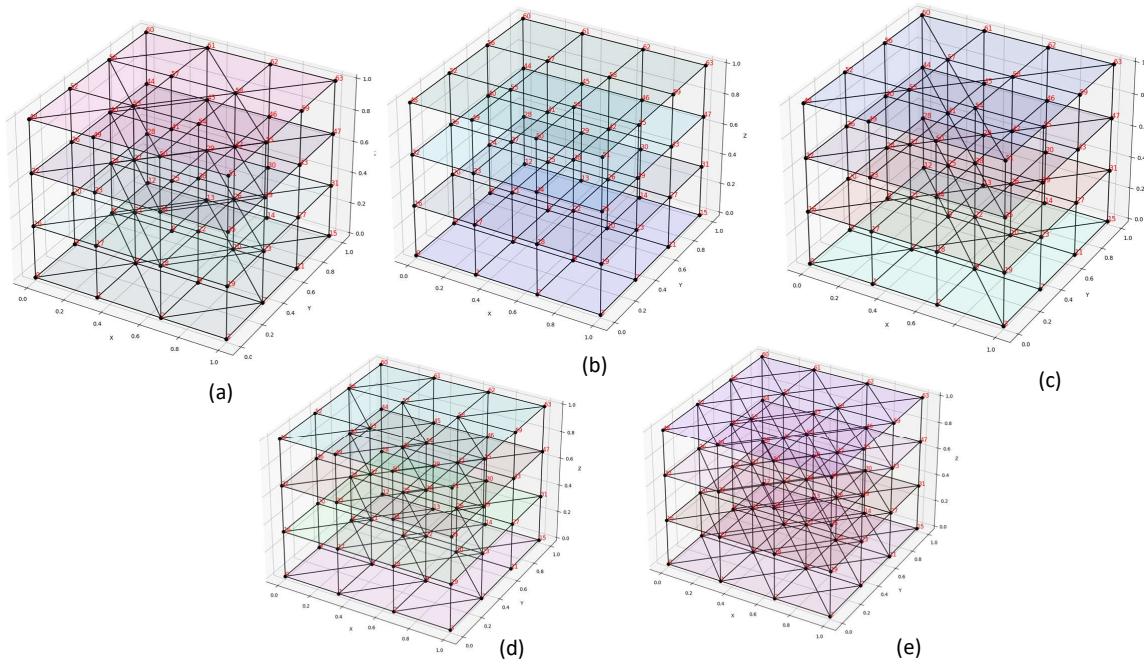

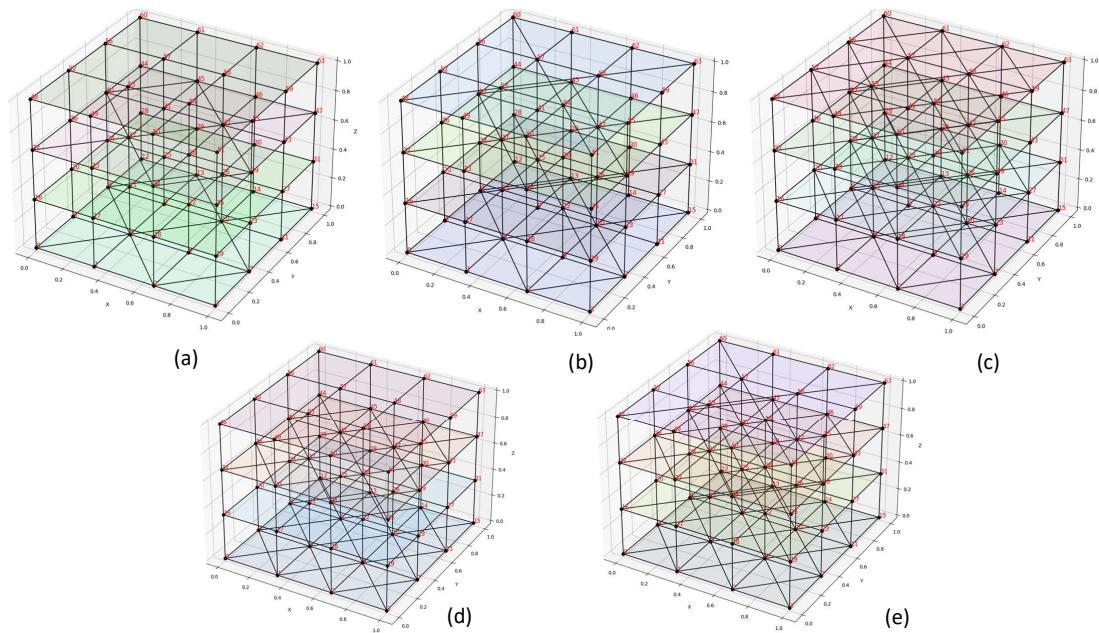

| 4.16 | (a)3D DiamondMesh; (b)3D Mesh; (c) 3D XDMesh; (d) 3D ZMesh; (e) 3D DMesh . . . . .                                                                                                                                                                                                 | 86 |

| 4.17 | (a)DiamondMesh+Mesh; (b)DiamondMesh+XDMesh; (c) DiamondMesh+DMesh; (d) DMesh+Mesh; (e) DMesh+XDMesh . . . . .                                                                                                                                                                      | 86 |

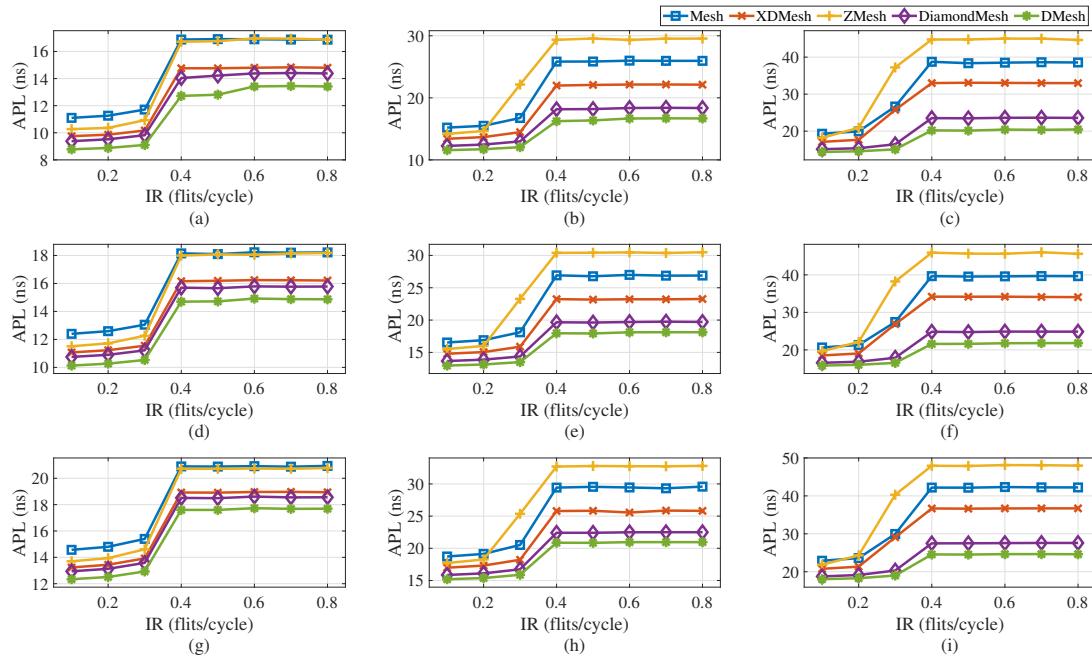

| 4.18 | Average Packet Latency characteristics of the considered topologies (a)16 nodes(1L); (b)36 nodes(1L); (c)64 nodes(1L); (d)32 nodes(2L); (e)72 nodes(2L); (f)128 nodes(2L); (g)64 nodes (4L); (h)144 nodes (4L); (i)256 nodes (4L) 1L:1 Layer, 2L: 2 Layers, 4L: 4 Layers . . . . . | 90 |

| 4.19 | Average Packet Latency characteristics of heterogeneous architectures (a) 64 nodes(4L); (b) 256 nodes(4L) . . . . .                                                                                                                                                                | 92 |

| 5.1  | Methodology to construct hierarchical hybrid wired-wireless NoC . . . . .                                                                                                                                                                                                          | 96 |

| 5.2  | 256_node hierarchical hybrid wired-wireless NoC . . . . .                                                                                                                                                                                                                          | 97 |

| 5.3  | 1024-node with 16 subnets . . . . .                                                                                                                                                                                                                                                | 98 |

---

|      |                                                                                       |     |

|------|---------------------------------------------------------------------------------------|-----|

| 5.4  | Proposed architectures                                                                | 99  |

| 5.5  | Comparison of 256-node configurations simulated under uniform random traffic pattern  | 105 |

| 5.6  | Comparison of 256-node configurations simulated under transpose traffic pattern       | 106 |

| 5.7  | Comparison of 256-node configurations simulated under bit reversal traffic pattern    | 107 |

| 5.8  | Comparison of 256-node configurations simulated under shuffle traffic pattern         | 110 |

| 5.9  | Comparison of 1024-node configurations simulated under uniform random traffic pattern | 111 |

| 5.10 | Comparison of 1024-node configurations simulated under transpose traffic pattern      | 111 |

| 5.11 | Comparison of 1024-node configurations simulated under bit reversal traffic pattern   | 112 |

| 5.12 | Comparison of 1024-node configurations simulated under shuffle traffic pattern        | 112 |

# List of Tables

|      |                                                                                                                               |    |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Summary of comparison of key features of on-chip interconnect technologies                                                    | 38 |

| 3.1  | Number of nodes for a given number of Hexagonal Stars                                                                         | 44 |

| 3.2  | Comparison of total number of Buffer Resources for HS and Mesh topologies                                                     | 50 |

| 3.3  | Topological Parameters                                                                                                        | 51 |

| 3.4  | Numerical comparison of the Topological Parameters                                                                            | 52 |

| 3.5  | Comparison of HS and Mesh topologies simulated under uniform traffic pattern varying injection rates                          | 57 |

| 3.6  | Comparison of HS-18 and Mesh-18 topologies simulated under transpose traffic pattern varying injection rates                  | 58 |

| 3.7  | Comparison of HS-32 and Mesh-32 topologies simulated under transpose traffic pattern varying injection rates                  | 58 |

| 3.8  | Comparison of HS and Mesh topologies simulated under tornado and bit complement traffic patterns varying injection rates      | 60 |

| 3.9  | Comparison of HS-18 and Mesh-18 topologies simulated under different traffic patterns varying injection rates from 0.1 to 0.8 | 61 |

| 3.10 | Synthesis Results                                                                                                             | 64 |

| 4.1  | Port directions of the Routers in $8 \times 8$ DiamondMesh                                                                    | 70 |

| 4.2  | Topological Parameters                                                                                                        | 72 |

| 4.3  | Network configuration parameters                                                                                              | 75 |

|     |                                                                     |     |

|-----|---------------------------------------------------------------------|-----|

| 4.4 | Comparison of Area occupied by considered topologies . . . . .      | 82  |

| 4.5 | Synthesis Results . . . . .                                         | 85  |

| 4.6 | Configuration Parameters for Homogeneous configurations . . . . .   | 88  |

| 4.7 | Number of Links . . . . .                                           | 89  |

| 4.8 | Tradeoff between the number of links and APL . . . . .              | 89  |

| 4.9 | Configuration Parameters for Heterogeneous configurations . . . . . | 91  |

| 5.1 | Proposed architecture specifications . . . . .                      | 101 |

| 5.2 | Network configuration parameters . . . . .                          | 103 |

| 5.3 | Results comparison for 256 nodes . . . . .                          | 107 |

| 5.4 | Results comparison for 1024 node networks . . . . .                 | 113 |

| 5.5 | Comparison of links and buffer resources . . . . .                  | 116 |

## List of Abbreviations

|       |                               |

|-------|-------------------------------|

| 2D    | Two Dimensional               |

| 3D    | Three Dimensional             |

| AAFR  | Average Accepted Flit Rate    |

| APL   | Average Packet Latency        |

| DOF   | Dimensional Order Routing     |

| DSM   | Deep Submicron                |

| EDP   | Energy-Delay-Product          |

| EPP   | Energy per packet             |

| FF    | FlipFlop                      |

| GAD   | Global average delay          |

| HCM   | HoneyComb Mesh                |

| HN    | Hub node                      |

| HS    | Hexagonal Star                |

| IC    | Integrated Circuit            |

| IP    | Intellectual Property         |

| IR    | Injection Rate                |

| LUT   | Look Up Table                 |

| MPSoC | Multiprocessor System-on-Chip |

| NoC   | Network-on-Chip               |

| ns    | nano second                   |

| NT    | Network Throughput            |

| PE    | Processing Element            |

| PIR   | packet injection rate         |

| PLP   | Power-Latency-Product         |

| SN    | Subnet node                   |

|       |                              |

|-------|------------------------------|

| SoC   | System-on-Chip               |

| TE    | Total Energy                 |

| TNP   | Total Network Power          |

| TSV   | Through Silicon Via          |

| VC    | Virtual Channel              |

| VLSI  | Very Large Scale Integration |

| WiNoC | Wireless Network-on-chip     |

| WI    | Wireless Interface           |

| WLs   | Wireless Links               |

| WR    | Wireless Radiohub            |

# Chapter 1

## Introduction

Network-on-Chip (NoC) is an interconnect architecture that is scalable, flexible, robust, and communication-centric. It is a game-changing solution for connecting a large number of cores in the complex Multiprocessor System-on-Chip (MPSoC) domain [6]. With rapid technological advancements, the number of components integrated on a standard sized IC (a chip), has been increasing in accordance with Moore's law. The definition of a chip changes with the integration scale. In LSI (Large Scale Integration) systems, a chip represents a component of a system module. In VLSI (Very Large Scale Integration) systems, a chip represents a module of a system. In ULSI (Ultra Large Scale Integration), a chip represents an entire system which is termed as a System-on-chip (SoC). As the technology scales, the complexity of SoC increases thereby posing serious challenges to researchers. In the Deep Submicron (DSM) era, to cope with increasing performance requirements of Multi-processor Systems-on-Chip (MPSoCs), on-chip interconnect architectures have evolved from shared buses to hierarchical buses and then to bus matrix architectures. Bus architectures have limited scalability. As the complexity of the SoC architecture increases, communication becomes a bottleneck to performance. Communication as well as coordination becomes a major concern. Growing chip density and demand for efficient and scalable communication infrastructure has led to the evolution of NoCs which address the limitations of Bus infrastructure. An efficient interconnection architecture should possess the potential to exchange data with low latency, low power consumption while occupying limited space. Ideally, communication infrastructure should be designed in a way that it brings trade-off among power, area and delay metrics [6–8].

## 1.1 Fundamentals of Network-on-Chip (NoC)

### 1.1.1 Evolution of NoC

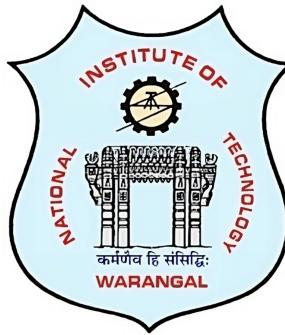

Ever since the introduction of the SoC concept, the SoC communication infrastructure has generally been facilitated by custom buses and point-to-point links. With increasing number of cores, the communication infrastructure has undergone an evolution from custom buses to NoC as shown in Figure 1.1.

**Figure 1.1** Evolution of NoC [1]

Shared buses such as AMBA bus and CoreConnect are popularly used communication infrastructure in SoCs. Even though they support a modular design approach, they become a performance bottleneck as the system bandwidth requirements scale up. Hierarchical Bus using multiple buses or bus segments alleviate the load on the main bus. This hierarchical structure allows communication between modules on the same bus segment without causing congestion on other bus segments. This structure is complex, offers less flexibility and scalability. Bus Matrix, a crossbar bus architecture, consists of a matrix switch fabric. To facilitate parallel multiple communications, this matrix connects all the inputs with all the outputs. However, the design of crossbar-based architecture is complex for multicore SoCs. With multi-core SoCs, bus architectures become a communication bottleneck. The success and scalability observed in switch-based networks and packet-based communication in parallel computing have motivated researchers to introduce the Network-on-Chip (NoC) architecture as a promising solution to meet intricate

on-chip communication challenges [1; 9].

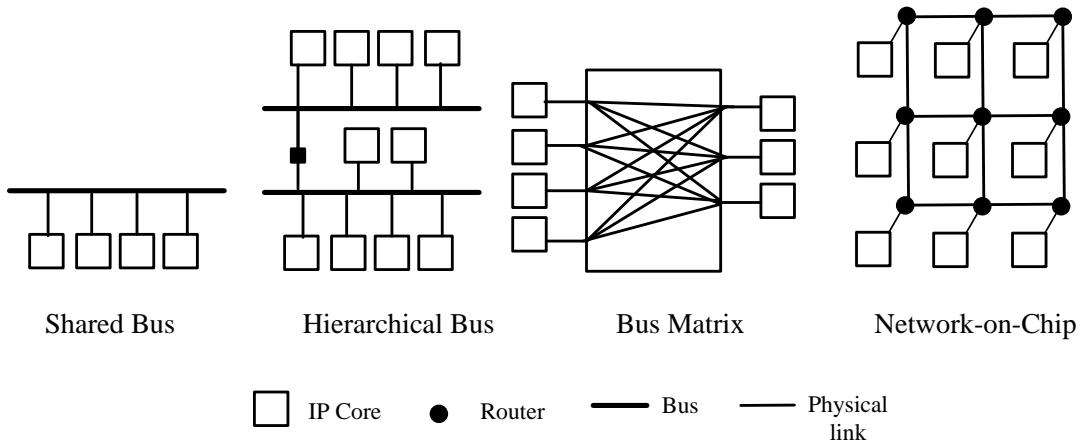

### 1.1.2 NoC: A layered architecture

Network-on-Chip (NoC) has evolved as a viable solution to meet the performance, bandwidth and power demands of complex MpSoC architectures. NoC has moved from computation-centric designs to communication-centric designs. NoC architecture can be realized as a layered architecture consisting of application, transport, network, data link, and physical layers as shown in Figure 1.2. A NoC router should contain both hardware and software to support the layers [2; 3].

**Figure 1.2** Layered architecture of NoCs [2]

#### 1.1.2.1 Application layer

An application can be represented as a set of computational units that are interconnected by communication infrastructure to exchange data. The computational units are termed processing elements (PEs). Network on chip forms the communication infrastructure of the application. The software layer is made up of system software which provides an abstraction of the underlying hardware components. The application is thus

implemented as a set of computational and communication tasks by the software. This software is tightly coupled to the network interface (NIs) which connects the PEs to the interconnect fabric. To get the best trade-off between power and performance, application mapping and scheduling should be considered with several kinds of architecture parameters.

#### **1.1.2.2 Transport layer**

The transport layer deals with packetizing algorithms, which decompose the message into packets at the source and assemble them at the destination to reproduce the message. The granularity of packetization i.e., the size of the packet, is a significant design parameter. It has an impact on the behaviour of network control algorithms which affect the performance, power and area footprint of NoC interconnect. Also, the transport layer addresses the congestion and flow control issues. It has to implement certain flow control mechanisms to assure congestion free routing of the packets, correct delivery of data with efficient utilisation of resources.

#### **1.1.2.3 Network layer**

Network layer is responsible for switching and routing the packets from source to destination. Switching techniques are used to establish the type of connection and routing algorithms determine the path strategies to transmit the packet from source to destination. Selection and implementation of the routing algorithms depend on two important aspects – determining the packet routes and resolving the conflicts if two packets request for the same route at the same time. Also, Network layer deals with the network topology or interconnect architecture which determines the physical layout of the processing elements (PEs) and the interconnections among the PEs. A suitable topology for the application is selected first, based on which routing algorithm is chosen.

#### **1.1.2.4 Data Link layer**

The Data Link Layer is divided into two sub-layers: bottom sub-layer which is closest to physical layer is Medium Access Control (MAC) sub-Layer and the upper sub-layer which is closer to the network layer is the Data Link Control (DLC) sub-layer. MAC sub-layer is responsible for regulating access to the physical layer and resolving contention issues. DLC sub-layer is responsible for error detection and correction schemes, error-

---

tolerant schemes to ensure reliable operation of the system.

#### 1.1.2.5 Physical layer

The physical layer is concerned with physical links or any other alternatives to wires which can act as the physical medium of data transmission. Bus architectures performance is limited by the long interconnect lengths, particularly in DSM technologies where wire delay prevails over gate delay. Pipelining or inserting buffers/registers to divide the longer interconnects into shorter segments can be employed to alleviate long delays. However, this approach often results in inefficient resource utilization, as the entire bus remains busy until a data transfer is completed, preventing the use of vacant wire segments by other masters. Network-on-Chip (NoC) fabrics offer a solution to the challenges posed to lengthy interconnects and inefficient utilisation of Bus resources that result in excessive wire delay. NoCs employ shorter, regularly sized wires (links) separated by switches (routers). Data packets traverse these links, also known as switch-to-switch links, within a single cycle, after which they are buffered in the routers before being routed to another link in the subsequent cycle. Unlike buses, NoCs are inherently designed to address wire delay from the outset, providing a more structured approach that simplifies the designer's efforts and reduces overall design time. In the giga billion transistor era or kilo-core MPSoC era, the wires (interconnects) cannot scale to the extent technology scales. So, in order to cope with the performance requirements of the complex MPSoCs, which even traditional NoCs are not able to meet, other promising technologies have evolved. The promising technologies which can replace the traditional metallic interconnects include Photonic Interconnects, Wireless Interconnects, Carbon Nanotubes (CNT).

#### 1.1.3 Basic building blocks of NoC

A typical NoC architecture as shown in Figure 1.3 comprises a set of processing elements (PEs) or IP core interconnected by means of a micro network of routers. The routers of the network are linked by multiple wire segments known as links. A network interface (NI) of a PE makes a logical connection between the PE and the network. NI packetizes the data generated by PE. The NI is connected to a router of the micro network. The input buffers of the router accepts data from NI or from other routers of the network. In Figure 1.3 (a), Mesh topology is considered [3] .

---

**Figure 1.3** (a) A typical NoC architecture; (b) A generic NoC router [3]

The basic building blocks of the NoC fabric are the Links, Router and Network interface.

A Link is composed of a set of wires and connects two routers in the network to transmit data among the cores of the architectures. Link consists of one or more physical or logical channels, each channel comprises a set of wires.

NoC router comprises a number of input and output ports, buffers, control logic, crossbar switch. Input and output ports connect the router to its neighbouring routers in the network or the PE. The control logic block implements the routing and flow control policies such as routing computation, arbitration. Crossbar switch connects the input ports to the output ports. The primary design aspects of the router includes implementing routing and flow control strategies, arbitration and switching logic, buffering.

Network Interface also called Network adapter makes the logical connection between the PEs and the network. It decouples computation from communication. It implements two interfaces, a front end and a backend. Frontend manages the core requests while backend handles the network protocol such as assembling and disassembling of packets,

implementing synchronization protocols and thus facilitating a layered design approach.

Topology, routing and flow control are critical design aspects of NoC architectures. The subsequent sections provide an overview on these aspects.

#### 1.1.4 Topology

Topology is one among many key design aspects of the interconnection architecture. Topology refers to the physical arrangement of nodes and the connecting links among the nodes of the interconnection architecture. It is the most critical design aspect of NoC, as it deals with wire lengths, node degree and routing strategies that affect the performance of the architecture. Topology determines the number of hops required for a packet to traverse between a pair of source and destination nodes thereby influencing the network latency and throughput. Topology determines the wired link lengths thereby influencing the area and power consumption of the architecture [10]. Further, topology determines the total number of alternate paths between a pair of nodes. With a greater number of alternate paths, higher throughput can be achieved and faster exchange of messages can be achieved by employing adaptive routing strategies. During the past few years, many NoC topologies like Mesh, CMesh, Torus, Spidergon, Octagon, Tree, Mesh of Tree, Honeycomb, Ring, Hexagonal, etc. have been proposed [10–14]. Star, Ring, Spidergon, Binary Tree, Mesh, and Torus are among the commonly utilized topologies in Network-on-Chip (NoC). Each topology has its own merits and demerits. Ring Topology is the most simple and one of the most widely employed topologies. In the Ring topology, all the nodes are connected in a circular fashion forming a closed loop as shown in Figure 1.4 (a). In this, each core is connected to exactly two neighboring cores. Design, deployment, and troubleshooting are easier. However, it has very poor scalability and poor path diversity.

Star topology connects all the nodes to a single centrally located hub node as shown in Figure 1.4 (b). Irrespective of the number of nodes, the network diameter excluding the hub is 2. The topology is simple and offers a minimum hop count. However, failure of the central hub results in the failure of the entire system. It is suitable for small network sizes.

Spidergon is similar to Ring topology enriched with across links between opposite nodes as shown in Figure 1.4 (c). For a node, clockwise, counterwise and across links

---

**Figure 1.4** NoC Topologies [1]

are present. This topology is simple, regular with vertex symmetry, and offers a constant node degree of 3 translating to simple and cost-effective routers. The topology is only for an even number of nodes. However, the topology has poor path diversity and fault tolerance.

Mesh topology comprises cores or nodes connected as a grid as shown in Figure 1.4 (d). Each single core is connected to a router. Each router except those at the corners and boundaries is connected to four neighboring routers. It has a simple, regular, and scalable structure. Mesh provides good fault tolerance because multiple paths exist between a pair of nodes. It has a drawback of a larger diameter and it increases with an increase in system size. This is due to the nonuniform node degree. The degree of the corner, edge, and inner nodes is 2,3,4 respectively. Because of this the associated bandwidth of corner and edge nodes is lower than that of the inner nodes.

Torus topology, a topology similar to the Mesh topology, is shown in Figure 1.4 (e). The limitation of the large network diameter of Mesh is addressed by Torus topology. Torus is formed by directly connecting the end nodes that are in the same row or same

column resulting in uniform network diameter of 4, a better bisection width. However, as the system size grows, the long wrap-around links leads to increased latency and increased complexity.

Considering the benefits of scalability, path diversity, fault tolerance, link complexity, short range links, simple structure of Mesh topology, it has become a preferred choice for less sophisticated networks. However, as the system size grows, the network diameter of the Mesh increases resulting in diminished performance.

#### 1.1.4.1 **Significant topological parameters considered**

Any interconnect network's performance is determined by its topological characteristics such as network diameter, bisection width, node degree, number of links, network cost, and packing density.

1. **Network diameter (Diameter):** It is the shortest distance between the two most distant nodes in the network. In other words, once the shortest path length from every node to all other nodes is calculated, the Network diameter is the longest of all the calculated path lengths.

2. **Node degree:** The node degree is the number of edges connecting a node to its neighbouring nodes. (Node refers to router or processing element (PE). If the node is a processing element, the node degree is '1' i.e., only the one edge that connects the PE to its router. If the node is a router, then the node degree includes the edges that connect the router to its neighboring routers and the edge that connects the router to the PE).

3. **Bisection width:** The bisection width of a network is the minimum number of links required to be removed for a network or graph to be bisected.

4. **Average Distance:** It is the average of the distances (hop count) between all pairs of nodes in a network.

5. **Network cost:** The Network cost is the scalar product of the Node degree and Network diameter.

$$\text{Network cost} = \text{Network diameter} \times \text{Degree}$$

6. **Scalability:** Scalability is defined as the property of expanding the network size, getting consistent performance.

7. **Link:** The physical channel that connects a node to another node.

8. **Packing density:** The packing density of a network is defined as the total number of nodes per total network cost. It indicates the size of the chip area of the VLSI layout.

$$\text{Packing density} = (\text{Total number of nodes}) / (\text{Network diameter} \times \text{Node degree})$$

The interconnection network with smaller diameter, larger bisection width, smaller node degree, a greater number of links, low network cost and high packing density achieves superior latency and throughput characteristics. A smaller diameter indicates fewer hops to reach the most remote nodes. Large bisection width enables a faster exchange of information. More number of links support higher bandwidth. Smaller node degree means an easier to build network. Larger packing density indicates smaller chip area of VLSI layout [10].

Mesh is the most extensively used and favoured architecture for implementing less sophisticated SoCs due to its simple, scalable, regular structure, low-radix routers and short-range links. However, as the network scales, Mesh suffers from degraded performance because of large diameter [15]. There are numerous approaches to optimize the performance of the network. Some of the approaches are bypassing some intermediate nodes by inserting express channels in k-ary n-cube networks to reduce latency [16], inserting long range links between distant nodes in the standard mesh [17–19], employing larger buffers, increasing number of virtual channels (VCs) [20; 21], improving router architecture [22; 23], inserting diagonal links in the regular Mesh [24–27], combining two topologies [28; 29] or two interconnect technologies i.e., hybrid topologies [30; 31].

### 1.1.5 Routing

Routing determines the traversal path of a packet from the source node to the destination node. Routing algorithms can be classified based on several categories. Routing

algorithms can be classified as source or distributed based on the node at which routing decision takes place. In source routing, pre-computed routing tables are stored at the node's network interface (NI). In distributed routing, each packet carries the source address and destination address. The routing decision is implemented in each routing either by a routing table or by executing a function. Further, depending on the adaptability, both source and distributed routing can be classified as deterministic (or static), oblivious and adaptive (or dynamic). In deterministic routing, packets consistently follow a predefined path from source to destination, ensuring in-order delivery. In contrast, oblivious routing selects paths randomly or cyclically. In both deterministic and oblivious routing, current state of the network is not taken into account. In contrast, adaptive routing makes decisions based on the current state of the network such as congestion, links availability e.t.c., dynamically choosing alternative paths to bypass congested or faulty links. Consequently, in-order delivery of the packets is not assured, necessitating packet reordering at the destination network interface (NI). Adaptive routing can be further classified as progressive routing and backtracking routing. In progressive routing, the header moves forward, reserving a new channel at each router. Backtracking routing permits the header to backtrack as well, releasing previously reserved channels. Backtracking algorithms are mainly used for fault-tolerant routing. Deterministic and adaptive routing can be categorized as minimal or non-minimal, depending on the number of hops taken from source to destination. In minimal routing, routing path from the source to the destination is the shortest possible between two nodes. Non minimal routing can use longer paths when a minimal path is not available, which can be advantageous for circumventing network congestion. Delay and power consumption are higher in non-minimal routing than in minimal routing as it requires more number of hops. Adaptive routing that follows a minimal path from source to destination can be classified as fully adaptive and partially adaptive [10].

The key challenge for any routing algorithm is to ensure that the routing remains free from livelock, deadlock and starvation conditions. Livelock occurs when a packet does not reach its destination, because it enters a cyclic path. Deadlock occurs when a packet does not reach its destination, because it is blocked at some intermediate resource. Starvation occurs when a packet does not reach its destination, because some resource does not grant access while it grants access to other packets.

---

### 1.1.6 Flow control

Flow control determines how network resources such as buffers, links e.t.c., are optimally allocated to the packets traversing in the network. The objective of flow control techniques is to avoid or manage congestion, provide error or fault recovery mechanisms for re-transmission of the packets in the network. Flow control protocols can be implemented at an end-to-end level or at a switch-to-switch level of the network. An end-to-end flow control results in higher average packet latency compared to a switch-to-switch flow control [10].

Credit-based flow control protocol is a standard protocol implemented for end-to-end scenario. In this protocol, an upstream node keeps count of data transfers, and the available free slots are referred as credits. When a transmitted data packet is consumed or forwarded, a credit is sent back. Switch-to-switch flow control can be further classified as flit level and packet level. In a switch-to-switch flow control, packet level shows higher latency than that of flit level. In NoC, flit level flow control technique is widely used. There are three types of switch-to-switch flit-level flow control protocols, namely, STALL/GO, T-Error, and ACK/NACK. STALL/GO is a simple implementation of an ON/OFF flow control protocol. It uses only two control wires: one that signals data availability going forward, and another that signals buffer status going backward, indicating either filled buffers ("STALL") or free buffers ("GO"). The T-Error flow control protocol is very complex as compared to other flow control protocols. It aims to improve either link performance or system reliability by catching timing errors. The T-Error protocol handles communication over physical links by either extending the distance between repeaters or increasing the operating frequency compared to a conventional design. T-Error lacks a really thorough fault handling in a real-time system operating in a noisy environment. T-Error's fault handling in a real-time system operating in a noisy environment is not adequately robust. In the ACK/NACK protocol, a copy of a data flit is stored in a buffer until an ACK signal is received. Upon receiving an ACK signal, the flit is removed from the buffer. However, if a NACK signal is received, the flit is scheduled for retransmission [10].

**Figure 1.5** On-Chip interconnect technologies

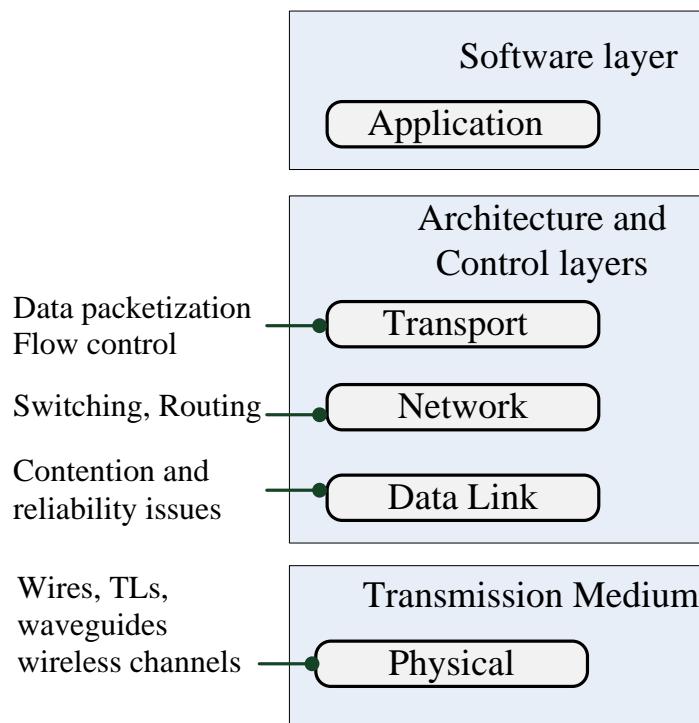

### 1.1.7 Interconnect technologies

As the trend to integrate more number of components on a single chip and demand for MPSoCs continues to grow, even the communication-centric NoC fabric becomes a limiting factor to the performance and power budgets of the architecture. This is because of the technological limitations of the electrical interconnects to scale power and delay at the same rate as that of transistors. The traditional electrical interconnects are not able to meet the requirements of complex SoCs, because with an increase in system size, the parasitic resistances and capacitances of the electrical interconnects increase leading to high power dissipations. The electrical interconnects may not be able to meet the power and performance demands of the future MPSoCs. Either they have to be augmented or even replaced with other emerging interconnect technologies like photonics and wireless.

Based on the interconnect technology, on-chip interconnects can be categorised as shown in Figure 1.5. Chapter 2 provides a review of the basic concepts, limitations, advancements of state-of-the-art and emerging on-chip interconnect technologies.

## 1.2 Motivation

Hybrid topologies have gained focus in NoC research. Hexagonal-shaped tiles pack efficiently without gaps between them. Non-Manhattan layouts reduce the wire lengths thereby reducing the area and power of the architectures. To fully utilize the benefits of non-Manhattan layouts, the architectures are to be implemented on hexagonal or octagonal ICs with maximal chip area usage. From previous studies, it is observed that hexagonal topologies have been less explored. Considering the benefits of hexagonal-

shaped structures and non-manhattan layouts, the authors were motivated to explore hexagonal-based hybrid topologies.

Further, with a demand for simple and scalable architectures to meet the performance requirements of complex SoC, there is a need to explore the topologies that can surpass Mesh topology in performance while retaining the simple, scalable and regular structure of Mesh. One among many approaches to address the limitation of Mesh topology is to incorporate diagonal links in the baseline Mesh in such a way that it outperforms Mesh in performance simultaneously bringing a trade-off among area-performance-power metrics in comparison with state-of-the-art diagonal mesh-based topologies.

Traditionally, Electrical wired interconnects have been utilised as communication infrastructure for SoCs. Electrical interconnects offer benefits such as lower power consumption, higher bandwidth, and smaller footprint for short-range communication. However, technology advancements enable the integration of more components on a single chip. With technology scaling, resistance of the wires increases, leading to higher interconnect delays. Network performance is significantly influenced by the interconnect wire delays, thus making it increasingly important. With growing chip density and demand for MPSoC, electrical interconnects may no longer meet the stringent performance and power requirements. This necessitates the exploration of alternative technologies, such as photonics and wireless communication.

### 1.3 Research Objectives

The objectives of the research are threefold – Following are the objectives composed for the present work:

- To design an area efficient high performance hybrid topology for on-chip interconnection networks.

- To design a simple, scalable energy efficient high-performance topology for on-chip interconnection networks suitable for many core SoCs.

- To design a hybrid wired-wireless on-chip interconnect architecture for kilo-core

architectures

Precisely, the work aims at developing efficient and scalable novel topologies – 2D-3D topology, hybrid wired topology and hybrid wired-wireless topology for on-chip interconnect architectures that outperform traditional Mesh topology.

## 1.4 Organization of the Thesis

The thesis presents a detailed study of and investigation on different 2D, 3D and hybrid topologies of on-chip interconnect architectures with a motive to address the limitations of widely used state-of-the-art interconnect topologies and to explore topologies that can bring a trade-off among the latency, power and area metrics enabling their application in complex SoCs.

The thesis is organized into six chapters. The following provides the outline of the chapters of the thesis.

**Chapter 1** presents a brief introduction to the basic concepts, motivation and objectives of the present research.

**Chapter 2** provides a literature review of the state-of-the-art on-chip and emerging interconnect technologies, on-chip interconnect topologies, and the numerous approaches that improve the efficiency of the architectures.

**Chapter 3** proposes a novel hexagonal-based hybrid wired topology named Hybrid Hexagonal Star. [The topological parameters of the proposed topology have been explored.](#) Design methodology, performance evaluation, simulation and synthesis findings have been discussed.

**Chapter 4** proposes a diagonal Mesh based topology named DiamondMesh. Design methodology, performance evaluation, simulation and synthesis findings have been discussed. DiamondMesh has been compared with state-of-the-art diagonal Mesh-based topologies. Further, the 2D Diagonal Mesh-based topologies are extended to 3D and have been evaluated. Also, different 3D-heterogeneous Diagonal Mesh-based topologies have been suggested and evaluated.

---

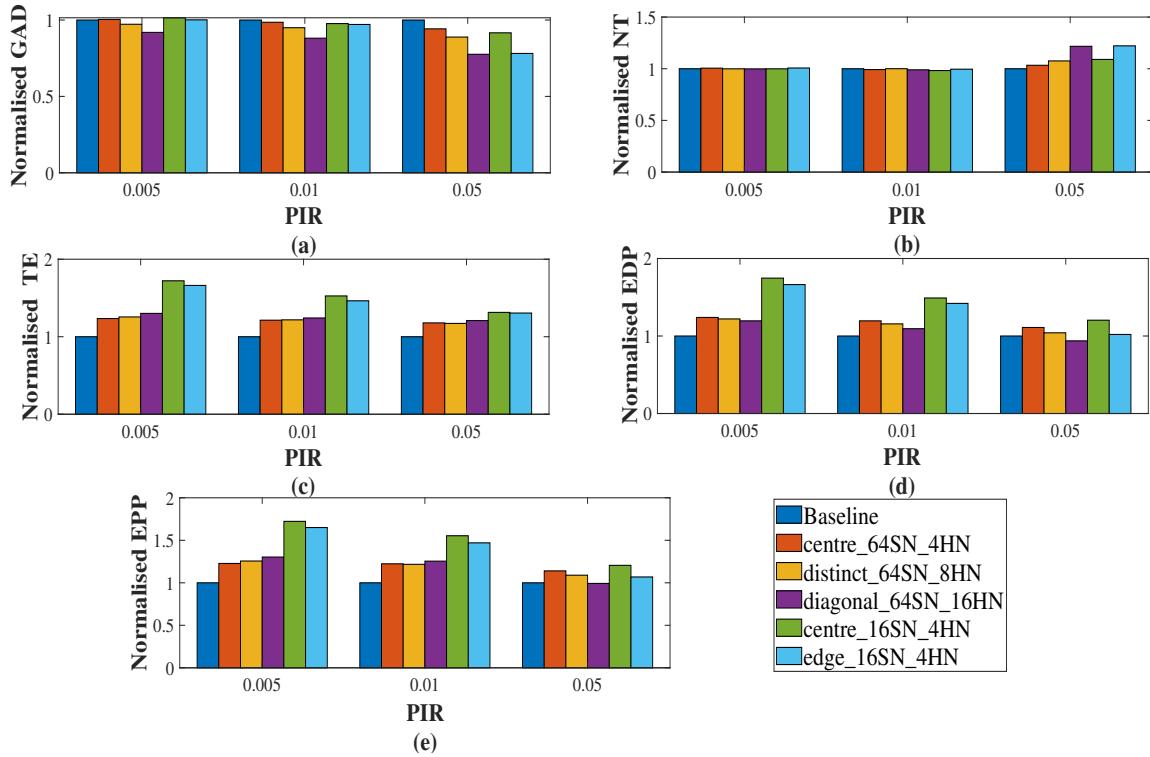

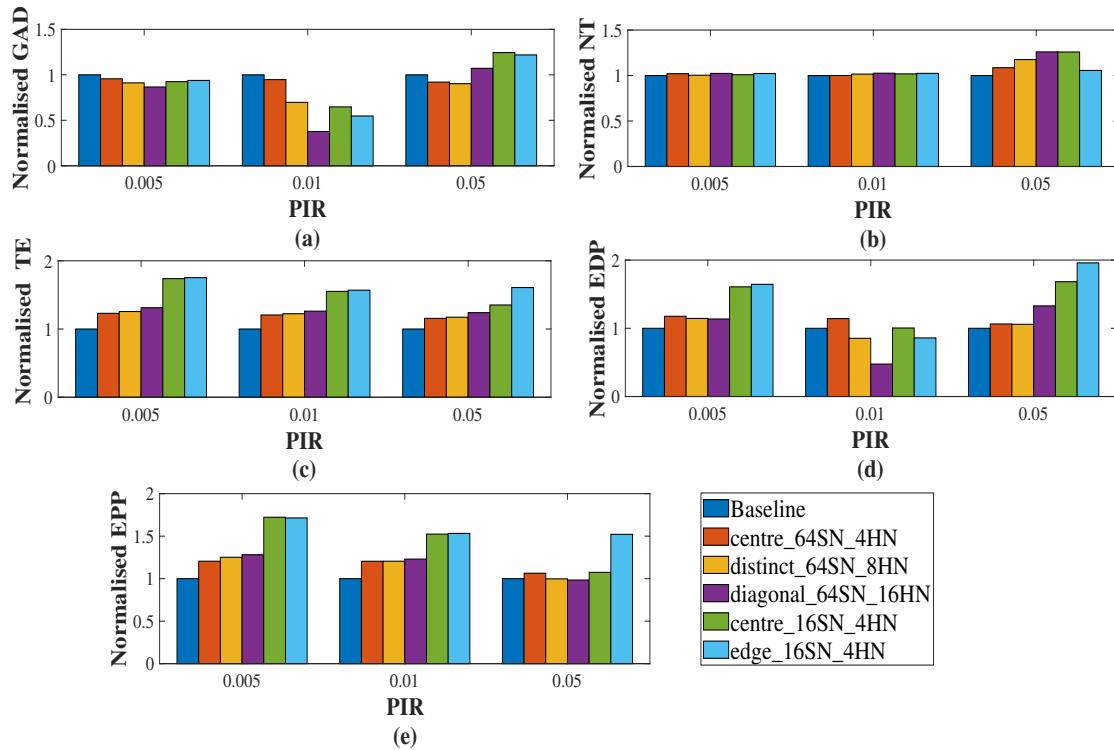

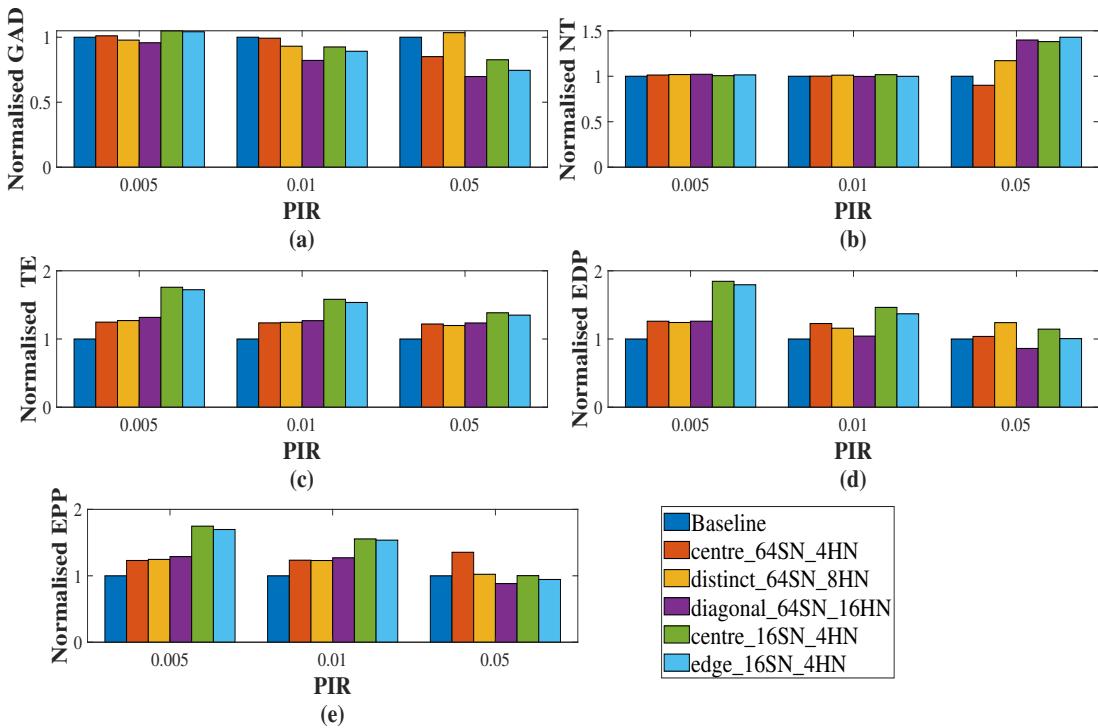

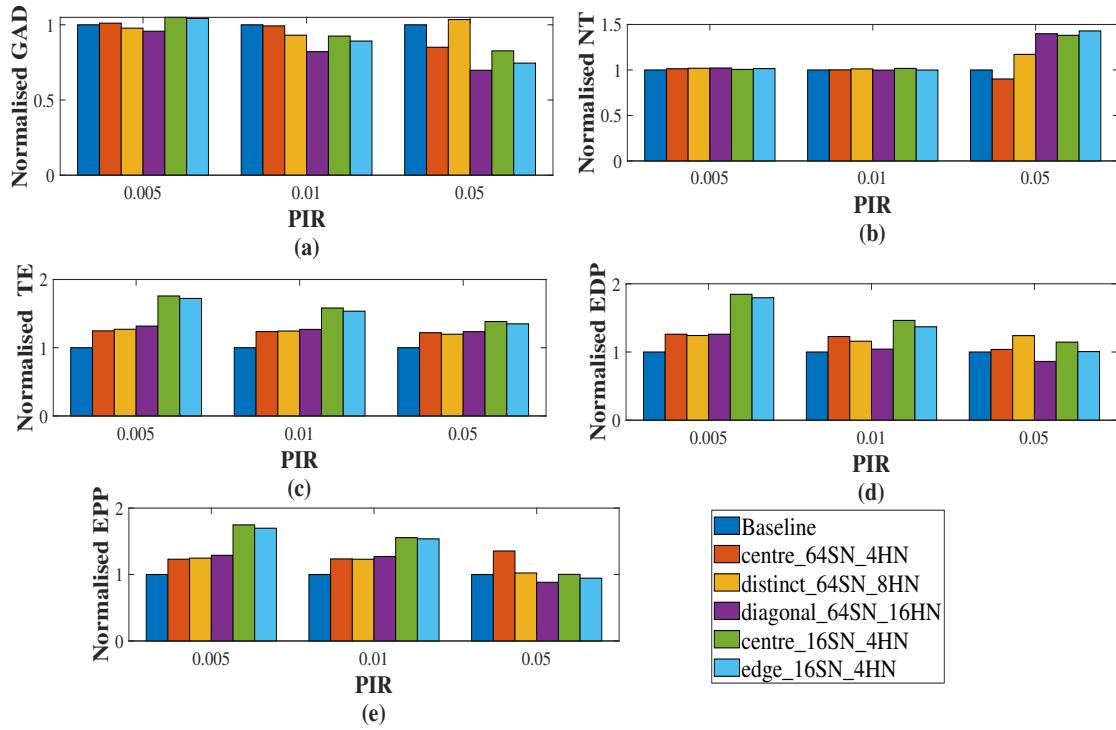

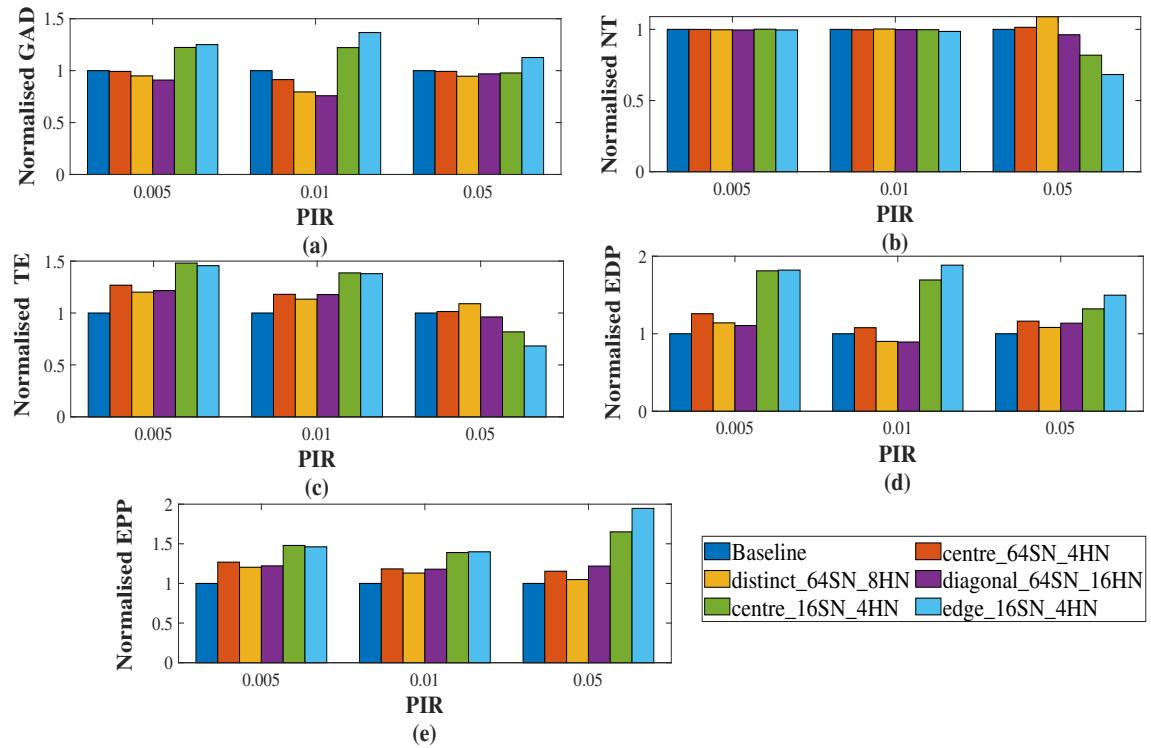

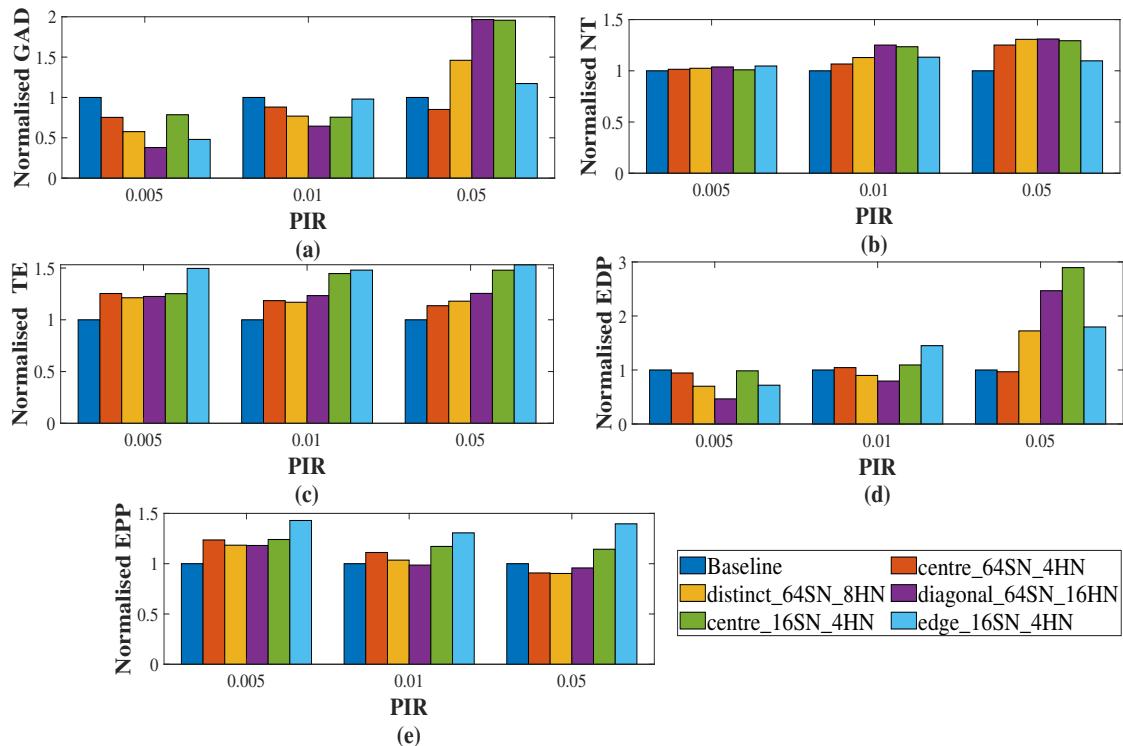

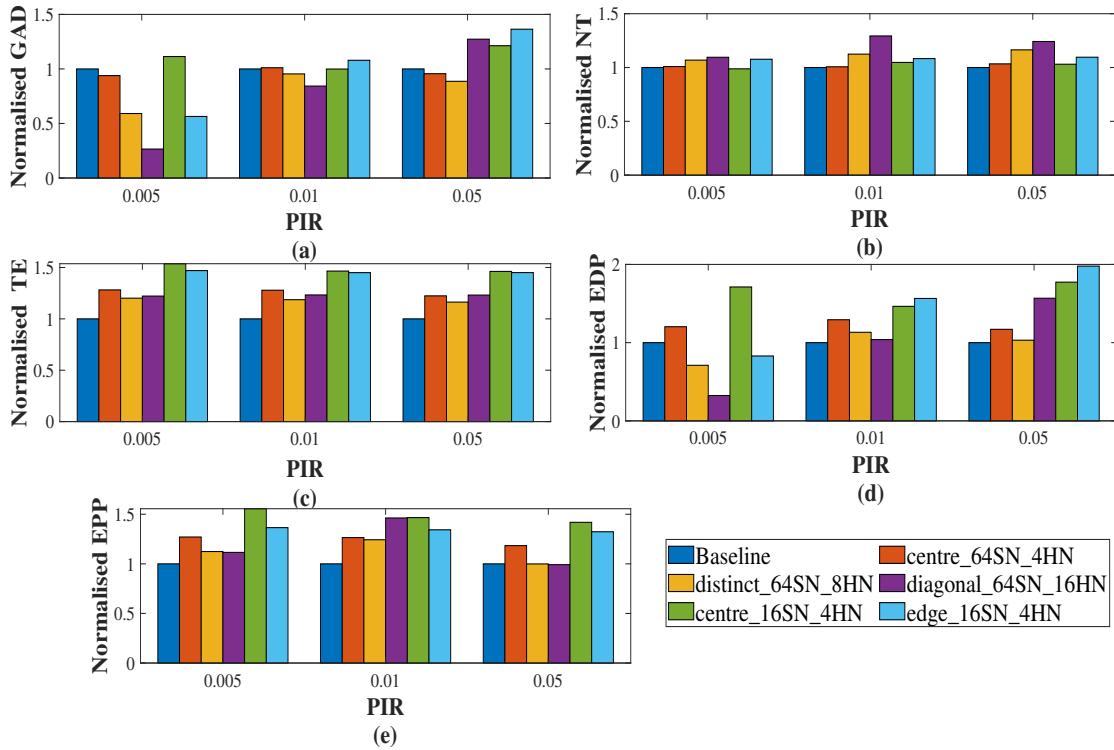

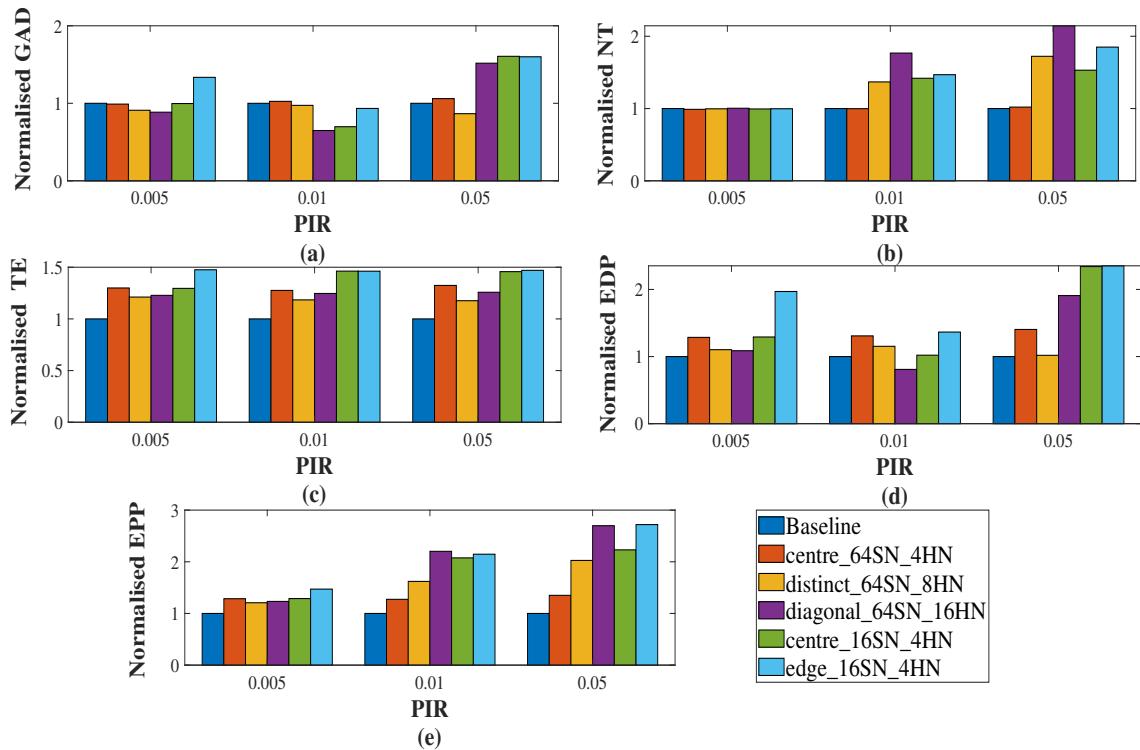

**Chapter 5** proposes three-level hierarchical hybrid wired-wireless Network-on-Chip (NoC) architectures. Various hybrid wired-wireless configurations have been proposed and examined under various traffic patterns at low, medium, and high traffic loads. 256-node and 1024-node hybrid wired-wireless architectures have been analysed and compared with that of identically configured 256-node and 1024-node baseline wired Mesh architectures respectively in terms of the metrics Global Average Delay (GAD), Network Throughput (NT), Total Energy (TE), Energy-Delay-Product (EDP) and Energy per packet (EPP).

**Chapter 6** summarizes the findings of the thesis and proposes scope for further research.

# Chapter 2

## Literature

### 2.1 On-chip interconnect topologies

This section provides a survey of on-chip topologies, specifically focusing on hexagonal-based, diagonal mesh-based, and hybrid wired-wireless topologies.

The mesh topology, which is illustrated in Figure 2.1(a), is widely employed in on-chip interconnect architectures owing to its simple, scalable, and regular structure. Nonetheless, its performance is constrained by its narrow bisection and large diameter. As a result, it is necessary to investigate potential strategies for enhancing the performance of the Mesh or alternative topologies that can deliver exceptional performance for large networks. There exist multiple methodologies to augment the performance of NoC architectures when applied to larger nodes. These encompass various strategies such as integrating express channels between distant nodes, utilizing sizable buffers, incorporating diagonal connections into the baseline mesh, merging two topologies, investigating alternative mesh structures, and contemplating alternative technologies.

#### 2.1.1 Numerous approaches to enhance the performance of NoCs

Kim *et al.* [17] have described the usage of high radix routers and mapping of flattened butterfly topology (FBT) for on-chip networks. FBT has been developed by combining or flattening the routers in each row of the conventional butterfly network into a single router. In comparison to conventional topologies such as Mesh and concentrated Mesh (CMesh), the FBT topology with high-radix routers and long-range links has demonstrated a decrease in latency and energy usage. Umit Y. Ogras *et al.* [18]

have introduced a novel design methodology for inserting application-specific long range links into a baseline Mesh, thereby reducing average packet delay and increasing Mesh throughput. The insertion of long range links depends on the traffic provided to that specific application. Grot *et al.* [23] suggested Multidrop Express Channels (MECS) networks built of unidirectional point-to-multipoint links based on express cubes. MECS has outperformed other similar topologies in terms of low-load latency and energy efficiency. With the increase in network size, inserting long range links appears to be an inefficient way as the complexity, area overhead and power consumption increases. Alternatively, network performance can be enhanced by increasing the number of virtual channels and buffer resources. However, this process consumes more space and energy. Feiyang Liu *et al.* [20], A. V. Bhaskar *et al.* [21] have investigated the performance of virtual-channel router at different buffer schemes. The results have indicated that upon increasing the number of virtual channels, the throughput has improved and latency has reduced. However, beyond a particular limit, increasing the number of virtual channels has not significantly improve throughput or latency characteristics. Nicopoulos *et al.* [22] have developed a novel router architecture called ViChaR, a dynamic Virtual Channel Regulator that dynamically assigns VCs based on network traffic. Instead of the static resource allocation employed by conventional routers, ViChaR permits the deployment of a flexible and dynamically varying virtual channel management method. At each input port, ViChaR allows a customizable number of VCs. Compared to conventional router with identical buffer size, ViChaR has showed performance and power improvement under various traffic patterns with more complicated logic. Sayed MS *et al.* [23] have presented a novel Flexible router architecture that makes efficient use of available buffers to alleviate the contention problem. In contrast to ViChar, this router architecture can be built with or without virtual channels. However, in a Flexible router design, packets may be received out of sequence. Wang *et al.* [28] have proposed a new interconnect architecture called TM that includes some advantages of both Mesh and Torus topologies. TM can be derived from Torus by removing one link in each row (column) properly to break the cycles. Following certain rules, the links have to be removed such that the average distance and diameter of the network reduces. The authors have also proposed deterministic and fully-adaptive deadlock-free routing schemes for the 2D TM network. TM has been shown to perform between Mesh and Torus. Moudi *et al.* [29] have proposed a new topol-

ogy called x-Folded TM. x-Folded TM is a TM topology that is folded according to the x-axis. x-Folded TM has reduced average distance, diameter and cost when compared to that of Mesh, Torus and TM topologies. The authors have discussed and analysed the topological properties of the x-Folded TM and also presented a routing and deadlock avoidance scheme for x-Folded TM topology.

### 2.1.2 Hexagonal based topologies

In this section, the study has focussed on exploring topology alternative to Mesh. Hexagonal and geometrically similar to hexagonal topology like Honeycomb have been reviewed. Hexagonal and HoneyComb networks find applications in many scientific fields like digital image processing [32], computer graphics [33], cellular networks [34]. Chen *et al.* [11] developed an addressing scheme, routing and broadcasting algorithms for hexagonal mesh topology. The addressing scheme is cumbersome and routing algorithms are complex. Carle *et al.* [35] proposed a simplified addressing scheme and routing algorithms for hexagonal interconnections. The proposed broadcasting algorithm is efficient but the addressing scheme exhibits asymmetry resulting in complicated routing. Fabian Garcia *et al.* [34] proposed a new addressing scheme which provides an efficient routing protocol. Xiao *et al.* [36] developed a 8-neighbor mesh topology and 6-neighbour hex grid topology which provide a much more effective inter-processor interconnect to reduce the application area, power consumption and total communication link lengths. Both topologies increase local connectivity while keeping much of the simplicity of a mesh-based topology. De-cayeux *et al.* [37] developed a 3D hexagonal network that can be built with 2D hexagonal meshes. The authors also presented a new addressing scheme and an optimal routing algorithm for a 2D hexagonal network based on the distance formula. This 3D architecture is suitable for cellular mobile computing indoor environment. Saini *et al.* [38] explored the 2D hexagonal mesh and compared with 3D Mesh. The results showed that with the proposed routing algorithm, for small PIR (Packet Injection Rate), the overall performance of 2D hexagonal mesh is better than 3D Mesh. For the increased loads, 3D mesh performs better than the 2D hexagonal meshes. Garcia *et al.* [39] studied higher-dimensional hexagonal networks. Addressing scheme and a simple routing algorithm are developed for the proposed hexagonal network but topological parameters are not explored and compared with the existing baseline topologies. For higher dimensions also, the degree remained

three. However, this is obtained by adopting complicated 3D structures. Stojmenovic *et al.* proposed 2D-Honeycomb Mesh topology [12] and explored topological properties and communication algorithms. Further, honeycomb networks with rhombus and rectangle as the bounding polygons were presented. However, the presented routing algorithm was not deadlock-free and thus was infeasible for the on-chip networks. A.W.Yin *et al.* [40] presented a 3D honeycomb structure by extending the existing 2D topology, stacking them vertically layer by layer. A.W.Yin *et al.* also presented the deadlock-free routing algorithm for 3D honeycomb topology. The 3D structure is simple as the implementation involves straightforward stacking of layers. However, the node degree is increased from three to four. A.Yin *et al.* [41], presented the comparison between Honeycomb Mesh and rectangular Mesh topology and the simulation results showed that honeycomb outperformed mesh in terms of area, power and communication delay. Jean Carle *et al.* [42], described higher dimensional Honeycomb networks, 3-D and k-D where  $k > 3$ . Further, the topological properties, routing and broadcasting algorithms were presented. The results showed that the cost of k-D honeycomb mesh was slightly better than that of k-D mesh. The above studies suggest that the hexagonal-like structure can be considered as an alternative NoC topology for mesh.

### 2.1.3 Diagonal Mesh topologies

With an objective to propose an alternative topology that can outperform the widely used Mesh topology, this work has focussed on Diagonal Mesh-based topologies known for their simplicity, scalability, and regularity, similar to Mesh. Moreover, incorporating diagonal links has been found to be an efficient way to enhance the performance of Mesh with a moderate level of complexity. In this section, Diagonal Mesh topologies including DMesh, XDMesh, and ZMesh shown in Figure 2.1 have been reviewed.

**Figure 2.1** (a) Mesh; (b) DMesh; (c) XDMesh; (d) ZMesh

In recent times, several diagonally linked mesh-based topologies have been proposed. Chifeng Wang *et al.* [24] have presented a diagonal mesh topology dubbed DMesh, which, as illustrated in Figure 2.1(b), contains diagonal connections across the network. DMesh has adopted an X-architecture routing approach to minimize latency with moderate implementation cost overhead. The evaluation results have indicated that employing diagonal links has been a more area- and power-efficient strategy for NoCs for improving network performance than using larger buffers.

Md. Hasan Furhad *et al.* [25] have suggested an extended diagonal mesh topology termed XDMesh, as illustrated in Figure 2.1(c), to improve network performance and lower the Mesh NoC's energy consumption. In terms of latency, throughput, energy consumption and area overhead, XDMesh has surpassed other leading-edge topologies such as mesh, extended-butterfly fat tree and diametrical mesh.

N. Prasad *et al.* [27] have proposed an energy-efficient diagonal mesh topology, named ZMesh, shown in Figure 2.1(d). The topological properties of ZMesh such as network diameter, bisection width, and the number of edges have been analysed. Performance comparison of ZMesh with other topologies including Mesh, DMesh, CMesh, PDNoC in terms of latency and power has been performed under different synthetic and real-time traffic patterns but only for injection rates varying from 0.05 to 0.3. The results have shown that ZMesh has performed better than Mesh, PDNoC, CMesh. It has been observed that the ZMesh has the lowest power-latency product (PLP) for injection rates up to 0.3. However, beyond the injection rate of 0.3, PLP of ZMesh has increased drastically when compared with that of DMesh.

## 2.2 On-chip interconnect technologies

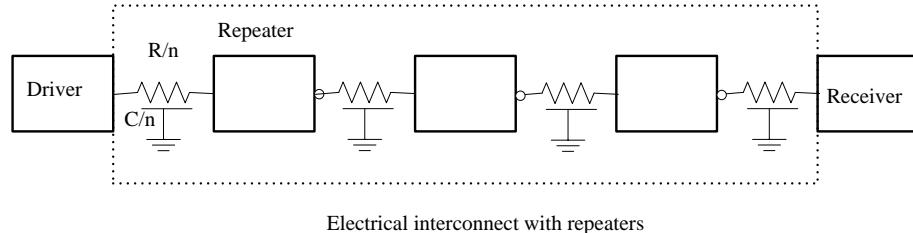

### 2.2.1 Electrical interconnect technology

Traditionally, electrical also called metallic interconnects have been used as the communication infrastructure for SoCs. Metallic interconnects have the advantages of lower power consumption, higher bandwidth and lesser area for short range communication. The basic block diagram for electrical interconnects is shown in Figure 2.2. Signalling in

this approach is based on charging and discharging of the wire segments to send information.

**Figure 2.2** Electrical communication system