# **IMPROVED HIGH GAIN DC-DC CONVERTERS FOR MICROGRID AND ELECTRIC VEHICLE APPLICATIONS**

Submitted in the partial fulfillment of the requirements

for the award of the degree of

## **DOCTOR OF PHILOSOPHY**

**By**

**Baba Fakruddin Monakanti**

**(Roll No. 719038)**

**Supervisor:**

**Dr. A. V. Giridhar**

Associate Professor

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506004, TELANGANA STATE, INDIA

October-2024**

## **APPROVAL SHEET**

This Thesis entitled "**Improved High Gain DC-DC Converters for Microgrid and Electric Vehicle Applications**" by **Baba Fakruddin Monakanti** is approved for the degree of Doctor of Philosophy.

### **Examiners**

---

---

---

### **Supervisor**

**Dr. A. V. Giridhar**

Associate Professor

EED, NIT Warangal

### **Chairman**

**Dr. Ch. Venkaiah**

Professor,

EED, NIT Warangal

**Date:** \_\_\_\_\_

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

WARANGAL – 506 004**

**DEPARTMENT OF ELECTRICAL ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL**

**CERTIFICATE**

This is to certify that the thesis entitled "**Improved High Gain DC-DC Converters for Microgrid and Electric Vehicle Applications**," which is being submitted by **Mr. Baba Fakruddin Monakanti** (Roll No. 719038), is a bonafide work submitted to the National Institute of Technology, Warangal in the partial fulfillment of the requirement for the award of the degree of **Doctor of Philosophy** in the Department of Electrical Engineering. To the best of my knowledge, the work incorporated in this thesis has not been submitted elsewhere for the award of any degree.

Date:

Place: Warangal

**Dr. A. V. Giridhar**

(Supervisor)

Associate Professor

Department of Electrical Engineering

National Institute of Technology

Warangal – 506004

## DECLARATION

This is to certify that the work presented in the thesis entitled "**Improved High Gain DC-DC Converters for Microgrid and Electric Vehicle Applications**" is a bonafide work done by me under the supervision of **Dr. A. V. Giridhar**, Department of Electrical Engineering, National Institute of Technology, Warangal, India and was not submitted elsewhere for the award of any degree.

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

**Baba Fakruddin Monakanti**

(Roll. No: 719038)

Date:

Place: Warangal

## ACKNOWLEDGEMENTS

Words cannot express the immense gratitude that I feel towards my supervisor *Dr. A. V. Giridhar*, Associate Professor, Department of Electrical Engineering, National Institute of Technology, Warangal. It has been a great experience learning from him and his constant support and guidance have always motivated me to do productive work. I appreciate his kindness in patiently listening to my problems and I am deeply indebted for all the efforts he took to support me during the most difficult days of my Ph.D. He taught me to be determined, dedicated, and patient towards work and this is something I would persevere in my future endeavors.

I am thankful for the support and co-operation offered by *Prof. N. V. Srikanth*, Head of the Department of Electrical Engineering.

I am very grateful to my Doctoral Scrutiny Committee chairman *Prof. Ch. Venkaiah* and other Doctoral Scrutiny Committee members, *Dr. B. L. Narasimharaju*, Professor, Department of Electrical Engineering, *Dr. A. Kirubakaran*, Associate Professor, Department of Electrical Engineering and *Dr. P. Muthu*, Associate Professor, Department of Mathematics for their constructive suggestions and advice for the progress of my research work.

I am grateful to *Prof. D M Vinod Kumar*, *Prof. B. L. Narasimharaju*, *Prof. M. Sailaja Kumari* and *Prof. S. Srinivasa Rao*, Professors and former Head of the Department of Electrical Engineering, for their constant motivation, support, and cooperation during the course of my work. I also appreciate the technical aid offered by other teaching and non-teaching members of the Department of Electrical Engineering, NIT Warangal.

I would like to express my deepest gratitude to our team including *Dr. V V K Satyakar*, *Dr. Hema Sundar Rao Kolla*, *Dr. Madhu Babu*, *Dr Ponna Srinivas*, *Dr Patnana Hema Kumar*, *Dr. Chinna Karasala* and *Dr. P Manoj* for all the useful insights and assistance offered during the course of work. I am sincerely thankful to my friends, *Mr. Ashok Kumar Kanithi*, *Dr. Chinmay Kumar Das*, *Dr M L Parvathy*, *Mr Gotte Vikram Raj*, *Dr Ajith Mohanty*, *Dr Arun Kumar*, *Dr Lokesh*, *Mr A Bhanu Chander*, *Mr Subba Reddy*,

*Mr Chandra Sekhar, Mr Ramesh Dharavath, Mr Satish Reddy Dodda, Mr Murali, Mr Devraj, Mr David Amar Raj, Mr Raghavan, Mr Ramesh Junju, Mrs Mounica R, Mr Rosiah, Mr G Ravi Kumar, Mr Chandra Sekhar Azad, Mr K V V D Ramana Kumar, Mr P Rahul, Mr P Ravi Teja, Mr Krupakar and Mrs Jaya Sree* for supporting me throughout this journey.

I would not have undertaken this journey without the encouragement and support provided by my father *Mr. M Dastagiri*, mother *Mrs. M. Jaharabee*, sister *Mrs N. Fakrabee*, and nephews *Mr N K Basha, Mr N Noor Basha*, and *Mr N Ahmad Hussain*. I am eternally grateful for their endless motivation and acknowledge all the efforts they have put in to support me throughout this journey. I am also thankful to my brothers, *Mr T Khadar Basha* and *Mr T Abdul Khadar* for their unceasing support and prayers. They have always encouraged me to do better in life and chase my dreams. I also thank my brother-in-law *Mr N Hussain* for his motivation and support during the course of my research. I wholeheartedly thank my friends, *Mr Siva Naga Raju, Mr Kalyan Immadisetty & Family, Mr Karthik, Mr Ganesh, Mr Sai* and *Dr Ramesh Krishna Gotte* for supporting me throughout the tough days of this journey.

Last, but not least, this journey would not have been accomplished without my partner, *P Sabiya.*, who whole-heartedly stood by my side, bearing my absence during this period. I appreciate all the efforts she took to support me to pursue my Ph.D. and thank her for guiding me through all the challenges. From being my biggest cheerleader to my critic, I am forever grateful to my wife for his relentless support during the best and worst days of my professional and personal life. Furthermore, I am grateful to the almighty for guiding me to seek paths that could evoke my knowledge and compassion.

**Baba Fakruddin Monakanti**

# ABSTRACT

**KEYWORDS:** Absolute common ground, Bidirectional dc-dc converter, Boost converter, High voltage gain, Interleaved converter, nonisolated dc-dc converter, Quadratic boost converter, Quasi Z Source converter, Switched Capacitor, Switched inductor, Split duty converter, Voltage lift, Voltage multiplier, Z Source converter.

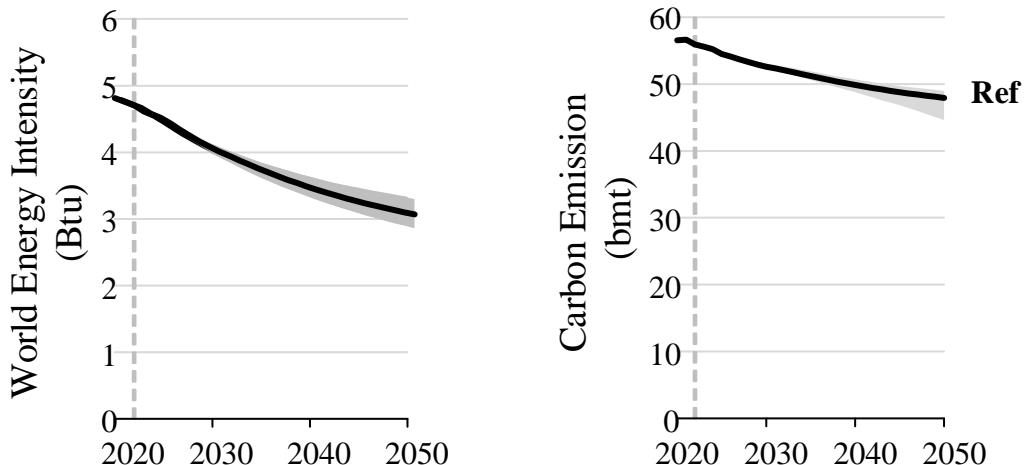

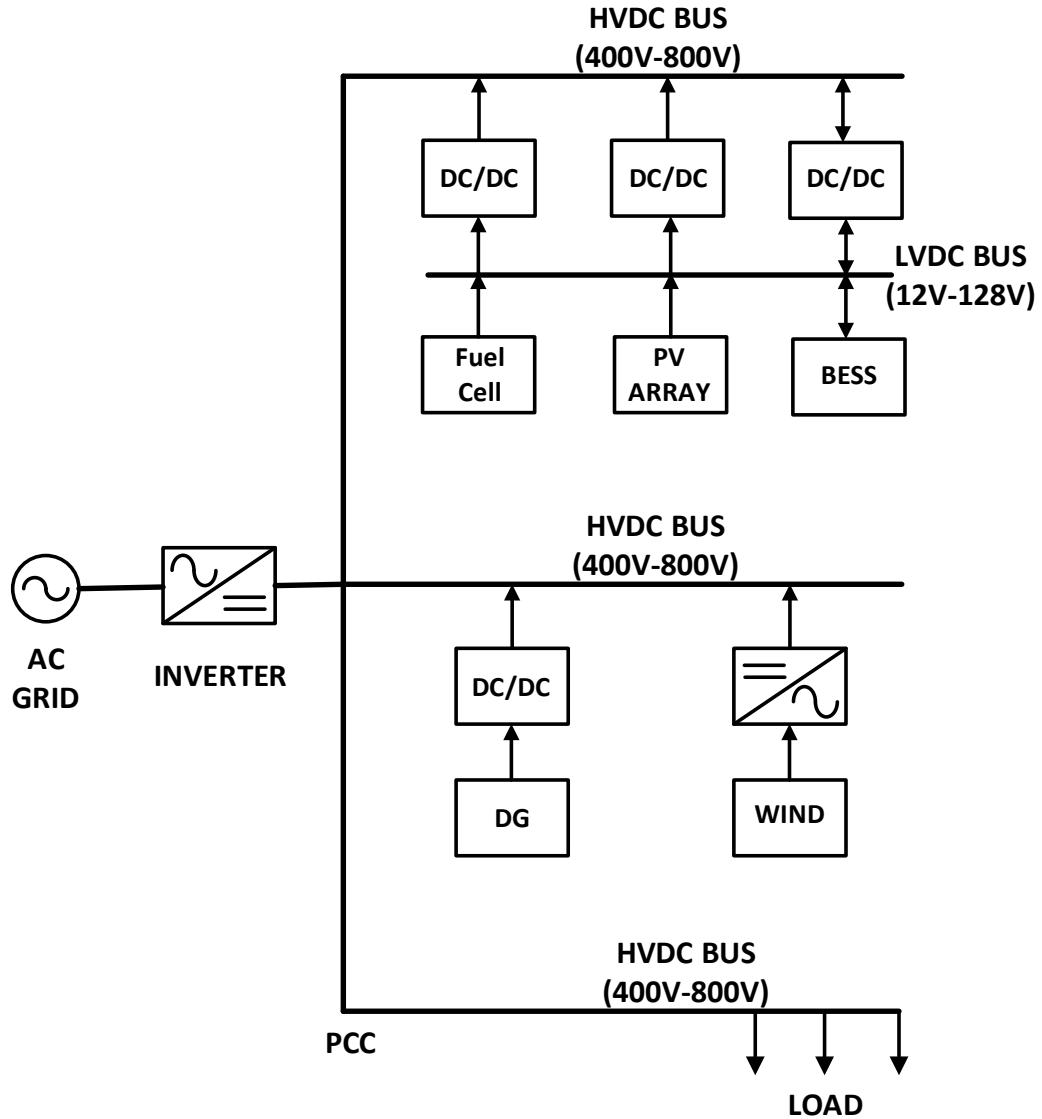

The world-wide energy consumption raised by 34% with associated carbon dioxide gas emissions increased by 15% from 35.7 billion metric tons (bmt) to projected 41 bmt in 2050. These factors of increased energy consumption and CO<sub>2</sub> emission have attracted the alternate green energy sources with zero carbon emission regarding environmental protection concerns. The aforementioned micro sources are mostly at consumer premises and can be able to form dc microgrids. The merits of green energy micro sources are zero-emission, highly consistent, low cost and on the other hand major limitation of these sources is the low voltage at their output terminals. In order to comply with the applicability concerns power electronic-based power conditioning is required for these micro sources in terms of the low terminal dc voltage.

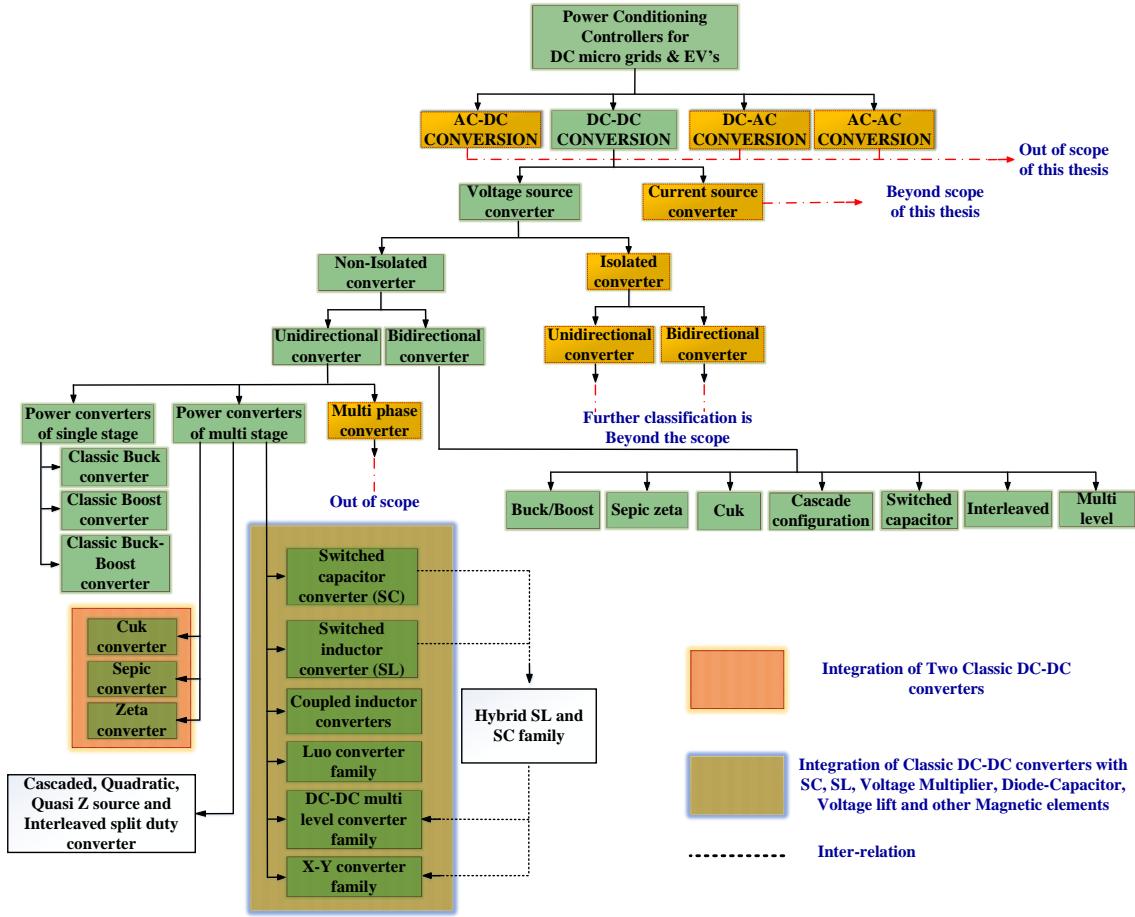

The amplification can be done by two types of power electronic converters i.e., isolated and nonisolated dc-dc converters. In isolated converters, the voltage transformation ratio depends on the magnetic coupling i.e., with transformer or coupled inductor technologies prime focus being on the turns ratio. These topologies are often in danger if their leakage flux is not properly processed. Moreover, this leakage flux also causes voltage spikes across the switch at the high-voltage side. The aforementioned constraints demand a peculiar design of magnetic components which in turn dictates the cost, density, efficiency, and scalability of the magnetically coupled dc-dc converters.

The nonisolated topologies i.e., non-magnetically coupled dc-dc converters are more in demand due to the absence of the aforementioned constraints. These nonisolated converters have inherent features such as simplicity in construction, compactness, efficiency, and low-cost concerns. The primitive classic boost converter is a simple solution but it has the adverse effects of drastically decreasing efficiency at extreme duty ratios at which it has to be operated to attain high and or ultra-high voltage gains. The later evaluated versions of boost converters like passive, active, and hybrid switched inductor converters, switched capacitor topologies, and voltage lift-voltage multiplier-based converters have major demerits such as high current stress, elevated component count, and reduced efficiency. Recent elegant interleaved integrated passive-switched-inductor topologies of common grounding with split duty and

reduction in long conducting intervals for switches are the viable alternate solutions for the aforementioned converters.

The interleaved split duty-based converters possess the feature of low duty for the switches but the overall cumulative duty cycle is still high with a relatively high element count and elevated output capacitor inrush currents at the end of each switching cycle. In addition, the overall elevated duty ratios make the efficiency of the converter to be less followed by the heating concerns. This typical concern demands the evolution of dc-dc converters consisting of high boosting factors at low duty ratios, such analogous featured converters are quadratic boost dc-dc converters. This converter features a high boost factor at a low duty which in turn lowers the voltage and current stresses, and improves the efficiency. Here much attention is required for the design of the second inductor because of its high voltage excitation and high sizing requirements.

The feature of high boost factor at low duty especially at lowered upper bound limit is also possible with impedance (L-C) network-based Z-Source converters that are highly volatile by having discontinuous input currents, this makes them less adoptable for majority applications. To overcome this demerit an analogous converter featuring similar voltage gain and more importantly, a series inductor at the input terminals is reported namely by a Quasi Z Source dc-dc converter, nevertheless because of the low charging interval for the inductors due to their limited upper bound on duty cycle makes the inductors to be bulky and henceforth associated packaging concerns, economical and spacing concerns will persist. In this regard, a single switched inductor modified Sheppard Taylor-based converter is proposed which surpasses the high inductor size and packaging concerns.

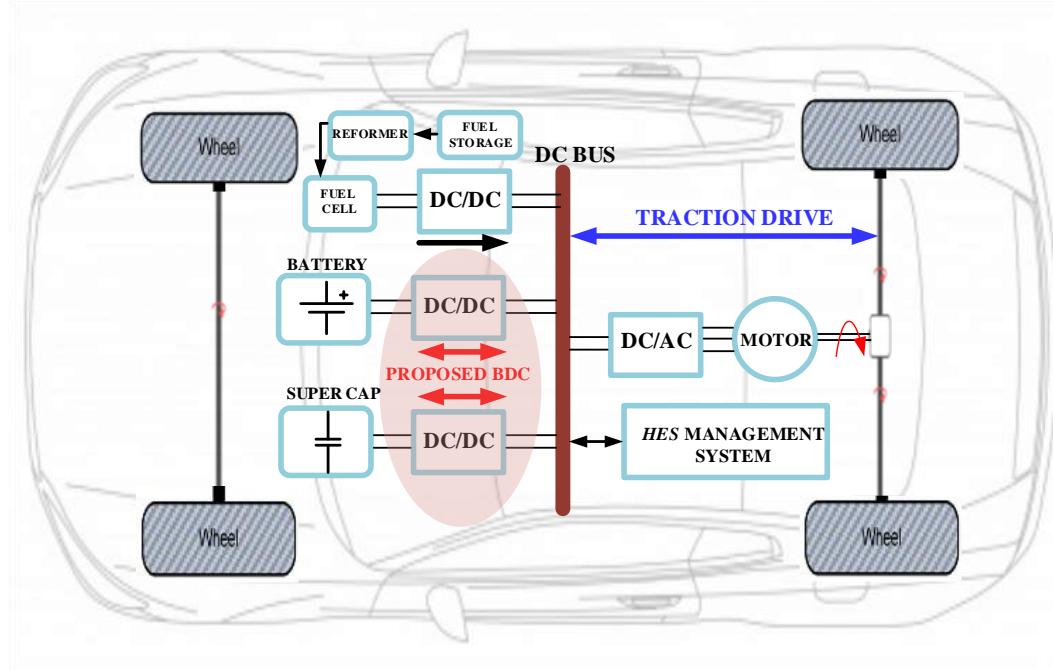

The recent evolution of dc-dc converters is also abundantly emphasizing the bidirectional dc-dc converters (BDC) for hybrid energy source-based electric vehicle propulsion systems. Among the plethora of BDC's quadratic boost-buck converters are popular because of their paramount amplification and attenuation consisting of a wide range of duty ratio flexibility, featuring simple topological synthesis and economical concerns towards the stated applications.

# Table of Contents

|                                                                                                                     |      |

|---------------------------------------------------------------------------------------------------------------------|------|

| <b>ACKNOWLEDGEMENTS .....</b>                                                                                       | i    |

| <b>ABSTRACT .....</b>                                                                                               | iii  |

| <b>Table of Contents.....</b>                                                                                       | v    |

| <b>List of Figures .....</b>                                                                                        | ix   |

| <b>List of Tables.....</b>                                                                                          | xiv  |

| <b>List of Symbols.....</b>                                                                                         | xvii |

| <b>Chapter 1. Introduction .....</b>                                                                                | 2    |

| 1.1 Background.....                                                                                                 | 2    |

| 1.2 Motivation .....                                                                                                | 8    |

| 1.3 Thesis objectives .....                                                                                         | 9    |

| 1.4 Organization of thesis .....                                                                                    | 10   |

| 1.5 Summary .....                                                                                                   | 11   |

| <b>Chapter 2. Literature Review.....</b>                                                                            | 13   |

| 2.1 Introduction .....                                                                                              | 13   |

| 2.2 Nonisolated Unidirectional High Voltage Gain DC-DC Converters.....                                              | 13   |

| 2.3 Nonisolated Unidirectional Quadratic Boost DC-DC Converters .....                                               | 19   |

| 2.4 Nonisolated Bidirectional Quadratic Boost DC-DC Converters (BDC)....                                            | 22   |

| 2.5 Nonisolated unidirectional Quasi Z Source (QZS) Converters .....                                                | 23   |

| 2.6 Summary .....                                                                                                   | 25   |

| <b>Chapter 3. Nonisolated High Gain Hybrid Switched-Inductor DC-DC Converter with Common Switch Grounding .....</b> | 27   |

| 3.1 Introduction .....                                                                                              | 27   |

| 3.2 HSL-CSG Topological Derivation .....                                                                            | 28   |

| 3.3 CCM Operation and Analysis .....                                                                                | 28   |

| 3.3.1 Mode I of Operation .....                                                                                     | 29   |

| 3.3.2 Mode II of Operation.....                                                                                     | 30   |

| 3.3.3 Mode III of Operation .....                                                                                   | 31   |

| 3.4 DCM Analysis .....                                                                                              | 32   |

| 3.5 Inductor and Capacitor Selection .....                                                                          | 33   |

| 3.6 Efficiency Analysis .....                                                                                       | 34   |

| 3.7 Experimental Results .....                                                                                      | 36   |

| 3.8 Performance Comparison.....                                                                                     | 41   |

|                                                                                                                                                       |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>3.9 Summary .....</b>                                                                                                                              | <b>44</b> |

| <b>Chapter 4. Active switched capacitor based ultra voltage gain quadratic boost dc-dc converters .....</b>                                           | <b>46</b> |

| <b>4.1 Introduction .....</b>                                                                                                                         | <b>46</b> |

| <b>4.2 The Proposed Topology Power Circuit Derivation .....</b>                                                                                       | <b>46</b> |

| <b>4.3 Analysis of ASCQBC-I Converter .....</b>                                                                                                       | <b>47</b> |

| <b>4.3.1 Operating State I (<math>0 \leq t \leq t_1; DT_S</math>) .....</b>                                                                           | <b>47</b> |

| <b>4.3.2 Operating State II (<math>t_1 \leq t \leq t_2; (1-D)T_S</math>) .....</b>                                                                    | <b>48</b> |

| <b>4.3.3 Diode-Switch Voltage Stress Analysis .....</b>                                                                                               | <b>49</b> |

| <b>4.3.4 Diode-Switch Current Stress Analysis .....</b>                                                                                               | <b>49</b> |

| <b>4.3.5 Parasitic parameters influence on voltage gain and efficiency .....</b>                                                                      | <b>50</b> |

| <b>4.4 Analysis of ASCQBC-II Converter .....</b>                                                                                                      | <b>52</b> |

| <b>4.4.1 Operating State I (<math>0 \leq t \leq t_1; DT_S</math>) .....</b>                                                                           | <b>52</b> |

| <b>4.4.2 Operating State II (<math>t_1 \leq t \leq t_2; (1-D)T_S</math>) .....</b>                                                                    | <b>53</b> |

| <b>4.4.3 Diode-Switch Voltage Stress .....</b>                                                                                                        | <b>54</b> |

| <b>4.4.4 Diode-Switch Current Stress .....</b>                                                                                                        | <b>54</b> |

| <b>4.5 Control Performance .....</b>                                                                                                                  | <b>55</b> |

| <b>4.6 Experimental Validation .....</b>                                                                                                              | <b>56</b> |

| <b>4.7 Comparison of ASCQBC Converters with High Voltage Gain Converters .....</b>                                                                    | <b>62</b> |

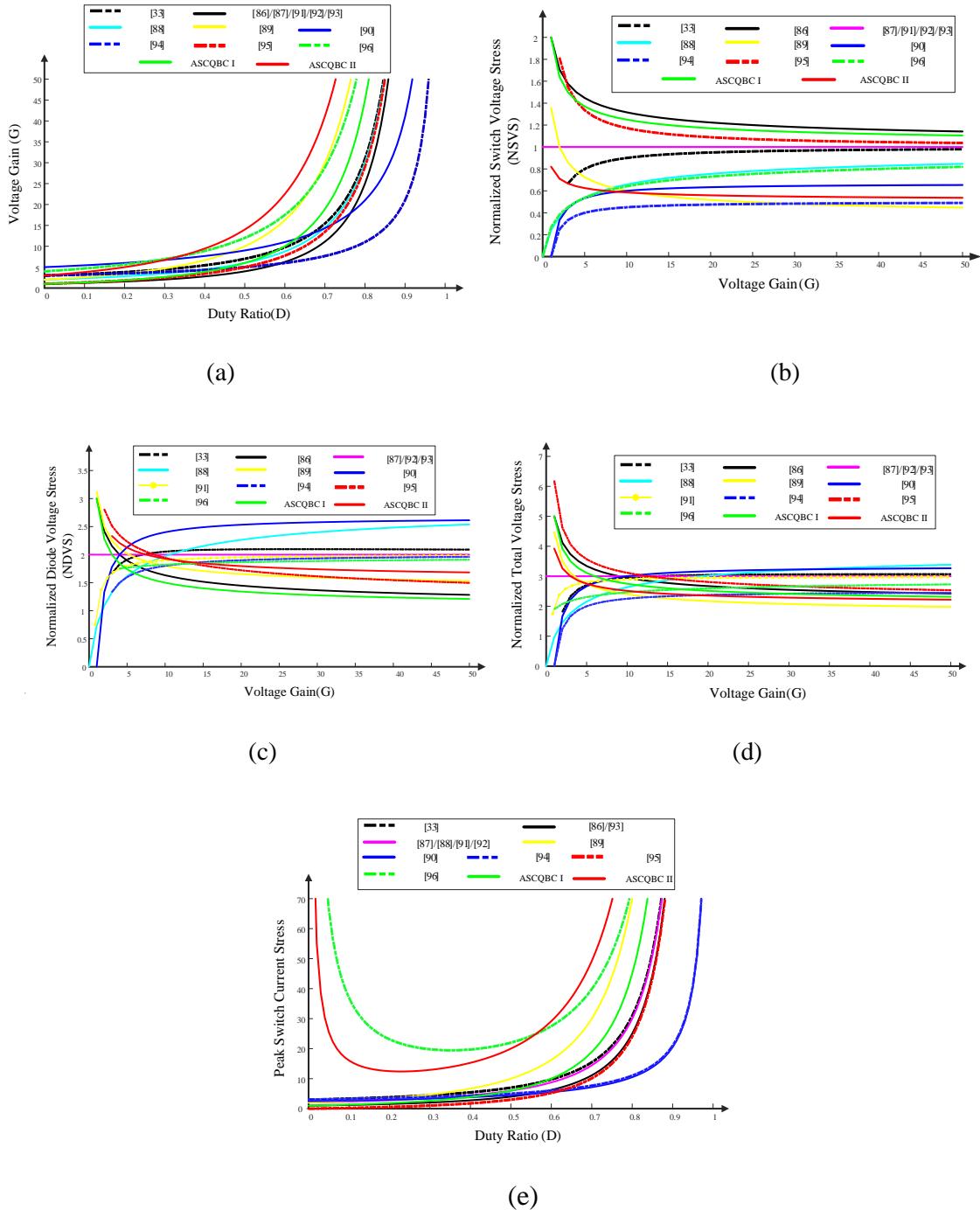

| <b>4.7.1 Voltage Gain .....</b>                                                                                                                       | <b>62</b> |

| <b>4.7.2 Element Voltage Stress .....</b>                                                                                                             | <b>62</b> |

| <b>4.7.3 Element Current Stress .....</b>                                                                                                             | <b>65</b> |

| <b>4.7.4 Miscellaneous Performance Indices .....</b>                                                                                                  | <b>65</b> |

| <b>4.8 Summary .....</b>                                                                                                                              | <b>66</b> |

| <b>Chapter 5. An Ultra High Gain Switched-Capacitor Boost DC-DC converter with Low Rear End Diode Voltage Stress and Reduced Ripple Current .....</b> | <b>68</b> |

| <b>5.1 Introduction .....</b>                                                                                                                         | <b>68</b> |

| <b>5.2 Topological Derivation .....</b>                                                                                                               | <b>68</b> |

| <b>5.3 Steady State CCM Operation and Analysis .....</b>                                                                                              | <b>70</b> |

| <b>5.3.1 Mode I of Operation .....</b>                                                                                                                | <b>70</b> |

| <b>5.3.2 Mode II of Operation .....</b>                                                                                                               | <b>70</b> |

| <b>5.4 Effect of Element Parasitics .....</b>                                                                                                         | <b>71</b> |

| <b>5.5 Design Specifications .....</b>                                                                                                                | <b>72</b> |

| <b>5.6 Control Performance .....</b>                                                                                                                  | <b>73</b> |

| <b>5.7 Simulation and Experimental Results .....</b>                                                                                                  | <b>75</b> |

| <b>5.8 Performance Comparison .....</b>                                                                                                               | <b>79</b> |

|                                                                                                                                                           |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>5.9 Summary .....</b>                                                                                                                                  | 84         |

| <b>Chapter 6. A Wide Voltage Range Bidirectional High Voltage Transfer Ratio Quadratic Boost DC-DC converter for EVs with Hybrid Energy Sources .....</b> | <b>86</b>  |

| <b>6.1 Introduction .....</b>                                                                                                                             | 86         |

| <b>6.2 Boost Mode of Operation and Analysis .....</b>                                                                                                     | 87         |

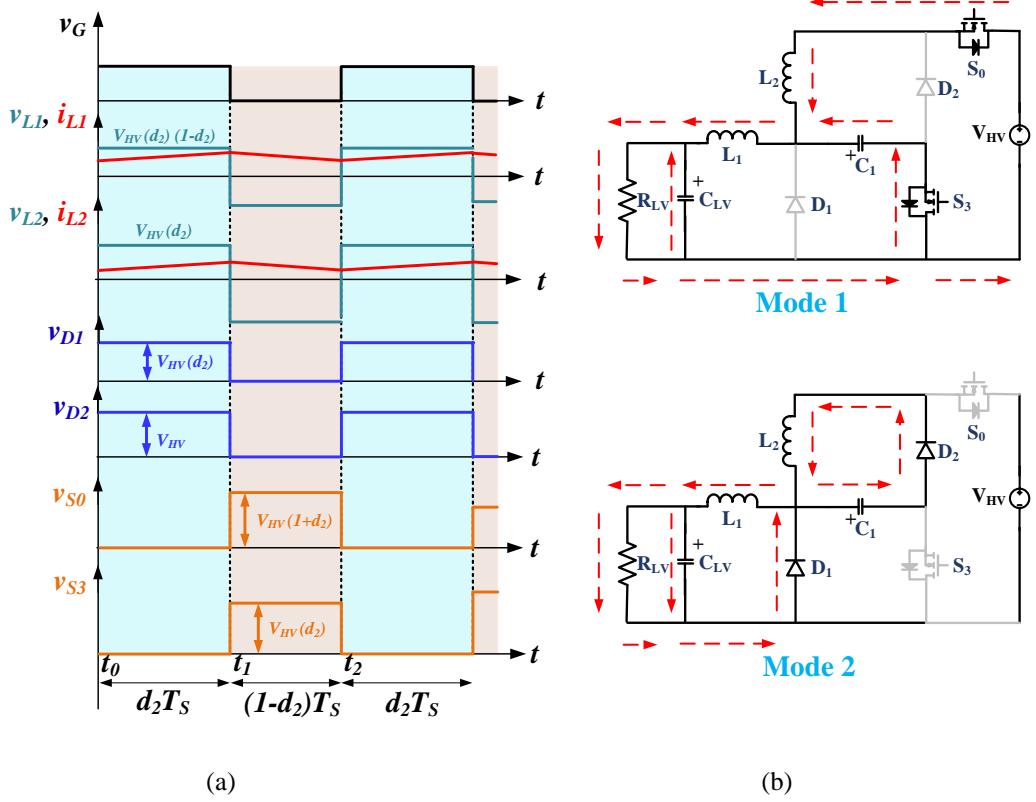

| <b>6.2.1 Operating State I: <math>[t_0-t_1]</math>.....</b>                                                                                               | 88         |

| <b>6.2.2 Operating State II: <math>[t_1-t_2]</math> .....</b>                                                                                             | 88         |

| <b>6.3 Buck Mode of Operation and Analysis .....</b>                                                                                                      | 88         |

| <b>6.3.1 Operating State I: <math>[t_0-t_1]</math>.....</b>                                                                                               | 89         |

| <b>6.3.2 Operating State II: <math>[t_1-t_2]</math> .....</b>                                                                                             | 89         |

| <b>6.4 Parameter Design and Control Performance.....</b>                                                                                                  | 90         |

| <b>6.4.1 Semiconductor Voltage Stress .....</b>                                                                                                           | 90         |

| <b>6.4.2 Semiconductor Current Stress .....</b>                                                                                                           | 90         |

| <b>6.4.3 Inductor Design.....</b>                                                                                                                         | 90         |

| <b>6.4.4 Capacitor Design.....</b>                                                                                                                        | 90         |

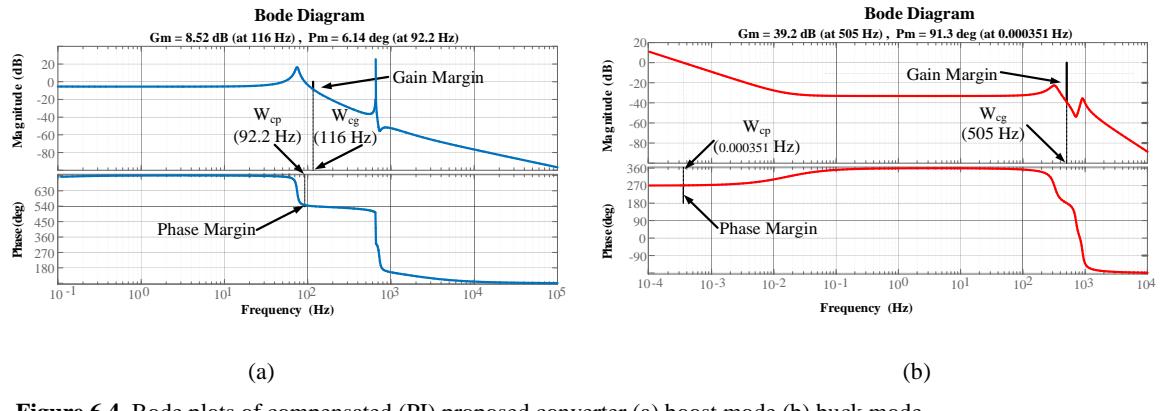

| <b>6.4.5 Control Performance.....</b>                                                                                                                     | 90         |

| <b>6.5 Experimental Results.....</b>                                                                                                                      | 92         |

| <b>6.6 Comparison with similar Quadratic BDC.....</b>                                                                                                     | 97         |

| <b>6.7 Summary .....</b>                                                                                                                                  | 100        |

| <b>Chapter 7 A Dual Switched Inductor-Switched Capacitor based High Boost DC-DC Converters.....</b>                                                       | <b>102</b> |

| <b>7.1 Introduction .....</b>                                                                                                                             | 102        |

| <b>7.2 Steady State Analysis .....</b>                                                                                                                    | 103        |

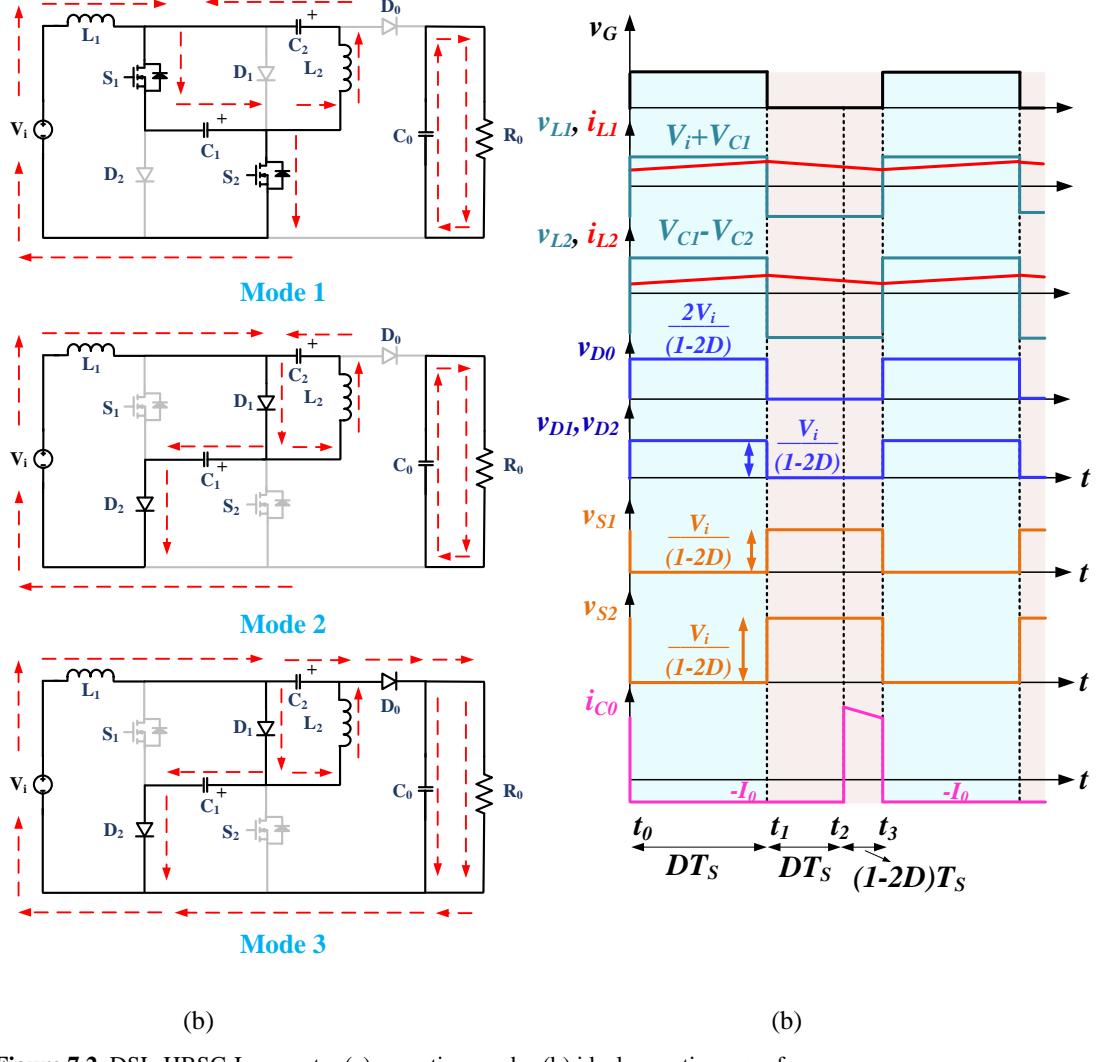

| <b>7.2.1 Mode 1: <math>[t_0-t_1, DT_s]</math> .....</b>                                                                                                   | 103        |

| <b>7.2.2 Mode 2: <math>[t_1-t_2, DT_s]</math> .....</b>                                                                                                   | 104        |

| <b>7.2.3 Mode 3: <math>[t_2-t_3, (I-2D)T_s]</math> .....</b>                                                                                              | 104        |

| <b>7.2.4 Voltage and Current Stresses .....</b>                                                                                                           | 105        |

| <b>7.2.5 Inductor and Capacitor Design .....</b>                                                                                                          | 105        |

| <b>7.2.6 Parasitics influence on Output Voltage and Efficiency .....</b>                                                                                  | 106        |

| <b>7.2.7 Small Signal Modelling.....</b>                                                                                                                  | 107        |

| <b>7.3 Case Study.....</b>                                                                                                                                | 108        |

| <b>7.4 Experimental Results .....</b>                                                                                                                     | 109        |

| <b>7.5 Performance Comparison.....</b>                                                                                                                    | 113        |

| <b>7.6 Summary .....</b>                                                                                                                                  | 116        |

| <b>Chapter 8. Conclusion and Future Scope.....</b>                                                                                                        | <b>118</b> |

| <b>8.1 Conclusion.....</b>                                                                                                                                | 118        |

|                              |     |

|------------------------------|-----|

| <b>8.2 Future scope.....</b> | 120 |

| <b>References .....</b>      | 122 |

| <b>Publications.....</b>     | 135 |

# List of Figures

|                                                                                                                                                                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1.1</b> Worldwide energy consumption and CO <sub>2</sub> emission .....                                                                                                                                                                                          | 2  |

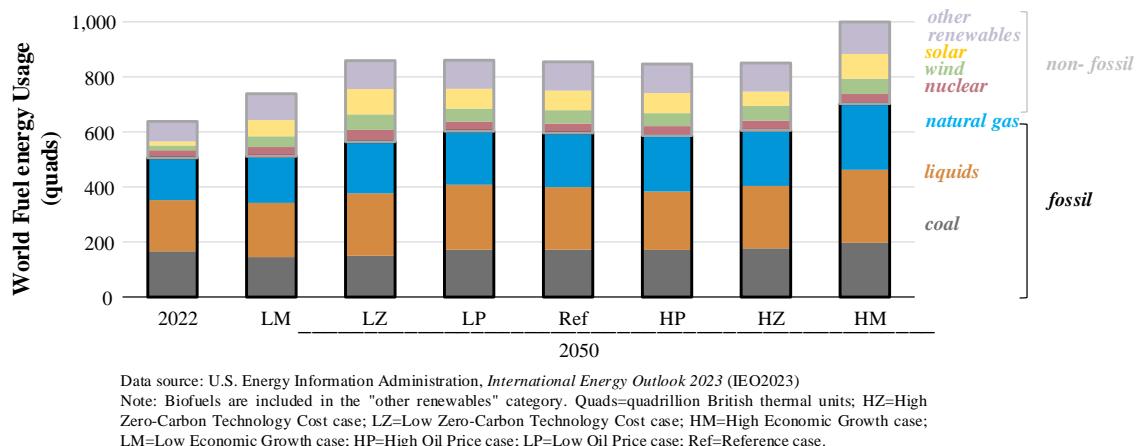

| <b>Figure 1.2</b> Source based Energy usage in the world .....                                                                                                                                                                                                             | 3  |

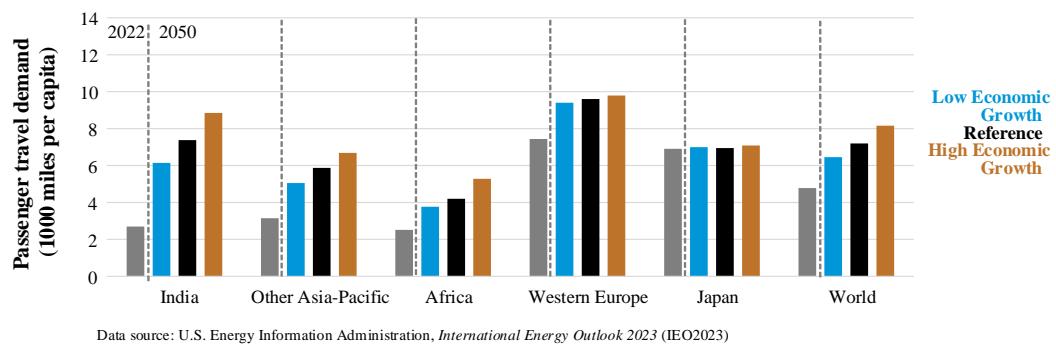

| <b>Figure 1.3</b> Travel demand of passengers .....                                                                                                                                                                                                                        | 4  |

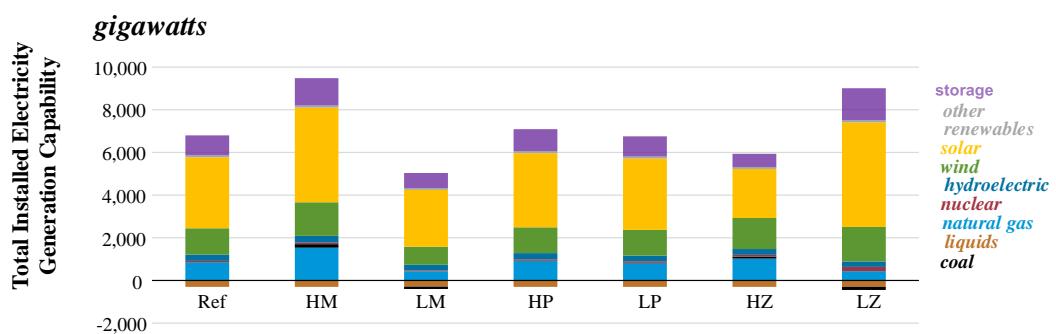

| <b>Figure 1.4</b> Global total installed generating capacity .....                                                                                                                                                                                                         | 4  |

| <b>Figure 1.5</b> General architecture of DC microgrid .....                                                                                                                                                                                                               | 5  |

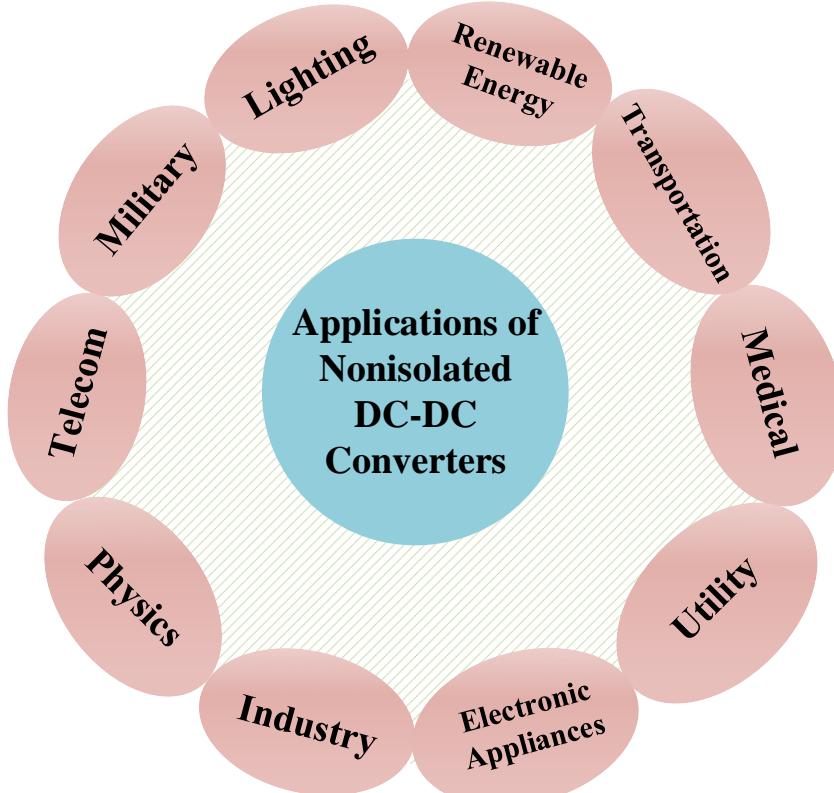

| <b>Figure 1.6</b> Overview of nonisolated dc-dc converters applications .....                                                                                                                                                                                              | 6  |

| <b>Figure 1.7</b> Power architecture of HES driven EV .....                                                                                                                                                                                                                | 7  |

| <b>Figure 2.1</b> Classification of Power conditioning-power electronic converters emphasizing nonisolated DC-DC converters .....                                                                                                                                          | 14 |

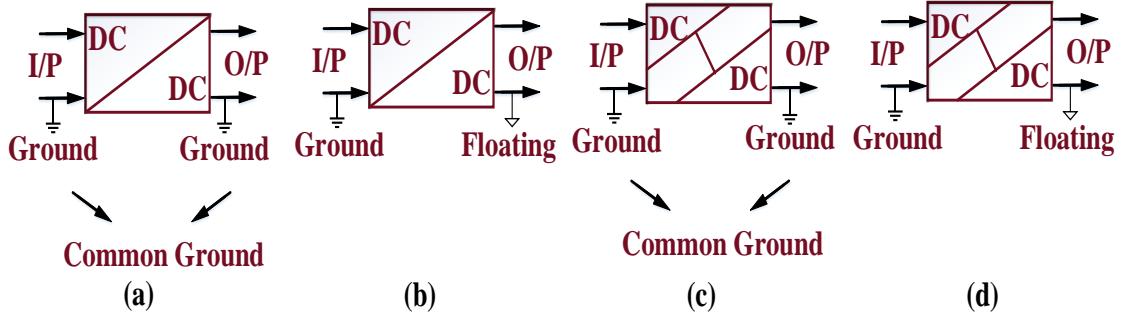

| <b>Figure 2.2</b> Non-Isolate Uni- Bidirectional DC-DC converter configuration focusing on grounding aspects (a) single stage common ground structure (b) single stage floating structure (c) multi stage common ground structure (d) multi stage floating structure ..... | 15 |

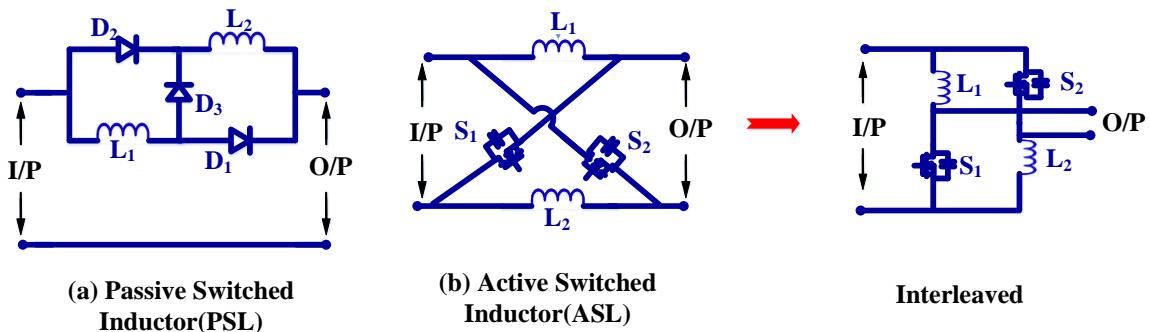

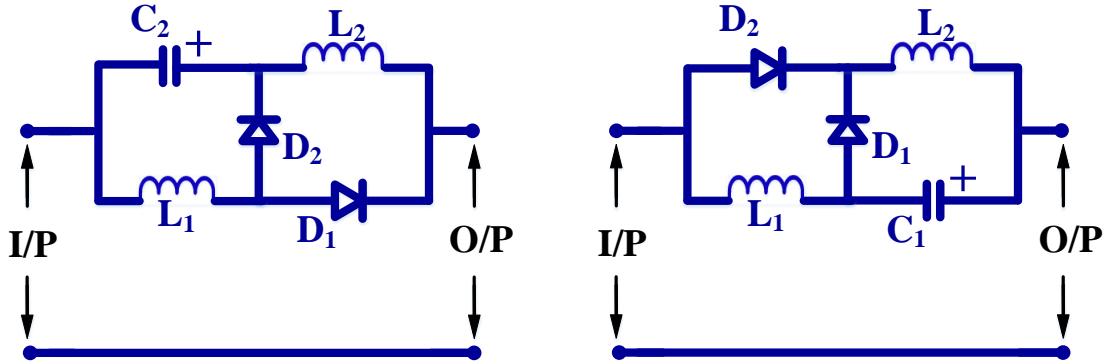

| <b>Figure 2.3</b> SL and SC based hybrid boost converters (a) PSL arrangement (b) ASL structure (c) asymmetric HSL and (d) symmetric HSL .....                                                                                                                             | 15 |

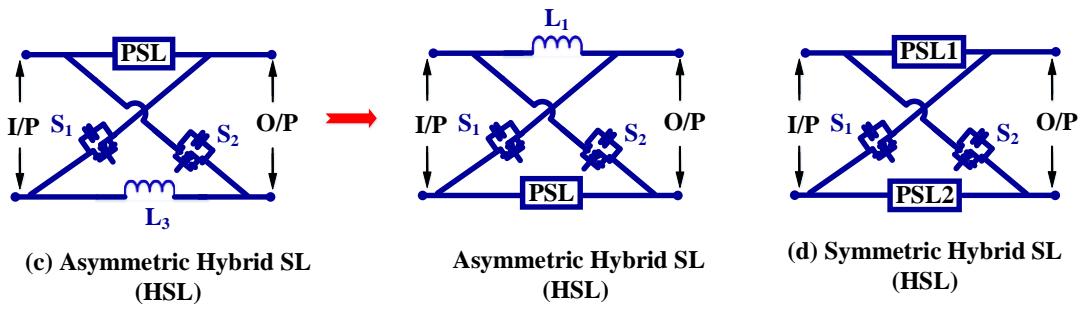

| <b>Figure 2.3</b> (contd.) Capacitor based voltage boosting arrangements; voltage doublers for (e) noninverting output (f) inverting output (g) voltage multiplier and (h) switched capacitor (SC) .....                                                                   | 16 |

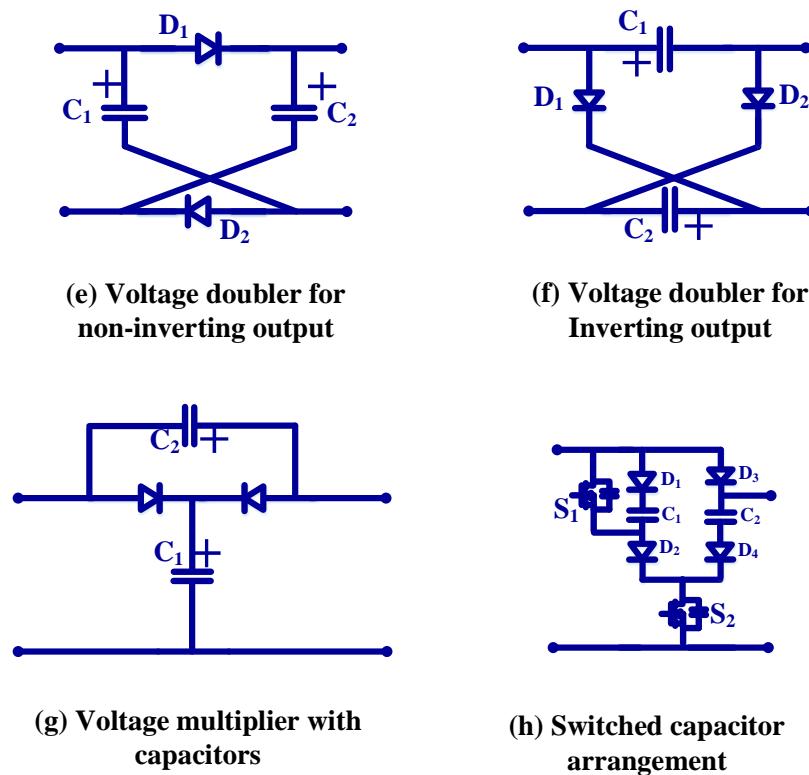

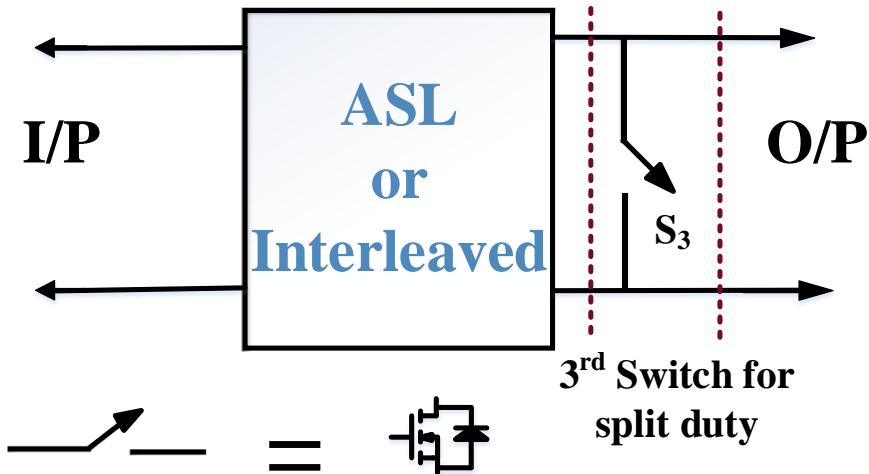

| <b>Figure 2.3</b> (contd.) ASL or interleaved structure based (i) split duty converter .....                                                                                                                                                                               | 17 |

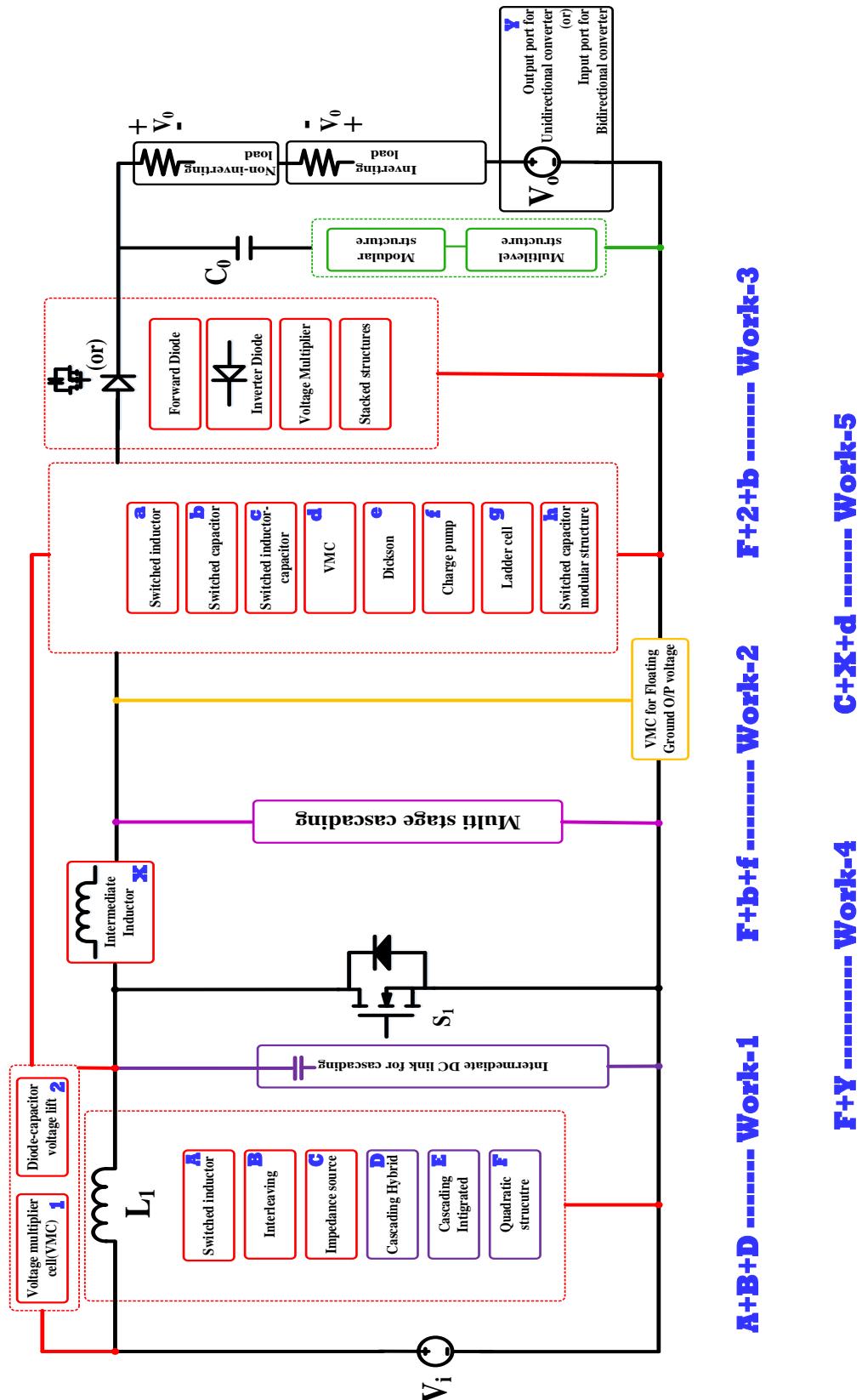

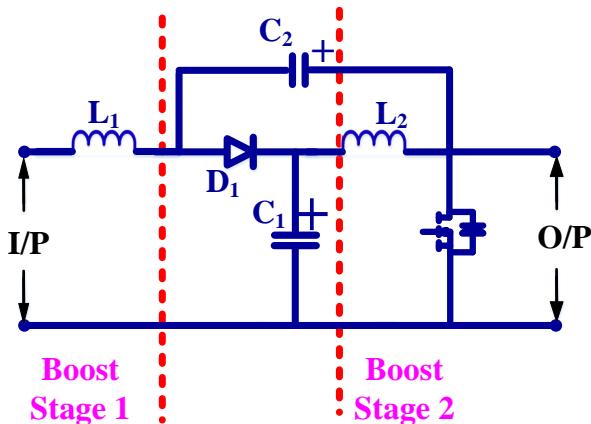

| <b>Figure 2.4</b> Nonisolated high Gain DC-DC converters power conditioning structures and voltage enhancing methodologies applied to boost converters .....                                                                                                               | 18 |

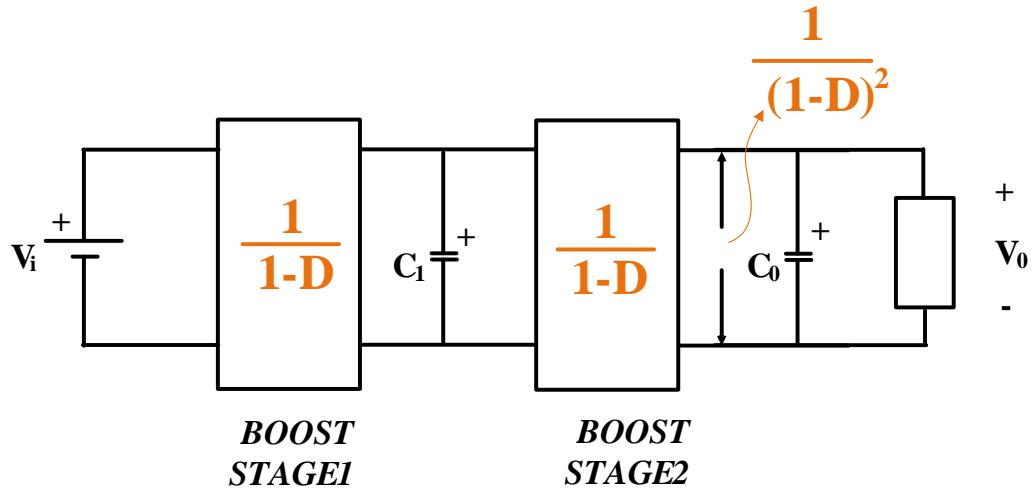

| <b>Figure 2.5</b> Two stage Quadratic boost converter .....                                                                                                                                                                                                                | 19 |

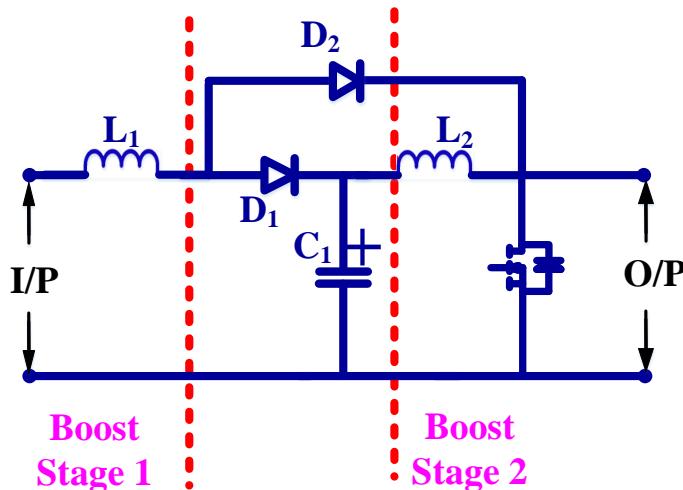

| <b>Figure 2.6</b> Single stage Quadratic boost converter .....                                                                                                                                                                                                             | 19 |

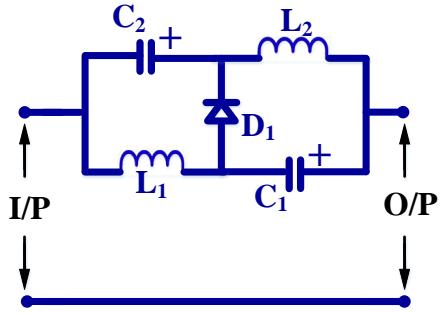

| <b>Figure 2.7</b> Quadratic boost structures derived from PSL .....                                                                                                                                                                                                        | 20 |

| <b>Figure 2.8</b> Formulation of QZS from (a) PSL and (b) two stage boosting .....                                                                                                                                                                                         | 24 |

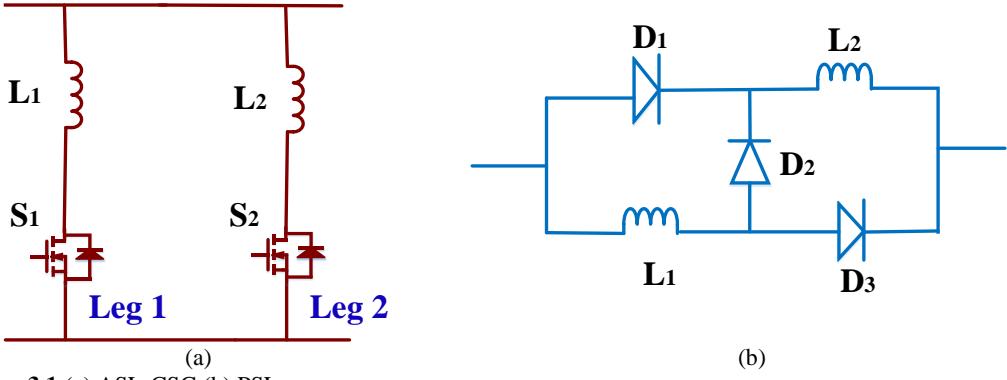

| <b>Figure 3.1</b> (a) ASL-CSG (b) PSL .....                                                                                                                                                                                                                                | 28 |

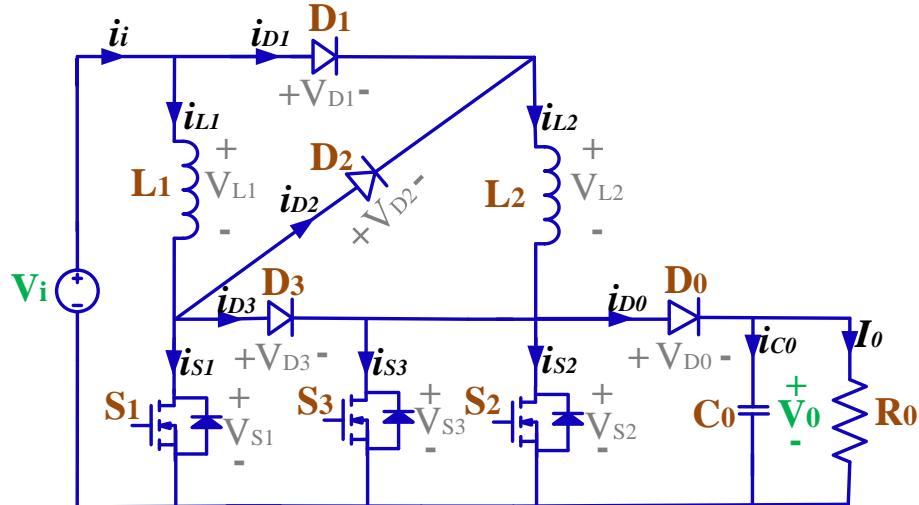

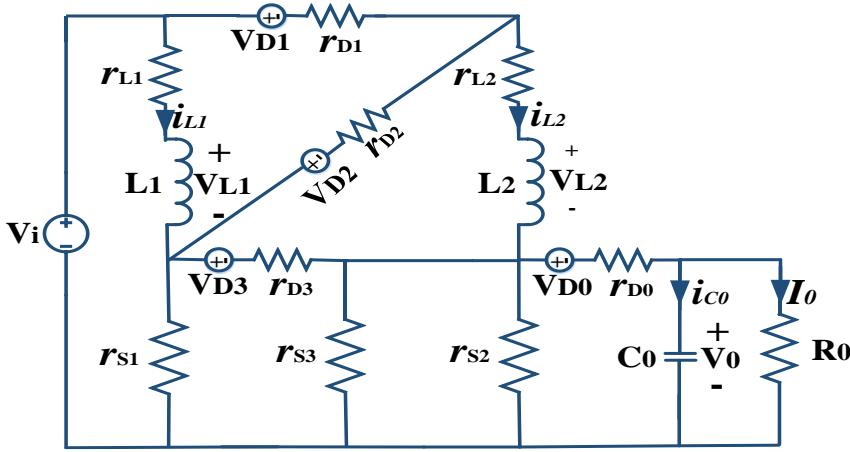

| <b>Figure 3.2.</b> Proposed HSL-CSG Topology .....                                                                                                                                                                                                                         | 29 |

| <b>Figure. 3.3</b> HSL-CSG converter (a) typical waveforms in CCM; modes of operation (b) $S_1, S_2$ ON for Mode I (c) $S_3$ is ON for Mode II and (d) $S_1, S_2, S_3$ are OFF for Mode III .....                                                                          | 30 |

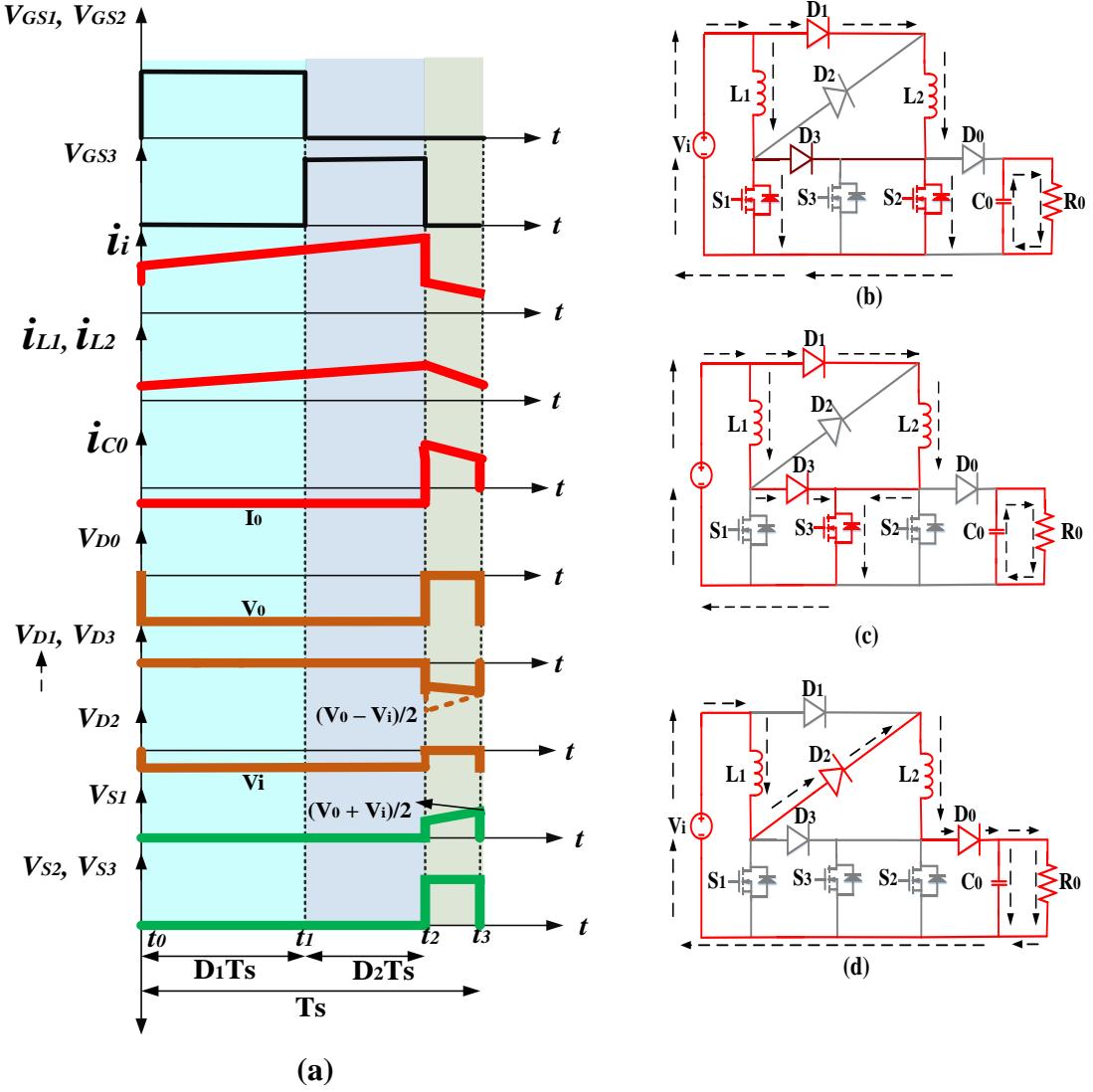

| <b>Figure 3.4.</b> Voltage gain (CCM) corresponding to variation in $D_1$ .....                                                                                                                                                                                            | 32 |

| <b>Figure. 3.5.</b> HSL-CSG converter DCM operation.....                                                                                                                                                                                                                   | 32 |

| <b>Figure. 3.6.</b> Equivalent circuit with parasitic parameters .....                                                                                                                                                                                                     | 34 |

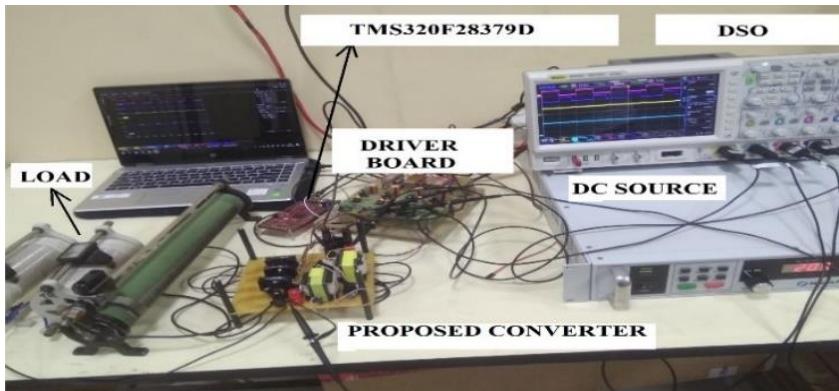

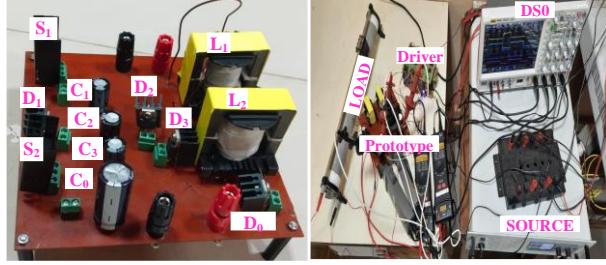

| <b>Figure 3.7.</b> Experimental setup.....                                                                                                                                                                                                                                 | 36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

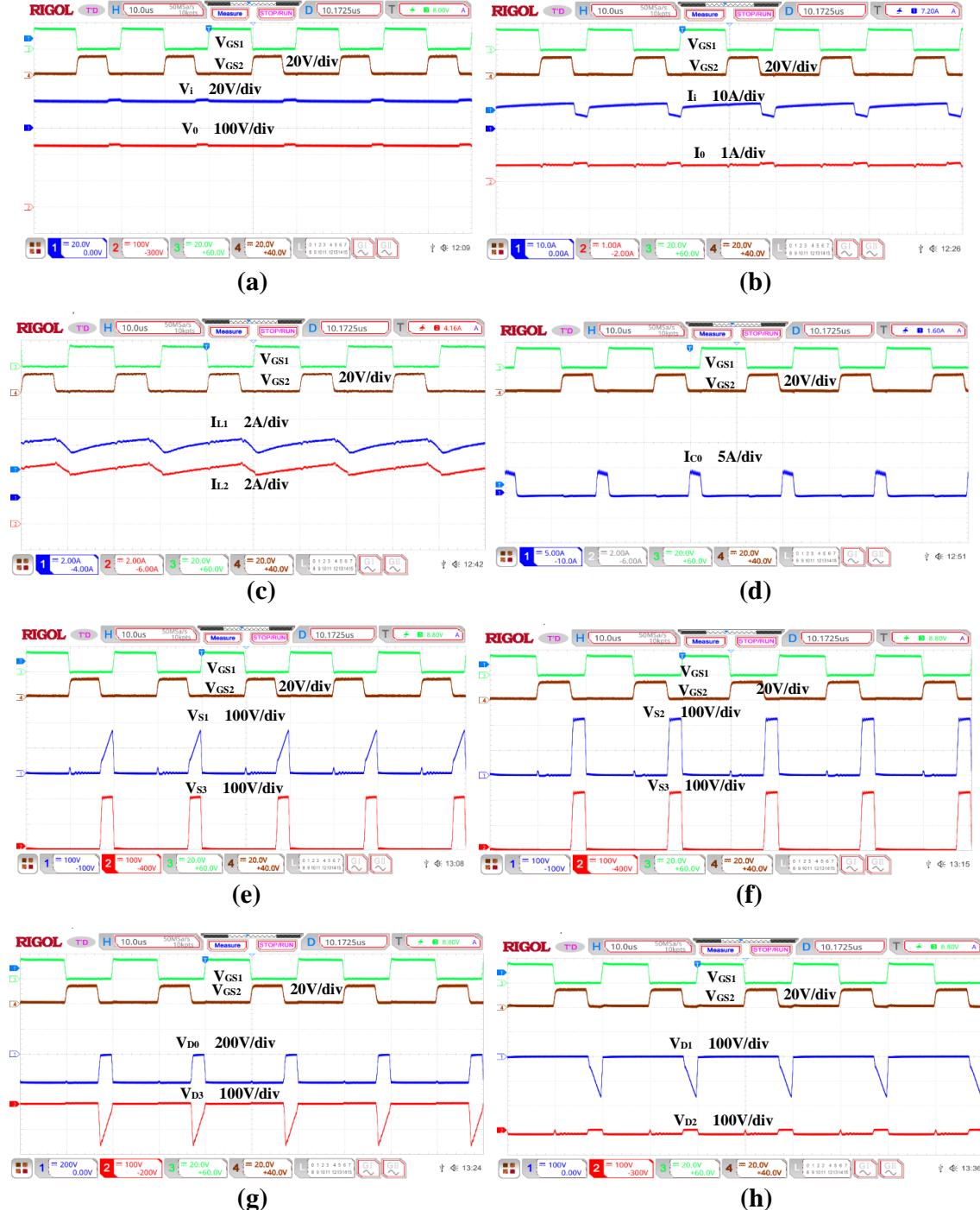

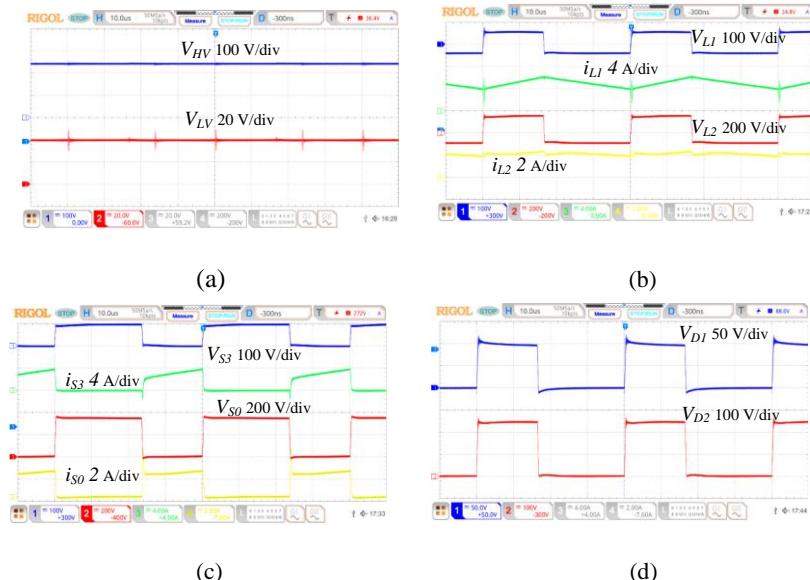

| <b>Figure 3.8.</b> Experimental results (A) Input and output voltages ( $V_i$ and $V_o$ ) (B) Input and output currents ( $i_i$ and $i_o$ ) (C) Inductor currents ( $i_{L1}$ and $i_{L2}$ ) (D) Capacitor current ( $i_{C0}$ ) (E) Switch voltages ( $V_{S1}$ and $V_{S3}$ ) (F) Switch Voltages ( $V_{S2}$ and $V_{S3}$ ) (G) Diode voltages ( $V_{D0}$ and $V_{D3}$ ) (H) Diode voltages ( $V_{D1}$ and $V_{D2}$ ) .....                                                                                                                                                                                   | 37 |

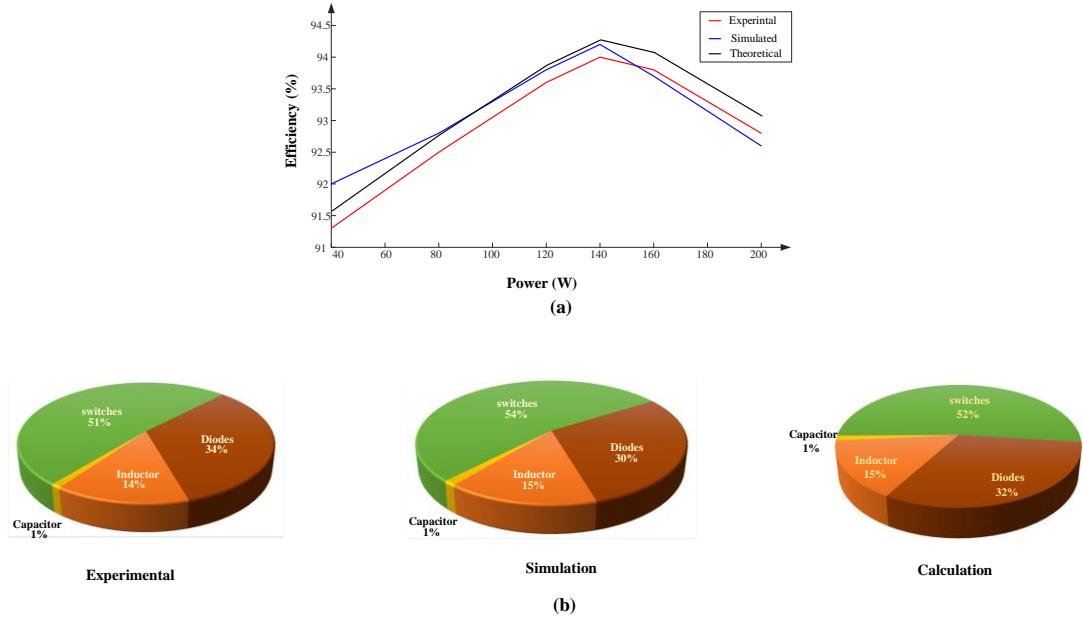

| <b>Figure 3.9.</b> (a) Efficiency corresponding to output powers and (b) Power loss distribution .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

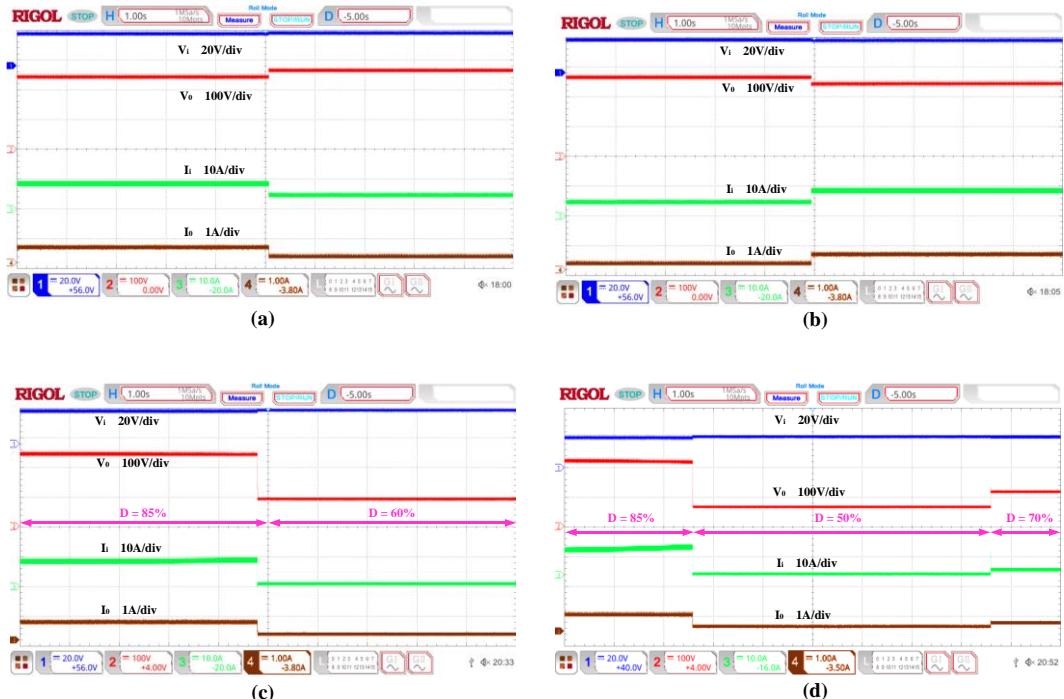

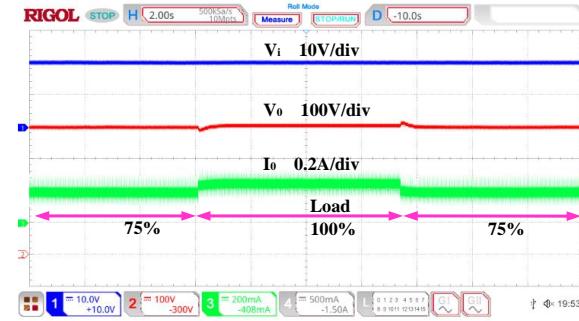

| <b>Figure 3.10.</b> Dynamic variation of HSL-CSG converter in terms of (A) load increase (B) load decrease (C) two step variation in duty ratio (D) Three step variation in duty ratio .....                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

| <b>Figure 3.11.</b> Closed loop validation of HSL-CSG converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

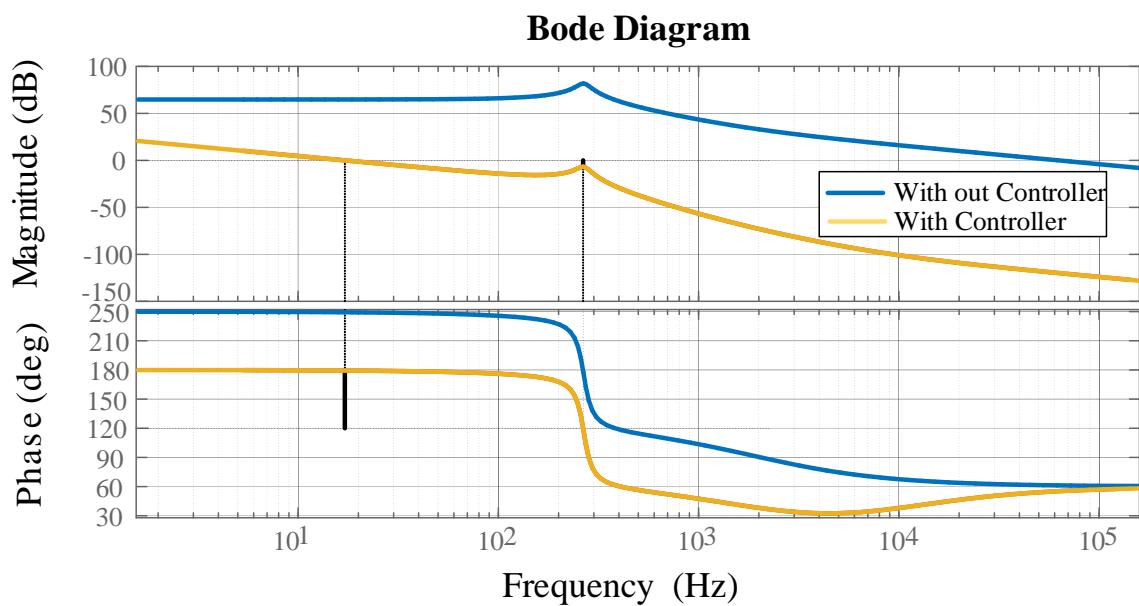

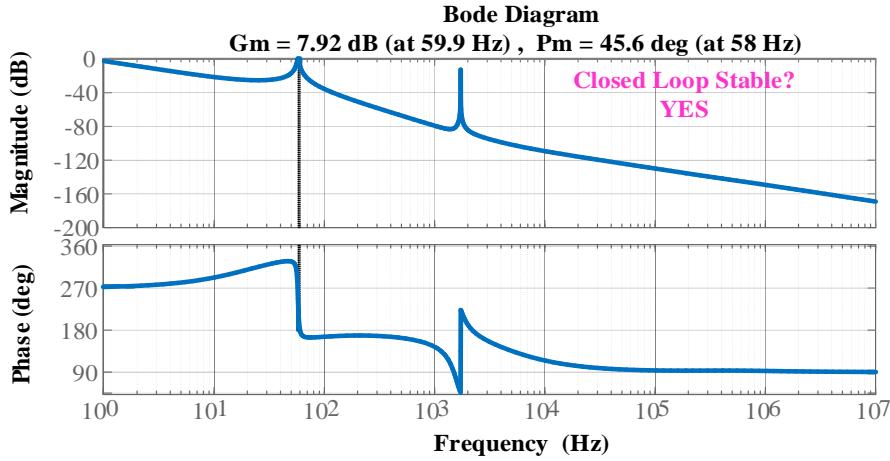

| <b>Figure 3.12.</b> Bode plots of HSL-CSG converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

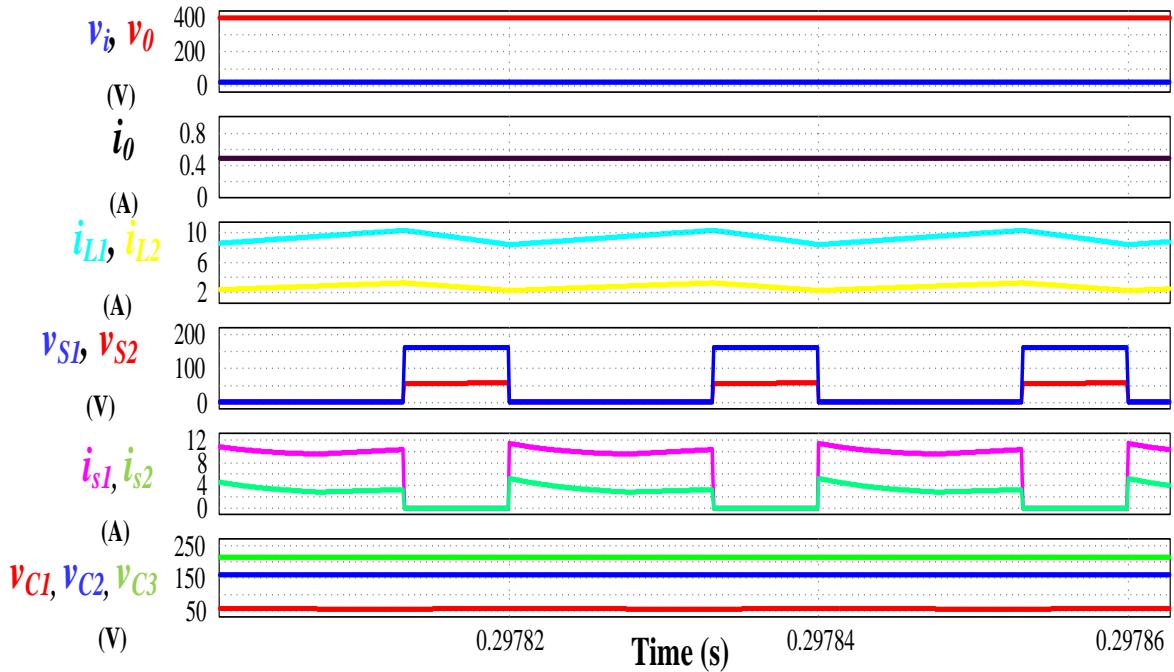

| <b>Figure 3.13.</b> Simulated results of HSL-CSG converter.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 |

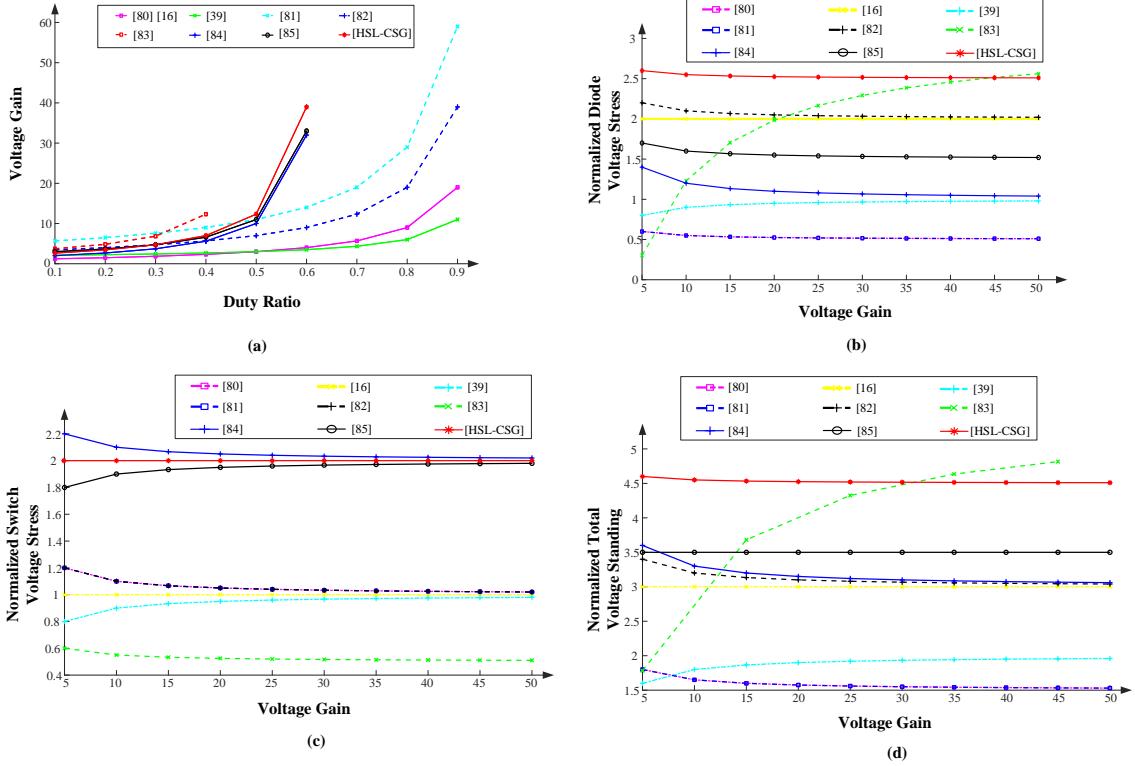

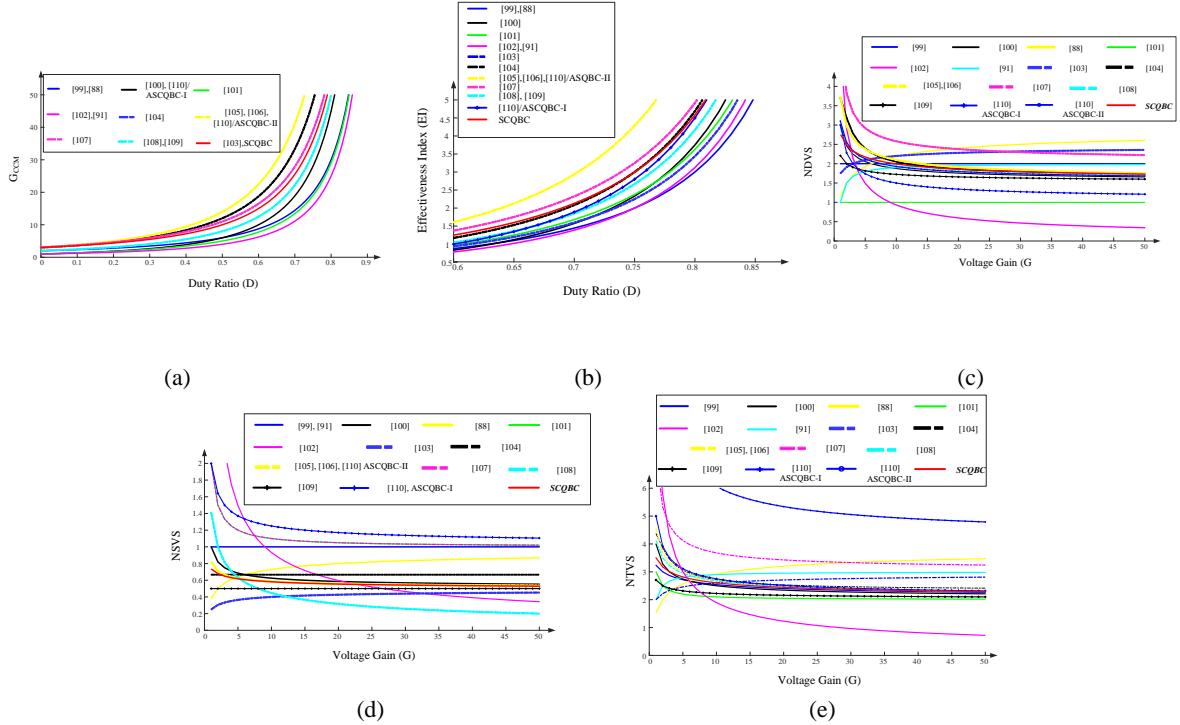

| <b>Figure. 3.14.</b> Performance comparison (a) voltage gain (b) NDVS (c) NSVS and (d) NTVS .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41 |

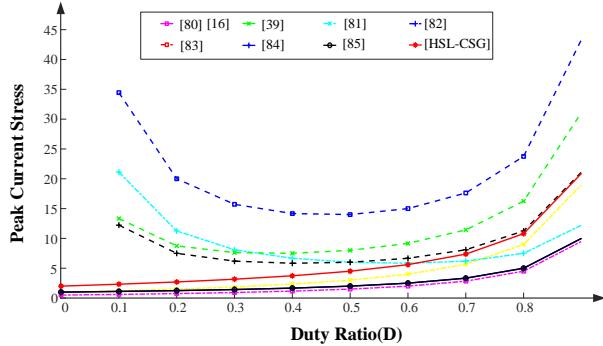

| <b>Figure. 3.15.</b> Peak current stress versus duty ratio of Switches .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41 |

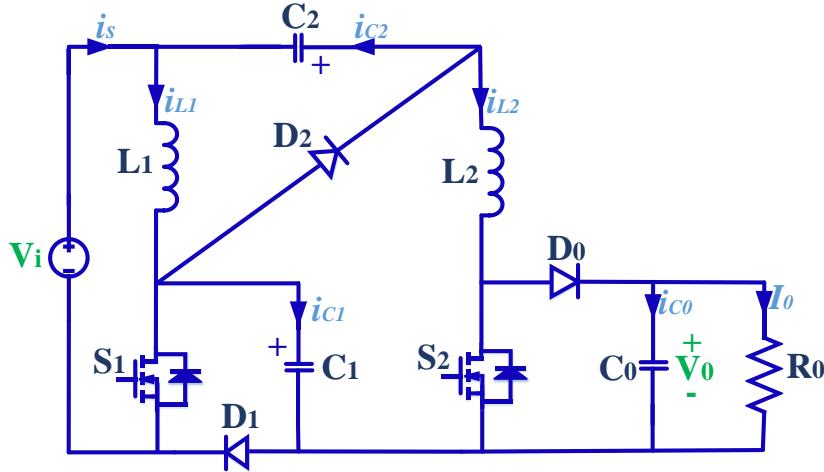

| <b>Figure 4.1.</b> ASC-QBC-I converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47 |

| <b>Figure 4.2.</b> ASC-QBC-II converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47 |

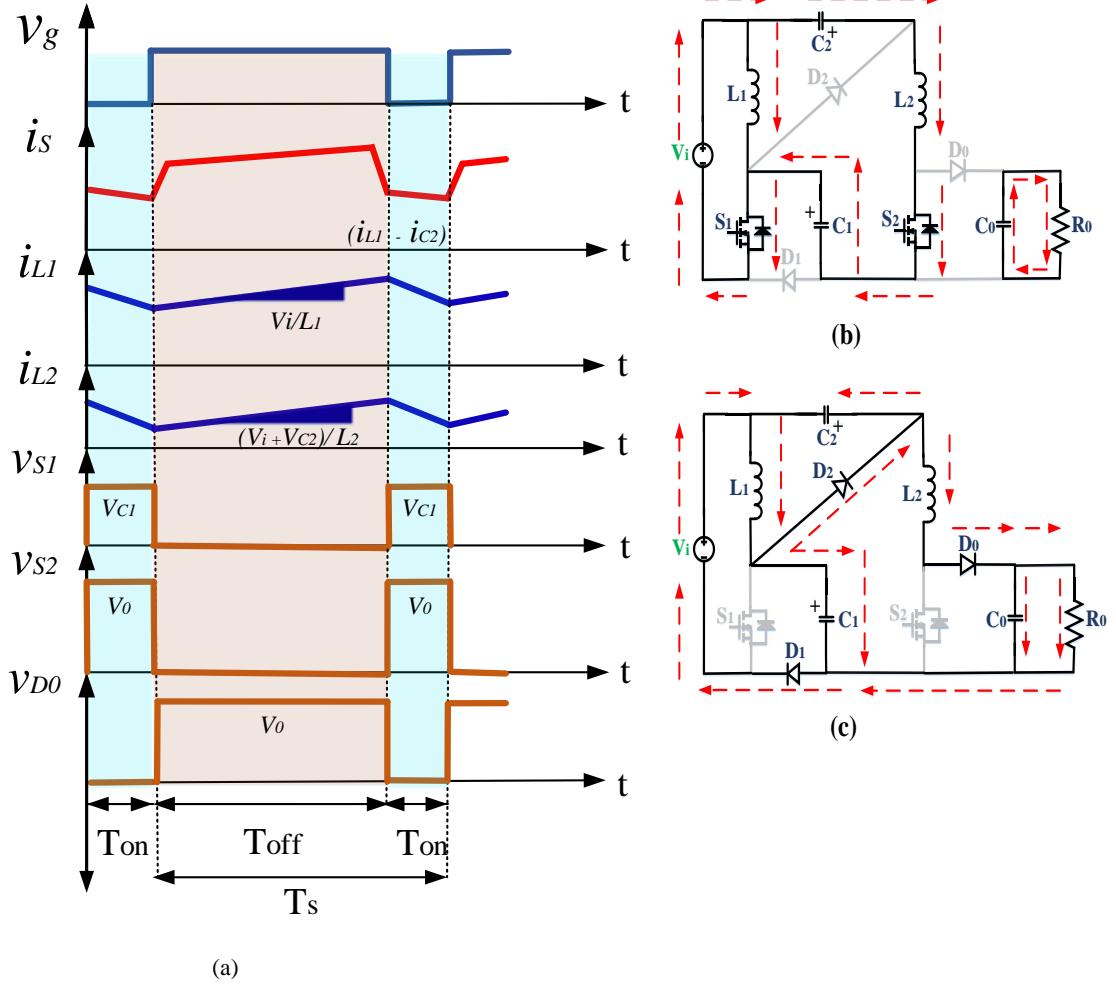

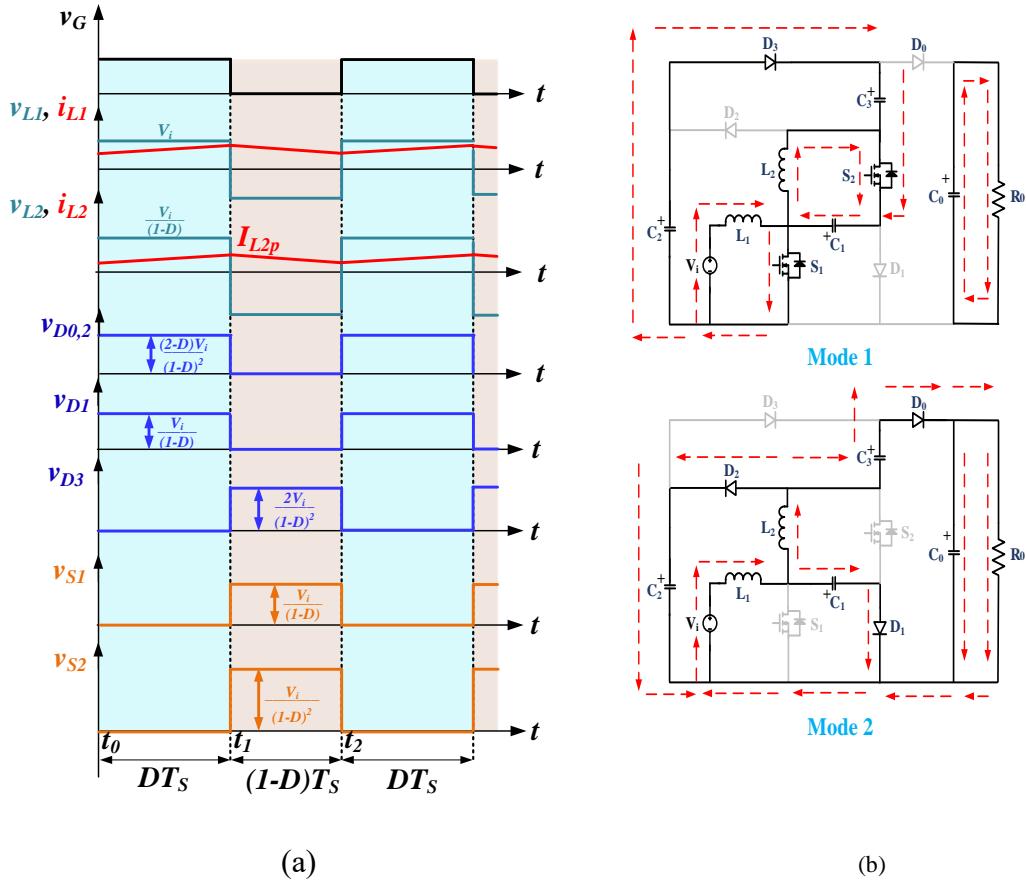

| <b>Figure 4.3.</b> ASC-QBC-I converter (a) ideal wave forms (b) and (c) operating modes .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

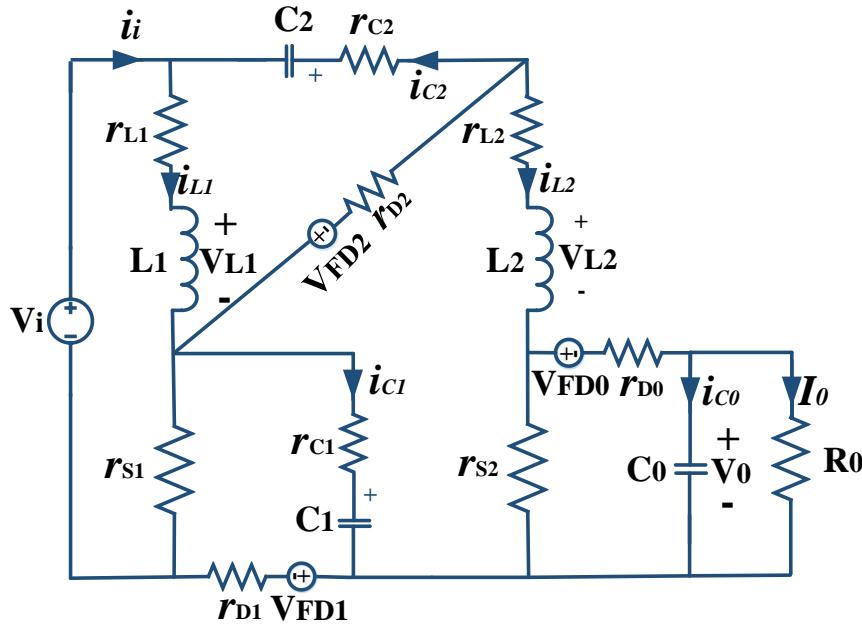

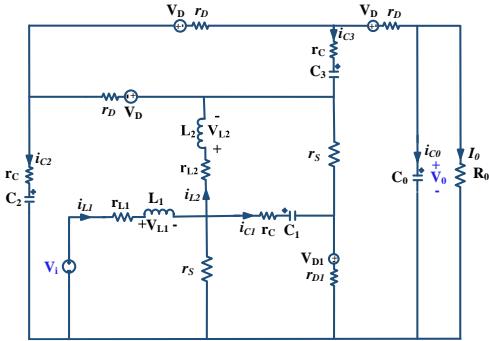

| <b>Figure 4.4.</b> Equivalent circuit of ASC-QBC-I converter with element parasitics .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

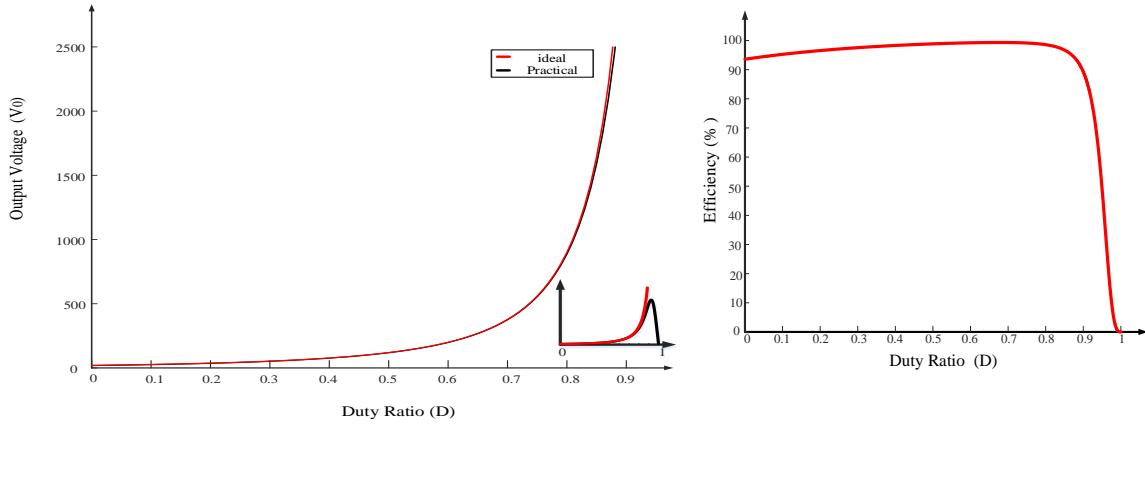

| <b>Figure 4.5.</b> Parasitics influence on ASCQBC-I converter (a) output voltage (b) efficiency ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51 |

| <b>Figure 4.6.</b> ASC-QBC-II converter (a) ideal wave forms (b) and (c) operating modes .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 |

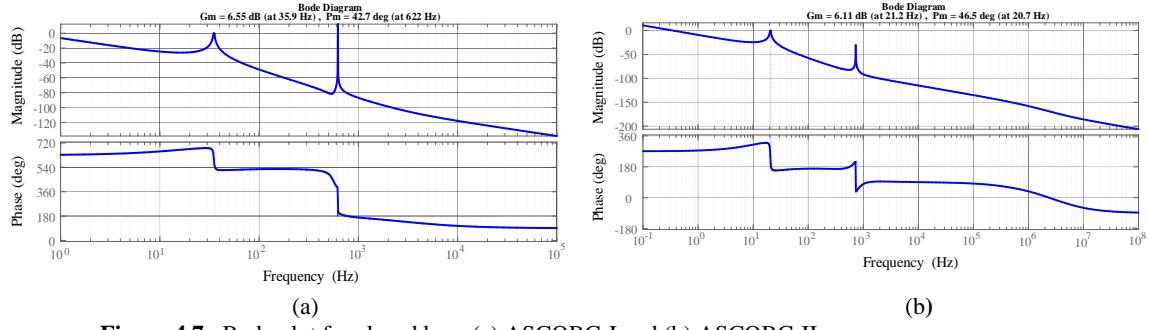

| <b>Figure 4.7.</b> Bode plot for closed loop (a) ASCQBC-I (b) ASCQBC-II .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56 |

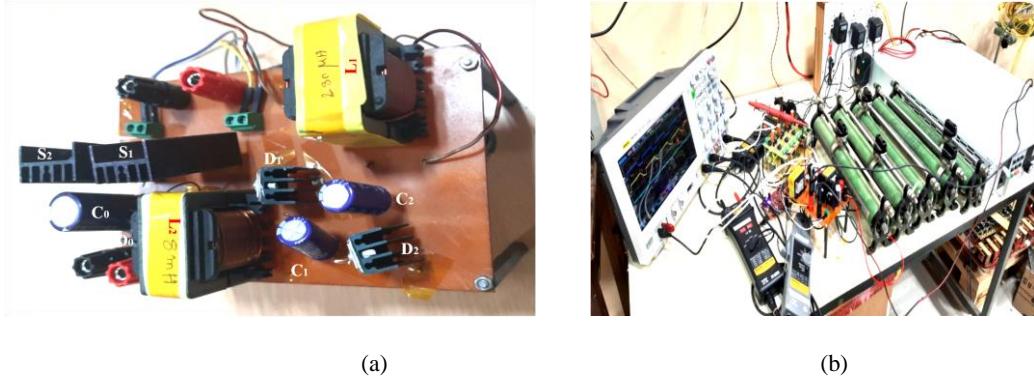

| <b>Figure 4.8.</b> ASCQBC-I (a) prototype (b) experimental setup .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56 |

| <b>Figure 4.9.</b> ASCQBC-II (a) prototype (b) experimental setup .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

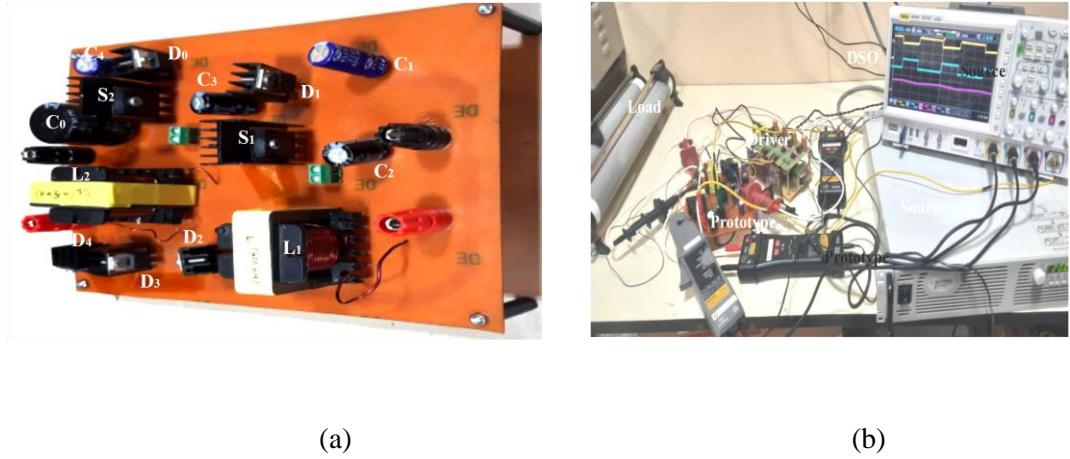

| <b>Figure 4.10.</b> (ASC-QBC-I). (a) Input and output voltage ( $V_i$ & $V_o$ ) (b) Inductor currents ( $i_{L1}$ & $i_{L2}$ ) (c) Switch Currents ( $i_{S1}$ & $i_{S2}$ ) (d) Capacitor Voltages ( $V_{C1}$ & $V_{C2}$ ) (e) Switch Voltages ( $V_{S1}$ & $V_{S2}$ ) (f) Diode voltages ( $V_{D0} - V_{D2}$ ); (ASC-QBC-II). (g)Input and output voltage ( $V_i$ & $V_o$ ) (h) Inductor currents ( $i_{L1}$ & $i_{L2}$ ) (i) Switch Currents ( $i_{S1}$ & $i_{S2}$ ) (j) Capacitor Voltages ( $V_{C1} - V_{C4}$ ) (k) Switch Voltages ( $V_{S1}$ & $V_{S2}$ ) (l) Diode voltages ( $V_{D0} - V_{D4}$ ) ..... | 59 |

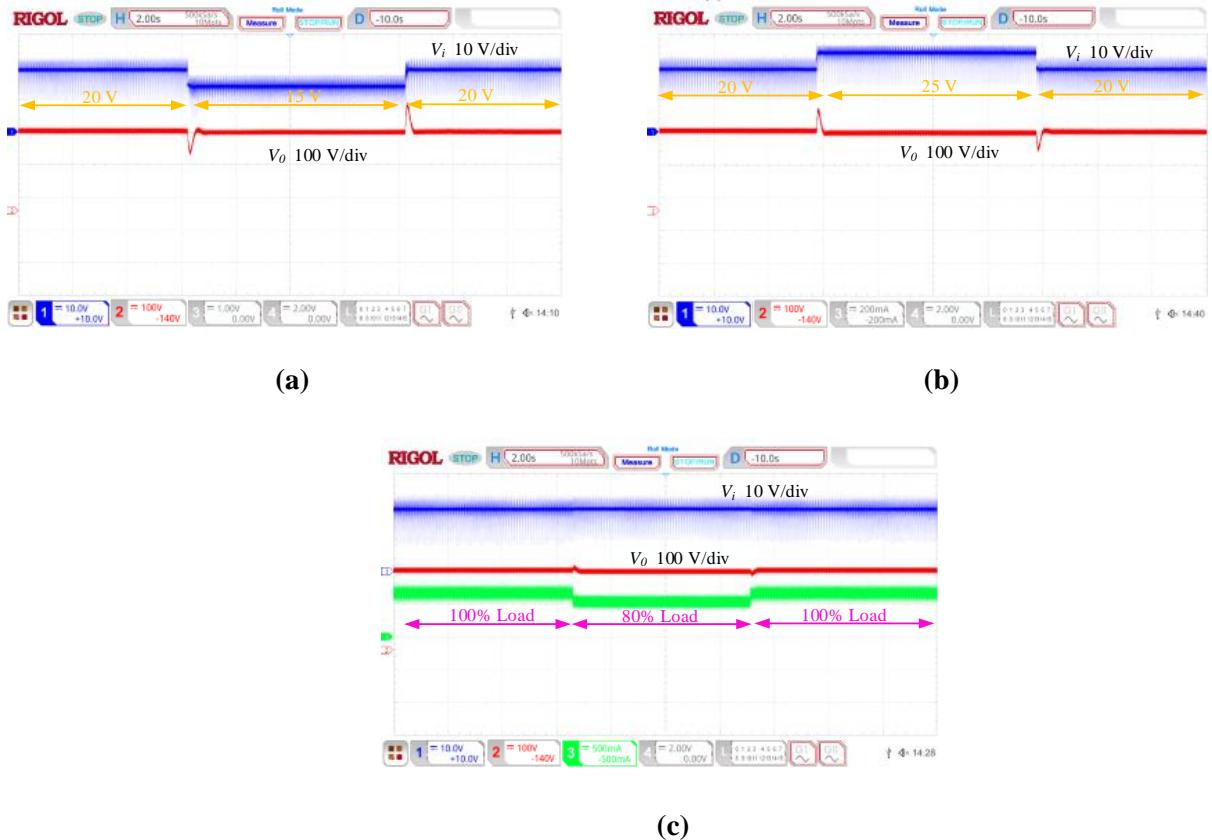

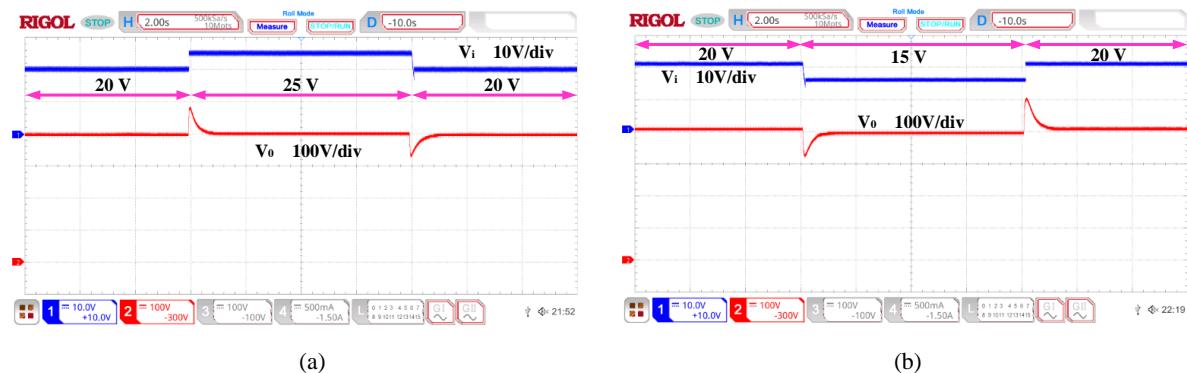

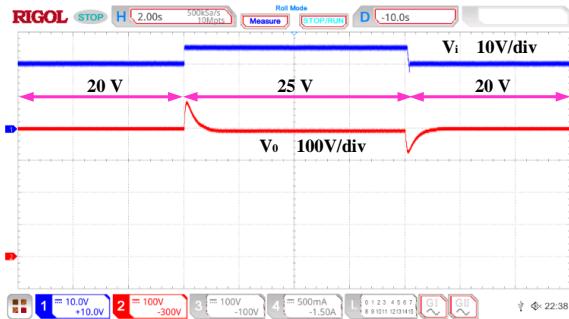

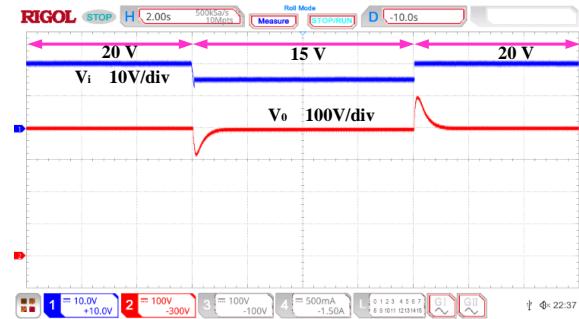

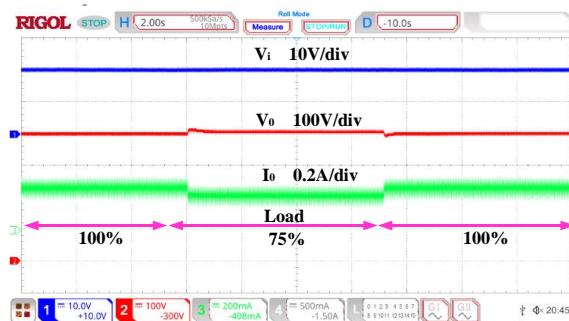

| <b>Figure 4.11.</b> Closed loop performance of ASC-QBC-I converter for step variation in input voltage (a) 20 V- 25 V- 20 V (b)20 V- 15 V- 20 V, ASC-QBC-II converter (c) 20 V- 25 V- 20 V (d) 20 V- 15 V- 20 V, step variations in load (e) ASCQBC-I (f) ASCQBC-II .....                                                                                                                                                                                                                                                                                                                                    | 60 |

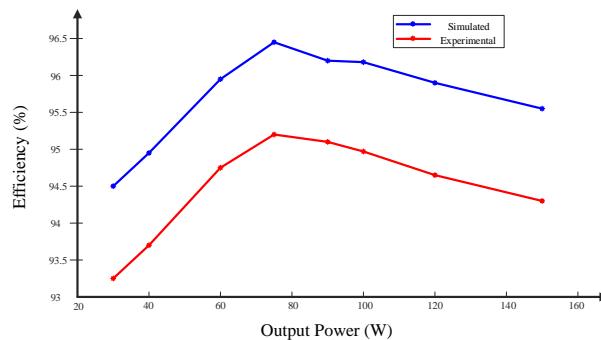

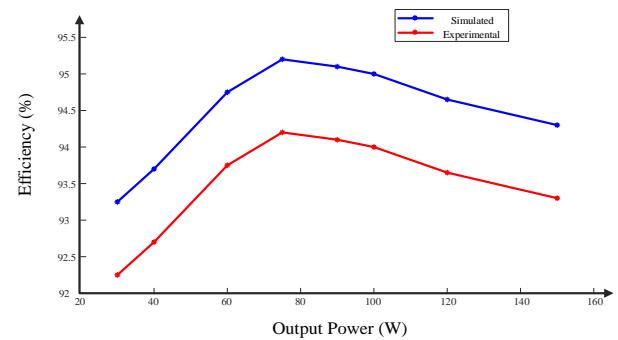

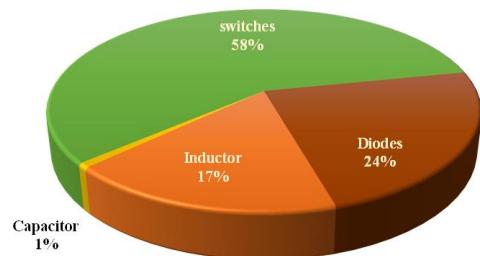

| <b>Figure 4.12.</b> Efficiency versus output power (a) ASC-QBC-I (b) ASCQBC-II .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60 |

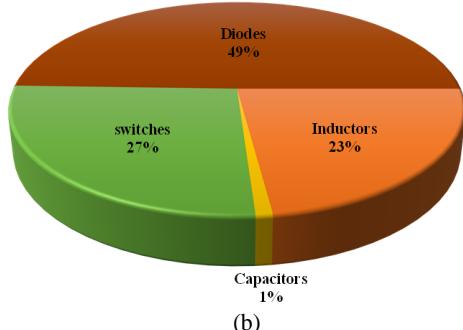

| <b>Figure 4.13.</b> Loss distribution of (a) ASC-QBC-I (b) ASCQBC-II .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

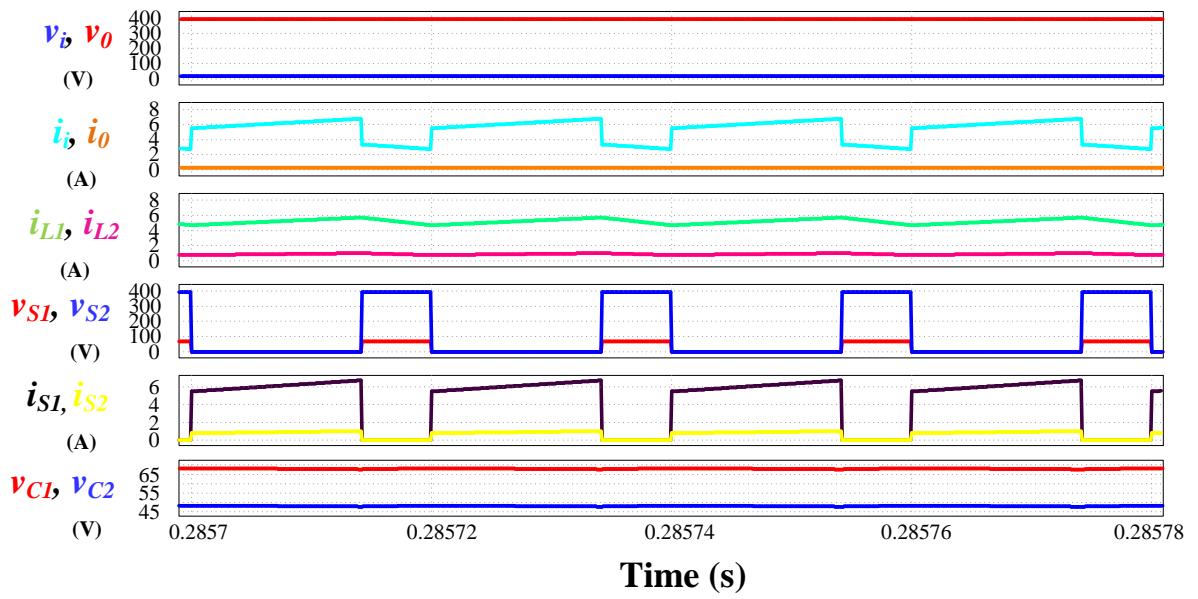

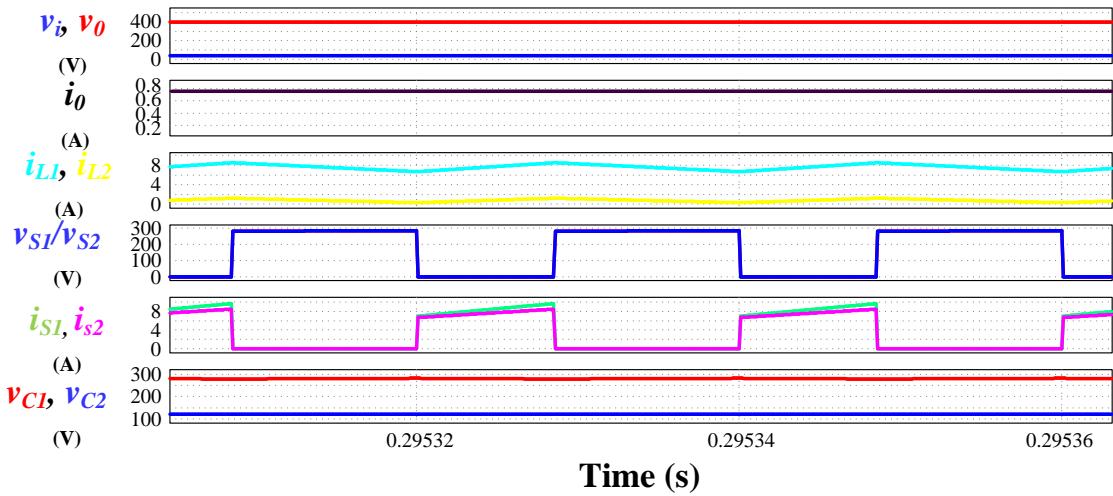

| <b>Figure 4.14.</b> Simulated results of ASC-QBC-I converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61 |

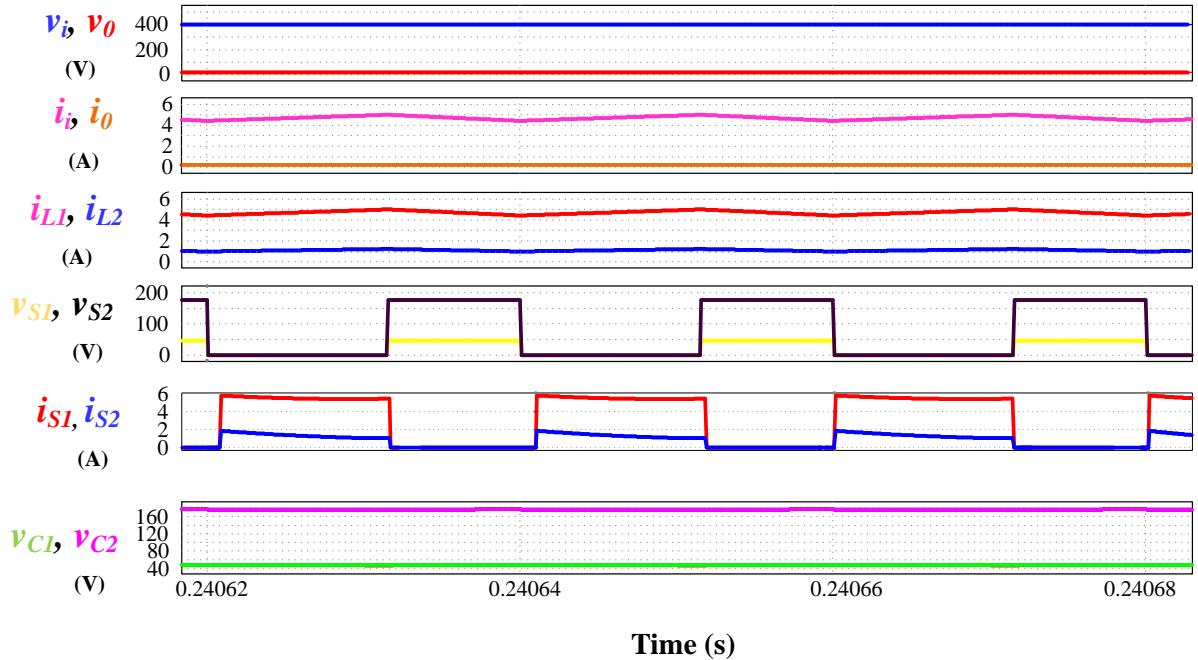

| <b>Figure 4.15.</b> Simulated results of ASC-QBC-II converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 4.16.</b> Performance comparison indices (a) voltage gain (b) NSVS (c) NDVS (d) NTVS (e) switch current stress .....                                                                                                                                                                                                                                                                                                                                                                            | 63 |

| <b>Figure 5.1.</b> SCQBC converter's CCM (a) ideal operating waveforms (b) modes of operation .....                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

| <b>Figure 5.2.</b> SCQBC equivalent circuit with element parasitics .....                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72 |

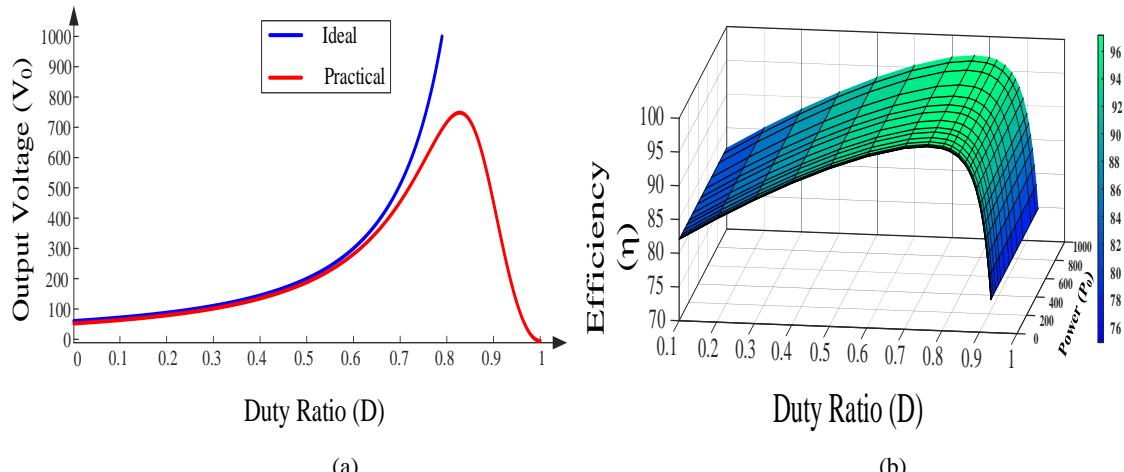

| <b>Figure 5.3.</b> SCQBC converter (a) $V_0$ versus $D$ (b) 3-D plot of efficiency, power versus duty ratio with element parasitics .....                                                                                                                                                                                                                                                                                                                                                                 | 72 |

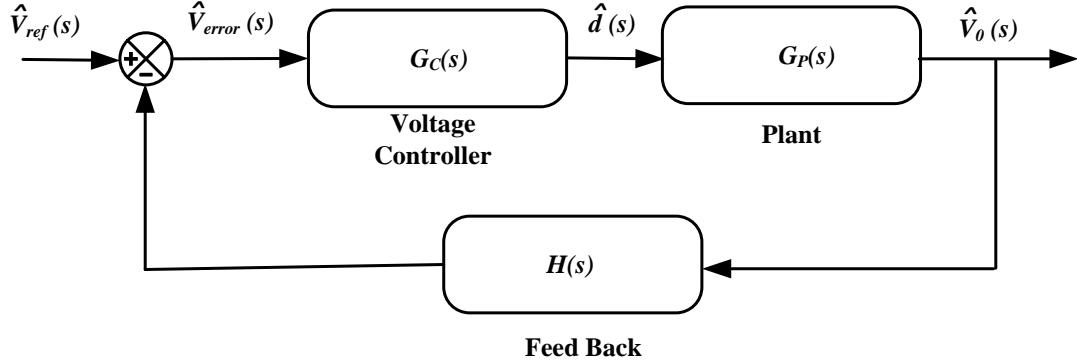

| <b>Figure 5.4.</b> Single loop voltage control scheme for SCQBC converter .....                                                                                                                                                                                                                                                                                                                                                                                                                           | 73 |

| <b>Figure 5.5.</b> Closed loop bode plot of SCQBC converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75 |

| <b>Figure 5.6.</b> Simulated results of SCQBC converter .....                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75 |

| <b>Figure 5.7.</b> SCQBC converter (a) prototype of (b) Experimental setup .....                                                                                                                                                                                                                                                                                                                                                                                                                          | 76 |

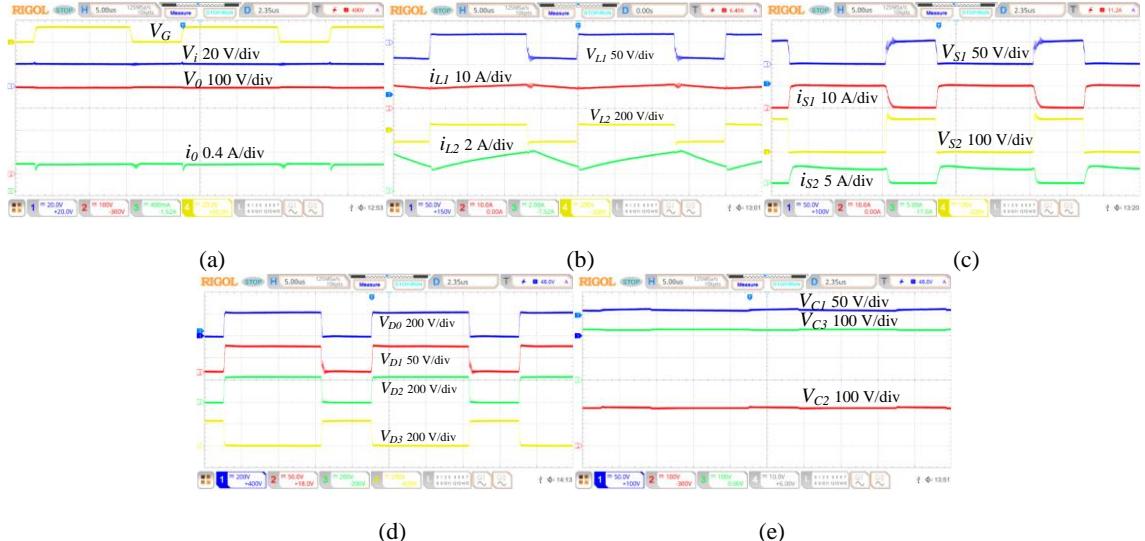

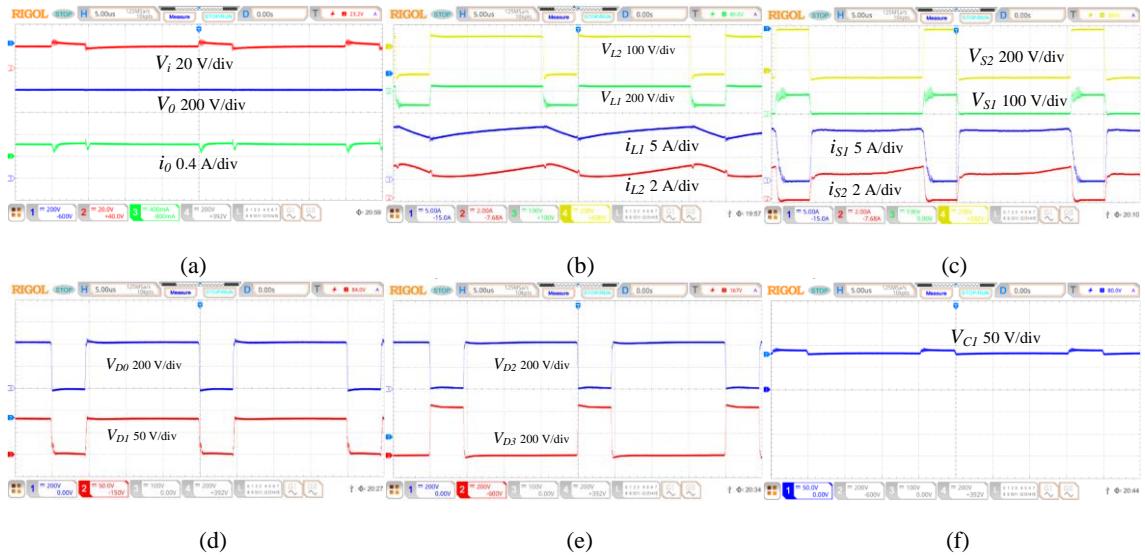

| <b>Figure 5.8.</b> Experimental results of SCQBC converter for 400 V output (a) input and output voltages $v_i$ and $v_o$ , load current $i_o$ (b) inductor voltages ( $v_{L1}$ and $v_{L2}$ ) and currents ( $i_{L1}$ and $i_{L2}$ ) (c) switch voltages ( $v_{S1}$ and $v_{S2}$ ) and currents ( $i_{S1}$ and $i_{S2}$ ) (d) diode voltages ( $V_{D0}$ – $V_{D3}$ ) (e) capacitor Voltages ( $V_{C1}$ – $V_{C3}$ ) .....                                                                                | 76 |

| <b>Figure 5.9.</b> Experimental results of SCQBC converter for 800 V output (a) input and output voltages $v_i$ and $v_o$ , load current $i_o$ (b) inductor voltages ( $v_{L1}$ and $v_{L2}$ ) and currents ( $i_{L1}$ and $i_{L2}$ ) (c) switch voltages ( $v_{S1}$ and $v_{S2}$ ) and currents ( $i_{S1}$ and $i_{S2}$ ) (d) diode voltages ( $V_{D0}$ – $V_{D1}$ ) (e) diode voltages ( $V_{D2}$ – $V_{D3}$ ) (f) capacitor Voltage ( $V_{C1}$ ). (g) Capacitor Voltages ( $V_{C2}$ – $V_{C3}$ ) ..... | 77 |

| <b>Figure 5.10.</b> Closed loop performance of SCQBC converter for (a) stepped $V_i$ (b) stepped load .....                                                                                                                                                                                                                                                                                                                                                                                               | 77 |

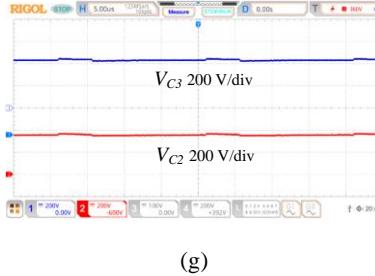

| <b>Figure 5.11.</b> SCQBC converter efficiency versus output power .....                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

| <b>Figure 5.12.</b> SCQBC converter loss distribution among various elements (a) ideal (b) experimental .....                                                                                                                                                                                                                                                                                                                                                                                             | 79 |

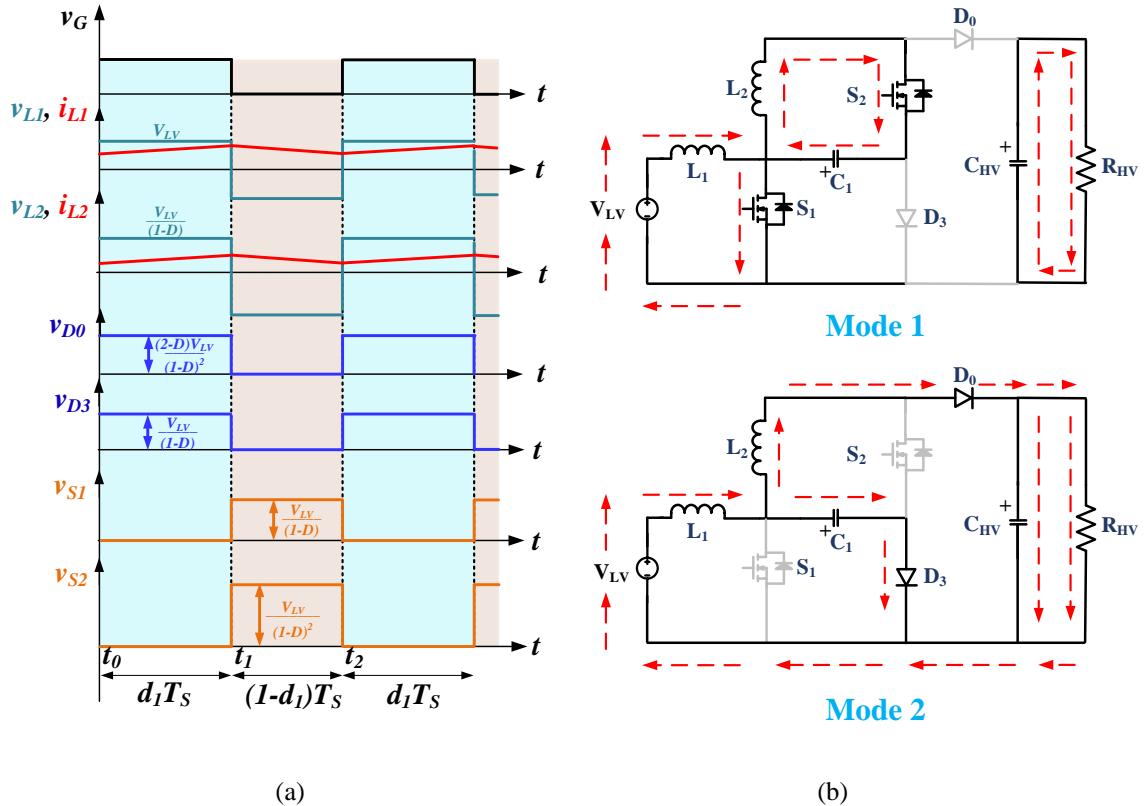

| <b>Figure 5.13.</b> Performance comparison of SCQBC converter with other quadratic boost dc-dc converters in terms of (a) voltage gain (b) EI (c) NSVS and (d) NTVS .....                                                                                                                                                                                                                                                                                                                                 | 83 |

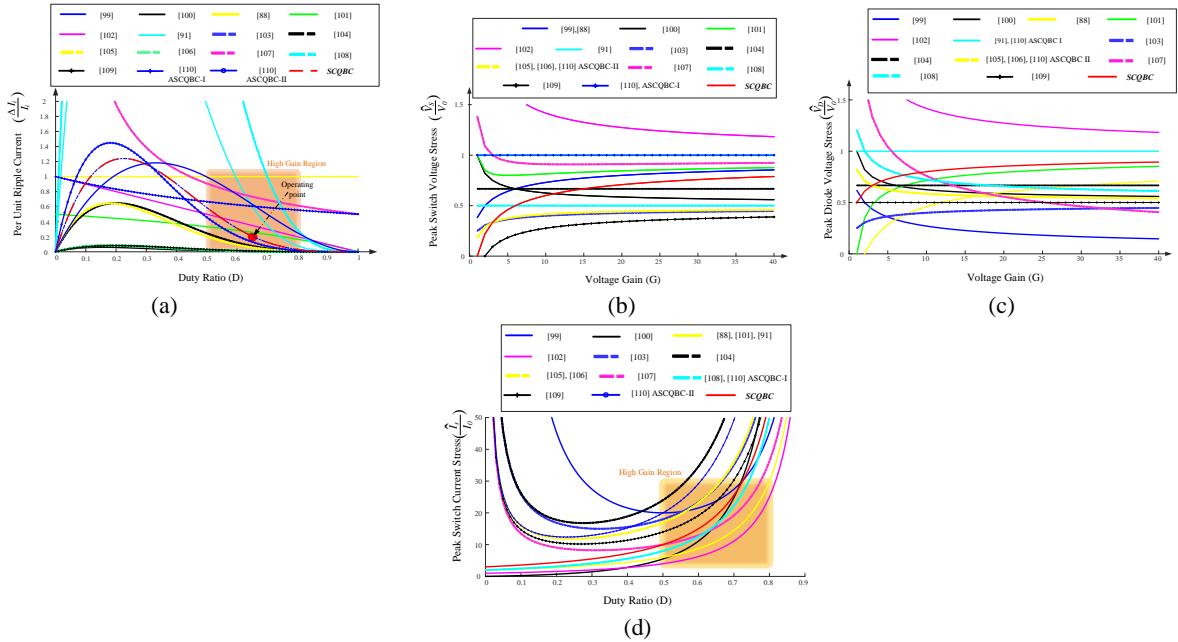

| <b>Figure 5.14.</b> Comparison of (a) Per unit ripple current (b) switches (c) diodes peak voltage stress and (d) switch peak current stress .....                                                                                                                                                                                                                                                                                                                                                        | 83 |

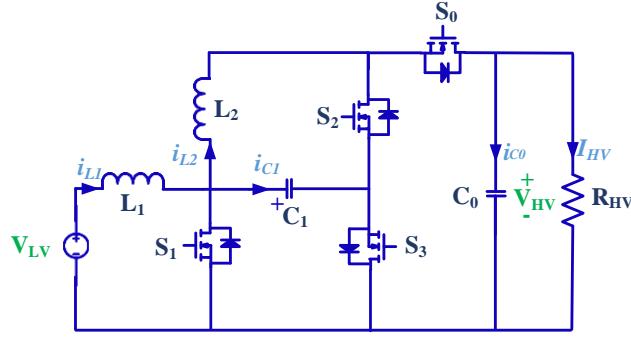

| <b>Figure 6.1.</b> Proposed bidirectional quadratic boost dc-dc converter .....                                                                                                                                                                                                                                                                                                                                                                                                                           | 87 |

| <b>Figure 6.2.</b> Boost mode (a) ideal operating waveforms (b) operating modes .....                                                                                                                                                                                                                                                                                                                                                                                                                     | 87 |

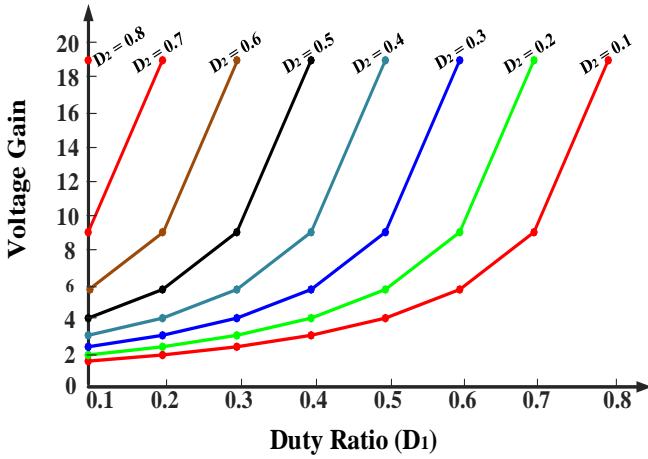

| <b>Figure 6.3.</b> Buck mode (a) ideal operating waveforms (b) operating modes .....                                                                                                                                                                                                                                                                                                                                                                                                                      | 89 |

| <b>Figure 6.4.</b> Bode plots of compensated (PI) proposed converter (a) boost mode (b) buck mode .....                                                                                                                                                                                                                                                                                                                                                                                                   | 92 |

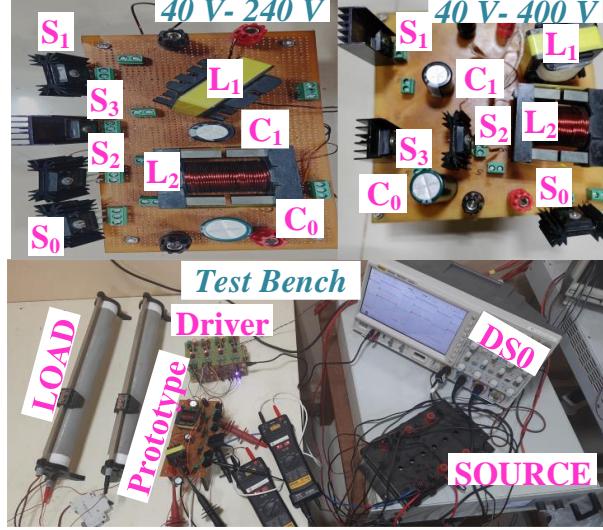

| <b>Figure 6.5.</b> Prototypes and experimental setup .....                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92 |

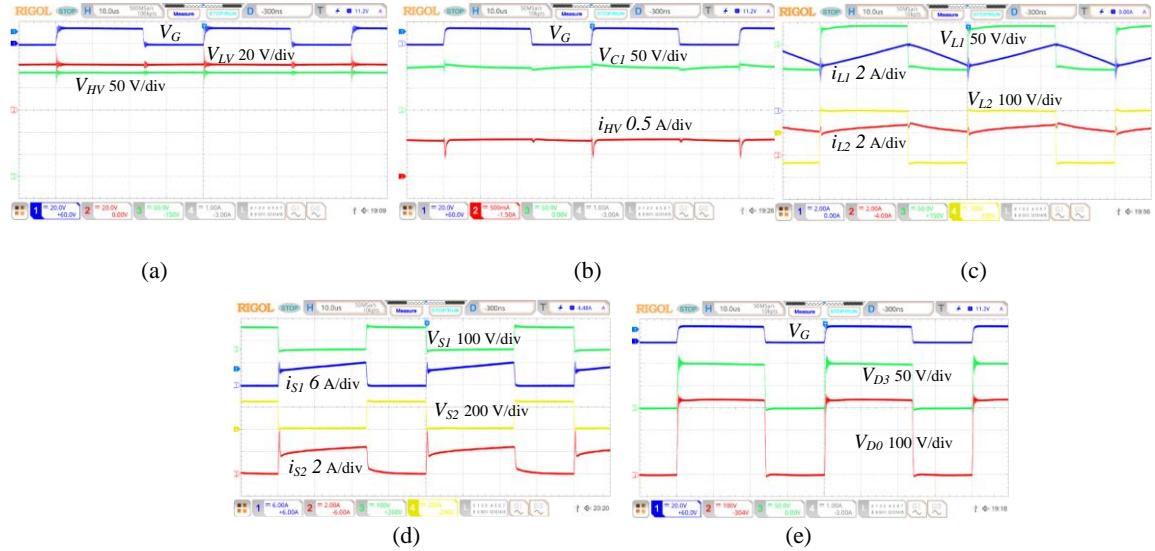

| <b>Figure 6.6.</b> Boost mode experimental results 40-240 V (a) input and output voltages ( $v_{LV}$ and $v_{HV}$ ) (b) intermediate capacitor $C_I$ voltage and HV side current ( $v_{CI}$ and $i_{HV}$ ) (c) inductor voltages and currents ( $v_L$ and $i_L$ ) (d) switch voltages and currents ( $v_S$ and $i_S$ ) (e) diode voltages ( $v_{D0}$ and $v_{D3}$ ) .....                                                                                                                                 | 93 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Figure 6.7.</b> Buck mode experimental results 240-40 V (a) input and output voltages ( $v_{LV}$ and $v_{HV}$ ) (b) inductor voltages and currents ( $v_L$ and $i_L$ ) (c) switch voltages and currents ( $v_S$ and $i_S$ ) (d) diode voltages ( $v_{D1}$ and $v_{D2}$ ) .....                                                                                                                                                                                                       | 93  |

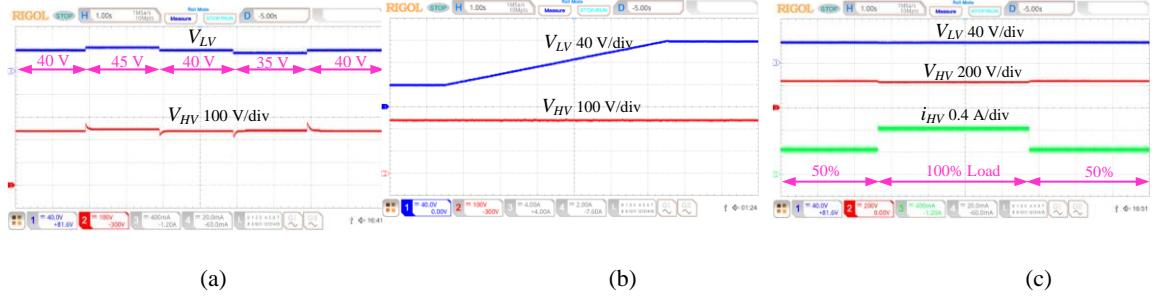

| <b>Figure 6.8.</b> Closed loop validation of 40-240 V (a) boost mode step change in $v_{LV}$ (b) buck mode ramped output $v_{LV}$ (c) boost mode step change in load 50% to 100% .....                                                                                                                                                                                                                                                                                                  | 94  |

| <b>Figure 6.9.</b> Boost mode experimental results 40-400 V (a) input and output voltages ( $v_{LV}$ and $v_{HV}$ ), and HV side current ( $i_{HV}$ ) (b) inductor voltages and currents ( $v_L$ and $i_L$ ) (c) switch voltages and currents ( $v_S$ and $i_S$ ) .....                                                                                                                                                                                                                 | 94  |

| <b>Figure 6.10.</b> Buck mode experimental results 400-40 V (a) input and output voltages ( $v_{LV}$ and $v_{HV}$ ) (b) inductor voltages and currents ( $v_L$ and $i_L$ ) (c) switch voltages and currents ( $v_S$ and $i_S$ ) .....                                                                                                                                                                                                                                                   | 94  |

| <b>Figure 6.11.</b> Boost mode simulated results 40-240 V.....                                                                                                                                                                                                                                                                                                                                                                                                                          | 94  |

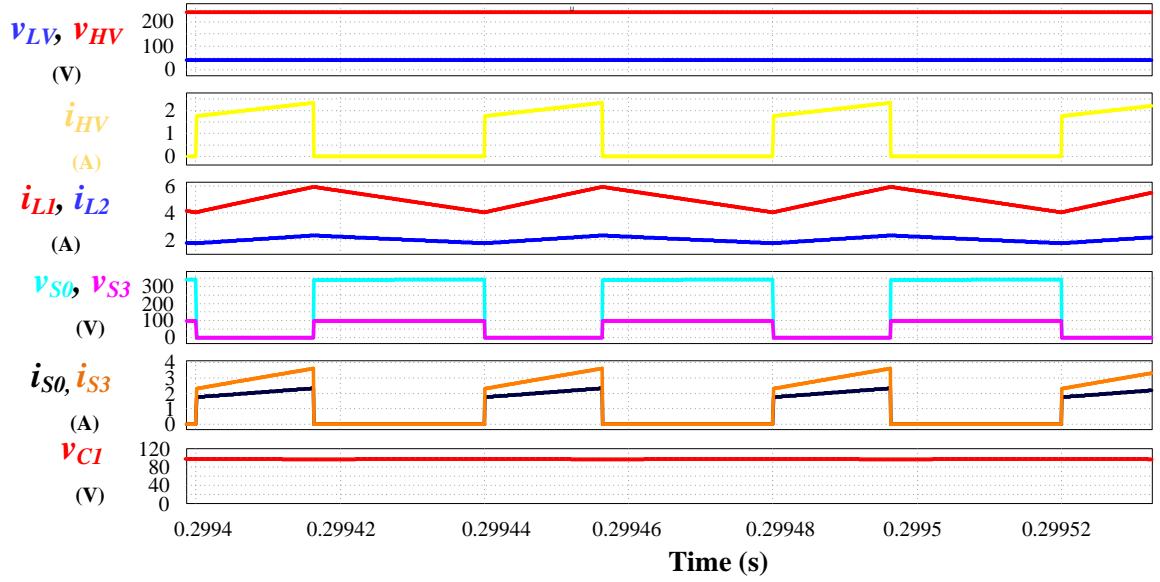

| <b>Figure 6.12.</b> Buck mode simulated results 240-40 V.....                                                                                                                                                                                                                                                                                                                                                                                                                           | 95  |

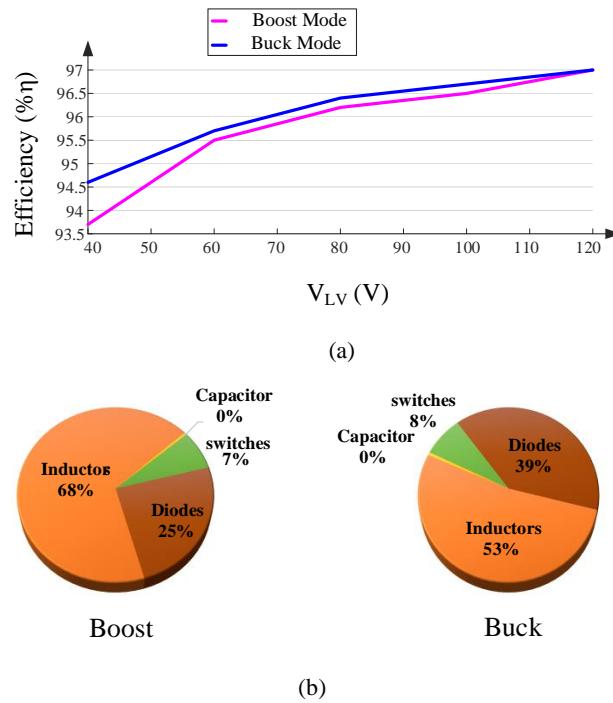

| <b>Figure 6.13.</b> (a) Efficiency variation of the proposed converter with wide range of $V_{LV}$ , 40~120 V (b) loss distribution for boost ( $V_{LV} = 40$ V) and buck ( $V_{HV} = 240$ V) modes .....                                                                                                                                                                                                                                                                               | 96  |

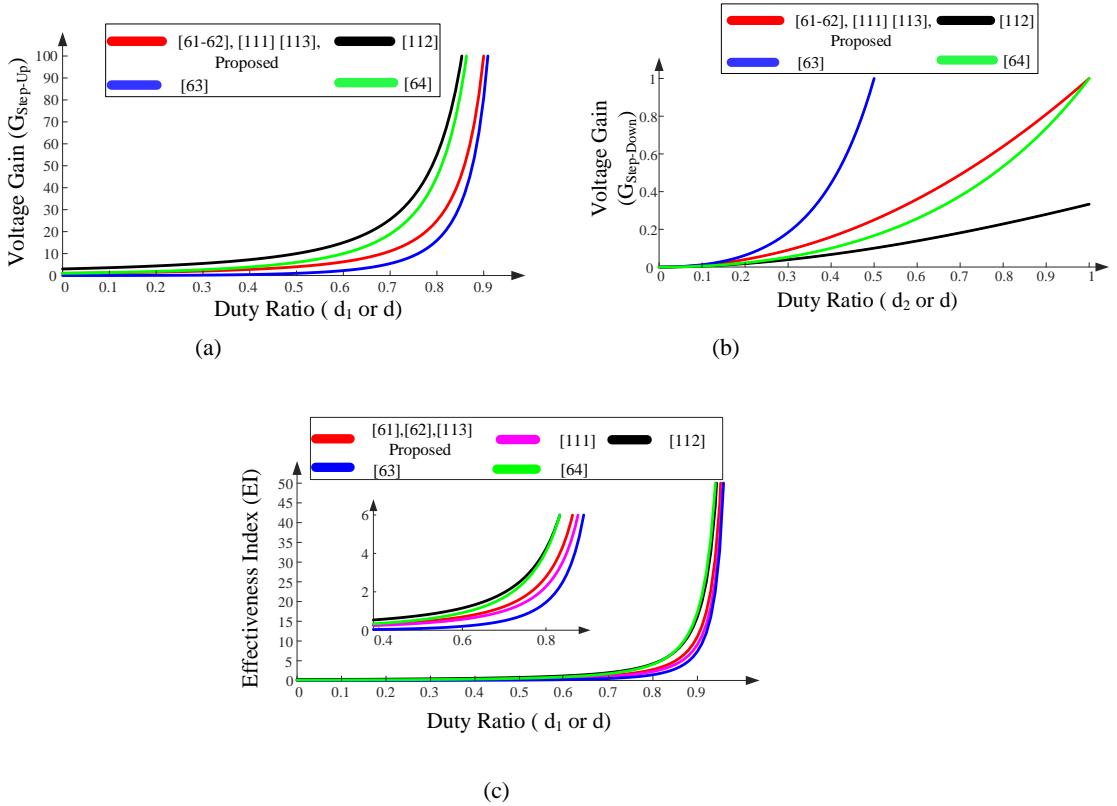

| <b>Figure 6.14.</b> Performance comparison VTR's and effectiveness index (a) GBoost (b) GBuck (c) EI .....                                                                                                                                                                                                                                                                                                                                                                              | 99  |

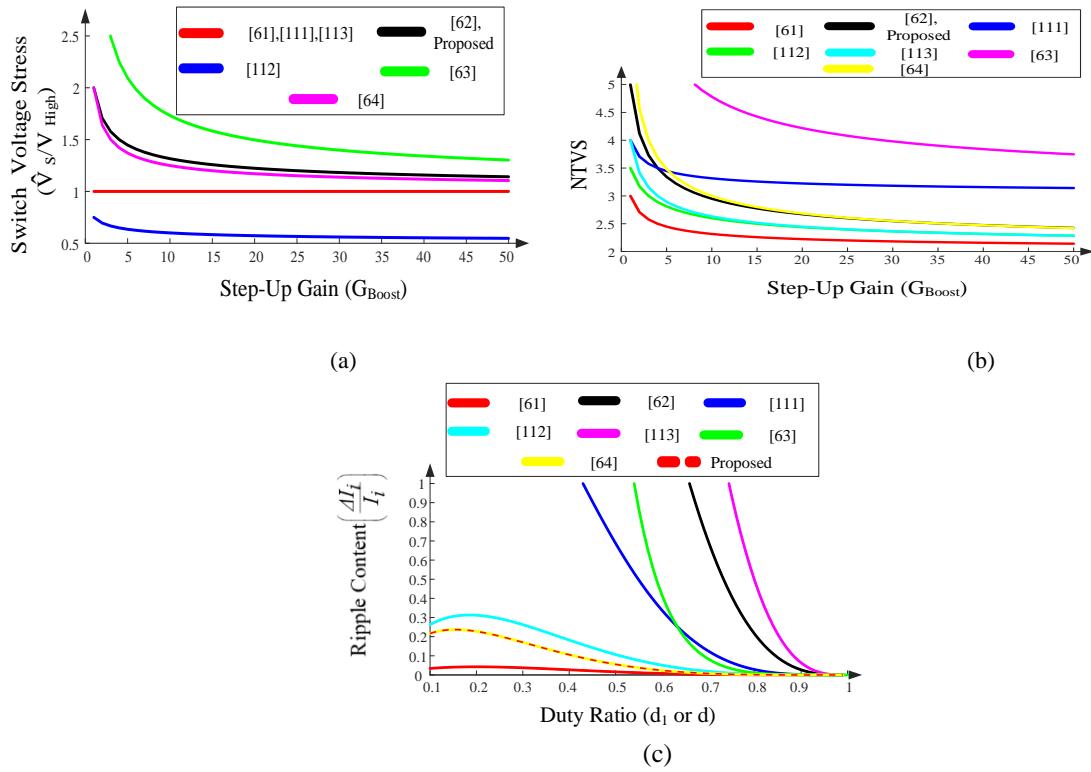

| <b>Figure 6.15.</b> Performance comparison of switch voltage stress and input current ripple (a) Maximum switch voltage stress (b) NTVS (c) per unit current ripple .....                                                                                                                                                                                                                                                                                                               | 99  |

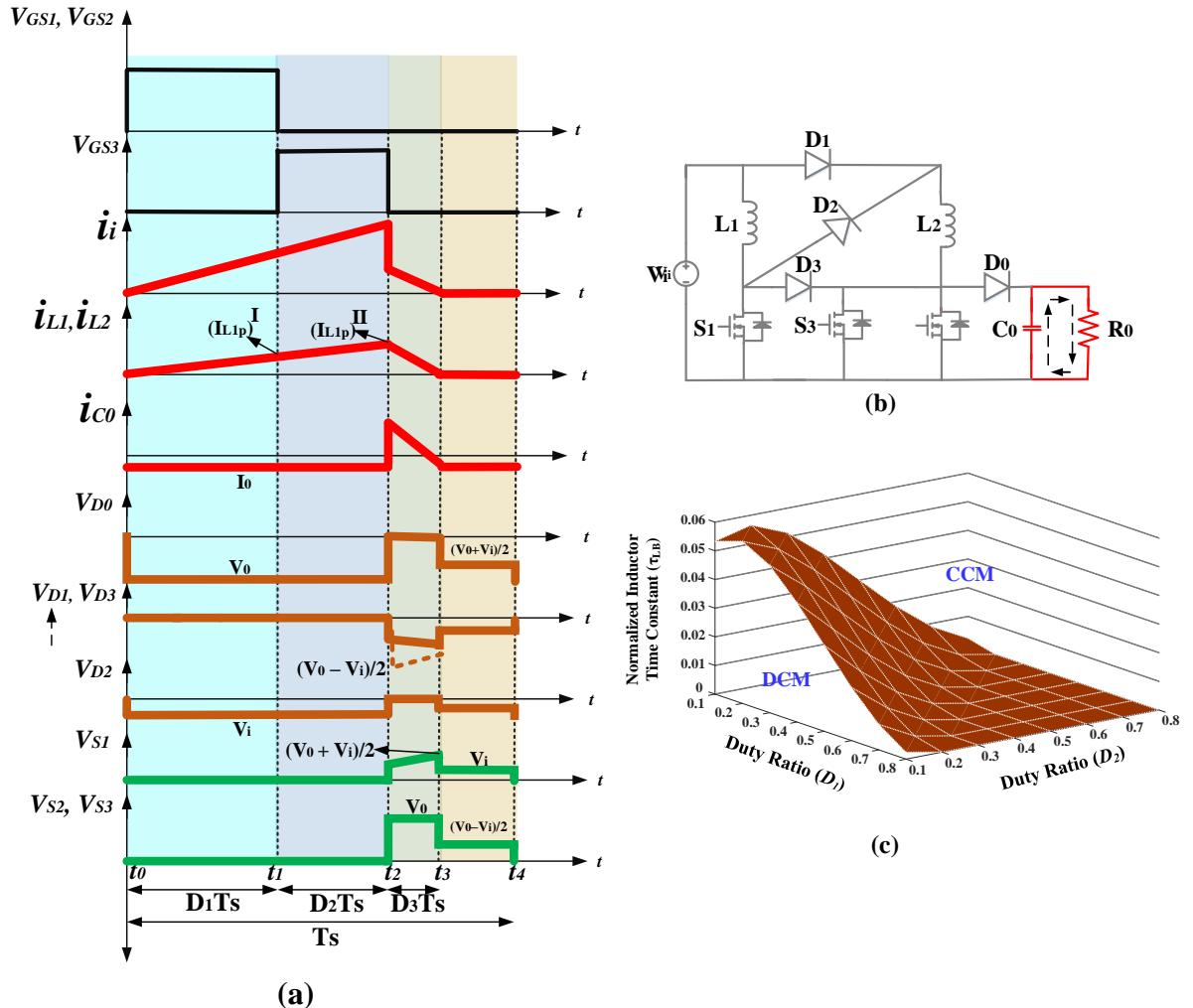

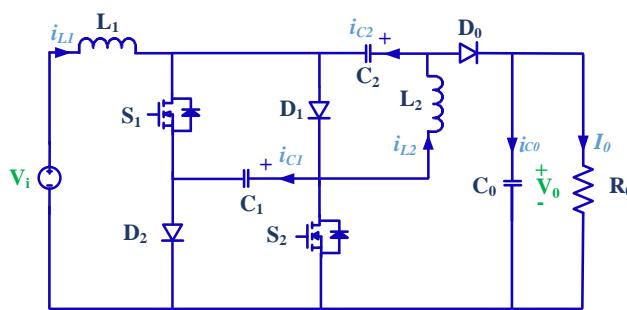

| <b>Figure 7.1.</b> Proposed DSL-HBSC-I converter.....                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102 |

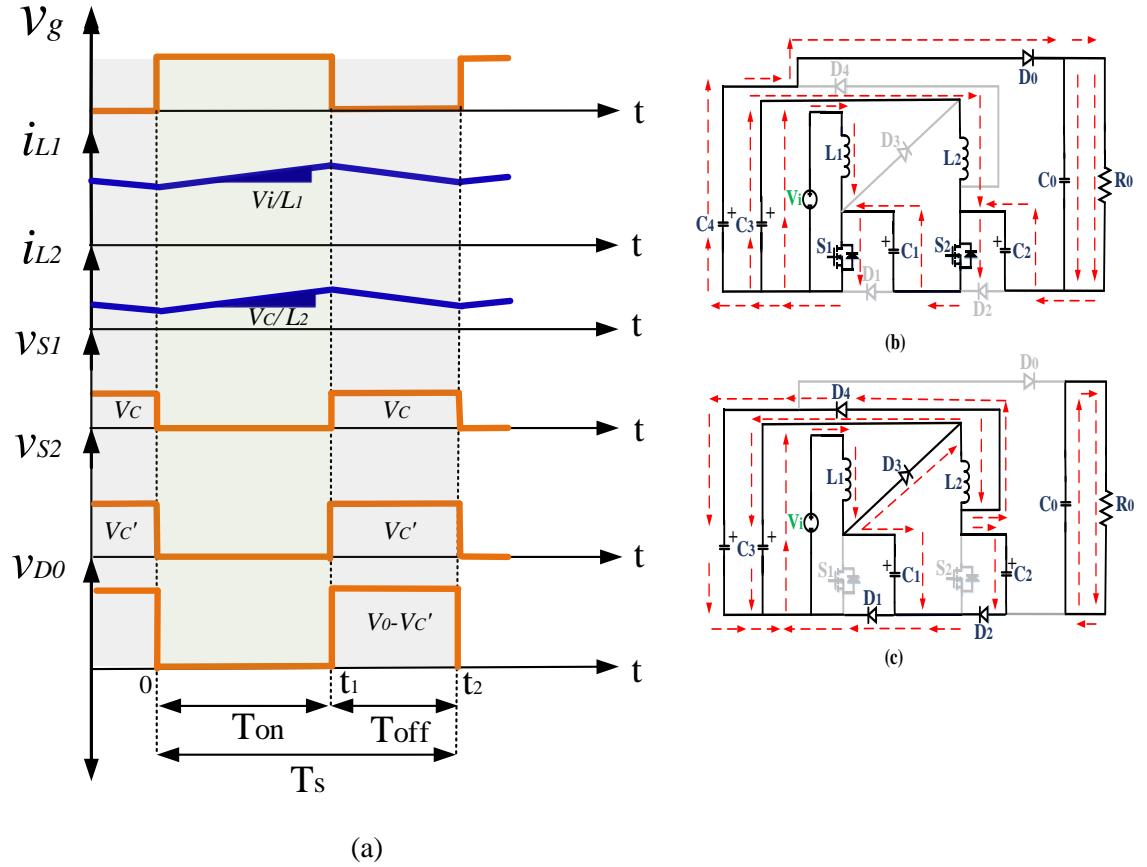

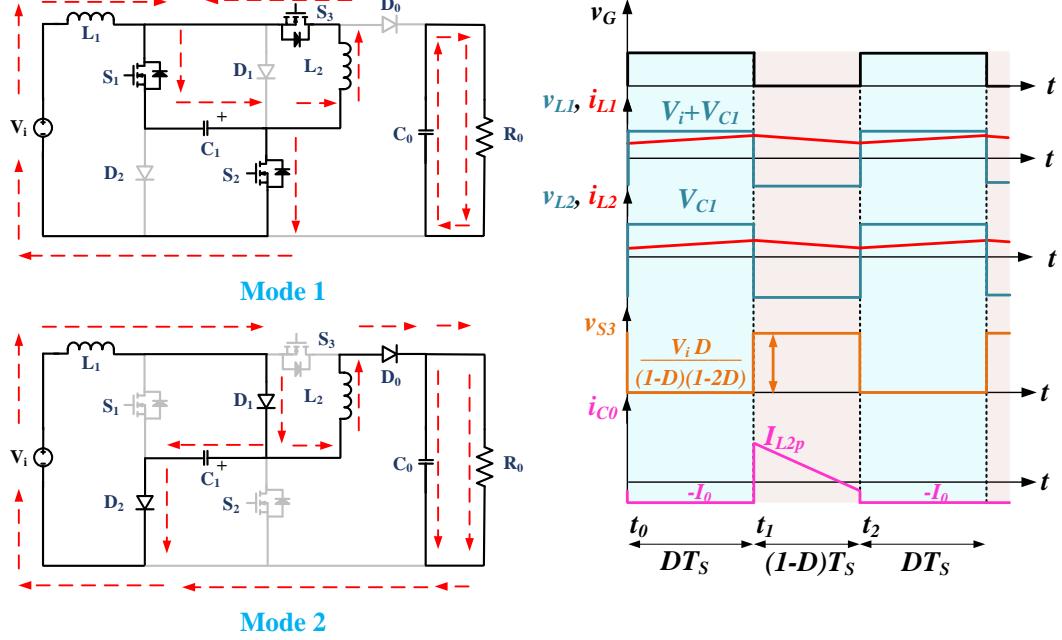

| <b>Figure 7.2.</b> DSL-HBSC-I converter (a) operating modes (b) ideal operating waveforms .....                                                                                                                                                                                                                                                                                                                                                                                         | 103 |

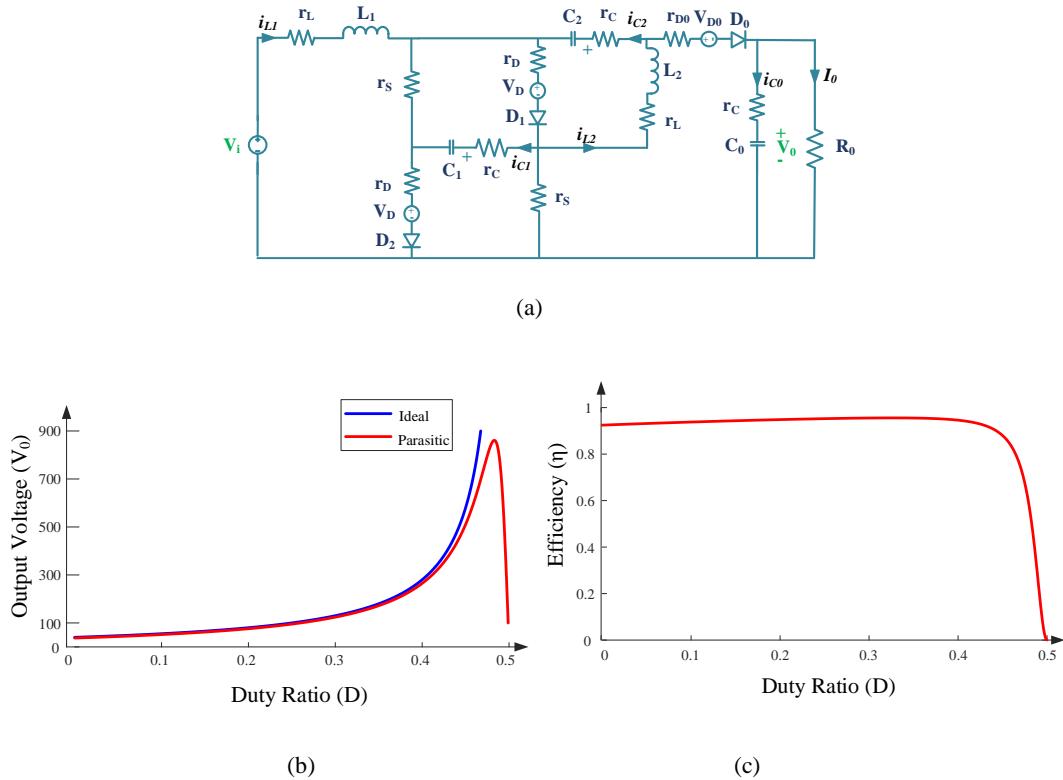

| <b>Figure 7.3.</b> Parasitic influence (a) DSL-HBSC-I converter (b) $V_0$ -Parasitic and (c) $\eta$ versus duty ratio .....                                                                                                                                                                                                                                                                                                                                                             | 107 |

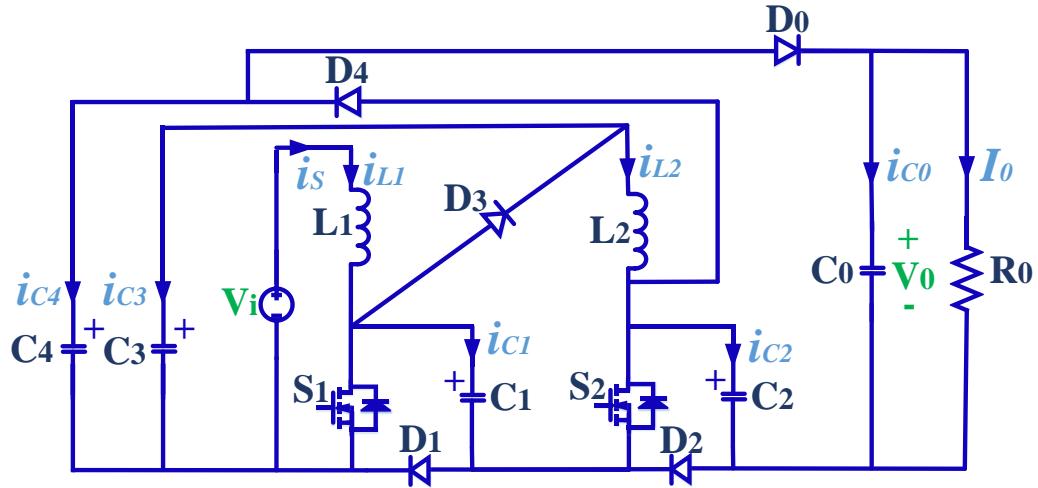

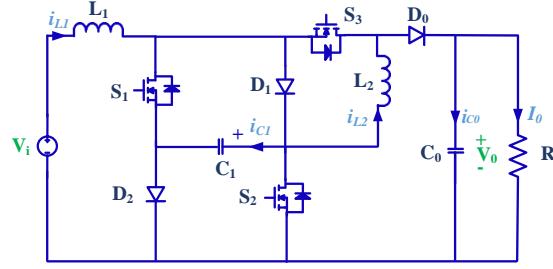

| <b>Figure 7.4.</b> DSL-HBSC-II converter (a) topology (b) operating modes (c) operating waveforms .....                                                                                                                                                                                                                                                                                                                                                                                 | 108 |

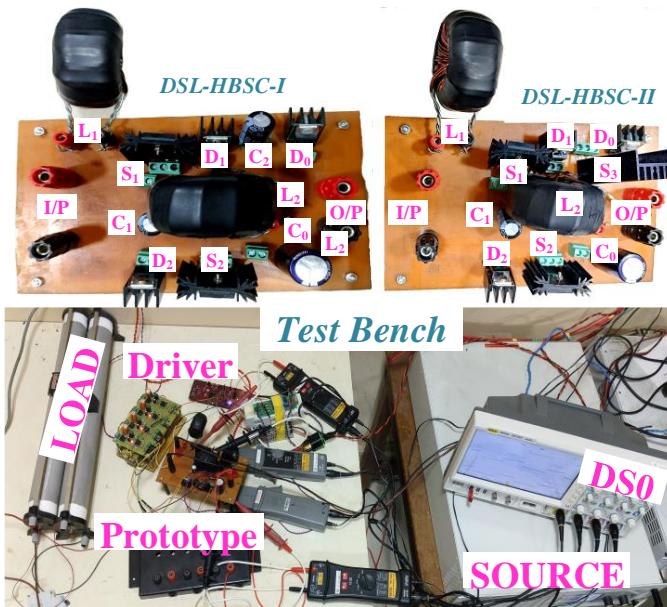

| <b>Figure 7.5.</b> Proposed DSL-HBSC converters and test bench .....                                                                                                                                                                                                                                                                                                                                                                                                                    | 109 |

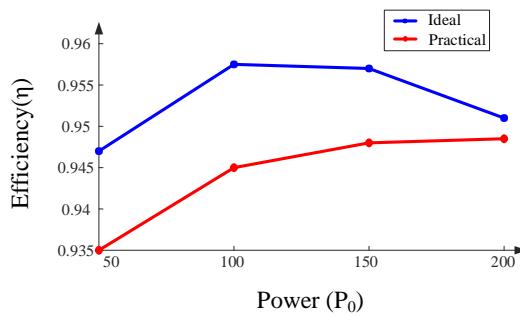

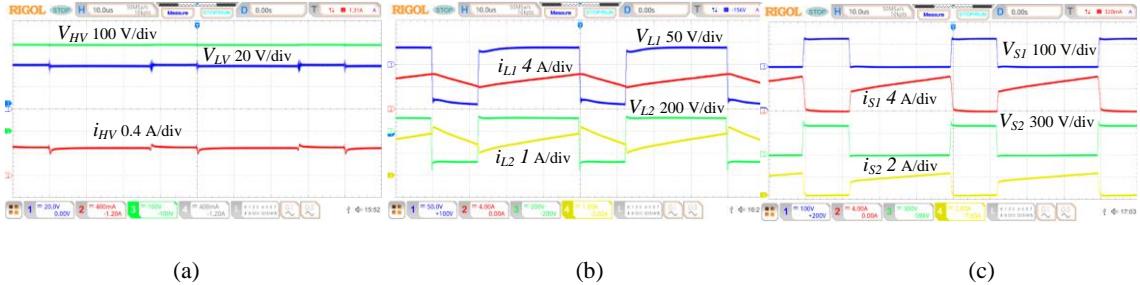

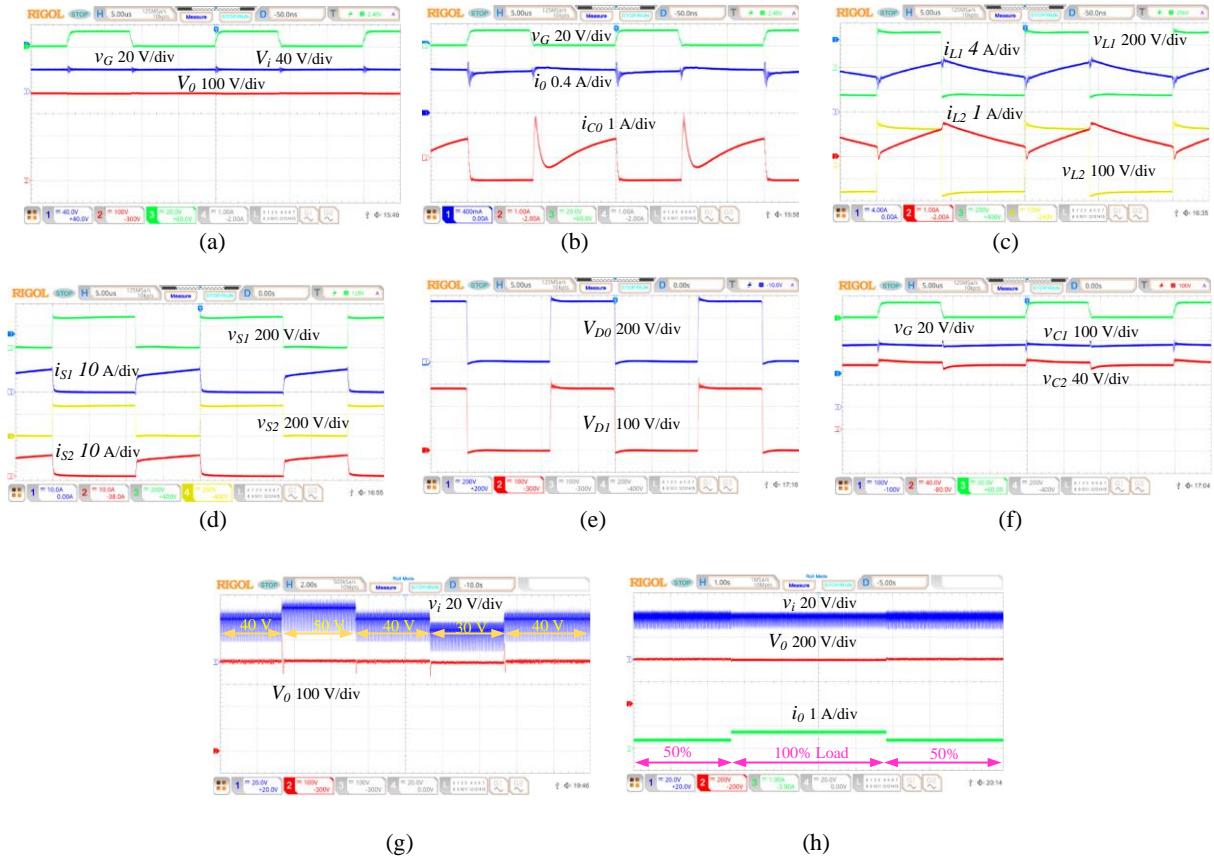

| <b>Figure 7.6.</b> DSL-HBSC-I converter experimental results (a) input and output voltages ( $v_i$ and $v_o$ ) (b) load and capacitor $C_0$ currents ( $i_o$ and $i_{C0}$ ) (c) inductor voltages and currents ( $v_L$ and $i_L$ ) (d) switch voltages and currents ( $v_S$ and $i_S$ ) (e) diode voltages ( $v_{D0}$ and $v_{D1}$ ) (f) capacitor voltages ( $v_{C1}$ and $v_{C2}$ ); closed loop validation (g) stepped $v_i$ and (h) stepped $i_o$ .....                             | 110 |

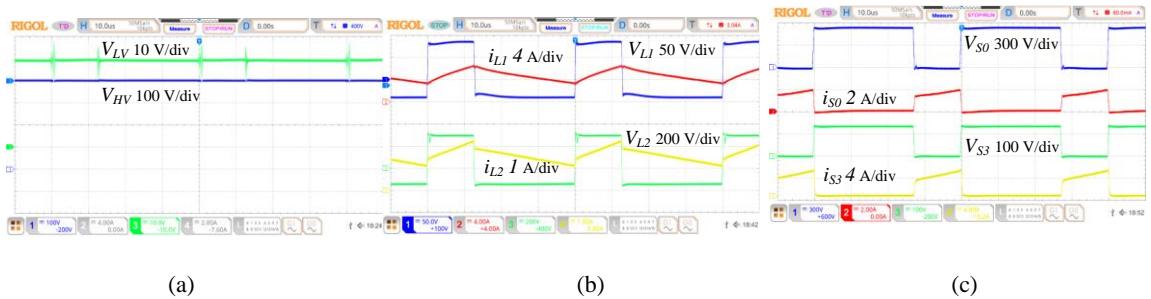

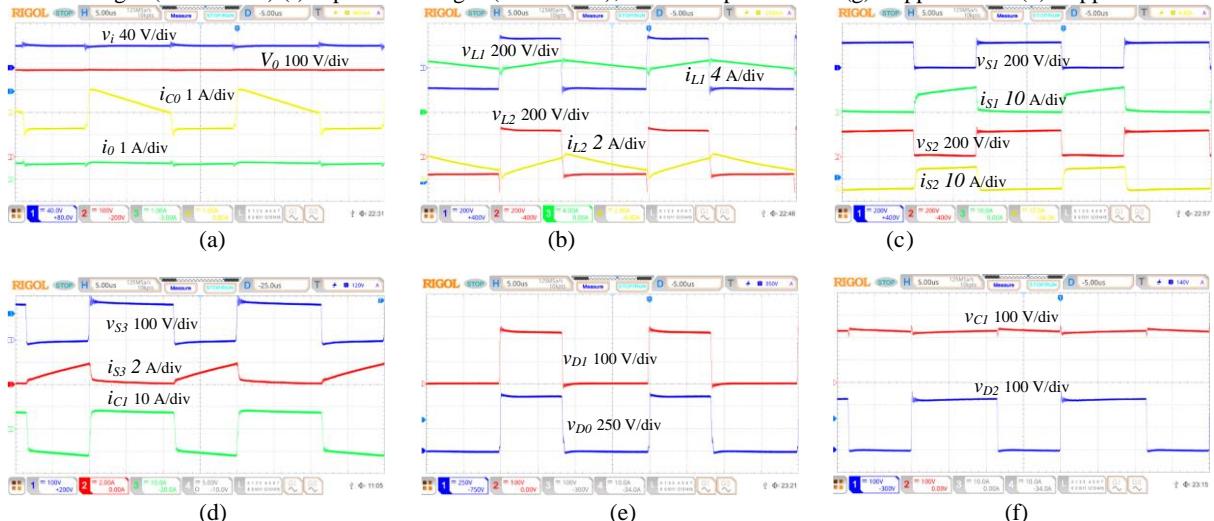

| <b>Figure 7.7.</b> DSL-HBSC-II converter experimental results (a) input and output voltages-currents ( $v_i$ , $v_o$ , $i_{C0}$ and $i_o$ ) (b) inductor voltages and currents ( $v_L$ and $i_L$ ) (c) switch voltages and currents ( $v_{S1/2}$ and $i_{S1/2}$ ) (e) switch $S_3$ voltage-current and capacitor $C_1$ current ( $v_{S3}$ and $i_{S3}$ ; $i_{C1}$ ) (f) diode voltages ( $v_{D0}$ and $v_{D1}$ ) (f) diode $D_2$ and capacitor voltages ( $v_{D2}$ and $v_{C1}$ ) ..... | 110 |

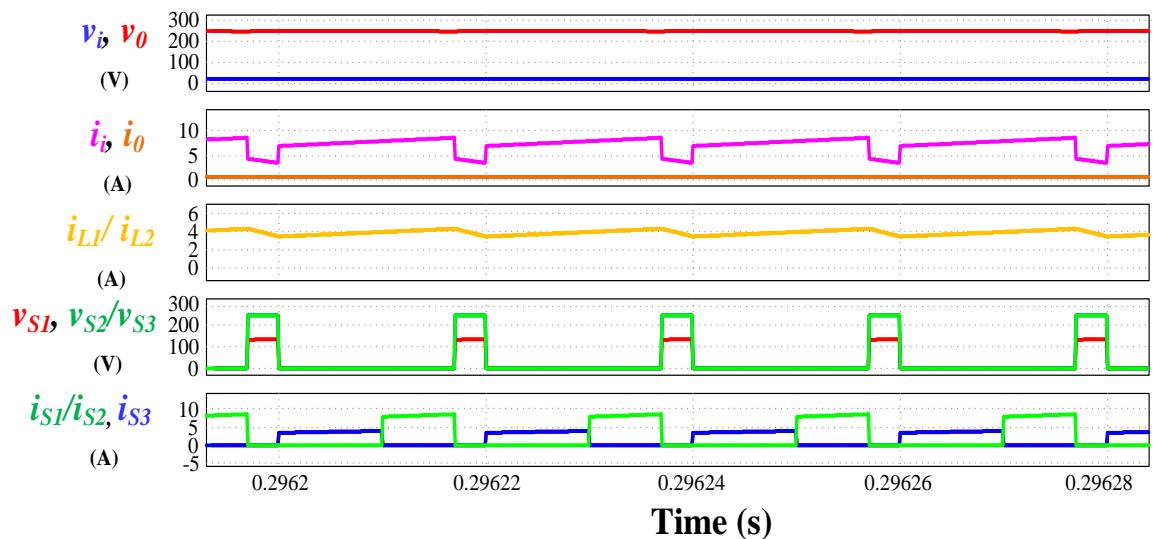

| <b>Figure 7.8.</b> Simulated results of DSL-HBSC-I converter .....                                                                                                                                                                                                                                                                                                                                                                                                                      | 112 |

| <b>Figure 7.9.</b> Simulated results of DSL-HBSC-II converter .....                                                                                                                                                                                                                                                                                                                                                                                                                     | 112 |

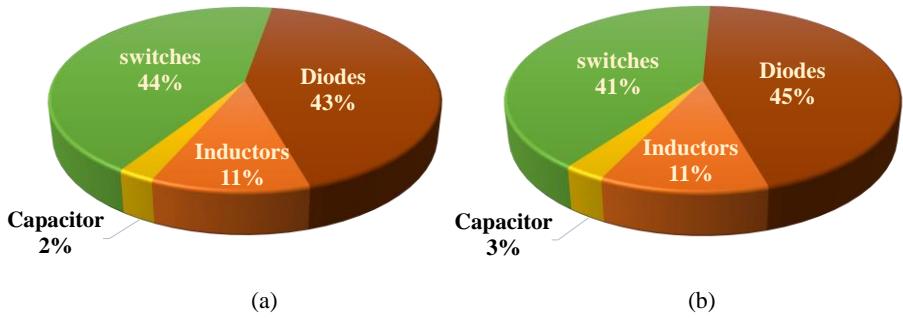

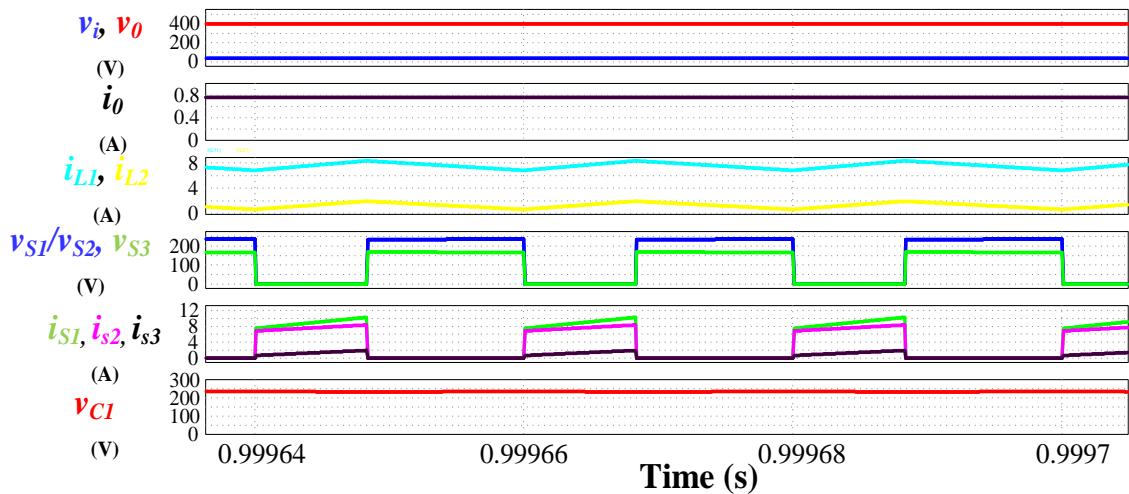

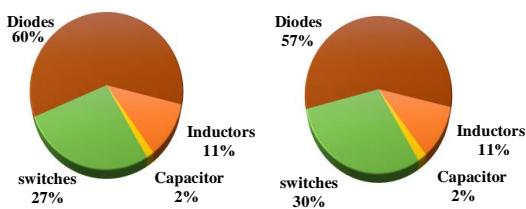

| <b>Figure 7.10.</b> Efficiency and loss distribution of proposed converters .....                                                                                                                                                                                                                                                                                                                                                                                                       | 112 |

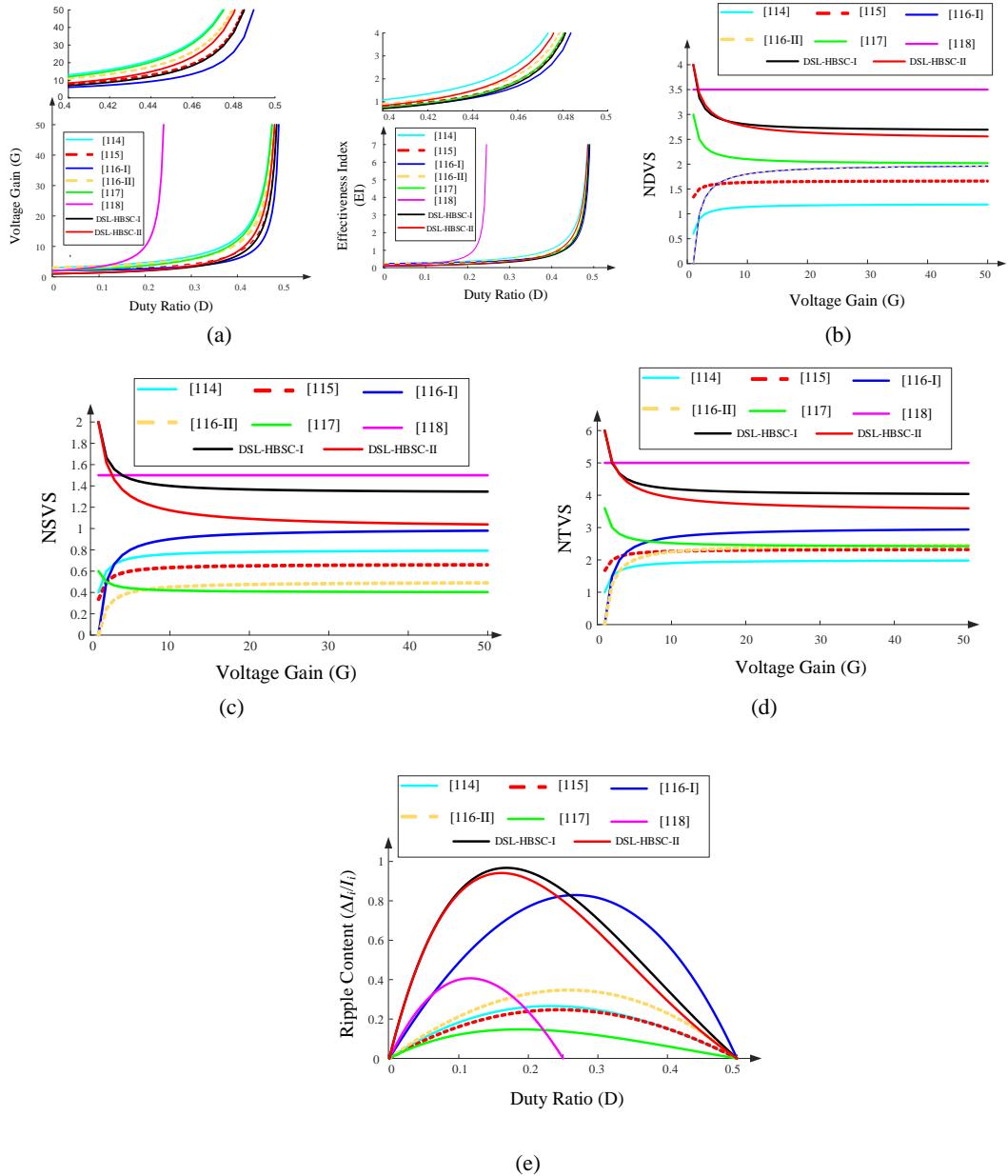

**Figure 7.11.** Proposed converters performance comparison (a)  $G$  and  $EI$  versus  $D$  (b)  $NDVS$  versus  $G$  (c)  $NSVS$  versus  $G$  (d)  $NTVS$  versus  $G$  and (e) per unit source current versus duty ..... 114

# List of Tables

|                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 1.1</b> Precise applications of nonisolated dc-dc converters in terms of power rating, input and output voltages ..... | 6   |

| <b>Table 3.1</b> Prototype Specifications of HSL-CSG converter .....                                                            | 39  |

| <b>Table 3.2</b> Comparison of Nonisolated and Split Duty Converters .....                                                      | 43  |

| <b>Table 3.3</b> Performance comparison of simulation and experimental results of HSL-CSG converter .....                       | 44  |

| <b>Table 4.1</b> Diode-Switch Voltage Stress of ASCQBC-I Converter .....                                                        | 49  |

| <b>Table 4.2</b> Diode-Switch Current Stress of ASCQBC-I Converter .....                                                        | 50  |

| <b>Table 4.3</b> Diode-Switch Voltage Stress of ASCQBC-II Converter .....                                                       | 54  |

| <b>Table 4.4</b> Diode-Switch Current Stress of ASCQBC-II Converter .....                                                       | 55  |

| <b>Table 4.5</b> Design Specifications of ASCQBC converters .....                                                               | 58  |

| <b>Table 4.6</b> Power loss distribution and comparison .....                                                                   | 58  |

| <b>Table 4.7</b> Performance Comparison of ASCQBC Converters .....                                                              | 64  |

| <b>Table 4.8</b> Performance comparison of simulation and experimental results of ASCQBC converters .....                       | 65  |

| <b>Table 5.1</b> Synthesis of Proposed Switched Capacitor based Quadratic Boost DC-DC Converter (SCQBC) .....                   | 69  |

| <b>Table 5.2.</b> Design Specifications of SCQBC converter.....                                                                 | 78  |

| <b>Table 5.3.</b> Comparison of SCQBC Converter with other Quadratic Boost Converters .....                                     | 80  |

| <b>Table 5.4.</b> Performance Comparison of Per Unit Ripple Current and Peak Semiconductor Stresses .....                       | 81  |

| <b>Table 5.5</b> Performance comparison of simulation and experimental results of SCQBC converters .....                        | 84  |

| <b>Table 6.1</b> Design Specifications .of BDC.....                                                                             | 96  |

| <b>Table 6.2</b> Performance comparison of BDC.....                                                                             | 98  |

| <b>Table 6.3</b> Performance comparison of simulation and experimental results of BDC converters .....                          | 100 |

| <b>Table 7.1</b> voltage and current stress of DSL-HBSC-II converter .....                                                      | 109 |

| <b>Table 7.2</b> Design Specifications of DSL-HBSC converters .....                                                             | 113 |

| <b>Table7.3</b> Performance Comparison of DSL-HBSC converters .....                                                             | 115 |

| <b>Table 7.4</b> Performance comparison of simulation and experimental results of DSL-HBSC converters.....                      | 116 |

| <b>Table 8.1</b> Specific outcomes of listed contributions.....                                                                 | 120 |

## Abbreviations

|      |                               |

|------|-------------------------------|

| AC   | Alternating Current           |

| ASC  | Active switched Capacitor     |

| ASL  | Active switched inductor      |

| BDC  | Bidirectional DC-DC converter |

| C    | Capacitors                    |

| CCM  | Continuous conduction mode    |

| CG   | Common ground                 |

| CIC  | Continuous input current      |

| CSG  | Common switch grounding       |

| DC   | Direct Current                |

| DCM  | Discontinuous conduction mode |

| DSO  | Digital Storage Oscilloscope  |

| DSP  | Digital Signal Processor      |

| EI   | Effectiveness index           |

| EMI  | Electromagnetic interference  |

| ESD  | Energy store devices          |

| ESR  | Equivalent series resistance  |

| EV   | Electric vehicle              |

| FC   | Fuel cell                     |

| FPGA | Field Programmable Gate Array |

| HES  | Hybrid energy source          |

| HGQB | High gain quadratic boost     |

| HSL  | Hybrid switched inductor      |

| IB   | Interleaved boost             |

| KVL  | Kirchhoff's voltage law       |

|      |                                                    |

|------|----------------------------------------------------|

| L    | Inductors                                          |

| NDVS | Normalised diode voltage stress                    |

| NMP  | Non-minimum phase                                  |

| NSVS | Normalised switch voltage stress                   |

| NTVS | Normalised total voltage stress                    |

| PCB  | Printed circuit board                              |

| PI   | Proportional-integral                              |

| PV   | Photovoltaic                                       |