# Zero Voltage Switching Floating Output High Gain Interleaved DC-DC Converter

Sagar S. Hujare

Dept. of Electrical Engg,

NIT Warangal, India.

e-mail: [sagarhujare@rediffmail.com](mailto:sagarhujare@rediffmail.com)

A. Kirubakaran

Dept. of Electrical Engg,

NIT Warangal, India.

e-mail: [a\\_kiruba81@rediffmail.com](mailto:a_kiruba81@rediffmail.com)

**Abstract**—This paper proposes a non-isolated high efficiency high gain DC-DC converter using zero voltage switching for renewable/green power supply system with photovoltaic (PV) cell or fuel cell. Proposed topology uses interleaved structure of boost converter with winding coupled inductor to offer higher power handling capacity, lower ripple for input current and lower semiconductor voltage stress. The power switches are turned on using zero voltage switching (ZVS) and the switch turned off voltage spike is suppressed by using boost type active clamping technique. This enables the use of lower voltage and  $R_{DS-ON}$  MOSFET switch with low switching and conduction losses. Diode turn off current falling rate is controlled by the leakage inductance of coupled inductor and by choosing proper value of leakage inductance, diodes can be turned off using zero current switching (ZCS) and diode reverse recovery problem is alleviated. The significant feature of the proposed topology includes continuous input/output current operation with rid of extreme duty cycle and limited reactive components size. The proposed converter operating modes are analyzed and theoretical waveforms are validated through simulation results.

**Keywords**— soft switching technique, interleave, winding coupled inductor, active clamping circuit.

## I. INTRODUCTION

High performance and high step up dc-dc converters are required in many applications such as electric vehicles, uninterrupted power supplies (UPS) and high intensity discharge (HID) lamp for automobile head lamps. Nowadays, more and more renewable energy sources are promoted around the world, such as photovoltaic (PV) cells and fuel cells which are characterized by low voltage, high current output and have strict current ripple requirement [1, 2, 3]. Consequently, as an important interface, dc-dc converter with high step up gain, low input current ripple, high efficiency and nonisolation is required [4].

Though conventional boost converter can theoretically give infinite voltage gain when duty cycle is close to one, in practice the actual output of boost converter is restricted due to current stress of main switch and diode, diode reverse recovery problem and parasitic elements associated with the converter components which do not allow high voltage gain. Also it is not feasible to use conventional boost converter with high duty cycle due to great variations in output voltage caused by small variation in the duty cycle, leading the boost converter to instability and slow transient response. Hence the boost converter with higher duty cycle degrades the overall

conversion efficiency and also increases the electromagnetic interference (EMI). Therefore, practically realizable voltage gain of basic boost converter is not higher than six [5, 6].

To improve the conversion efficiency and achieve high step up voltage gain, many topologies based on the boost converter have been proposed [7]; the cascaded boost converter proposed in [8] requires two sets of power devices, a magnetic core and control circuits; they thus increase voltage gain at the expense of the higher cost and complex control circuit. The converters using switched capacitors technique with high step up gain presented in [9] is suitable for low power applications, since current stress on semiconductor devices is high because of the charging characteristics of capacitor.

Therefore, to provide high gain voltage support as well as reduction in switching voltage stress, coupled inductors are utilized in [10, 11]. It also efficiently alleviates the reverse recovery problem of the output voltage. However the energy associated with the leakage inductance of the coupled inductor is large due to large input current. Hence, the main switch experiences a high voltage spike across the switch during turn off due to occurrence of resonance between leakage inductor and output capacitor of the switch. This necessitates the use of higher voltage range MOSFET switches and snubber circuit with added cost of converter and also degrades the overall efficiency. Also the single phase single switch topology leads to large input current ripple and limited power handling capacity [12].

Therefore, in this paper, the design of a new high efficiency high voltage gain interleaved dc-dc converter is presented. In this structure, winding coupled inductor is used as both forward and flyback converter. This thus allows the use of switched capacitor technique by charging the capacitor when the coupled inductor behaves like forward converter and discharge in series with the secondary of the coupled inductor when the coupled inductor behaves like flyback converter.

Active clamping technique is used to achieve zero voltage switching (ZVS) turn on of main switches. The leakage inductance of coupled inductor controls the diode turn off current falling rate, turning them off by zero current switching (ZCS) and alleviating the reverse recovery problem. Hence the switching losses are reduced greatly which enable us to go for higher switching frequency and smaller reactive components. The voltage rating of the components is lower than half of the output voltage which adds to reduced cost and smaller size of converter. The active clamping circuit is not connected to input

side but the output side [13] which eliminates the need of extra power diode and clamping capacitor as compared to converter in [14]. The two interleaved converter modules are operated with interleaved PWM technique, i.e. gating pulses is shifted by half of switching time period (T).

## II. PROPOSED TOPOLOGY

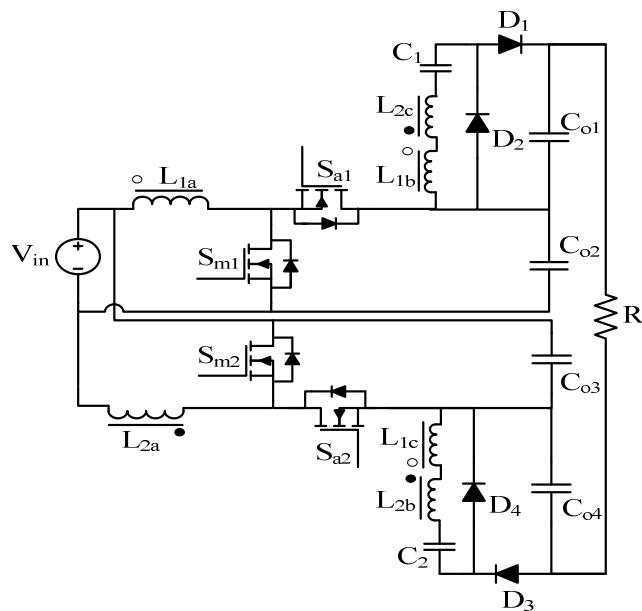

Fig. 1 shows the circuit configuration of the proposed ZVS floating output interleaved input converter. This converter uses boost converter with interleaved input structure and voltage doubler switched capacitor with coupled inductor to achieve high gain and lower input current ripple [12, 15]. ZVS is realized in this converter by using boost type active clamping technique which also recycles the leakage energy of inductor. All the four active switches are turned on using ZVS while the rectifiers are turned off using ZCS. Besides, instead of using two winding coupled inductors, three winding coupled inductors [16] are used with one of the secondary windings of each inductor cross coupled with another phase of interleaved structure. The coupling method of winding coupled inductors is marked by a dark circle and an open circle as shown in Fig.1.

Fig. 1. Circuit configuration of proposed converter.

## III. OPERATION PRINCIPLE

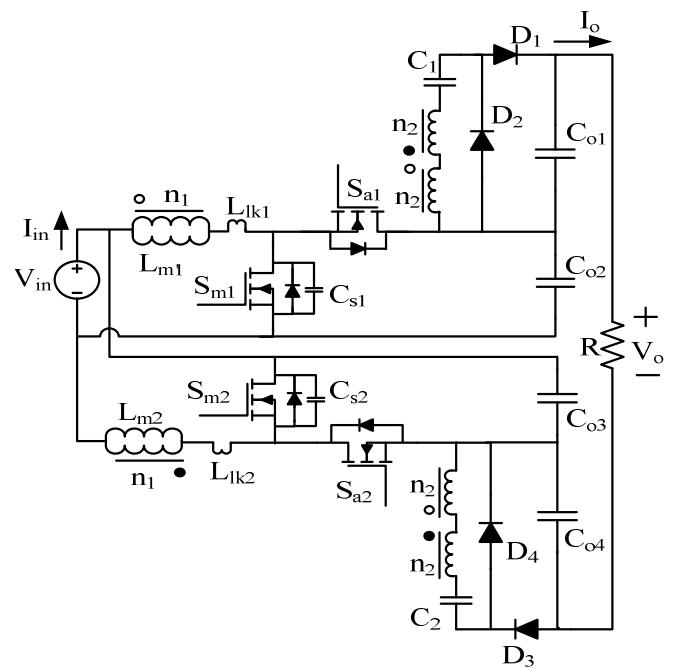

Fig.2 shows the equivalent circuit configuration of the proposed converter.  $L_m$  and  $L_{lk}$  are magnetizing inductors.  $L_{lk1}$  and  $L_{lk2}$  are leakage inductors.  $S_{a1}$  and  $S_{a2}$  are the active clamp or auxiliary switches. Gating pulses of auxiliary switches are complementary to that of main switches.  $C_s$  is the parallel combination of output capacitance main and auxiliary switch.  $C_s$  and  $L_{lk}$  are resonant to achieve ZVS turn on of  $S_m$  and  $S_a$ .

The following assumptions are made to simplify the circuit analysis.

1.  $L_m \gg L_{lk}$ .

2. Winding coupled inductor turns ratio  $N = n_2/n_1$ .

Fig. 2. Simplified circuit model of proposed converter.

3. All the switches are ideal except their output capacitance and anti-parallel diode.

4. Capacitor voltages  $V_{co1}$ ,  $V_{co2}$ ,  $V_{co3}$ ,  $V_{co4}$ ,  $V_{c1}$  and  $V_{c2}$  are almost constant.

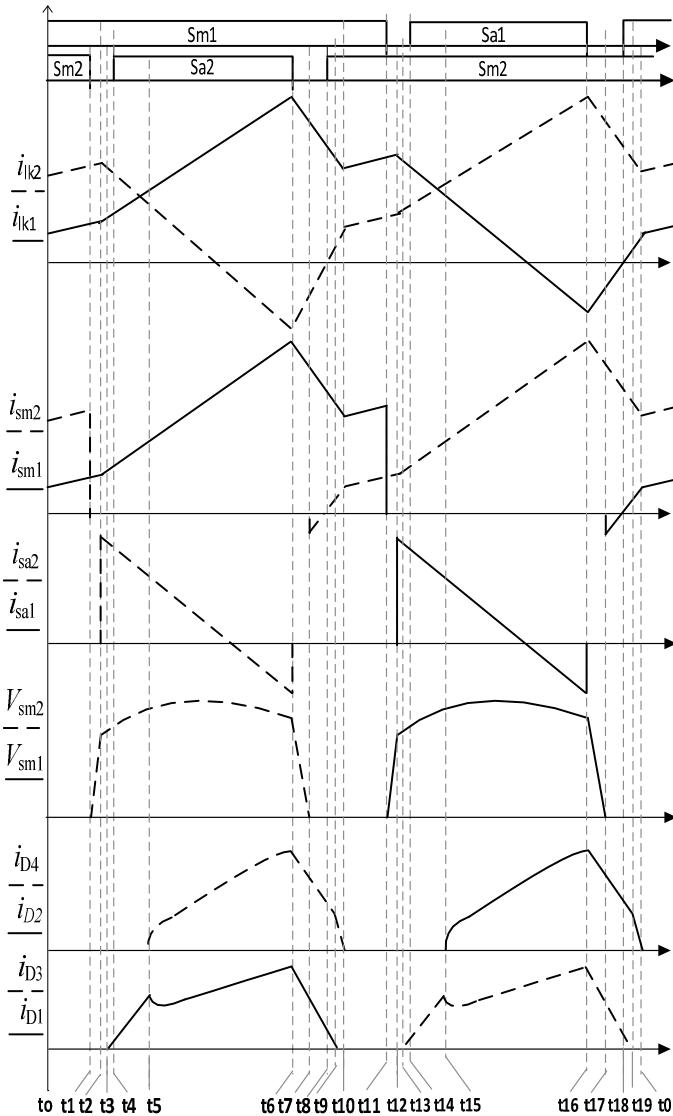

Fig. 3 gives the time sequence of key waveforms of the proposed converter. There are 20 stages in one switching period. Due to symmetry of switching waveforms, only ten stages are analyzed and their corresponding equivalent circuit for each operation stage is highlighted as shown in Fig. 4.

When switch  $S_m$  is closed, the voltage across magnetizing inductor is given by

$$V_{lm} = k * V_{in} \quad (1)$$

Where,

$$k = \frac{L_m}{L_m + L_{lk}}$$

The  $L_{lk} \ll L_m$  hence  $k$  can be considered unity to simplify the analysis.

Mode1. [t0 - t1]: In this mode, the main switches  $S_{m1}$ ,  $S_{m2}$  are closed and the auxiliary switches  $S_{a1}$  and  $S_{a2}$  are off. The diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  are reverse biased, hence no current flows through secondary winding. Magnetizing and leakage inductor are charged linearly by the DC input source  $V_{in}$ .

$$i_{Lm1}(t) = \frac{V_{in}}{L_{m1} + L_{lk1}} t + I_{Lm1}(t0) \quad (2)$$

$$i_{Lm2}(t) = \frac{V_{in}}{L_{m2} + L_{lk2}} t + I_{Lm2}(t0) + I_o \quad (3)$$

Fig. 3. Key waveforms of proposed converter.

Mode 2. [t1 – t2]: In Fig. 3 at t1, main switch  $S_{m2}$  is turned off. Since the value of  $C_{s2}$  is very small it is charged linearly by magnetizing current which is also equal to current through the leakage inductor. In this mode,  $V_{cs2}$  is less than  $V_{co3}$  and anti-parallel diode of  $S_{a2}$  is off. Due to the presence of parallel capacitor  $C_{s2}$ , the main switch  $S_{m2}$  is turned off using ZVS condition. The capacitor voltage is expressed as

$$V_{cs2} = \frac{[I_{Lm2}(t1) + I_o]}{C_{s2}} (t - t1) \quad (4)$$

Mode 3. [t2- t3]: At t2,  $C_{s2}$  is charged to  $V_{co3}$ , since  $C_{s2}$  is smaller all the magnetizing current is diverted to  $C_{o3}$  resulting in anti-parallel diode of  $S_{a2}$  to start conduct; consequently the voltage appearing across the magnetizing inductance  $V_{Lm2}$  decreases as  $V_{co3}$  increases according to voltage divider action

$$V_{Lm2} = \frac{L_{m2}}{L_{m2} + L_{lk2}} (V_{in} - V_{co3}) \quad (5)$$

The switch  $S_{a2}$  should be turned on before  $i_{lk2}$  becomes negative for ZVS turn on.

Mode 4. [t3 – t4]: At t3, the magnetizing voltage  $V_{Lm2}$  is sufficient to induce coupled inductor secondary voltage to forward bias  $D_1$ . Diode  $D_4$  is still reverse biased. Current through leakage inductor  $i_{lk}$  is a summation of the magnetizing current  $i_{Lm}$  and reflected current  $i_{D1}$  through output diode  $D_1$ .

$$I_{lk1}(t) = i_{Lm1}(t) + N * i_{D1}(t) \quad (6)$$

$$I_{lk2}(t) = i_{Lm2}(t) - N * i_{D1}(t) + I_o \quad (7)$$

Mode 5. [t4 – t5]: At t4, the auxiliary switch  $S_{a2}$  is turned on using ZVS condition because its anti-parallel diode is on. Current paths are same as that of previous mode except  $S_{a2}$  is conducting instead of its body diode.

Mode 6. [t5 – t6]: At t5, the  $V_{Lm2}$  is decreased to the value sufficient to forward bias  $D_4$ . As the rate of change of secondary current is controlled by leakage inductance and the voltage across it which is almost constant, the rate at which diode current  $i_{D1}$  was increasing in earlier mode is divided between  $i_{D1}$  and  $i_{D4}$  equally in this mode.

Mode 7. [t6 – t7]: Auxiliary switch  $S_{a2}$  is turned off at t6 terminating resonant circuit between  $i_{lk2}$  and  $C_{o3}$ , and switch capacitance  $C_{s2}$  starts discharging in a resonant manner due to the leakage inductance  $L_{lk2}$ . The auxiliary switch is turned off using ZVS condition due to  $C_{s2}$ .

Mode 8. [t7 – t8]: At t7, capacitor  $C_{s2}$  is discharged completely and anti-parallel diode of  $S_{m2}$  prevent  $C_{s2}$  voltage from going negative. In this interval  $S_{m2}$  can be turned on using ZVS condition.

Mode 9. [t8 – t9]:  $S_{m2}$  is on, and the transformer secondary current decreases as leakage inductor current  $i_{lk}$  increases. At t9 the current through diode  $D_1$  decreases to zero while  $D_4$  is still conducting. The falling rate of diode current is controlled by the leakage inductance and the voltage across it which can be expressed as

$$\frac{di_{D1}(t)}{dt} + \frac{di_{D4}(t)}{dt} \approx \frac{V_{co3}}{2N * L_{lk}} \quad (8)$$

From (8) it is observed that, as the secondary current is divided between two diodes, a small value of leakage inductance is sufficient to achieve ZCS turn off of diodes.

Mode 10. [t9 – t10]: At t9, the transformer secondary current is flowing through  $D_4$  which is decreasing linearly and almost at twice rate as compared to previous mode. At t10, secondary current decreases to zero and  $D_4$  is reverse biased, and the current through  $L_{lk2}$  is equal to current through  $L_{m2}$ .

$$\frac{di_{D4}(t)}{dt} \approx \frac{V_{co3}}{2N * L_{lk}} \quad (9)$$

A similar operation is repeated in the remaining ten stages of a switching period. Hence the input current ripple has a frequency twice that of the operating frequency. Fig. 4 shows the equivalent circuit of each operating mode in the half cycle of switching period.

Fig. 4. Operating modes of proposed converter for half of a switching period.

#### IV. CHARACTERISTICS

##### A. DC Conversion Ratio

The output voltage at any given moment can be expressed as

$$V_o = V_{co1} + V_{co2} + V_{co3} + V_{co4} - V_{in} \quad (10)$$

By applying voltage-second balance to the magnetizing inductor and ignoring the effect of leakage inductance, the voltages  $V_{co1}$ ,  $V_{co2}$ ,  $V_{co3}$  and  $V_{co4}$  are given by

$$V_{co2} = V_{co3} = \frac{1}{1-D} V_{in} \quad (11)$$

$$V_{c1} = V_{c2} = N * V_{co3} \quad (12)$$

$$V_{co1} = V_{co4} = 2N * V_{co3} \quad (13)$$

Substituting (11) and (13) in (10) the expression for voltage gain can be obtained as presented in (14)

$$M = \frac{V_o}{V_{in}} = \frac{4N + 1 + D}{1 - D} \quad (14)$$

From (14) the voltage gain is large even if  $N=1$ . So, moderate duty cycle ( $D$ ) can be used in proposed converter as compared to conventional boost converter which can reduce input and output current ripple.

##### B. Voltage Stress of Semiconductor Devices

The filter capacitor of a conventional boost converter itself acts as clamping capacitor, which is large enough to suppress the switch turned off voltage spike.

The normalized voltage stress of active devices is given by

$$V_{sm1, stress} = V_{sm2, stress} = V_{co2} = \frac{1}{1-D} V_{in} \quad (15)$$

$$V_{sa1, stress} = V_{sa2, stress} = V_{co2} = \frac{1}{1-D} V_{in} \quad (16)$$

From (15) and (16) voltage stress of power switches can be controlled by controlling duty cycle and transformer turns ratio. So, low voltage and high performance device can be used to reduce switching and conduction losses.

##### C. Soft Switching Performance

Because of auxiliary active clamping circuit all semiconductor switches are turned on with ZVS due to which switching losses are reduced. Also, all the diodes are turned off using ZCS due to presence of leakage inductance in coupled inductor.

$$\frac{di_{D1}(t)}{dt} + \frac{di_{D4}(t)}{dt} \approx \frac{V_{co3}}{2N * L_{lk}} \quad (17)$$

$$\frac{di_{D2}(t)}{dt} + \frac{di_{D3}(t)}{dt} \approx \frac{V_{co2}}{2N * L_{lk}} \quad (18)$$

#### V. SYSTEM DESIGN

##### A. Turns Ratio Selection

In this converter, turns ratio selection determines the voltage stress of power devices, diode current falling rate and duty ratio. Hence turns ratio should be chosen carefully. We assumed that the effective maximum duty cycle of  $S_{m1}$  and  $S_{m2}$  is  $D_{max}$ . The turns ratio for minimum input voltage  $V_{in}$  is given by

$$N = \frac{n2}{n1} = \frac{1}{4} \left[ \frac{V_o}{V_{in, min}} (1 - D_{max}) - 1 - D_{max} \right] \quad (19)$$

##### B. Power Device Selection

Assuming the clamp capacitor is large enough to suppress the voltage spike caused by the leakage inductor, the voltage stress of main and auxiliary switch is given by

$$V_{sm1, stress} = V_{sm2, stress} = \frac{1}{1-D} V_{in} \quad (20)$$

$$V_{sa1, stress} = V_{sa2, stress} = \frac{1}{1-D} V_{in} \quad (21)$$

From (20) & (21) voltage stress of switches is less than one fourth of output voltage, which makes it suitable for high performance switch with low voltage stress and  $R_{DS\_ON}$ .

##### C. Leakage Inductor Design

The leakage inductance has a direct influence on the diode turn off current falling rate; as the diode reverse recovery charge depends on diode turn off current falling rate,  $L_{lk}$  is selected to alleviate diode reverse recovery problem.

$$L_{lk} \approx \frac{V_{co3}}{2N \left[ \frac{di_D(t)}{dt} \right]} \quad (22)$$

Where,  $i_D(t)$  is the total secondary current flowing through output diodes.

From (22) a small amount of leakage inductor is also sufficient to keep lower current falling rate.

##### D. Capacitors Selection

In this converter, the clamp capacitor and filter capacitor of conventional boost are integrated. This capacitor is designed to minimize output voltage ripple and suppress the switch turn off voltage spike and to avoid excessive resonant ringing [17] due to parasitic elements of the power switch and transformer. A capacitor of minimum capacitance value is selected so that one half of resonant period exceeds the maximum turn off time of main switches, which is given by

$$C_{o2} \geq C_{o3} \geq \frac{(1 - D_{min})T^2}{\pi^2 * L_{lk}} \quad (23)$$

## VI. SIMULATION RESULTS

The proposed converter is developed in MATLAB/SIMULINK environment for 600 watt capacity to verify the theoretical waveforms using simulation results in steady state condition. The nominal input voltage is 40V and the minimum and maximum input voltages are 35 and 48V respectively. Output voltage is maintained constant at 400V. Selected switching frequency is 100 kHz and duty cycle (D) range is from 0.5 to 0.65. It should be noted that to achieve ZVS on main switches, the duty cycle must be greater than 0.5. Table I summarizes the converter specifications and the values of components used. Key simulated waveforms of proposed converter at full load condition are shown.

TABLE I. CONVERTER SPECIFICATIONS

| Parameters                                   | Value        |

|----------------------------------------------|--------------|

| Input voltage (Vin)                          | 35 - 48V     |

| Output voltage (Vo)                          | 400V         |

| Output power (Po)                            | 600 W        |

| Switching frequency (f)                      | 100 kHz      |

| Transformer turns ratio (N)                  | 0.7          |

| Capacitors: C <sub>o1</sub> ,C <sub>o4</sub> | 30 $\mu$ F   |

| C <sub>o2</sub> , C <sub>o3</sub>            | 17 $\mu$ F   |

| C <sub>1</sub> , C <sub>2</sub>              | 20uF         |

| C <sub>s</sub>                               | 1.5nF        |

| Magnetizing inductance (L <sub>m</sub> )     | 47 $\mu$ H   |

| Leakage inductance, L <sub>lk</sub>          | 1.15 $\mu$ H |

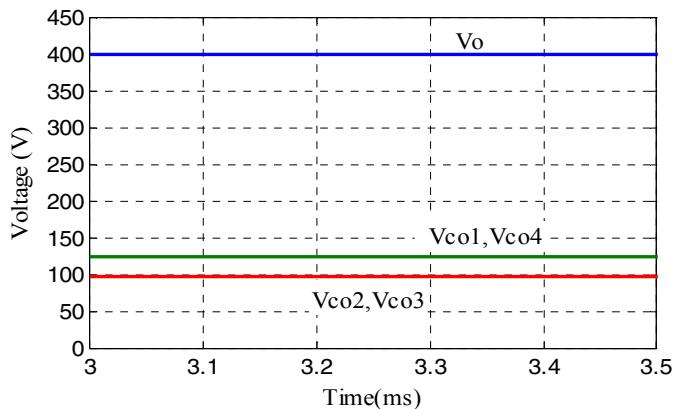

Fig. 5 gives the simulated output voltage waveforms of proposed DC-DC converter. The voltage across capacitors C<sub>o1</sub>, C<sub>o4</sub> and C<sub>o2</sub>, C<sub>o3</sub> are equal. The difference between V<sub>co1</sub>, V<sub>co4</sub> and V<sub>co2</sub>, V<sub>co3</sub> depends on the transformer turns ratio selected. The voltage across individual capacitors is less than half of output voltage which will reduce the size and cost of capacitors.

Fig. 5. Output voltage and voltages across each capacitor at full load.

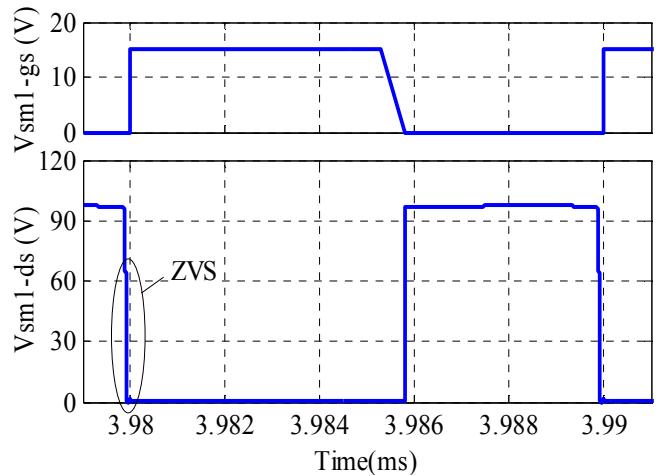

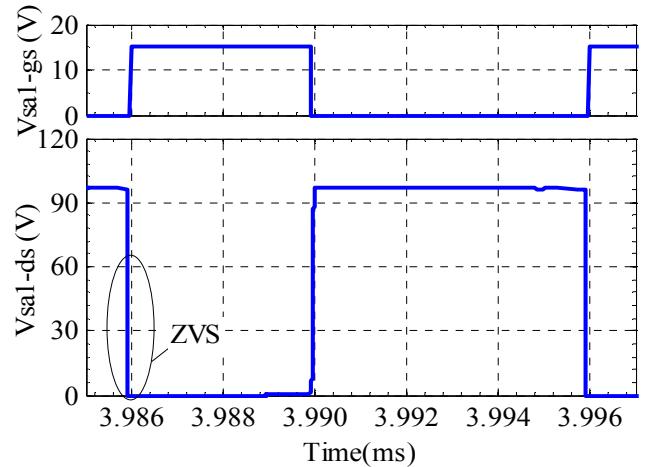

Fig. 6 and 7 give the gate voltages and drain voltages of active switches S<sub>m</sub> and S<sub>a</sub>. Before switches S<sub>m</sub> and S<sub>a</sub> are gated, the drain to source voltages are brought down to zero. Thus all semiconductor switches are turned on with ZVS. Also voltage stress of switches is smaller as compared to output voltage, which ensures that high performance switch with low R<sub>DS-ON</sub> can be used. Hence both switching and conduction losses are reduced which improves the efficiency of converter. The voltage spike across the switch is clamped effectively by

output capacitors and the energy associated with leakage inductor is recovered.

Fig. 6. Simulated results of gate voltage and drain voltage of switch S<sub>m1</sub> at full load condition.

Fig. 7. Simulated results of gate voltage and drain voltage of switch S<sub>a1</sub> at full load condition.

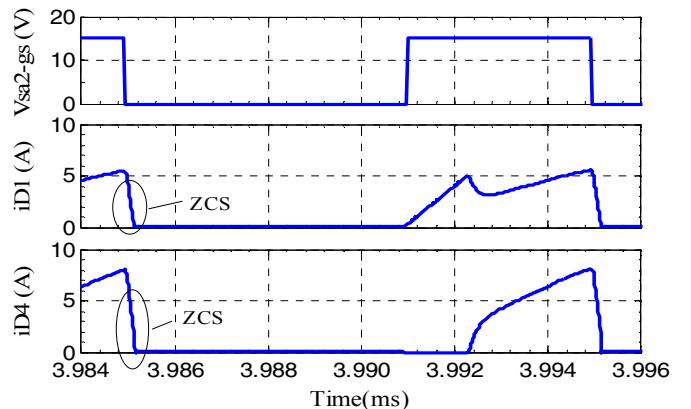

Fig. 8 shows simulated waveforms of gate voltage V<sub>sa2,gs</sub> and diode currents i<sub>D1</sub> and i<sub>D4</sub>. Diode currents are decreased to zero with lower d<sub>iD</sub>/dt and the diodes are turned off at ZCS. Hence diode reverse recovery problem is alleviated.

Fig. 8. Simulated waveforms of V<sub>sa2,gs</sub> and diode currents i<sub>D1</sub> and i<sub>D4</sub> at full load condition.

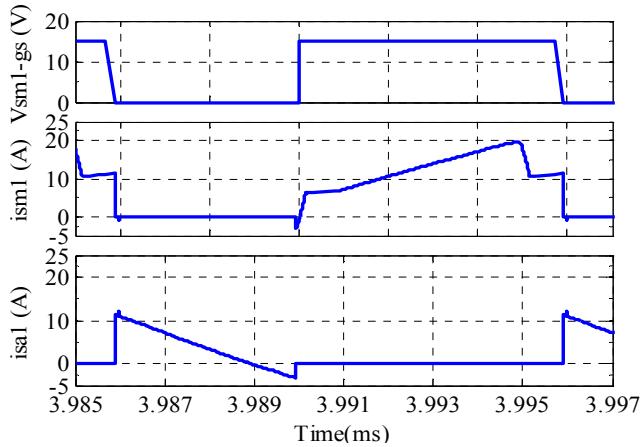

Fig. 9 shows the gate voltage  $V_{sm1,gs}$  and current flowing through main switch  $S_m$  and auxiliary switch  $S_a$ .

Fig. 9. Simulated waveforms of  $V_{sm1,gs}$ , switch current  $i_{sm1}$  and current  $i_{sal}$  at full load condition.

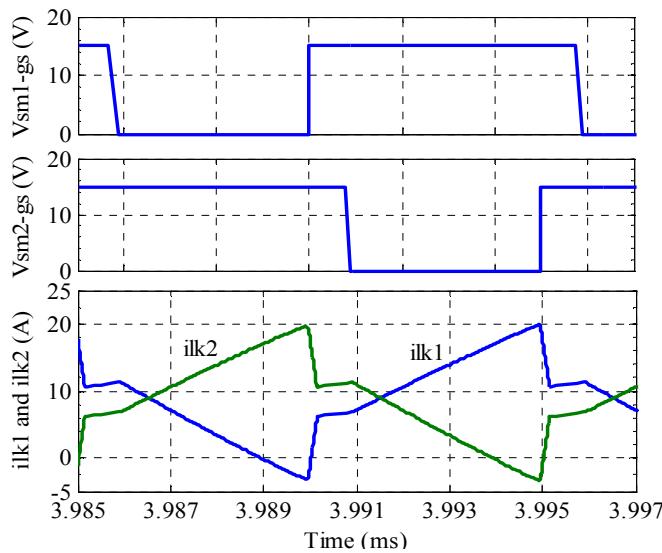

Fig. 10 shows the current flowing in the leakage inductance  $L_{lk1}$  and  $L_{lk2}$ . From simulated waveforms, it is observed that these currents are approximately mirror replica of each other which results in input current ripple cancellation. Thus interleaved structure helps in reducing input current ripple as well as increasing converter power level.

Fig. 10. Simulated waveforms of  $V_{sm1,gs}$ ,  $V_{sm2,gs}$ , current  $i_{lk1}$  and  $i_{lk2}$  at full load condition.

## VII. CONCLUSION

This paper introduces a novel interleaved input floating output boost converter with winding coupled inductor which offers large voltage gain with the help of proper turn ratio selection. Consequently the power switch has lower voltage stress. Power switch turn off voltage spike is suppressed and leakage energy of coupled inductor is released in output through clamp capacitors. In addition, all semiconductor devices are switched on/off using soft switching scheme i.e. power switches are turned on by using ZVS while all diodes are turned off using ZCS improving the efficiency. Interleaved

structure with winding coupled inductor adds lower input and output current ripples, smaller size of reactive component and turns ratio which in turn reduces the overall size and cost of converter.

## REFERENCES

- [1] F. Blaabjerg, Z. Chen, and S.B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Trans. Power Electronics*, vol. 19, no. 5, pp. 1184-1194, Sep. 2004.

- [2] S.B. Kjaer, J.K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Industry Applications*, vol. 41, no. 5, pp. 1292-1306, Sep. 2005.

- [3] Q. Li, and P.J. Wolfs, "A review of the single phase photovoltaic module integrated converter topologies with three different DC link configurations," *IEEE Trans. Power Electronics*, vol. 23, no. 3, pp. 1320-1333, May 2008.

- [4] Q. Zhao, and F.C. Lee, "High-efficiency high step-up DC/DC converters," *IEEE Trans. Power Electron.*, 2003, 1, (1), pp. 65-73.

- [5] R.W. Erickson, and D. Maksimovic, "Fundamentals of power electronics", Kluwer Academic, 2nd edn., 2001.

- [6] N. Mohan, T. Undeland, and W. Robbins, "Power Electronics-Converters, Applications, and Design," 2nd ed. New York: Wiley, 1995.

- [7] W. Li, and X. He, "Review of nonisolated high-step-up DC/DC converters in photovoltaic grid-connected applications," *IEEE Trans. Ind. Electron.*, 2011, 58, (4), pp. 1239-1250.

- [8] X.G. Feng, J.J. Liu, and F.C. Lee, "Impedance specifications for stable dc distributed power systems," *IEEE Trans. Power Electron.*, vol. 17, no. 2, pp. 157-162, Mar. 2002.

- [9] O. Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Step-up switching-mode converter with high voltage gain using a switched-capacitor circuit," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 50, 1098-1102, 2003.

- [10] P.M. Barbosa, and I. Barbi, "A single-switch flyback current-fed DC-DC converter," *IEEE Trans. Power Electronics*, vol. 13, no. 3, pp. 466-475, May 1998.

- [11] C.W. Roh, S.H. Han, and M.J. Youn, "Dual coupled inductor fed isolated boost converter for low input voltage applications," *Electron. Lett.*, 1999, 35, pp. 1791-1792.

- [12] T.J. Liang, S.M. Chen, L.S. Yang, J.F. Chen and A. Ioinovici, "Ultra-large gain step-up switched-capacitor dc-dc converter with coupled inductor for alternative sources of energy," *IEEE Trans. on Circuits Syst. I*, vol. 59, no. 4, April 2012.

- [13] H.W. Seong, H.S. Kim, K.B. Park, G.W. Moon and M.J. Youn, "High step-up dc-dc converters using zero-voltage switching boost integration technique and light-load frequency modulation control," *IEEE Trans. On Power Electron.*, vol. 27, no. 3, March 2012.

- [14] B.R. Lin, and J.Y. Dong, "New zero-voltage switching DC-DC converter for renewable energy conversion systems," *IET Power Electron.*, vol. 5, Iss. 4, pp. 393-400, 2012.

- [15] S. Choi, V.G. Agelidis, J. Yang, D. Coutellier and P. Marabeas, "Analysis, design and experimental results of a floating-output interleaved-input boost-derived DC-DC high-gain transformer-less converter," *IET Power Electron.*, vol. 4, Iss. 1, pp. 168-180, 2011.

- [16] W. Li, and X. He, "A Family of Interleaved DC-DC Converters Deduced From a Basic Cell With Winding-Cross-Coupled Inductors (WCCIs) for High Step-Up or Step-Down Conversions," *IEEE Trans. Power Electron.*, vol. 23, no. 4, July 2008.

- [17] R. Watson, F.C. Lee, and G.C. Hua, "Utilization of an active-clamp circuit to achieve soft switching in flyback converters," *IEEE Trans. Power Electron.*, 1996, 1, (1), pp. 162-169.